Universitat Politècnica de València Departament de Informàtica de Sistemes i Computadors

## Floorplan-Aware High Performance NoC Design

A dissertation submitted in partial fulfilment of the requirements for the degree of

> Doctor of Philosophy (Computer Engineering)

> > Author Antoni Roca Pérez

> > > Advisor

José Flich Cardo Federico Silla

VALÈNCIA, 2012

Contents

## Contents

| 1        | Intr | oducti  | ion                                                                                         | 1  |

|----------|------|---------|---------------------------------------------------------------------------------------------|----|

|          | 1.1  | Motiva  | ation                                                                                       | 1  |

|          |      | 1.1.1   | Network-On-Chip                                                                             | 2  |

|          |      | 1.1.2   | NoC Topologies                                                                              | 4  |

|          |      | 1.1.3   | Crossbars                                                                                   | 8  |

|          |      | 1.1.4   | Contribution                                                                                | 11 |

|          | 1.2  | Object  | tives                                                                                       | 15 |

|          | 1.3  | Disser  | tation Outline                                                                              | 16 |

| <b>2</b> | Tec  | hnical  | Background and Related Work                                                                 | 17 |

|          | 2.1  | On-ch   | ip Interconnection Networks                                                                 | 17 |

|          |      | 2.1.1   | Design Factors                                                                              | 18 |

|          | 2.2  | Interco | onnection Network Basics                                                                    | 19 |

|          |      | 2.2.1   | Network Topology                                                                            | 20 |

|          |      | 2.2.2   | The Switch $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 28 |

|          |      | 2.2.3   | Data Units                                                                                  | 29 |

|          |      | 2.2.4   | Switching                                                                                   | 30 |

|          |      | 2.2.5   | Flow Control                                                                                | 36 |

|          |      | 2.2.6   | Arbitration                                                                                 | 37 |

|          |      | 2.2.7   | Routing                                                                                     | 38 |

|          | 2.3  | Relate  | ed Work                                                                                     | 39 |

|          |      | 2.3.1   | Switch Design                                                                               | 39 |

|          |      | 2.3.2   | High-Performance NoC Topologies                                                             | 43 |

|          |      | 2.3.3   | Long Link Issues                                                                            | 45 |

| 3        | Mo                   | dular Switch 4                                                                                     |     |  |  |  |

|----------|----------------------|----------------------------------------------------------------------------------------------------|-----|--|--|--|

|          | 3.1 Canonical Switch |                                                                                                    |     |  |  |  |

|          | 3.2                  | Modular Switch                                                                                     | 51  |  |  |  |

|          |                      | 3.2.1 Output Port Controller                                                                       | 51  |  |  |  |

|          |                      | 3.2.2 AC Module                                                                                    | 52  |  |  |  |

|          |                      | 3.2.3 RC Module                                                                                    | 55  |  |  |  |

|          |                      | 3.2.4 Advantages and Disadvantages of the Design $\ldots$ .                                        | 56  |  |  |  |

|          |                      | 3.2.5 Flow Control                                                                                 | 57  |  |  |  |

|          |                      | 3.2.6 AC Module Radix Comparison                                                                   | 61  |  |  |  |

|          | 3.3                  | Modular Switch Analysis                                                                            | 62  |  |  |  |

|          | 3.4                  | Network Performance with Synthetic traffic                                                         | 65  |  |  |  |

|          |                      | 3.4.1 AC Radix Influence                                                                           | 67  |  |  |  |

|          | 3.5                  | Application Performance and Power Consumption $\ldots \ldots \ldots$                               | 70  |  |  |  |

|          | 3.6                  | Reliability Analysis                                                                               | 73  |  |  |  |

|          | 3.7                  | Conclusions                                                                                        | 76  |  |  |  |

| 4        | Dist                 | tributed Switch                                                                                    | 77  |  |  |  |

|          | 4.1                  | Distributed Switch                                                                                 | 78  |  |  |  |

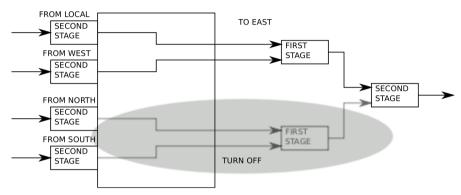

|          |                      | 4.1.1 Reducing Power Consumption                                                                   | 81  |  |  |  |

|          |                      | 4.1.2 Distributed Switch With Spread Buffers                                                       | 82  |  |  |  |

|          |                      | 4.1.3 Wire Design $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 83  |  |  |  |

|          | 4.2                  | Distributed Switch Analysis                                                                        | 86  |  |  |  |

|          |                      | 4.2.1 Link Delay vs Link Length                                                                    | 86  |  |  |  |

|          |                      | 4.2.2 Area Results                                                                                 | 86  |  |  |  |

|          |                      | 4.2.3 Power Consumption                                                                            | 89  |  |  |  |

|          |                      | 4.2.4 Operating Frequency vs. Peak Power Consumption                                               | 97  |  |  |  |

|          |                      | 4.2.5 Variability Robustness                                                                       | 98  |  |  |  |

|          |                      | 4.2.6 Fault Tolerance                                                                              | 99  |  |  |  |

|          | 4.3                  | Leverage Distributed Switch to FPGA Environment 1                                                  | 00  |  |  |  |

|          | 4.4                  | Conclusions                                                                                        | 102 |  |  |  |

| <b>5</b> | Hig                  | h-Radix Topologies 1                                                                               | 05  |  |  |  |

|          | 5.1                  | Topology Comparison                                                                                | 106 |  |  |  |

|          | 5.2                  | Distributed High-Radix Topologies                                                                  | .08 |  |  |  |

|          | 5.3                  | Implementation Analysis                                                                            | 12  |  |  |  |

|              | 5.4   | Network Performance                                                                 |

|--------------|-------|-------------------------------------------------------------------------------------|

|              | 5.5   | Conclusions                                                                         |

| 6            | A D   | istributed Crossbar 121                                                             |

|              | 6.1   | A Distributed Pipelined Decoupled Crossbar $\ \ . \ . \ . \ . \ . \ . \ . \ . \ . $ |

|              |       | 6.1.1 DC Floorplan                                                                  |

|              |       | 6.1.2 Flow Control                                                                  |

|              |       | 6.1.3 Hierarchical Distributed Crossbar                                             |

|              | 6.2   | Implementation Analysis                                                             |

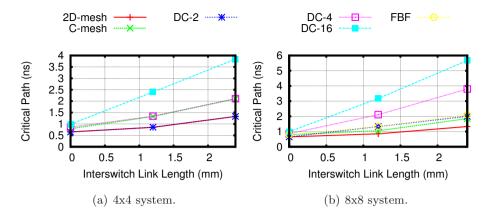

|              |       | 6.2.1 Critical Path $\ldots$ 134                                                    |

|              |       | 6.2.2 Area and Wiring Analysis                                                      |

|              | 6.3   | Performance Analysis                                                                |

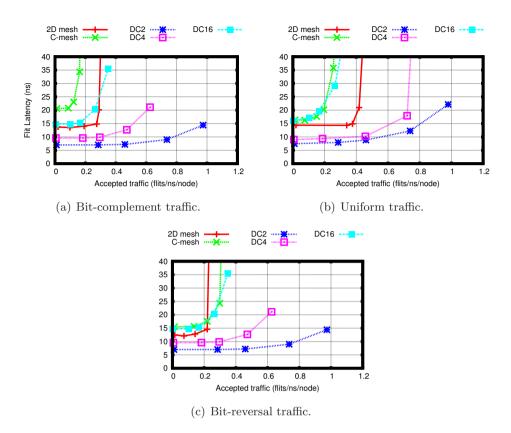

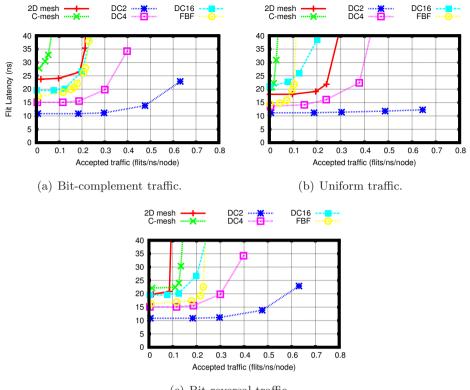

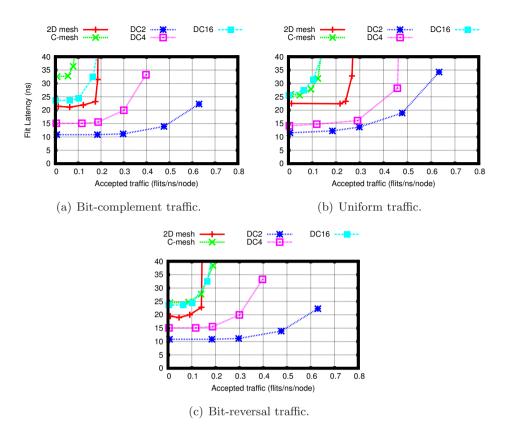

|              |       | 6.3.1 Synthetic traffic                                                             |

|              |       | 6.3.2 $$ Performance an Energy Results With Applications $$ 142 $$                  |

|              | 6.4   | Hierarchical Distributed Crossbar Performance                                       |

|              | 6.5   | Conclusions                                                                         |

| 7            | Con   | clusions 149                                                                        |

|              | 7.1   | Conclusions                                                                         |

|              | 7.2   | Contributions                                                                       |

|              | 7.3   | Future Work                                                                         |

|              | 7.4   | Publications                                                                        |

| $\mathbf{A}$ | Can   | onic Switch Model 157                                                               |

|              | A.1   | gNoC: A Switch Design for CMP Systems $\hdots$                                      |

|              |       | A.1.1 Pipeline Organization                                                         |

|              |       | A.1.2 Flow Control                                                                  |

|              |       | A.1.3 Virtual Channel Support                                                       |

|              |       | A.1.4 Switch Implementation                                                         |

|              |       | A.1.5 Virtual Cut-Through and Tree-Based Broadcast Support 166                      |

|              |       | A.1.6 High-radix Switches                                                           |

|              |       | A.1.7 Variability in the Router                                                     |

| Bi           | bliog | raphy 175                                                                           |

Contents

# List of Figures

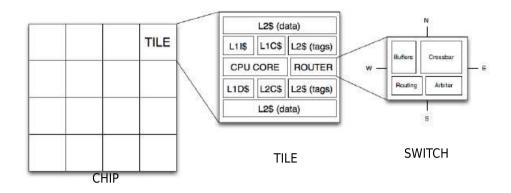

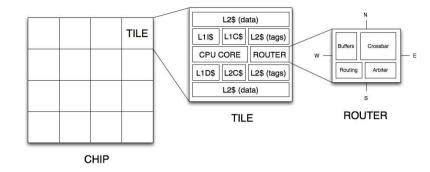

| 1.1            | Tiled CMP                                                                      | 2               |

|----------------|--------------------------------------------------------------------------------|-----------------|

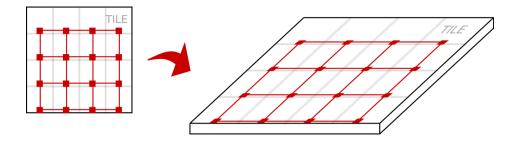

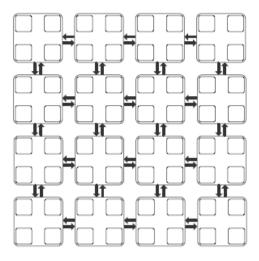

| 1.2            | 2D mesh planar scalability schematic                                           | 3               |

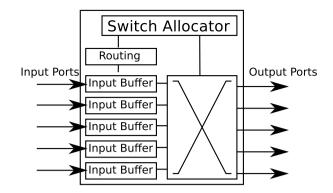

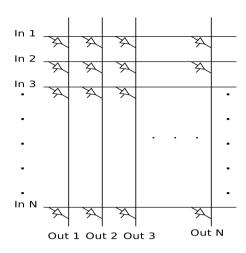

| 1.3            | $5\times 5$ crossbar-based canonical switch schematic                          | 4               |

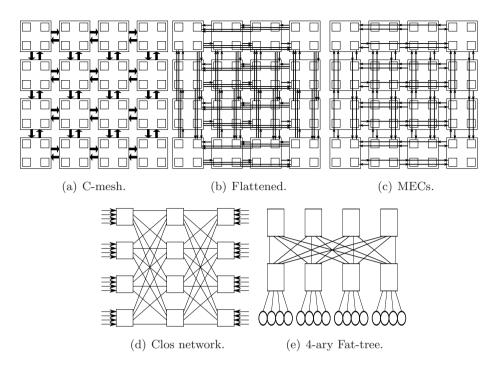

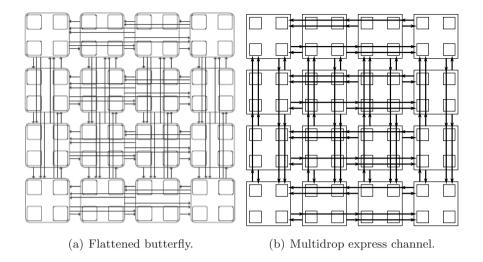

| 1.4            | Complex network topologies.                                                    | 6               |

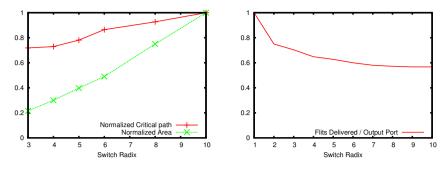

| 1.5            | Switch properties as a function of switch radix                                | 8               |

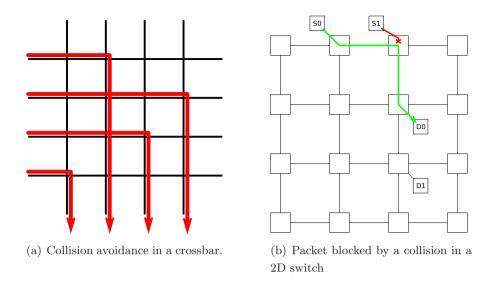

| 1.6            | Crosspoint-based crossbar                                                      | 9               |

| 1.7            | Collision avoidance in a crossbar network                                      | 10              |

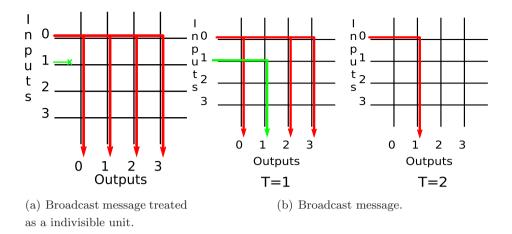

| 1.8            | Broadcast support for a fully connected network                                | 11              |

| 1.9            | Crossbar-based fully connected network floorplan [1]                           | 11              |

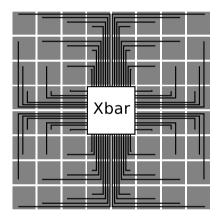

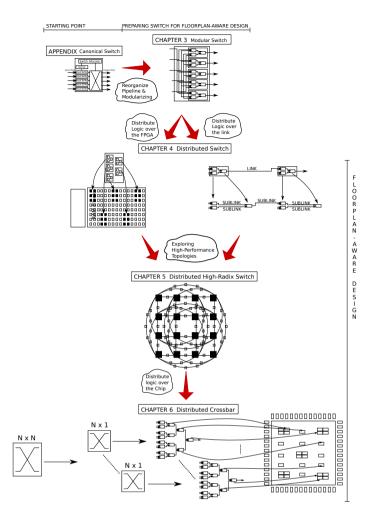

| 1.10           | Thesis flow diagram.                                                           | 13              |

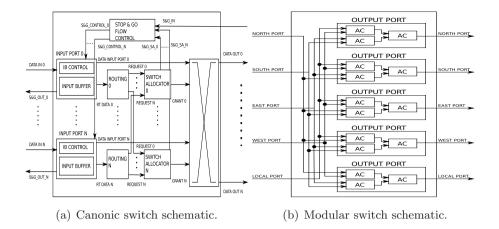

| 1.11           | Canonic and modular switches schematic.                                        | 14              |

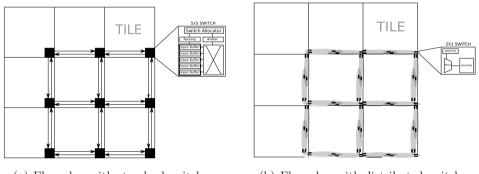

| 1.12           | Floorplan of a 2D mesh with standard and distributed switches.                 | 14              |

| 2.1            | Routing, switching and flow control in a network                               | 20              |

| 2.1            | Network architectures                                                          | 20<br>21        |

| 2.2            | A crossbar network.                                                            | 21              |

| 2.0            | A $4 \times 4$ 2-dimensional mesh and torus.                                   | $\frac{20}{24}$ |

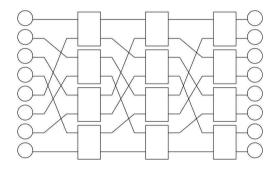

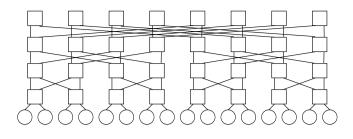

| 2.5            | A multistage network topology. $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ | 24<br>24        |

| 2.6            | The processing element in a tile-based CMP.                                    | 24<br>25        |

| 2.0            | A $8 \times 8$ concentrated Mesh.                                              | 26<br>26        |

| 2.1            | A $8 \times 8$ flattened butterfly and multidrop express channel               | $20 \\ 27$      |

| 2.8            | A O X O HALLEHEU DULLEHIV AUG HUHLIGHOD EXDLESS CHAHLEL                        | 41              |

|                |                                                                                | 20              |

|                | A $4 \times 4$ fat-tree topology.                                              | 28<br>20        |

| 2.10           | A $4 \times 4$ fat-tree topology                                               | 29              |

| $2.10 \\ 2.11$ | A $4 \times 4$ fat-tree topology.                                              |                 |

| 2.13 | Circuit switching                                                                                                               | 32 |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Store and forward switching.                                                                                                    | 33 |

| 2.15 | Virtual cut-through switching.                                                                                                  | 34 |

| 2.16 | Wormhole switching                                                                                                              | 35 |

| 2.17 | Virtual channels                                                                                                                | 35 |

| 2.18 | Ack/nack flow control                                                                                                           | 36 |

| 2.19 | Stop & go flow control                                                                                                          | 37 |

| 2.20 | Credit-based flow control                                                                                                       | 37 |

| 3.1  | Canonical switch schematic and pipeline.                                                                                        | 51 |

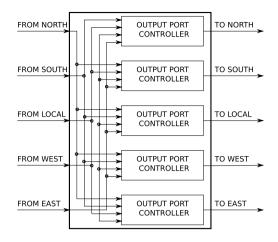

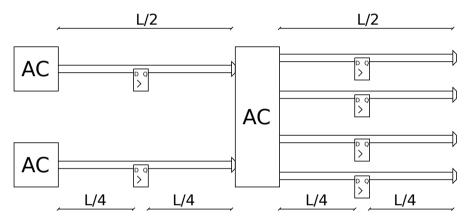

| 3.2  | Modular switch schematic                                                                                                        | 52 |

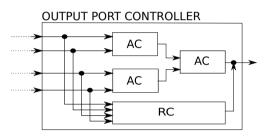

| 3.3  | Output port controller schematic                                                                                                | 52 |

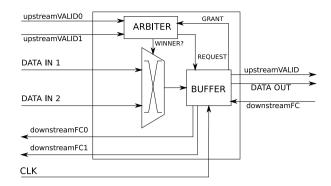

| 3.4  | AC module of degree 2 schematic.                                                                                                | 53 |

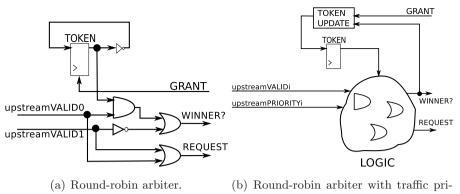

| 3.5  | Round-robin arbiters.                                                                                                           | 54 |

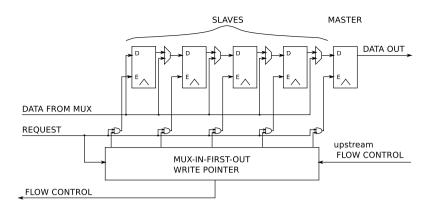

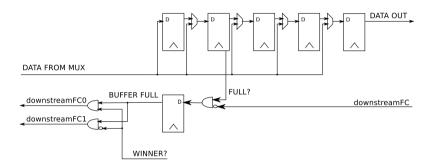

| 3.6  | AC module buffer schematic. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                               | 56 |

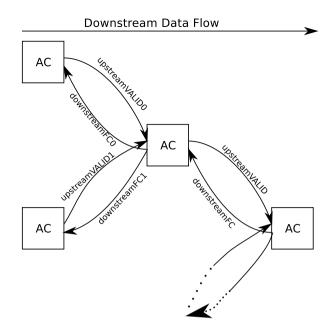

| 3.7  | Flow control signalling                                                                                                         | 58 |

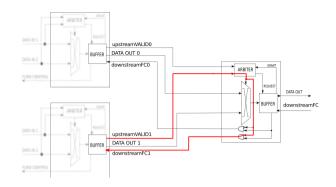

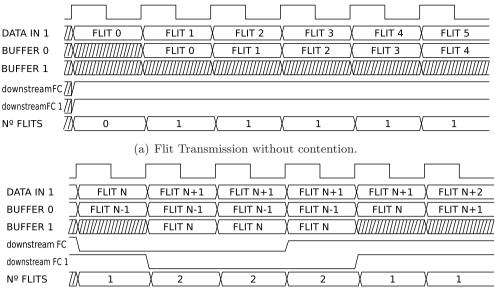

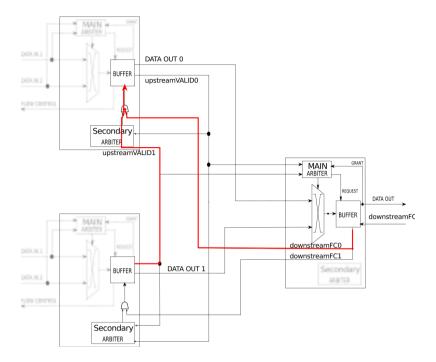

| 3.8  | Flow control signalling generation.                                                                                             | 59 |

| 3.9  | Buffer state signal generation                                                                                                  | 59 |

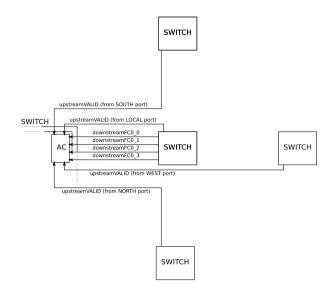

| 3.10 | Example of flow control operation between two AC modules. $\ .$                                                                 | 60 |

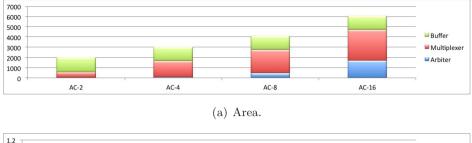

| 3.11 | Area and delay for different AC module radices                                                                                  | 63 |

| 3.12 | Modular switch delay path                                                                                                       | 63 |

| 3.13 | Modular switch delay                                                                                                            | 65 |

| 3.14 | Cycle-level load-latency graph for a 64-node network built with<br>a modular switch with different AC radices. Messages are one |    |

|      | flit long                                                                                                                       | 68 |

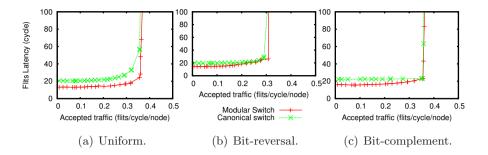

| 3.15 | Load-latency graph for a 16-node network built with the mod-<br>ular and the canonical switch. Messages are one flit long       | 69 |

| 3.16 | Load-latency graph for a 64-node network built with the mod-                                                                    |    |

|      | ular and the canonical switch. Messages are one flit long                                                                       | 69 |

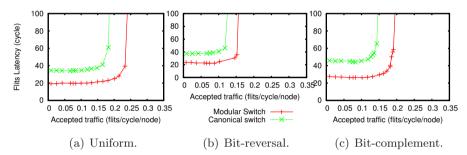

| 3.17 | Cycle-level load-latency graph for a 16-node network built with<br>the modular and the canonical switch. Bimodal traffic: 70%   |    |

|      | 1-flit messages and 30% 9-flit messages                                                                                         | 70 |

| 3.18 | Cycle-level load-latency graph for a 64-node network built with                        |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | the modular and the canonical switch. Bimodal traffic: $70\%$                          |     |

|      | 1-flit messages and $30\%$ 9-flit messages. $\ldots$ $\ldots$ $\ldots$                 | 70  |

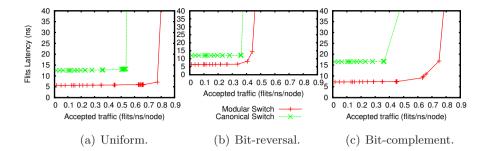

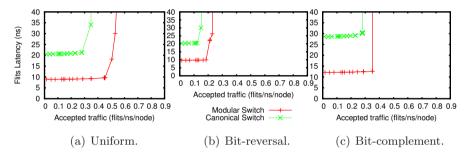

| 3.19 | Time-level load-latency graph for a 16-node network built with                         |     |

|      | the modular and the canonical switch. Messages are one flit long.                      | 71  |

| 3.20 | Time-level load-latency graph for a 64-node network built with                         |     |

|      | the modular and the canonical switch. Messages are one flit long.                      | 71  |

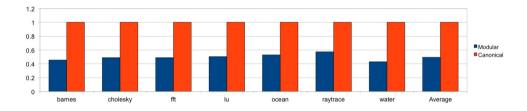

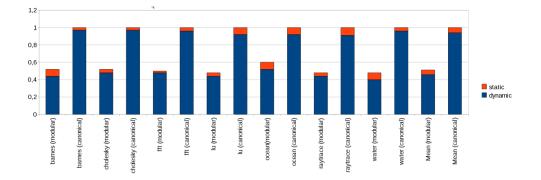

| 3.21 | Execution time when running different SPLASH-2 applications                            |     |

|      | with a modular and canonical switches. $\ldots$ $\ldots$ $\ldots$ $\ldots$             | 72  |

| 3.22 | Energy consumed by network implemented with modular and                                |     |

|      | canonical switches when running different SPLASH-2 applica-                            |     |

|      | tions                                                                                  | 73  |

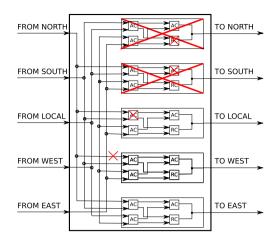

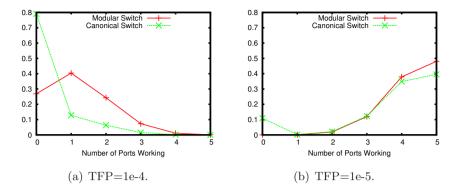

| 3.23 | Fault tolerance of the modular switch                                                  | 74  |

| 3.24 | Probability of having different number of ports working for dif-                       |     |

|      | ferent switch designs                                                                  | 75  |

| 4 1  | Output a set controller for a madeler south band a distributed                         |     |

| 4.1  | Output port controller for a modular switch and a distributed                          | 70  |

| 4.9  | switch.                                                                                | 79  |

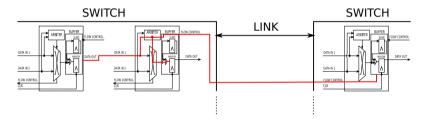

| 4.2  | Link scheme for both scenarios a modular switch and a dis-<br>tributed switch designs. | 80  |

| 19   | -                                                                                      | 81  |

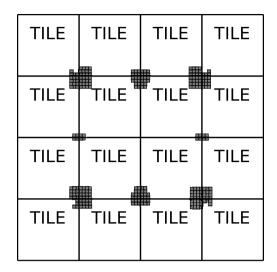

| 4.3  | Floorplan of a 2D mesh with standard and distributed switches.                         | 01  |

| 4.4  | Removing intra switch sublinks when using XY to minimize                               | 82  |

| 4 5  | power consumption.                                                                     | 83  |

| 4.5  | Distributed with spread buffers switch                                                 |     |

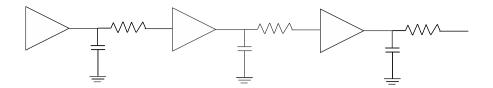

| 4.6  | Diagram of a repeated wire composed of three sections                                  | 84  |

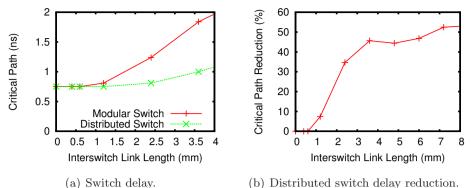

| 4.7  | Modular and distributed switch delay.                                                  | 87  |

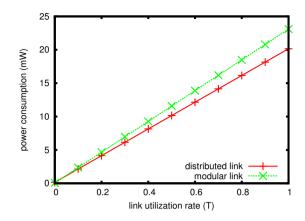

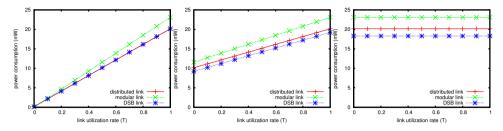

| 4.8  | Power consumption of a modular link and a distributed link.                            | 93  |

| 4.9  | Power consumption of a modular, distributed, and a DSB switch.                         |     |

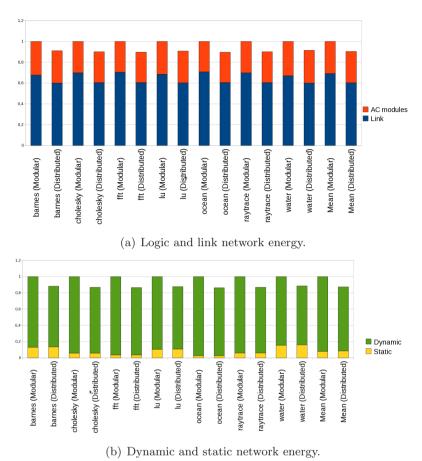

|      | Network Energy for different applications                                              | 96  |

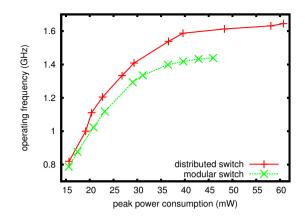

|      | Operating frequency of a modular switch and a distributed switch.                      | 97  |

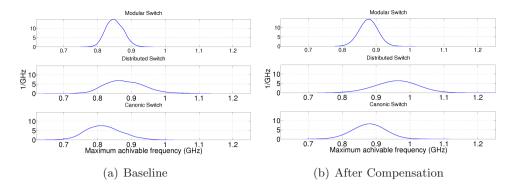

| 4.12 | Probability density function of the maximum achievable fre-                            | 0.0 |

|      | quency of switch architectures.                                                        | 98  |

|      |                                                                                        | 100 |

| 4.14 | Canonical and distributed FPGA switches                                                | 101 |

| 5.1  | Output Port Controller                                              | 109 |

|------|---------------------------------------------------------------------|-----|

| 5.2  | 16-to-1 output port controller to handle 10 input ports             | 110 |

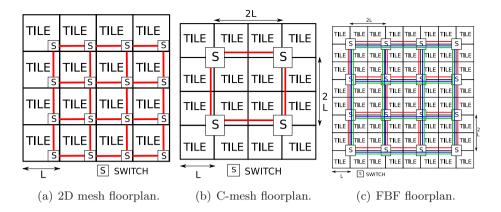

| 5.3  | Different topology floorplans                                       | 112 |

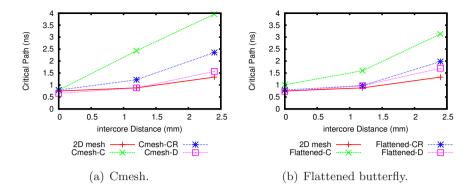

| 5.4  | Critical path for high-radix topologies and the 2D mesh for a       |     |

|      | 64-node network when implemented using different switch ar-         |     |

|      | chitectures                                                         | 114 |

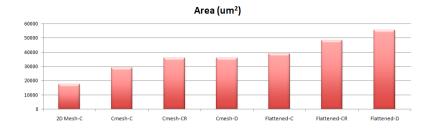

| 5.5  | Canonical and distributed switch area for different architectures.  | 115 |

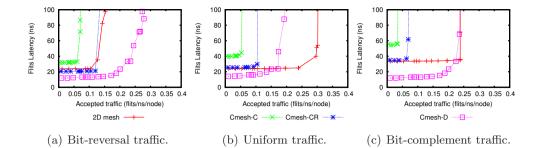

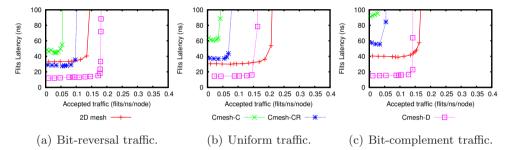

| 5.6  | Load-latency graph for a 64-node 2D mesh-C, Cmesh-C, Cmesh-         |     |

|      | CR and Cmesh-D networks. Messages are one flit long. $\ . \ . \ .$  | 117 |

| 5.7  | Load-latency graph for a 64-node 2D mesh-C, Cmesh-C, Cmesh-         |     |

|      | CR and Cmesh-D networks. Bimodal traffic considered                 | 117 |

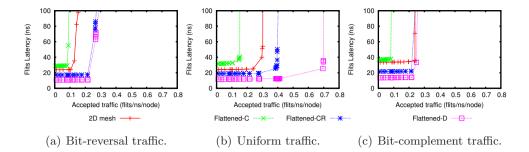

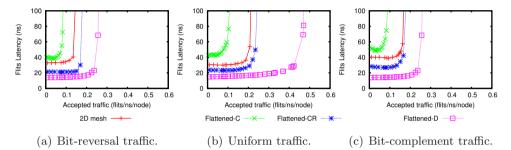

| 5.8  | Load-latency graphs for a 64-node 2D mesh-C, Flattened-C,           |     |

|      | Flattened-CR and Flattened-D networks. Messages are one flit        |     |

|      | long                                                                | 118 |

| 5.9  | Load-latency graphs for a 64-node 2D mesh-C, Flattened-C,           |     |

|      | Flattened-CR and Flattened-D networks. Bimodal traffic con-         |     |

|      | sidered                                                             | 118 |

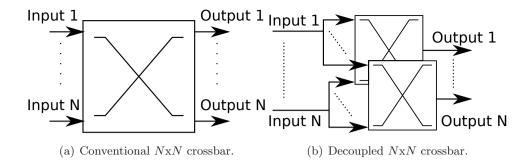

| 6.1  | Conventional and decoupled $N \times N$ crossbars                   | 122 |

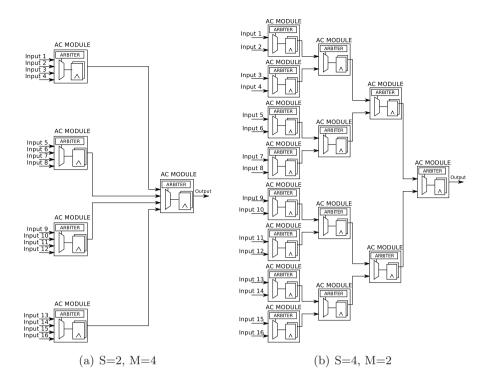

| 6.2  | Pipelined decoupled $16 \times 1$ network (N=16) with different or- |     |

|      | ganizations.                                                        | 123 |

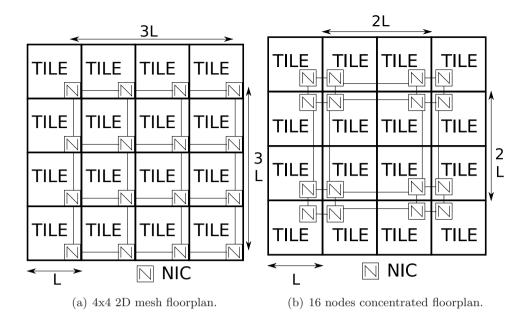

| 6.3  | 2D mesh and a concentrated floorplan                                | 125 |

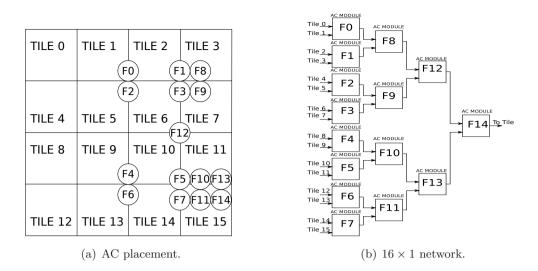

| 6.4  | AC module placement for a $16 \times 1$ subnetwork, corresponding   |     |

|      | to TILE15. $M = 2, S = 4$                                           | 126 |

| 6.5  | 16-node AC module placement                                         | 127 |

| 6.6  | Improved flow control signalling generation.                        | 128 |

| 6.7  | Unfeasible flow control optimization for the modular switch         | 129 |

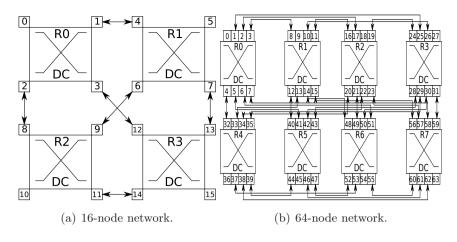

| 6.8  | 16-node and 64-node HDC networks.                                   | 130 |

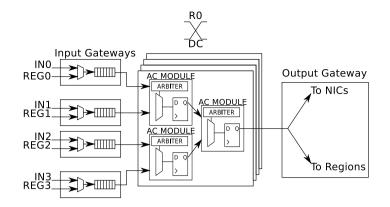

| 6.9  | 16-node HDC region schematic                                        | 131 |

| 6.10 | Critical path measured in nanoseconds for different network ar-     |     |

|      | chitectures                                                         | 135 |

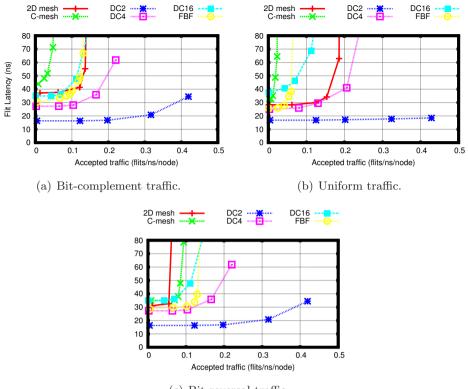

| 6.11 | Accepted traffic and end-to-end flit latency for a 16-node 2D       |     |

|      | mesh, C-mesh, FBF and $DCx$ topologies. Link length equals to       |     |

|      | 1.2mm                                                               | 138 |

| 6.12 | Accepted traffic and end-to-end flit latency for a 64-node 2D   |      |

|------|-----------------------------------------------------------------|------|

|      | mesh, C-mesh, FBF and $DCx$ topologies. Link length equals to   |      |

|      | 1.2mm                                                           | 139  |

| 6.13 | Accepted traffic and end-to-end flit latency for a 16-node 2D   |      |

|      | mesh, C-mesh, FBF and $DCx$ topologies. Link length equals to   |      |

|      | 2.4mm                                                           | 140  |

| 6.14 | Accepted traffic and end-to-end flit latency for a 64-node 2D   |      |

|      | mesh, C-mesh, FBF and $DCx$ topologies. Link length equals to   |      |

|      | 2.4mm                                                           | 141  |

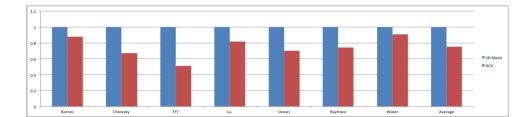

| 6.15 | Normalized execution time and energy for the DC2, and a mesh-   |      |

|      | based network for real applications. Results normalized to the  |      |

|      | 2D-mesh case                                                    | 144  |

| 6.16 | Accepted traffic and end-to-end latency for different network   |      |

|      | architectures with uniform traffic                              | 146  |

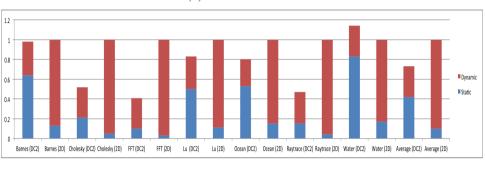

| 6.17 | Normalized execution time and energy for a HDC, DC, and a       |      |

|      | 2D mesh network for real applications                           | 147  |

|      |                                                                 | 1 50 |

| A.1  | Switch schematic.                                               | 158  |

| A.2  | Pipeline stages when forwarding a message through a gNoC        |      |

|      | switch                                                          | 159  |

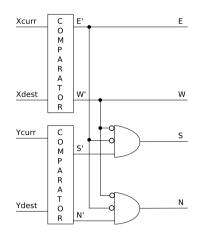

| A.3  | Simple DOR implementation in gNoC switch design                 | 161  |

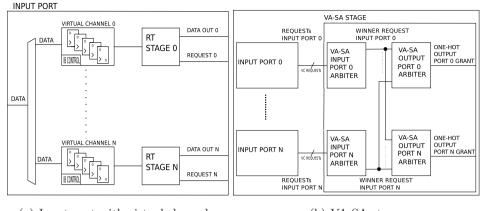

| A.4  | gNoC switch support for virtual channels                        | 164  |

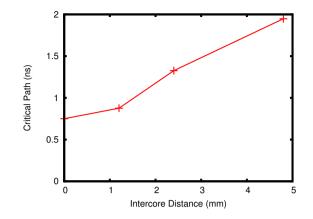

| A.5  | gNoC critical path                                              | 165  |

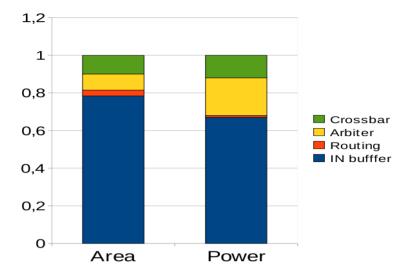

| A.6  | Area and power of the gNoC switch                               | 166  |

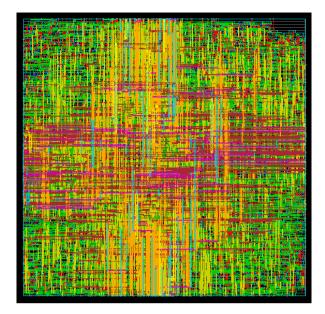

| A.7  | Core floorplan of the canonic switch                            | 167  |

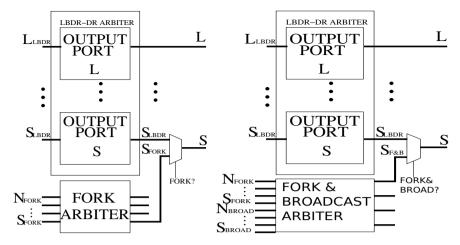

| A.8  | Arbiter for the VCT switch with fork or broadcast requests      | 169  |

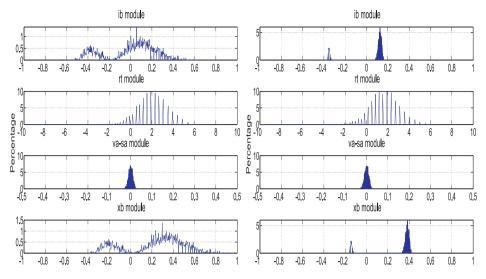

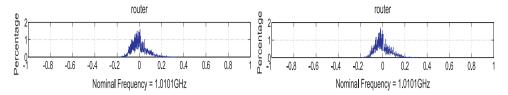

| A.9  | Frequency variation in the stages of a switch pipelined         | 171  |

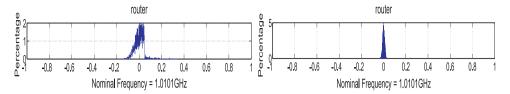

|      | Frequency variation in switch pipeline                          | 173  |

| A.11 | Frequency variation in the stages of a switch pipelined as a    |      |

|      | consequence of both systematic and random variations. $\ldots$  | 173  |

| A.12 | Prequency variation in switch pipeline as a consequence of both |      |

|      | systematic and random variations.                               | 174  |

# List of Tables

| 1.1 | Analytical properties for different 64-node topologies                                                                       | 7   |

|-----|------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Area requirements and delay for different AC-radix modules.<br>Increment with respect to AC-2 included.                      | 62  |

| 3.2 | Area requirements and latency by the modular and canonical<br>switch when link length is zero. Increment values with respect |     |

|     | to the canonical switch shown. $\ldots$ . $\ldots$ . $\ldots$ . $\ldots$ .                                                   | 65  |

| 3.3 | CMP configuration.                                                                                                           | 72  |

| 4.1 | Physical and electrical data for 45nm NoC wires                                                                              | 85  |

| 4.2 | Number and size of the repeaters of a wire. $\ldots$                                                                         | 85  |

| 4.3 | Area occupied by a modular switch and a distributed switch                                                                   | 87  |

| 4.4 | Area occupied by the repeaters of a link $\ldots \ldots \ldots \ldots$                                                       | 89  |

| 4.5 | Area occupied by the whole switch                                                                                            | 89  |

| 4.6 | Power consumption of a modular and a distributed switch                                                                      | 90  |

| 4.7 | Power consumption in a clock cycle for different link lengths                                                                | 91  |

| 4.8 | CMP configuration.                                                                                                           | 95  |

| 4.9 | The area in slices and the delay in nanoseconds of the canonical                                                             |     |

|     | and distributed switch                                                                                                       | 102 |

| 5.1 | Area referred parameters for 64-end nodes for different topolo-                                                              |     |

|     | gies implemented using the modular switch design                                                                             | 107 |

| 5.2 | High-level parameters for 64-end nodes for different topologies                                                              |     |

|     | implemented using the modular switch design. $\ldots$                                                                        | 107 |

| 5.3 | Different topology parameters when implementing using a dis-                                                                 |     |

|     | tributed switch                                                                                                              | 111 |

|     |                                                                                                                              |     |

| 5.4 | Link length configuration for a 2D mesh, C-mesh, and FBF                                             |     |

|-----|------------------------------------------------------------------------------------------------------|-----|

|     | architectures                                                                                        | 112 |

| 6.1 | Maximum link length between adjacent AC modules. In the                                              |     |

|     | DCx designs, the concentrated floorplan is used. $\ldots$ .                                          | 125 |

| 6.2 | High-level parameters for 64-end nodes for different HDC con-                                        |     |

|     | figurations and a 2D-mesh.                                                                           | 132 |

| 6.3 | Network area for different architectures and system sizes                                            | 136 |

| 6.4 | Improvements in performance of DC2 and DC4 over the FBF                                              | 142 |

| 6.5 | CMP configuration.                                                                                   | 143 |

| 6.6 | Area and critical path of the 2D mesh, DC and HDC. $\ldots$ .                                        | 145 |

| 6.7 | Accepted traffic and end-to-end latency for a HDC, DC, and a                                         |     |

|     | mesh-based network implementations                                                                   | 147 |

| A.1 | Area and delay the router modules and gNoC                                                           | 164 |

| A.2 | Area and delay of the gNoC with no VC and five VC                                                    | 166 |

| A.3 | Area and frequency for the wormhole and VCT switches                                                 | 169 |

| A.4 | Area and frequency for the wormhole and VCT switches                                                 | 170 |

| A.5 | Correlation between stage delay and switch delay                                                     | 173 |

| A.6 | Nominal, maximum, mean and minimum frequencies and fre-                                              |     |

|     | quency variation of a switch $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 174 |

## Resum

Arquitectures de múltiples nuclis com a multiprocessadors (CMP) i solucions multiprocessador per a sistemes dins del xip (MPSoCs) actuals es basen en l'eficàcia de les xarxes dins del xip (NoC) per a la comunicació entre els diversos nuclis. En aquest sentit, els CMPs i MPSoCs que s'han fabricat en els darrers anys s'han implementat basant-se en NoC amb una topologia simple, normalment malles o anells. No obstant, a mesura que els nombre de elements a connectar creixia, xarxes simples no eren capaç de satisfer els requeriments del sistema, que són principalment, una baixa latència i alt rendiment. Així, la comunitat investigadora ha proposat i analitzat NoCs ms complexes. No obstant, aquestes solucions són més difícils de implementar – especialment els enllaços llargs – fent que aquest tipus de topologies complexes siguen massa costoses o inclòs inviables.

En aquesta tesi, presentem un metodologia de disseny que minimitza la pèrdua de prestacions de la xarxa degut a la seua implementació real, principalment per la complexitat dels commutadors i dels enllaços llargs. Com a primer pas, re-dissenyem el commutador fent-lo modular. Cada mòdul del commutador és capaç de arbitrar, commutar, i emmagatzemar els missatges que li arriben. Com a segon pas, flexibilitzem la col.locació d'aquestos mòduls arran del xip, permetent que mòduls d'un mateix commutador estiguen distributs per el xip.

Aquesta metodologia de disseny l'hem aplicat en diferents escenaris. Primerament, hem transformat NoC ja conegudes com la malla 2D introduint el nostre commutador modular. Els resultats mostren com la modularitat i la distribució del commutador redueixen la latència i el consum de potència de la xarxa. A més a més, aquests beneficis són majors en aquelles topologies on la complexitat del commutador és major, com per exemple, la *flattened butterfly* o la *concentrated mesh*.

En segon lloc, hem utilitzat la nostra metodologia de disseny per a implementar un *crossbar* distribuït. El nostre *crossbar* distribuït té unes prestacions clarament millors que la resta de configuracions, tant en latència com en rendiment. No obstant, per a xarxes amb un gran nombre de nodes, el nostre *crossbar* distribuït requereix massa recursos. En aquest cas, hem analitzat un *crossbar* distribuït jeràrquic viable que, a més a més manté pràcticament les prestacions del *crossbar* distribuït.

### Abstract

Network-on-Chip (NoCs) have been widely accepted as the interconnection choice for Chip MultiProcessor (CMP) and MultiProcessor System-on-Chip (MPSoCs). In this sense, current CMPs or MPSoCs rely on simple NoC designs based on rings or meshes. As the number of cores to interconnect grows, simple NoCs are not able to fulfil system requirements, that is, low latency and high throughput. In this sense, more complex NoC solutions have been proposed and analyzed. However, complex designs means complex implementations – specially critical is link length – which makes these solutions costly or even unaffordable.

In this dissertation, we present a floorplan-aware NoC design methodology that minimizes the implementation drawbacks of complex NoC designs, that is, high-radix switches and long links. As a first step, we redesign the switch by making it modular and locally self contained. That is, each small block has its own buffering, arbitration, and crossing capabilities. As a second step, we flexibilize the placement of the basic modules, allowing a distribution of the switch basic blocs all over the chip.

We have applied our floorplan-aware NoC design into different scenarios. First, we show that it is possible to build a conventional NoC as a 2D mesh by using a floorplan-aware switch. Results show that modularizing and distributing the switch along the link reduces the network critical path and power consumption over conventional implementations. Additionally, these benefits increase as the switch radix increases, and hence, our floorplan-aware switch fits perfectly in complex NoC implementations, as the flattened butterfly or concentrated meshes.

Second, we have leveraged our floorplan-aware NoC design methodology

to implement a distributed crossbar. Our distributed crossbar clearly outperforms in terms of latency and throughput the rest of configurations. For very large networks, our crossbar resources requirements could be unaffordable. In this case, a hierarchical approach has been implemented which almost keeps all the crossbar benefits but reducing resources used.

## Resumen

Las actuales arquitecturas de múltiples núcleos como los chip multiprocesadores (CMP) y soluciones multiprocesador para sistemas dentro del chip (MPSoCs) han adoptado a las redes dentro del chip (NoC) como elemento óptimo para la inter-conexión de los diversos elementos de dichos sistemas. En este sentido, fabricantes de CMPs y MPSoCs han adoptado NoCs sencillas, generalmente con una topología en malla o anillo, ya que son suficientes para satisfacer las necesidades de los sistemas actuales. Sin embargo a medida que los requerimientos del sistema – baja latencia y alto rendimiento – se hacen más exigentes, estas redes tan simples dejan de ser una solución real. Así, la comunidad investigadora ha propuesto y analizado NoCs más complejas. No obstante, estas soluciones son más difíciles de implementar – especialmente los enlaces largos – haciendo que este tipo de topologías complejas sean demasiado costosas o incluso inviables.

En esta tesis, presentamos una metodología de diseño que minimiza la pérdida de prestaciones de la red debido a su implementación real. Los principales problemas que se encuentran al implementar una NoC son los conmutadores y los enlaces largos. En esta tesis, el conmutador se ha hecho modular, es decir, formado como unión de módulos más pequeños. En nuestro caso, los módulos son idénticos, donde cada módulo es capaz de arbitrar, conmutar, y almacenar los mensajes que le llegan. Posteriormente, flexibilizamos la colocación de estos módulos en el chip, permitiendo que módulos de un mismo conmutador estén distribuidos por el chip.

Esta metodología de diseño la hemos aplicado a diferentes escenarios. Primeramente, hemos introducido nuestro conmutador modular en NoCs con topologias conocidas como la malla 2D. Los resultados muestran como la modularidad y la distribución del conmutador reducen la latencia y el consumo de potencia de la red.

En segundo lugar, hemos utilizado nuestra metodología de diseño para implementar un *crossbar* distribuido. Nuestro *crossbar* distribuido tiene unas prestaciones claramente mejores que el resto de configuraciones, tanto en latencia como en rendimiento. No obstante, para redes con un gran número de nodos, nuestro *crossbar* distribuido necesita demasiados recursos. Para solucionar este problema de escalabilidad, se ha estudiado un *crossbar* distribuido jerárquico viable que, además mantiene prácticamente las prestaciones del *crossbar* distribuido.

### Chapter 1

### Introduction

In this chapter, we first introduce the reasons that have motivated this dissertation (Section 1.1). Then, we briefly define the specific objectives aimed by the dissertation (Section 1.2). Finally, we outline the structure of the remaining chapters in this document (Section 1.3).

#### 1.1 Motivation

As technology advances, more and more transistors can be included in the same die. In this scenario, conventional out-of-order superscalar uniprocessors present an excessive design complexity that do not exploit all the technology opportunities at reasonable power budgets. In contrast, Chip Multiprocessor (CMP) and Multiprocessor System-on-Chip (MPSoC) systems have been chosen as the power efficient solution for current necessities and challenges. Rather than a complex monolithic uniprocessor, a CMP system is compounded of multiple replicated simple tiles on a single die where each tile includes a processor, some cache structure, and a switch.

The complexity of conventional uniprocessor solutions is managed via replication and design reuse. Nowadays, commercial solutions are able to reach several tens of cores (see Figure 1.1). Examples of such solutions are the Polaris prototype chip [2] by Intel with 80 simple cores, the Single-chip Cloud Computing prototype [3] by Intel with 24 x86 dual-core tiles, and the Tilera 100-core chip [4]. On the other hand, an MPSoC system is built by multiple

Figure 1.1: Tiled CMP.

heterogeneous processing elements with different sizes and functionalities, such as processors, memories and I/O components. MPSoCs are typically used in the embedded system market domain. In both cases, the trend is that the number of replicated cores will be increased up to thousands of cores.

#### 1.1.1 Network-On-Chip

Aggregating several cores in a single die leads to the necessity of interconnecting them. Initially, when the number of cores to interconnect was low, ad-hoc wiring solutions or a shared bus [5, 6] were sufficient solutions to fulfil performance requirements. However, as the number of cores to interconnect increases, those initial solutions became inefficient. As an alternative, Network-on-Chip (NoC) have been widely accepted as the proper interconnection choice for CMPs and MPSoCs. NoCs are able to meet the severe constraints imposed by the new on-chip environment [7, 8]. The idea is quite simple: a point-to-point network inside the chip connects all the devices by means of switches and links. The popularity of NoCs grew also due to its physical scalability, specially when a simple 2D topology with a low-radix switch is implemented. That is, the planar structure of a 2D NoC makes them suitable for the planar silicon technology, as for example the simple 2D mesh as can be seen in Figure 1.2. For that reason, most existing NoC designs are based on simple topologies as rings [9] or the most popular 2D mesh [10, 11]. In fact, current commercial solutions rely on a 2D mesh such as the Polaris pro-

Figure 1.2: 2D mesh planar scalability schematic.

totype chip [2] and the Single-chip Cloud Computing prototype [3] by Intel. The Tilera 100-core chip [4] includes several 2D meshes. Simpler commercial solutions can be found, as for example the Intel Nehalem [12], which relies on a bidirectional ring.

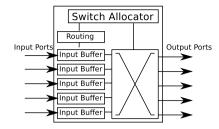

A NoC is built from basic components as switches, links, and network interfaces. Switches and end nodes are connected by links, thus forming the topology and final network structure. Although the network interface must be carefully designed in order not to introduce bottlenecks, the complexity is usually shifted to the switch design. A basic switch should store its incoming flits, route them, and deliver them onto the proper output port. Despite that a switch can be designed in different manners, a crossbar-based switch design has been widely accepted [13,14,14], that is, a switch in which inputs and outputs are interconnected by a matrix of connections. Figure 1.3 shows a basic  $5 \times 5$ crossbar-based canonical switch. This switch is made of input buffers, which store the incoming flits. Then, a routing module, usually replicated at each input port, is used to compute the proper output port for the stored incoming flits. Next, the switch allocator arbitrates which input port is connected to an output port. Finally, the crossbar is the interconnection structure that physically connects – based on the switch allocator decision – the input ports with the output ports. Typically, the most critical components in a switch are the crossbar and the switch allocator. That is, these elements fix the switch throughput and switch operating frequency. In contrast, the input buffering is the main responsible for the area and power consumption of the switch. Notice that, as the switch radix increases more input/output ports must be handled by the switch components, and hence, the switch complexity increases,

Figure 1.3:  $5 \times 5$  crossbar-based canonical switch schematic.

leading to an unavoidable increment in area, and most probably a decrease in its operating frequency.

On the other hand, in the NoC scenario, link design becomes more critical than switch design. NoC severe timing and power consumption constraints have made link design a priority. Contrary to the off-chip domain, wiring delay becomes not only appreciable but significant in the message's critical path. Wire delay can be reduced by inserting repeaters along the link at the expense of increasing its area and power consumption. This fact gets worse as the wire length increases to connect more distant components (nodes or switches). Long interconnects are costly or even unfeasible [15] in terms of power consumption. In fact, the popularity of modular and scalable NoC topologies as the 2D mesh is in part due to these wiring concerns. However, despite that the 2D mesh minimizes wire length with respect to more complex architectures and topologies, link power consumption can still be more than 70% of the total network energy consumption [16].

#### 1.1.2 NoC Topologies

Simple 2D network topologies as rings or meshes rely on low-radix switches which leads to a fast network with good performance when the number of elements to interconnect remains low. However, meanwhile a simple 2D topology offers a proper connectivity for systems with dozens of tiles (processors), those network implementations are unable to fulfil larger system requirements. As the amount of devices to interconnect increases, the performance – measured as latency and throughput [17] – of these simple topologies is highly impacted due to its lack of scalability. First, message latency increases due to the larger network diameter, increasing also the energy to transmit messages even with a very low traffic injection rate when no contention exists. But, the main limitation is the network throughput these topologies may achieve. Indeed, the throughput of these topologies is highly impacted as the bisection bandwidth<sup>1</sup> increases linearly with the square of the number of nodes to interconnect. As the network traffic increases, it becomes congested, and hence, message latency exponentially increases due to the queueing latency. Furthermore, the 2D mesh structure may bring an unbalanced network utilization. Switches placed at the borders are underused with respect to switches placed at the center of the network. Unbalanced network utilization reinforces the congestion problem by increasing queueing message latency and making message latency unpredictable.

The performance degradation and energy increment that those topologies suffer when the number of cores to interconnect increases, force the designers to explore new solutions based on planar processes. However, the current planar silicon substrate technology restricts the space of implementable networks  $[18]^2$ . In this sense, researchers have developed more complex topologies that overcome the inefficiencies of basic ones but still being implemented as a planar structure. A flattened butterfly topology [21,22] (see Figure 1.4(b)), multi-stage networks such as the Clos network [23] (see Figure 1.4(d)), topologies based on fat-tree networks [24,25] (see Figure 1.4(e)), concentrated meshes (C-meshes) [26] (see Figure 1.4(a)), hierarchical topologies [27], or multidrop express channels (MEC) [28] (see Figure 1.4(c)) are some remarkable solutions recently suggested by researchers.

In general, these complex topologies reduce network latency by reducing the hop count of messages. Reducing hop count is achieved by *concentrating* nodes to a switch (C-mesh), by increasing the connectivity between switches (flattened butterfly or MEC), or by completely modifying the network con-

<sup>&</sup>lt;sup>1</sup>Bisection is the minimum set of network components that split the network in two equal halves. Bisection bandwidth is the bandwidth at the bisection.

<sup>&</sup>lt;sup>2</sup>Recently, a 3D silicon technology has appeared. However, this technology is currently in experimentation phase [19, 20] so will not be considered in this thesis.

Figure 1.4: Complex network topologies.

cept (Clos or tree-based networks). From the theoretical point of view, there is no wining topology that clearly overcomes the rest in all the critical aspects of the NoC environment, mainly performance (throughput and latency), power consumption, and implementation costs (area). In Table 1.1 we can see different metrics for different 64-node topologies. As it can be seen, a 4-ary 3-tree topology (similar construction as Figure 1.4(e)) presents the maximum bisection bandwidth but the number of switches and the network diameter is higher than the C-mesh topology (see Figure 1.4(a)) and the 4-ary 3-flat topology (see Figure 1.4(b)). The 4-ary 3-flat topology has the lowest network diameter, but the switch radix (number of ports) – and hence its complexity – is the highest too. Moreover, final applications to run on top of these systems influence the topology selection process [7]. Thus, low latency, resources available, or throughput requirements fixed by applications can determine the topology pick for the network design.

In NoCs, contrary to the off-chip domain, complex topologies exacerbate two important drawbacks. First, those topologies rely on high-radix switches.

|              | Switches | Bisection BW | Diameter | Switch radix |

|--------------|----------|--------------|----------|--------------|

| 2D mesh      | 64       | 16           | 15       | 5            |

| 4-ary 3-tree | 48       | 64           | 5        | 8            |

| C-mesh       | 16       | 16           | 5        | 8            |

| 4-ary 3-flat | 16       | 32           | 3        | 10           |

Table 1.1: Analytical properties for different 64-node topologies.

Second, more resources are needed when designing such switches which leads to an increment in power consumption. This increment in resources gets even worse since the number and length of links increases. As the switch radix increases, switch complexity – and hence switch latency – increases too, as can be seen in Figure 1.5(a). This figure shows the normalized critical path and area<sup>3</sup>. As the radix increases, both the switch delay and area increase – the increment in area is specially critical. Beyond 10 ports, the increment curve is even higher. Thus, topologies made by high-radix switches, although reduce hop count, they suffer from increased switch latency. Furthermore, high-radix switches suffer from traffic concentration, that is, they receive traffic from a higher number of input ports which can lead to a switch congestion, and hence, reducing overall network throughput. Figure 1.5(b) shows the throughput per output port of a switch when each input port has an injection traffic rate of one flit/cycle<sup>4</sup>. As it can be seen, the throughput of a switch gets worse as the number of input/output ports increases. This traffic concentration is noticeable in high-radix topologies<sup>5</sup>. For example, the concentrated mesh topology, the flattened topology or the hierarchical proposals presented in [27] achieve a network throughput that is even lower than the one achieved by the simple 2D mesh topology.

If we add the fact that long links (found in high-radix networks) also lead to possibly prohibitive increases in power dissipation, all the previous comments lead to questioning whether high-radix networks are feasible and preferable.

<sup>&</sup>lt;sup>3</sup>Results obtained after synthesising the canonical switch presented in Appendix A with the 45nm Opensource Nangate Library.

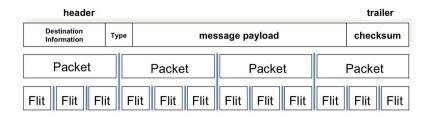

<sup>&</sup>lt;sup>4</sup>Flit (flow control bit) is the minimum amount of information that is flow controlled in the network.

<sup>&</sup>lt;sup>5</sup>We refer to high-radix topologies those implemented by using high-radix switches.

(a) Normalized critical path and area. (b) Switch throughput per output port.

Figure 1.5: Switch properties as a function of switch radix.

#### 1.1.3 Crossbars

When derived to the ideal case, a fully connected network where each node is directly connected to any node with a bidirectional link is the most aggressive high-radix network. Alternatively, a less aggressive solution is a single crossbar which can also be used to interconnect all the nodes. Figure 1.6 shows a  $N \times N$  crossbar where a simple matrix connects N inputs with N outputs. The crossbar has been traditionally discarded by the common belief of its infeasibility due to its high wiring complexity, and its arbiter complexity (Ninputs to N outputs). Notice that replacing an entire conventional NoC, like a 2D mesh, by a crossbar provides many advantages from a conceptual point of view. First, the bisection bandwidth of a crossbar is higher than that of the 2D-mesh network. While the bisection bandwidth of the 2D mesh is  $\sqrt{N}$ , the bisection bandwidth of the crossbar can be computed as  $N^2/4$ , where N is the number of nodes in the network. Moreover, the average latency in a crossbar is noticeably reduced (theoretically in terms of cycles) as only one hop (one cycle) is required by a node to reach any other node in the die.

In addition to the huge performance improvement, crossbars present several interesting features. As each node is directly connected to the rest of nodes a crossbar does not depends on the traffic pattern, that is, traffic to a node does not affect traffic to the rest of nodes avoiding collisions between packets addressed to different destinations (see Figure 1.7(a)). In this sense, a crossbar is insensitive to bursty traffic and network contention. A burst of

#### 1.1. Motivation

Figure 1.6: Crosspoint-based crossbar.

messages from a given input to a given output will not interfere with other communicating flows. On the contrary, in a 2D mesh (Figure 1.7(b)), the red flow is temporarily blocked by the green flow of messages, even in the case both flows are for different destinations. The absence of network conflicts reduces traditional problems as deadlock or head-of-line blocking. A crossbar ensures deadlock-freedom. Whereas Head-of-line blocking (where packets requesting free resources are blocked by packets requesting to other outputs) is removed inside the crossbar, it may occur on the NIC limiting the throughput to a 58.6% when uniform traffic and a single FIFO per input is used [29]<sup>6</sup>. More complex NIC implementation or buffered crossbars can increase this limit up to 100% [30].

In addition, direct connection between nodes simplifies implementation. First, there is no need for routing packets that traverse the network and, hence, no routing bits must be prepended to packet headers, thus increasing the effective network throughput. Most important is that support for multicast and broadcast in crossbars is straight-forward, as only the crossbar has to be configured to multiple outputs. Figure 1.8 shows two forms to manage a broadcast message. In Figure 1.8(a) any broadcast message compete for all the outputs at a time. When a broadcast message wins it uses all the outputs.

<sup>&</sup>lt;sup>6</sup>Despite that this limit is far away than the maximum -100 % – is still higher than in other architectures, specially as the network size increases.

Figure 1.7: Collision avoidance in a crossbar network.

On the other hand, in Figure 1.8(b) a broadcast message is sent at the same time a unicast message progresses. As it can be seen, at cycle one, input two requires the use of output two, and hence, the broadcast message is able to arrive to any destination but to output two. During the next cycle, the broadcast message is sent to output two. Broadcast transmission ends when the broadcast message is transmitted to all the requested outputs. Notice that to support multicast messaging, the network interface will need minor changes. The properties mentioned above – high throughput, absence of collisions – joined to the constant latency obtained from any source node to any destination node promote the crossbar as highly predictable, which allows for simpler QoS solutions being implemented in crossbars.

Although theoretically crossbar are not scalable, in [1, 31] a  $128 \times 128$  centralized crossbar has been designed and synthesized. In [32] buffers are introduced inside the crossbar design to solve scalability and implementation cost issues. In these works, it is shown that a proper and meticulous design process can lead to a feasible large centralized crossbar as in Figure 1.9. Similarly, in [21, 24, 28], it is shown that high-radix topologies are feasible without an excessive cost in terms of resources.

In addition to the resources needed for these high-radix solutions, the de-

Figure 1.8: Broadcast support for a fully connected network.

Figure 1.9: Crossbar-based fully connected network floorplan [1].

sign of each component is also critical. Indeed, a naive implementation of the switch will minimize or even cancel the theoretical benefits of these topologies. Indeed, the real problem is that those designs are not floorplan-aware, in the sense that the design tools can not take profit from the design and perform an optimal floorplan.

#### 1.1.4 Contribution

In this dissertation, we aim to minimize the negative impact of a real implementation of a NoC by presenting a novel floorplan-aware design methodology. We consider a complex NoC design as a concatenation of small and simple modules. The simplicity of those modules makes them easily optimized at design time or by the synthesis tools. In addition, the modularity of a large and complex design allows the designer to properly place each module along the chip. By simplifying, modularizing, and spreading along the chip a complex NoC design, higher operating frequencies can be achieved because problems related with long links are minimized and switch design is optimized. With this approach, the large gap between the theoretical performance of high-radix networks and their real performance when implemented is closed with respect to other methodologies.

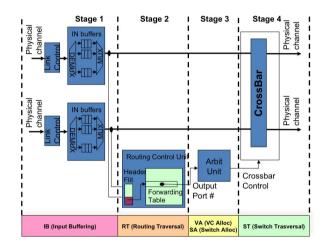

Figure 1.10 shows the flow diagram of this dissertation. The starting point is a canonical switch in which its major components are buffering, routing, arbitration, and forwarding incoming flits. The first step in this thesis is to convert the canonical switch into a modular switch design made of simple and identical modules. To perform this first step, it is necessary to reorganize the canonical switch pipeline. With this approach, we mimic the canonical switch behaviour. We call this novel switch the *modular switch* (see Figure 1.11(b)). In the modular switch, each output port is independent of the rest of ports. That is, each output port is able to store, arbitrate, and forward a flit. In addition to the independence of the output ports, the *modular switch* has another interesting property. Output port tasks – arbitration, buffering, and forwarding – are splitted in smaller units thus leading to simpler and faster decisions.

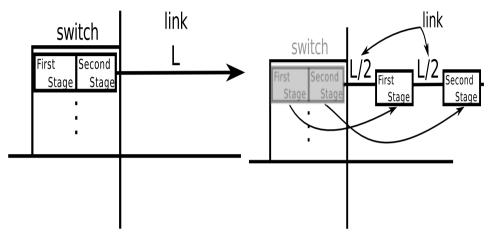

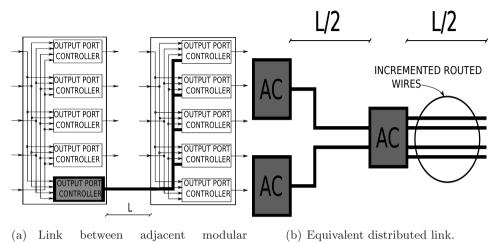

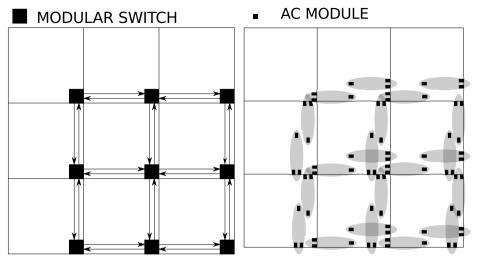

Modularizing the switch allows the designer to properly place and route the switch along the chip, because each module can be handled independently. The NoC design methodology presented in this dissertation fixes the basic module (termed AC) as the basic design unit. In this sense, as it can be seen in Figure 1.12, it is possible to spread a single switch along the chip by spreading the AC modules that compound that switch. Thus, as a second contribution in this thesis, we provide a distributed switch approach where the switch components are spread over the chip. At the physical level, the network becomes a chain of AC modules uniformly distributed over the chip surface (see Figure 1.12(b)). By spreading basic modules link length is reduced by half, and hence, the link power consumption is reduced and overall network

Figure 1.10: Thesis flow diagram.

frequency is increased.

By reducing link length, and modularizing the switch, high-radix topologies can be reconsidered with this approach. Indeed, in a third contribution in this thesis, we promote the use of high-radix networks by using the distributed modular switch approach. By doing this, the gap between theoretical network performance and real network performance (when placed and routed) gets reduced.

Indeed, it is possible to reuse the *modular switch* design philosophy to implement a large crossbar in an efficient, modularized, and distributed manner

Figure 1.11: Canonic and modular switches schematic.

for small and even medium – up to 64 node – size networks. Basically, a large crossbar is decomposed in a cascade of AC modules. In fact, our floorplanaware design we propose in this thesis for a distributed crossbar is able to use less resources than a conventional 2D mesh for small networks. In order to cover ultra-large many-core systems, a hierarchical design is proposed to overcome the scalable problems of very large crossbars. A hierarchical distributed crossbar allows a crossbar-based design for systems larger than 64 nodes.

### 1.2 Objectives

This section presents the objectives of this dissertation. The key objective we seek is to describe a simple and novel philosophy to design a NoC that reduces the negative impact of long links and improve overall network performance. Basically, NoC overall functionality – buffering, arbitration and forwarding– is mixed and splitted into simpler and spread –distributed – decisions. In order to achieve this overall goal, we pursue the following specific goals:

- Provide an insight of the most recent related work in switch and highperformance on-chip network design.

- Describe a new switch architecture (*modular switch*) where arbitration, buffering, and forwarding capabilities are pipelined into a cascade of small and simple modules.

- Propose a new floorplan-aware 2D mesh NoC architecture which reduces link interconnect negative impact. For that purpose we design a proper place-and-route of our *modular switch*, called the *distributed switch*. The *distributed switch* is the foundation of our high-performance NoC solutions.

- Leverage our *distributed switch* to implement and improve current high-radix 2D topologies.

- Demonstrate the feasibility of fully connected networks implemented as large crossbars for small and medium networks, when the *distributed switch* philosophy design is reused. We refer to our crossbar as the *distributed crossbar*. We show the inefficiencies of current 2D high-radix topologies with respect to crossbars for small and medium networks.

- Propose a feasible and efficient high-performance floorplan-aware hierarchical distributed crossbar design – *hierarchical distributed crossbar* – for many-core systems.

In conclusion, we propose a new floorplan-aware NoC design philosophy, that is able to improve current designs. Our philosophy can be used to implement a simple 2D mesh –  $distributed \ switch$  – or leverage this solution to

implement a feasible high-radix topology. Finally, our *distributed switch* can be leveraged to recover traditionally discarded solutions as large crossbars. Our *distributed crossbar* is suitable for small and medium networks, meanwhile our *hierarchical distributed crossbar* is suitable for high-performance large networks.

#### 1.3 Dissertation Outline

This dissertation begins with this introductory chapter (Chapter 1). Then, we continue with Chapter 2 describing the basics of on-chip interconnection networks and an analysis of the current state of art that contributes to the matter of this dissertation. Chapter 3 presents the *modular switch* which is the baseline switch that will be used in later Chapters. Chapter 4 presents the *distributed switch* which is the solution to minimize the impact of long links. Chapter 3 and Chapter 4 focus on a simple topology as the 2D mesh, however, these chapters present the basic concepts and design methodology that will be used in Chapter 5. Indeed, in Chapter 5 we present the application of the distributed switch design to high-radix topologies. Then, Chapter 6 shows that a fully connected network designed as a distributed crossbar is feasible for medium networks. To overcome scalability concerns, a hierarchical distributed crossbar is presented in the same chapter. Finally, the dissertation ends with Chapter 7, which summarizes the conclusions and summarizes the contributions related to the research field.

# Chapter 2

# Technical Background and Related Work

In this chapter, the goal is to describe the basics and terminology of onchip interconnection networks. For the sake of understanding we will cover the main aspects, but it is not the intention of this chapter to provide an in-depth view on the subject, since the on-chip network field is as complex as the general interconnection network field, and there exist several aspects that are beyond the scope of this dissertation. We refer the reader to the established textbooks on this topic and related ones for further background and introductory material [7,8,17,33].

First, in Section 2.1 a brief description of the design parameters that involve networks-on-chip are presented. Then, in Section 2.2, we dive into a more extensive description of the aspects that surround this kind of networks. Finally, this chapter, in Section 2.3, shows the related work and existent contributions that serve as a reference for this dissertation.

### 2.1 On-chip Interconnection Networks

In the field of interconnection networks, there is a growing interest and amount of research in the on-chip domain. Since the appearance of the NoC concept, many research groups and institutions have turned their attention into it and they have contributed to a plethora of proposals in related conferences and journals. The integrated circuit technology has evolved to accommodate a multiprocessing device capable of high-performance computation. As a result of the high integration scale in the deep sub-micron domain and the increasing number of connecting elements, on-chip interconnection has become a need and influences the performance of the final system. So, any gain in the efficiency of the on-chip interconnection layer will be highly beneficial for the entire system. Next, we describe the main design factors that should drive any research devoted to NoCs.

#### 2.1.1 Design Factors

As aforementioned, NoCs play a major role in the design of the modern highperformance computers, nevertheless, they are not simple; there are many factors that affect the choice of an appropriate interconnection layer at design time. The main factors are:

- *Performance*. As commented, performance is a key point in interconnection networks, not only from the point of view of raw throughput, but also from the point of view of latency. Latency is a critical design issue in several systems such as real-time systems. Moreover, in on-chip networks, messages must reach destinations in terms of nanoseconds.

- Scalability. Scalability is the first design rule that an interconnect designer should keep in mind. Scalability in interconnection networks implies that the bandwidth of the network increases proportionally to the number of elements of the system. Latency should also be kept to reasonable limits when increasing the system size. Otherwise, the interconnection network would become a bottleneck, limiting the efficiency of the whole system. Scalability also implies that network cost and resources are proportional to the network size.

- *Reliability.* An interconnection network should be able to deliver information in a reliable manner. Interconnection networks should be designed for continuous operation in the presence of a limited number of faults. More important, as technology scales, manufacturing defects will increase, thus demanding an efficient treatment.

- Simplicity. Not only for the sake of cost, but making simpler designs leads to the implementation of architectures that work with higher working frequencies, thus, increasing the system performance, and occupying less area. In fact, the silicon area usage is a critical aspect in on-chip networks. Indeed, reducing the area, translates into the opportunity for making room for more devices inside the chip.

- *Power consumption.* One of the most important aspects in networkson-chip, not critical in other network environments, is the reduction or minimization of power consumption. Indeed, effective power-aware techniques are needed to bring better management of the total power consumed by the processing cores.

All these previous factors must be specifically considered when designing an on-chip network. In this thesis all the contributions take most of these factors as a reference. In the next section we present the basics for interconnection networks.

# 2.2 Interconnection Network Basics

The network architecture design is the result of several design choices like network *topology*, *switching and flow control* techniques and *routing strategies*. The network topology defines the physical interconnection between nodes and other elements. The switching and flow control techniques define how and when the information is transmitted through the network resources. Finally, the routing strategies manage the different path choices of communication between the nodes.

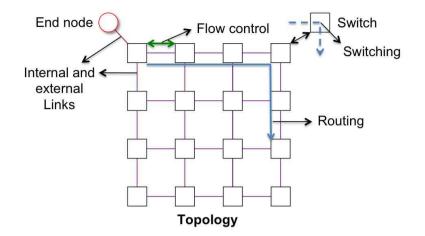

There are some common elements that conform a network architecture. The first elements are the nodes. Nodes are the elements that communicate through the network and perform basically two main tasks: computation and/or storage. Nodes connect to other nodes through a network interface associated to a switch, depending on the topology of the network. A switch is the basic component that connects different devices. Links are used to connect the devices (network interfaces and switches) among them. Figure 2.1 shows

Figure 2.1: Routing, switching and flow control in a network.

a network with a 2D-Mesh topology highlighting where switching, flow control and routing is performed. Next, we describe each network component.

#### 2.2.1 Network Topology

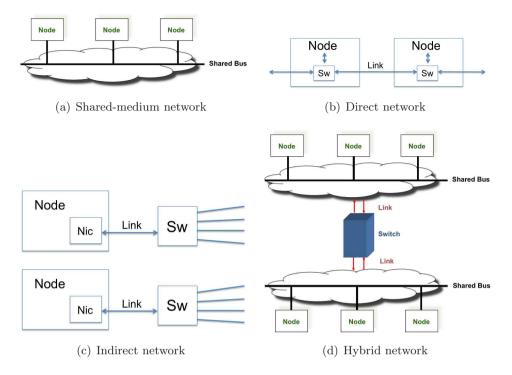

Different network categories can be devised based on how all the elements of a system are connected to the network (see examples in Figure 2.2):

- Shared-medium networks: In this type of network there is a transmission medium that is shared by all the nodes, and only one node is able to begin communication at a time, the rest of nodes read (and monitor) the shared medium. Every device has the circuitry to handle addressing of other nodes and the data management. In these networks, the routing device is the shared medium, called also bus. Buses have limited bandwidth, so they suffer from scalability problems, as the number of connected nodes increases.

- *Direct networks:* Each node has a routing device attached, called switch, which is the component that establishes the connection to other nodes through point-to-point links. Each node is directly connected usually to a small subset of nodes in the network. The concept of network interface is weak in this type of networks as the end node and the switch (also

Figure 2.2: Network architectures.

called router) are tightly connected. Nodes are connected according to a certain interconnection pattern (topology).

- *Indirect networks:* Instead of directly connecting the nodes through point-to-point links, the communication between a pair of nodes can be performed by intermediate stand-alone switches. Every node has a network interface that connects to a switch (through a point-to-point link) and switches are connected between them (also through point-to-point links).

- *Hybrid networks:* This type of networks is a mixture of the previous approaches. In general, they combine mechanisms from shared-medium-networks and direct or indirect networks.

Although there are very subtle differences between direct and indirect networks, the functionality is similar in many aspects. An indirect network in which every switch is connected to a single node is equivalent to a direct network. Also, terms router and switch, although having different meanings, are used with no distinction by the community, so both terms for the routing devices are interchangeable. In the rest of the dissertation, unless noted, the term switch is assumed.

There are also some common aspects to all these types of networks. Although links are usually formed by two communication channels, one in each direction, one of the basic aspects of a network is how communication channels are arranged. Network performance significantly differs if links are bidirectional or unidirectional. This choice impacts directly on the routing techniques and algorithms and associated issues, like deadlock avoidance. We assume the use of bidirectional channels on every link, though.

Each type of network can also be categorized with different properties:

- *Switch degree:* This property refers to the number of channels that connect a switch to its neighbours.

- *Diameter:* Is the maximum distance between a pair of end nodes in the network.

- *Regularity:* A network is defined as regular when all the switches have the same degree.

- *Bisection Bandwidth:* Bisection of the network encompasses the minimum set of links that split the network in two equal halves. Bisection bandwidth is the resulting bandwidth at the bisection.

- *Homogeneity:* A network is homogeneous if every node is equal in all aspects to the rest of nodes.

There are three common basic topologies used in interconnection networks. The first one is the *crossbar*. A crossbar (see Figure 2.3) allows the connection from any node to any other node simultaneously at the same time other connections are established (as long as the requested input and output are free). Crossbar networks, typically, are used for high-performance computing multiprocessor solutions and in the design for switches in direct networks. The drawback with crossbar topologies is that they do not scale well as system grows due to the quadratic requirement of connections.

Figure 2.3: A crossbar network.

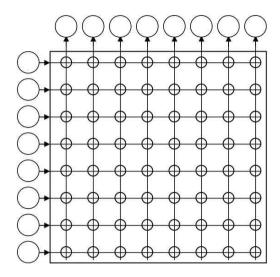

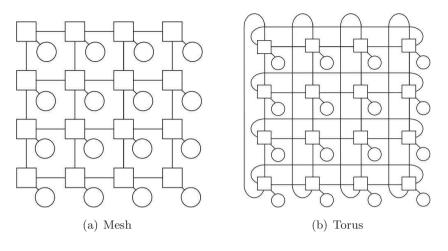

Strictly orthogonal topologies are the second common type. In this kind of networks we can find the *n*-dimensional meshes and tori (see Figure 2.4). A n-dimensional mesh or torus has k nodes placed along each dimension. A mesh differs from a torus because it does not have the wraparound channels that connect the nodes at the borders of the topology. Note that the torus topology duplicates the bisection bandwidth of the mesh topology and reduces the diameter. These topologies are the most common example of direct networks.

Multistage interconnection networks (MINs) are topologies driven by the concept of indirect networks as seen in Figure 2.5. Between input and output devices there are several switch stages. Examples of these networks are Clos networks, tree based networks or the butterfly network [7]. The arrangement of stages and the connection patterns determine the routing in these networks. MINs have been heavily used to interconnect parallel computers with large number of processors in commercial and high-performance solutions. However, for on-chip networks mapping of such topology pattern in the 2-dimensional surface of the chip is a big challenge [23].

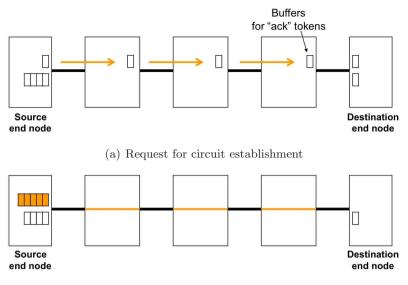

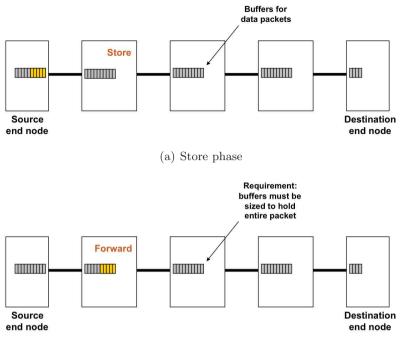

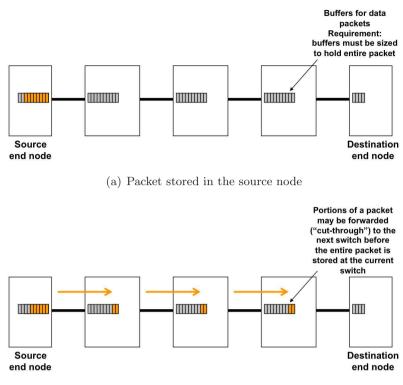

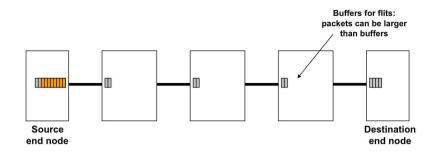

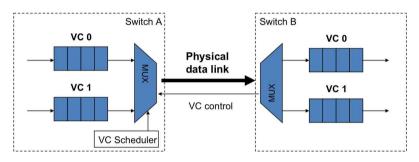

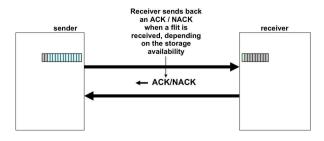

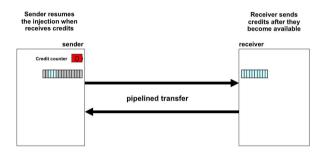

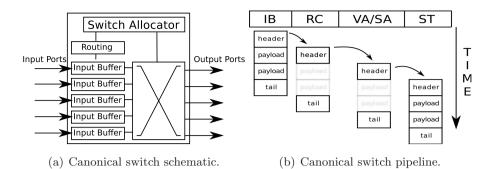

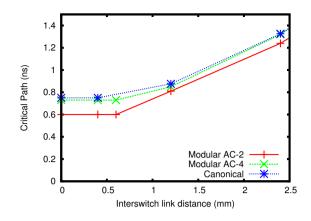

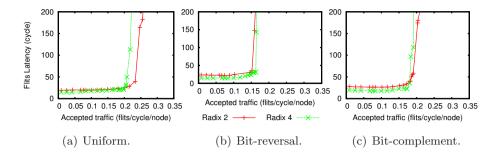

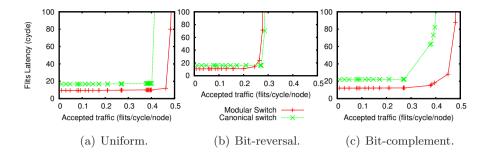

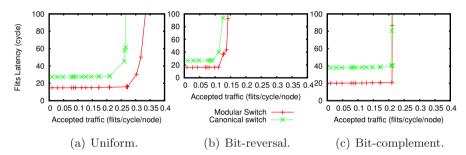

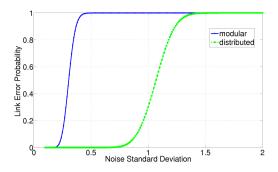

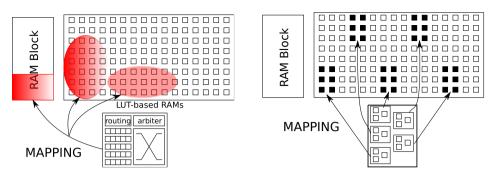

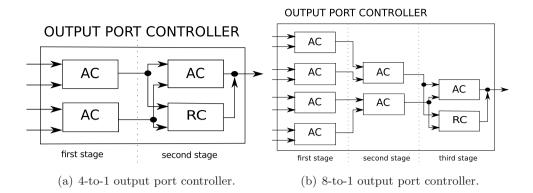

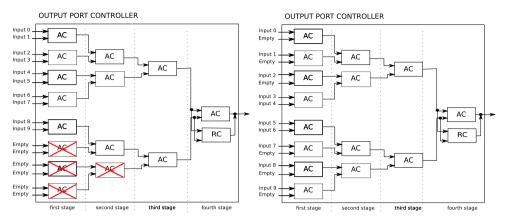

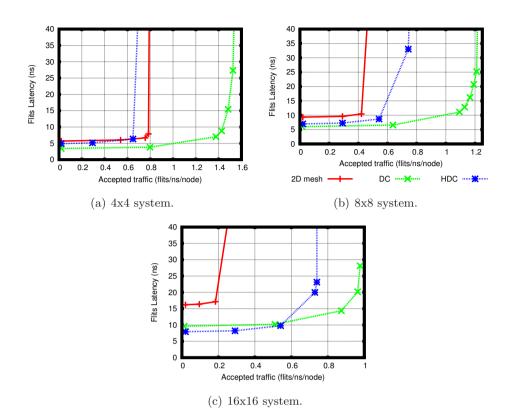

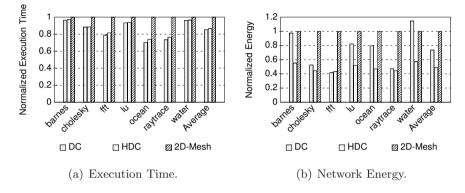

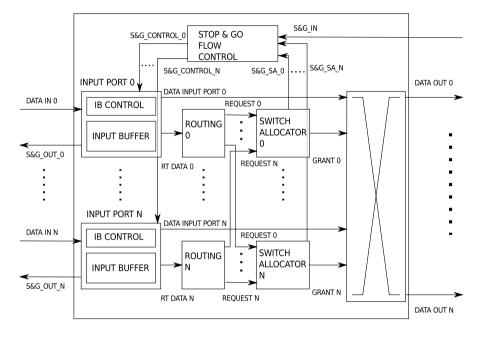

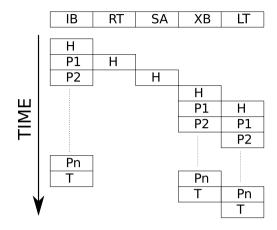

Figure 2.4: A  $4 \times 4$  2-dimensional mesh and torus.