## DEPARTAMENTO DE INFORMÁTICA DE SISTEMAS Y COMPUTADORES

# Interference Analysis and Resource Management in Server Processors: From HPC to Cloud Computing

A thesis submitted in fulfillment with the requirements for the degree of

Doctor of Philosophy (Computer Engineering)

Author

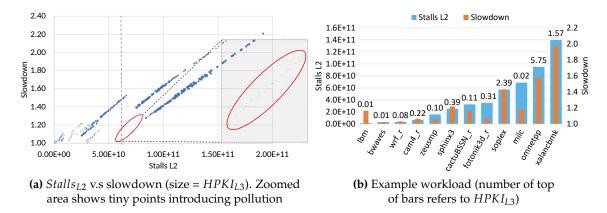

Lucía Pons Escat

Advisor

Prof. Julio Sahuquillo Borrás

Valencia, June 2023

# Agradecimientos

"El éxito es la consecuencia directa de la perseverancia".

"La gratitud nos fortalece, enriquece y eleva". Rafa Sansores Majul

Esta tesis es la culminación de años de esfuerzo, dedicación y determinación: un sueño cumplido. El doctorado ha supuesto una experiencia de aprendizaje excepcional. No ha sido un camino fácil: una pandemia, una diabetes y muchos resultados fallidos, pero la constancia y la perseverancia han sido clave para superar todos los obstáculos y alcanzar mis metas. Por ello, escribo estas palabras muy feliz y orgullosa de mi misma.

Una parte fundamental para haber logrado esta tesis han sido todas las personas que han estado junto a mi, cuyo apoyo ha sido crucial. Quiero agradecer, en primer lugar, a mi director de tesis, Julio Sahuquillo, quien ha confiado en mi desde que era alumna de 2ndo de grado y me ha guiado en mi carrera investigadora. Gracias por todo lo que me has enseñado y las innumerables horas que has dedicado a ayudarme a realizar los trabajos de esta tesis. Gracias por involucrarme en diferentes proyectos que, aunque a veces fuera todo un reto, me han permitido adquirir una experiencia de valor incalculable.

En segundo lugar, quisiera agradecer a las personas con las que he tenido el placer de trabajar. A Timothy M. Jones, por su gran acogida en la Universidad de Cambridge (a pesar de la pandemia) así como su contribución en uno de los trabajos realizados en esta tesis. A Chaoyi Huang, por proponernos un proyecto ambicioso del cual es fruto una parte importante de esta tesis. A Salva Petit y María Engracia Gómez, por su ayuda y sus valiosos consejos que han enriquecido los trabajos de esta tesis. A mi padre, Julio Pons, por ser mi mano derecha y ayudarme a resolver los problemas que surgían. A Vicent Selfa, por iniciarme en los primeros pasos y obligarme a dar lo mejor de mi. A Josué Feliu, por compartir su experiencia y ayudarme con las dudas que he tenido. A Marta Navarro, por ayudarme a desarrollar la faceta de enseñar y ser una gran compañera.

También quiero dar las gracias a mis compañeros de laboratorio y del GAP por los buenos momentos que hemos disfrutado juntos, sobre todo en los viajes a ACACES, SARTECO 2022 y Nápoles. Y por supuesto a mis amigos/as y a mi falla por esos momentos de desconexión y risas tan necesarios.

Finalmente, quiero agradecer a las personas más importantes de mi vida, mi familia. A mis padres, gracias por inculcarme el valor del esfuerzo y enseñarme a sobreponerme a las adversidades. Pero sobretodo, por apoyarme en cada paso que doy y animarme en los momentos más difíciles. Vuestra sonrisa de orgullo es la mejor recompensa. A mis abuelos, por su amor infinito que siempre me da fuerzas. A mis hermanos mayores, con los que puedo contar siempre. A Julio y Miljana, por su apoyo y cariño, y al pequeño Julio que ha llenado la familia de felicidad. A Alfonso, por ser mi fiel compañero y estar siempre a mi lado. Y también a mi novio, Mario, por sacarme una sonrisa cuando más lo necesito. Gracias por motivarme a ser mejor cada día y perseguir mis sueños.

# **Abstract**

One of the main concerns of today's data centers is to maximize server utilization. In each multi-core server processor, multiple applications are executed concurrently, increasing resource efficiency as system resources are shared. However, performance and fairness are highly dependent on the share of resources that each application receives, leading to performance unpredictability. The rising number of cores (and running applications) with every new generation of processors is leading to a growing concern for interference at the shared resources.

Resource sharing has been typically tackled in High-Performance Computing (HPC); nevertheless, due to the increasing prominence of cloud computing, issues typically handled in HPC are now being targeted in this domain. This thesis focuses on addressing resource interference when different applications are consolidated on the same server processor from two main perspectives: HPC and cloud computing.

In the context of HPC, resource management approaches are proposed to reduce interapplication interference at two major critical resources: the last level cache (LLC) and the processor cores. The LLC plays a key role in the system performance of current multicores by reducing the number of long-latency main memory accesses. LLC partitioning approaches are proposed for both inclusive and non-inclusive LLC, as both designs are present in current server processors. In both cases, newly problematic LLC behaviors are identified and efficiently detected, granting a larger cache share to those applications that make profitable use of the LLC space. As for processor cores, many parallel applications, like graph applications, do not scale well with an increasing number of threads/processes due to hardware and software issues. However, the default Linux time-sharing scheduler performs poorly when running graph applications, which, unlike other scientific applications, process vast amounts of data. To maximize system utilization, this thesis proposes to co-locate multiple graph applications on the same server processor by assigning the optimal number of cores to each one. By dynamically adapting the number of threads spawned by the running applications, it is possible to change the number of cores allocated to meet applications' runtime requirements.

When studying the impact of system shared resources on cloud computing, this thesis addresses three major challenges: the complex infrastructure of cloud systems, the nature of cloud applications, and the impact of inter-VM interference on the VMs' performance. Firstly, this dissertation presents the experimental platform developed to perform repre-

sentative cloud performance studies with the main cloud system components (hardware and software). Secondly, an extensive characterization study is presented on a set of representative latency-critical workloads as many important cloud workloads must meet strict quality of service (QoS) requirements to provide a satisfactory user experience. The aim of the studies is to outline considerations cloud providers should take into account to improve performance and resource utilization. Finally, we propose an online approach that detects and accurately estimates inter-VM interference in scenarios with multiple colocated latency-critical VMs. The approach relies on metrics that can be easily monitored in the public cloud as VMs are handled as "black boxes". The research described above is carried out following the restrictions and requirements to be applicable to public cloud production systems.

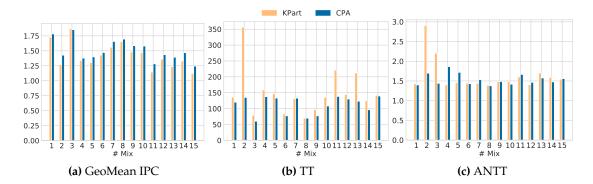

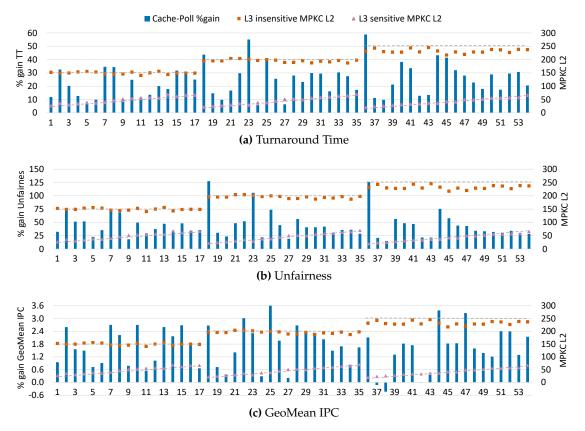

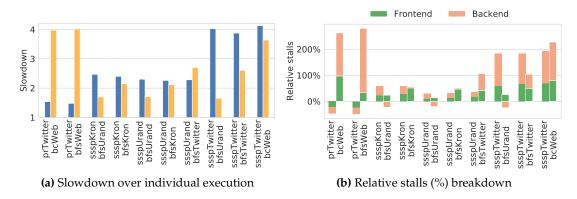

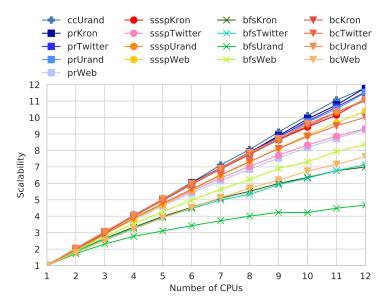

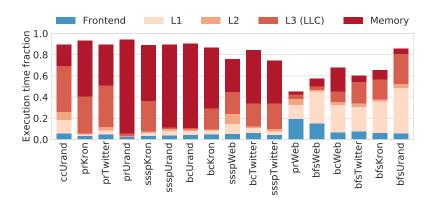

In summary, this thesis addresses contention in the main system shared resources in the context of server consolidation, both in HPC and cloud computing. Experimental results show that important gains are obtained over the Linux OS scheduler by reducing the interference at the shared resources. In inclusive LLCs, turnaround time (TT) is reduced by over 40% while sustaining (and even improving) IPC by more than 3%. In non-inclusive LLCs, fairness and TT are improved by 44% and 24%, respectively, while even improving performance up to 3.5%. By distributing core resources efficiently, an almost perfect fairness can be obtained (on average 94%), and TT can be reduced by up to 80% In cloud computing environments, performance degradation due to resource contention can be estimated with an overall prediction error of 5%. All of the approaches proposed in this dissertation have been designed to be applied in commercial server processors without requiring any prior information. Decisions are performed dynamically at execution time using the data collected from the hardware performance counters.

# Resumen

Una de las principales preocupaciones de los centros de datos actuales es maximizar la utilización de los servidores. En cada servidor o procesador multinúcleo se ejecutan simultáneamente varias aplicaciones, lo que aumenta la eficiencia de los recursos gracias a la compartición de los mismos. Sin embargo, el rendimiento y la equidad dependen en gran medida de la proporción de recursos que recibe cada aplicación, lo que provoca que su tiempo de ejecución sea imprevisible. El creciente número de núcleos (y de aplicaciones ejecutándose al mismo tiempo) con cada nueva generación de procesadores hace que crezca la preocupación por el efecto causado por las interferencias en los recursos compartidos.

La compartición de recursos se ha abordado típicamente en la computación de alto rendimiento (HPC); sin embargo, debido a la creciente importancia de la computación en la nube, los problemas que suelen tratarse en HPC se han trasladado a este ámbito. Esta tesis se centra en mitigar la interferencia en los recursos compartidos cuando diferentes aplicaciones se consolidan en un mismo procesador desde dos perspectivas: HPC y computación en la nube.

En el contexto de HPC, para reducir la interferencia causada por la ejecución concurrente de múltiples aplicaciones, en esta tesis se proponen políticas de gestión para dos de los recursos más críticos del sistema: la caché de último nivel (LLC) y los núcleos del procesador. La LLC desempeña un papel clave en las prestaciones del sistema con los procesadores multinúcleo actuales ya que reducen considerablemente el número de accesos de alta latencia a la memoria principal. Se proponen estrategias de particionado de la LLC tanto para cachés inclusivas como no inclusivas, ya que ambos diseños están presentes en la actualidad en los procesadores para servidores. Para los dos esquemas de caché, se identifican y detectan eficientemente nuevos comportamientos problemáticos en lo que se refiere a la LLC. Esto permite asignar un mayor espacio de caché a aquellas aplicaciones que hacen un uso eficiente del mismo. En cuanto a los núcleos del procesador, muchas aplicaciones paralelas, como las aplicaciones de grafos, no escalan bien a medida que se incrementa el número de hilos/procesos debido a problemas hardware y software. Sin embargo, el planificador de Linux, que aplica una estrategia de tiempo compartido, no ofrece buenas prestaciones cuando se ejecutan aplicaciones de grafo, ya que, a diferencia de otras aplicaciones científicas, procesan grandes cantidades de datos. Para maximizar la utilización del sistema, esta tesis propone ejecutar múltiples aplicaciones de grafo simultáneamente en el mismo procesador, asignando el número óptimo de núcleos

a cada una. Adaptando el número de hilos creados por las aplicaciones en tiempo de ejecución, es posible cambiar el número de núcleos asignados para satisfacer los requisitos de las aplicaciones de manera dinámica.

Para estudiar el impacto de los recursos compartidos del sistema en la computación en la nube, esta tesis aborda tres grandes retos: la compleja infraestructura de los sistemas en la nube, las características de las aplicaciones que se ejecutan en la nube y el impacto de la interferencia entre máquinas virtuales (MV) en el rendimiento de éstas. En primer lugar, esta tesis presenta la plataforma experimental desarrollada con los principales componentes de un sistema en la nube (hardware y software) para realizar estudios representativos del rendimiento de la nube. En segundo lugar, se presenta un amplio estudio de caracterización sobre un conjunto de aplicaciones de latencia crítica representativas, ya que muchas cargas de trabajo importantes en la nube deben cumplir estrictos requisitos de calidad de servicio (QoS) para brindar una experiencia de usuario satisfactoria. El objetivo de los estudios es identificar las cuestiones que los proveedores de servicios en la nube deben tener en cuenta para mejorar el rendimiento y la utilización de los recursos. Por último, se realiza una propuesta que, de manera dinámica, permite detectar y estimar de forma precisa la interferencia entre MV en escenarios en los que se ejecutan múltiples MV con aplicaciones de latencia crítica. El enfoque se basa en métricas que pueden monitorizarse fácilmente en la nube pública, ya que las MV deben tratarse como "cajas negras". Toda la investigación descrita se lleva a cabo respetando las restricciones y cumpliendo los requisitos para ser aplicable en entornos de producción en la nube pública.

En resumen, esta tesis aborda la contención en los principales recursos compartidos del sistema en el contexto de la consolidación de servidores, tanto en entornos de altas prestaciones como en entornos de nube. Los resultados experimentales muestran importantes ganancias de prestaciones sobre el planificador del sistema operativo Linux al reducir las interferencias en los recursos compartidos. En los procesadores con LLC inclusiva, el tiempo de ejecución (TT) se reduce en más de un 40%, mientras que se mantiene (e incluso mejora) el IPC en más de un 3 %. En los sistemas con LLC no inclusiva, la equidad y el TT mejoran en un 44 % y un 24 %, respectivamente, al mismo tiempo que se obtiene una mejora del rendimiento de hasta en un 3,5 %. Al distribuir los núcleos del procesador de forma eficiente, se alcanza una equidad casi perfecta (de media un 94 %), y el TT puede reducirse hasta un 80 %. En entornos de computación en la nube, la degradación del rendimiento debido a la contención en los recursos compartidos puede estimarse con un error de un 5 % en la predicción global. Todas las propuestas presentadas en esta tesis han sido diseñadas para ser aplicadas en procesadores de servidores comerciales sin requerir ninguna información previa. Las decisiones se toman dinámicamente en tiempo de ejecución utilizando los datos recogidos de los contadores de prestaciones hardware.

# Resum

Una de les principals preocupacions dels centres de dades actuals és maximitzar la utilització dels servidors. A cada servidor o processador multinucli s'executen simultàniament diverses aplicacions, cosa que augmenta l'eficiència dels recursos gràcies a la compartició dels mateixos. Tot i això, el rendiment i l'equitat depenen en gran mesura de la proporció de recursos que rep cada aplicació, cosa que provoca que el seu temps d'execució siga imprevisible. El nombre creixent de nuclis (i aplicacions executant-se alhora) amb cada nova generació de processadors fa que creixca la preocupació per l'efecte causat per les interferències en els recursos compartits.

La compartició de recursos s'ha abordat típicament a la computació d'alt rendiment (HPC); no obstant això, a causa de la creixent importància de la computació al núvol, els problemes que solen tractar-se en HPC s'han traslladat a aquest àmbit. Aquesta tesi se centra a mitigar la interferència en els recursos compartits quan diferents aplicacions es consoliden en un mateix processador des de dues perspectives: HPC i computació al núvol.

En el context d'HPC, per reduir la interferència causada per l'execució concurrent de múltiples aplicacions, en aquesta tesi es proposen polítiques de gestió per a dos dels recursos més crítics del sistema: la memòria cau d'últim nivell (LLC) i els nuclis del processador. La LLC exerceix un paper clau a les prestacions del sistema en els processadors multinucli actuals ja que redueixen considerablement el nombre d'accessos d'alta latència a la memòria principal. Es proposen estratègies de particionament de la LLC tant per a caus inclusives com no inclusives, ja que ambdós dissenys són presents actualment en els processadors per a servidors. Per als dos esquemes de memòria cau, s'identifiquen i detecten eficientment nous comportaments problemàtics pel que fa a la LLC. Això permet assignar un major espai de memòria cau a aquelles aplicacions que en fan un ús eficient. Pel que fa als nuclis del processador, moltes aplicacions paral·leles, com les aplicacions de grafs, no escalen bé a mesura que s'incrementa el nombre de fils/processos a causa de problemes *hardware* i *software*. Tot i això, el planificador de Linux, que aplica una estratègia de temps compartit, no ofereix bones prestacions quan s'executen aplicacions de graf, ja que, a diferència d'altres aplicacions científiques, processen grans quantitats de dades. Per maximitzar la utilització del sistema, aquesta tesi proposa executar múltiples aplicacions de grafs simultàniament al mateix processador, assignant el nombre òptim de nuclis a cadascuna. Adaptant el nombre de fils creats per les aplicacions en temps

d'execució, és possible canviar el nombre de nuclis assignats per satisfer els requisits de les aplicacions de manera dinàmica.

Per estudiar l'impacte dels recursos compartits del sistema a la computació al núvol, aquesta tesi aborda tres grans reptes: la complexa infraestructura dels sistemes al núvol, les característiques de les aplicacions que s'executen al núvol i l'impacte de la interferència entre màquines virtuals (MV) al rendiment d'aquestes. En primer lloc, aquesta tesi presenta la plataforma experimental desenvolupada amb els principals components d'un sistema al núvol (hardware i software) per fer estudis representatius del rendiment del núvol. En segon lloc, es presenta un ampli estudi de caracterització sobre un conjunt d'aplicacions de latència crítica representatives, ja que moltes càrregues de treball importants al núvol han de complir requisits de qualitat de servei estrictes (QoS) per brindar una experiència d'usuari satisfactòria. L'objectiu dels estudis és identificar les güestions que els proveïdors de serveis al núvol han de tenir en compte per millorar el rendiment i la utilització dels recursos. Finalment, es fa una proposta que de manera dinàmica permet detectar i estimar de manera precisa la interferència entre MV en escenaris on s'executen múltiples MV amb aplicacions de latència crítica. L'enfocament es basa en mètriques que es poden monitoritzar fàcilment al núvol públic, ja que les MV han de tractar-se com a "caixes negres". Tota la investigació descrita es duu a terme respectant les restriccions i complint els requisits per ser aplicable en entorns de producció al núvol públic.

En resum, aquesta tesi aborda la contenció en els principals recursos compartits del sistema en el context de la consolidació de servidors, tant en entorns d'altes prestacions com en entorns de núvol. Els resultats experimentals mostren que s'obtenen importants guanys sobre el planificador del sistema operatiu Linux en reduir les interferències en els recursos compartits. En els processadors amb una LLC inclusiva, el temps d'execució (TT) es redueix en més d'un 40%, mentres que es manté (i fins i tot millora) l'IPC en més d'un 3%. En els que tenen una LLC no inclusiva, l'equitat i el TT es milloren en un 44% i un 24%, respectivament, al mateix temps que s'obté una millora del rendiment de fins a un 3,5%. Distribuint els nuclis del processador de manera eficient es pot obtindre una equitat quasi perfecta (de mitjana un 94%), i el TT pot reduir-se fins a un 80%. En entorns de computació al núvol, la degradació del rendiment degut a la contenció en els recursos compartits pot estimar-se amb un error de predicció global d'un 5%. Totes les propostes presentades en aquesta tesi han sigut dissenyades per a ser aplicades en processadors de servidors comercials sense requerir cap informació prèvia. Les decisions es prenen dinàmicament en temps d'execució utilitzant les dades recollides dels comptadors de prestacions hardware.

# List of Acronyms

ANTT Average Normalized Turnaround Time

CBM Capacity Bitmask

CLOS Class of Service

DDR Double Data Rate

DIMM Dual In-line Memory Module

DRAM Dynamic Random Access Memory

EDP Energy Delay Product FaaS Function as a Service

GIPS Giga Instructions Per Second

HPC High-Performance Computing

HPKI\_LLC Hits Per Kilo Instruction of the LLC

I/O Input/Output

IaaS Infrastructure as a Service

Intel CAT Intel Cache Allocation Technology

Intel MBA Intel Memory Bandwidth Allocation

Intel RDT Intel Resource Director Technologies

IPC Instructions Per Cycle LLC Last Level Cache

MPKC\_LLC Misses Per Kilo Cycle of the LLC MPKI\_LLC Misses Per Kilo Instruction of the LLC

NUMA Non-Uniform Memory Access

PCIe Peripheral Component Interconnect Express

PID Process Identifier

QoS Quality of Service

QPS Queries Per Second

SLA Service Level Agreement

SMT Simultaneous MultiThreading

SSD Solid-State Drives

TT Turnaround Time

vCPU Virtual CPU

VM Virtual Machine

# Contents

| A  | bstra             | ct                                       | V        |

|----|-------------------|------------------------------------------|----------|

| R  | esum              | en                                       | vii      |

| R  | esum              |                                          | ix       |

| Li | st of             | Acronyms                                 | xi       |

|    | onten             |                                          | xiii     |

| 1  |                   | roduction                                | 1        |

| 1  | 1.1               | Resource Sharing in Server Processors    | 1        |

|    | 1.1               | Cloud Computing Paradigm                 | 3        |

|    | 1.3               | Objectives of the Thesis                 | 5        |

|    | 1.4               | Main Contributions of the Thesis         | 6        |

|    | 1.4               |                                          | 8        |

| _  |                   | Thesis Outline                           |          |

| 2  |                   | te of the Art                            | 9        |

|    | 2.1               | Resource Management Approaches           | 9        |

|    | 2.2               | Emerging Workloads in Server Processors  | 12       |

|    | 2.3               | Interference in Cloud Systems            | 15       |

| 3  | Exp               | erimental Framework                      | 17       |

|    | 3.1               | Experimental Platforms                   | 17       |

|    | 3.2               | Cloud Computing Infrastructure           | 19       |

|    | 3.3               | Resource and Application Manager         | 22       |

|    | 3.4               | Benchmarks                               | 26       |

|    | 3.5               | Metrics                                  | 28       |

| I  | Hig               | gh-Performance Computing (HPC)           | 31       |

| 4  | _                 | usive LLC Resource Management            | 33       |

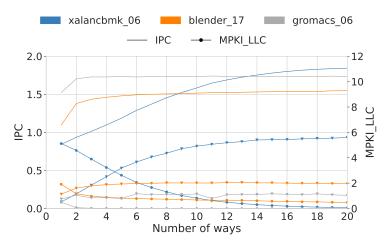

| •  | 4.1               | Application Sensitivity to the LLC Space | 34       |

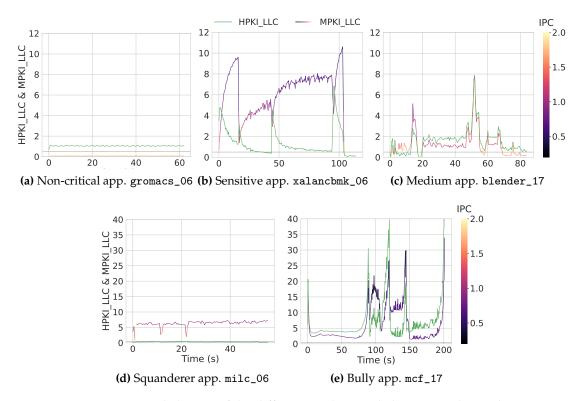

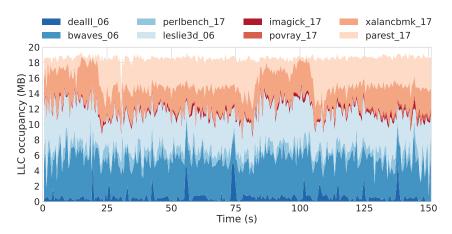

|    | 4.2               | Dynamic Behavior of Applications         | 37       |

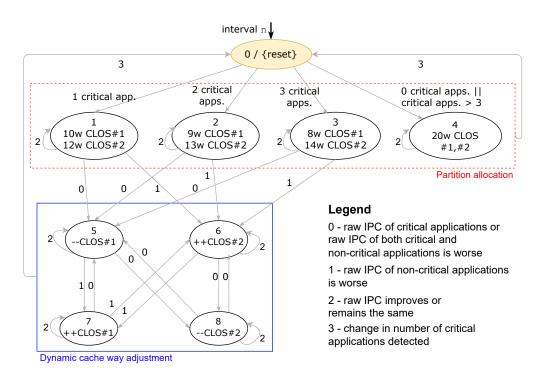

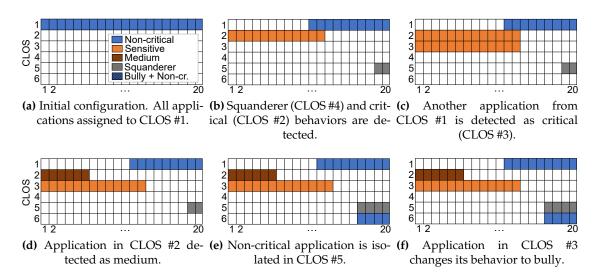

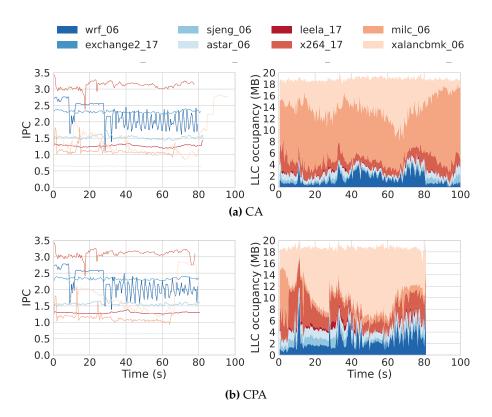

|    | 4.3               | Critical-Aware Approach                  | 41       |

|    | $\frac{4.5}{4.4}$ | Critical Phase-Aware Proposal            | 43       |

|    | 4.5               | Experimental Setup                       | 49       |

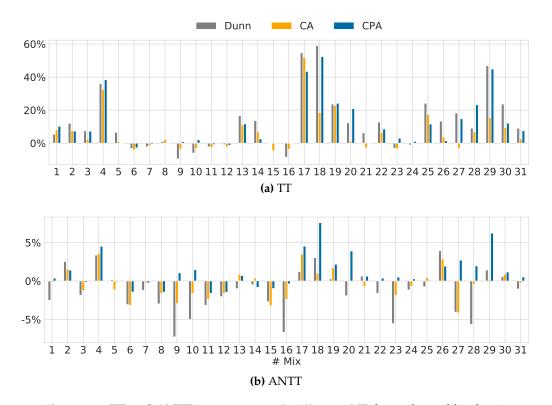

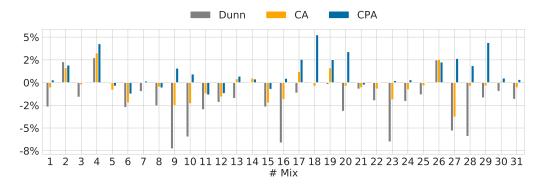

|    | 4.6               | Evaluation                               | 50       |

|    | 4.7               |                                          | 56       |

| _  |                   | Summary                                  |          |

| 5  |                   | n-Inclusive LLC Resource Management      | 57       |

|    | 5.1<br>5.2        | Motivation                               | 57<br>58 |

|    | $^{\prime}$       | Background                               | אר       |

#### **CONTENTS**

| 6  | 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br><b>Core</b><br>6.1 | Characterizing L3 Cache Behavior Cache-Poll Approach Experimental Setup Evaluation Summary Resource Management Motivation: Weaknesses of the Default Linux Time-Sharing Scheduler with | 59<br>63<br>66<br>68<br>72<br><b>73</b> |

|----|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|    |                                                       | Graph Workloads                                                                                                                                                                        | 74                                      |

|    | 6.2                                                   | Experimental Setup                                                                                                                                                                     | 75<br>76                                |

|    | 6.3<br>6.4                                            | Graph Model and Stratical School along                                                                                                                                                 | 76<br>80                                |

|    | 6.5                                                   | Graph Workloads Spatial Scheduler                                                                                                                                                      | 85                                      |

|    | 6.6                                                   | Summary                                                                                                                                                                                | 89                                      |

|    | 0.0                                                   |                                                                                                                                                                                        | 0,                                      |

| II | Clo                                                   | oud Computing                                                                                                                                                                          | 91                                      |

| 7  |                                                       | kload Characterization in the Public Cloud                                                                                                                                             | 93                                      |

| -  | 7.1                                                   | Experimental Methodology                                                                                                                                                               | 94                                      |

|    | 7.2                                                   | QoS and Tail Latency Analysis                                                                                                                                                          | 97                                      |

|    | 7.3                                                   | Major System Resource Consumption Analysis and Findings' Correlation                                                                                                                   | 101                                     |

|    | 7.4                                                   | Analysis of Inter-VM Interference at the Main Shared Resources                                                                                                                         | 106                                     |

|    | 7.5                                                   | Summary                                                                                                                                                                                | 111                                     |

| 8  | Dete                                                  | ecting and Estimating Inter-VM Interference in the Public Cloud                                                                                                                        | 113                                     |

|    | 8.1                                                   | Motivation                                                                                                                                                                             | 114                                     |

|    | 8.2                                                   | Experimental Setup                                                                                                                                                                     | 115                                     |

|    | 8.3<br>8.4                                            | Cloud White: Detecting the Inter-VM Interference                                                                                                                                       | 117<br>120                              |

|    | 8.5                                                   | Cloud White: Modeling Performance Degradation                                                                                                                                          | 120                                     |

|    | 8.6                                                   | Comparison to Prior Work                                                                                                                                                               | 132                                     |

|    | 8.7                                                   | Applying Cloud White to Improve QoS                                                                                                                                                    | 133                                     |

|    | 8.8                                                   | Summary                                                                                                                                                                                | 134                                     |

|    |                                                       |                                                                                                                                                                                        |                                         |

| 9  | Con                                                   | clusions                                                                                                                                                                               | 135                                     |

|    | 9.1                                                   | Contributions                                                                                                                                                                          | 135                                     |

|    | 9.2                                                   | Future Directions                                                                                                                                                                      | 139                                     |

|    | 9.3                                                   | Publications                                                                                                                                                                           | 140                                     |

| Re | ferer                                                 | ices                                                                                                                                                                                   | 143                                     |

# Introduction

This chapter presents the main research issues addressed in this doctoral thesis and the motivation for the work done. To help contextualize the research problem, first, important background information is provided on interference at the main system resources, focusing on the last level cache (LLC) and core resources. Resource sharing has been typically addressed in High-Performance Computing (HPC); however, the growing popularity of cloud computing makes that problems commonly faced in HPC shift to this area. In this regard, compared to HPC, the challenges faced in cloud computing are magnified due to the importance of managing resource interference in public clouds to meet QoS requirements. Finally, the objectives and main contributions of this thesis are described.

## 1.1 Resource Sharing in Server Processors

Current data centers are equipped with thousands of modern high-performance multicore processors. Each single processor allows multiple applications to be executed concurrently, increasing resource utilization thanks to resource sharing. As the co-running applications compete for the shared resources and present different resource demands, the performance of each individual application becomes unpredictable. In other words, the inter-application interference affects differently to each application yielding the system to performance unpredictability, which aggravates as the *unfairness* grows. This thesis focuses on analyzing the inter-application interference and proposing management strategies to deal both with performance and unfairness. The research concentrates on two major critical resources: the LLC and the processor cores.

#### 1.1.1. Last Level Cache (LLC)

Modern processors commonly implement a three-level cache hierarchy. The lower cache levels (e.g., L2 and L3) are key components to hide the long main memory latencies, and so they are sized big to reduce the number of accesses to the off-chip main memory. While the L2 cache is private to the core, the L3 or the last level cache (LLC) is

shared among all cores. The fact that the LLC is shared allows to improve its utilization and presents important advantages over splitting its storage capacity into smaller private caches [1]. However, sharing the LLC can lead to important shortcomings from a system performance perspective. One of the most harmful effects is known as *cache pollution*, which refers to inaccurate prefetch requests [2, 3] that fill up the cache with blocks that are never (or scarcely) referenced again, replacing other useful blocks.

The destructive interference among applications accessing the LLC increases the number of accesses to the off-chip main memory, which incur long latencies that can severely impact on the system performance. For this reason, the common design choice taken by computer architects is to provide a huge LLC, in the order of a few MBs per core, which adds up to tens of MBs. The capacity becomes even larger when the LLC is built using denser memory technologies, like the eDRAM (embedded DRAM) used in the IBM POWER9 [4] and in the Intel Knights Landing [5] processors.

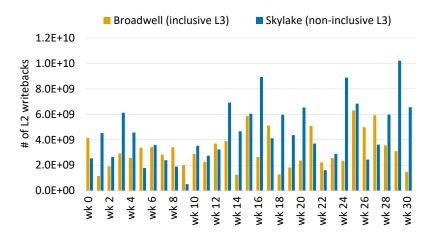

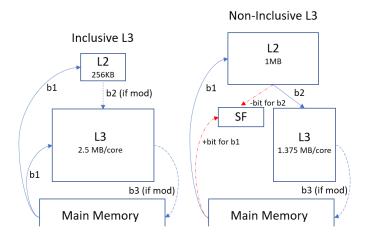

In recent years, the increasing number of cores and the ongoing pursuit of better performance has motivated the trend towards a higher reliance on private caches (e.g., large L2 caches [6]). Therefore, new cache hierarchy organizations were introduced aimed at keeping a larger amount of private data closer to the processor. Among these designs, non-inclusive caches have been implemented in recent processors [7, 8, 9]. This design choice avoids cache line replication (i.e., in the L2 and the LLC), using the available cache space more efficiently. In this organization, the L2 cache is made larger, and the LLC slice is reduced over that of inclusive LLCs. Overall, the cache space per core is reduced, saving silicon area. The fact that there is less space per core to manage makes cache management more critical in processors with a non-inclusive LLC than with an inclusive LLC. In addition, the number of accesses to the LLC is typically higher since it acts as a victim cache of the L2 cache. This means that a fierce competition for cache space can take place. Consequently, making efficient use of the smaller LLC space is even more critical than in inclusive caches, as the *cache pollution* effect is magnified.

To address the interference at the LLC, some processor manufacturers like Intel, ARM, and AMD have deployed technologies in server processors that allow distributing LLC cache ways among co-running applications. For instance, Intel has deployed *Cache Allocation Technology* (CAT) [10], which allows creating cache partitions and assigning them to applications. The first processors that deployed Intel CAT had an inclusive LLC. This technology has also been included in newer processors with a memory hierarchy containing a non-inclusive LLC.

#### **1.1.2. CPU** Cores

Server processors are made up of multiple cores. Most processor manufacturers implement the simultaneous multithreading (SMT) paradigm [11], which allows a physical core to issue instructions from different threads in each cycle. SMT allows increasing the processor throughput; however, instructions from the threads concurrently running on the same core compete, among other shared resources, for the scarce number of issue ports, thus, introducing inter-thread interference that harms their performance with

respect to their individual execution. Intel's implementation of the SMT paradigm is known as Hyper-Threading technology [12]. It typically supports the concurrent execution of two threads. From the OS perspective, a given physical core is seen as two logical cores or CPUs. In a multi-core processor with Hyper-Threading cores, it is important to differentiate between physical and logical cores when analyzing resource sharing. Two threads running on different physical cores only share the off-core processor resources, mainly the LLC and main memory. However, when two threads are assigned to the two logical cores of the same physical core, they also compete for intra-core components. These components are critical for performance and include, among others, issue ports, reorder buffer (ROB), physical registers, load queue, store queue, functional units, as well as L1 and L2 caches. As a consequence, the performance of a given thread highly depends on the demands of the internal components of the thread it is co-running with [13].

The current trend in server processors is to increase the number of cores. Recent processors like the 4th generation Xeon Scalable CPUs deploy up to 60 cores [14], and AMD EPYC processors include up to 128 cores [15]. To provide full system utilization, processor cores must be fully subscribed. Many parallel scientific applications [16, 17, 18, 19] provide the capability of launching as many threads/processes as available cores.

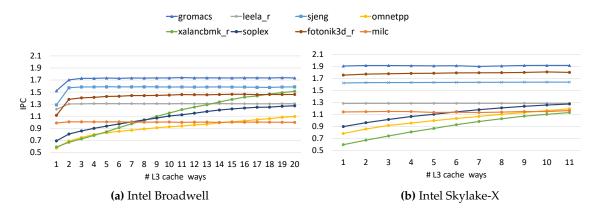

Over the last years, research initiatives have been proposed to make parallel applications' number of threads/processes reconfigurable. However, many parallel applications are not capable of scaling as the number of threads increases due to different hardware and software issues: load balancing, data synchronization, cache interference, issue bandwidth, and functional-unit saturation [20, 21, 22]. For this reason, many research efforts have been made to use hardware resources best by adjusting the thread-level parallelism (TLP) of multithreaded applications. More precisely, by assigning to an application the *optimal* number of cores so that it launches the number of threads that achieves maximum performance, avoiding resources being wasted or underused. To this end, parallel applications must be able to adapt the number of threads/processes dynamically at execution time.

## 1.2 Cloud Computing Paradigm

Cloud computing has evolved as a key computing paradigm. An increasing amount of computing is being performed in public clouds, such as Amazon's EC2 [23], Microsoft Azure [24], and Google Compute Engine [25]. Compared to traditional on-site setups, cloud platforms provide two major advantages for end-users [26, 27]: i) cost efficiency as users can quickly launch jobs without the up-front and operational costs of owning a cluster, and ii) flexibility as users can easily request or release computational resources.

Most public cloud systems deploy powerful computing servers. Following the typical virtualization model, the cloud provider allocates multiple virtual machines (VMs) in the same physical machine, which provides fault isolation, security, and improved manageability. This enables high flexibility and resource control.

#### 1.2.1. Issues and Particularities of Public Cloud Systems

Compared to research carried out in the context of HPC, cloud computing research imposes multiple challenges, especially if research is intended to be applicable to public cloud production systems.

In order to perform representative cloud performance studies, the experimental platform should resemble as much as possible to a real production environment. This fact is especially hard to achieve due to the complexity (both hardware and software) of production systems. Consequently, research works simplify the experimental framework. Unfortunately, existing studies omit important system components [28, 29, 30, 31, 32, 33] or do not consider virtualization with VMs [34, 30, 31, 33], which results in losses of representativeness.

Despite the public cloud can run any kind of workload, an important characteristic that makes public cloud servers different from traditional computing nodes is that they frequently run latency-critical workloads. Most online or interactive services are examples of these workloads. Unlike scientific workloads used in HPC, the performance of latency-critical applications is given by the obtained tail latency, indicated as a percentile (e.g., 95<sup>th</sup> or 99<sup>th</sup>) of all the latencies and accounts for the requests that take longer to complete.

A major shortcoming that cloud providers need to face when measuring and evaluating performance is that they do not have information about the applications running on the VMs. This means that VMs are treated as "black boxes".

#### 1.2.2. Resource Sharing and QoS

The fact that cloud providers co-locate multiple VMs in the same physical machine means that inter-VM performance interference will appear due to competition for the major system resources (e.g., processor cores, LLC, or main memory), making performance unpredictable. In other words, the interference adversely impacts on the quality of service (QoS) of the applications. Moreover, when the QoS degrades, it might not comply with the service level objectives (SLOs) stated in the service level agreement (SLA) between a cloud provider and a customer.

To avoid QoS violations and tackle the inter-VM performance interference, cloud providers typically adopt an *overprovisioning* strategy. That is, resources are assigned to each VM in excess to avoid possible performance degradation due to the inter-VM interference. When running latency-critical applications, system resources must be conservatively over-provisioned to ensure compliance with the SLA, as the performance of these workloads is very sensitive to the inter-VM interference. This workaround, however, results in poor utilization of the major resources of the cloud system. For instance, the average CPU utilization is typically far below 50% in cloud servers running latency-critical applications [35] and, in most cases, below 20% [36, 37].

The previous rationale means that an important concern for cloud providers is to reduce the overprovisioning costs of the system resources associated with the VM; in other

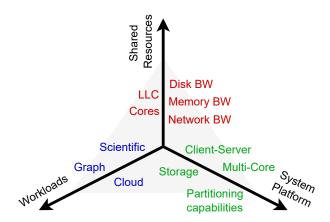

Figure 1.1: The three main axes of research covered in this thesis.

words, there is an interest in improving the resource efficiency to lower the cost of VMs. However, the public cloud imposes significant limitations to implementing a resource management approach. First, it should not have prior knowledge of the workloads running on the VMs (i.e., they should be treated as black boxes). Second, it should not require costly actions (e.g., isolating a VM). And third, it should be general enough to adapt to different workloads and system conditions.

### 1.3 Objectives of the Thesis

The overall objective of this thesis is to address the inter-application interference at the main system shared resources from two main perspectives: HPC and cloud computing. Within each scope of research, this objective spawns across three main axes. First, the target shared resource(s) to be studied are specified (e.g., the LLC). Then, the workloads to be run are selected (e.g., single-threaded scientific applications), considering the induced interference we intend to study (e.g., cache thrashing behavior). Finally, the system platform is selected depending on the workloads and the specific resource to be studied, and the workload characteristics. Below, we summarize the extent to which this thesis deals with these three axes:

**Shared Resources.** The main system shared resources addressed in this thesis vary depending on the scope (HPC or cloud) of the study. Regarding HPC, the study focuses on two major processor resources: the LLC and CPU cores. In the context of cloud computing, the main shared resources of the entire system (CPU cores, LLC, main memory bandwidth, disk bandwidth, and network bandwidth) are considered, as public cloud environments cannot obviate any resource.

**Workloads.** Depending on the scope and the resource to be studied, different benchmark suites are typically used. The manuscript starts by presenting resource management approaches aimed at HPC environments. In this context, we have used scientific single-threaded applications to study the LLC interference and graph parallel workloads to focus the research on core-allocation policies regulating thread-level parallelism (TLP).

However, the popularity and increase in computational load of cloud computing have caused resource sharing to be a concern for cloud providers. Therefore, this thesis evolves the work performed in HPC to cloud computing. In this domain, cloud latency-critical workloads are used to explore resource interference in cloud computing.

**System Platform.** The experimental setup is highly dependent on both the workload characteristics and target shared resource(s) chosen to be studied. To study resource partitioning in HPC, multi-core processors with resource partitioning tools are required. Two different processor architectures are considered in order to study interference at inclusive and non-inclusive LLCs. In the case of cloud computing, a more complex experimental platform is required with a client-server architecture, a storage node, and a system software stack to implement virtualization. For this purpose, we implement an experimental setup to perform cloud research. Also, the main memory storage capacity and the number of cores (and threads) can be critical elements depending on memory requirements and scalability features of mulithreaded applications.

#### 1.4 Main Contributions of the Thesis

This section summarizes the major contributions of this thesis, grouped according to the two main computing paradigms addressed in this dissertation.

#### 1.4.1. High-Performance Computing (HPC)

The research developed in HPC focuses on the resource management of the LLC (both inclusive and non-inclusive design) and the CPU cores.

- System TT and throughput improvement via LLC partitioning. This dissertation proposes LLC partitioning approaches that leverage Intel CAT to improve the performance of multi-program workloads by identifying and protecting the applications whose performance is more damaged by LLC sharing. Newly *problematic* LLC behaviors are identified, which can significantly drop the system performance if not properly dealt with. We also propose an LLC partitioning phase-driven approach that dynamically adjust the partitioning according to changes in the LLC behavior that applications experience during their execution.

- Containing cache pollution by partitioning of non-inclusive LLC. Current server processors have redistributed the cache hierarchy space over previous generations, making the LLC smaller but designed as non-inclusive to reduce the number of replicated blocks. Cache management in this organization becomes more critical than in inclusive caches. To address the harmful effect known as LLC pollution, we propose Cache-Poll partitioning policy that, based on the *polluting* behavior and the cache requirements of the co-running applications, distributes the LLC space at run-time among applications. Cache-Poll exploits the non-inclusive LLC design by leaving little room for cache-insensitive and polluting applications.

• Spatial core-allocation varying TLP transparently. The default Linux scheduler, which adopts a time-sharing policy to provide a fair scheduler, performs poorly when multiple graph applications share a system. To deal with this issue, we propose AFAIR, a core-allocation policy that dynamically adjusts the number of cores assigned to each graph application based on the shared-memory resource that bottlenecks the processor performance. AFAIR adapts the number of threads spawned by the running applications dynamically without modifying the applications' source code.

#### 1.4.2. Cloud Computing

The work carried out in this thesis on cloud computing is focused on analyzing how the performance of VMs is affected by the consumption of the main system resources considering a public cloud environment. In addition, we outline specific hints cloud providers should take into account to improve the system performance and resource utilization.

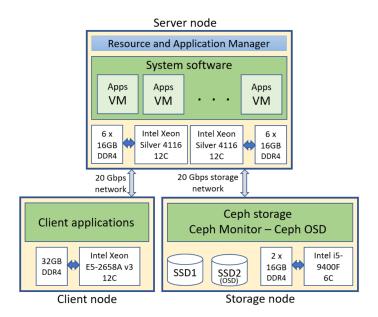

- Experimental platform to carry out controlled cloud research. To perform cloud research, a small experimental platform is commonly used, which hides the huge system complexity and provides flexibility. Most platforms used in existing work do not include all cloud components or lack the deployment of VMs to provide isolation. To comply with all the main features of cloud production systems, we present Stratus, an experimental platform used to carry out the cloud research presented in this dissertation. Stratus uses VMs to isolate tenant applications, deploys the three types of cloud nodes (server, client, and storage), and manages all main shared system resources (cores, LLC space, memory, network, and disk bandwidth).

- Characterization of cloud latency-critical workloads. Understanding how performance is affected by the consumption of the main system resources is a major concern for cloud providers in order to devise virtualization strategies that improve system efficiency. For this aim, a set of representative latency-critical applications are characterized, revealing that the performance of some applications does not scale with the number of threads, and the performance of some others is insensitive to the Hyper-Threading technology. To identify these applications at run-time, the utilization trend of the major system resources is analyzed. In addition to CPU, we have also studied how assigning the share of other major shared system resources to each application impacts on performance.

- Detecting and estimating QoS degradation in the public cloud. To prevent QoS violations, cloud providers adopt overprovisioning strategies, but they reduce server utilization and increase operational costs. A mechanism that accurately estimates performance degradation dynamically in a production system would allow cloud providers to improve the servers' utilization. This thesis proposes Cloud White, an approach that is able to detect the inter-VM interference in scenarios with multiple co-located latency-critical VMs and estimate the performance degradation using multi-variable regression models. Unlike previous proposals, Cloud White esti-

mates performance in terms of tail latency and considers the limitations of a public cloud production system.

#### 1.5 Thesis Outline

The remainder of this thesis is organized into eight chapters. Chapter 2 discusses the related work and state-of-the-art approaches. Chapter 3 presents the experimental setup designed to carry out the experiments presented in this thesis. The rest of the chapters are grouped into two main blocks according to the scope of the research.

Regarding the research performed on HPC, Chapters 4 and 5 study the interference at the LLC and propose cache partitioning approaches for inclusive and non-inclusive LLC, respectively. Chapter 6 focuses on cores resource management, presenting a core-allocation policy to improve the co-location performance of graph workloads.

With respect to the work performed on cloud computing, Chapter 7 analyzes the behavior of cloud workloads from a performance and resource-consumption perspective, considering the scalability, load, thread-allocation, and inter-VM interference. Chapter 8 proposes a dynamic approach to detect inter-VM interference and estimate the resulting QoS degradation.

Finally, Chapter 9 summarizes the main contributions of this thesis, discusses future work, and lists the related publications.

# State of the Art

This chapter describes relevant previous work on the topics covered in this dissertation. First, the relevant work on resource management is introduced, analyzing approaches that target HPC and Cloud Computing. Second, works analyzing the performance of emerging workloads are revised. Finally, we discuss key state-of-the-art approaches proposed to detect and estimate performance degradation in cloud production systems.

### 2.1 Resource Management Approaches

#### 2.1.1. Last Level Cache (LLC)

The first approaches dealing with cache partitioning were implemented using simulation frameworks. Some approaches like UCP [38], ASM [39], Vantage [40], PriSM [41] need to modify the eviction and insertion policies to partition the cache; hence they cannot be implemented in existing processors. Other approaches, like the filter cache [42] and ROCA [43], split the cache into different structures to reduce interference.

An alternative approach has been to perform cache partitioning using software tools. Many are based on *page-coloring*, a mechanism that allows controlling which cache sets are assigned to the application data. Among them, an interesting proposal is the work by Liu et al. [44], which proposes a multi-policy memory allocation approach, profiling at run-time the slowdown obtained by applications when the cache space is reduced and selecting the best partitioning policy (horizontal partitioning, vertical partitioning or randomized page interleaving policy) based on this characterization. Park et al. [45] profile applications' cache behavior at page level to assess the page reusability. Then, the LLC is divided into two partitions to place low and high reusability pages together.

Recently, the research trend has changed as some recent processors from distinct vendors provide support to partition the cache [10, 8, 9], so nowadays, the main focus is on implementing cache partitioning policies in commercial processors.

#### **Inclusive Caches**

The works focusing on inclusive L3 caches aim to distribute a high number of cache ways, 20 or more in most processors, among the co-running applications. They mainly differ in the type of the applications (e.g., latency-critical, best-effort, or high-priority) co-running in the processor, which receive different treatment according to the aim of the approach (e.g., quality of service of latency-critical, fairness, or turnaround time). These works can be split into two main groups depending on whether they concentrate on HPC or cloud workloads. Below these groups are discussed.

In the context of HPC, Selfa et al. [1] cluster applications using the k-means algorithm and distribute cache ways between the groups, giving exponentially more space to the applications whose performance suffer more from the interference at the LLC to improve system fairness. El-Sayed et al. [46] also group applications into clusters, assigning them to different CLOS. While it significantly improves throughput in selected workloads, it uses detailed profiling, making KPart a more complex solution than those proposed in this thesis. Similarly, DICER [47] uses a similar profiling to perform cache partitioning where high-priority and best-effort applications are executed together. DCAPS [48] proposes a framework based on predictors that use miss rate curves and LLC occupancy predictions. This approach estimates the LLC occupancy from the number of misses incurred, which can lead to wrong conclusions since some applications present a low number of LLC misses but a high number of memory accesses due to prefetches, resulting in a high LLC occupancy. Contrary to this work, we measure the effective LLC occupancy to identify anomalous LLC behaviors that can drop the performance of the co-runners. Sun et al. [49] propose combining cache partitioning with prefetch control to reduce prefetcher-caused inter-core interference. Authors designed the Coordinated Multi-resource Management (CMM) framework to detect prefetch-aggressive applications and allocate resources (prefetcher and cache space) accordingly.

In the context of cloud computing, research works [50, 31, 51] have been published dealing with multiple hardware and software resource management mechanisms (among them, cache partitioning) for cloud systems. These systems present workloads with particular characteristics, like latency-critical applications, where the quality of service (QoS) must be satisfied, which run jointly with best-effort applications to improve resource utilization. Multiple resources are tuned simultaneously (e.g., the number of cache ways and cores) to meet QoS requirements. While Heracles [50] only considers a single latency-critical application placed in a private partition, Parties [31] can manage multiple latency-critical applications. In [51] Funaro et al. use a marked-driven auction system to partition the LLC into isolated partitions. In this way, each guest can bid based on the number of resources it wants to use.

#### **Non-Inclusive Caches**

Non-inclusive L3 caches (i.e., LLC) are the newest design trend; therefore, the most recent works have been performed in processors with non-inclusive LLCs.

Some approaches are designed for scientific workloads, targeting system throughput and fairness. POCAT [52] uses Intel Top-down Microarchitecture Analysis Method (TMAM), leveraging machine learning to predict applications' IPC for different cache sizes. This model also captures changes in the IPC behavior. However, it requires using a machine learning dataset created by previously collecting TMAM metrics and IPC values of each application for each cache way setting. Xiao et al. [53] identify prefetching sensitive applications to drive cache partitioning using an online profiling phase. Each prefetchingsensitive application is assigned a single private cache way, and prefetching-insensitive applications share the remaining cache ways. Park et al. [54] focus on workload consolidation of commodity servers. Both memory bandwidth and the L3 cache are studied and partitioned together. However, the focus is on improving system fairness rather than system performance. Saez et al. [55] propose LFOC+, a cache-clustering policy that uses dynamic profiling to classify applications. Like [54], LFOC+ targets system fairness. Chatterjee et al. [56] use compiler-generated information to collect information about the memory footprint, cache sensitivity, reuse behavior, and phase timing to estimate the applications' memory requirements. With this information, they propose a proactive cache partitioning scheme that dynamically partitions the cache and schedules processes.

Most current data centers include processors with non-inclusive LLCs; thus, the latest research in resource management in cloud computing has focused on these processors. CLITE [30] propose multi-resource partitioning. It explores a model-learned relationship between job performance and the assigned resource shares (number of cores, LLC ways, memory bandwidth, memory capacity, disk bandwidth, and/or network bandwidth) using Bayesian Optimization. Alita [29] proposes eliminating interference by throttling resource polluters. Regarding the LLC, Alita isolates LLC polluters in one or few cache ways, avoiding cache thrashing and disturbing VM's with *normal* behavior, which share all LLC space. Themis [57] manages memory subsystem resources to provide fair resource sharing while meeting QoS requirements of latency-critical applications. It clusters VMs with similar memory bandwidth consumption to the same CLOS and configures the number of LLC ways and memory bandwidth throttling value accordingly.

#### 2.1.2. Cores

Recent works have proposed core allocation strategies to mitigate resource contention in multi-core processors.

Kundan et al. [58] characterize the pressure that applications inflict on both LLC and memory bandwidth to schedule applications to the processor cores, prioritizing those applications that made the least progress. However, offline information (IPC of the application alone) is required to estimate the progress. In addition, Hyper-Threading is disabled.

Some works have exploited the fact that current parallel application runtimes (e.g., OMP and MPI) support changing the number of spawned threads dynamically to improve resource efficiency and system throughput. Galante et al. [59] have surveyed the approaches proposed in this area in different memory architectures (shared and distributed)

and computing environments (cloud and fog). In [60], authors propose a dynamic resizing of malleable parallel applications scheduler for distributed-memory clusters. The aim is to improve cluster utilization and job execution time. However, the code of applications must be changed to make them resizable. Yang et al. [61] present a specific solution for iterative workloads running on Apache Spark named iSpark. Iterative applications usually present initially a high CPU usage, which diminishes as the execution continues. Thus, the authors propose a provisioning approach that dynamically changes the number of allocated long-running processes (e.g., executors) to avoid resource wastage and handle under-utilization. SCALO [62] estimates scalability at runtime considering dynamic contention effects to control the threads allocated to each running OpenMP multithreaded application. Authors instrument OpenMP runtime to enable setting the degree of parallelism during the execution of parallel regions and allow communication with the SCALO daemon. TBFT [63] combines dynamic thread adjustment on OpenMP applications (without modifying or recompiling the code) with dynamic boosting mode tuning with the objective of optimizing EDP (energy-delay product). NuPoCo [64] aims to maximize system utilization while minimizing execution time by controlling the degree of parallelism of co-located parallel applications and scheduling them in NUMA multi-socket multi-core systems. The authors implement a dynamic loop scheduler in the OpenMP runtime system to provide dynamic spatial scheduling. A similar approach, MAPPER [65], focuses on ensuring QoS rather than maximizing system utilization. MAPPER may run without runtime modification (i.e., MAPPER applies only the scheduling part), but minor performance improvements are obtained.

In the context of scheduling, approaches have been proposed to optimize the execution of concurrent parallel application execution. Some works [22, 66] aim to improve performance by selecting the target number of threads (i.e., thread-level parallelism) each application should execute. Then, given a set of applications, the best scheduling order is decided based on this fact and the available hardware resources. These approaches, however, provide little flexibility as they require knowing the running applications before the execution starts and do not allow adapting the number of spawned threads dynamically. PredG [67] uses machine learning to select the best thread and data mapping policies to run graph applications on a NUMA system. Both approaches require knowing application-level information, such as the input graphs for decision-making.

## 2.2 Emerging Workloads in Server Processors

#### 2.2.1. Graph Workloads

Much research on graph applications has focused on proposing new hardware [68, 69, 70, 71] or the use of accelerators [72, 73, 74, 75] for optimizing graph processing performance. However, these solutions are not currently available in data centers. Therefore, commodity servers (i.e., general-purpose processors) are the popular choice to execute graph workloads.

Some previous works have characterized the performance of graph applications both under simulators and on real processors to guide future hardware design optimizations for graph processing. Most works [76, 71, 77, 78] focus on the memory subsystem's impact on graph applications. The main conclusions of these works are the following: i) good performance scalability is obtained with increasing numbers of cores [77, 76]; ii) graph applications are memory-latency bound since they do not fully utilize the memory bandwidth [76, 77, 78]; iii) graph applications do show some locality [76, 78] and can benefit from caching, being performance more sensitive to the LLC (L3 cache) space than to the L2 cache [71]; iv) SMT introduces modest performance improvements [78, 76].

Other works focus the study on specific domains, such as the impact of branch prediction on performance [79, 80], hardware prefetchers [81, 76], architectural enhancements, and software optimizations [82] and energy efficiency [83].

#### 2.2.2. Cloud Workloads

Due to the nature and fast evolution of the public cloud and related industry concerns, many research works have been proposed in the last few years. These studies apply a wide range of characterization methodologies that present significant differences regarding virtualization levels (e.g., VMs, containers, or no virtualization), performance metrics (e.g., execution time, throughput, or tail latency), target shared resources (e.g., LLC, main memory, etc.), and system configurations (e.g., SMT vs. no SMT, system specifications). In contrast to previous research works, in this thesis, we perform a comprehensive study including all the main shared resources (i.e., CPU, LLC, main memory, network, and disk); focusing on a realistic configuration for cloud providers with a full virtual machine-oriented system stack and SMT-enabled CPUs; and considering tail latency as a key metric to evaluate QoS from the tenant perspective.

The workload characterization performed in previous works is often leveraged to propose novel resource management approaches dealing with distinct shared resources that affect the behavior of these applications. These approaches significantly differ in whether the target workloads represent public cloud deployments. This is the case when the workload is implemented using virtual machines (VMs) running in full-stack system configurations. This section summarizes previous research taking into account this differentiation.

#### **Approaches Not Considering VMs**

In [54], Park et al. focus on the interference at the LLC and/or memory bandwidth, but they do not consider other major shared resources in the cloud environment like the network or the disk. This approach only characterizes each application's behavior according to the number of LLC misses and accesses per second. However, the system performance is not considered at all. Moreover, the approach mainly focuses on HPC workloads, and only a small section studies the behavior of scenarios where a single latency-critical application runs concurrently with other batch workloads.

Also, regarding memory bandwidth, in [84], the impact of Intel Memory Bandwidth Allocation (MBA) technology on performance is studied. MBA provides a relatively coarse interface to limit main memory bandwidth consumption. Therefore, this approach also studies complementary techniques such as thread packing [85] and clock modulation [86].

Jeatsa et al. [87] propose CASY, a cache allocation system for serverless functions in Function as a service (FaaS) platforms. CASY leverages machine learning models to predict the amount of cache to be assigned to each function based on the input data size.

In [88], each application is categorized considering four main aspects that affect performance: scale-up (amount of resources per server), scale-out (number of servers per workload), server configuration, and interference (symbiotic workloads). This categorization can be used to establish the right amount of resources allocated to an application to reach a given performance level while maximizing overall resource utilization (i.e., avoid over-provisioning). The resources considered are the number of compute cores, memory, and storage capacity. Unlike our work, neither LLC occupancy, main memory bandwidth, nor disk bandwidth are considered.

In [50], similarly to our work, Lo et al. characterize the impact of interference at shared resources on performance for different load levels; however, just three latency-critical Google workloads are characterized. To study the effect of interference, synthetic benchmarks stress each shared resource. Nevertheless, the interference at the disk is not analyzed. In contrast, Parties [31] considers disk interference, analyzing six latency-critical applications. However, Parties, as some of the works mentioned above, studies applications running in Linux containers, which are more light-weighted than full VMs. Thus, the studied workloads are not representative of a significant amount of public cloud deployments.

#### Full System Stack Approaches with VM Support

In [89], a mix of batch (Hadoop running over Mahout and Spark jobs) and latency-critical applications (memcached jobs) are studied in three representative workload scenarios (minimum, medium, and high load variability). This study focuses on finding the optimal mapping of applications, in terms of the number of virtual CPUs, to reserved and on-demand VM instances. Therefore, there is no insight into the exact resources (e.g., cache, disk bandwidth) that affect the jobs' execution time.

To determine the best VM to physical core mapping, in [90], VMs are classified as compute or memory intensive, considering readings from several performance counters. In particular, only three performance events (L2 cache misses, L1 cache misses, and committed instructions) are used to classify applications. The focus is on best-effort scenarios, and the evaluated workloads are four-application mixes composed of SPEC CPU2006 benchmarks, which are scheduled in pairs to the processor cores.

Finally, DeepDive [91] pursues to identify interference between VMs in Infrastructure as a service (IaaS) clouds. Deepdive uses about a dozen low-level metrics (including per-

formance events acting at the L2 cache as the LLC in the system, the iostat and netstat tools, and available hypervisor -VM- statistics) to find out if interference is introduced as well as what is the main shared resource where interference rises. Nevertheless, Deep-Dive lacks important performance events, which are present in modern processors, and partitioning mechanisms (i.e., Intel CAT and MBA) dealing with shared resources like the LLC and the main memory bandwidth. The analysis introduces unexpected metrics, like using the private L1 cache misses, mainly because the L2 is the LLC. In modern processors, the latency of most L1 cache misses is hidden by the out-of-order mechanisms. Experiments use three cloud and latency-critical (web search) workloads.

### 2.3 Interference in Cloud Systems

#### 2.3.1. Interference Detection Based on Simple Measurements

There is extensive literature on detecting interference due to co-located jobs or resource sharing. Many approaches [92, 31, 93, 88], however, monitor QoS (e.g., in terms of average latency or queries per second), which cloud providers cannot carry out in real production systems since VMs should be handled as black boxes.

Recent approaches [32, 29] have tried to detect inter-VM interference while complying with public cloud limitations. In [32], Javadi et al. propose Scavenger, a resource manager that considers tenant workloads as black boxes and identifies performance interference by monitoring the usage of a subset of the major system resources (memory, network, LLC, and CPU) consumed by the VM. Chen et al. propose Alita [29], which identifies contention online considering a different subset of the system resources (memory bus, LLC, and power supply) based on low-level metrics but omitting important shared resources like disk and network. These approaches present two main shortcomings. On the one hand, the performance interference is detected in a subset of the system resources. On the other hand, no prediction is made on how performance interference impacts on the QoS of VMs.

#### 2.3.2. Performance Interference Prediction Models

Prior works have proposed models to estimate the impact on performance caused by the interference (e.g., introduced by co-runners or limited resources) in distinct environments or from different perspectives. In [94], online prediction models are built from a user-level perspective. Microbenchmarks are run to estimate resource contention at the shared resources, and then application-specific models are used to estimate its impact on performance. Instead, this document focuses on the cloud provider's point of view, and therefore, we assume no knowledge of the application running within each VM.

Another important piece of research [95, 96, 33, 91] has focused on predicting the performance interference that background applications introduce when co-located with latency-critical applications. Other works like [97] focus on the co-location of HPC applications.

All of these works [95, 96, 33, 97] access to data about the performance of individual applications, which is not accessible by cloud providers, making these approaches not practical in real production systems.

DeepDive [91] detects performance interference based on the aggregated resource system utilization of VMs by monitoring low-level metrics. Nevertheless, an important weakness of DeepDive is the *isolation-based methodology* used to quantify interference in VMs, which is prohibitive in public cloud environments. Resource Central [36], based on that certain VMs show consistent behaviors over multiple lifetimes, learns offline from past behaviors to predict the future online behavior of the customer's VM. This approach predicts high-level metrics like CPU utilization, cores, memory, or workload class. To this end, it uses machine-learning methods (e.g., random forest) to output buckets instead of predicting a single number through regression models.

Some approaches [98, 99, 30] use prediction models to estimate the resulting performance when modifying a given resource configuration. Rusty [98] leverages neural networks to make resource and energy consumption predictions, but performance is quantified in terms of IPC and not tail latency. Twig [99] uses performance counters to estimate the QoS that results from different dynamic voltage and frequency scaling (DVFS) and core combinations. CLITE [30] elaborates prediction models to search for near-optimal resource partitioning. However, both Twig and CLITE require monitoring the performance (e.g., latency) of the executing applications at run-time, thus not considering VMs as black boxes. In addition, performance degradation due to the interference is continuously being estimated instead of only when detected.

# **Experimental Framework**

This chapter describes the experimental framework used to conduct the experiments presented in this thesis.

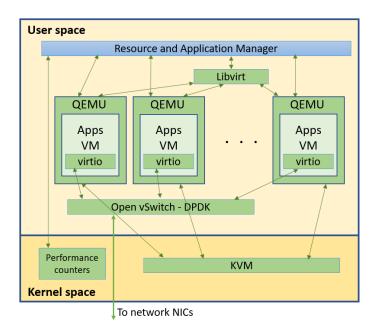

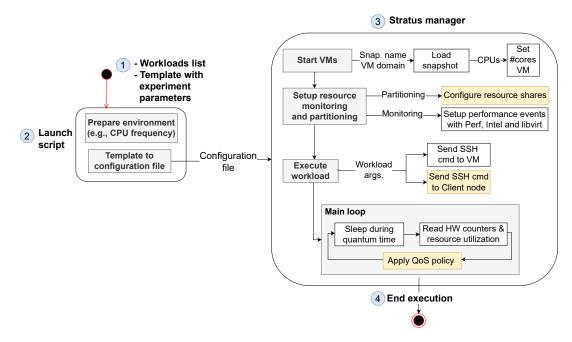

First, the experimental platforms are presented. Two Intel multi-core processors have been used to carry out the work on HPC, each from a different microarchitecture. Regarding Cloud Computing, we have deployed an experimental platform (Stratus) to perform controlled cloud research, focusing on intra-node interference.

Then, we present the Resource and Application Manager developed to automate the execution of experiments carried out in this thesis, as well as monitor and partition the system-shared resources. This manager has been used both in the work conducted in HPC and Cloud Computing.

Finally, this chapter describes the benchmark suites used.

## 3.1 Experimental Platforms

Two main Intel multi-core processors have been used to obtain the experimental results of the work performed in this thesis.

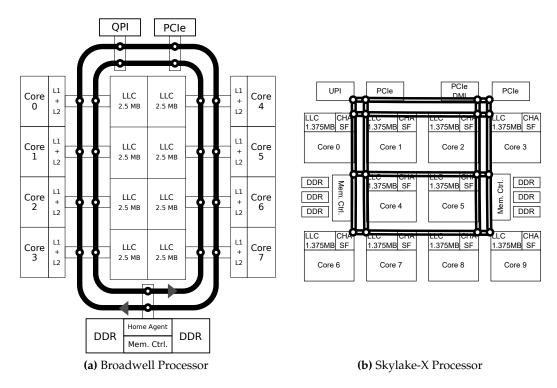

- Intel Broadwell Processor. The work performed in inclusive LLC (Chapter 4) has been carried out in an Intel Xeon E5-2620 v4 processor, which features eight cores supporting Hyper-Threading. This processor implements a three-level cache hierarchy, with a 20-way 20MB (1MB /way) LLC. Regarding main memory, it has two 16GB memory channels, making a total DRAM capacity of 32GB. It supports the Intel Resource Directory Technologies (RDT) and includes up to sixteen Classes of Service or CLOS (see Section 3.3.1).

- Intel Skylake-X Processor. The research carried out in non-inclusive LLC (Chapter 5) and in the server node in the cloud computing part of this thesis (Chapters 7 and 8) has been performed in a 12-core Intel Xeon Silver 4116 processor running at

**Figure 3.1:** Block diagram of the Intel Xeon Broadwell and Skylake processors with low core count (LCC SoC) to illustrate the differences among both microarchitectures.

2.1GHz. Each core has a 1-MB private L2 cache, and all cores share a 16.5MB 11-way (1.5MB/way) non-inclusive L3 cache. This processor supports also supports Intel Resource Directory Technologies (RDT), but the maximum number of supported CLOS is 8. The machine has six main memory channels, holding each 16GB, which amounts to a 96GB (6x16GB) DRAM. It supports a maximum bandwidth of 58 GB/s.

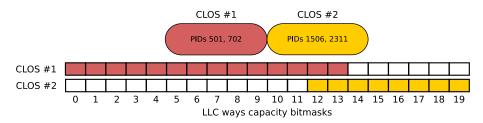

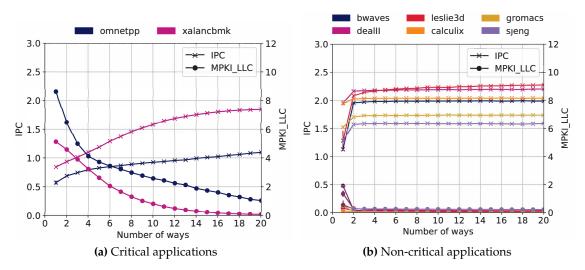

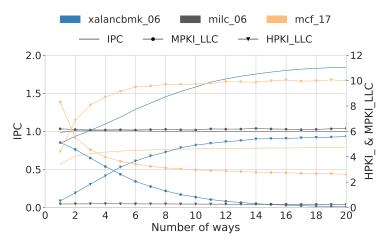

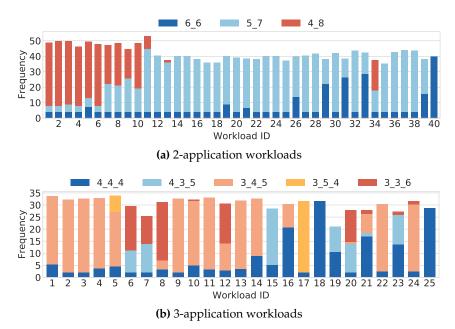

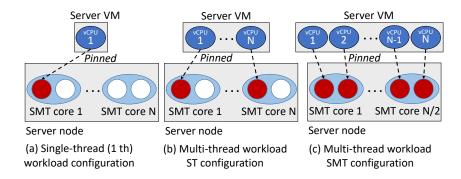

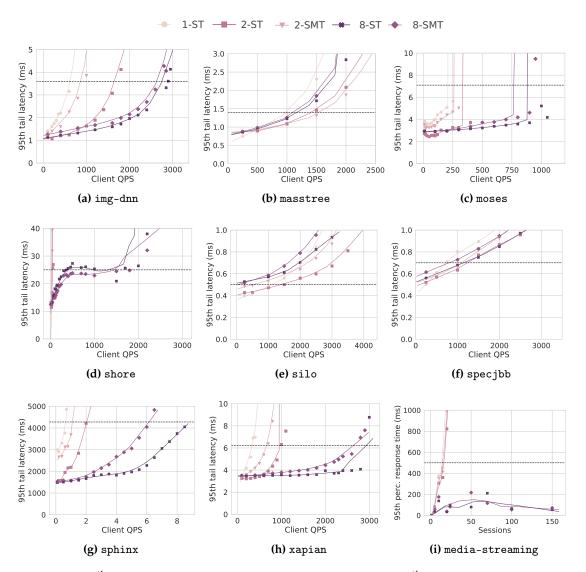

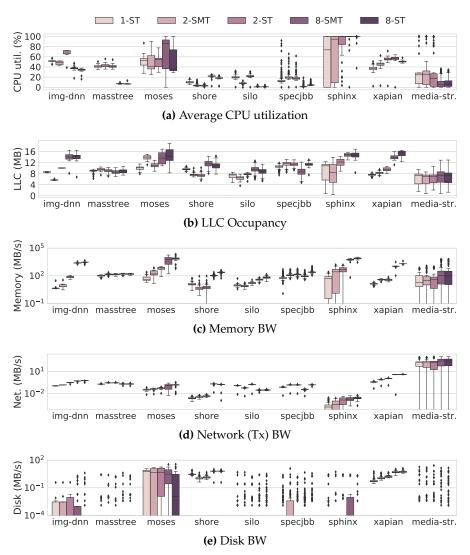

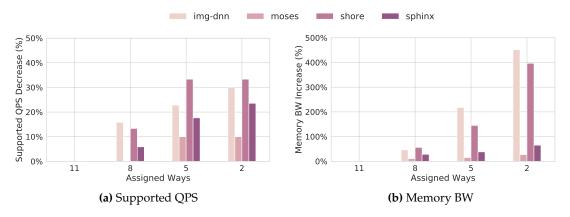

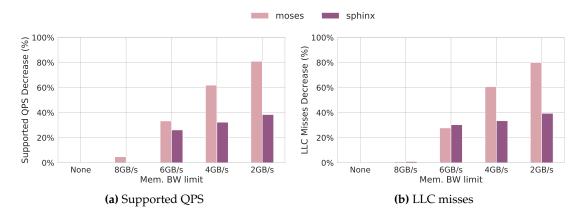

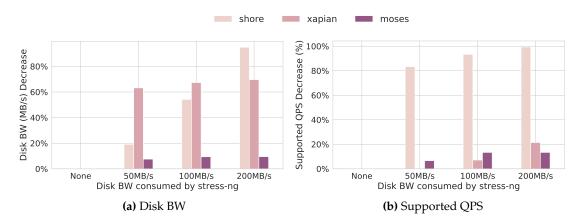

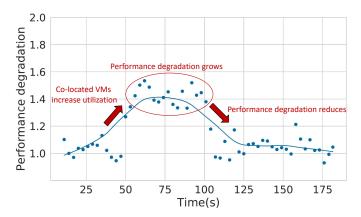

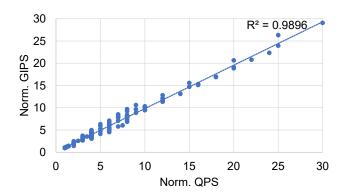

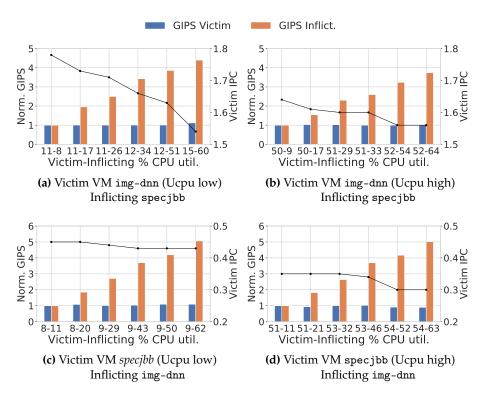

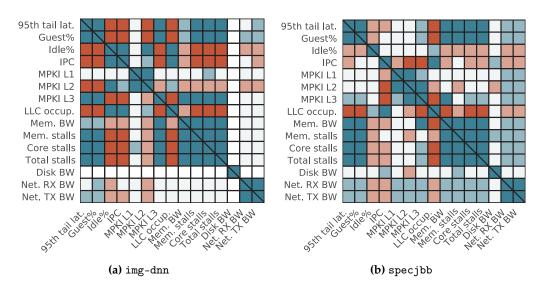

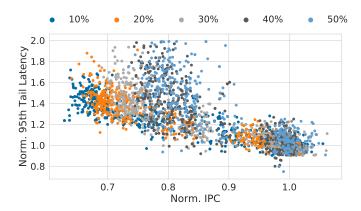

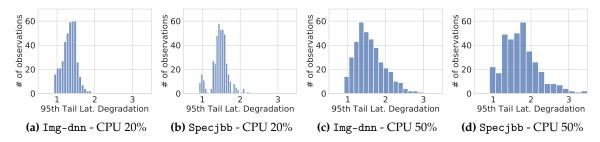

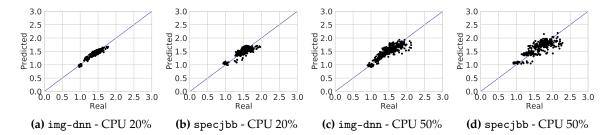

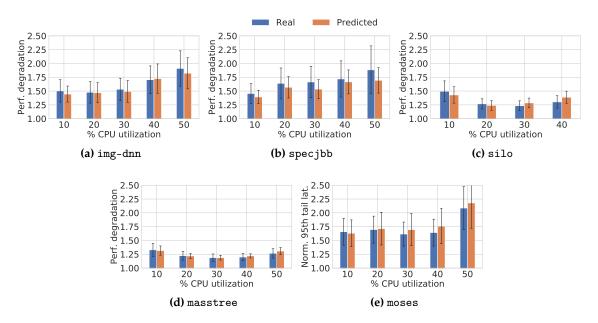

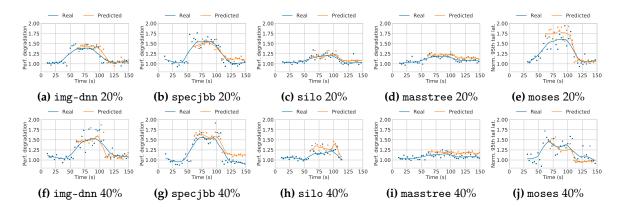

Figure 3.1 shows a block diagram of the memory and the cores of both the Intel Broadwell and Skylake-X processors. The Skylake-X architecture belongs to the Intel Xeon Scalable processors, which marks a new era in the Xeon processors segments as it includes many enhancements [100, 101].