## Architecture And Algorithms For The Implementation Of Digital Wireless Receivers In FPGA And ASIC: ISDB-T And DVB-S2 Cases

### UNIVERSITAT Politècnica de València

EDUARDO RODRIGUES DE LIMA DEPARTAMENTO DE COMUNICACIONES

Thesis Directors

VICENÇ Almenar Terré Santiago Flores Asenjo

January 2016

#### $\operatorname{ITHAKA}^1$

As you set out for Ithaka hope the voyage is a long one, full of adventure, full of discovery. Laistrygonians and Cyclops, angry Poseidon - don't be afraid of them: you'll never find things like that on your way as long as you keep your thoughts raised high, as long as a rare excitement stirs your spirit and your body. Laistrygonians and Cyclops, wild Poseidon - you won't encounter them unless you bring them along inside your soul, unless your soul sets them up in front of you.

Hope the voyage is a long one. May there be many a summer morning when, with what pleasure, what joy, you come into harbors seen for the first time; may you stop at Phoenician trading stations to buy fine things, mother of pearl and coral, amber and ebony, sensual perfume of every kind as many sensual perfumes as you can; and may you visit many Egyptian cities to gather stores of knowledge from their scholars.

KEEP ITHAKA ALWAYS IN YOUR MIND. ARRIVING THERE IS WHAT YOU ARE DESTINED FOR. BUT DO NOT HURRY THE JOURNEY AT ALL. BETTER IF IT LASTS FOR YEARS, SO YOU ARE OLD BY THE TIME YOU REACH THE ISLAND, WEALTHY WITH ALL YOU HAVE GAINED ON THE WAY, NOT EXPECTING ITHAKA TO MAKE YOU RICH.

Ithaka gave you the marvelous journey. Without her you would not have set out. She has nothing left to give you now.

And if you find her poor, Ithaka won't have fooled you. Wise as you will have become, so full of experience, you will have understood by then what these Ithakas mean.

CONSTANTINE P. CAVAFY(1863-1933)

<sup>&</sup>lt;sup>1</sup>Translated by Edmund Keeley/Philip Sherrard

What is now proved was once only imagined. William Blake(1757-1827)

IN THE MEMORY OF MY FATHER, FERNANDO TO MY MOTHER, ELIETE TO MY WIFE, CELIA TO MY BABY, HENRIQUE

## Acknowledgements

This has been a very long journey, full of discoveries. At this point, besides I have figured out new techniques, written several papers as well as my thesis, and the viva *voce* defense is approaching. I realized that I have had the opportunity to figure out new cultures, new countries (even nations within countries) and new languages. For sure, the pressure of pursuing a PhD in such a scenario has significantly changed the way I see the things and the World, which became smaller. Those who know me personally can see that. Nevertheless, none of that would make sense without the people I have found along the way. Now, they are part of my personal history. Indeed I have made a lot of good friends and colleagues that at this moment are spread all over the world, settling them own ways to Ithaka. During this journey I've meet a lot of characters that inspired me and contributed in some way to help me going further. Some of them helped me in technical aspects, other helped me to support the long time far away from my family and Brazilian friends, during part of this journey that was performed in Europe. But all of them, even without realizing that, helped me to grow as a human been. Having said that, it is time to thank. So, the minimum I must do is to express my deepest gratitude to everyone which was involved in this process.

First of all I would like to say thanks to my thesis directors Prof. Vicenç Almenar Terré for all support, opportunities and patience during all these years, as well as for the excellent reviews on my thesis, and the elegant Professor Santiago Flores Asenjo, especially for opening the UPV doors to me and to introduce me to COST273 Cooperation Group which gave access and closeness to inspiring people like Prof. Luis Correa, Prof. Alister Burr, Prof. Mischa Dohler, Prof. Ernst Bonek, Dr. Reinaldo Valenzuela, Prof. Alan Sibile, Prof. Roberto Verdone, Prof. Luc Vandendorpe, Prof. Emmanuel Van Lil, Prof. Andreas Molish, Dr. Robert Bultitude, Dr. Tricia Willink, and many other bright minds in the telecommunications community.

Despite Professor Javier Valls Coquillat from UPV was not my formal adviser, I consider him as so. As such, I owe him a special thanks for introducing me to the FPGA world and to the wireless communications implementations aspects in FPGA. Thanks for the long conversation during the SPL2010, in São Carlos , Brazil. That

talk gave me the necessary strength and courage to go ahead. I will also always remember the Fideuá you cooked for our research team, at Playa de Xeraco. Definitely, you are a great guy.

I would like to thank the members of my thesis reviewing committee, for have found time in them busy agenda to evaluate my work in a timely manner: Prof. Vicente Baena Lecuyer from the Electronics Engineering Department, of the Universidad de Sevilla - my thesis is strongly related to his research field - and Prof. Rodolfo Jardim Azevedo from the Computing Institute of the Universidade Estadual de Campinas, which introduced me to the Brazil-IP and CI-Brasil Program, so in short, without have met him, this thesis would be quite different.

On my thesis evaluation committee, I first thank the busy Prof. Alberto Gonzalez Salvador for being so kind and accept to be the president of the Jury. He is an example to follow and still keeps inspiring me. When I do some research I always remember the first time I went to his office and I asked his opinion about a theoretical idea on Joint Probability and Mutual Information to be used in Frequency Diversity in OFDM, and he asked me: "does it have any practical application?". That question says a lot about him. Next, Prof. Antonio Garcia Rios from the Electronics and Computers Technology Department at Universidad de Granada, which gently accepted to be the Secretary of my thesis Jury, and who certainly will significantly contribute for improving my work due to his large experience on the implementation of Digital Signal Processing in FPGA and VLSI. For last but not least, I give a special thanks to Prof. Hercules Pereira Neves, from Uppsala Universitet and United Semiconductors. As one of the Brazilians who gave his contributions for past and current attempts, to make Brazil a player in the international semiconductor industry, he has advised me and gave me an unique perspective, as someone who is working in this area for a long time. In this way, he helped me to figure out how I could contribute for the current Brazilian attempt. Thanks also for being part of my reviewing committee.

Prof. Maria José Canet and Dr. Fabian Angarita you are great guys! Thank you for always being there during my staying in Gandia, to give me support, for the friendship, and an especial thanks for the remote support when I came back Brazil. I also thanks José Miguel and Kleber Iguchi for the friendship and for sharing good times in València. Other members of UPV that I'm in debt are Prof. Narcis Cardona, Prof. Trini Sansaloni, Prof. Asunción Perez-Pascual, Prof. Vicente Torres, Prof. Amparo Girona, Prof. José Marin-Roig, Prof. Gema Piñero, Prof. Juan Reig Pascal, Prof. Juan L. Corral, Prof. José F. Alarcón, Prof. Raul Bosch, Prof. Francisco Castells, Prof. José Javier López, Prof. Luis Vergara, Prof. José Capmany, Prof. Vicente Casares, Prof. Luis Guijarro and Prof. Marta Cabedo. I'm also in debt with Prof. Eduardo Boemo and Prof. Gustavo Sutter from Universidad Autônoma de Madrid, as well as Prof. Elias Todorovich from UNICEN, Argentina.

While pursuing my doctoral degree, I had the pleasure to be accepted as international scholar at Katholieke Universiteit Leuven and performed research at IMEC, in Leuven-Belgium. There I rediscovered the passionate Microelectronics world, that was introduced me by Prof. Nobuo Oki during the Electrical Engineering undergraduate course at UNESP in Ilha Solteira, and I was introduced to Nanoelectronics. During my research period at IMEC, I have also confirmed that top level research can live in peace with practical applications. There, I have met several smart and kind persons. I know that part of you are no longer at IMEC but you will always be my IMEC connection. Thank you all to propitiate such a good time in Belgium: Dr. Liesbet V. der Peere, Dr. Frederik Petre, Dr. David Novo, Carolina Blanch, Cinzia De Marco, Dr. Francesca Barbagini, Dr. Vitto Giannini, Dr. Yann Joncour, Adrian Sarbu ,Steve Stoffels, Daniel Aguado, Salvador Eslava, Enrico Tenaglia, Olalla Varela, Suevia Rodriguez, Concepción Sanz, Dr. Francesca Clemente, Lühn Ole, Thomas Schuster, Hans Cappelle, Roeland Vandebriel, Dr. Mustafa Badaroglu, Dr. Jimmy Nsenga, Dr. Claude Desset, and Eduardo Estraviz. A special thanks to Prof. David Gesbert, from EURECOM, that introduced me to Dr. Frederick Petré that opened the DESICS/IMEC doors for me.

A special thanks to the other two members of my Brazilian connection that I had the pleasure to meet at IMEC: Dr. Augusto Redolfi and Dr. Guilherme Lujan . Together, we laugh a lot during the lunch time, chatting (a lot) often about an infinity of subjects and of course about micro and nanoelectronics and the future of microelectronics in Brazil.

I would like to thanks Prof. Guido Araújo from Computing Institute at UNI-CAMP and Prof. Edna Barros from LINCS/CETENE/UFPE for introducing me to the Brazil-IP and CI-Brasil Program. I salute you for the effort you have done for the success of microelectronics in Brazil. Thanks to my former colleagues at UNI-CAMP: Prof. Romis Attux, Tarciano Pegoraro, Prof. Ricardo Suyama. You inspired me to start my doctorate. I also thanks Prof. João Marcos Romano from DE-COM/UNICAMP, because it was during his classes that I started thinking seriously on pursuing a PhD.

Many, many thanks to my former colleagues at Idea! Electronic Systems, that worked hard in the DTV01 project, and strongly contributed and some of them still contribute for the attempt to bring Brazil to the international scenario of the semiconductor industry, as a reliable silicon design provider. Together we had good times, we did great things and even given the limited resources, we did our best. You guys must be proud of it: Valdiney Pimenta, Gabriel Teles, Tiago Barros, Pedro Paro, Tomaz Vilela, Mauricio Suguiy, Jefferson Capovilla, Marcelo Guedes, Roberto Barbosa, Roberto Borgognoni, Aleksey Covacevice, Rafael Madeira, Tiago Lyrio, Agknaton Bottenberg, Alexandre Santiago, Davi Castro, Thiago Crespo, Leandro Gontijo, Flavio Silva, Denis Fantinato, Felipe Torrezan, Daniela Corsi and Frederico Gonalves. Thank you also, Samuel Goto and Felipe Renon.

A special thanks to the enthusiastic, energetic and busy José Eduardo Bertuzzo from Instituto de Pesquisas Eldorado for all his support during the ISDB-T and DVB-S2 receivers projects, and for the personal and professional engagement in the microelectronics projects. Thank Rodrigo Sales to always, when possible, answer my requests for equipments and budget for travels and conferences, as well as for sharing some Friday evening with me, Renato Nascimento and Haroldo Onisto, in get togethers (of course before I get started writing my thesis).

Eu quero agadecer especialmente à minha me Eliete, aos meus irmãos José Carlos, Waldisia, Walmir e Waldir, s minhas cunhadas, aos meus sobrinhos Luciana, Felipe e Fernando, pelo apoio e torcida durante todos estes anos. No decorrer desta tese novos sobrinhos nasceram e fizeram parte desta jornada mais alegre e agitada: minha afilhada Gabrieli, Ana Clara, Alexsander, Daniel, Lucas e Ana Julia.

A very special thank to my team at Instituto de Pesquisas Eldorado that worked on the DVB-S2 project: Augusto Queiroz, Gabriel Silva, Denise Alves, Cesar Chaves, André Sapper, João Tardelli, as well as the others members of my team: Maique Correa, Daniel Urdaneta, Tiago Diadami, Vanessa Brischi, Jssica Oliveira and José Arnaldo. I also thank Prof. Marcelo Fernandes from UFRN for the support during the DVB-S2 project, specially on Adaptive Equalization issues. I also thank to the former DVB-S2 mattes Felipe Erazo, Gerson Brito and Marcos Matias.

My sincere thank to my colleagues at Eldorado that took part in the ISDB-T receiver project (DTV01): Fernando Idalirio, Ricardo Yoshioka, Marcelo Jara (former Idea! and Eldorado), Ciro Carvalho, Hamilton Costa, Jeroen Veremereen, Victor Boni, Fernando Martines, Jackeline Mertes, Tiago Merlo, Pedro Mietto, Murillo Fraguas, Erasmo Chiappetta, Sergio Rueda, Jairo Arguello, Tiago Rubia, Flávia Costa and the former Eldorado colleagues: Rodolfo Quarto, Honório Gomes and Fábio Ribas. My sincere thanks also goes to the Perceptia Devices Inc. colleagues: Andy Growstra and Tim Robins.

Thank you Eduardo Catto to be so nice and accepted to review the English language of part of my thesis, on such a short notice.

I also would like to thank the entities that granted me scholarships during my PhD studies or had funded the projects presented in this thesis in certain way: Instituto de Pesquisas Eldorado, Idea! Electronics Systems, Brazilian Ministry of Science, Technology and Innovation (MCTI), CNPq, CI-Brasil Program, Brasil-IP, FINEP/SIBRATEC and Generalitat Valenciana.

Last but certainly not least, my most heartfelt thank to my loved wife Célia - she knows my best side and tolerate my worst, we share plans, dreams and nightmares and to the sunshine of our lives, our little Henrique, who brought joy into our lives.

Eduardo Rodrigues de Lima

Campinas, December 2015.

## Abstract

The first generation of Terrestrial Digital Television(DTV) has been in service for over a decade. In 2013, several countries have already completed the transition from Analog to Digital TV Broadcasting, most of which in Europe. In South America, after several studies and trials, Brazil adopted the Japanese standard with some innovations. It was the first country to commercially broadcast Digital Television in the region, in 2007. Nevertheless, in 2013 the country still had not completed the transition to Digital.

Japan and Brazil started Digital Terrestrial Television Broadcasting (DTTB) services in December 2003 and December 2007 respectively, using Integrated Services Digital Broadcasting - Terrestrial (ISDB-T), also known as ARIB STD-B31 [1]. ISDB-T was clearly inspired on DVB-T [2], the first generation of European Terrestrial Digital Television Broadcast standard. Nevertheless, it overcomes one of the weaknesses of DVB-T, i.e. the bad performance under impulsive noise. DVB-T and ISDB-T make use of Orthogonal Frequency Division Multiplex (OFDM) as a Transmission Technique. Due to its unique characteristics, OFDM has been chosen by several wireless systems designers and standardization bodies. In order to provide an idea about the importance of the OFDM transmission technique, we can mention some examples of standards that employ it: IEEE802.15.4.g, IEEE802.11a/g/n/ac, Wimax, DVB-T, IEEE 802.20 and the 3GPP Long Term Evolution (LTE) mobile broadband standard downlink.

Before adopting ISDB-T, the Brazilian government made an enormous effort, putting together Universities, R&D Centers, the local Broadcast Industry and Broadcasters in order to establish a Brazilian digital television standard that would explore state-of-art techniques, e.g., Low Density Parity Check (LDPC) code and Space-Time Coding. Nevertheless, after all that effort, due to scale economy and its unique characteristics at that time, the Brazilian government adopted the ISDB-T Physical Layer, with some updates on Video and Audio Coding and Interactivity, as the basis for the Brazilian System of Terrestrial Digital Television (SBTVD). So, the ISDB-T with the aforementioned updates became known as ISDB-Tb. On the Digital Broadcasting Expert Group (DIBEG) website (www.dibeg.org), the reader can find the equivalence between the Brazilian and Japanese Standards for Terrestrial Digital Television.

In June 2005 the Committee for the Information Technology Area (CATI) of Brazilian Ministry of Science and Technology and Innovation MCTI approved the incorporation of the IC-Brazil Program, in the National Program for Microelectronics (PNM) which is a Priority Program within the Brazilian Policies for Informatics and Automation. The main goals of IC-Brazil are the formal qualification of IC designers, support to the creation of semiconductors companies focused on projects of ICs within Brazil, and the attraction of semiconductors companies focused on the design and development of ICs in Brazil.

The work presented in this thesis originated from the unique momentum created by the combination of the birth of Digital Television in Brazil and the creation of the IC-Brazil Program by the Brazilian government. Without this combination it would not have been possible to make these kind of projects in Brazil. These projects have been a long and costly journey, albeit scientifically and technologically worthy, towards a Brazilian DTV state-of-the-art low complexity Integrated Circuit, with good economy scale perspectives due to the fact that at the beginning of this project ISDB-T standard was not adopted by several countries like DVB-T.

During the development of the ISDB-T receiver proposed in this thesis, it was realized that due to the continental dimensions of Brazil, the DTTB would not be enough to cover the entire country with open DTV signal, specially for the case of remote localizations far from the high urban density regions. A natural choice to overcome this issue is to use satellite broadcasting system, as medium to distribute open DTV signal straight to the households, without the need of having a local DTTB system. At that time, Eldorado Research Institute and Idea! Electronic Systems, foresaw that, in a near future, there would be an open distribution system for high definition DTV over satellite, in Brazil. Based on that, it was decided by Eldorado Research Institute, that would be necessary to create a new ASIC for broadcast satellite reception. At that time DVB-S2 standard was the strongest candidate for that, and this assumption still stands nowadays. Therefore, it was decided to apply to a new round of resources funding from the MCTI - that was granted - in order to start the new project.

This thesis discusses in details the Architecture and Algorithms proposed for the implementation of a low complexity Intermediate Frequency(IF) ISDB-T Receiver on Application Specific Integrated Circuit (ASIC) CMOS. The Architecture proposed here is highly based on the COordinate Rotation Digital Computer (CORDIC) Algorithm, that is a simple and efficient algorithm suitable for VLSI implementations. The receiver copes with the impairments inherent to wireless channels transmission and the receiver crystals. The thesis also discusses the Methodology adopted and presents the implementation results. The receiver performance is presented and compared to those obtained by means of simulations.

Furthermore, the thesis also presents the Architecture and Algorithms for a DVB-

S2 receiver targeting its ASIC implementation. However, unlike the ISDB-T receiver, only preliminary ASIC implementation results are introduced. This was mainly done in order to have an early estimation of die area to prove that the project in ASIC is economically viable, as well as to verify possible bugs in early stage. As in the case of ISDB-T receiver, this receiver is highly based on CORDIC algorithm and it was prototyped in FPGA. The Methodology used for the second receiver is derived from that used for the ISDB-T receiver, with minor additions given the project characteristics.

### Resumen

La primera generación de Televisión Digital Terrestre(DTV) ha estado en servicio por más de una década. En 2013, varios países completaron la transición de transmisión analógica a televisión digital, la mayoría de ellas en Europa. En América del Sur, después de varios estudios y ensayos, Brasil adoptó el estándar japonés con algunas innovaciones. Fue el primer país en difundir comercialmente televisión digital en la región, en 2007. Sin embargo, en 2015 el país todavía no haba completado la transición a digital.

Japón y Brasil comenzaron a prestar el servicio de Difusión Televisión Digital Terrestre (DTTB) en diciembre de 2003 y diciembre de 2007 respectivamente, utilizando Radiodifusión Digital de Servicios Integrados (ISDB-T), también conocida como ARIB STD-B31 [1]. ISDB-T es claramente inspirado en DVB-T [2], la primera generación de la norma europea de Televisión Digital Terrestre. Sin embargo, ISDB-T supera una de las debilidades de DVB-T, el mal desempeño bajo ruido impulsivo. DVB-T e ISDB-T hacen uso de la técnica de transmisión Acceso múltiple por división de frecuencias ortogonales (OFDM). Debido a sus características únicas, OFDM ha sido elegido por varios diseñistas de sistemas inalámbricos y los organismos de normalización. Con el fin de dar una idea de la importancia de la técnica de transmisión OFDM, podemos mencionar algunos ejemplos de normas que la emplean: IEEE802.15.4.g, IEEE802.11a/g/n/ac, Wimax, DVB-T, IEEE 802.20 y el estándar de banda ancha móvil 3GPP Long Term Evolution (LTE).

Antes de adoptar el estándar ISDB-T, el gobierno brasileño hizo un enorme esfuerzo, juntando Universidades, Centros de I&D, la Industria de difusión y las emisoras locales con el propósito de establecer un estándar de televisión digital brasileña que explorarse técnicas de punta, por ejemplo, códigos para comprobación de paridad de baja densidad (LDPC) y de Espacio-Tiempo. Sin embargo, después de todo ese esfuerzo, debido a la economía de escala y a sus características únicas en ese momento, el gobierno brasileño adoptó la capa física del ISDB-T, con algunas actualizaciones en la codificación de vídeo y audio e interactividad, como base para el Sistema Brasileño de Televisión Digital Terrestre (SBTVD). Así, el ISDB-T con las actualizaciones antes mencionadas, se hizo conocido como ISDB-Tb. En el sitio web del Grupo de Expertos de Radiodifusión Digital (DiBEG) (www.dibeg.org), el lector puede encontrar la equivalencia entre las normas brasileñas y japonesas para la Televisión Digital Terrestre.

En junio de 2005, el Comité del Área de Tecnología de la Información (CATI) del Ministerio de Ciencia, Tecnología e Innovación de Brasil - MCTI aprobó la incorporación del Programa CI-Brasil, en el Programa Nacional de Microelectrnica (PNM), el cual es un programa prioritario dentro de las Políticas brasileñas de Informática y Automatización. Los principales objetivos de la CI-Brasil son la formación de disensistas de CIs, apoyar la creación de empresas de semiconductores enfocadas en proyectos de circuitos integrados dentro de Brasil, y la atracción de empresas de semiconductores interesadas en el diseño y desarrollo de circuitos integrados en Brasil.

El trabajo presentado en esta tesis se originó en el impulso único creado por la combinación del nacimiento de la televisión digital en Brasil y la creación del Programa de CI-Brasil por el gobierno brasileño. Sin esta combinación no hubiera sido posible realizar estes tipo de proyectos en Brasil. Estos proyectos han sido un trayecto largo y costoso, aunque meritorio desde el punto de vista científico y tecnológico, hacia un Circuito Integrado brasileño de punta y de baja complejidad para DTV, con buenas perspectivas de economía de escala debido al hecho que al inicio de este proyecto, el estándar ISDB-T no fue adoptado por varios países como DVB-T.

Durante el desarrollo del receptor ISDB-T propuesto en esta tesis, se observó que debido a las dimensiones continentales de Brasil, la DTTB no sería suficiente para cubrir todo el país con la señal de televisión digital abierta, especialmente para el caso de localizaciones remotas, apartadas de las regiones de alta densidad urbana. Una elección natural para superar este problema es utilizar el sistema de radiodifusión por satélite, como medio para distribuir la señal de televisión digital abierta y de alta definicin directamente a los hogares, sin la necesidad de tener un sistema DTTB local. En ese momento, el Instituto de Investigación Eldorado e Idea! Sistemas Electrónicos, previeron que en un futuro cercano habría un sistema de distribución abierto para DTV de alta definición a través de satélite en Brasil. Con base en eso, el Instituto de Investigación Eldorado decidió que sería necesario crear un nuevo ASIC para la recepción de radiodifusión por satélite. En ese tiempo, el estándar DVB-S2 era el candidato más fuerte para eso, y esta suposición sigue en pie hoy en día. Por lo tanto, se decidió aplicar a una nueva ronda de financiación de recursos del MCTI - que se concedió - con el fin de iniciar el nuevo proyecto con esto propósito.

En esta tesis se analiza en detalle la Arquitectura y algoritmos propuestos para la implementación de un receptor ISDB-T de baja complejidad y frecuencia intermedia (IF) en Application Specific Integrated Circuit (ASIC) CMOS. La arquitectura aquí propuesta se basa fuertemente en el algoritmo del computador digital para rotación de coordenadas (CORDIC), el cual es un algoritmo simple, eficiente y adecuado para implementaciones VLSI. El receptor hace frente a las deficiencias inherentes a las transmisiones por canales inalámbricos y los cristales del receptor. La tesis también analiza la metodología adoptada y presenta los resultados de la implementación. El desempeño del receptor es presentado y comparado con los obtenidos por medio de simulaciones.

Por otro lado, la tesis también presenta la arquitectura y los algoritmos para un receptor DVB-S2 dirigido a la implementación en ASIC. Sin embargo, a diferencia del receptor ISDB-T, se introducen sólo los resultados preliminares de implementación en ASIC. Esto se hizo principalmente con el fin de tener una estimación temprana del área del die para demostrar que el proyecto en ASIC es económicamente viable, así como para verificar posibles errores en etapa temprana. Como en el caso de receptor ISDB-T, este receptor se basa fuertemente en el algoritmo CORDIC y fue un prototipado en FPGA. La metodología utilizada para el segundo receptor se deriva de la utilizada para el receptor ISDB-T, con adiciones menores, dadas las características del proyecto.

## Resum

La primera generació de Televisió Digital Terrestre (TDT) ha estat en servici durant més d'una dècada. En 2013, diversos països ja van completar la transició de la radiodifusió de televisió analògica a la digital, i la majoria van ser a Europa. A Amèrica del Sud, després de diversos estudis i assajos, Brasil va adoptar l'estàndard japonés amb algunes innovacions. Va ser el primer país a difondre comercialment televisió digital a eixa regió, el 2007. No obstant això, en 2015 el país encara no havia completat la transició a la TV digital.

Japó i Brasil van comenar els servicis de Radiodifusió de Televisió Terrestre Digital (DTTB) al desembre de 2003 i al desembre de 2007, respectivament, utilitzant la Radiodifusió Digital amb Servicis Integrats de (ISDB-T), també coneguda com a ARIB STD-B31 [1]. Òbviament, la ISDB-T estava inspirada en la DVB-T [2], la primera generació de la norma europea de Radiodifusió de Televisió Terrestre Digital. No obstant això, va superar una de les debilitats de la DVB-T, és a dir, el baix rendiment amb soroll de commutació. Tant la DVB-T com la ISDB-T fan ús del Múltiple per Divisió Ortogonal de Freqëència (OFDM) com a tècnica de transmissió. A causa de les seues característiques úniques, el OFDM ha estat escollit per diversos dissenyadors de sistemes sense fil i organismes de normalització. Per tal de donar una idea de la importància de la tècnica de transmissió OFDM, podem esmentar alguns exemples de normes que la fan servir: IEEE802.15.4.g, IEEE802.11a/g/n/ac, Wimax, DVB-T, IEEE 802.20 i l'enlla de baixada estàndard de banda ampla móbil 3GPP Long Term Evolution (LTE).

Abans d'adoptar la ISDB-T, el govern brasiler va fer un enorme esfor, en fer col.laborar universitats, centres de R+D, la indústria de radiodifusió i les emissores locals a fi d'establir un estàndard brasiler de televisió digital que explorés tècniques punteres, com ara la Comprovació de Paritat de Baixa Densitat (LDPC) i la codificació espai-temps. No obstant això, després de tot eixe esfor, a causa de l'economia d'escala i les seues característiques úniques d'eixe moment, el govern brasiler va adoptar la Capa Física de la ISDB-T, amb algunes actualitzacions en codificació de vídeo i àudio i interactivitat, com a base per al Sistema Brasiler de Televisió Digital Terrestre (SBTVD). Així, l'ISDB-T amb estes actualitzacions va passar a conéixer-se com a ISDB-Tb. Al lloc web del Grup d'Experts de Radiodifusió Digital (DiBEG) (www.dibeg.org), el lector pot trobar l'equivalència entre les normes brasileres i japoneses de Televisió Digital Terrestre.

Al juny de 2005, el Comité de l'Àrea de Tecnologia de la Informació (CATI) del Ministeri de Ciència i Tecnologia i Innovació del Brasil (MCTI) va aprovar la incorporació del programa CI Brasil al Programa Nacional de Microelectrnica (PNM), que és un programa prioritari dins de les polítiques brasileres d'informàtica i automatització. Els principals objectius de CI Brasil són la qualificació formal dels dissenyadors de circuits integrats, el suport a la creació d'empreses de semiconductors centrades en projectes de circuits integrats dins del Brasil i l'atracció d'empreses de semiconductors centrades en el disseny i desenvolupament de circuits integrats al Brasil.

El treball presentat en esta tesi es va originar en l'impuls únic creat per la combinació del naixement de la televisió digital al Brasil i la creació del programa Brasil CI pel govern brasiler. Sense esta combinació no hauria estat possible realitzar este tipus de projectes a Brasil. Estos projectes han suposat un viatge llarg i costós, tot i que digne científicament i tecnològica, cap a un circuit integrat punter de baixa complexitat per a la TDT brasilera, amb bones perspectives d'economia d'escala perquè a l'inici d'este projecte l'estàndard ISDB-T no va ser adoptat per diversos països, com el DVB-T.

Durant el desenvolupament del receptor de ISDB-T proposat en esta tesi, va resultar que, a causa de les dimensions continentals de Brasil, la DTTB no seria suficient per cobrir tot el país amb el senyal de TDT oberta, especialment pel que fa a les localitzacions remotes allunyades de les regions d'alta densitat urbana. Una elecció natural per superar este problema és utilitzar el sistema de radiodifusió per satèl.lit com a mitjà per distribuir el senyal de TDT directament a les llars, sense la necessitat de tenir un sistema DTTB local. En este moment, l'Institut de Recerca Eldorado i Idea! Sistemes Electrònics van preveure que, en un futur pròxim, no hi hauria a Brasil un sistema de distribució oberta de TDT d'alta definició a través de satèl.lit. D'acord amb això, l'Institut de Recerca Eldorado va decidir que seria necessari crear un nou ASIC per a la recepció de radiodifusió per satèl.lit. En eixe moment, l'estàndard DVB-S2 era el candidat més fort per aò i esta suposició segueix en peus hui en dia. Per tant, es va decidir demanar una nova ronda de finanament de recursos del MCTI que es va concedir , per tal d'iniciar el nou projecte.

En esta tesi s'analitza en detall l'arquitectura i els algorismes proposats per l'execuci d'un receptor ISDB-T de Freqüència Intermèdia (FI) de baixa complexitat sobre CMOS de Circuit Integrat d'Aplicacions Específiques (ASIC). L'arquitectura ací proposada es basa molt en l'algorisme de l'Ordinador Digital de Rotació de Coordenades (CORDIC), que és un algorisme simple i eficient adequat per implementacions VLSI. El receptor fa front a les deficiències inherents a la transmissió de canals sense fil i els cristalls del receptor. Esta tesi també analitza la metodologia adoptada i presenta els resultats de l'execució. Es presenta el rendiment del receptor i es compara amb els obtinguts per mitjà de simulacions.

D'altra banda, esta tesi també presenta l'arquitectura i els algorismes d'un receptor de DVB-S2 de cara a la seua implementació en ASIC. No obstant aixó, a diferència del receptor ISDB-T, només s'introdueixen resultats preliminars d'implementació en ASIC. Això es va fer principalment amb la finalitat de tenir una estimació primerenca de la zona de dau per demostrar que el projecte en ASIC és econòmicament viable, així com per verificar possibles errors en l'etapa primerenca. Com en el cas del receptor ISDB-T, este receptor es basa molt en l'algorisme CORDIC i va ser un prototip de FPGA. La metodologia utilitzada per al segon receptor es deriva de la utilitzada per al receptor ISDB-T, amb addicions de menor importància, ateses les característiques del projecte.

## Contents

| Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | i     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | v     |

| Resumen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ix    |

| Resum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xiii  |

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xvii  |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | xxvii |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xxxv  |

| 1 Introduction         1.1 Motivation         1.2 From Landell to Digital Television in a Glance         1.2.1 DTV First Efforts and Tests         1.2.2 The R&D Efforts         1.2.3 The Decision and Some Numbers         1.2.4 How DTV Influenced the Brazilian Industry of         1.3 The National Program on Microelectronics and the Ar         Brazilian Government         1.4 Thesis Objectives         1.5 Outline of the Thesis and Survey of the Contributions         1.6 Summary of my Main Roles and Responsibilities on ISDI S2 Receivers Projects |       |

| <ul> <li>2 Wireless Communications Basics</li> <li>2.1 OFDM - Orthogonal Frequency Division Multiplex .</li> <li>2.1.1 OFDM Advantages and Drawbacks</li> <li>2.1.1.1 Advantages of OFDM</li> <li>2.1.1.1.1 High Spectral Efficiency</li> <li>2.1.1.1.2 One Tap Equalization</li> </ul>                                                                                                                                                                                                                                                                              |       |

### CONTENTS

|     |        | 2.1.1.1.3 Robust Against ISI                          | 21 |

|-----|--------|-------------------------------------------------------|----|

|     |        | 2.1.1.1.4 Resistance Against Fading and Narrowband    |    |

|     |        |                                                       | 21 |

|     |        | 2.1.1.1.5 Efficient Implementation Using FFT 2        | 21 |

|     |        | 2.1.1.1.6 Low Sensitivity to Time Synchronization Er- |    |

|     |        |                                                       | 22 |

|     |        | 2.1.1.1.7 SFN and Macrodiversity                      | 22 |

|     |        | •                                                     | 22 |

|     |        |                                                       | 22 |

|     |        |                                                       | 22 |

|     |        |                                                       | 23 |

|     |        |                                                       | 23 |

|     |        | ě                                                     | 23 |

| 2.2 | Wirele | 0                                                     | 24 |

|     | 2.2.1  |                                                       | 25 |

|     |        | 0                                                     | 27 |

|     |        |                                                       | 27 |

|     |        |                                                       | 27 |

|     |        | v v                                                   | 28 |

|     |        |                                                       | 28 |

|     |        |                                                       | 29 |

|     |        |                                                       | 30 |

|     |        |                                                       | 31 |

|     |        |                                                       | 31 |

|     |        |                                                       | 32 |

|     |        | v. 0 0                                                | 32 |

|     |        | - · · ·                                               | 33 |

|     |        |                                                       | 33 |

|     |        |                                                       | 33 |

|     |        |                                                       | 34 |

|     |        |                                                       | 34 |

|     |        |                                                       | 34 |

|     |        |                                                       | 36 |

|     |        |                                                       | 36 |

|     |        | 2.2.1.10.2 Path Loss                                  | 36 |

|     |        |                                                       | 36 |

|     |        | 2.2.1.10.2.2 Typical Suburban                         | 37 |

|     |        | 2.2.1.10.2.3 Rural                                    | 37 |

|     |        |                                                       | 38 |

|     |        |                                                       | 38 |

|     |        |                                                       | 38 |

|     |        |                                                       | 39 |

|     |        |                                                       | 39 |

|     |        |                                                       | 39 |

|     | 2.2.2  | Main RF Analog Front-End Impairments                  | 41 |

| 2.2.2.1 Radio Conversion Architectures Impairments        | 42        |

|-----------------------------------------------------------|-----------|

| 2.2.2.2 A Second Look at RF Analog Front-End and Wireless |           |

| Chanel Impairments                                        | 42        |

| 2.2.2.2.1 Non-Linearity                                   |           |

| 2.2.2.2.2 Power Amplifier Distortion                      | 45        |

| 2.2.2.2.3 Phase Noise                                     | 45        |

| 2.2.2.2.4 Carrier Frequency Offset                        |           |

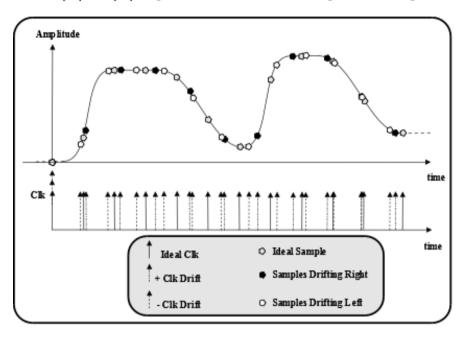

| 2.2.2.2.5 Sampling Clock Offset                           | 47        |

| 2.2.2.2.6 Timing Synchronization Errors                   |           |

| 2.2.2.2.7 I&Q Imbalance or I&Q Mismatch                   |           |

| 2.2.2.2.8 DC Offset                                       |           |

| 2.2.2.2.9 Additive Noise                                  |           |

| 2.2.2.2.9.1 Noise Figure and Sensitivity                  |           |

| 2.2.2.2.10 Multipath                                      |           |

| 2.2.2.2.11 Quantization Noise and Limited Bit Length      |           |

| 2.2.2.2.12 Quantization Clipping (Saturation)             |           |

| •                                                         |           |

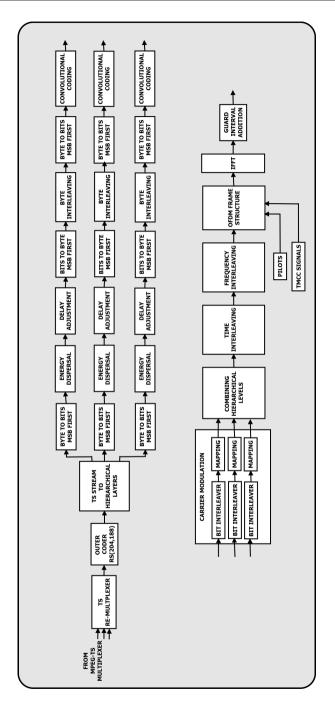

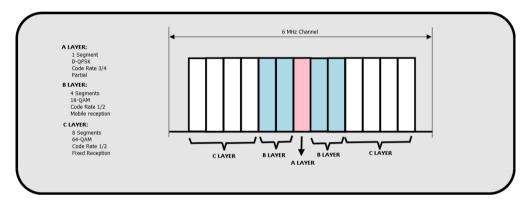

| ISDB-T and DVB-S2 Standards                               | <b>53</b> |

| 3.1 ISDB-T Standard Basics                                |           |

| 3.1.1 ISDB-T a First Look                                 |           |

| 3.1.2 ISDB-T a Detailed View                              |           |

| 3.1.2.1 Transport Stream Re-multiplexer (Remux) $\ldots$  |           |

| 3.1.2.2 Reed Solomon Encoder                              | 58        |

| 3.1.2.3 Hierarchical Layer Divider                        |           |

| 3.1.2.4 Bytes to Bit $\ldots$                             | 59        |

| 3.1.2.5 Energy Dispersal                                  | 59        |

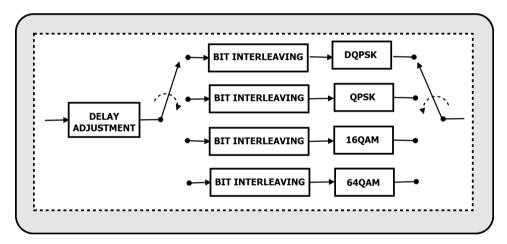

| 3.1.2.6 Delay Adjustment                                  | 59        |

| 3.1.2.7 Bits to Byte $\ldots$                             | 59        |

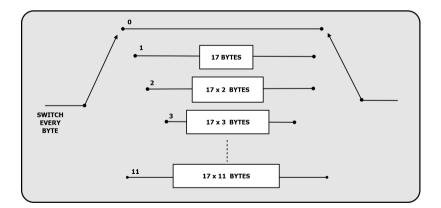

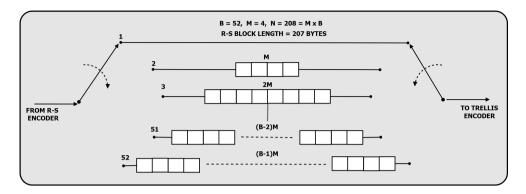

| 3.1.2.8 Byte Interleaving                                 | 59        |

| 3.1.2.9 Byte to Bits $\ldots$                             | 61        |

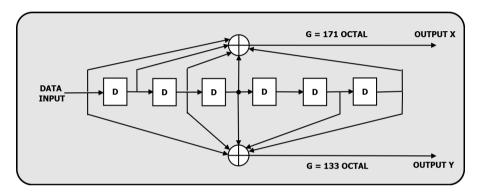

| 3.1.2.10 Convolutional Coding                             |           |

| 3.1.2.11 Carrier Modulation                               |           |

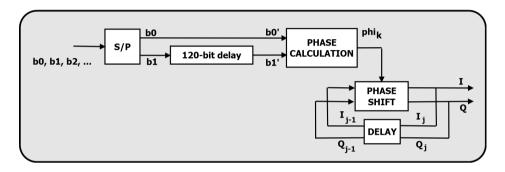

| 3.1.2.11.1 DQPSK                                          |           |

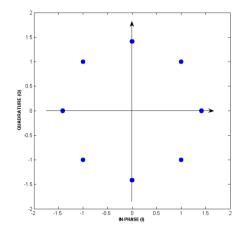

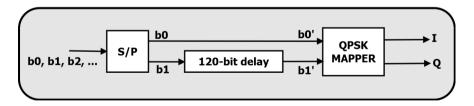

| 3.1.2.11.2 QPSK                                           |           |

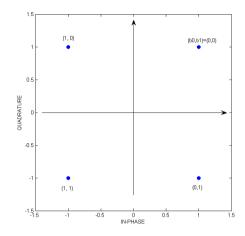

| 3.1.2.11.3 16-QAM                                         | 65        |

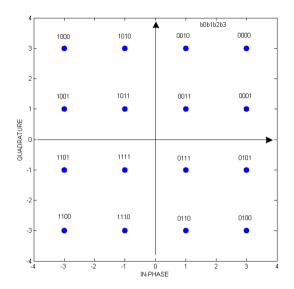

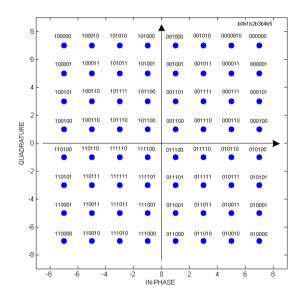

| 3.1.2.11.4 64-QAM                                         |           |

| 3.1.2.11.5 NORMALIZATION FACTOR                           | 66        |

| 3.1.2.11.6 Data Segment $\ldots$                          | 68        |

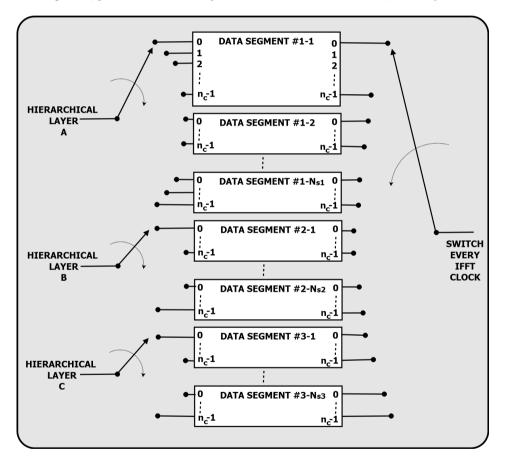

| 3.1.2.12 Hierarchical Layer Combining                     |           |

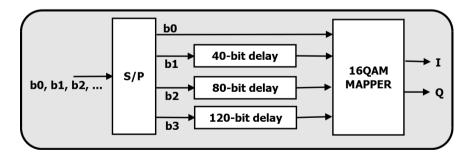

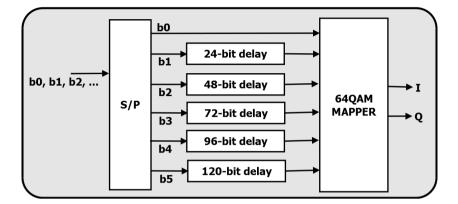

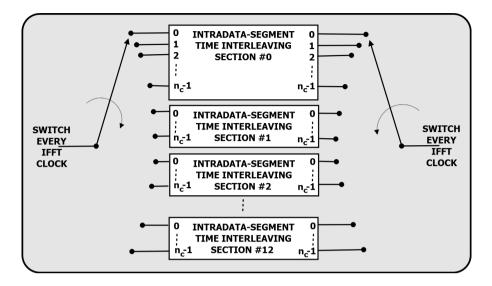

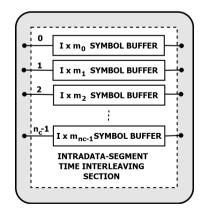

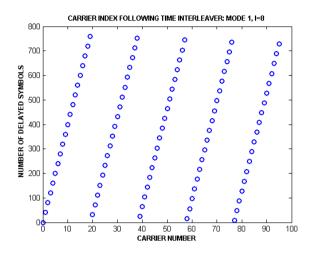

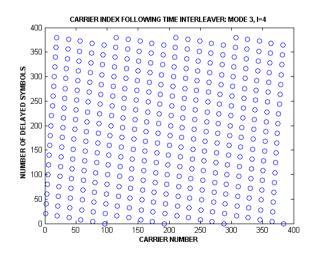

| 3.1.2.13 Time Interleaving                                |           |

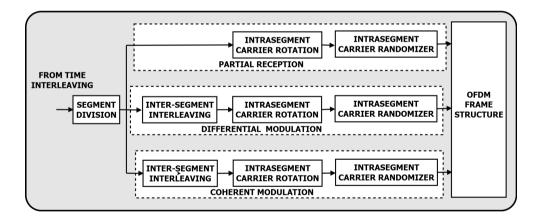

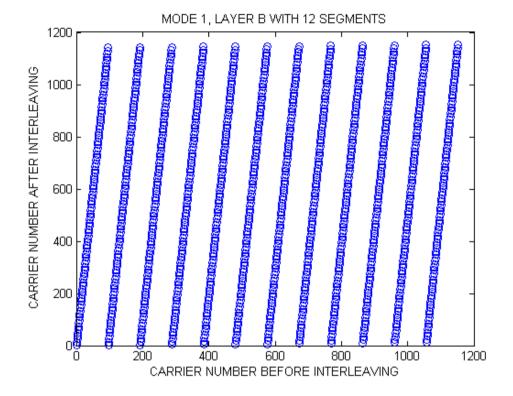

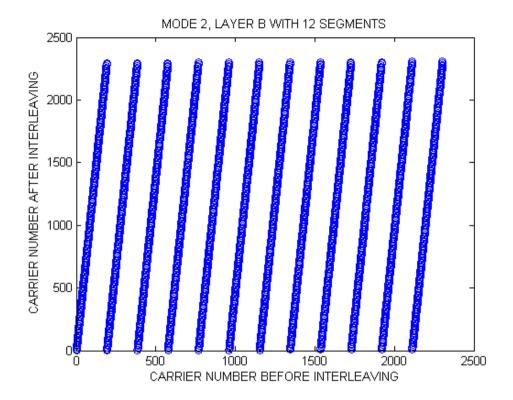

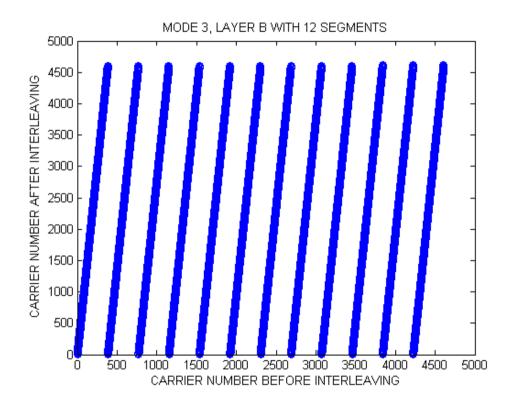

| 3.1.2.14 Frequency Interleaving                           |           |

| 3.1.2.14.1 Intersegment Time Interleaving                 | 74        |

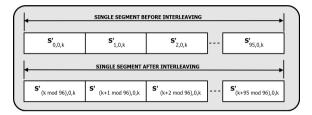

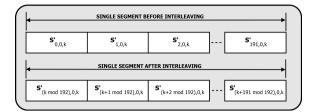

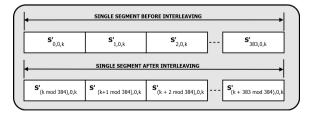

| 3.1.2.14.2 Intrasegment Interleaver                       |           |

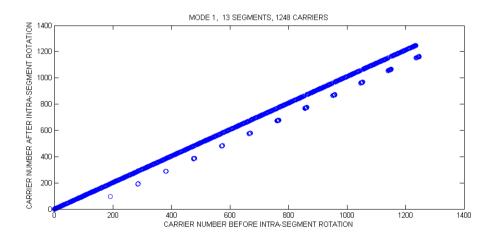

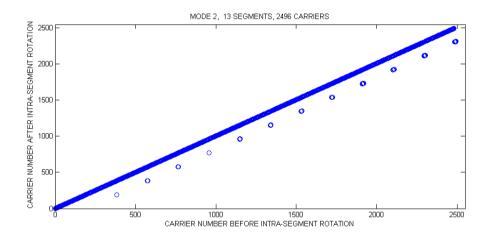

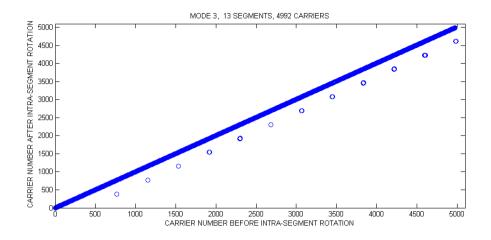

| 3.1.2.14.2.1 Intrasegment Carrier Rotation                |           |

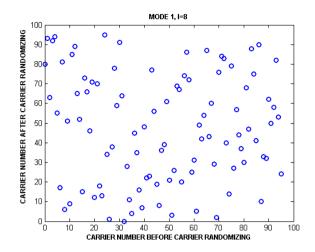

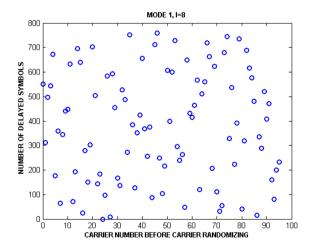

| 3.1.2.14.3 Intrasegment Carrier Randomizer                | 78        |

3

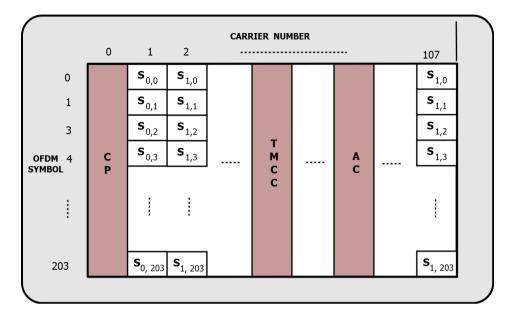

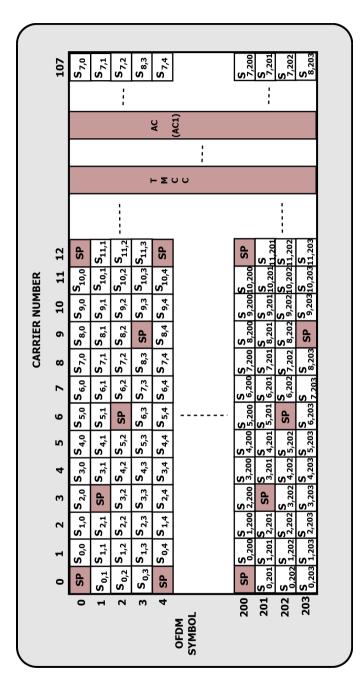

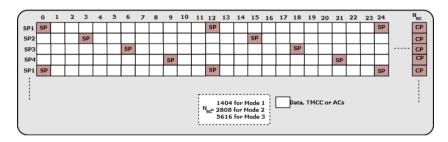

| 3.1.2.15 OFDM Frame Structure                                                                        | 82  |

|------------------------------------------------------------------------------------------------------|-----|

| 3.1.2.15.1 OFDM Segment for Differential Modulation                                                  | 82  |

| 3.1.2.15.2 OFDM Segment for Coherent Modulation                                                      | 82  |

| 3.1.2.16 Pilot and Control Signals                                                                   | 84  |

| 3.1.2.16.1 Scattered Pilot (SP) $\ldots$ $\ldots$ $\ldots$ $\ldots$                                  | 84  |

| 3.1.2.16.2 Continual Pilot (CP) $\ldots$ $\ldots$ $\ldots$                                           | 87  |

| 3.1.2.16.3 TMCC                                                                                      | 87  |

| 3.1.2.16.4 AC                                                                                        | 88  |

| 3.1.2.16.5 Transmission Spectrum                                                                     | 88  |

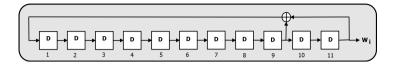

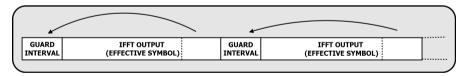

| 3.1.2.16.6 IFFT and GI                                                                               | 89  |

| 3.1.2.17 TMCC Fields                                                                                 | 89  |

| 3.1.2.17.1 Synchronization Word                                                                      | 90  |

| 3.1.2.17.2 Segment Type Identification                                                               | 90  |

| 3.1.2.17.3 TMCC Information                                                                          | 90  |

| 3.1.2.17.3.1 System Identification                                                                   | 91  |

| 3.1.2.17.3.2 Transmission Parameter Switching                                                        | 91  |

| 3.1.2.17.3.3 Emergency Alarm Broadcast Flag                                                          | 91  |

| 3.1.2.17.3.4 Current and Next Information                                                            | 92  |

| 3.1.2.17.3.5 Phase-Shift Correction for Terrestrial                                                  |     |

| Audio Broadcasting                                                                                   | 92  |

| 3.1.2.17.3.6 Parity Bits                                                                             | 92  |

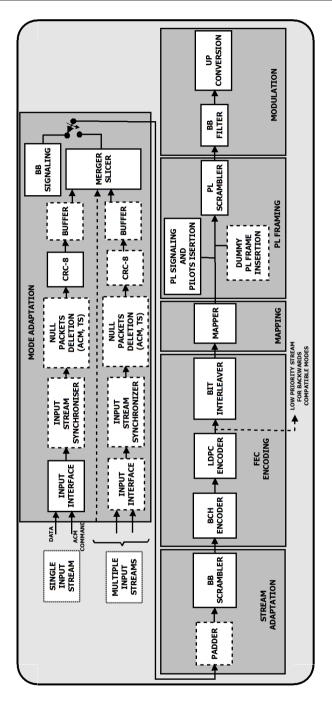

| DVB-S2 Standard Basics                                                                               | 92  |

| 3.2.1 DVB-S2 a Detailed View                                                                         | 93  |

| 3.2.1.1 Mode Adaptation                                                                              | 93  |

| 3.2.1.1.1 Input Interface                                                                            | 93  |

| 3.2.1.1.2 Input Stream Synchronizer                                                                  | 95  |

| 3.2.1.1.3 Null Packets Deletion                                                                      | 95  |

| 3.2.1.1.4 CRC-8 Encoder                                                                              | 95  |

| 3.2.1.1.5 Merger/Slicer                                                                              | 96  |

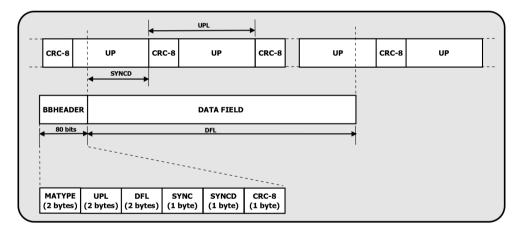

| 3.2.1.1.6 Base Band Header (BBHEADER)                                                                | 96  |

| 3.2.1.2 Stream Adaptation                                                                            | 97  |

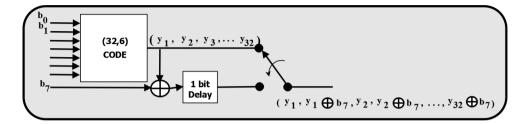

| 3.2.1.2.1 Base Band (BB) Scrambling                                                                  | 97  |

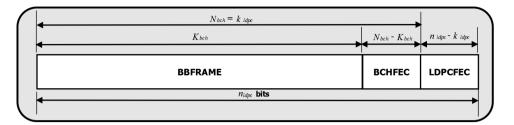

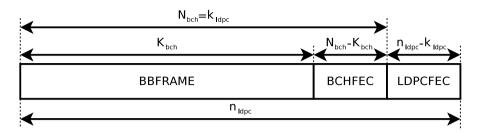

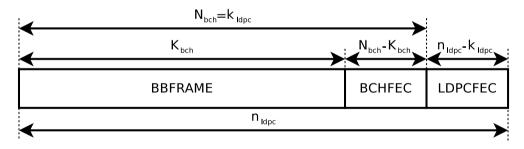

| 3.2.1.3 FEC Encoding Subsystem                                                                       | 97  |

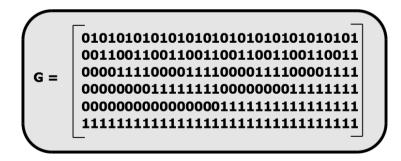

| 3.2.1.3.1 BCH Encoder                                                                                | 97  |

| 3.2.1.3.2 Low Density Parity Check (LDPC) Encoder                                                    | 98  |

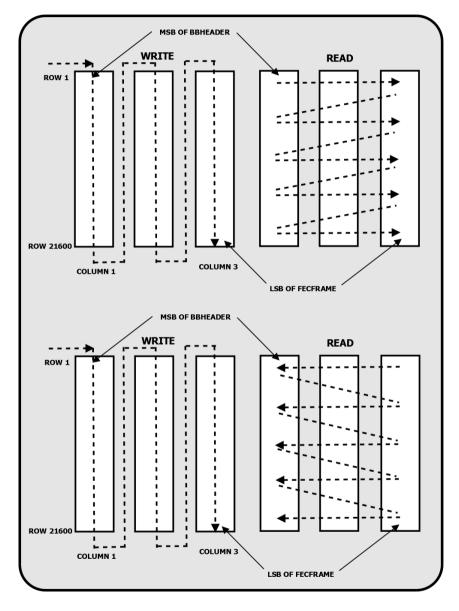

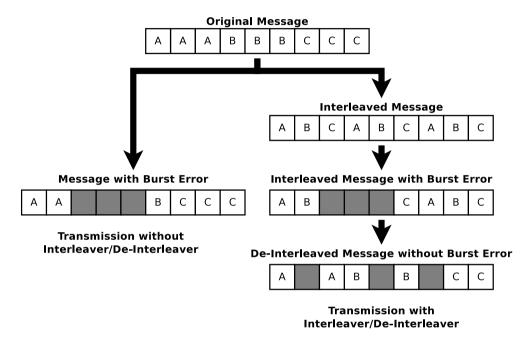

| $3.2.1.3.3  \text{Bit Interleaver}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 102 |

| 3.2.1.4 Bit Mapping                                                                                  | 102 |

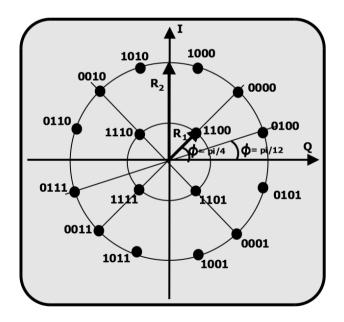

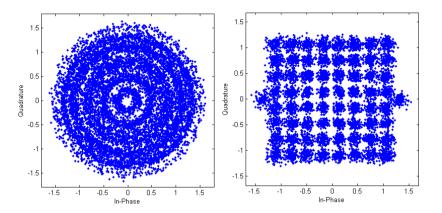

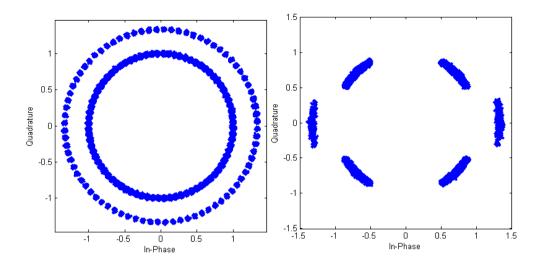

| 3.2.1.4.1 16APSK                                                                                     | 104 |

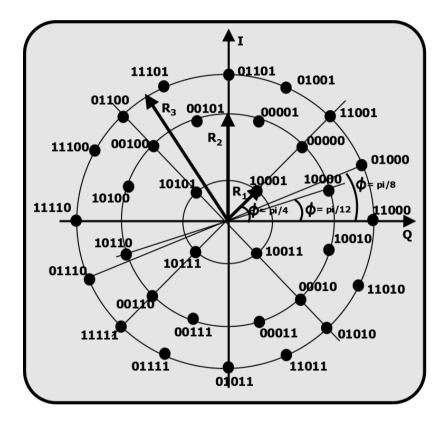

| 3.2.1.4.2 32APSK                                                                                     |     |

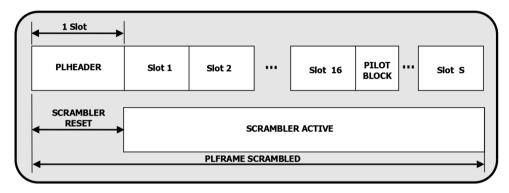

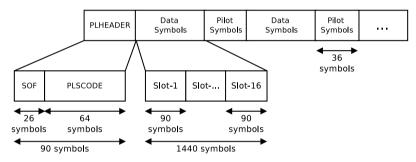

| 3.2.1.5 Physical Layer (PL) Framing                                                                  | 105 |

| 3.2.1.5.1 Dummy PLFRAME Insertion                                                                    | 107 |

| 3.2.1.5.2 PL Signaling                                                                               | 108 |

| $3.2.1.5.2.1$ Start-Of-Frame (SOF) Field $\ldots$                                                    | 108 |

| 3.2.1.5.2.2 MODCOD Field                                                                             | 108 |

| 3.2.1.5.2.3 TYPE Field                                                                               | 109 |

3.2

### CONTENTS

|   |     |       | 3.2.1.5.2.4 PLS Code                                                                         | . 109 |

|---|-----|-------|----------------------------------------------------------------------------------------------|-------|

|   |     |       | 3.2.1.5.3 Pilots Insertion                                                                   | . 109 |

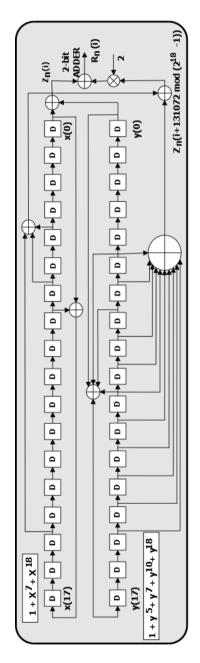

|   |     |       | 3.2.1.5.4 Physical Layer Scrambling                                                          | . 111 |

|   |     |       | 3.2.1.6 Base Band Shaping                                                                    | . 111 |

|   |     | 3.2.2 | DVB-S2X: the Future of DVB-S2                                                                | . 113 |

| 4 | The |       | B-T Receiver Design Methodology                                                              | 115   |

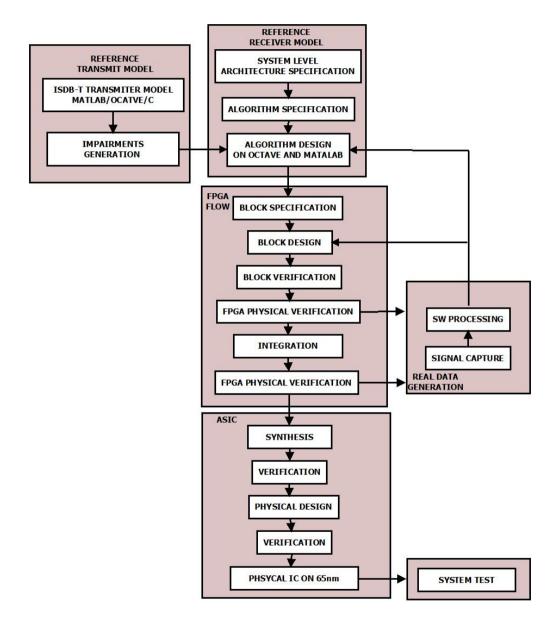

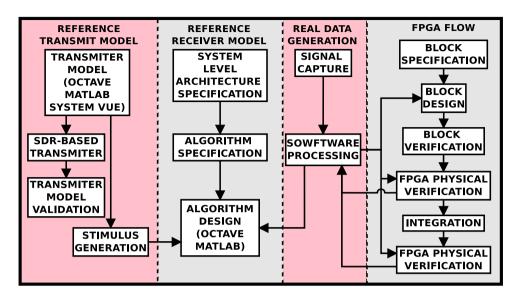

| 4 | 4.1 |       | iew of the Methodology                                                                       |       |

|   | 4.2 |       | ver Design Steps                                                                             |       |

|   | 1.2 | 4.2.1 | Transmitter Model and Impairments Generation                                                 |       |

|   |     | 1.2.1 | 4.2.1.1 ISDB-T Transmitter Model                                                             |       |

|   |     |       | 4.2.1.2 Impairments Generation                                                               |       |

|   |     | 4.2.2 | Receiver Architecture and Model                                                              |       |

|   |     |       | 4.2.2.1 System Level Architecture Specification                                              |       |

|   |     |       | 4.2.2.2 Algorithm and Block Design In Octave and Matlab                                      |       |

|   |     | 4.2.3 | Digital Front-End Design and FPGA Prototyping                                                |       |

|   |     |       | 4.2.3.1 Block Specification                                                                  |       |

|   |     |       | 4.2.3.2 Block Design                                                                         |       |

|   |     |       | 4.2.3.3 Block Verification                                                                   |       |

|   |     |       | 4.2.3.4 FPGA Physical Verification of Blocks                                                 | . 122 |

|   |     |       | 4.2.3.5 Receiver Integration                                                                 | . 123 |

|   |     |       | 4.2.3.6 FPGA Physical Verification of the Receiver                                           | . 123 |

|   |     |       | 4.2.3.7 Real data generation and capturing                                                   | . 124 |

|   |     | 4.2.4 | ASIC Design Flow                                                                             | . 124 |

|   |     |       | $4.2.4.1  \text{Synthesis}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | . 124 |

|   |     |       | 4.2.4.2 Gate level post-synthesis verification                                               |       |

|   |     |       | 4.2.4.3 Physical design                                                                      |       |

|   |     |       | 4.2.4.4 Gate level post-physical design verification                                         |       |

|   |     |       | 4.2.4.5 Physical IC in 65 nm                                                                 |       |

|   |     | 4.2.5 | System Test and IC Characterization                                                          | . 126 |

| 5 | The | Prop  | osed ISDB-T Receiver Architecture and Algorithms                                             | 127   |

| 0 | 5.1 |       | luction                                                                                      |       |

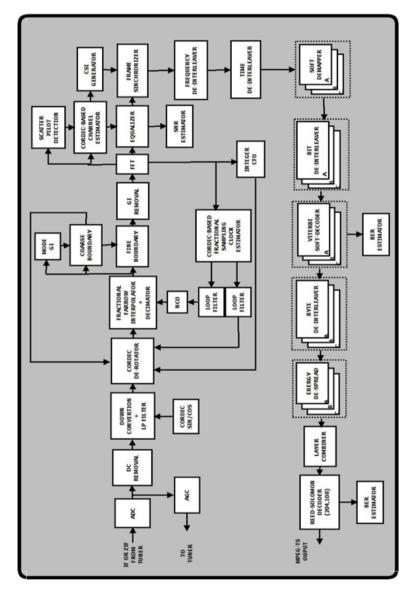

|   | 5.2 |       | chitecture for an IF Digital Receiver for ISDB-T Signal Reception                            |       |

|   | 5.3 |       | Digital Receiver Algorithms in Details                                                       |       |

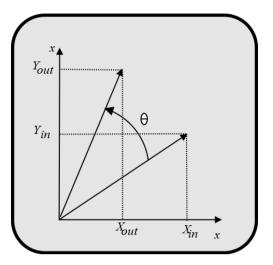

|   | 0.0 | 5.3.1 | CORDIC Algorithm                                                                             |       |

|   |     |       | 5.3.1.1 The CORDIC Algorithm                                                                 |       |

|   |     | 5.3.2 | Time Synchronization                                                                         |       |

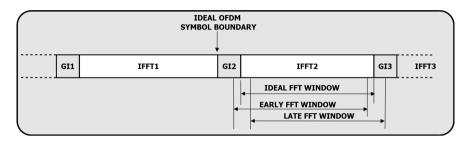

|   |     |       | 5.3.2.1 Effects of Timing Offset                                                             | . 137 |

|   |     |       | 5.3.2.2 Symbol Boundary Detection, Coarse Fractional Car-                                    |       |

|   |     |       | rier Frequency Offset Estimation and, Mode and GI                                            |       |

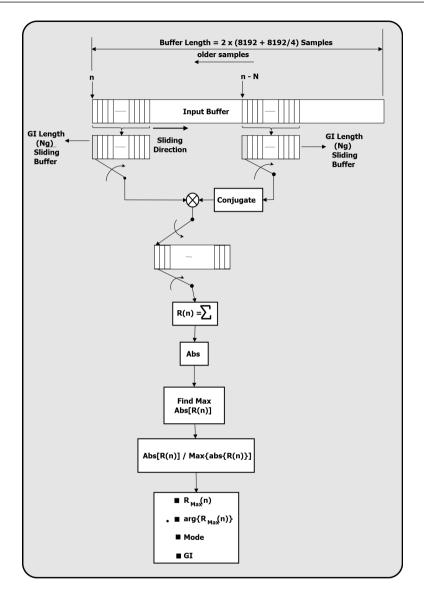

|   |     |       | Detection Algorithm                                                                          |       |

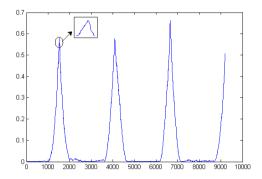

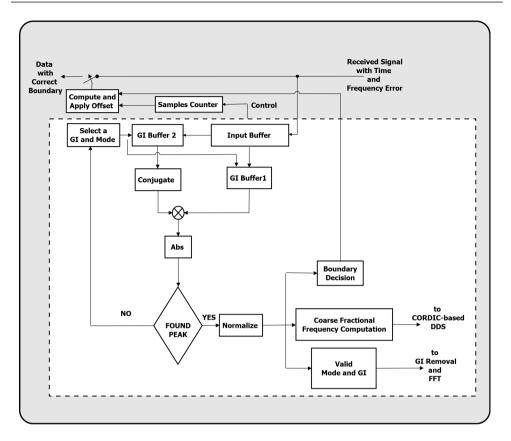

|   |     |       | 5.3.2.2.1 Detection of Coarse and Fine Symbol Bound-                                         |       |

|   |     |       | aries, Mode and GI                                                                           | . 141 |

|   |     |       | 5.3.2.2.2 Coarse Fractional CFO Estimation                                                   |       |

|                   | 5.3.3            | Fine and Integer Carrier Frequency Offset                  |                     |

|-------------------|------------------|------------------------------------------------------------|---------------------|

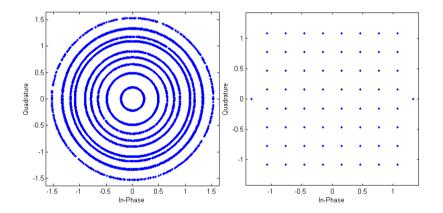

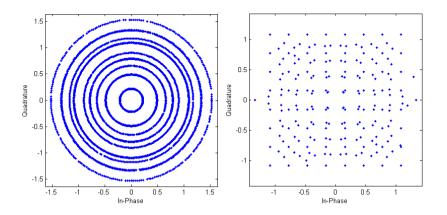

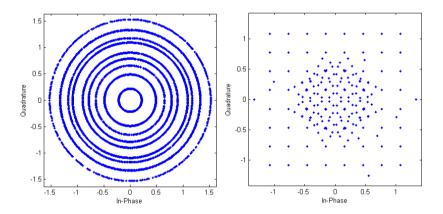

|                   |                  | 5.3.3.1 The Effects of ICFO and RCFO                       | . 146               |

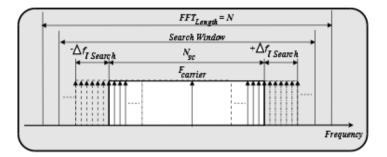

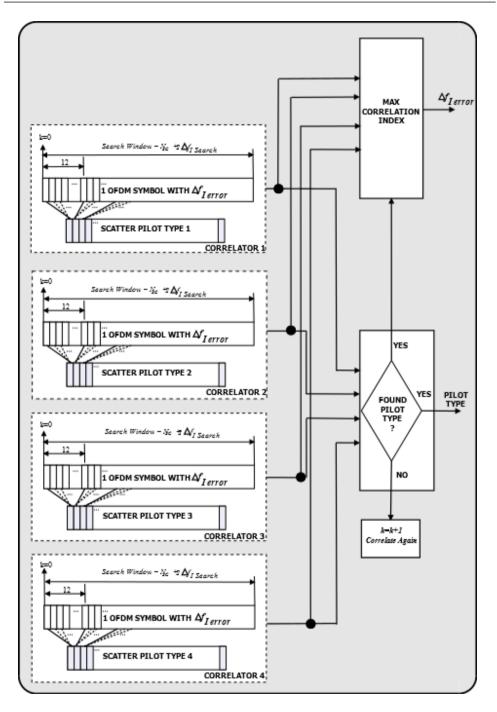

|                   |                  | 5.3.3.2 ICFO Estimation                                    | . 149               |

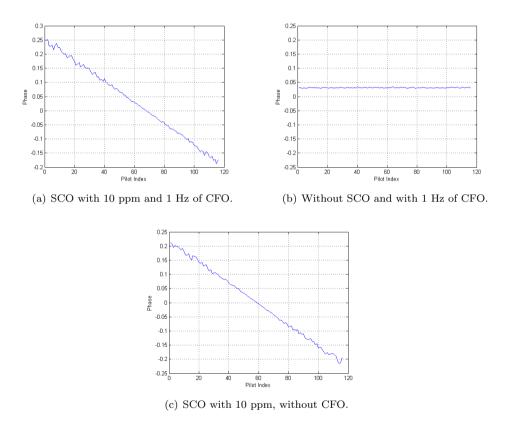

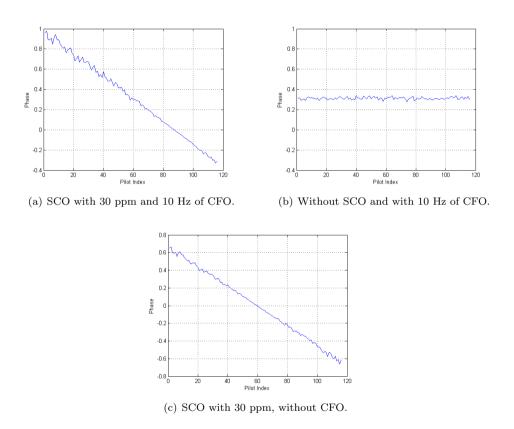

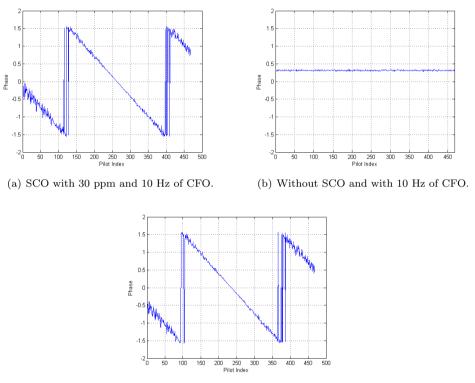

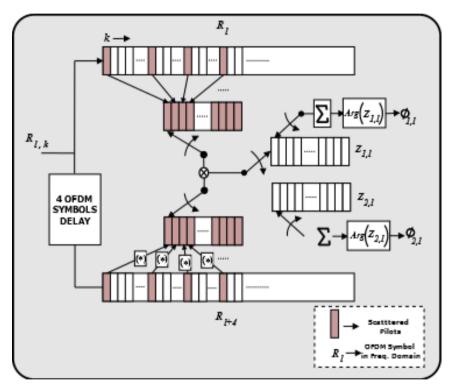

|                   | 5.3.4            | Joint RCFO and SCO Estimator                               | . 151               |

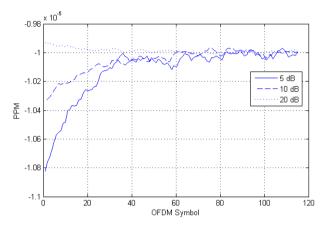

|                   |                  | 5.3.4.1 Estimation of RCFO and SCO                         | . 153               |

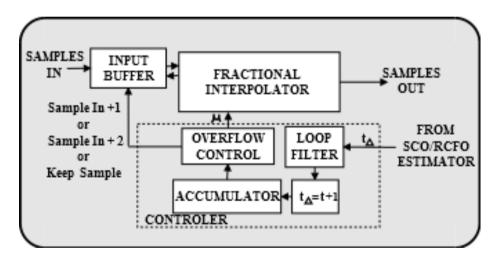

|                   |                  | 5.3.4.2 Correction of RCFO and SCO                         | . 159               |

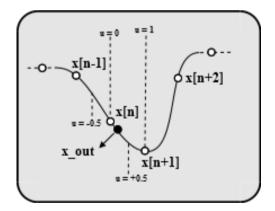

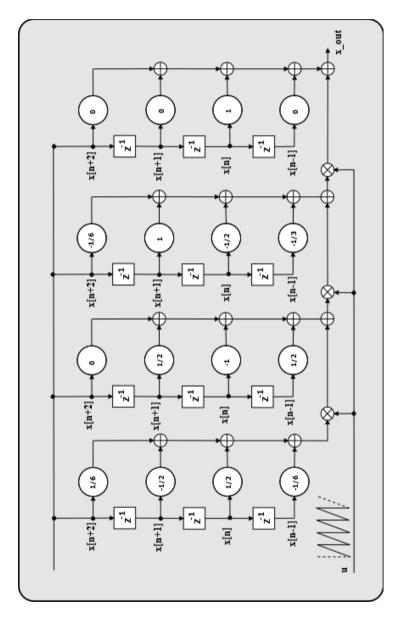

|                   |                  | 5.3.4.2.1 Farrow Interpolation Advantages and Dis-         |                     |

|                   |                  | advantages                                                 | . 164               |

|                   | 5.3.5            | Frequency Domain Equalizer                                 | . 165               |

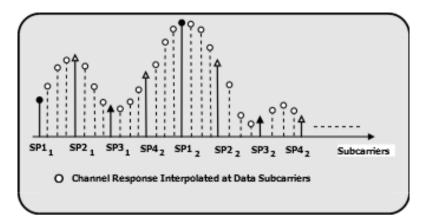

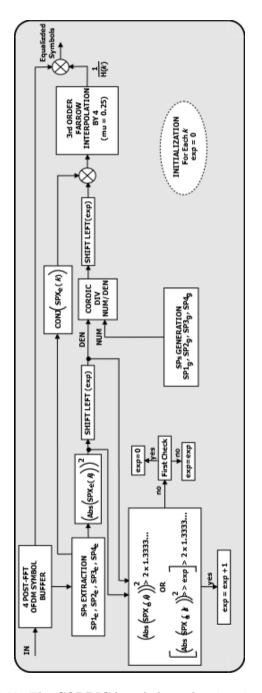

|                   |                  | 5.3.5.1 The Channel Estimator and the Equalization         | . 165               |

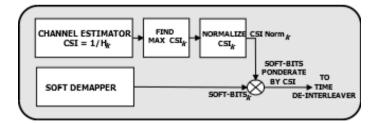

|                   | 5.3.6            | Soft-Demapper With CSI                                     | . 171               |

|                   |                  | 5.3.6.1 The Soft Bits Computation                          | . 173               |

|                   |                  | 5.3.6.1.1 QPSK                                             | . 173               |

|                   |                  | 5.3.6.1.2 16-QAM                                           | . 173               |

|                   |                  | 5.3.6.1.3 64-QAM                                           | . 173               |

|                   |                  | 5.3.6.1.4 QPSK                                             | . 174               |

|                   |                  | 5.3.6.1.5 16-QAM                                           | . 174               |

|                   |                  | 5.3.6.1.6 64-QAM                                           | . 174               |

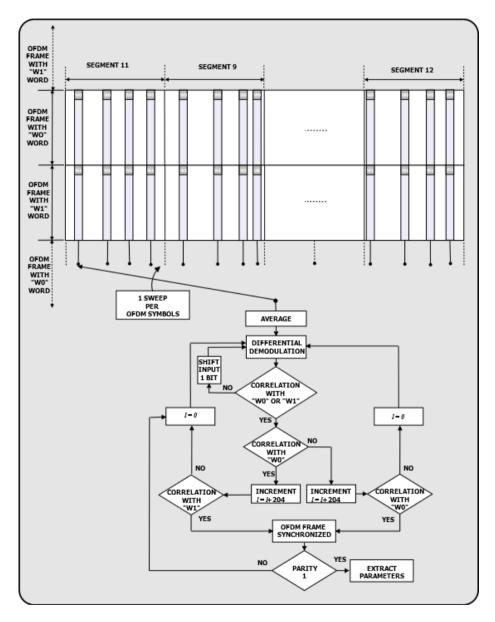

|                   | 5.3.7            | Joint TMCC Detection and Frame Synchronization             | . 175               |

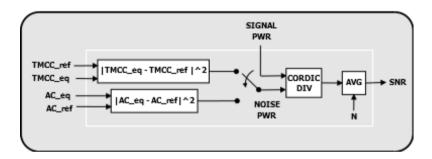

|                   | 5.3.8            | SNR Estimator                                              | . 177               |

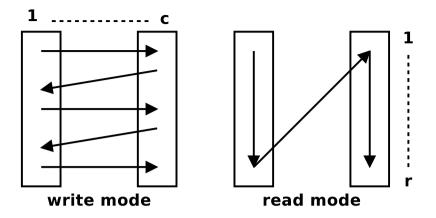

|                   | 5.3.9            | Soft Time Deinterleaver                                    | . 177               |

|                   | 5.3.10           | BER Estimator                                              | . 178               |

|                   |                  | 5.3.10.1 Post Viterbi Decoder Bit Error Rate (BER)         | . 178               |

|                   |                  | 5.3.10.2 Post Reed-Solomon BER                             | . 178               |

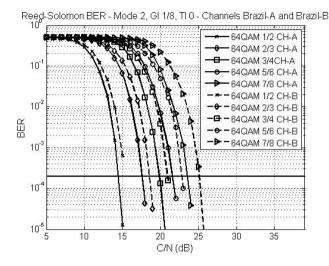

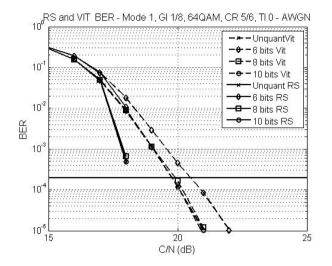

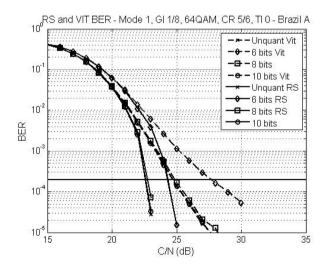

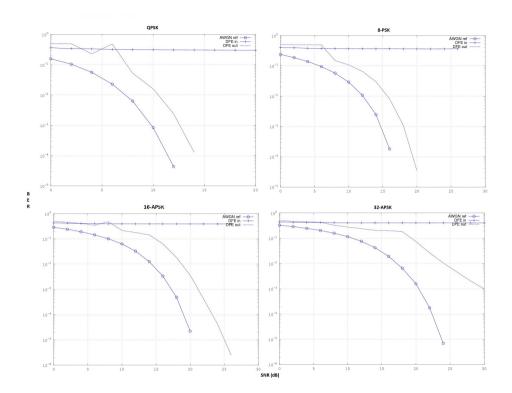

| 5.4               | Simula           | ation Results                                              | . 179               |

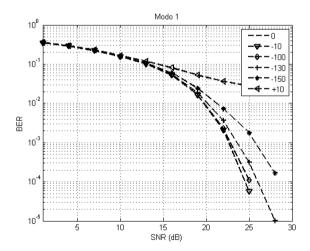

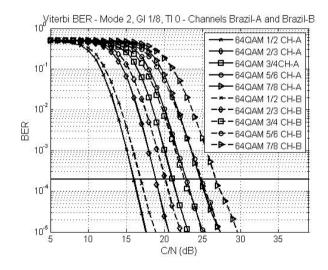

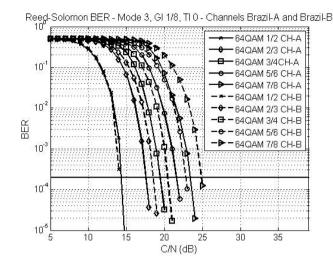

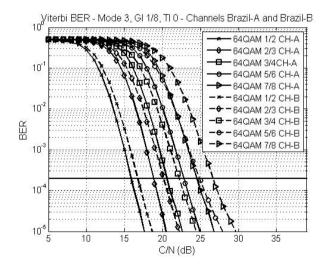

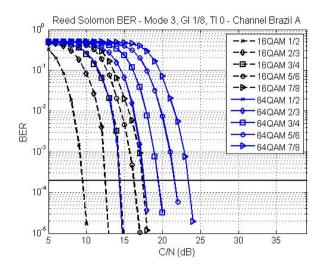

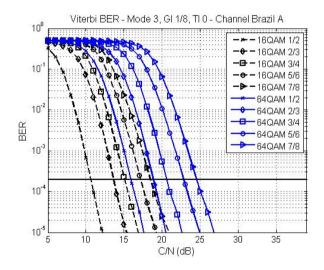

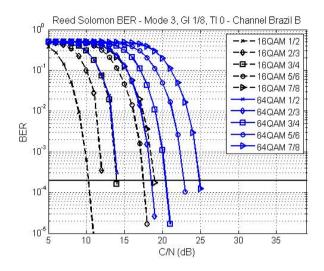

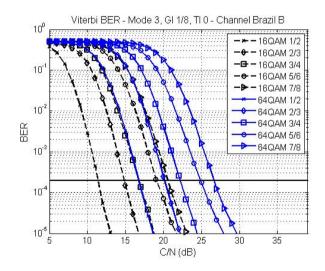

|                   | 5.4.1            | Performance Over Brazil-A and Brazil-B Wireless Channels . | . 180               |

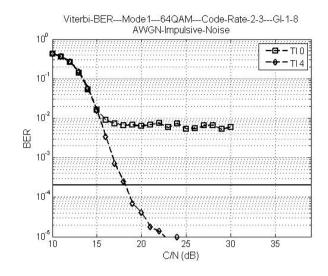

|                   | 5.4.2            | Performance Under Impulsive Noise                          | . 184               |

|                   | 5.4.3            | ADC Quantization Effects in the Performance                | . 185               |

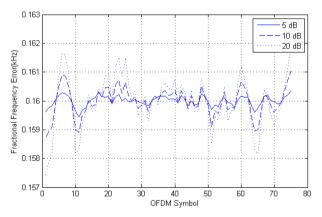

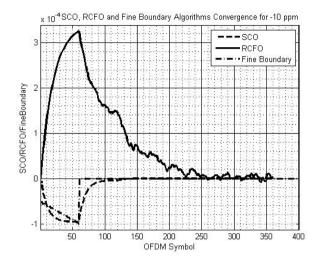

|                   | 5.4.4            | SCO, RCFO and Fine Boundary Convergence                    | . 186               |

| 5.5               | Conclu           | usions                                                     | . 186               |

| TOP               |                  |                                                            |                     |

|                   | B-T R<br>ults    | eceiver: VLSI Implementation, FPGA Prototype and Te        |                     |

| <b>Res</b><br>6.1 |                  | uction                                                     | <b>189</b><br>. 189 |

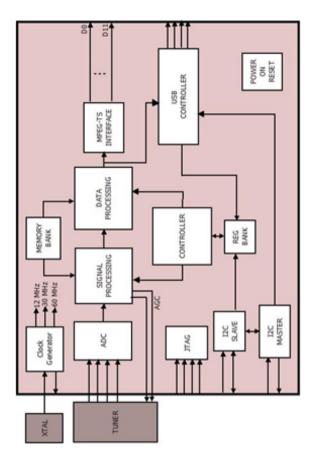

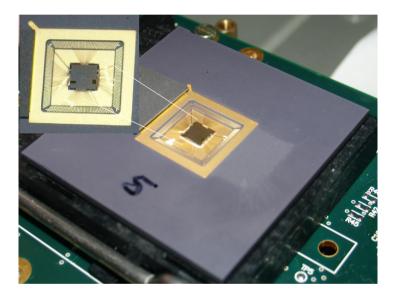

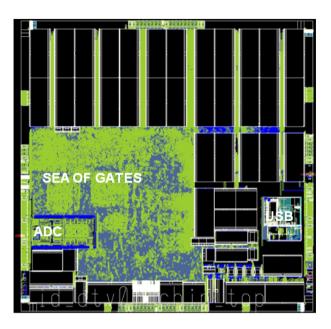

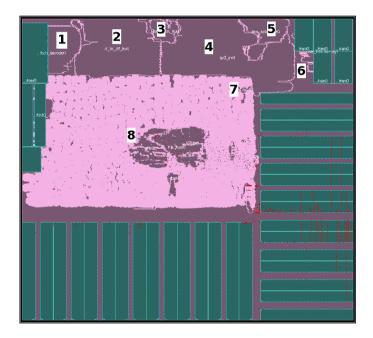

| 6.1               |                  | Implementation in 65 nm CMOS                               |                     |

| 0.2               | 6.2.1            |                                                            |                     |

|                   | 6.2.1            | Physical Synthesis                                         |                     |

|                   |                  | Physical Design                                            |                     |

|                   | $6.2.3 \\ 6.2.4$ | Memory Area                                                |                     |

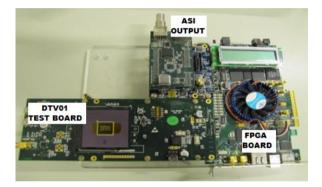

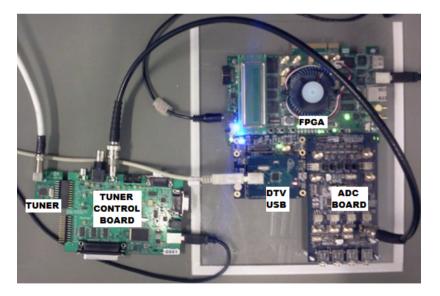

|                   |                  | DTV01 Demo Board                                           |                     |

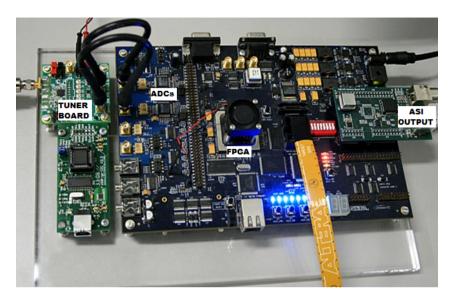

| ດາ                | 6.2.5<br>FDCA    | Mini PCI Based DTV01 Demo Board and Multi-Chip-Module(M    | /                   |

| 6.3               |                  | Prototype                                                  |                     |

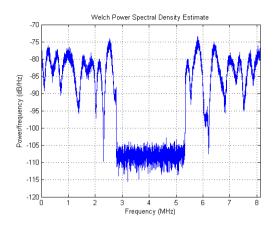

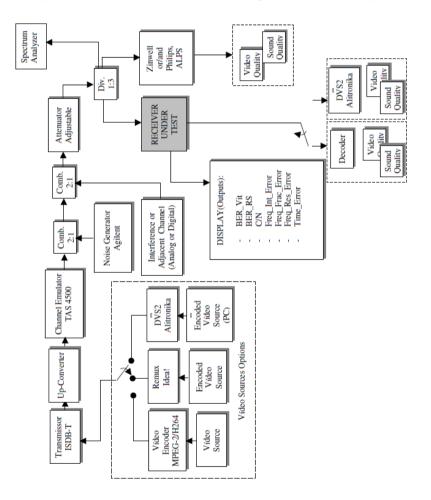

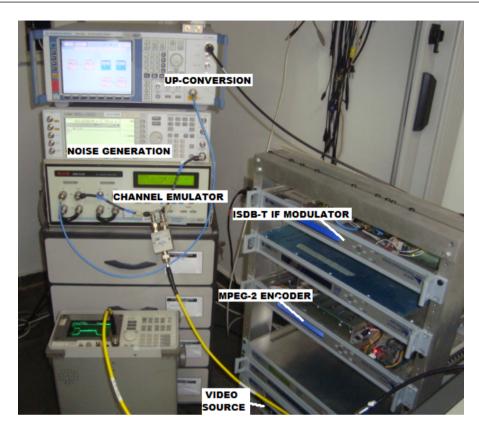

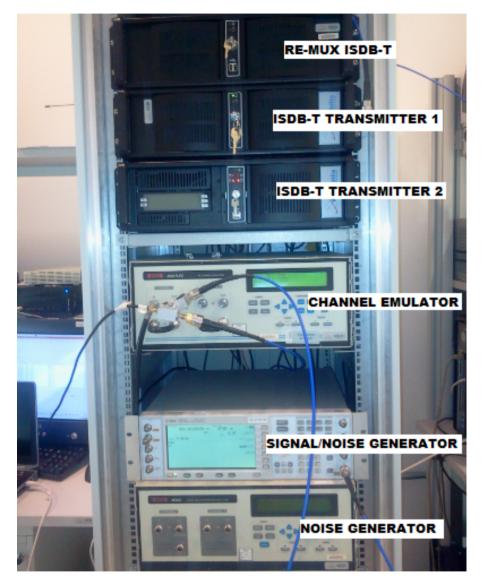

| 6.4               |                  | Convironment                                               |                     |

| 6.5<br>6.6        | -                | imental Results                                            |                     |

| 6.6               | Conclu           | usions                                                     | . 205               |

6

| 7 | The | Prope  | osed DVB-S2 Receiver Architecture and Algorithms                                                 | 207 |

|---|-----|--------|--------------------------------------------------------------------------------------------------|-----|

|   | 7.1 |        | uction $\ldots$ | 207 |

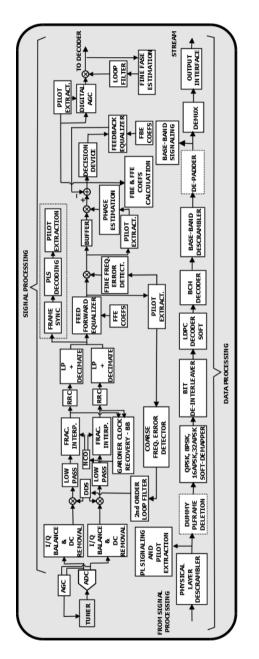

|   | 7.2 | Archit | ecture for an IF Digital Receiver for DVB-S2 Signal Reception .                                  | 208 |

|   |     | 7.2.1  | The Current Implemented Architecture                                                             | 208 |

|   |     |        | 7.2.1.1 Signal Processing                                                                        | 211 |

|   |     |        | 7.2.1.2 Data Processing                                                                          | 212 |

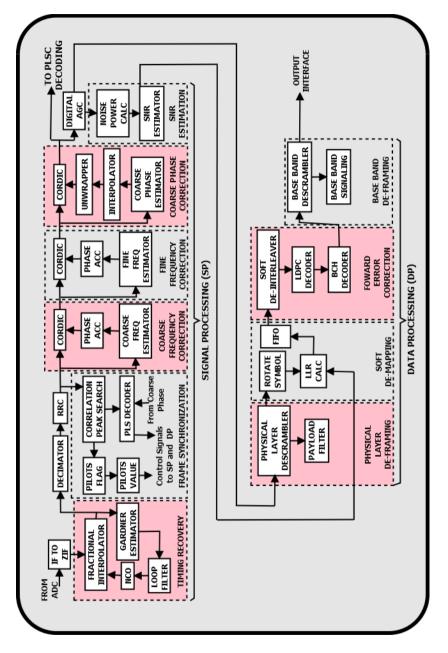

|   |     | 7.2.2  | The Final Architecture                                                                           | 213 |

|   | 7.3 | The D  | igital Receiver Algorithms in Details                                                            | 215 |

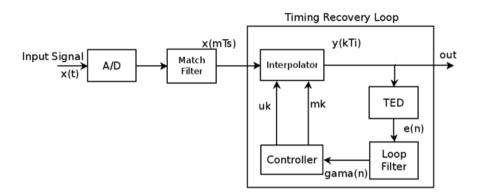

|   |     | 7.3.1  | Timing Recovery                                                                                  | 215 |

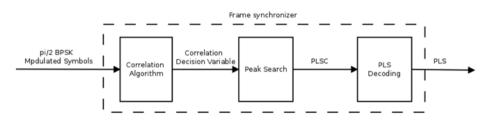

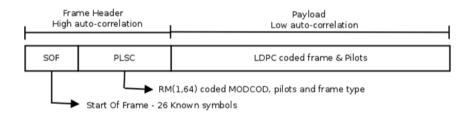

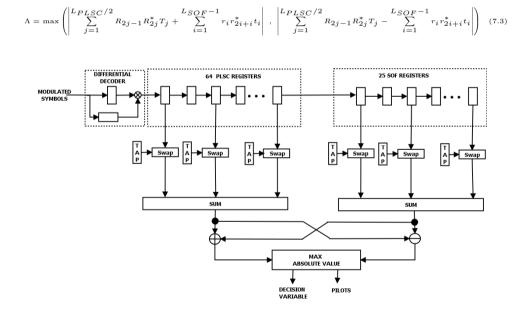

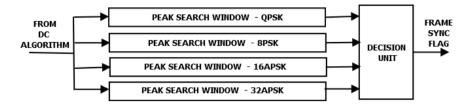

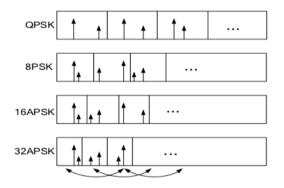

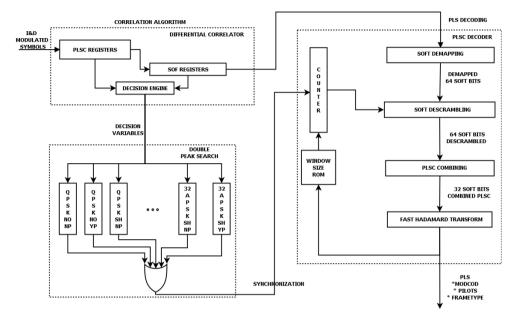

|   |     | 7.3.2  | Frame Synchronization and PLS Decoding                                                           | 216 |

|   |     |        | 7.3.2.1 Frame Synchronization and PLS Decoding                                                   |     |

|   |     |        | 7.3.2.1.1 Acquisition $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                         |     |

|   |     |        | 7.3.2.1.2 Peak Search                                                                            |     |

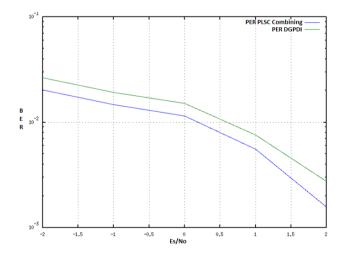

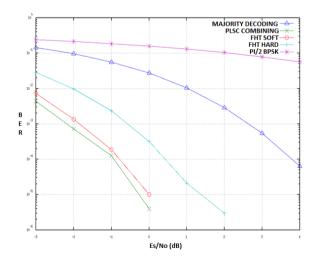

|   |     |        | 7.3.2.2 PLS Decoding                                                                             |     |

|   |     |        | 7.3.2.3 The Proposed Implementation Architecture                                                 | 224 |

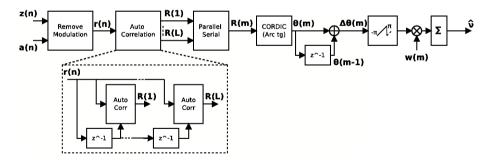

|   |     | 7.3.3  | Coarse and Fine Frequency Estimation (CFE and FFE) and                                           |     |

|   |     |        | Correction                                                                                       |     |

|   |     |        | 7.3.3.1 Coarse Frequency Estimation and Correction                                               |     |

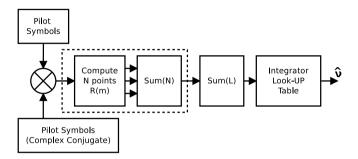

|   |     |        | 7.3.3.2 Fine Frequency Estimation and Correction                                                 |     |

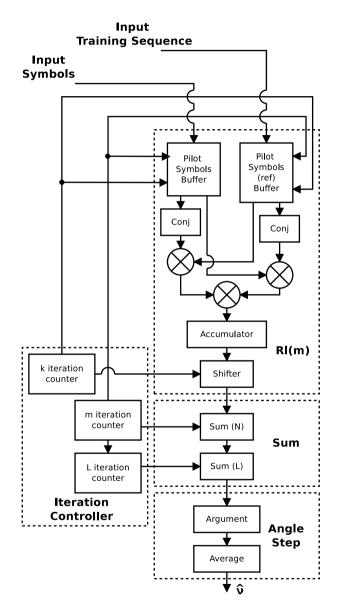

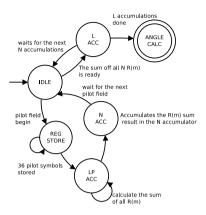

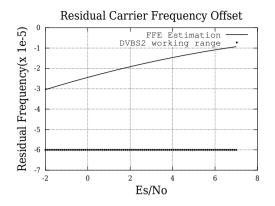

|   |     |        | 7.3.3.2.1 The Proposed Architecture                                                              |     |

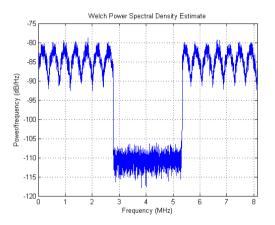

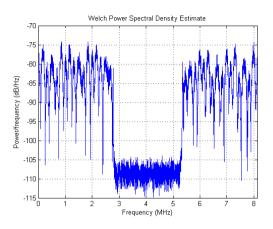

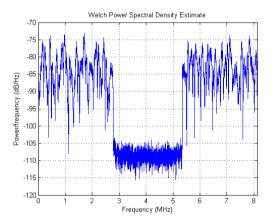

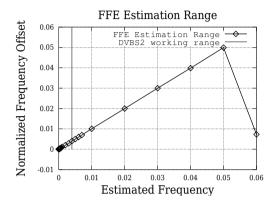

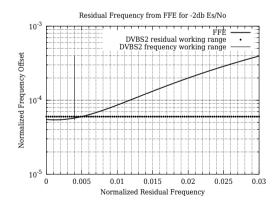

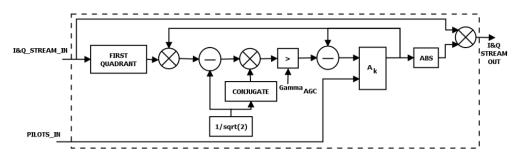

|   |     |        | 7.3.3.2.2 Simulations                                                                            |     |

|   |     | 7.3.4  | Coarse Phase Estimation and Correction                                                           |     |

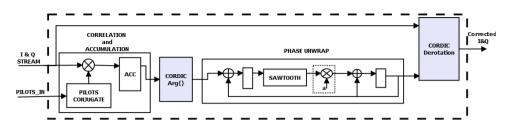

|   |     | 7.3.5  | Digital Automatic Gain Control (AGC)                                                             |     |

|   |     | 7.3.6  | Physical Layer Descrambler - PL Descrambler                                                      |     |

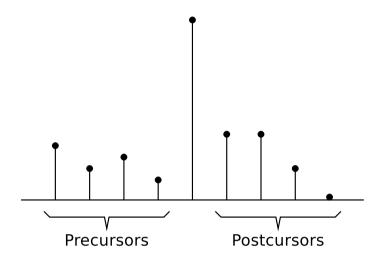

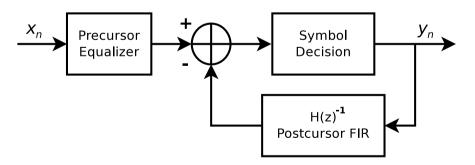

|   |     | 7.3.7  | Adaptive Equalizer                                                                               |     |

|   |     |        | 7.3.7.1 Proposed Equalizer Architecture                                                          |     |

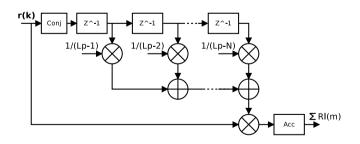

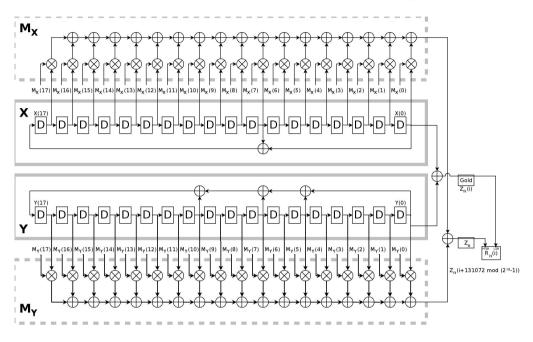

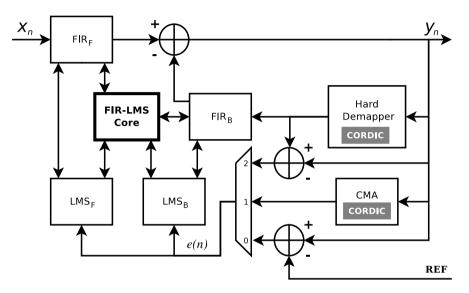

|   |     |        | 7.3.7.1.1 FIR-LMS Core                                                                           |     |

|   |     |        | 7.3.7.1.2 Error Tracking $\ldots$                                                                |     |

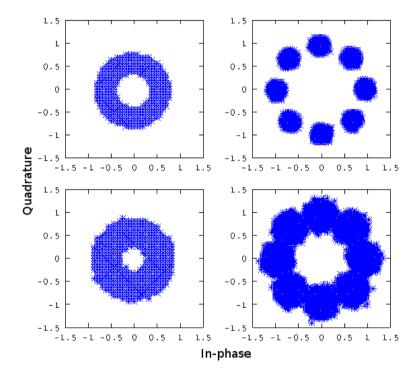

|   |     |        | 7.3.7.1.3 CMA                                                                                    |     |

|   |     |        | 7.3.7.1.4 Decision Device                                                                        |     |

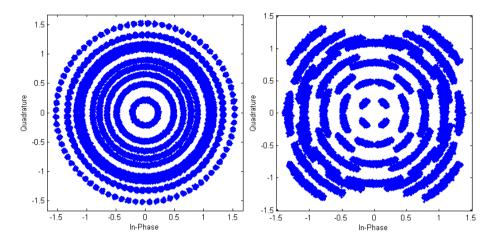

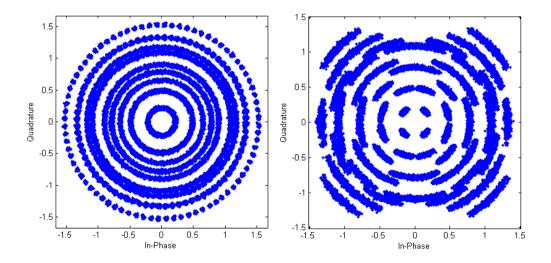

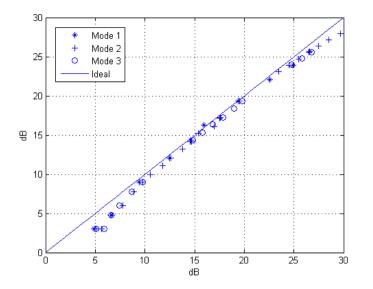

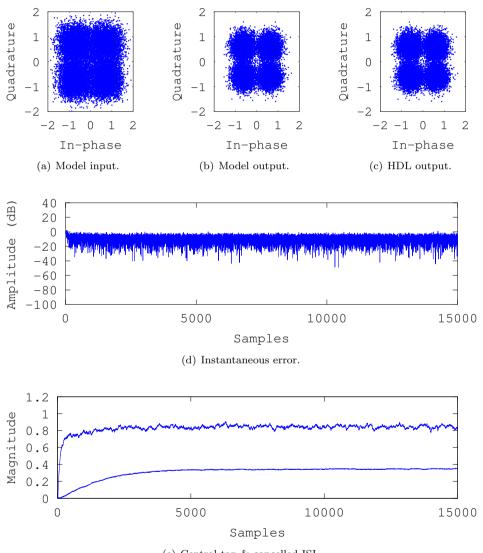

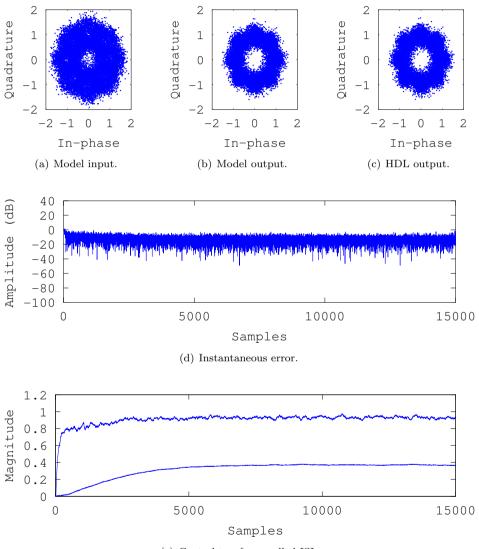

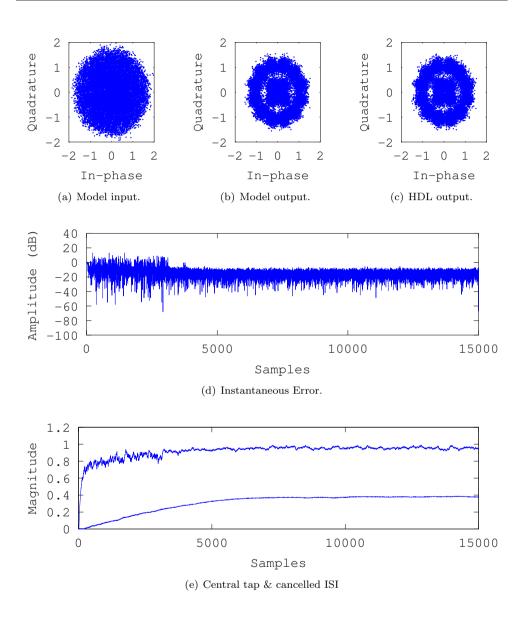

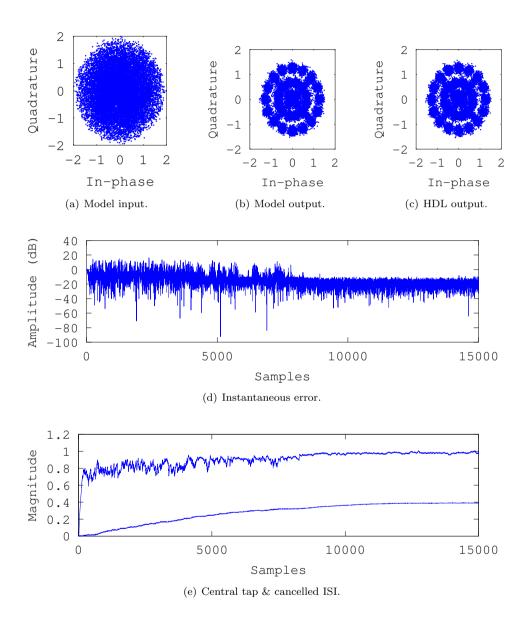

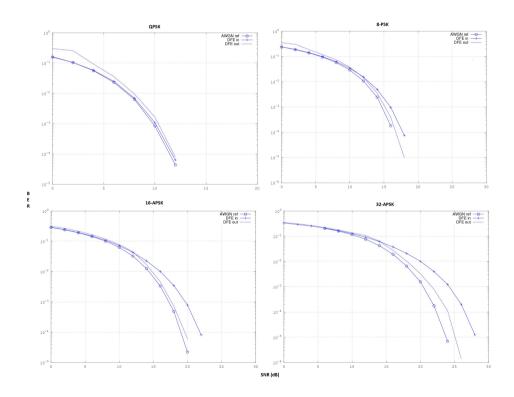

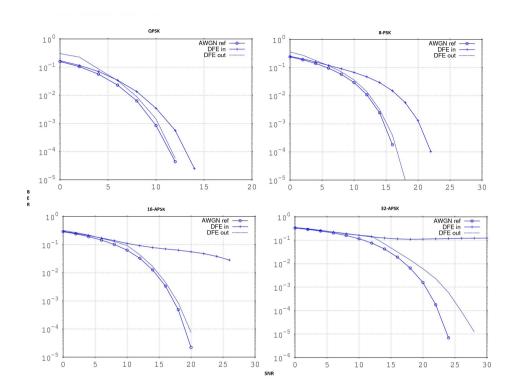

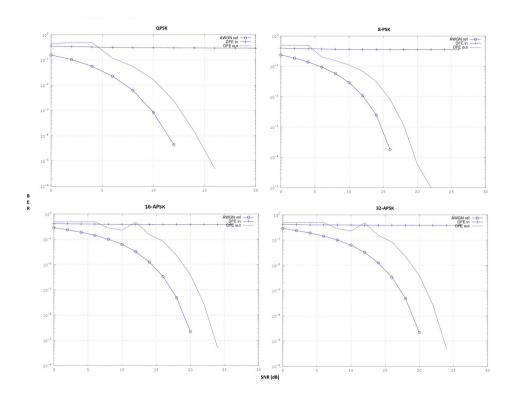

|   |     |        | 7.3.7.2       Simulation Results                                                                 |     |

|   |     |        | 7.3.7.2.2 TWTA Nonlinear Effect                                                                  |     |

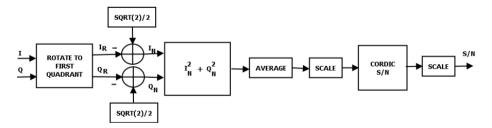

|   |     | 7.3.8  | SNR Estimator                                                                                    |     |

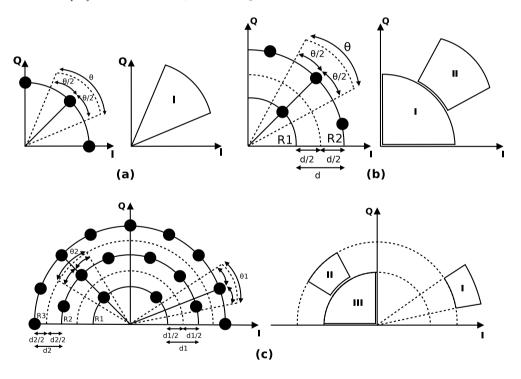

|   |     | 7.3.9  | Soft and Hard-Decision Demappers                                                                 |     |

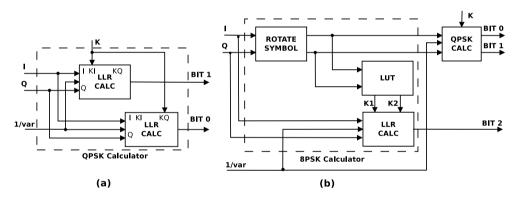

|   |     | 1.5.9  | 7.3.9.1 Hard-Decision Demapper                                                                   |     |

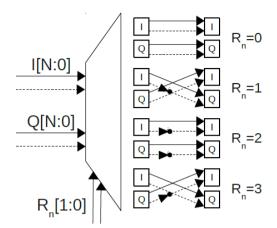

|   |     |        | 7.3.9.1         Inald-Decision Demapper           7.3.9.2         Soft Demapper (SD)             |     |

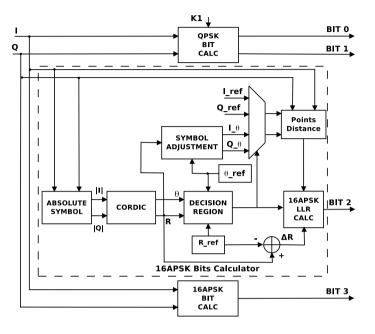

|   |     |        | 7.3.9.3     Proposed Architecture                                                                |     |

|   |     |        | 7.3.9.3.1 Hard Demapper                                                                          |     |

|   |     |        | 7.3.9.3.2 Soft Demapper                                                                          |     |

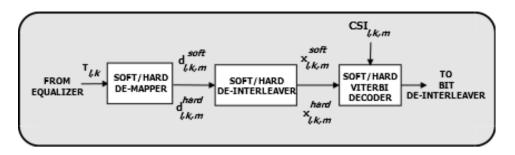

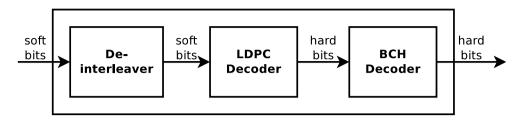

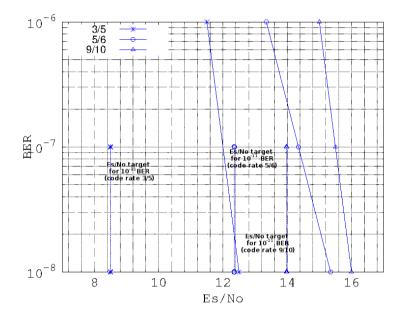

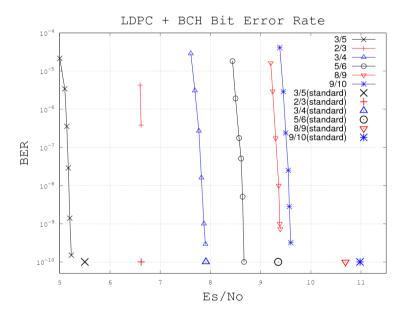

|   |     | 7310   | FEC Subsystem and BER Measurement Platform                                                       |     |

|   |     | 1.0.10 | 7.3.10.1 Deinterleaver                                                                           |     |

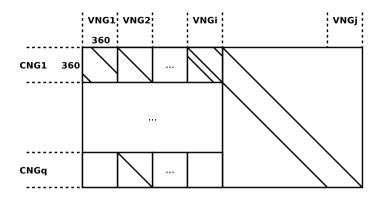

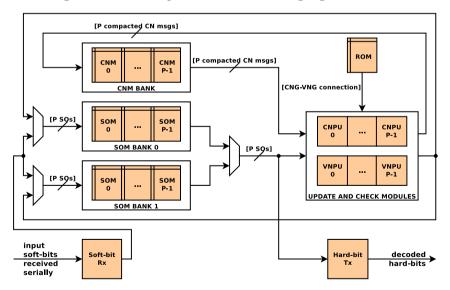

|   |     |        | 7.3.10.2 LDPC Decoder                                                                            |     |

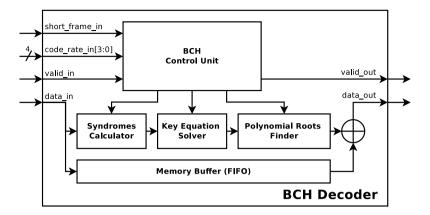

|   |     |        | 7.3.10.3 BCH Decoder                                                                             |     |

|   |     |        | 7.3.10.4 Platform for FEC Subsystem BER Measurement                                              |     |

### CONTENTS

|              | 7.4             | Conclusions                                                           | 268         |

|--------------|-----------------|-----------------------------------------------------------------------|-------------|

| 8            |                 | B-S2 Receiver: The Methodology, VLSI Implementation, FPGA             |             |

|              |                 | totype and Test Results                                               | <b>27</b> 1 |

|              | 8.1             | Introduction                                                          | 271         |

|              | 8.2             | The Methodology                                                       |             |

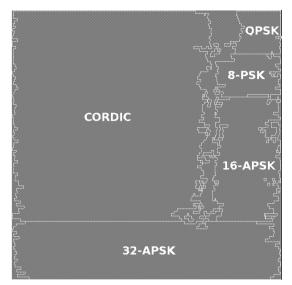

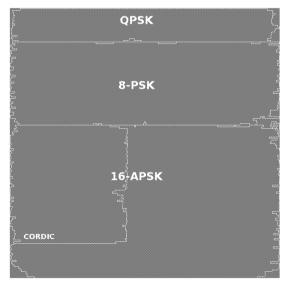

|              | 8.3             | Prototype in FPGA and VLSI Implementation in 65nm CMOS                |             |

|              |                 | 8.3.1 Full Receiver FPGA Prototyping                                  |             |

|              |                 | 8.3.2 Receiver VLSI Physical Synthesis                                |             |

|              | 8.4             | FEC FRAME Decoder: FPGA Prototype                                     | 280         |

|              | 8.5             | Soft and Hard Demappers: FPGA Prototype and VLSI Physical Syn-        | 000         |

|              |                 | thesis                                                                |             |

|              | 8.6             | Adaptive Equalizer: FPGA Prototype Results                            |             |

|              | 8.7             | Optimized Fine Frequency Estimator: FPGA Prototype Results            |             |

|              | 8.8             | Conclusions                                                           | 285         |

| 9            | Con             | clusions and Future Work                                              | 287         |

|              | 9.1             | Fundamental Understanding on the Wireless Radio Impairments           | 289         |

|              | 9.2             | Proposal of a ISDB-T Receiver Architecture and Algorithms Exploration | n290        |

|              | 9.3             | ISDB-T Receiver: VLSI Implementation, FPGA Prototype and Test         |             |

|              |                 | Results                                                               | 291         |

|              | 9.4             | Proposal of a DVB-S2 Receiver Architecture and Algorithms Exploration | n291        |

|              | 9.5             | DVB-S2 Receiver: FPGA Prototype, Early VLSI Design Exploration        |             |

|              |                 | and Test Results                                                      | 292         |

|              | 9.6             | Creating and Proving the Competences for ASIC Implementation in       |             |

|              |                 | Brazil                                                                | 293         |

|              | 9.7             | Future Works Directions                                               | 294         |

| $\mathbf{A}$ | $\mathbf{List}$ | of Publications                                                       | 297         |

| в            | Dig             | ital Terrestrial Television Around The World                          | 301         |

| 2            |                 | Digital Terrestrial Television Around The World                       |             |

|              | 2.1             | B.1.1 First Generation of Digital Television                          |             |

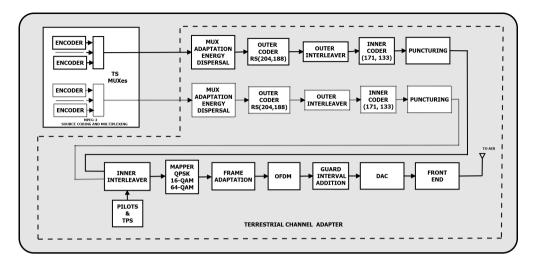

|              |                 | B.1.1.1 Digital Video Broadcasting - Terrestrial (DVB-T)              | 302         |

|              |                 | B.1.1.1.1 Mux Adaptation and PRBS Scrambling                          | 302         |

|              |                 | B.1.1.1.2 Reed Solomon Encoding                                       | 302         |

|              |                 | B.1.1.1.3 Byte-Wise Interleaving                                      |             |

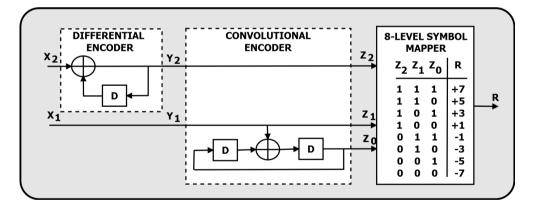

|              |                 | B.1.1.1.4 Convolutional Encoding                                      |             |

|              |                 | B.1.1.1.5 Bit and Symbol Interleaving                                 | 304         |

|              |                 | B.1.1.1.6 Constellation Mapping                                       | 308         |

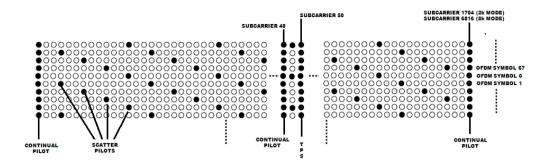

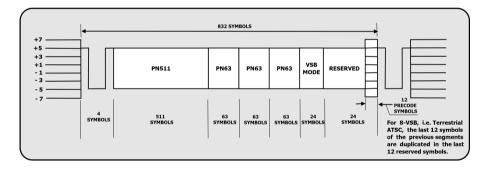

|              |                 | B.1.1.1.7 OFDM Frame Structure                                        | 311         |

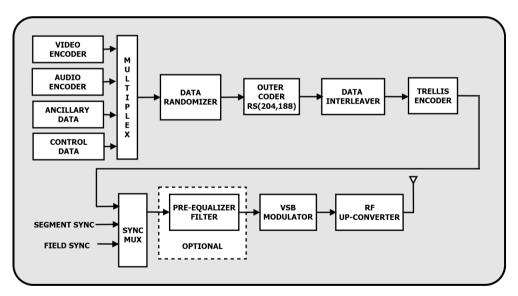

|              |                 | B.1.1.2 ATSC - Advanced Television Systems Committee Stan-            |             |

|              |                 | dards                                                                 | 316         |

|              |                 | B.1.1.2.1 Transmission Data Organization                              | 316         |

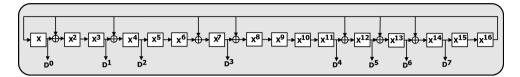

|              |                 | B.1.1.2.2 Data Randomizing                                            | 317         |

|              |                 |                                                                       |             |

| Bibliog    | raphy 3                                                               | 37         |

|------------|-----------------------------------------------------------------------|------------|

|            | C.1.2 What PNM Has Achieved So Far                                    | 335        |

|            | 8                                                                     | 335        |

|            |                                                                       | 334        |

|            |                                                                       | 334        |

|            | 0                                                                     | 332        |

| C.1        |                                                                       | 331        |

|            |                                                                       | <b>331</b> |

| <b>C C</b> | in a laster Anna in Durail                                            | 191        |

|            | B.3.2 The Future of Terrestrial DTV                                   | 329        |

|            |                                                                       | 327        |

|            |                                                                       | 327        |

| B.3        | Second Generation Digital Television and a Little About the Future of |            |

|            | B.2.4 Chinese Mobile Multimedia Broadcasting - CMMB                   | 327        |

|            |                                                                       | 326        |

|            |                                                                       | 326        |

|            | 1                                                                     | 326        |

|            |                                                                       | 325        |

|            | 8                                                                     | 325        |

|            |                                                                       | 325        |

| D.2        |                                                                       | 324<br>324 |

| Вð         |                                                                       | 323<br>324 |

|            | e e e e e e e e e e e e e e e e e e e                                 | 322        |

|            | 0 1                                                                   | 322        |

|            | 0                                                                     | 318        |

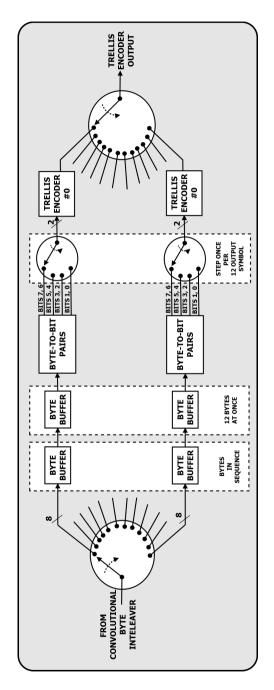

|            | B.1.1.2.5 Trellis Coding and Intrasegment Symbol In-                  |            |

|            | • 0                                                                   | 318        |

|            | 0                                                                     | 318        |

|            |                                                                       | ~          |

# List of Figures

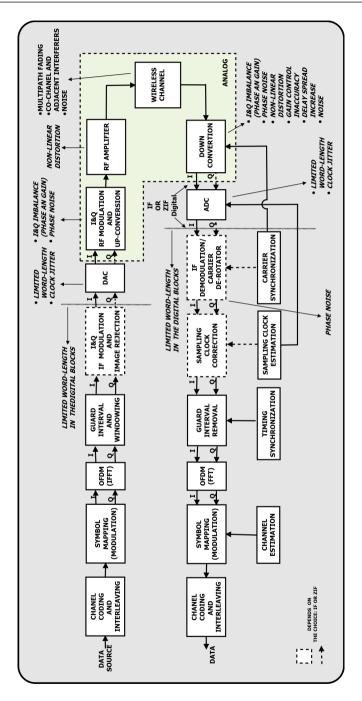

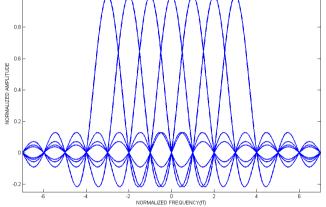

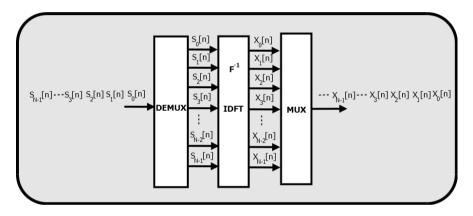

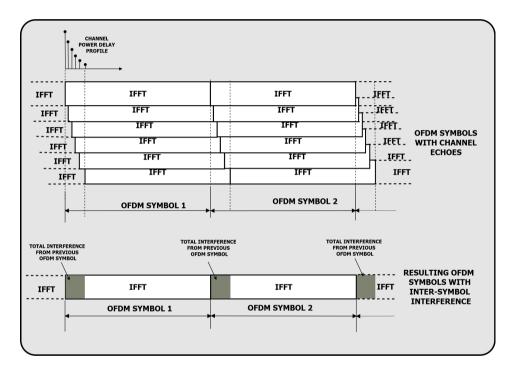

| 2.1                                                                                                  | Simplified OFDM transceiver and, radio and mixed signal impairments,                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                     |

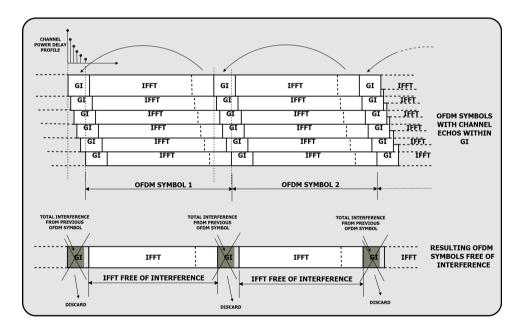

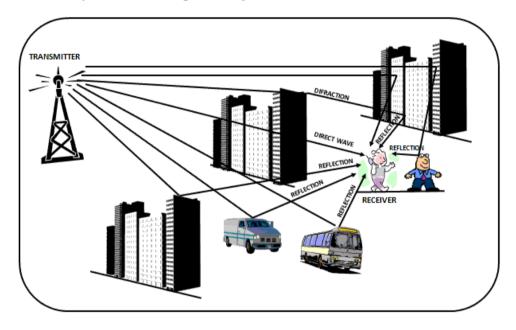

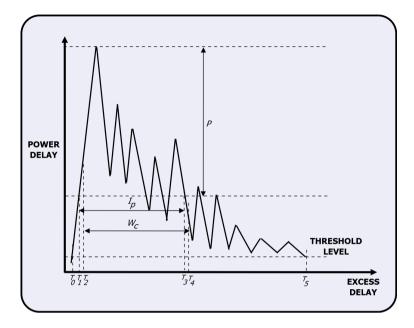

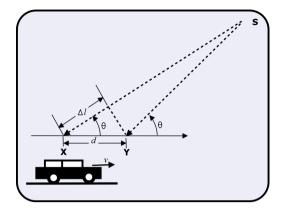

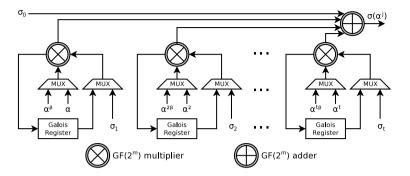

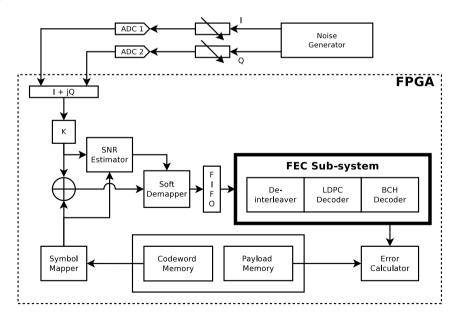

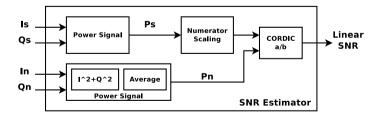

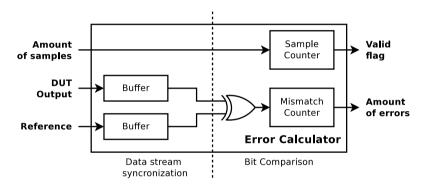

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|