# New Fault Detection, Mitigation and Injection Strategies for Current and Forthcoming Challenges of HW Embedded Designs

Jaime Espinosa Garcia

Advisors: David de Andrés Martínez, PhD Juan Carlos Ruiz Garcia, PhD

Valencia, July 2016

"The problem with the world is that the intelligent people are full of doubts, while the stupid ones are full of confidence."

Charles Bukowski

# Agraïments

Volguera començar agraïnt totes aquelles persones que han fet possible que esta tesi esdevinguera realitat. A totes aquelles persones i que m'han acompanyat durant tot este temps, amb el seu suport tècnic, lingüístic, físic, econòmic o psicològic.

Primerament, agrair els meus directors els doctors David de Andrés i Juan Carlos Ruiz per la seua dedicació, suport i ànim durant estos anys. Heu sigut de gran ajuda. També al professor Pedro Gil per confiar en mi i donar-me el recolzament econòmic i científic per portar a terme el projecte.

Així mateix, també volguera tenir unes paraules per als meus companys del grup de Sistemes Tolerants a Fallades (STF) i en especial als del laboratori: el ja doctor Jesus Friginal, Miquel Martinez, Héctor Marco, Javier Cancio i Antonio Bustos. Haveu sigut els millors, i junts hem passat molt bons moments. També agrair els companys de l'estada a Edinburgh Félix Casado i Ali Ebrahim, i molt especialment als del Barcelona Supercomputing Center Carles, Jaume, Mikel, Javi, Maria, David, Roberto, Milos, Mladen, Suzanna, Quixiao, Leonidas i la resta del grup CAOS per fer-me sentir com a casa.

Per descomptat que no només he rebut suport dels companys de recerca. Per això he d'esmentar la meua estimada Sara, per donar-me tot el suport i l'estima possibles i impossibles, i els meus pares i germans, perquè sempre han estat fentme costat i m'han animat a seguir estudiant per comprendre millor el món que ens envolta.

Finalment a les persones de la Universitat en general, i del món científic en particular, a la vocació dels quals devem que el sistema continue funcionant.

Jaume.

### Sumari

La rellevància que l'electrònica adquireix en la seguretat dels productes ha crescut inexorablement, puix cada volta més aquesta abasta una major influència en la funcionalitat dels mateixos. Però, per descomptat, aquest fet ve acompanyat d'un constant necessitat de majors prestacions per acomplir els requeriments funcionals, mentre es mantenen els costos i consums en uns nivells reduïts. Donat aquest escenari, la indústria està fent esforços per proveir una tecnologia que complisca amb totes les especificacions de potència, consum i preu, tot a costa d'un increment en la vulnerabilitat a diversos tipus de fallades conegudes, i a la introducció de nous tipus.

Per oferir una solució a les noves i creixents fallades als sistemes, els dissenyadors han recorregut a tècniques tradicionalment associades a sistemes crítics per a la seguretat, que en general oferixen resultats sub-òptims. De fet, les arquitectures empotrades modernes oferixen la possibilitat d'optimitzar les propietats de confiabilitat en habilitar la interacció dels nivells de hardware, firmware i software en el procés. Tot i això eixe punt no està resolt encara. Es necessiten avanços a tots els nivells en l'esmentada direcció per poder assolir els objectius d'una tolerància a fallades flexible, robusta, resilient i a baix cost. El treball ací presentat se centra en el nivell de hardware, amb la consideració de fons d'una potencial integració en una estratègia holística.

Els esforços d'esta tesi s'han centrat en els següents aspectes: (i) la introducció de models de fallada addicionals requerits per a la representació adequada d'efectes físics que apareixen en les tecnologies de fabricació actuals, (ii) la provisió de ferramentes i mètodes per a la injecció eficient del models proposats i dels clàssics, (iii) l'anàlisi del mètode òptim per estudiar la robustesa de sistemes mitjançant l'ús d'injecció de fallades extensiva, i la posterior correlació amb capes de més alt nivell en un esforç per retallar el temps i cost de desenvolupament, (iv) la provisió de nous mètodes de detecció per cobrir els reptes plantejats pels models de fallades proposats, (v) la proposta d'estratègies de mitigació enfocades cap al tractament dels esmentats escenaris d'amenaça i (vi) la introducció d'una metodologia automatitzada de desplegament de diversos mecanismes de tolerància a fallades de forma robusta i sistemàtica.

Els resultats de la present tesi constitueixen un conjunt de ferramentes i mètodes per ajudar el dissenyador de sistemes crítics en la seua tasca de desenvolupament de dissenys robustos, validats i a temps adaptats a la seua aplicació.

## Sumario

La relevancia que la electrónica adquiere en la seguridad de los productos ha crecido inexorablemente, puesto que cada vez ésta copa una mayor influencia en la funcionalidad de los mismos. Pero, por supuesto, este hecho viene acompañado de una necesidad constante de mayores prestaciones para cumplir con los requerimientos funcionales, al tiempo que se mantienen los costes y el consumo en unos niveles reducidos. En este escenario, la industria está realizando esfuerzos para proveer una tecnología que cumpla con todas las especificaciones de potencia, consumo y precio, a costa de un incremento en la vulnerabilidad a múltiples tipos de fallos conocidos o la introducción de nuevos.

Para ofrecer una solución a los fallos nuevos y crecientes en los sistemas, los diseñadores han recurrido a técnicas tradicionalmente asociadas a sistemas críticos para la seguridad, que ofrecen en general resultados sub-óptimos. De hecho, las arquitecturas empotradas modernas ofrecen la posibilidad de optimizar las propiedades de confiabilidad al habilitar la interacción de los niveles de hardware, firmware y software en el proceso. No obstante, ese punto no está resulto todavía. Se necesitan avances en todos los niveles en la mencionada dirección para poder alcanzar los objetivos de una tolerancia a fallos flexible, robusta, resiliente y a bajo coste. El trabajo presentado aquí se centra en el nivel de hardware, con la consideración de fondo de una potencial integración en una estrategia holística.

Los esfuerzos de esta tesis se han centrado en los siguientes aspectos: (i) la introducción de modelos de fallo adicionales requeridos para la representación adecuada de efectos físicos surgentes en las tecnologías de manufactura actuales, (ii) la provisión de herramientas y métodos para la inyección eficiente de los modelos propuestos y de los clásicos, (iii) el análisis del método óptimo para estudiar la robustez de sistemas mediante el uso de inyección de fallos extensiva, y la posterior correlación con capas de más alto nivel en un esfuerzo por recortar el tiempo y coste de desarrollo, (iv) la provisión de nuevos métodos de detección para cubrir los retos planteados por los modelos de fallo propuestos, (v) la propuesta de estrategias de mitigación enfocadas hacia el tratamiento de dichos escenarios de amenaza y (vi) la introducción de una metodología automatizada de despliegue de diversos mecanismos de tolerancia a fallos de forma robusta y sistemática.

Los resultados de la presente tesis constituyen un conjunto de herramientas y métodos para ayudar al diseñador de sistemas críticos en su tarea de desarrollo de diseños robustos, validados y en tiempo adaptados a su aplicación.

## Abstract

Relevance of electronics towards safety of common devices has only been growing, as an ever growing stake of the functionality is assigned to them. But of course, this comes along the constant need for higher performances to fulfill such functionality requirements, while keeping power and budget low. In this scenario, industry is struggling to provide a technology which meets all the performance, power and price specifications, at the cost of an increased vulnerability to several types of known faults or the appearance of new ones.

To provide a solution for the new and growing faults in the systems, designers have been using traditional techniques from safety-critical applications, which offer in general suboptimal results. In fact, modern embedded architectures offer the possibility of optimizing the dependability properties by enabling the interaction of hardware, firmware and software levels in the process. However, that point is not yet successfully achieved. Advances in every level towards that direction are much needed if flexible, robust, resilient and cost effective fault tolerance is desired. The work presented here focuses on the hardware level, with the background consideration of a potential integration into a holistic approach.

The efforts in this thesis have focused several issues: (i) to introduce additional fault models as required for adequate representativity of physical effects blooming in modern manufacturing technologies, (ii) to provide tools and methods to efficiently inject both the proposed models and classical ones, (iii) to analyze the optimum method for assessing the robustness of the systems by using extensive fault injection and later correlation with higher level layers in an effort to cut development time and cost, (iv) to provide new detection methodologies to cope with challenges modeled by proposed fault models, (v) to propose mitigation strategies focused towards tackling such new threat scenarios and (vi) to devise an automated methodology for the deployment of many fault tolerance mechanisms in a systematic robust way.

The outcomes of the thesis constitute a suite of tools and methods to help the designer of critical systems in his task to develop robust, validated, and on-time designs tailored to his application.

# Contents

| Agraïments                           | v   |

|--------------------------------------|-----|

| Sumari                               | vii |

| Sumario                              | ix  |

| Abstract                             | xi  |

| 1 Introduction                       | 1   |

| 1.1 Motivation                       | 1   |

| 1.2 Objectives                       | 4   |

| 1.3 Structure of the thesis          | 5   |

| 2 Faults Modeling                    | 9   |

| 2.1 Pathology                        | 9   |

| 2.2 Manifestation                    | 10  |

| 2.3 Propagation                      | 13  |

| 2.4 Modeling                         | 15  |

| 2.5 Summary                          | 18  |

| 3 Fault Injection                    | 19  |

| 3.1 Introduction                     | 19  |

| 3.1.1 Fault space: what, where, when | 20  |

| 3.1.2 Properties of fault injection  | 21  |

| 3.2 Injection methodologies                    | 22 |

|------------------------------------------------|----|

| 3.2.1 Physical fault injection methods         | 22 |

| 3.2.2 Software-based fault injection methods   | 23 |

| 3.2.3 Emulation-based fault injection methods  | 23 |

| 3.2.4 Simulation-based fault injection methods | 24 |

| 3.2.5 Analysis of injection results            | 24 |

| 3.2.6 Summary of methods                       | 25 |

| 3.3 Injection tools                            | 25 |

| 3.3.1 Physical fault injection tools           | 26 |

| 3.3.2 SWIFI tools                              | 26 |

| 3.3.3 Emulation-based injection tools          | 27 |

| 3.3.4 Simulation-based injection tools         | 28 |

| 3.4 The FALLES Tool                            | 29 |

| 3.4.1 Presentation                             | 29 |

| 3.4.2 Detailed operation                       | 30 |

| 3.4.3 Analysis in FALLES                       | 34 |

| 3.5 Summary                                    | 36 |

|                                                |    |

| 4 Dependability Assessment                     | 37 |

| 4.1 Introduction                               | 37 |

| 4.2 Analysis of injection results              | 38 |

| 4.3 Multi-level correlation                    | 40 |

| 4.4 Summary                                    | 42 |

|                                                | 40 |

| 5 Fault Tolerance Mechanisms                   | 43 |

| 5.1 Detection                                  | 43 |

| 5.2 Error handling                             | 46 |

| 5.3 Fault diagnosis                            | 47 |

| 5.4 Fault recovery                             | 48 |

| 5.5 Summary                                    | 48 |

| 6 Discussion and Conclusions                   | 51 |

|                                                | -  |

| 6.1 Discussion                                 | 51 |

| 6.1.1 Fault models                             | 52 |

| 6.1.2 Fault injections                         | 53 |

| 6.1.3 Dependability assessment                                                                                                                                                                                                                                                                                                                                                                       | 54                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 6.1.4 Fault Tolerance mechanisms                                                                                                                                                                                                                                                                                                                                                                     | 54                                                                  |

| 6.1.5 Fault tolerance implementation                                                                                                                                                                                                                                                                                                                                                                 | 56                                                                  |

| 6.2 Conclusion                                                                                                                                                                                                                                                                                                                                                                                       | 56                                                                  |

| 6.3 Future work                                                                                                                                                                                                                                                                                                                                                                                      | 59                                                                  |

| 7 Summary of contributions                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                  |

| 7.1 Publications                                                                                                                                                                                                                                                                                                                                                                                     | 61                                                                  |

| 7.1.1 Conferences                                                                                                                                                                                                                                                                                                                                                                                    | 61                                                                  |

| 7.1.2 Journals                                                                                                                                                                                                                                                                                                                                                                                       | 63                                                                  |

| 7.1.3 Book chapters                                                                                                                                                                                                                                                                                                                                                                                  | 63                                                                  |

| 7.2 Framework of the Dissertation                                                                                                                                                                                                                                                                                                                                                                    | 63                                                                  |

| 7.2.1 Research projects                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                  |

| 7.2.2 International research stays                                                                                                                                                                                                                                                                                                                                                                   | 64                                                                  |

| 7.2.3 Collaborations                                                                                                                                                                                                                                                                                                                                                                                 | 64                                                                  |

| 7.3 Awards                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                     |

| Appendices                                                                                                                                                                                                                                                                                                                                                                                           | 67                                                                  |

| Appendices<br>A Tolerating multiple faults with proximate manifestations i<br>FPGA-based critical designs for harsh environments                                                                                                                                                                                                                                                                     |                                                                     |

| A Tolerating multiple faults with proximate manifestations i                                                                                                                                                                                                                                                                                                                                         | n<br>69                                                             |

| A Tolerating multiple faults with proximate manifestations i<br>FPGA-based critical designs for harsh environments                                                                                                                                                                                                                                                                                   | n<br>69<br>70                                                       |

| A Tolerating multiple faults with proximate manifestations i<br>FPGA-based critical designs for harsh environments<br>A.1 Introduction                                                                                                                                                                                                                                                               | n<br>69<br>70<br>71                                                 |

| A Tolerating multiple faults with proximate manifestations i<br>FPGA-based critical designs for harsh environments<br>A.1 Introduction                                                                                                                                                                                                                                                               | n<br>69<br>70<br>71<br>73                                           |

| A Tolerating multiple faults with proximate manifestations i<br>FPGA-based critical designs for harsh environments<br>A.1 Introduction                                                                                                                                                                                                                                                               | n<br>69<br>70<br>71<br>73<br>74                                     |

| A Tolerating multiple faults with proximate manifestations i<br>FPGA-based critical designs for harsh environments<br>A.1 Introduction                                                                                                                                                                                                                                                               | n<br>69<br>70<br>71<br>73<br>74<br>74                               |

| A Tolerating multiple faults with proximate manifestations i<br>FPGA-based critical designs for harsh environments<br>A.1 Introduction                                                                                                                                                                                                                                                               | n<br>69<br>70<br>71<br>73<br>74<br>74<br>75                         |

| A Tolerating multiple faults with proximate manifestations i         FPGA-based critical designs for harsh environments         A.1 Introduction         A.2 Faults in SRAM FPGAs         A.3 Fault tolerance for FPGA-based designs         A.4 A multiple fault tolerance approach         A.4.1 Global architecture         A.4.2 Detailed description                                            | n<br>69<br>70<br>71<br>73<br>74<br>74<br>75<br>77                   |

| A Tolerating multiple faults with proximate manifestations i         FPGA-based critical designs for harsh environments         A.1 Introduction         A.2 Faults in SRAM FPGAs         A.3 Fault tolerance for FPGA-based designs         A.4 A multiple fault tolerance approach         A.4.1 Global architecture         A.4.2 Detailed description         A.4.3 Design of the FSM controller | n<br>69<br>70<br>71<br>73<br>74<br>74<br>75<br>77<br>80             |

| A Tolerating multiple faults with proximate manifestations i         FPGA-based critical designs for harsh environments         A.1 Introduction         A.2 Faults in SRAM FPGAs         A.3 Fault tolerance for FPGA-based designs         A.4 A multiple fault tolerance approach         A.4.1 Global architecture         A.4.2 Detailed description         A.4.3 Design of the FSM controller | n<br>69<br>70<br>71<br>73<br>74<br>74<br>74<br>75<br>77<br>80<br>81 |

| B The Challenge of Detection and Diagnosis of Fugacious Hard-                                   |     |

|-------------------------------------------------------------------------------------------------|-----|

| ware Faults in VLSI Designs                                                                     | 85  |

| B.1 Introduction                                                                                | 86  |

| B.2 The problem of Fast Fault Detection and Diagnosis                                           | 87  |

| B.2.1 On-line detection of faults and errors                                                    | 88  |

| B.2.2 Considered fault models                                                                   | 90  |

| B.2.3 Fault diagnosis                                                                           | 90  |

| B.3 Solutions for detection and diagnosis                                                       | 91  |

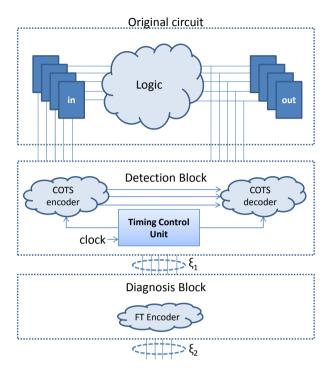

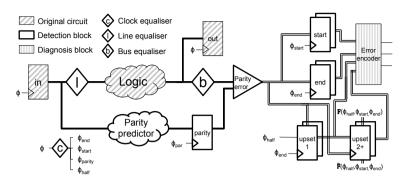

| B.3.1 Architecture of a faults detection and discrimination system                              | 91  |

| B.3.2 Workflow to apply in the proposed technique                                               | 94  |

| B.4 Ongoing Work                                                                                | 95  |

| C Increasing the Dependability of VLSI Systems Through Early                                    |     |

| Detection of Fugacious Faults                                                                   | 97  |

| C.1 Introduction                                                                                | 98  |

| C.2 Fugacious fault models                                                                      | 100 |

| C.3 Novel architecture for detecting and diagnosing fugacious faults                            | 102 |

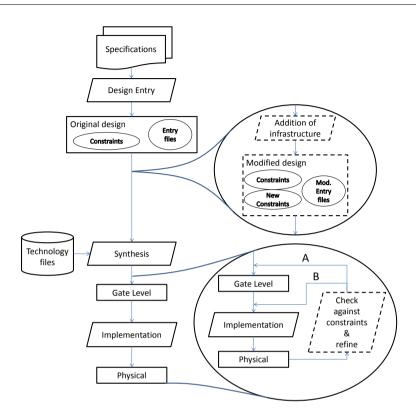

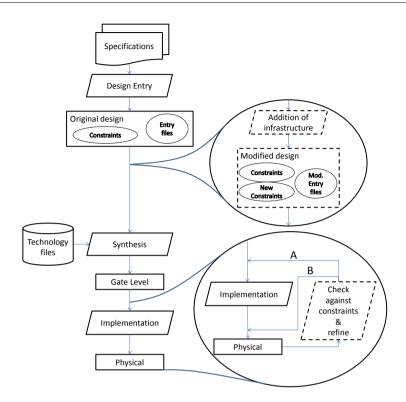

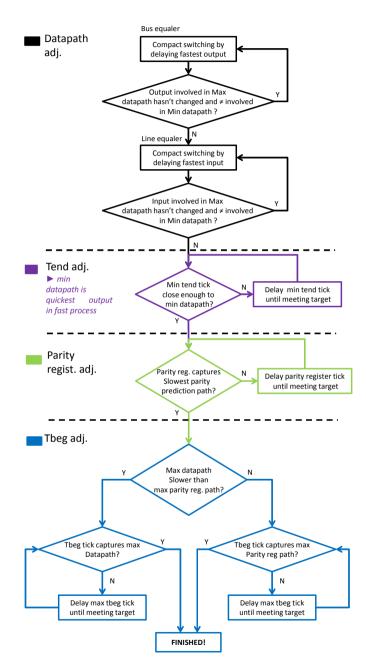

| C.4 Proposed implementation flow                                                                | 104 |

| C.5 First prototype and case study                                                              | 108 |

| C.6 Results and discussion                                                                      | 110 |

| C.7 Conclusions                                                                                 | 112 |

| D An Aspect-oriented Approach to Hardware Fault Tolerance                                       |     |

| for Embedded Systems                                                                            | 115 |

| D.1 Introduction                                                                                | 116 |

| D.2 Related Work                                                                                | 118 |

| D.2.1 Metaprogramming and aspect orientation                                                    | 118 |

| D.2.2 Hardware fault and intrusion tolerance automation                                         | 119 |

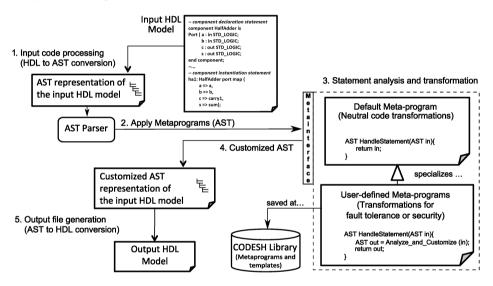

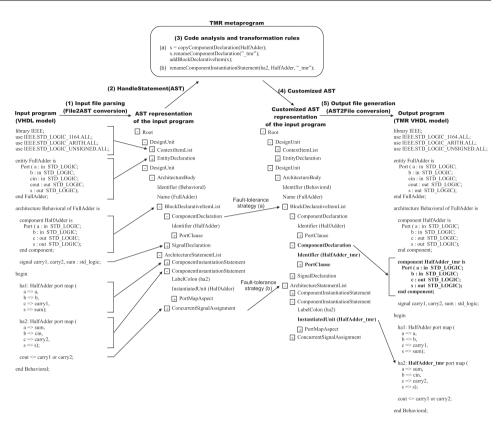

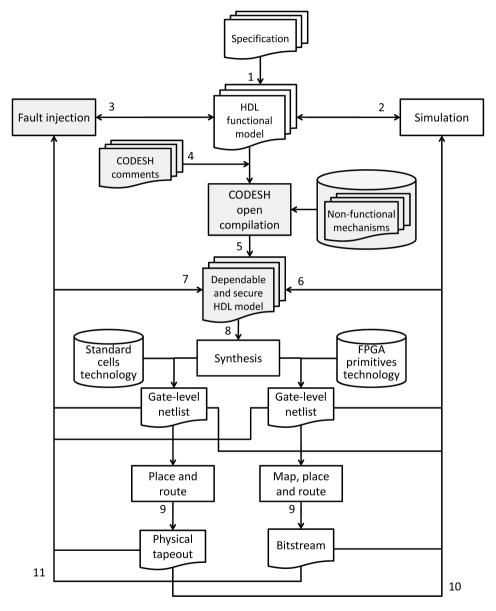

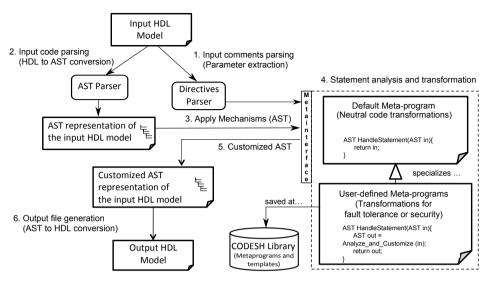

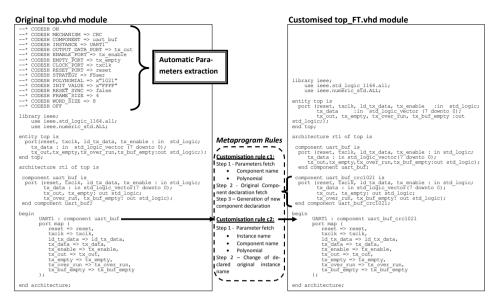

| D.3 Metaprogramming the design of dependable and secure HDL-based embedded systems              | 121 |

| D.3.1 Open compilation to support the customization of hardware systems                         | 122 |

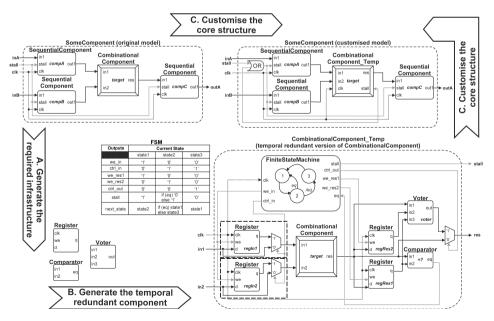

| D.3.2 Architecting hardware fault tolerance mechanisms as metaprograms                          | 124 |

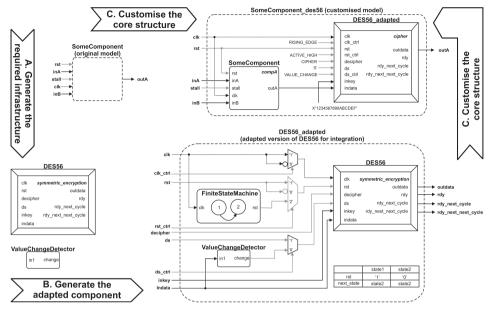

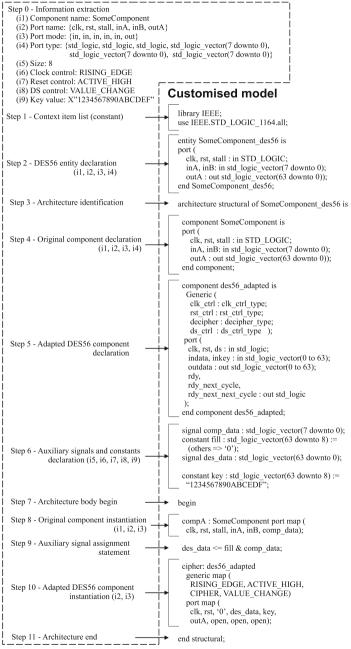

| D.3.3 Integration within the regular hardware design flow                                       | 126 |

| D.4 Dealing with white and black box IP cores as case studies $\ldots \ldots \ldots \ldots$     | 128 |

| D.4.1 White box IP cores: tolerating transient faults via temporal redundancy $% \mathcal{D}$ . | 129 |

|     |     | $\mathrm{D.4.2}$ Black box IP cores: integrating third party cores for symmetric encryption | 132 |

|-----|-----|---------------------------------------------------------------------------------------------|-----|

| Ι   | D.5 | Analysis of Results and Discussion                                                          | 136 |

|     |     | D.5.1 Experimental setup                                                                    | 138 |

|     |     | D.5.2 Analysis of results                                                                   | 138 |

| Ι   | D.6 | Conclusions and Open Challenges                                                             | 141 |

| ΕF  | Roł | oust communications using automatic deployment of a CRC-                                    |     |

|     |     |                                                                                             | 145 |

| I   | E.1 | Introduction                                                                                | 146 |

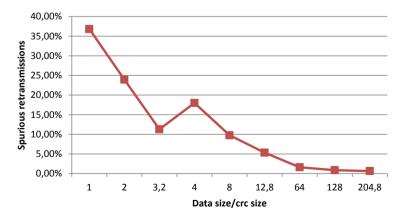

| I   | E.2 | Research context                                                                            | 147 |

|     |     | E.2.1 CRCs and fault tolerance.                                                             | 147 |

|     |     | E.2.2 Metaprograms and open compilation                                                     | 148 |

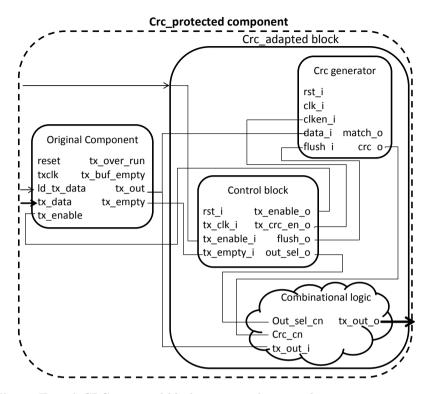

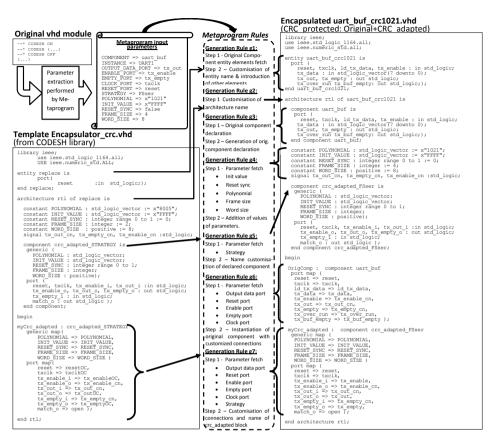

| Ι   | E.3 | CRC as a metaprogram.                                                                       | 149 |

|     |     | E.3.1 Phase 1: Infrastructure generation                                                    | 149 |

|     |     | E.3.2 Phase 2: Component encapsulation                                                      | 151 |

|     |     | E.3.3 Phase 3: Component integration                                                        | 152 |

|     |     | E.3.4 Bridging mechanism deployment and VHDL coding                                         | 152 |

| Ι   | E.4 | Case study                                                                                  | 153 |

|     |     | E.4.1 CRC-protected UART transmitter                                                        | 153 |

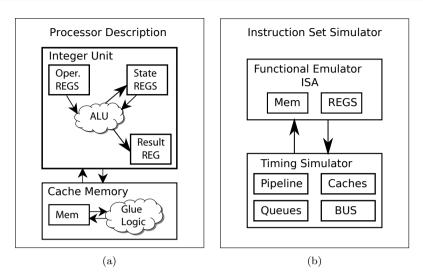

|     |     | E.4.2 Faultload                                                                             | 153 |

|     |     | E.4.3 Experimental procedure.                                                               | 154 |

| I   | E.5 | Results and discussion                                                                      | 155 |

| I   | E.6 | Conclusions                                                                                 | 157 |

| ΓΊ  | Гov | vards Certification-aware Fault Injection Methodologies Us-                                 |     |

| ing | Vi  | rtual Prototypes                                                                            | 159 |

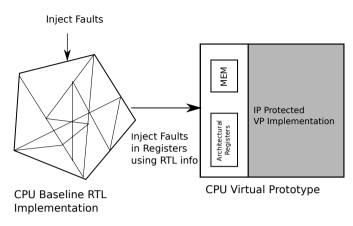

| I   | F.1 | Introduction                                                                                | 160 |

| I   | F.2 | Related Work                                                                                | 161 |

| I   | F.3 | Certification-Aware Fault Injection in Virtual prototypes                                   | 162 |

|     |     | F.3.1 Characterizing Fault behaviour at RTL level                                           | 162 |

|     |     | F.3.2 Fault injection at Virtual prototypes                                                 | 163 |

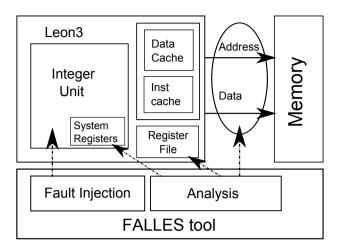

| I   | F.4 | FALLES: Fault injection and Analysis for Low Level Evaluation Suite                         | 164 |

| I   | F.5 | Experimental Results                                                                        | 164 |

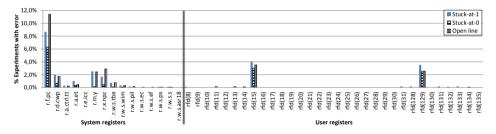

|     |     | F.5.1 Experimental Setup                                                                    | 165 |

|     |     | F.5.2 Results                                                                               | 166 |

| F.6 Conclusions                                                                                                       | 167       |

|-----------------------------------------------------------------------------------------------------------------------|-----------|

| G Analysis and RTL Correlation of Instruction Set Simulator<br>for Automotive Microcontroller Robustness Verification | s<br>169  |

| G.1 Introduction                                                                                                      | 170       |

| G.2 Towards Simulation-based Robustness Verification                                                                  | 171       |

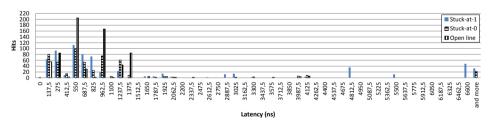

| G.2.1 Fault injection at the RTL                                                                                      | 172       |

| G.2.2 Fault injection at the ISS Level                                                                                | 173       |

| G.2.3 ISS-based Verification                                                                                          | 173       |

| G.3 Correlating RTL with ISS fault injection                                                                          | 175       |

| G.4 Experimental Validation                                                                                           | 177       |

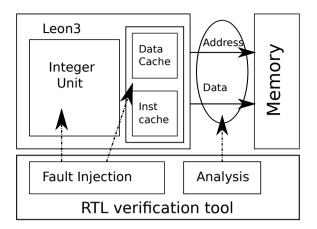

| G.4.1 Experimental Setup                                                                                              | 177       |

| G.4.2 Experimental Results                                                                                            | 178       |

| G.5 Related Work                                                                                                      | 182       |

| G.6 Conclusions                                                                                                       | 183       |

| H Characterizing Fault Propagation in Safety-Critical Processo<br>Designs                                             | or<br>185 |

| H.1 Introduction                                                                                                      | 186       |

| H.2 Background on Simulation-based Robustness Verification                                                            | 187       |

| H.2.1 Fault injection at the RTL                                                                                      | 189       |

| H.2.2 Fault injection at the ISS Level                                                                                | 189       |

| H.3 Characterizing Fault Propagation                                                                                  | 190       |

| H.4 Experimental Results                                                                                              | 192       |

| H.4.1 Experimental Setup                                                                                              | 192       |

| H.4.2 Results                                                                                                         | 193       |

| H.5 Conclusions                                                                                                       | 196       |

| Bibliography                                                                                                          | 199       |

# List of Figures

| 1.1 | Factors of dependability: fault, error, failure chain                                                                                | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Pathology of permanent faults [66]                                                                                                   | 11 |

| 2.2 | Pathology of transient faults [66]                                                                                                   | 11 |

| 2.3 | Pathologies of faults manifested as intermittent [69]                                                                                | 12 |

| 2.4 | Electrical filtering effect                                                                                                          | 14 |

| 2.5 | Logical filtering effect                                                                                                             | 15 |

| 2.6 | Temporal filtering effect                                                                                                            | 15 |

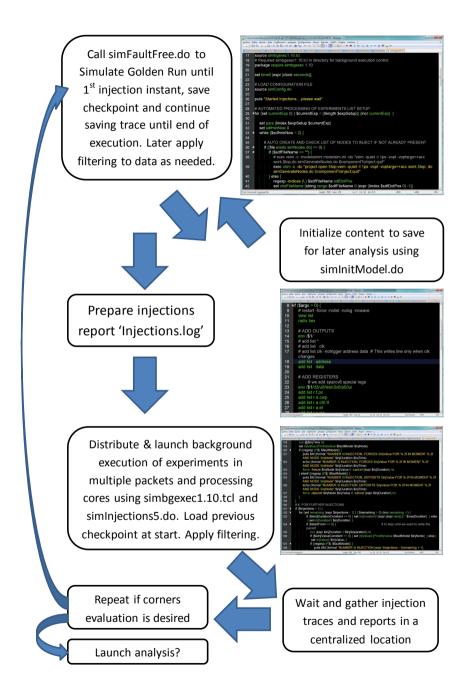

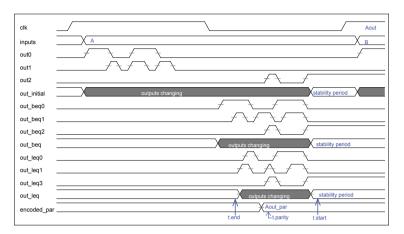

| 3.1 | Workflow for FALLES, part1                                                                                                           | 32 |

| 3.2 | Workflow for FALLES, part2                                                                                                           | 33 |

| 3.3 | Latency analysis and error count in FALLES                                                                                           | 35 |

| A.1 | Global architecture of the proposed fault masking and correction mechanism.                                                          | 75 |

| A.2 | Detailed architecture of the proposed approach                                                                                       | 76 |

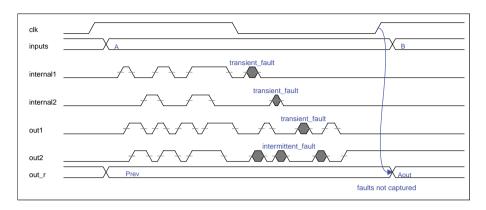

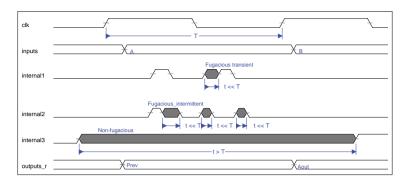

| B.1 | Temporal filtering of fugacious faults                                                                                               | 89 |

| B.2 | Global scheme of the faults detection and diagnosis infrastructure. Timing Control Unit handles temporisation of Detection decoder . | 92 |

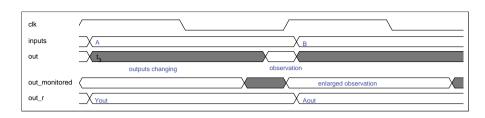

| B.3 | Observation window enlarged by means of reducing period of signal switching                                                                        | 93  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| B.4 | Tools interaction                                                                                                                                  | 94  |

| C.1 | Characterisation of fugacious faults                                                                                                               | 99  |

| C.2 | Low level schematic implementation of the proposed detection and diagnosis architecture                                                            | 101 |

| C.3 | Proposed implementation flow                                                                                                                       | 105 |

| C.4 | Control flow for stretching the observation window $\ldots \ldots \ldots$                                                                          | 106 |

| C.5 | Stretching the observation window step by step $\ldots \ldots \ldots \ldots$                                                                       | 107 |

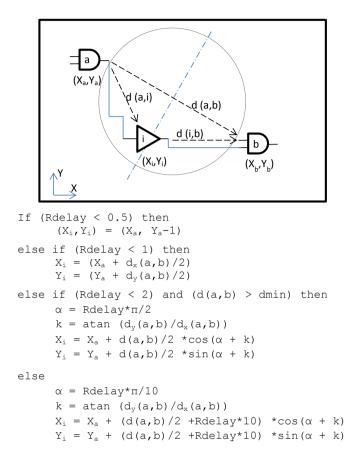

| C.6 | Strategy for locating delay pass-through elements $(X_i, Y_i)$ , showing physical distances inside device. Delays are expressed in relative units. | 109 |

| D.1 | Open compilation process defined by CODESH                                                                                                         | 122 |

| D.2 | CODESH Open compilation process in action: a TMR case $\ . \ . \ .$                                                                                | 124 |

| D.3 | Integrating the proposed open compilation process into the regular hardware design flow                                                            | 127 |

| D.4 | Metaprogramming temporal redundancy                                                                                                                | 129 |

| D.5 | Metaprogramming the integration of a third party core providing symmetric data encryption into a given model                                       | 134 |

| D.6 | Metaprogram generation rule required to integrate the symmetric data encryption third party component.                                             | 137 |

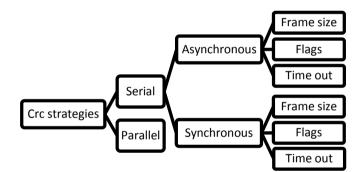

| E.1 | Transmission CRC strategies                                                                                                                        | 147 |

| E.2 | CODESH workflow                                                                                                                                    | 149 |

| E.3 | A CRC-protected block structure showing relevant interconnections                                                                                  | 150 |

| E.4 | Phase 2, encapsulation of the new CRC-protected component using template                                                                           | 151 |

| E.5 | Phase 3, integration of the CRC-protected component into the tar-<br>get system.                                                                   | 152 |

| E.6 | Relation between the spurious retransmission rate and the data/CRC size ratio                                                                   | 155  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

| F.1 | Proposed methodology                                                                                                                            | 162  |

| F.2 | RTL robustness verification framework                                                                                                           | 165  |

| F.3 | Errors distribution in system and user registers, ttsprk $\hdots$                                                                               | 166  |

| F.4 | Histogram of propagation latencies from error to failure, ttsprk $\ .$ .                                                                        | 166  |

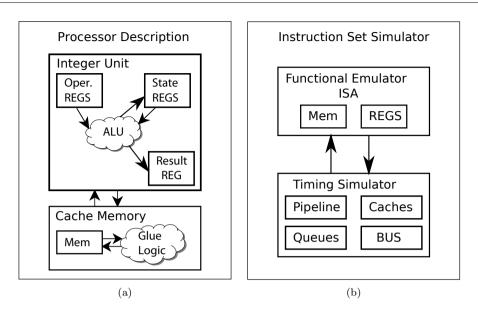

| G.1 | (a) RTL processor description (b) Microarchitectural processor de-<br>scription                                                                 | 172  |

| G.2 | RTL robustness verification framework                                                                                                           | 177  |

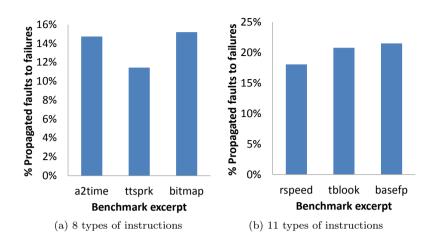

| G.3 | Input data variation in 2 sets of benchmark excerpts with uniform instruction types and numbers, using stuck-at-1 injections at integer unit    | 180  |

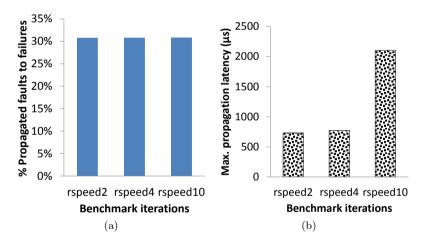

| G.4 | Input data variation impact analyzed with 2, 4, and 10 full iterations of benchmark rspeed using stuck-at-1 injections at integer unit $\ldots$ | 180  |

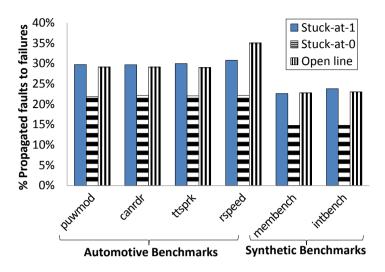

| G.5 | Fault injection experiments for different benchmarks and fault models at IU nodes                                                               | 181  |

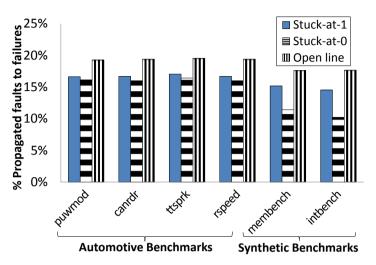

| G.6 | Fault injection experiments for different benchmarks and fault models at CMEM nodes.                                                            | 182  |

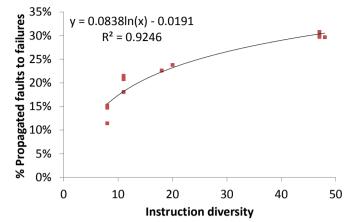

| G.7 | Propagated faults in terms of instruction diversity for the stuck-at-1 model in IU                                                              | 183  |

| H.1 | (a) RTL processor description (b) Microarchitectural processor de-<br>scription                                                                 | 188  |

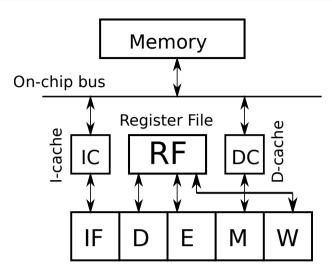

| H.2 | Generic processor pipeline scheme. IF (instruction fetch), D (de-<br>code), E (execution), M (Memory), W (Write-back)                           | 191  |

| H.3 | RTL robustness verification framework                                                                                                           | 193  |

| H.4 | Percentage of failures in the experiments according to whether they caused a prior error or not.                                                | 194  |

| H.5 | Percentage of experiments which cause 1 or more errors in the registers                                                                         | s195 |

| H.6 | Errors distribution    | n in system | and user | registers for | different bench- |     |

|-----|------------------------|-------------|----------|---------------|------------------|-----|

|     | marks $\ldots\ldots$ . |             |          |               |                  | 196 |

# List of Tables

| 2.1 | Considered combinations of faults with proximate manifestation                                           | 17  |

|-----|----------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Evaluation of properties of different injection methodologies                                            | 25  |

| 3.2 | Fault models currently supported by FALLES                                                               | 29  |

| 4.1 | SIL levels for systems occasionally used                                                                 | 39  |

| 4.2 | SIL levels for systems in continuous use                                                                 | 39  |

| A.1 | Considered single fault models                                                                           | 71  |

| A.2 | Considered multiple fault models                                                                         | 72  |

| A.3 | Considered scenarios and combination of faults $\ldots \ldots \ldots \ldots$                             | 79  |

| A.4 | TMR-MDR approach coverage                                                                                | 82  |

| A.5 | Temporal intrusion of the TMR-MDR approach                                                               | 83  |

| A.6 | Area required and clock period attained by the original, the eTMR and the TMR-MDR versions of the target | 84  |

| C.1 | Diagnosis of fugacious faults $^{*}$                                                                     | 103 |

| C.2 | Minimum width of fugacious transient faults for correct detection .                                      | 110 |

| C.3 | Minimum inactive time of intermittent fugacious faults for correct detection                             | 110 |

| C.4 | Check all diagnosis cases in all eligible fault injection points $\ . \ . \ .$                           | 111 |

| C.5 | Overhead induced in terms of area and clock period                                                                                                   | 112 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| D.1 | Metaprogram interface (a) and transformation rules (b) required to insert the new component into the original model (customize the core structure)   | 133 |

| D.2 | Comparison of the original (PIC), temporally redundant (TR), and secured (DES) cores in terms of failures, area, throughput, and energy consumption. | 139 |

| E.1 | Number of experiments for the selected configurations $\ldots \ldots \ldots$                                                                         | 154 |

| E.2 | Results for single bit faults                                                                                                                        | 155 |

| E.3 | Results for 16-bits burst faults                                                                                                                     | 156 |

| E.4 | Results for multiple bit faults: HD $\ldots$                                                                                                         | 156 |

| E.5 | Results for multiple bit faults: HW                                                                                                                  | 156 |

| G.1 | Benchmarks characterization                                                                                                                          | 178 |

### Chapter 1

# Introduction

1.1

Motivation

1.3

Structure of the thesis

1.2 Objectives

A general introduction and background of the work is presented here alongside summarized points of motivation, goals and structure of the thesis.

### 1.1 Motivation

Embedded systems are becoming more and more ubiquitous in everyday life, just as computers did in recent years. For that reason, development of new foundation technology and applications for them has never stopped, what also brings a whole new set of challenges to tackle in several domains. In the present thesis the challenges covered are those related mainly to hardware aspects of dependability, with some additional hints on the security side these entail.

Dependability is defined as the justified confidence that can be placed in a service or function to be delivered correctly by a system to its user, be it another system or a human being. Security, while related to dependability, is defined as the capability to provide service to authorized requests while avoiding the provision of information to unauthorized ones and ensuring no undesired system or information alterations have occurred. Because not always correct service is delivered, the causes and consequences of deviations from the expected function receive the name of factors of dependability: faults, errors and failures.

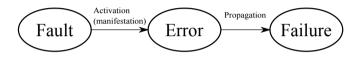

Faults are physical defects in hardware like a short-circuit or external events such as radiation (or mistakes in software functions) provoking errors, i.e. deviations from correct values in electrical nodes (which in turn affect data), and failures are the lack of delivery of expected outputs, or the delivery of incorrect ones as a consequence of errors. Figure 1.1 illustrates the process.

Figure 1.1: Factors of dependability: fault, error, failure chain

As long as errors are not perceived by users the system is considered as free of failures. Existence of failures is critical since they may lead to important harm to human life, monetary losses, leakage of information or damage to reputation. It is worth mentioning that the causal chain defined between faults, errors and failures is recursive, since a failure at a given system level can be seen as a fault from the perspective of another system level or user.

In the field of embedded systems, dependability is not a new topic. However, it is a quickly evolving topic where practitioners are continuously required to meet new and ever-growing demands arising from several sides, typically related to reduced failure rates, safe degradation modes or guaranteed lifetimes. To list some of the most powerful drivers of research in the field, it is possible to mention 3 main pillars: (i) new fabrication **technology** nodes, (ii) new safety and reliability **standards** for existing applications and (iii) completely new **applications** where never before had such systems been used. Security has likewise received a boost of attention in recent times, as educated individuals and organizations have demonstrated the potential harm malicious attacks can cause to insecure systems.

As fabrication technology progresses to keep the pace of rising demand for high performance, low power and a very low cost, dependability properties are likewise affected. Thus, high performance is achieved by adding more and more computing elements working in parallel, which increase the total cross section for charged particles arriving into the system. This means more radiation *events* will impact the system. Furthermore due to the reduction of single element cross section, an increase in the number of *multiple bit upsets* is also foreseeable, what poses an additional challenge to fault tolerance strategies. Thermal and power stress are also worsened as a consequence of more and more elements switching simultaneously. Low power computing has jumped from battery-powered devices to every kind of system, as thermal and power considerations have been gaining importance exponentially. However, the achieved benefits come associated with important costs in several aspects. Because power budgets are so scarce, noise becomes a major concern, both the internally and externally originated. Moreover, an added source of unreliability comes from increased sensitivity to power supply variations. Additionally, to keep power low, feature dimensions are scaled accordingly, what greatly increases aging effects (NBTI, EM, HCI...) in deep sub-micron technologies. Finally low cost is a well known golden driver in industry. In that sense less and less fabs are willing to invest the quickly growing amounts of money required to develop new process nodes, what forces them to close in most cases due to insufficient workload. Those left in production face the challenge of coping with manufacturing defects, what reduces yield thus increasing price per unit. The use of fault tolerance techniques can increase yield to achieve sustainable productivity. With that panorama for the near future, insecurity can also turn an important issue. The reduced amount of manufacturers, located solely in far east countries, could increase the chances that any embedded systems designed in other countries may be tampered or illegally copied, beside the fact that any problem in the production line of a single fab could cause serious monetary losses and shortages. Although a number of fault tolerance techniques are already in use, they were designed with a set of specifications that is continuously changing. Therefore some gaps appear which are not correctly covered by existing solutions.

Safety and reliability standards have been evolving over the years alongside technology and applications. As a result, older standards are deprecated and new, more demanding ones appear as substitutes. Typical applications where such traditional standards apply are automotive, aerospace, railway, nuclear or process industries. In the new standards such as ISO26260 [81], DO-254 [40], IEC62278 [80], IEC61511 [79], etc. there is a trend to require for fault injection in the systems, in order to assess, at all stages of the development, the dependability of the systems. To that end, industrial sector demands optimized processes related to safety and robustness verification, in order to obtain approved certification at the lowest cost. The currently available set of injection tools needs to be completed with faster and more insightful choices to provide solid evidence towards certifications.

New exciting applications have found their way in the embedded systems realm. Many of those involve what is known as cyber-physical systems (CPS), where a computational system is tightly linked to a physical machine. These machines boast utterly useful capabilities for tackling all sorts of tasks, what makes them specially interesting under harsh environments which humans would not tolerate. Additionally, some are commanded to perform life, mission or business critical tasks. Under those premises application-specific integrated circuits (ASICs) but also special field-programmable gate arrays (FPGAs) have been in the market for some time, only to see commercial type SRAM based FPGAs get into that niche in recent times due to their superior performance and value. For traditional and the newly introduced devices alike, detection and mitigation of potentially critical faults is a must if they are intended to operate correctly under critical environments. Moreover, powerful tools for simulating the mission conditions, such as injection of abnormalities, are another important requirement for the success of the whole program. Nevertheless, not only critical applications or very specific markets can benefit from proper detection, mitigation and/or assessment. General purpose recent applications like smart meters, cryptography blocks or even ubiquitous smartphones can also benefit from increased tolerance to spontaneous malfunctioning, premature aging or detection of an attempt of tampering, thus improving the quality perception of the brand and decreasing the negative impact accidental or malicious events may have on the economy or lives of human beings.

### 1.2 Objectives

The challenges presented in the previous motivation section cover a wide spectrum of areas. In the present dissertation, the aim is to contribute to such areas as a way to improve dependability of the future embedded systems, and by means of providing the community with new tools, methodologies and strategies to deal with present and upcoming challenges. The main objectives of this thesis can be established as the following:

• Study the current and upcoming accidental faults affecting embedded systems to better understand their origin, evolution and consequences and provide new representative models whenever required.

With proper models it is possible to emulate physical events in laboratory conditions, testbeds or simulators, to quickly evaluate solutions before an actual device is built. The goal is to fix any dependability issues in the system as soon as possible to reduce cost of re-spins.

• Provide a fault injection and analysis tool capable of exploiting the current computing state of the art and focused on performance and flexibility, to accelerate the tasks.

The tool will need to deal with HDL defined circuits at various levels, and support the utilization of newly defined models along classical ones. Flexibility in the analysis capabilities is a further objective for the tool.

• Develop a dependability assessment methodology which cuts development time for the industry and help optimize costs.

By employing simulation-based fault injection in early development stages, it is desirable to propose and validate a methodology to obtain quick assessment on the robustness characteristics as accurate as possible, thus incorporating dependability considerations at the beginning of the design process. Moreover, assessment helps to infer statistics of interest to design more robust circuits according to applicable fault models. This is indicated for ensuring smooth standards fulfillment.

• Propose new fault tolerance mechanisms better suited to the current technology and applications trends.

As a means to fulfill this goal a study on available and currently used fault tolerance strategies will be performed where additional requirements are introduced. With the fault injection, detected weaknesses can be used to find a proposal for a better suited fault mitigation mechanism, helping to reach the required dependability levels.

### 1.3 Structure of the thesis

This section outlines the organization of the thesis document, with its different chapters. For each of them a brief explanation is given.

The present thesis is based in a collection of publications in the dependability area developed in the course of this PhD, and linked around a central challenge: the provision of dependable embedded devices for current and forthcoming demands in the industry. For the sake of explaining the reader what can be read hereafter, an introduction to each of the dealt areas comes first, situating the work topics in which advances have been made. After that, a wrap-up of the whole work is developed including conclusions and a summary of the production in the thesis.

- **Chapter 2: Faults modeling.** This chapter focuses on the fault process, pathology, manifestation and modeling. It reviews the current state of the art in the topic and presents the contributions to it included in the present thesis, mainly based in some new faults to consider and how to model them.

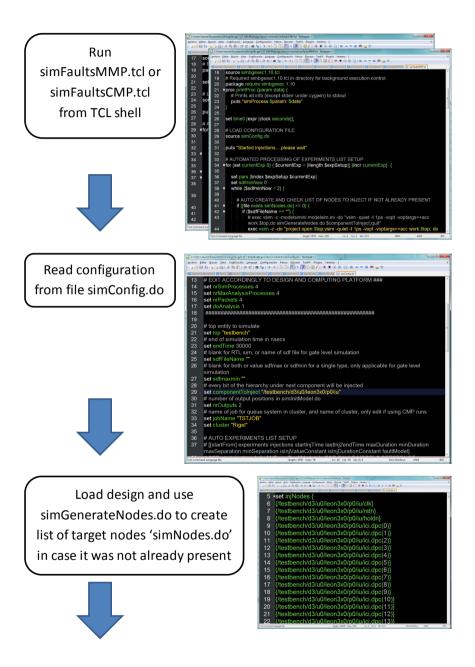

- **Chapter 3: Fault injection.** In this chapter a state of the art on different fault injectors precedes the justification for development of a new tool of the type, taking as the basis a preexisting tool in the group. It deals with the questions on what, when, how and where to inject faults, plus details in the different possible analysis to apply to the raw data. The prototype tool is called *F* ault injection and *A*nalysis for *L*ow *L*evel *E*valuation *S*uite.

- Chapter 4: System dependability assessment. In this chapter new methodologies to perform assessment on the dependability levels of embedded devices are explored. A survey on current practice is included with the contributions of this thesis in the area of multi-level correlation for obtaining

(more) accurate early robustness verification results. The presented work studies the relationships between different levels of abstraction in terms of dependability assessment.

- Chapter 5: Fault tolerance mechanisms. This chapter is devoted to fault detection, diagnosis, mitigation and recovery. It surveys alternatives available in those areas, and states the problems and benefits of them. Later it introduces the contributions presented in this work. These are mainly centered in the fault models presented in previous chapters. Likewise, the main technical implementation issues are discussed. Finally, testing of the mechanisms for proper detection of fault models is discussed.

- Chapter 6: Discussion and conclusions. Contributions of this work are discussed in detail in this chapter, with a keen emphasis on the advances and limitations. The degree of accomplishment of the goals is discussed. Finally, some guidelines for future work are suggested to further enhance the presented solutions or tackle some of their current limitations.

- **Chapter 7: Contributions.** The main scientific contributions derived from the work developed in this dissertation are listed in this section. The scientific framework in which this work has been involved is also described, including related research projects, international collaborations and awards.

#### Annexes: Papers

In the annexes each of the papers is reproduced, one per chapter. For a proper understanding they are organized in thematic areas, where contributed areas are mentioned.

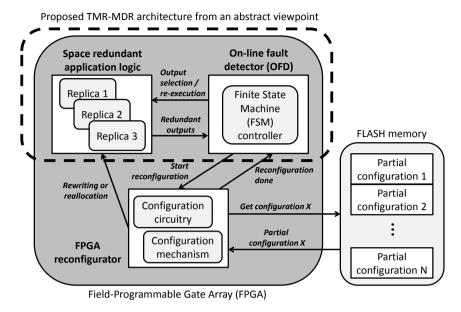

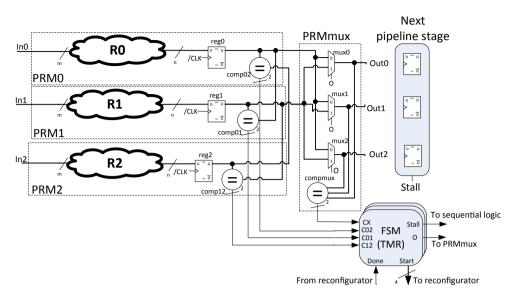

- Chapter A: Tolerating multiple faults with proximate manifestations in FPGA-based critical designs for harsh environments. In this chapter an new model for faults is introduced where the increased rates observed in most recent devices is introduced in the problem. A new mechanism to deal with it in SRAM-based FPGAs is presented based in rewrite and relocation actions among others. Contributes to Fault Modeling and Tolerance.

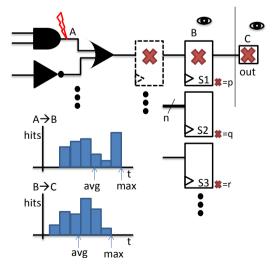

- Chapter B: The Challenge of Detection and Diagnosis of Fugacious Hardware Faults in VLSI Designs. In this chapter attention is focused towards those short duration faults which until now were ignored due to being time filtered, but which mean a good opportunity to improve dependability of systems. They are named *fugacious faults*. A tailored fault model is proposed, and the problems for effective detection and diagnosis are identified. Contributes to Fault Modeling and Tolerance.

- Chapter C: Increasing the Dependability of VLSI Systems Through Early Detection of Fugacious Faults. In this chapter a complete fault

detection and diagnosis mechanism is presented, to tackle fault models introduced in the previous chapter. Alongside an implementation workflow and helping tool is presented. Finally application to a small design provides some measurements. Contributes to Fault Modeling and Tolerance.

- Chapter D: An Aspect-oriented Approach to Hardware Fault Tolerance for Embedded Systems. The chapter explains how aspect oriented programming can be employed to automatically deploy fault tolerance mechanisms in IP cores. A few different examples are shown to demonstrate the feasibility. Contributes to Fault Tolerance.

- Chapter E: Robust communications using automatic deployment of a CRC-generation technique in IP-blocks. The chapter extends the fault tolerance mechanisms presented as samples of possible automated applications to a communications targeted mechanism like custom CRC code generation. Contributes to Fault Tolerance.

- Chapter F: Towards Certification-aware Fault Injection Methodologies Using Virtual Prototypes. This chapter presents a newly developed fault injector named FALLES, and provides a sketch of what could be done with virtual prototypes focused towards helping in safety certification. To do so extensive injections using FALLES can help improve the accuracy of the process. Contributes to Fault Injection and Dependability Assessment.

- Chapter G: Analysis and RTL Correlation of Instruction Set Simulators for Automotive Microcontroller Robustness Verification. In this chapter a correlation is found for using instruction set simulators as virtual prototypes and the dependability metrics involved in safety of automotive microcontrollers. To do so permanent fault models have been injected using FALLES to study the outputs and compare them with the information available for the instruction set simulator. Contributes to Fault Injection and Dependability Assessment.

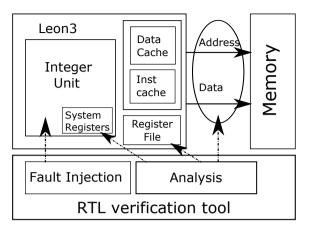

- Chapter H: Characterizing Fault Propagation in Safety-Critical Processor Designs. In this paper a thorough analysis of propagation of faults through the pipeline of a Leon3 processors is presented. The purpose is to conclude whether injection at the architectural registers can capture the information conveyed by injection results obtained at RTL. Contributes to Fault Injection and Dependability Assessment.

### Chapter 2

# Faults Modeling

| 2.1 | Pathology     | <b>2.4</b> | Modeling |

|-----|---------------|------------|----------|

| 2.2 | Manifestation | 2.5        | Summary  |

| 2.3 | Propagation   |            |          |

This chapter is devoted to the study of faults in their whole dimension: their pathology, propagation, manifestation and central to this work, modeling. A set of references and previous work is presented together with some views on the new trends and directions we can find in novel technologies coming out in the market.

### 2.1 Pathology

Advances in the semiconductor industry have been following over the last 50 years the well-known Moore's law [115]. It states that, for the same die size, transistor count will double every two years. The rule kept reasonably cheap to follow for many years but, with the advent of deep sub-micron technology nodes, the game changed completely. Alongside the benefits of doubled power and less consumption, came an important aggravation of the already-known problems of reliability, manufacturing defects, etc... which many practitioners have described [35, 3, 162, 154, 23]. The involved physical effects are Time Dependent Dielectric Breakdown (TDDB), ElectroMigration (EM), Negative Bias Thermal Instability (NBTI) or Hot Carrier Injection (HCI) to name a few. TDDB is a consequence of long term operation beyond specified voltages; EM is due to high currents carrying material away from its original position; NBTI happens as a side consequence of dopants introduced to reduce leakage current and causes increase in threshold voltage, and HCI provokes charge carriers to get trapped in the gate dielectric hindering correct operation of the MOSFET. The most dangerous in terms of long term reliability can be the NBTI, but for high current devices EM can also pose severe design constraints. TDDB comes next in importance and HCI is the least severe of the mentioned effects.

While those are mainly intrinsic faults coming from inside the circuit or device. they have had a replica in the extrinsic faults, originated in the external side. Sadly enough, newer highly integrated technologies have turned more and more sensitive to the so-called *soft errors* [101, 17], which are caused by charged particles  $(\alpha \text{ particles})$ , neutrons reaching the silicon die and altering the logical value of an electrical node. The energy exchange process is similar to a bullet of a certain size hitting ever smaller targets. The critical charge required to 'damage' (upset) a single node is smaller and smaller, thus smaller bullets will have effect on that smaller target causing more upsets to appear. Additionally, sensitivity to power supply noise [62] or Electro Magnetic Interference (EMI) [124], because of reduced power budgets, has raised. To understand why, a quick look to energy consumption growth and heat density inside die explains the need to operate with low voltage power rails. Therefore logic levels are so close that fluctuations in the power supply and small interferences can cause a value to change. Finally, crosstalk [31] sensitivity has also raised dramatically, because an increase in switching speeds also involves an increase in generated noise to the vicinity.

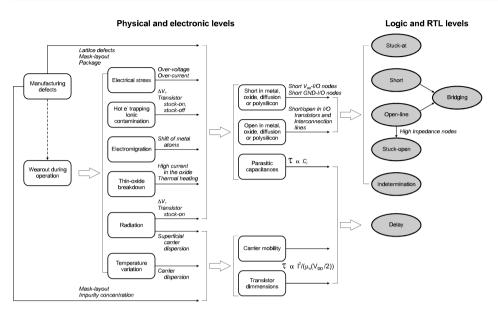

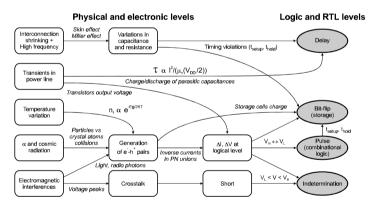

As a summary of different physical processes involved in faults, 2 different figures in [66] were reproduced, one for permanent faults (Figure 2.1) and one for transient faults (Figure 2.2). In the figures, counterparts of the physical and electronic processes as logic/RTL level fault models are also shown for reference. The parameter used for separation -the different manifestation type- is developed in the next section.

#### 2.2 Manifestation

All the previous section phenomena happen in different time spans. Some of them only take place during temporary periods and later disappear –transient faults– while others can only appear but never stop their unwelcome effect –permanent faults [13]. Moreover, there is a special type of faults which appear and disappear at random instants of time, i. e. they manifest themselves intermittently –the intermittent faults [34, 37]. These intermittent manifestations in the same location can be due to operational circumstances, which may eventually disappear, or be caused by wearout processes or manufacture defects. In the latter case they are

Figure 2.1: Pathology of permanent faults [66]

Figure 2.2: Pathology of transient faults [66]

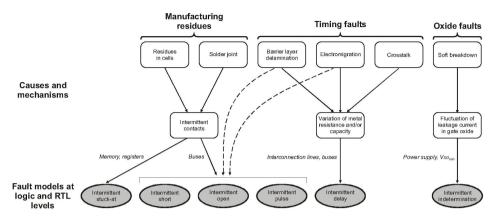

preclude of permanent manifestations which follow a growing trend in time and intensity [159]. A table showing several of the physical processes which can lead to intermittent faults is shown in Figure 2.3.

There exist several different manifestations the community has identified which, up to day, are not well covered with current models, if covered at all. Such manifestations can happen in single or multiple fashion. In the latter case, for instance, the combination of an intermittent manifestation which has not been cleared from

Figure 2.3: Pathologies of faults manifested as intermittent [69]

the system together with (e.g.) an additional transient or permanent, pose a new feasible threat to discuss. In fact, the same pathology can change its manifestation according to differing base technologies. Truly some of the fault processes which showed permanently under old ecosystems happen to manifest intermittently under modern scenarios, only to turn to permanent behavior much later. An example can be found in the ElectroMigration (EM) effect, which in time ends up breaking the physical continuity of a conductor but, in modern high frequency circuits, and due to skin effect, can cause increased delays which would randomly show an effect in the functionality. Only after an important lapse of time intermittent manifestation would lead to permanent disconnection. Likewise, processes which were responsible for transient faults, like crosstalk effects, have suffered a general increase in severity. Closer, more packed metal interconnects become the main reason after it. Therefore certain nodes can show now an intermittent manifestation, with a much higher potential of negatively impacting the system. The more complex manifestations faults have means new complex responses must be placed in order to adequately respond. Thus, mitigation techniques have to be revisited to continuously adapt to those complex fault footprints.

Returning to the consequences of size miniaturization from the dependability point of view, other notable facts must be underlined. Continuous tests show that, as channel length sizes have been reduced, so have been the fault manifestations when it comes to timespan. Measurements in laboratory conditions demonstrated that, for the same energy of the offending abnormality (charged particle, EMI interference, etc...), shorter transient faults were generated [60, 59, 43] and also less energy was required to cause an upset of the logical values of the circuit [41]. As narrowly shaped voltage variations have been traditionally filtered out, they have received little attention. However, with the most advanced sub-micron technologies not only they become more frequent, but they can also reach propagation to further logic stages.

## 2.3 Propagation

After an undesired alteration of the voltage has affected an electrical node, it may or may not propagate through the circuit. Take for instance a fault causing a pulse in a combinational node. If propagation is not hindered in any of the ways explained next, the wrong value with traverse the logic path, reach into a sequential element and possibly have a negative impact in the provided service and therefore in the dependability level. However important filtering effects apply, avoiding every single manifested error to propagate and disrupt correct operation.

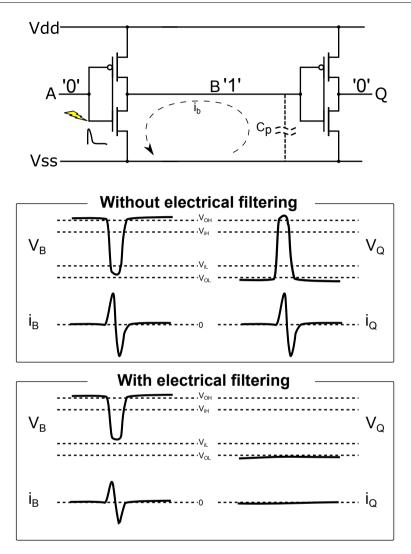

If the reached voltage is lower than the voltage threshold of the technology  $V_{th}$ , or the duration of the pulse is really small, it will not be able to switch the logical value of the next gate, since not enough energy will have been accumulated/discharged in the capacity associated to the affected node. Thus, an effect of *electrical filtering* will happen (Figure 2.4). In the literature there are plenty of studies related to the energy required to allow propagation but one of the most comprehensive can be found in [59].

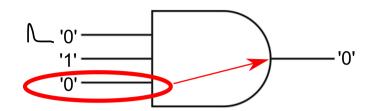

When the upset has reached enough energy to propagate ahead in the base technology, other effects can stop it from doing so. One of the most relevant is *logic filtering*. The mechanism is simple: take for instance an AND gate, where one of its inputs is logical '0'. If any of the other inputs suffers an unexpected alteration of its value, there will be no impact at the output of the gate, and thus no propagation (Figure 2.5).

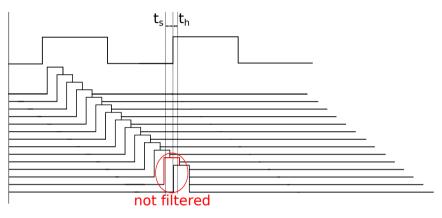

Once the upset has propagated all the way through the combinational logic down to the sequential elements, there is still a very important filtering mechanism to defeat: the *temporal filtering*. Any voltage value can be present at the input of a sequential element, but the only value to be captured will be that which is applied during the period in-between the set-up and hold associated to the capture clock edge (Figure 2.6). In [25] an experimentation with laser beams shows that, for a transient fault in combinational logic, there is great dependence on the frequency of the circuit w.r.t. the errors which will be propagated to the sequential elements. Conversely, upsets in the sequential elements will be totally independent from clock frequency.

When an upset has reached a sequential element, it can further propagate to the system or module outputs, (causing a failure) or not. But just as in the process from the manifestation of a failure until an upset hits the sequential element, filtering will apply. Hence, a complex function of system current state, inputs, instant of execution and workload will define the reach a fault will have in its

Figure 2.4: Electrical filtering effect

utmost consequences. Fault tolerance practitioners need tools to investigate those effects well in advance of the availability of the silicon, for economical and technical reasons, and the inputs to those tools will be models of the evaluated faults.

Figure 2.5: Logical filtering effect

Figure 2.6: Temporal filtering effect

## 2.4 Modeling

In order to know how faults behave, i.e. their impact in circuits and systems, accurate models are required. With the purpose of providing such models, several works have been studying fault models for dependability analysis [66, 136]. In them, it is made clear how important models are to be able to study faults and their effects. In that sense a simplification, or an adaptation of what is present in the physical layer has to be done to suit the layer at which the model will be used, with a keen emphasis in retaining an accurate representation of the effects caused onto the target layer. It is a hot topic of research to explore the degree of precision achieved in the current representations at different levels, of a process occurring in the very physical level of a chip.

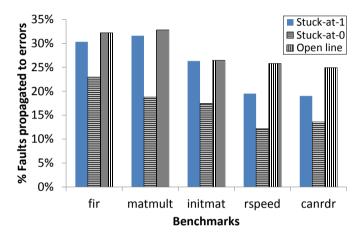

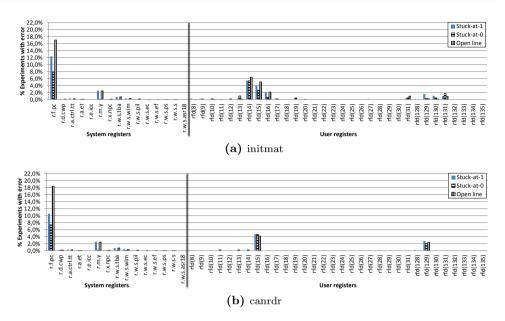

As the different levels of description entail different properties, those can make advantages or disadvantages from the dependability assessment point of view. In this section logic/RTL level is considered as the target level for a reason: it is the closest representation to physical where valuable injection properties of repeatability, reproducibility, non-intrusiveness, representativity and reachability (explained in following chapters) are attained at high levels.