B.Sc.Eng. Thesis Bachelor of Science in Electronic Engineering

DTU Space National Space Institute

Fault Tolerance Techniques for FPGA-based Space Applications

A study of the effects of radiation in SRAM-based FPGAs and their solutions

Gabriel Cobos Tello

DTU Space 2019

DTU Space National Space Institute Technical University of Denmark

Elektrovej Building 327 2800 Kongens Lyngby, Denmark Phone +45 4525 95 00 office@space.dtu.dk www.space.dtu.dk/English

## Summary

This thesis focuses on mitigation techniques for SRAM-based FPGAs and how they improve design reliability. The FPGA implemented design is a basic AVR CPU running a matrix multiplication workload. The process followed starts with faults being injected into the basic design to obtain a reliability baseline. Mitigation techniques are then used, in the form of basic TMR and hamming code EDAC, to improve the reliability of the design. Then an iterative process of mitigation techniques and fault injection is carried out to optimise resources and maximise design reliability. This is all done in hopes of presenting a realistic approximation of space system design and the margins this area of engineering is limited by.

The mitigation techniques where all developed for the purpose of the thesis, using state of the art techniques as reference. The CPU was obtained from OpenCores alongside with the tool-chain required to program the custom workload. The fault injection methods where provided by David de Andrés and Ilya Tuvoz, from UPV's department of computer engineering. II\_\_\_\_\_\_

## Preface

### A symphony of Space, Radiation and Electronics

Space has always been a mysterious field for science and technology, so naturally, I felt tremendously attracted to it. This attraction consisted mostly of the kind of infantile curiosity that characterises any endeavor with lots of promise and an unsuspected difficulty. The reasons I use this two words to describe what I experienced while working in this thesis, is because through the course of the project there was a recurring theme of fascination, followed by frustration at how complicated bringing the theory to practice was. This was something I overlooked when I first proposed a broad idea for a Thesis to my supervisor David de Andrés. At the time I just wanted to work with FPGAs and if possible get a head start at what I hoped one day would become a successful space career. David was the one to propose the topic of fault tolerance in FPGAs, offering his supervision and mentoring. I promptly accepted and started looking for supervisors at DTU Space, since I was certain I wanted to carry out the project in a department specialized in space research. Eventually Jose M.G Merayo was the one to show interest in the nature of my thesis and he offered to become the DTU supervisor. With a full team of supervisors, also including Carlos Dominguez, a computer science professor at UPV, I started work on this thesis.

DTU Space, June 20, 2019

Gabriel Cobos Tello

İV

# Acknowledgements

I would like to thank Carlos Dominguez for his help as the administrative supervisor of this thesis. It was due to his efforts that it was possible for me to fulfil the complex task of writing a thesis in a foreign university.

Of course any effort would have been in vain without the help and involvement of Jose M.G Merayo, my supervisor at DTU. During the first months our weekly meetings allowed me to grasp the basics of the project while also bringing a sense of security to the entire process. It would be hard to imagine how alienating it would have been to work on a thesis at a new university without the constant care and support of Jose.

David de Andres was my secondary supervisor at UPV, yet his involvement was total. It is thanks to his generosity and patience during the first times we met that the thesis happened in the first place. I can not begin to imagine the amount of hours invested by him from Valencia to assist me in my work here at DTU. Not only did he provide the methods for me to test my designs, but he also made sure they worked, alongside Ilya Tuvoz his PhD student and co-developer of the fault injection mechanisms. In my opinion David proved to be someone truly invested in teaching others, as he would always answer any queries without the slightest trace of annoyance, always looking out for the student's best interests. I can honestly confess that without his help I would have never been able to break the barrier of entry for this topic, and for that I am truly grateful.

To my parents I also owe a well deserved thank you, for it is through their sacrifices that I can focus on my studies and experience adventures like studying abroad. Specially my mother, for whom I have no words that can describe the extend to which she has gone to make sure I grow and flourish. If I ever achieve anything it is thanks to you, for you gave me the base upon which to build my life. Yet, you know while reading this, that these are just words and what truly counts are the actions taken every day. The gestures that allow us to rely on each other and develop as people. This is something I don't share with anyone else and for that we will always be special for each other.

A Papa: Si no fuera por lo mucho que trabajas y por como siempre nos tienes en mente a mi y a mama, jamas podría hacer las cosas que hago. Es gracias a ti que algún día pueda llegar a ser alguien que contribuya a la sociedad, pudiendo centrarme hoy por hoy plenamente en mis estudios, pero eso ya lo sabes. Lo que quizás no sepas es que incluso si algún día decides que tienes que descansar, por poco que sea, nada cambiara. Yo siempre te voy a querer igual, es algo crónico e incondicional, no depende ni del trabajo ni de tus acciones. Yo siempre voy a conseguir llegar a cumplir mis objetivos, porque ese es el tipo de persona que me as ayudado a ser. Yo siempre estaré listo para cambiar de rol cuando lo necesites, porque a veces es necesario que la persona que mas se apoya en ti se gire, y por una vez de de su hombro a apoyar, para con suerte alibiar la carga generada a lo largo de los años. Con amor, Gabriel.

# Contents

| Su            | immary                                                                                                                                                                                                                       | i                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Pr            | reface<br>A symphony of Space, Radiation and Electronics                                                                                                                                                                     | <b>iii</b><br>iii          |

| Ac            | cknowledgements                                                                                                                                                                                                              | $\mathbf{v}$               |

| Co            | ontents                                                                                                                                                                                                                      | vii                        |

| $\mathbf{Li}$ | st of Figures                                                                                                                                                                                                                | ix                         |

| $\mathbf{Li}$ | st of Acronyms                                                                                                                                                                                                               | xi                         |

| 1             | Introduction                                                                                                                                                                                                                 | 1                          |

| 2             | Overview on Space Radiation in Electronics2.1Near-Earth Radiation Environment2.2Semiconductors: Single Event Effects                                                                                                         | <b>3</b><br>3<br>5         |

| 3             | FPGAs in Space Applications3.1Dependability and Security in the Face of SEU3.2The Peculiar Effect of Radiation on SRAM-based FPGAs3.3Architectural overview of 7-series Xilinx FPGAs3.4SEU Mitigation and Recovery for FPGAs | 7<br>7<br>13<br>16<br>19   |

| 4             | Making and Testing a Dependable and Secure CPU4.1A simple CPU4.2Fault Injection in the CPU4.3Assessing the CPU's Dependability4.4Conclusion                                                                                  | 27<br>27<br>29<br>33<br>42 |

| 5             | Discussion                                                                                                                                                                                                                   | 43                         |

| $\mathbf{A}$  | Calculations, Resources and Floor-Plans                                                                                                                                                                                      | 45                         |

| Bi            | bliography                                                                                                                                                                                                                   | 63                         |

viii

# List of Figures

| 2.1  | Ionizing particle colliding with silicon semiconductor surface $[10]$                            | 5  |

|------|--------------------------------------------------------------------------------------------------|----|

| 3.1  | Device Protected by TMR [10]                                                                     | 9  |

| 3.2  |                                                                                                  | 10 |

| 3.3  | TMR for Combinational and Sequential Logic [10]                                                  | 10 |

| 3.4  |                                                                                                  | 11 |

| 3.5  | Data Bits represented by Parity Bits in an EDAC(12,8)                                            | 12 |

| 3.6  |                                                                                                  | 12 |

| 3.7  | Flow diagram for an EDAC(12,8)                                                                   | 13 |

| 3.8  |                                                                                                  | 14 |

| 3.9  | Routing and Logic Before Upset [4]                                                               | 14 |

| 3.10 | Routing and Logic After Upset[4]                                                                 | 15 |

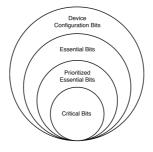

| 3.11 | Classification of Configuration Bits by Criticality                                              | 15 |

| 3.12 |                                                                                                  | 16 |

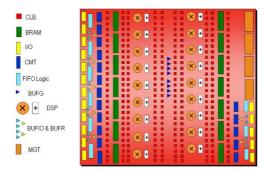

| 3.13 | 7 series FPGA Fabric                                                                             | 17 |

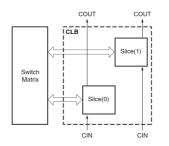

| 3.14 | Types of PIPs. (a)Break-point PIP.(b)Cross-point PIP.(c)MUX                                      | 17 |

| 3.15 | Slices within CLB                                                                                | 18 |

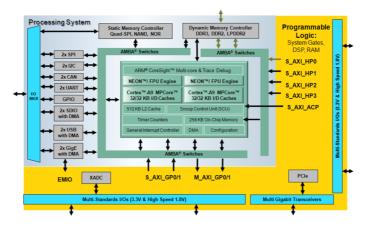

| 3.16 | Xilinx SoC Architecture                                                                          | 18 |

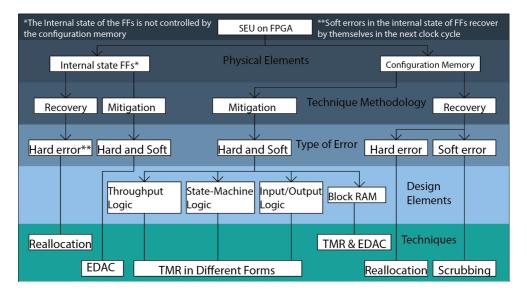

| 3.17 | Top Down Flowchart for Fault Tolerant Techniques                                                 | 19 |

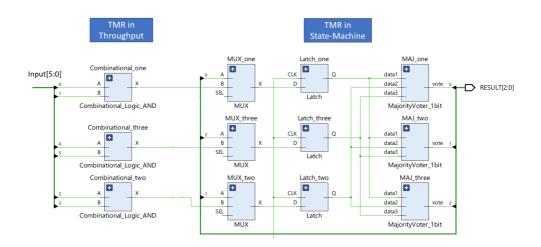

| 3.18 | TMR Design for a Combinational Block and a FF with Feedback $\$                                  | 21 |

| 3.19 | TMR Clock Divider                                                                                | 21 |

| 3.20 | Waveform Showing TMR Error Mitigation                                                            | 22 |

| 3.21 | EDAC for a 16 Bit Register                                                                       | 22 |

| 3.22 | Waveform Showing EDAC Error Mitigation                                                           | 23 |

| 3.23 | Frame Address Registers [22]                                                                     | 24 |

| 3.24 | Basic Scrubbing Components [4]                                                                   | 25 |

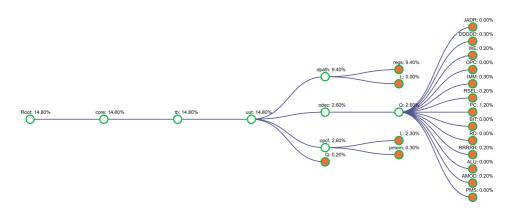

| 4.1  | 0                                                                                                | 28 |

| 4.2  | Block Diagram of Design Top-Level with ARM CPU                                                   | 29 |

| 4.3  | Architecture of the fault injector at the software and hardware layers $\label{eq:architecture}$ | 30 |

| 4.4  | 0                                                                                                | 36 |

| 4.5  | FF specific PoF Distribution in Basic AVR                                                        | 37 |

| 4.6  | Comparison of Resources, PoFs and FITs for the Different Designs (Simple    |    |

|------|-----------------------------------------------------------------------------|----|

|      | Faults)                                                                     | 40 |

| 4.7  | Comparison of Resources, PoFs and FITs for the Different Designs (4 Faults) | 42 |

| A.1  | Calculations for the Basic AVR Design                                       | 46 |

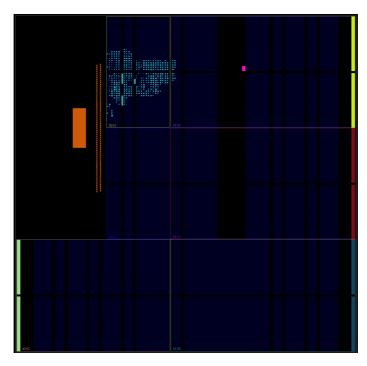

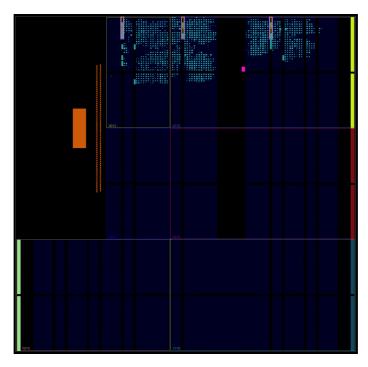

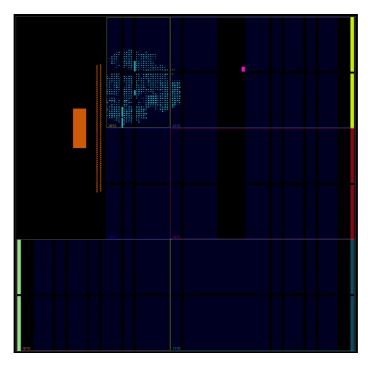

| A.2  | Floor-Plan for the Basic AVR Design                                         | 47 |

| A.3  | Resources employed by the Basic AVR Design                                  | 47 |

| A.4  | Calculations for the Device TMR Design                                      | 48 |

| A.5  | Floor-Plan for the Device TMR Design                                        | 49 |

| A.6  | Resources employed by the Device TMR Design                                 | 49 |

| A.7  | Calculations for the ALU TMR Design                                         | 50 |

| A.8  | Floor-Plan for the ALU TMR Design                                           | 51 |

| A.9  | Resources employed by the ALU TMR Design                                    | 51 |

| A.10 | Calculations for the OPC-DECO TMR Design                                    | 52 |

|      | Floor-Plan for the OPC-DECO TMR Design                                      | 53 |

| A.12 | Resources employed by the OPC-DECO TMR Design                               | 53 |

| A.13 | Calculations for the EDAC in BRAMs and FFs Design                           | 54 |

| A.14 | Floor-Plan for the EDAC in BRAMs and FFs Design                             | 55 |

| A.15 | Resources employed by the EDAC in BRAMs and FFs Design                      | 55 |

| A.16 | Calculations for the Design with TMRs and EDAC                              | 56 |

| A.17 | Floor-Plan for the Design with TMRs and EDAC                                | 57 |

| A.18 | Resources employed by the Design with TMRs and EDAC                         | 57 |

| A.19 | Calculations for the Device TMR, 4 Faults                                   | 58 |

| A.20 | Calculations for the Design with TMRs and EDAC, 4 Faults                    | 59 |

| A.21 | Calculations for the Design with TMRs and EDAC plus Device TMR, 4           |    |

|      | faults                                                                      | 60 |

| A.22 | Floor-Plan for the Design with TMRs and EDAC plus Device TMR                | 61 |

| A.23 | Resources employed by the Design with TMRs and EDAC plus Device TMR         | 61 |

x

# List of Acronyms

| ALU Arith | metic L | logic U | Unit |

|-----------|---------|---------|------|

|-----------|---------|---------|------|

- ASIC Application Specific Integrated Circuits

- ASMBL Advanced Silicon Modular Block

- **BRAM** Block RAMs

- **CB** Critical Bits

- **CPU** Central Processing Unit

- CLB Configurable Logic Blocks

- **CMT** Clock Management Tiles

- **COTS** Commercial of the Shelf

- **DUT** Design Under Test

- **EB** Essential Bits

- EDA Electronic Design Automation

- **ESA** European Space Agency

- **EDC** Error Detection Code

- **ECC** Error Correction Code

- **EDAC** Error Detection and Correction Code

- FF Flip Flops

- **FIT** Failure in Time

- FPGA Field Programmable Gate Array

- GCR Galactic Cosmic Radiation

- HDL Hardware Description Language

| IP            | Internet Protocol                                  |

|---------------|----------------------------------------------------|

| IR            | Interconnect Resources                             |

| INO           | IN and Output Block                                |

| IOB           | Input and Output Blocks                            |

| LUT           | Look Up Table                                      |

| MAJ           | Majority Voter                                     |

| MUX           | Multiplexers                                       |

| MOSFET        | Metal Oxide Semiconductor Field-Effect Transistors |

| NASA          | National Aeronautics and Space Administration      |

| PC            | Program Counter                                    |

| $\mathbf{PL}$ | Programmable Logic                                 |

| $\mathbf{PS}$ | Programmable System                                |

| PoF           | Probability of Failure                             |

| PIP           | Programmable Interconnect Points                   |

| RoF           | Rate of Faults                                     |

| $\mathbf{SM}$ | Switch Matrices                                    |

| SOI           | Sillicon on Insulator                              |

| SEU           | Single Event Upsets                                |

| SET           | Single Event Transient                             |

| SOC           | System on a Chip                                   |

| SAA           | South Atlantic Anomaly                             |

| SRAM          | Static Random Access Memory                        |

| TMR           | Triple Modular Redundancy                          |

| TID           | Total Ionising Dose                                |

| UART          | Universal Asynchronous Receiver-Transmitter        |

| XOR           | Exclusive OR                                       |

|               |                                                    |

## CHAPTER

## Introduction

Several developments through out the years have placed FPGAs in an interesting spot in relation to space applications. One such development, shared by most electronic devices, is the trend of constant increasing density of logic resources. This trend, paired with the significant improvements in the clock speeds at which this devices can operate, has allowed for higher performance and lower power consumption in FPGAs when compared to microprocessors or application specific integrated circuits (ASICs) [11]. These events see FPGAs being used in the place of ASICs in many systems. This being the case in space applications as well, where FPGA's re-programmability would in theory be of most use. Either for long space or short near earth missions, this re-programmability grants FPGAs and the systems within which they operate, great flexibility in the form of system updates that can be implemented at a hardware level, or the ability of fixing design issues once the mission has already started.

Of course all these advantages come at a cost. The reason why FPGAs stand in an interesting spot in relation to space applications is because their biggest strengths are also their biggest weakness. Both their great logic density and field programmability make FPGAs extremely sensible to radiation effects, specially in radiation rich environments like space. FPGAs that try to amend this issue exist and are known as Space-Grade FPGAs but they also come with some disadvantages. Normal FP-GAs, known as commercial of the shelf (COTS) FPGAs, can have up to 2.5 times the logic resources of a Space-Grade, faster switch time, less power consumption and the support of modern design tools [5]. This leaves system designers at a cross roads, in which they have to decide whether to prioritize reliability at the cost of higher performance rates, or prioritize more modern COTS devices and invest in expensive testing to apply fault tolerant technology.

The topic hereby presented will assume the latter option is chosen and will be a detailed analysis of fault tolerance techniques for SRAM-based FPGAs employed in space applications.

2\_\_\_\_\_

# CHAPTER 2 Overview on Space Radiation in Electronics

This overview will focus on the theory related to the general space radiation environment and the effect of radiation on electronics as a whole. Yet, types of radiation do not change throughout the entire region of space in our known solar system, with only the quantities and spectrum of these varying depending on the location being studied [9]. Hence, the thesis will be focused on the near-Earth radiation environment, since it provides a milder radiation environment and good sources of data from ESA and NASA, without limiting the types of radiation to be discussed. It is important to understand the general concepts behind the topic of space radiation on electronics before progressing on to the focus of the thesis, as this very understanding is the justification for the subjects explained in detail in chapter 3.

## 2.1 Near-Earth Radiation Environment

The near-Earth radiation environment can be divided into a trapped radiation environment and a transient radiation environment [9], with some secondary sources of radiation also appearing occasionally. The trapped radiation environment consists of charged particles that are confined to certain regions due to Earth's magnetic field. These regions are denominated Van Allen Belts and normally there are one proton and two electron belts, although this can change due to strong solar events. The transient radiation environment is composed of solar wind, solar flares and Galactic Cosmic Radiation (GCR), which are not only present in the near-Earth region but also in the interplanetary space regions.

**Trapped Radiation Environments** The trapped radiation belts extend from approximately 500 km to about 12 Earth radii (roughly 76,000 km) [9]. It is within this range that the previously mentioned electron and proton bands are located. These

bands are populated with electrons, protons and small amounts of low energy heavy ions that are trapped by the Earth's magnetic field, above the dense atmosphere. These particles gyrate around, bounce along magnetic field lines and are reflected back and forth between pairs of regions with maximum magnetic field strength along their trajectory through opposite hemispheres[15].

Given how trapped radiation is so heavily dependent on the Earth's magnetic field lines, there is a special phenomenon that has to be taken into account, the South Atlantic Anomaly (SAA). The Earth's magnetic field axis does not point to the geographic north and does not pass directly through the center of the Earth, this causes a deformation in the magnetic field over the South Atlantic and over Southeast Asia, with the net effect of an increase in radiation harshness from trapped particles in this regions [9]. The effects of the SAA are so severe that they are always factored into the calculations of the orbits of satellites.

**Transient Radiation Environments** Solar wind is composed of low energy electrons and protons and its considered to be negligible when compared to other sources of radiation, with the exception of externally mounted spacecraft components where it can sometimes be energetically significant. Solar flares are the other source of radiation originating from our sun, in particular when a magnetic disruption in the solar photosphere occurs, causing a variety of radiation types and energies to erupt [9]. These eruptions can produce energetic protons and heavy ions that when impacting on electronic devices will cause unwanted effects. The last of the three transient radiation sources are GCRs, these are composed of electrons, protons and heavy ions, all of which are believed to have an origin outside the solar system and to be omnidirectional [9]. Just like solar flares GCRs can cause unwanted effects in electronic components.

Solar flares and GCRs always have to be taken into consideration alongside the Earth's magnetic field. The magnetic forces originating from the Earth also act on the charged particles contained in these sources of radiation, meaning that for a given magnetic field strength only a certain number of sufficiently energetic particles will penetrate without being reflected along the magnetic field lines.

The radiation sources described will, in general terms, produce ionizing particles that might impact electronic system causing unwanted effects. The amount and frequency by which this particles may impact has to be estimated based on the scenario where the electronic system will be deployed. It is in this estimation where an advanced understanding of space physics and weather is required. Without good approximations to the radiation harshness of the scenario, the system designers might implement either too much or too little robustness into their system. Thus causing problems in the long run, such as production delays or even system failures during real missions.

On top of a good understanding of the scenario, knowledge on the general effects of ionizing radiation in electronics (semiconductor devices) is required in order to

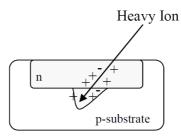

Figure 2.1: Ionizing particle colliding with silicon semiconductor surface [10].

successfully predict the behaviour of radiation on any specific system.

### 2.2 Semiconductors: Single Event Effects

Just like the radiation environment is narrowed down to that of the low-Earth orbit, the effects of radiation on electronic devices will also be narrowed down to Single event effects, without taking into consideration cumulative effects. The reason being that the techniques deployed in later chapters only protect against the effects of particle impacts, also known as Single Event Upsets (SEU), and not the Total Ionising Dose (TID) responsible for some of the possible permanent errors within the device.

When studying the effects of ionizing particles colliding with electronic devices its important to focus on their most basic component, the transistor. In specific Metal Oxide Semiconductor Field-Effect Transistors (MOSFET), which have been dominant in the fabrication of integrated digital circuits. When an ionizing particle impacts the semiconductor region of the transistor it loses energy via the production of free electron-hole pairs in its trajectory [10], figure 2.1. The number of electron-hole pairs is proportional to the deposited energy by the particle and thus the effects are proportional to the particle energy too. Depending on the orientation of the electrons or holes produced, the electrical current in the transistor might start flowing or be stopped. This might cause the originally intended behaviour of the transistor to change, in turn affecting the electronic device's behaviour at a digital level too. This phenomenon is referred to as a SEU.

There are two types of SEU, destructive or non-destructive, based on the damage they cause to the element at impact. Destructive SEU will lead to hard errors that will permanently affect the element until it is repaired or replaced. Non-destructive SEU will lead to transient faults that might ripple through the device where the element resides, this is known as a soft error. Non-destructive SEU are more common and depending on the device their effects will vary greatly. For instance SEUs in FPGAs have very particular effects that make this type of devices very interesting to study, hence the focus of the thesis as presented in the next chapter. <u>6</u>\_\_\_\_\_

# CHAPTER **3** FPGAs in Space Applications

As mentioned in the introduction, there is a general interest within the space industry to see COTS FPGAs achieve high levels of reliability. This is the core principle behind the focus of the thesis and the reason why the device of choice throughout the project will be an SRAM-based FPGA, specifically the zybo-z7020. This kind of FPGAs grant performance, flexibility and scheduling benefits to system designers, when compared to other more robust FPGAs such as the fuse or flash based FPGAs [6]. Yet, like all static memory cells, SRAM-based configuration cells used in SRAM FPGAs are susceptible to data corruption from high-energy radiation [19]. Furthermore, given how the number of configuration cells in FPGAs are increasing due to logic resources density, as previously mentioned, upsets within the configuration memory are also increasing. This kind of upsets, when occurring in re-configurable systems like FPGAs, are especially troublesome since these cells specify the operation of the re-configurable fabric and thus the architecture of the digital circuit designed. Based on this concepts, a variety of fault tolerance techniques will be discussed in section 3.1, with special consideration been taken for the effects of SEU in FPGAs as described in detail in section 3.2.

### 3.1 Dependability and Security in the Face of SEU

**State-of-the-Art** Technological advancements in fabrication technologies, following Moore's law, are progressively making electronic devices more sensible to external disturbances [3]. From these, ionizing radiation is of special interest to us. Normally and for many years, shielding was the main prevention security measure for spacecraft systems, as this solution was enough to avoid errors from radiation effects [10]. Nowadays, due to the aforementioned technological advancements, shielding is no longer sufficient as a single means of dependability. This is why mitigation and removal techniques are being developed in order to avoid faults in the electronic devices aboard spacecrafts. A classification methodology from [2] is used in order to organise these state-of-the-art techniques:

- 1. Fault prevention, such as:

- a) Epitaxial CMOS processes

- b) Advanced process such as Sillicon on Insulator (SOI).

- c) Shielding

- 2. Fault Tolerance, such as:

- a) Detection techniques:

- i. Hardware redundancy

- ii. Time redundancy

- iii. Error Detection code (EDC)

- iv. Self-checker techniques

- a) Mitigation techniques:

- i. Triple Modular Redundancy (TMR)

- ii. Multiple redundancy with voting

- iii. Error Detection and Correction Code (EDAC)

- iv. Hardened memory cells

- 3. And Recovery Techniques (applied to programmable logic only), such as:

- a) Reconfiguration

- b) Partial configuration

- c) Reallocating design

The first of these groups, the fault prevention techniques, is outside the scope of this thesis as it implies either fabrication process-based techniques or shielding. We will focus on COTS FPGAs, as mentioned earlier, so any technology that implies fabrication will not be discussed. Shielding is an external measure and as such will not be discussed either. The second category of fault tolerant techniques, specifically mitigation, will be the main focus of the thesis. Lastly, the fault removal techniques are also of great interest to us. This kind of methodology is only available to FPGA like devices and plays a great role in the long term robustness of any programmable logic based design.

Fault tolerant techniques are broadly used for ASIC design due to how they can target design architecture without requiring special fabrication methods. As such, many of the fault tolerant techniques are made for non re-programmable devices, like ASICs and do not take into account the special effects of radiation in FPGAs. Fault tolerance techniques can be employed for fault detection (detection techniques) but normally they are applied to both detect and correct system errors in the presence of SEUs or SETs (mitigation techniques). The main principle behind these techniques is that of redundancy, in the form of hardware redundancy, meaning extra components or in the form of time redundancy, which implies extra execution time or different sampling rates for data. Most frequently a combination of both these types of redundancies is applied for optimal results, yet we will focus solely in hardware redundancy.

#### 3.1.1 Full Hardware Redundancy

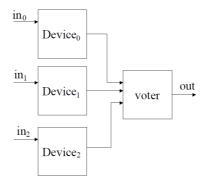

Mitigation techniques are, as their name implies, techniques that take effect once the SEU has already happen, preventing it from disturbing the normal functioning of the circuit. As such they tend to be applied with a focus on efficiency, by protecting only critical elements and saving resources, full hardware redundancy is no exception. This type of redundancy can be summarised as logic redundancy, meaning extra logic components or extra paths that allow a design to continue operation even when some of the logic fails. In order to protect a design from the effects of both SEUs and SETs one of the techniques applied is that of TMR. In TMR the logic is triplicated and voters are placed in the output to identify and select the correct value. The most basic form of TMR is that of device TMR, as seen in figure 3.1. This kind of implementation is not resource optimised and allows only for mitigation of any number of faults in a single replica.

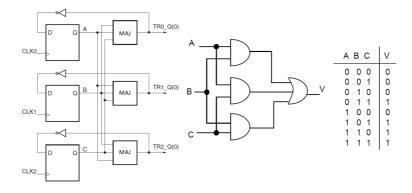

In figure 3.2 a better implementation of TMR is shown. Here the solution is applied more efficiently by focusing on a sensitive element of the design, in this case a memory cell, a FF. This type of implementation protects the design, specifically the sequential logic, from the accumulation of SEUs. The way this is intended to work is for the majority voters (MAJ) to detect any errors happening in the FFs between clock cycles, correct them and send them back to the FFs for them to be latched. This method only allows for one upset per FF at a time.

In [10] a TMR design is proposed to protect both combinational and sequential logic while still preventing the accumulation of upsets, figure 3.3. The combinational

Figure 3.1: Device Protected by TMR [10].

Figure 3.2: Sequential Counter Protected by TMR [10].

logic is triplicated and fed to Multiplexers (MUX) that will ensure the FFs latch the correct value. The MUXs select between the output of the voters or the combinational logic by means of a select input line controlled by a clock frequency established by the designer. This prevents errors that happen between clock cycles from accumulating, since the FFs will have either a new value from the combinational logic or the previous correct value from the voter. Yet again this type of TMR has some limitations and will only prevent failure as long as only one of the branches presents errors at the same time.

Figure 3.3: TMR for Combinational and Sequential Logic [10].

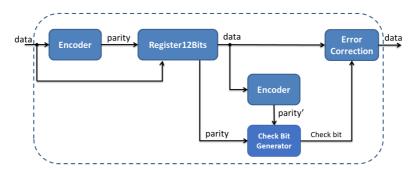

### 3.1.2 EDAC

EDACs are another form of mitigation techniques targeted at sequential memory elements. Their purpose is to encode the input of the memory element generating parity bits. These parity bits are then compared to a second group of parity bits generated at the output of the memory element. By doing this several check bits are produced that allow the EDAC to detect if there was an error in the data stored at the memory element. Based on these check bits the EDAC can decide which data bit needs correction, changing its value to the originally intended. A simple EDAC can detect and correct one error at a time within the memory element.

The theory behind the EDAC described is based on the idea of Hamming codes [13]. These codes use the aforementioned parity bits to represent the data bits contained by the memory element. The amount of parity bits required depends on the number of data bits to protect, with a relation shown in the following equation:

$$2_n^P \ge D_n + P_n + 1 \tag{3.1}$$

Where  $(D_n)$  represents the number of data bits and  $(P_n)$  the number of parity bits. The combination of parity and data bits forms what is referred to as the code word. This code word follows a certain structure, with parity bits placed in location numbers based on the power of 2  $(2^0, 2^1, ..., 2^{P_n})$ , with the least significant parity bit,  $(P_0)$  being placed at  $2^0$  and the most significant,  $(P_n)$ , at  $2^{P_n}$ . Thus the structure of a 12 bit code word protecting an 8 bit register, which needs 4 parity bits  $(2^4 \ge 8+4+1 = 16 \ge 13)$ , will be like the one shown in figure 3.4.

Each of the parity bits represents a certain number of data bits based on its position. For instance parity bit  $(P_0)$  will represent data bits  $(D_0, D_1, D_3, D_4, D_6...)$ . The way of looking at this logically is by starting at the position of bit  $(P_0)$  skipping a number of bits equal to its position and then taking into account a number of bits also equal to its position. So in the case of bit  $(P_0)$  being in position 1 we would skip 1 bit, then take 1 bit, then skip 1 bit,...etc, until the end of the code word is reached. Once again using the 12 bit code word in figure 3.4, the bits represented by parity bits  $(P_{0-3})$  will be as shown in figure 3.5.

This relation between parity bits and data bits is characterised as Exclusive OR (XOR) behaviour. So the equations for each of the parity bits in the 12 bit code word

| Position  | 12             | 11    | 10    | 9     | 8     | 7     | 6     | 5     | 4     | 3     | 2     | 1              |

|-----------|----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------------|

| Code Word | D <sub>7</sub> | $D_6$ | $D_5$ | $D_4$ | $P_3$ | $D_3$ | $D_2$ | $D_1$ | $P_2$ | $D_0$ | $P_1$ | Ρ <sub>0</sub> |

Figure 3.4: Code Word for an EDAC(12,8).

| Po             | D <sub>7</sub> | D <sub>6</sub> | $D_5$ | $D_4$ |                | D <sub>3</sub> | $D_2$          | $D_1$ |                | D <sub>0</sub> |                | Po |

|----------------|----------------|----------------|-------|-------|----------------|----------------|----------------|-------|----------------|----------------|----------------|----|

| P <sub>1</sub> | D <sub>7</sub> | D <sub>6</sub> | $D_5$ | $D_4$ |                | D <sub>3</sub> | D <sub>2</sub> | $D_1$ |                | D <sub>0</sub> | Ρ <sub>1</sub> |    |

| P <sub>2</sub> | D <sub>7</sub> | $D_6$          | $D_5$ | $D_4$ |                | $D_3$          | $D_2$          | $D_1$ | P <sub>2</sub> | D <sub>0</sub> |                |    |

| P <sub>3</sub> | D <sub>7</sub> | D <sub>6</sub> | $D_5$ | $D_4$ | P <sub>3</sub> | $D_3$          | D <sub>2</sub> | $D_1$ |                | D <sub>0</sub> |                |    |

Figure 3.5: Data Bits represented by Parity Bits in an EDAC(12,8).

are as follows:

$$P_0 = D_0 \oplus D_1 \oplus D_3 \oplus D_4 \oplus D_6$$

$$P_1 = D_0 \oplus D_2 \oplus D_3 \oplus D_5 \oplus D_6$$

$$P_2 = D_1 \oplus D_2 \oplus D_3 \oplus D_7$$

$$P_3 = D_4 \oplus D_5 \oplus D_6 \oplus D_7$$

Once the parity bits are generated at both the input and the output of the memory element, they are compared to generate the check bits. This comparison also follows XOR behaviour.

$$C_n = P_n(in) \oplus P_n(out) \tag{3.2}$$

Using the check bits, the EDAC can detect errors in the data bits following the truth table shown in figure 3.6. This is then used to decide which data bits need correction. A full diagram representing the entire system can be seen in figure 3.7.

| C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> | Error in Data Bit |

|----------------|----------------|----------------|----------------|-------------------|

| 0              | 0              | 0              | 0              | None              |

| 0              | 0              | 0              | 1              | Parity bit        |

| 0              | 0              | 1              | 0              | Parity bit        |

| 0              | 0              | 1              | 1              | D <sub>0</sub>    |

| 0              | 1              | 0              | 0              | Parity bit        |

| 0              | 1              | 0              | 1              | $D_1$             |

| 0              | 1              | 1              | 0              | D <sub>2</sub>    |

| 0              | 1              | 1              | 1              | D <sub>3</sub>    |

| 1              | 0              | 0              | 0              | Parity bit        |

| 1              | 0              | 0              | 1              | $D_4$             |

| 1              | 0              | 1              | 0              | D <sub>5</sub>    |

| 1              | 0              | 1              | 1              | D <sub>6</sub>    |

| 1              | 1              | 0              | 0              | D <sub>7</sub>    |

Figure 3.6: Errors in Data Bits Detected by Check Bits in an EDAC(12,8).

Figure 3.7: Flow diagram for an EDAC(12,8).

### 3.1.3 Reconfiguration and Reallocation

Recovery techniques follow a completely different approach to increasing robustness when compared to mitigation techniques. Recovery, as the name implies, describes any technique that takes place once the error has occurred and subsequently allows the system to recover from it. In the case of none field-programmable devices recovery would imply replacing damaged parts or components for new ones, but in the case of devices such as FPGAs , techniques like reallocation can be deployed. Reallocation is a technique that targets the design implemented in any FPGA like device, with intentions of re-implementing it on another part of the device that has not been affected by permanent faults. Another similar technique that can be applied for system recovery in FPGA like devices, is that of reconfiguration. Here the device would be reprogrammed in order to fix errors that can't be mitigated and are not permanent. The details on recovery techniques will be described in section 3.4.3, after a more in-depth background on FPGAs has been provided for proper understanding of such techniques.

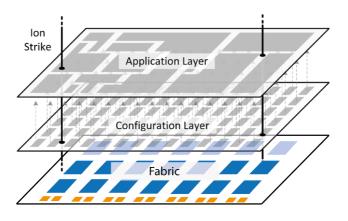

## 3.2 The Peculiar Effect of Radiation on SRAM-based FPGAs

Unlike in ASICs, SEUs have a peculiar effect in FPGAs. When a particle hits the combinational logic in an ASIC, it is interpreted as a transient pulse and depending on its duration it might or might not be latched by a storage cell. When the fault occurs in the sequential logic, it is referred to as a bit-flip and will remain in the storage cells affected until their next load [10]. The difference within FPGAs lies in all the sequential and combinational logic being implemented in Configurable Logic Blocks (CLB) by customizable logic memory cells, SRAM cells. This is known as the configuration memory. A way of looking at this is by segmenting the FPGA in three

Figure 3.8: Conceptual Layers of an FPGA [8].

layers, the application layer, the configuration layer and the fabric, as seen in figure 3.8. Both the application layer and the configuration layer are abstractions of the fabric, the first being the design described in Hardware Description Language (HDL) and the second the configuration establishing this design in the fabric. The fabric is the only real physical layer, containing the CLBs plus all the other elements characteristic of an FPGA architecture. When an upset occurs in the combinational or sequential logic designed in the application layer, it will in reality affect the fabric. Since this physical layer is controlled by the configuration memory, the vast majority of the errors that happen will permanently reconfigure the design until the bitstream is updated and the values of the configuration memory are reestablished to the intended ones.

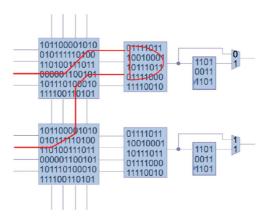

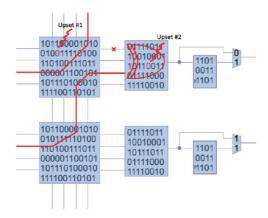

In figure 3.9 we can see the configuration layer. Here an arrangement of logic bits

Figure 3.9: Routing and Logic Before Upset [4].

Figure 3.10: Routing and Logic After Upset[4].

in the SRAM cells are configuring the routing and functioning of the fabric, in order to achieve the design specified in the application layer. The design shown here is that of a simple AND gate. If an upset was to occur in the routing logic within the fabric, it might affect the configuration bits establishing the connections. This in turn could result in one of the inputs of the AND gate getting disconnected. Furthermore, if an upset happened within the Look Up Table (LUT) responsible for the AND gate behaviour, its configuration bits could change and the physical LUT in the fabric could start behaving as a XOR, or any other gate. In this case this would happen by permanently updating the results for the input combinations of the LUT. Both this events can drastically change the functioning of the digital circuit, as can be seen in figure 3.10.

Not all impacts from radiation will actually affect the design. If a SEU takes place in the part of the fabric where none of the elements are being used, the effects of the SEU will still be felt by the FPGA but the design wont be affected and will continue

Figure 3.11: Classification of Configuration Bits by Criticality.

functioning as normal. Furthermore, even in the case that the part of the fabric affected is being used by the design, the configuration bit affected by the SEU, in this case known as Essential Bits (EB), could still not disturb the normal operation of the design. Configuration bits that disturb the functioning of the design when affected by SEUs are called Critical Bits (CB). A relationship that explains the concept of bit importance can be seen in figure 3.11.

### 3.3 Architectural overview of 7-series Xilinx FPGAs

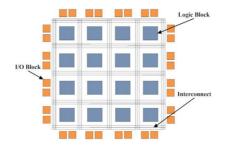

Given the insight into the effects of SEUs in FPGAs presented in the last section, some clarifications as to what the fabric of the FPGA is actually composed of are required. The architecture of the 7-series FPGAs can be described as a column based Advanced Silicon Modular Block (ASMBL) architecture [20]. This architecture changes from family to family, yet the differences are minor and reserved to only some changes in the column fabric related to the number and type of columns available. For simplicity purposes we will use a simplified model of the Xilinx FPGA architecture in order to describe its main components, figure 3.12.

In the figure we can observe the center of the chip being surrounded by Input and Output Blocks (IOB), this elements of the fabric are what allow the chip to communicate with the external world. At the center of the chip the CLBs can be found. These blocks are the main logic resource for implementation of sequential as well as combinational circuits and thus essentially contain the designed digital circuit. Both the IOBs and CLBs are connected by customizable routing resources, commonly referred to as the Interconnect Resources (IR), generally consisting of wire segments and Switch Matrices (SM) made up by Programmable Interconnect Points (PIP) [12]. The fabric will also have other silicone based elements such as Block RAMs (BRAM) or Clock Management Tiles (CMT) that will still be managed by the configuration memory, just like the IRs, the IOBs and CLBs. A more detailed view of the complex 7- series architecture can be observed in figure 3.13.

Figure 3.12: Simplified FPGA Fabric[1].

Figure 3.13: 7 series FPGA Fabric.

IR in Xilinx 7-series FPGAs As mentioned before the IR structure is mostly composed of wire segments and SMs. The SMs are considered a key routing structure between the CLBs [12]. It is through these SMs that the FPGA can achieve flexibility in its implementation of the design. The SMs are composed of PIPs consisting of one or several transmission gates separately controlled by configuration bits. There are three types of PIPs present in FPGAs, seen in figure 3.14, the Break-point PIP, the Cross-point PIP and the multiplexers (MUXs) [16]. Another element present in the IR is the buffer. Buffers are similar to PIPs with the exception that they only connect elements in a specific direction. The totality of the IRs can take up to 80% of the available space depending on the FPGA and is referred to as the global IRs. The individual SM connecting to each CLB, as seen in figure 3.15, are considered local IRs.

**CLB in Xilinx 7-series FPGAs** Each of the Xilinx 7-series CLBs is composed of two slices and connected to a SM for access to the global IRs, figure 3.15. Both slides individually consist of four 6-input LUTs plus their eight FFs, multiplexers and arithmetic carry logic. The LUTs as well as the FFs can carry out different functions depending on their configuration bits and the arrangement of all the elements within the CLB depends on the configuration memory. The only exception would be that

Figure 3.14: Types of PIPs. (a)Break-point PIP.(b)Cross-point PIP.(c)MUX..

Figure 3.15: Slices within CLB.

of the internal state of the FFs, which are independent, with their values changing based on the design and its clock cycles.

Xilinx's System on a Chip (SOC) devices Given our board of choice, the zyboz7020 with a ZYNQ SoC FPGA, a brief explanation of the particular architecture of SOC FPGA devices has to be given. These FPGA chips are composed of two different parts, the Programmable System (PS) and the Programmable Logic (PL). The PS is a silicon implemented microcontroller, in our case an ARM. The PL is the part of the chip characteristic of any FPGA and in our case it is equivalent to the Artix7 family of FPGAs. The combination of this to parts is what constitutes a SOC, as can be seen in figure 3.16. The PS in the zybo-z7020 is responsible for UART communication with the computer, meaning that all designs implemented in the zybo that use UART will have to be connected to the ARM by means of a block design. With the ARM itself being programmed in C through Xilinx's SDK platform

Figure 3.16: Xilinx SoC Architecture.

#### [14].

Based on this general description of the Xilinx 7-series architecture, the contents of the configuration data for an SRAM FPGA define the values held in LUTs and RAMs, the interconnection between resources, and the modes of the resources [7]. With the exception of the internal state of FFs and the PS

## 3.4 SEU Mitigation and Recovery for FPGAs

When design based mitigation techniques are applied to digital circuits inside FPGAs, we say the mitigation is being implemented at the High-Level description. Referring back to figure 3.8 this high level description is the application layer, so any mitigation technique applied here will inevitably be implemented in the fabric by the configuration memory, just as usual. This poses a great problem for FPGA designs with SEU mitigation, due to mitigation techniques only preventing errors as long as their configuration bits are not affected by ionizing radiation, something that is bound to happen in aggressive environments such as space. In order to supplement mitigation techniques applied in FPGA designs, recovery techniques have to be deployed alongside them. Recovery techniques make sure that the configuration bitstream remains the same as the originally intended, fixing any errors in the configuration bits. A flowchart analysis of the different mitigation and recovery techniques can be seen in figure 3.17.

Figure 3.17: Top Down Flowchart for Fault Tolerant Techniques.

The flowchart shows a top-down classification of the different fault tolerant techniques that can be used. Given the nature of FPGAs and their configuration memories, the first important distinction is that of the elements from the fabric that don't depend on the configuration layer. In the case of Xilinx 7 series FPGAs the only elements not dependent on the configuration memory are the Flip Flops (FF), particularly their internal state. Once the physical element distinction has been made the type of fault tolerance methodology to be followed has to be selected. When following the recovery methodology it is critical to consider the type of error, as they will require different treatments. When following the mitigation methodology the most important distinction lays in the design elements, as the way to mitigate errors in them will differ. In order to know which techniques to apply depending on the design its important to know the physical elements used by the FPGA when implementing the design, as mentioned in section 3.3.

### 3.4.1 TMR in FPGAs

In the case of following a mitigation methodology for FPGA designs implemented by the configuration memory, TMR is the most common technique to be applied. The ways TMR is applied vary in each design, but a general classification of the design elements where it will be deployed at a small scale can still be made and extrapolated to general designs. This classification encompasses three basic types of design elements that are present in most, somewhat complex, FPGA designs. These design elements are Throughput Logic, State-Machine Logic and Input-Output Logic. The first describes any circuit where the output only depends on the inputs and has no feedback loop. The second describes circuits that have loops and depend on different stages of a pipeline. The third describes the connections to the physical inputs and outputs of the FPGA.

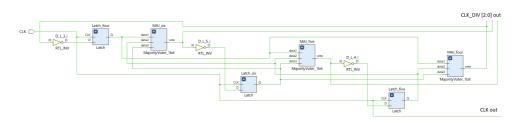

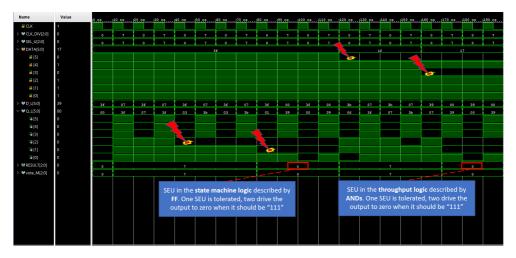

In order to demonstrate the differences in TMR, a simple design was carried out to encapsulate the mitigation of SEUs in Throughput Logic and State-Machine Logic, figure 3.18. The design here would be a real application of the theoretical concept presented in section 3.1.1 figure 3.3. With the addition of a TMR clock divider, figure 3.19, following the theory represented in figure 3.2.

The functioning of this TMR design can be observed in the simulation presented in figure 3.20. Here the waveform shows the behaviour of the different signals. The first signal of interest is that of the DATA signal, this signal is fed directly to the combinational logic blocks which alter it based on typical AND behaviour. The second signal of interest is the output of the FFs which update every clock cycle. During the simulation the impact of a SEU in one of the FFs is replicated by setting the value of its output to '0' when it should be '1'. This kind of SEU induced error is caught by the voters and corrected, as can be seen in the final output, since it shows the correct "111" result. When two of these errors happen at once, in two different FFs, the voter is unable to cope with it and the result signal is driven to zero. A similar behaviour can be seen when simulating a fault in the combinational blocks. When

Figure 3.18: TMR Design for a Combinational Block and a FF with Feedback.

Figure 3.19: TMR Clock Divider.

one of the data lines is forced to a '0', the result signal still maintains its intended "111" value, yet if two data lines experience faults simultaneously the result will be driven to zero as well.

The simulation shows that two errors cannot happen simultaneously in two different lines, no matter if at the combinational or sequential stage, if the result is to be corrected by the voters. Yet in reality this system is capable of dealing with multiple errors due to the MUX select lines feeding the correct value from the voter at a specific frequency. If for instance 2 errors where to occur in the combinational logic while the MUX select line is active, the system will simply just load the previous correct values, hence mitigating the errors. So ultimately the most sensible part of the design are the FFs, since they can only hold one error at a time, independently of the MUX.

Figure 3.20: Waveform Showing TMR Error Mitigation.

### 3.4.2 EDAC in FPGAs

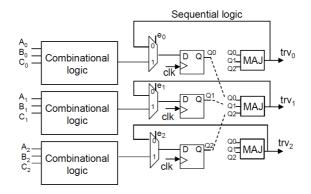

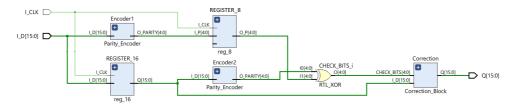

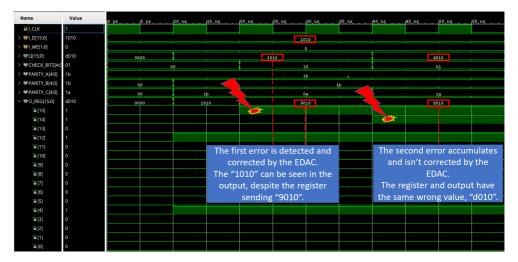

In the case of the internal state of FFs or block RAMs all together, implementing an EDAC into their design is the best way to ensure some mitigation. Based on the theory presented in section 3.1.2, a simple design for a 16 register is proposed in figure 3.21.

The design is composed of two encoders that generate the parity bits by means of XOR gates, two registers, the main one being the 16 bit register where the data is stored and the second one holding the values of the first parity bits generated and a correction block composed of MUXs and NOT gates. The purpose of the encoders is to generate a pair of 5 parity bits, one at the input of the 16 bit register and one at the output, in order to allow for comparison and error detection in the correction block. The correction block follows a behaviour that can be described by means of a truth table with the check-bits as its inputs. This truth table shows which bit of the code-word has the error based on the values of the check-bits, following an

Figure 3.21: EDAC for a 16 Bit Register.

incremental progression where "00001" represents position '0' in the code word and "10101" represents position '20' in the code-word. Based on the specific value of the check-bits the affected bit is restored to its intended value, as can be seen in the waveform shown in figure 3.22.

In the waveform we can observe how an initial SEU impacts the register changing one of its bits from a '0' to a '1'. This is detected by comparing the parity bits thus generating the specific check-bits that in turn are used to correct the output. As can be seen in the waveform during the initial SEU the output of the design remains equal to the input, thus ensuring the correct functioning of the system during the upset. The same cannot be said for the second SEU simulated, since in this case two SEUs are happening at the same time, the EDAC is unable to cope with it and the output changes according to the bits that are affected.

### 3.4.3 Scrubbing in FPGAs

From the two previous sections it is easy to see that mitigation will only work as long as faults do not happen in multiple lines at the same time, in the case of TMR, or as long as they do not affect several bits of a register or a combinational block, in the case of an EDAC. So in order to remove this faults before more occur and eventually accumulate, techniques related to the recovery methodology such as scrubbing can be applied.

But, before diving into the specifics of scrubbing it is essential to understand how the FPGA is configured each time we upload a design, as the same method will be also used when scrubbing the FPGA. The most critical part of the FPGA configuration

Figure 3.22: Waveform Showing EDAC Error Mitigation.

process is a file generated by the Electronic Design Automation (EDA) tools, known as the bitstream. This file contains all the information necessary to program the specific elements inside the fabric that will be a part of the design described in the application layer. This information encompasses all of the elements described by the end of section 3.3 and represents them by means of one or more bits within the bitstream.

In the case of Xilinx FPGAs the bitstream itself is divided into groups of 32-bit words that are known as frames and are the smallest addressable unit of the configuration memory [22]. These frames have addresses that specify their location within the FPGA that can be broken down into specific segments, figure 3.23. A segment of special importance within the frame address is the block type. It contains the three top bits of the frame address and deals with the different resource components of the FPGA, including the CLBs, CLKs, IOBs and more.

The bitstream itself is organized following a general composition shared by every Xilinx FPGA, with a header, a big chunk of configuration data and a footer. The header is a small section containing commands that prepare the FPGA for receiving the configuration data. The footer comes after the data has been transmitted and sends the FPGA into its startup sequence. The size of the bitstream changes depending on the number of frames it contains, which in turn depends on the number of CLBs in the FPGA.

A specific process has to be followed to load the bitstream into the FPGA. This process is carried out by the configuration module, the sole gateway into the previously described configuration memory layer. In general terms, the configuration module evaluates the bitstream and places its data into the configuration memory. It is through this configuration module that any scrubbing technique will take place.

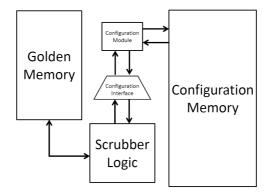

Scrubbing is normally carried out by specific elements designed for that purpose, either processors or finite state machines implemented in FPGA logic. This elements are referred to as scrubbers and are normally composed of three basic components, figure 3.24: a configuration interface that grants them access to the configuration module, some type of processing logic that is capable of both generating read and write commands as well as interpreting data returned by the configuration module

| Address Type   | Bit Index | Description                                                                                                                                |

|----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Block Type     | [25:23]   | Valid block types are CLB, I/O, CLK (000), block RAM content<br>(001), and CFG_CLB (010). A normal bitstream does not<br>include type 011. |

| Top/Bottom Bit | 22        | Select between top-half rows $(0)$ and bottom-half rows $(1)$ .                                                                            |

| Row Address    | [21:17]   | Selects the current row. The row addresses increment from center to top and then reset and increment from center to bottom.                |

| Column Address | [16:7]    | Selects a major column, such as a column of CLBs. Column addresses start at 0 on the left and increase to the right.                       |

| Minor Address  | [6:0]     | Selects a frame within a major column.                                                                                                     |

Figure 3.23: Frame Address Registers [22].

and a golden memory module containing the correct bitstream [4]. Scrubbers tend to work in a deterministic manner, meaning they will scan the configuration memory frame by frame following a specific order. In the case of a SEU in any element linked to the configuration memory, its correspondent bits will be affected and this will be detected by the scrubber while it is doing its scan. The scrubber will then reload the original bitstream stored in its own memory into the FPGA configuration module that will in turn reprogram the FPGA. This will remove any non permanent faults in the physical elements whose internal values, modes or arrangements are controlled by the configuration memory.

The process of scrubbing is much more complex and detailed that the one described here and as such it escapes the scope of this thesis. This is the reason why no scrubbing techniques will be deployed in the application described in the next chapter. Yet, scrubbing is a crucial aspect of FPGA dependability and had to be discussed nevertheless.

### 3.4.4 Design Reallocation in FPGAs

Design reallocation is another recovery technique that can be implemented to cope with permanent faults within the FPGA fabric. It follows a similar process to that of scrubbing with the principal difference being the bitstream that is uploaded into the FPGA. In reallocation, the module responsible for detecting a fault in the configuration memory will also have to detect whether this fault is permanent or not. This could be done by seeing what faults persist after an initial scrubbing process. Once a permanent fault is detected, the module would recognise the configuration memory frame affected. Using the block type data contained in the affected frame, the reallocation module will be able to find out which logic element is permanently damaged. Knowing this the module will then proceed to rewrite the bitstream, with the intention of implementing the design in a different section of the fabric, where no

Figure 3.24: Basic Scrubbing Components [4].

damage has been taken.

This is an even more complex process that scrubbing and as such it will not be implemented in the application either. It is also worth commenting that there is a lot of research being done for advanced reallocation techniques that can maximise the efficiency of the process, so the information presented in this section is a vast simplification meant as an introduction to the concept and nothing more.

# CHAPTER **4** Making and Testing a Dependable and Secure CPU

When considering the subject of dependability for FPGA platforms the idea of protecting an application or design was the intended final outcome. After all, the purpose of any FPGA deployed in space is that of carrying out a specific arrangement of tasks. Yet, this thesis does not present a particular space application, such as image processing or a communication system, in hopes of simplifying the project's approach while maintaining a realistic outlook. In fact, what is presented in this thesis is a basic micro-controller that works with C applications and could in theory carry out all manner of tasks. Furthermore, micro-controllers implemented in FPGAs are fully customizable bringing more and more advantages to the table in the form of improved performance, flexibility and time to market when considering them as SOC devices [10]. Making the choice of a microcontroller as the target design a sensible one.

# 4.1 A simple CPU

In order to cut on development time and avoid overstretching the scope of the thesis, it was decided that an already existing micro-controller design will be used, rather than developing one from the grounds up. The design chosen was a basic CPU developed in a lecture by Dr. Juergen Sauermann [14]. The CPU has a similar instruction set to that of the 8-bit CPUs developed by Atmel, specifically an AVR. The instruction set implemented in the CPU is sufficient to run most C programs, meaning that it can execute our custom workloads. The selection process for the CPU was mostly based on the documentation available and the toolchain provided for generating the memory contents of CPU's program memory. On the technical aspect, priority was given to simple CPUs that had a well known instruction set and were at least 8-bit in size.

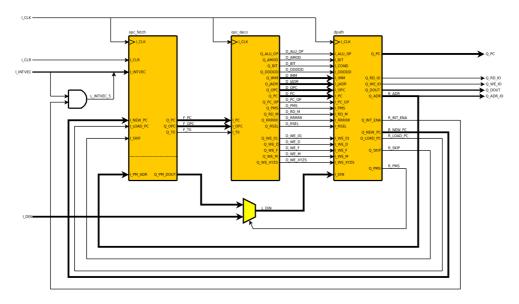

The chosen CPU consists of the CPU core and a external input/output unit (INO) at the design top level, with the CPU core being the actual AVR. This CPU core

Figure 4.1: Block Diagram of CPU Core [14].

is a three stage pipeline formed by an opcode fetch, an opcode decoding and an execution stage, figure 4.1. The fetch stage contains the program memory and drives the Program Counter (PC) and opcodes alongside other signal to the decoder stage. This second stage decodes the opcodes and generates control signal accordingly for the execution stage.

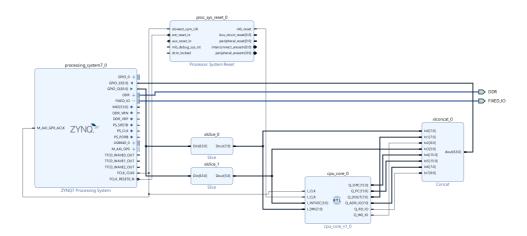

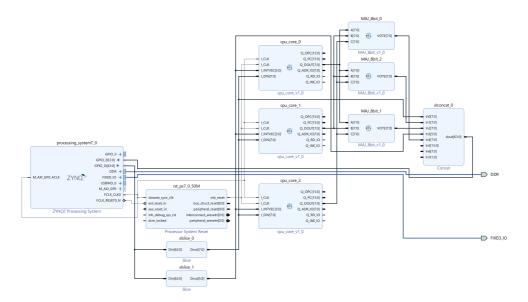

Some changes had to be made when implementing the CPU in our zybo-z7020 FPGA. For instance, the reset signal for the AVR was also used as the control input for the MUXs, meaning some synchronization errors were intrinsic to the design. In order to avoid these meta-stability and synchronization errors, a register was added at the reset input. Another register was also added at the AVR output in order to hold the data going out. Since the CPU was initially designed for a Spartan 3 FPGA some special considerations had to be made with regards to the ARM CPU in our zybo-z7020 FPGA, since it is through this PS that the UART is driven. The ARM's GPIO was connected to the inputs and outputs of the AVR, with the intention of using this SOC as a control unit. It is through the ARM that the communication with the AVR and the external world is carried out. In figure 4.2 we can see the design including the ARM CPU (Zynq7 PS) and other blocks.

## 4.1.1 Preparing a Workload

Having a functioning CPU is not of much use if there is no application to run on it, specially if the reason to get it running in the first place is to test its dependability.

Figure 4.2: Block Diagram of Design Top-Level with ARM CPU.

This is why a workload was designed to represent a realistic use of most of the CPU's resources, with results that can be tested and compared. The workload chosen for the AVR was a basic matrix multiplication, an operation that is representative image processing, a common application in space systems. The workload sends the result from the matrix multiplication to the arm through the outputs of the AVR. The result should always be the same since it was pre-calculated and the matrices never change. The workload was programmed in C and was loaded into the program memory of the AVR by means of a tool-chain provided in [14].

With the workload configured into the AVR's program memory the functioning of the AVR could be tested by running a behavioral simulation in the Vivado suit [14]. Through this simulation it was possible to find out the number of clock cycles that the workload required for completion as well as if the calculations where done correctly by checking the results within the AVR's data memory. Once the functioning of the AVR was demonstrated through simulation it was implemented and simulated postimplementation to ensure it will run perfectly on the zybo-z7020. It was through the completion of this tests that the basic AVR design, before any fault tolerance, was fully developed.

# 4.2 Fault Injection in the CPU

With the basic AVR design complete with a running workload, it would be possible to test its robustness by means of a method called fault injection. Two different models were used to test the device's robustness, statistical fault injection, for the CLBs and block RAM and simulation based injection, for the internal state of the FFs. These models where both provided by my supervisor Dr. David de Andrés Martínez and his PhD student Ilya Tuzov.

## 4.2.1 FPGA-Based Statistical Injection Method

The statistical injection model is based on the process of drawing conclusions for an entire population after conducting a study for a sample taken from that population [17]. In the case of fault injection the conclusions would be the probability of the device failing when injecting faults into its population. The population itself would consist of all the EBs from the configuration memory representing it. Since the two main groups of elements controlled by the configuration memory are the CLBs and BRAMs, these are the two populations that will be tested by the statistical injection method. Since the faults are only injected into the EBs representing the specific population being tested (either CLBs or BRAMs), the probability of failure obtained will represent the percentage of faults within that population that disrupt the functioning of the general design. In our basic AVR design we have 279850 essential bits just for the CLBs alone, so in order to test our entire population we would have to inject faults in each of these bits for each clock cycle, meaning a total of 3917900000 tests to find the exact probability of the design failing according to the CLBs. This would take an unfathomable amount of time and as such the statistical approach is preferred. In order to reduce the amount of tests while maintaining a sensible error margin, the injector is executed with a fixed margin and tests will be carried out until the result is within the pre-established margin. Normally an error margin of  $\pm 0.1$  will be set and the injector will run until the probability of the device is within this margin. The statistical injection of faults adds more complexity to a model that in itself is already quite complex. Normal fault injection requires a deep understanding of both FPGA architecture and software programming in order to understand and develop successful models. The model used here was developed

Figure 4.3: Architecture of the fault injector at the software and hardware layers (as provided by the developers).

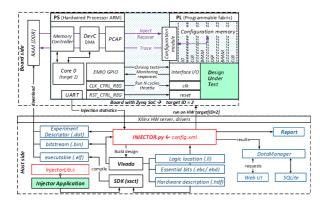

by Ilya Tuvoz and David de Andrés and consists of a high performance fault injector that targets Xilinx Zynq SoC FPGAs, this being the main reason why the device used in the thesis is a zybo-z7020 FPGA. The fault injector can be fully deployed on-chip and presents many advantages regarding accuracy and minimization of interference with the Design Under Test (DUT).

The fault injector, as explained by the developers, consists of three main components: i) a set of hardware targets (board side) connected to the Xilinx's hardware server (host side), ii) a standalone fault injection application executed on these targets (board side), and iii) an experimentation management application run by the host (host side). The two different sides refer to the platforms needed by the injector, the board being the FPGA where it is implemented and the host being the computer running the scripts and communicating with the FPGA by UART. This complex layout can be seen in figure 4.3.

**Board side** The board is responsible for running the fault injection, meaning that it is the one executing the workload for the DUT, monitoring and verifying the DUT's responses and toggling essential bits to emulate SEUs. The board also resets the bitstream after each injection, traces de state of the DUT's writable memory and collects the results, reporting the corresponding statistics back to the host. In our case, with the zybo-z7020, all the infrastructure required to execute this tasks is present in the PS.

**Host side** The host side runs a python script developed by Ilya Tuvoz. This script builds the design in Vivado obtaining the bitstream and corresponding hardware files as well as the essential bits and the logic allocation files. The script also determines the location of the logic cells that should be traced and recovered after injection. These files are used to build an experiment description file that contains all the information required to create a customized template for the DUT. Having the template the script executes SDK and compiles the injector app, which will then be loaded to the device and launched. While the injector runs in the device, the host will start monitoring duties, receiving data and storing it in the database. When the host detects the error margin has been met it will send a command and the injector will stop.

The statistical injector is capable of injecting faults in either the CLBs or the block RAMs, meaning that two tests will have to be carried out in order to obtain accurate results for the DUT's probability of failure. The way to choose where in the configuration memory to inject the faults, as well as other customizable aspects of the injector, is by editing the job description in the python script written by Ilya Tuvoz, shown in Listing 4.1.

```

raw_input("Preconditions fixed, press any key to run the injector >")

jdesc = JobDescriptor(1)

jdesc.UpdateBitstream = 1

jdesc.Blocktype = 1

jdesc.Essential_bits = 1

```

```

jdesc.CheckRecovery = 1

6

jdesc.LogTimeout = 5000

8

jdesc.StartIndex = 0

jdesc.Masked = 0

9

idesc.Failures = 0

jdesc.sample_size_goal = 0

jdesc.error_margin_goal = float(0.1)

jdesc.FaultMultiplicity = 1

jdesc.PopulationSize = float(14000)*Injector.

14

EssentialBitsPerBlockType[jdesc.Blocktype]

jdesc.Mode = 100

#Very custom injection mode (without callbacks)

jdesc.SamplingWithoutRepetition = 0

16

res = Injector.run(OperatingModes.SampleUntilErrorMargin, jdesc,

18

False)

```

Listing 4.1: Job Description Variables in the Python Script.

The Blocktype variable refers to the first address type from the configuration memory frames. By changing this variable we can control which resource to inject faults at. The Esssential\_bits variable controls whether the injector will introduce faults into all the bits of the configuration memory or only those used by the design. The error\_margin\_goal establishes the margin towards which the injector will aim, the lower we set this value the more tests the injector will carry out. Finally, another important variable is the FaultMultiplicity, this variable controls the number of bit-flips that will take place at the same time, meaning the number of SEUs simulated on the same instant in time. By increasing this variable we can simulate harsher radiation environments.

### 4.2.1.1 The Difficulties of Statistical Fault Injection

The statistical injection model presented above works at the theoretical level, yet when implemented into the FPGA things change. Xilinx does not provide any information regarding the correlation between the bitstream and the elements of the fabric, making it hard to know what is being changed when a bit from the bitstream is flipped. The only exception being the LUTs and BRAMs, as these two elements can be located due to the mask provided in the logic allocation file generated by Vivado. The PIPs on the other hand remain a complete mystery, making changes in the bitstream really hard to trace.