# Escola Tècnica Superior d'Enginyeria Informàtica Universitat Politècnica de València

# Mejorar las prestaciones del prefetcher utilizando técnicas de deep learning

TRABAJO FIN DE GRADO

Grado en Ingeniería Informática

Autor: Manel Lurbe Sempere

Tutores: Julio Sahuquillo Borrás

Salvador Vicente Petit Martí

Director experimental: Josué Feliu Pérez

Curso 2018-2019

# Glosario

- **API** Constituye una interfaz de programación de aplicaciones (*Application Programming Interface*). Es un conjunto de rutinas que provee acceso a funciones de un determinado software. 27, 35, 50

- array Vector de elementos.. 40

- **bash** Programa informático, cuya función consiste en interpretar órdenes, y un lenguaje de consola. 50

- **benchmark** Consiste en una prueba de rendimiento o comparativa. Es una técnica utilizada para medir el rendimiento de un sistema o uno de sus componentes, y poder comparar los resultados con máquinas similares. 25, 27, 29, 32, 41, 51

- **caché** Componente de hardware que almacena datos para que las solicitudes futuras de esos datos se puedan atender con mayor rapidez. 1, 2, 11–13, 19, 24

- **deep learning** Conjunto de algoritmos de aprendizaje automático que intenta modelar abstracciones de alto nivel en datos usando arquitecturas computacionales que admiten transformaciones no lineales múltiples e iterativas de datos expresados en forma matricial o tensorial. 5, 11, 14–16, 50

- **DSCR** Data Streams Control Register. Registro de control del prefetch en procesadores IBM POWER8. 20–22, 27, 29, 34, 35, 39, 40

- **eDRAM** *embedded DRAM* (o «DRAM embebida»). Tipo de memoria dinámica de acceso aleatorio basada en condensadores que se integra en el mismo encapsulado que un microprocesador. 12, 20

- framework Entorno de trabajo o marco de trabajo, que consta de un conjunto estandarizado de conceptos, prácticas y criterios para enfocar un tipo de problemática particular que sirve como referencia, para enfrentar y resolver nuevos problemas de índole similar. 8

- **funciones de loss** Mide que tan insatisfechas resultan las predicciones de un modelo de *machine learning* con respecto a una respuesta correcta. 17, 36, 41

- hardware Conjunto de elementos físicos o materiales que constituyen una computadora o un sistema informático. 2–4, 7, 8, 13, 19, 24, 25, 30, 35, 49, 50

- hit Acierto. En el ámbito de memorias de computadores, cuándo una aplicación solicita un dato y este se encuentra en una memoria caché. 11, 13

IV Glossary

**kernel de Linux** Corresponde al núcleo del sistema que se encarga de manejar los recursos hardware, en este caso se llama Linux. 19

- **Ley de Moore** Expresa que aproximadamente cada dos años se duplica el número de transistores en un microprocesador. 1

- **LLC** *Last level cache*. Corresponde a la denominación de la caché de último nivel en las jerarquías de memoria. 2, 12

- machine learning Aprendizaje automático. Estudio científico de algoritmos y modelos estadísticos que los sistemas informáticos utilizan para realizar una tarea específica sin utilizar instrucciones explícitas, sino que se basan en patrones e inferencias.. 1–5, 13–16, 27, 35, 49

- miss Fallo. En el ámbito de memorias de computadores, cuándo una aplicación solicita un dato y este no se encuentra en una memoria caché. Esto genera un acceso a memoria principal o un nivel inferior de la jerarquía. 11, 13

- on-chip Referido a los componentes que están incluidos en el propio chip. 19

- **overfitting** Sobreajuste. En aprendizaje automático, efecto de sobreentrenar un algoritmo de aprendizaje con unos ciertos datos para los que se conoce el resultado deseado. 17, 38

- PID *Process Identifier*. Identificador de proceso dentro de un sistema informático. 22 prefetch Prebúsqueda. 3–5, 7, 13, 20, 22, 25, 26, 29–32, 40, 42–47, 50 prefetcher Mecanismo de prebúsqueda. 2–5, 7, 8, 13, 20, 22, 24, 27, 29, 30, 46, 49

- red neuronal artificial Modelo computacional vagamente inspirado en el comportamiento observado en el funcionamiento de las neuronas humanas. Consiste en un conjunto de unidades, llamadas neuronas artificiales, conectadas entre sí para transmitirse señales. La información de entrada atraviesa la red neuronal (donde se somete a diversas operaciones) produciendo unos valores de salida. 4, 5, 13–15, 27, 30–32, 35, 38

- registro Memoria de alta velocidad y poca capacidad que integran los procesadores, algunos registros tienen funciones de hardware específicas y pueden ser de solo lectura o solo de escritura. 20

- script Archivo de texto plano que almacena distintas ordenes de consola para facilitar la ejecución de comandos. 26, 49

- **shell** Intérprete de órdenes o intérprete de comandos. Es el programa informático que provee una interfaz de usuario para acceder a los servicios del sistema operativo. 26

- **SMT** Simultaneous Multithreading. Se refiere a la posibilidad de ejecutar múltiples subprocesos y tareas simultáneamente en un mismo núcleo de un procesador. 8, 19

- **software** Representa un conjunto de programas y rutinas que permiten a la computadora realizar determinadas tareas. 8, 13, 27

- **SRAM** *Static Random Access Memory*. Tipo de tecnología de memoria RAM basada en semiconductores, capaz de mantener los datos, mientras siga alimentada, sin necesidad de circuito de refresco. 19

Glossary

# Resum

Recentment hi ha hagut un gran increment d'aplicacions de les xarxes neuronals gràcies a noves tècniques d'aprenentatge profund (*deep learning*), un nou tipus d'aprenentatge automàtic que ha estat possible gràcies a l'augment de la capacitat de còmput i de l'ús de xarxes neuronals multicapa, les quals actuen com aproximadors universals que permeten modelar relacions no lineals entre dades d'entrada i sortida. En aquest projecte es pretén utilitzar les xarxes neuronals i l'aprenentatge profund per predir quina configuració de la prebúsqueda maximitza les prestacions del sistema executant aplicacions. D'aquesta manera, serà possible establir un model basat en xarxes neuronals que prediga la configuració del *prefetcher* més adequada per a cada aplicació.

Paraules clau: Deep learning, Reds neuronals, Prebúsqueda hardware, Prestacions del sistema

# Resumen

Recientemente ha habido un gran incremento de aplicaciones de las redes neuronales gracias a nuevas técnicas de aprendizaje profundo (*deep learning*), un nuevo tipo de aprendizaje automático que ha sido posible gracias al incremento de la capacidad de cómputo y del uso de redes neuronales multicapa, las cuales actúan como aproximadores universales que permiten modelar relaciones no lineales entre datos de entrada y salida. En este proyecto se pretenden aprovechar las redes neuronales y el aprendizaje profundo para predecir qué configuración de la prebúsqueda maximiza las prestaciones de un sistema ejecutando aplicaciones. De esta manera, será posible establecer un modelo basado en redes neuronales que prediga la configuración del *prefetcher* más adecuada para cada aplicación.

Palabras clave: Deep learning, Redes neuronales, Prebúsqueda hardware, Prestaciones del sistema

# **Abstract**

Recently there has been a large increase in applications of neural networks thanks to new deep learning techniques, a new type of machine learning that has been possible thanks to the increase in computing capacity and the use of multilayer neural networks, which act as universal approximators that allow modeling nonlinear relationships between input and output data. This project aims to use neural networks and deep learning to predict which pre-search configuration maximizes system performance by running applications. In this way, it will be possible to establish a model based on neural networks that predicts the most appropriate prefetcher configuration for each application.

Key words: Deep learning, Neural networks, Prefetch, System perfomance

# Índice general

| Ín | dice | general<br>de figuras<br>de tablas                                             | VII<br>IX<br>IX |

|----|------|--------------------------------------------------------------------------------|-----------------|

| 1  | Intr | oducción                                                                       | 1               |

|    | 1.1  | Descripción del problema                                                       | 1               |

|    | 1.2  | Motivación                                                                     | 2               |

|    | 1.3  | Objetivos                                                                      | 3               |

|    | 1.4  | Impacto esperado                                                               | 3               |

|    | 1.5  | Metodología                                                                    | 3               |

|    | 1.6  | Estructura de la memoria                                                       | 4               |

|    | 1.7  | Convenciones                                                                   | 5               |

| 2  |      | ido del arte                                                                   | 7               |

|    | 2.1  | Trabajos relacionados con el <i>prefetch</i> y la jerarquía de memoria         | 7               |

|    | 2.2  | Trabajos relacionados con la configuración de hardware empleando <i>machi-</i> | c               |

|    | _    | ne learning                                                                    | 8               |

| 3  |      | aceptos básicos                                                                | 11              |

|    | 3.1  |                                                                                | 11              |

|    |      | 3.1.1 Jerarquías de memoria                                                    | 11              |

|    | 2.2  | 3.1.2 Prebúsqueda                                                              | 12<br>13        |

|    | 3.2  | Machine learning                                                               | 13              |

|    |      | 3.2.2 Terminología básica                                                      | 15              |

| 4  | Ent  |                                                                                | 19              |

| 4  | 4.1  | orno de trabajo<br>Arquitectura del sistema                                    | 19              |

|    | 4.1  | 4.1.1 Procesador IBM POWER8                                                    | 19              |

|    |      | 4.1.2 Mecanismos de prebúsqueda en el IBM POWER8                               | 20              |

|    |      | 4.1.3 Configuración del mecanismo de prebúsqueda                               | 22              |

|    | 4.2  |                                                                                | 24              |

|    | 4.3  | Benchmarks SPEC CPU 2006                                                       | 25              |

|    | 4.4  | Herramientas                                                                   | 26              |

| 5  | Con  | ofiguración dinámica de prebúsqueda basada en machine learning                 | 29              |

|    | 5.1  | Efectos de las configuraciones del <i>prefetcher</i> en cada aplicación        | 29              |

|    | 5.2  | Diseño de la propuesta                                                         | 30              |

|    |      | 5.2.1 Obtención de los datos                                                   | 30              |

|    |      | 5.2.2 Diseño de la red neuronal artificial                                     | 35              |

|    | 5.3  | Evaluación de la red neuronal artificial                                       | 36              |

|    | 5.4  | Implementación de la red neuronal artificial en el planificador                | 38              |

| 6  | Res  | ultados experimentales                                                         | 41              |

|    | 6.1  | Análisis de los resultados                                                     | 41              |

| 7  | Con  | aclusiones                                                                     | 49              |

|    | 7 1  | Visión general del trabajo realizado                                           | 49              |

| /III | ÍNDICE GENERAL |

|------|----------------|

|      |                |

| 7          | .2 Relación con los estudios cursados                   | 49<br>50<br><b>53</b> |

|------------|---------------------------------------------------------|-----------------------|

| Apé        | ndices                                                  |                       |

| <b>A</b> ( | Código ejecución de los Benchmarks en lenguaje C        | 55                    |

| В          | Código de la red neuronal artificial en lenguaje Python | 73                    |

# Índice de figuras

| 3.1<br>3.2<br>3.3<br>4.1                                                          | Ejemplo de la estructura de una jerarquía de memoria de tres niveles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12<br>15<br>15                   |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

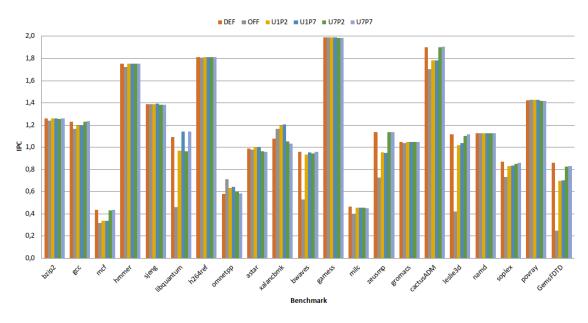

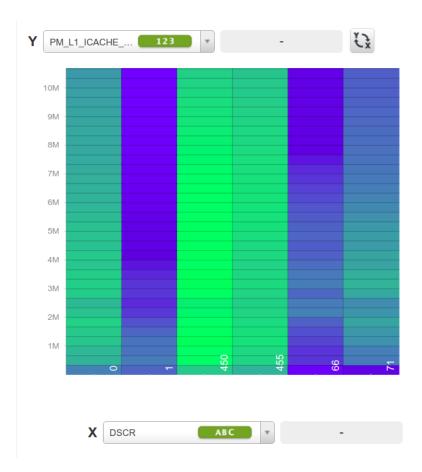

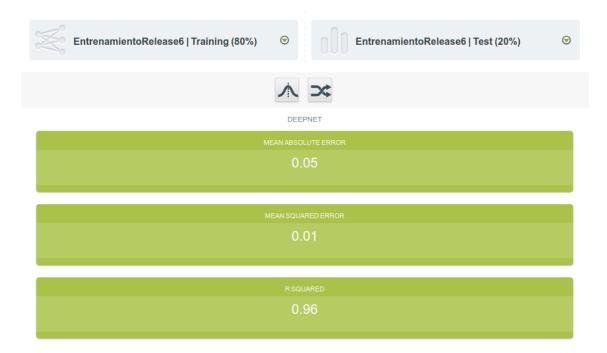

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                                     | IPC de cada una de las aplicaciones en ejecución individual empleando las configuraciones mencionadas anteriormente.  Espacio que representa la relación entre el evento <i>PM_L1_ICACHE_RELOADE</i> y las distintas configuraciones.  Resultados de la evaluación del modelo con los datos de test                                                                                                                                                                                                                                                                                                                                     | 29                               |

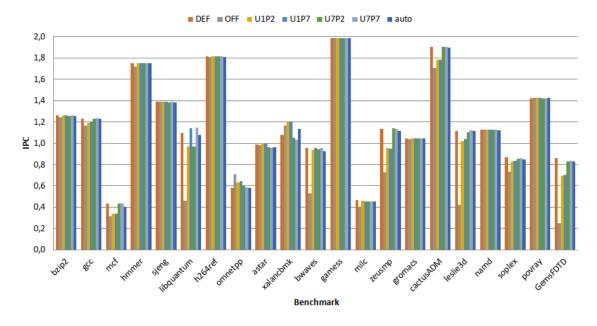

| <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li><li>6.6</li></ul> | Prestaciones de las configuraciones estudiadas y nuestra implementación (auto) para los distintos benchmarks.  Rendimiento de las aplicaciones insensibles a la configuración del prefetch.  Historial de predicciones con respecto al rendimiento real de las aplicaciones insensibles a la configuración del prefetch.  Rendimiento de las aplicaciones sensibles a la configuración del prefetch.  Porcentaje de predicción de las configuraciones del prefetch durante la ejecución de las aplicaciones.  Historial de predicciones con respecto al rendimiento real de las aplicaciones sensibles a la configuración del prefetch. | 41<br>42<br>43<br>44<br>45<br>47 |

|                                                                                   | Índice de tabla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | S                                |

| 4.1<br>4.2                                                                        | Estructura del registro DSCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21<br>22                         |

| <ul><li>5.1</li><li>5.2</li></ul>                                                 | Eventos utilizados como <i>inputs</i> para entrenar la red neuronal artificial que determinará la mejor configuración del <i>prefetch</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                               |

| 0.2                                                                               | haber cuatro contadores cada vez además de las instrucciones y los ciclos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31                               |

# CAPÍTULO 1 Introducción

## 1.1 Descripción del problema

Actualmente existe un auge en el uso de algoritmos de *machine learning* para atacar problemas clásicos, con los que por falta de potencia en los computadores en la época en la que surgían, eran imposibles de implementar de forma eficiente. Con el avance de la tecnología, ha habido un incremento enorme en las prestaciones de los procesadores comerciales, con lo que estos algoritmos se vuelven más atractivos de implementar y utilizar, incluso en sistemas que requieren una respuesta muy rápida por parte de la red neuronal. Uno de los problemas clásicos más importantes, que esta causando más problemáticas los últimos años, es el de la configuración óptima del mecanismo de prebúsqueda.

Los procesos de fabricación de los procesadores han evolucionado de tal forma que permiten cada vez incorporar más transistores en el chip del procesador, como pronosticó la Ley de Moore. Esto ha permitido incrementar el tamaño y número de las memorias caché con el fin de reducir el tiempo medio de acceso a memoria, aprovechando los transistores adicionales incluidos en el chip. Las memorias caché se sitúan entre el procesador y la memoria principal, actuando de intermediarias para ocultar, al estar más cerca del procesador, la latencia de acceso a memoria. Su tamaño, en comparación con la memoria principal, permite que su tiempo de acceso sea mucho más reducido. Estas memorias permiten ocultar en gran medida la latencia de acceso a memoria principal gracias a la localidad que exhiben los datos e instrucciones. La diferencia de velocidad entre la memoria principal y las cachés hizo que los procesadores empezaran a organizar las cachés de manera jerárquica. Normalmente en los procesadores modernos se implementan tres niveles.

Sin embargo, utilizar una jerarquía de cachés no es suficiente para ocultar por completo la latencia de acceso a memoria, lo que puede puede repercutir negativamente en las prestaciones de muchas aplicaciones. Si los datos que necesita el procesador no se encuentran en ninguna de las memorias cachés, la latencia de acceso a los mismos se incrementa significativamente, ya que el tiempo de acceso a memoria principal suele ser superior al centenar de ciclos en los procesadores actuales, lo que conlleva una gran pérdida de prestaciones.

Estos accesos frecuentes a memoria principal suelen ser provocados por dos motivos. El primero viene dado por el incremento de potencia de los procesadores y aumento de su frecuencia de funcionamiento, mientras que en el caso de la evolución de las memorias caché no han habido aumentos tan significativos en su velocidad, sino más bien en sus tamaños, que cada vez son mayores. En segundo lugar, existe una limitación física

2 Introducción

relacionada con los pines que se emplean para acceder al bus de memoria principal que acotan el ancho de banda disponible entre memoria y procesador.

Otra técnica que surge para minimizar la degradación de prestaciones provocada por los lentos accesos a memoria principal es la técnica de prebúsqueda hardware. Esta técnica se emplea para sacar el máximo beneficio de las jerarquías de caché. La prebúsqueda intenta prever qué datos o instrucciones van a ser usados por el procesador en los siguientes ciclos y trasladarlos a las memorias cachés de manera especulativa. Aunque como veremos más adelante en el presente trabajo, no siempre resulta beneficioso su uso o existen muchas configuraciones posibles que podrían mejorar su rendimiento pero es difícil identificar las configuraciones óptimas, poder configurar estos mecanismos de forma dinámica en ejecución para seleccionar la mejor configuración en función de las características de las aplicaciones resultaría una tarea muy interesante.

Este trabajo se enmarca dentro de un proyecto del plan de investigación estatal "Tecnologías Innovadoras de Procesadores, Aceleradores y Redes para Centros de datos y Computación de Altas Prestaciones (T-PARCCA)". El objetivo final de este proyecto es aplicar técnicas de aprendizaje automático o machine learning (en inglés) a distintos mecanismos de la arquitectura del procesador, como la prebúsqueda hardware y la caché compartida. En este trabajo nos centramos en la configuración dinámica de la prebúsqueda hardware. En concreto, se presentan resultados para aplicaciones en ejecución individual en un solo núcleo que servirán de base para el desarrollo de la investigación posterior con un mayor número de núcleos y ejecuciones en paralelo.

#### 1.2 Motivación

Desde el inicio de los primeros procesadores, el aumento de prestaciones en los procesadores ha inquietado a los arquitectos de computadores. A lo largo de los años, mientras los procesadores han ido evolucionando, su complejidad y prestaciones también lo han hecho. Hoy en día los procesadores están compuestos por múltiples núcleos en un mismo chip. Estos cuentan con sus recursos privados y además comparten otros, como son la la memoria principal y la memoria caché de último nivel (LLC), en los casos que la tengan.

Los procesadores modernos implementan mecanismos de prebúsqueda hardware o prefetchers para evitar esta pérdida de prestaciones. Para ello, predicen las instrucciones a ejecutar y los datos que utilizará el procesador y los traen de manera especulativa a la memoria caché. Como estos mecanismos son predicciones, pueden ser verdaderas o falsas, con lo que en algunos casos pueden mejorar el rendimiento de una aplicación, pero por el contrario también pueden empeorarlo.

Por ello, buscar una solución para poder configurar el *prefetcher* en tiempo real, obteniendo las mejores prestaciones para todo tipo de aplicaciones, según la influencia de la prebúsqueda en ella, puede resultar muy interesante.

Hoy en día existe un gran incremento de aplicaciones de las redes neuronales gracias a nuevas técnicas de aprendizaje profundo, un nuevo tipo de aprendizaje automático que ha sido posible gracias al incremento de la capacidad de cómputo y del uso de redes neuronales multicapa, las cuales actúan como aproximadores universales que permiten modelar relaciones no lineales entre datos de entrada y salida. Por esta razón, en este trabajo se estudiará la posibilidad de emplear un planificador dinámico para la configuración del *prefetcher* entrenado con algoritmos de *machine learning*.

1.3 Objetivos 3

# 1.3 Objetivos

En el presente trabajo se pretende utilizar técnicas de aprendizaje automático para implementar un programa que configure de manera dinámica, en tiempo de ejecución, la configuración del *prefetcher* adecuada para cada aplicación, con el fin de alcanzar las máximas prestaciones del sistema. Los objetivos planteados en este proyecto se pueden clasificar en:

- 1. Estudio y selección de las variables y parámetros necesarios para realizar el entrenamiento. El conjunto seleccionado debe proporcionar datos significativos que diferencien entre las configuraciones del *prefetcher* del sistema.

- 2. Diseño e implementación de un programa que obtenga los datos medidos en los contadores hardware y los normalice para realizar el entrenamiento de un modelo de *machine learning*.

- 3. Implementación de un algoritmo de *machine learning* capaz de clasificar las configuraciones del *prefetch* según su rendimiento.

- 4. Pruebas test y resultados teóricos para verificar el comportamiento del algoritmo de *machine learning*.

- 5. Desarrollo de un planificador dinámico que implemente el modelo de *machine lear-ning* para configurar el *prefetcher*.

- 6. Evaluación del modelo entrenado en ejecución real.

## 1.4 Impacto esperado

El procesador *IBM POWER8* dispone de una configuración por defecto que alcanza buenas prestaciones para un rango amplio de aplicaciones, especialmente, cuando se ejecutan solas sobre el sistema. Este problema se agrava cuando existen múltiples aplicaciones en ejecución concurrente.

La configuración por defecto (U4P4) se aplica independientemente del tipo de aplicación que se encuentre en ejecución. Por el contrario, la técnica propuesta permite seleccionar la mejor configuración del *prefetcher* para cada aplicación en cada instante. En consecuencia, permite que el sistema en general consiga mejorar las prestaciones (IPC).

# 1.5 Metodología

Para para cumplir con los objetivos de este trabajo se han seguido los siguientes pasos:

- Estudio sobre trabajos relacionados. Se ha hecho una búsqueda para conocer con detalle las implementaciones de modelos de machine learning para la configuración de la prebúsqueda actualmente en desarrollo o más recientes que resulten interesantes.

- 2. Estudio sobre *machine learning*. Se ha estudiado como implementar algoritmos *machine learning*, cuáles son los pasos para implementar un algoritmo de este tipo y conceptos previos a tener en cuenta.

$oldsymbol{4}$  Introducción

3. Plataforma de trabajo. En este paso se ha estudiado la arquitectura del sistema dónde se realizarán las pruebas y las herramientas que se emplearán durante el desarrollo del mismo.

- 4. Análisis del problema. Este paso se ha desarrollado en las siguientes fases:

- *a*) Primero se ha estudiado el efecto que tienen las diversas configuraciones del *prefetch* en cada aplicación.

- b) En segundo lugar, se estudia el impacto de las diversas características que nos permitan obtener datos significativos para diferenciar entre las configuraciones del *prefetcher* que tenemos.

- c) Para finalizar esta fase, se desarrolla un programa que nos extrae y normaliza los datos de entrenamiento necesarios para entrenar un modelo de *machine learning*.

- 5. Implementación y entrenamiento de un algoritmo de *machine learning* capaz de clasificar los *prefetchers* según su rendimiento.

- 6. Implementación en la máquina real. En este paso se ha elaborado la propuesta de configuración dinámica, eligiendo la mejor configuración del *prefetcher* en función del rendimiento de la aplicación en tiempo real.

- 7. Validación de los resultados obtenidos. Último paso en este trabajo, en el que se valida el modelo en tiempo real mientras se ejecutan diversas aplicaciones para comprobar cuál es el rendimiento obtenido.

## 1.6 Estructura de la memoria

El presente trabajo de fin de grado se divide en los siguientes capítulos.

- Capítulo 2. Estado del arte. En este capítulo se resumen los principales trabajos científicos publicados recientemente relacionados con la temática del presente trabajo, diferenciando entre los trabajos relacionados con la jerarquía de memoria y el prefetch, y el uso de algoritmos de aprendizaje automático para la configuración de hardware.

- Capítulo 3. Conceptos básicos. En este capítulo se pretende introducir a los conceptos básicos que se deben tener en cuenta para entender el funcionamiento de los algoritmos de *machine learning*. Además se realiza una pequeña descripción del subsistema de memoria y los mecanismos de prebúsqueda, relevantes para entender el resto del trabajo.

- Capítulo 4. Entorno de trabajo. Se exponen las herramientas y materiales empleados en el desarrollo del presente trabajo. También se presenta la metodología usada para evaluar la propuesta.

- Capítulo 5. Configuración dinámica de prebúsqueda basada en *machine learning*. En este apartado se realiza el estudio de las diferentes aplicaciones para evaluar su comportamiento en términos de prestaciones empleando diversas configuraciones de *prefetch*. Se realiza un estudio de los mejores contadores de prestaciones disponibles para la posterior implementación de una red neuronal artificial. Se expone y explica como se ha desarrollado la propuesta.

1.7 Convenciones 5

Capítulo 6. Resultados Experimentales. Se ejecutan pruebas y se evalúan los resultados.

- Capítulo 7. Conclusiones. Finalmente, presentaremos las conclusiones alcanzadas al terminar este trabajo, así como futuros posibles trabajos derivados de este e incluso publicaciones del mismo.

- Anexo A, código en C para ejecutar las aplicaciones con el planificador dinámico.

- Anexo B, código en *Python* empleado para ejecutar la red neuronal artificial.

## 1.7 Convenciones

En el desarrollo de la memoria para este trabajo se han seguido las siguientes convenciones:

- Mecanismo de prebúsqueda y prebúsqueda se utilizan de forma indistinta con prefetcher y prefetch respectivamente.

- Algoritmos de aprendizaje profundo y aprendizaje automático se usan de manera indistinta con algoritmos de *deep learning* o *machine learning*.

- Se han escrito en cursiva las siglas, nombres propios de aplicaciones, procesadores, algoritmos y palabras extranjeras.

# CAPÍTULO 2 Estado del arte

En el presente capítulo se nombran los principales trabajos científicos publicados recientemente relacionados con la temática del presente trabajo, diferenciando entre los trabajos relacionados con la jerarquía de memoria y el *prefetch*, y el uso de algoritmos de aprendizaje automático para la configuración de hardware.

# 2.1 Trabajos relacionados con el *prefetch* y la jerarquía de memoria

La prebúsqueda de datos se ha investigado durante mucho tiempo y sigue siendo un tema de investigación activo, ya que puede afectar en gran medida el rendimiento de la jerarquía de memoria.

El estudio realizado en [6], propone *ADP*, que apaga el prefetcher en núcleos específicos cuando no se esperan beneficios locales o se está interfiriendo negativamente con otros núcleos. El componente clave de *ADP* es la política de activación que debe prever cuándo será beneficiosa la captación previa sin que el prefetcher esté activo. El prefetcher propuesto mejora tanto el rendimiento como el consumo energético.

En el trabajo realizado en [7], se propone *weighted-majority filter*, una forma experta de predecir la utilidad de las direcciones de memoria por parte de la prebúsqueda. El filtro propuesto es de naturaleza adaptativa y utiliza la predicción de los mejores predictores de un conjunto de predictores. Este filtro es ortogonal al algoritmo de captación previa subyacente.

Un trabajo anterior realizado en nuestra escuela [8], propone *Bandwidth-Aware Prefetcher Configuration* (BAPC), una estrategia de prebúsqueda que elige la mejor configuración para cada aplicación en cargas multiprogramadas ejecutándose en un sistema *IBM POWER8*. La propuesta se basa en la caracterización del comportamiento de las aplicaciones, en términos de prestaciones y consumo de ancho de banda. El estudio caracteriza las aplicaciones *prefetch friendly* en dos grandes grupos: *prefetch-configuration sensitive* y *prefetch-configuration insensitive*. La propuesta persigue aumentar el ancho de banda disponible eligiendo la configuración con menor demanda de este recurso para las aplicaciones *prefetch unfriendly* y *prefetch-configuration insensitive*.

8 Estado del arte

# 2.2 Trabajos relacionados con la configuración de hardware empleando *machine learning*

El uso de algoritmos de aprendizaje automático para optimizar programas y sistemas se ha convertido en una tendencia popular para las comunidades de investigación de arquitectura, ya que se ha vuelto eficaz para resolver problemas no lineales, como la predicción y el ajuste del rendimiento.

En [9], los autores proponen una metodología basada en el aprendizaje automático para seleccionar cuál de los 4 *prefetchers* disponibles en los procesadores *Intel Core* 2 *Quad* debe activarse o desactivarse.

Otros trabajos recientes [10], propone un *framework* para la configuración dinámica del SMT (subprocesamiento múltiple simultáneo) basado en predicción (PBDST), para ajustar el recuento de subprocesos en los núcleos SMT de los procesadores *IBM POWER8* mediante el uso de algoritmos de aprendizaje automático. Su innovación radica en la adopción de predicciones de configuración SMT en línea derivadas del perfil de nivel de microarquitectura, para regular el recuento de hilos que podrían lograr un rendimiento casi óptimo.

El artículo [11] estudia el efecto de la prebúsqueda hardware en el código multiproceso y presenta una técnica de aprendizaje automático para predecir la combinación óptima de mecanismos de prebúsqueda para una aplicación determinada.

En [12] se estudian dos tipos de técnicas de prebúsqueda que están disponibles en un procesador *Intel Xeon Phi* de 61 núcleos, prebúsqueda software (guiada por compilador) y prebúsqueda hardware en una variedad de cargas de trabajo. Se emplean técnicas de aprendizaje automático, sintetizan las fases de la carga de trabajo y la secuencia de los patrones de fase utilizando datos de rendimiento de contadores de hardware, tales como el ancho de banda de memoria, índices de fallas, prebúsquedas previas emitidas, etc.

En la publicación [13], se demuestra el potencial del aprendizaje profundo para abordar el cuello de botella de  $von\ Neumann^1$  en el rendimiento de la memoria. Se centran en aprender patrones de acceso a la memoria, con el objetivo de construir *prefetchers* de memoria precisos y eficientes. Relacionan las estrategias contemporáneas de prebúsqueda con los modelos de n-gramas $^2$  en el procesamiento del lenguaje natural, y demuestran cómo las redes neuronales recurrentes $^3$  pueden servir como un reemplazo directo.

Los autores del artículo [14], presentan como la localidad semántica puede capturar la relación entre los datos de una manera independiente del diseño de datos real, y argumentan que la localidad semántica trasciende en las preocupaciones espacio-temporales. Además, presentan el *context-based prefetcher*, que se aproxima a la localidad semántica mediante el aprendizaje por refuerzo (redes neuronales recurrentes). El prefetcher identifica patrones de acceso a memoria mediante la aplicación de métodos de aprendizaje por refuerzo sobre la máquina y los atributos de código, que proporcionan pistas sobre la semántica de acceso a la memoria. Demuestran que, el *context-based prefetcher*, hace posible

<sup>&</sup>lt;sup>1</sup>Idea de que el rendimiento del sistema informático es limitado debido a la capacidad relativa de los procesadores en comparación con las tasas máximas de transferencia de datos. Según esta descripción de la arquitectura de los computadores, un procesador está inactivo durante un cierto tiempo mientras se accede a la memoria.

<sup>&</sup>lt;sup>2</sup>Tipo de modelo probabilístico que permite hacer una predicción estadística del próximo elemento de una secuencia de elementos sucedida hasta el momento.

<sup>&</sup>lt;sup>3</sup>Área del aprendizaje automático inspirada en la psicología conductista, cuya ocupación es determinar qué acciones debe escoger un agente de software en un entorno dado con el fin de maximizar alguna noción de «recompensa» o premio acumulado.

que, implementaciones ingenuas basadas en punteros de algoritmos irregulares, logren un rendimiento comparable al del código espacialmente optimizado.

Por último en [15], presentan un esquema dinámico de ajuste de la prebúsqueda, denominado *Prefetch Automatic Tuner* (PATer). PATer utiliza un modelo de predicción basado en el aprendizaje automático para ajustar dinámicamente la configuración de prebúsqueda en función de los valores de los contadores que monitorizan el rendimiento del hardware. Demuestran que PATer es capaz de acelerar la ejecución de diversas cargas de trabajo hasta 1.4 veces.

# CAPÍTULO 3 Conceptos básicos

En este capítulo se describen los conceptos básicos para facilitar la lectura y la comprensión del resto de capítulos del presente trabajo.

De manera análoga al capítulo anterior, los conceptos se encuentran agrupados según la temática que tratan: aquellos relacionados con los mecanismos de reducción de la latencia de acceso a memoria en general (y con las técnicas de prebúsqueda en particular), y aquellos relacionados con técnicas de *deep learning*.

# 3.1 Mecanismos de reducción de la latencia de acceso a memoria

### 3.1.1. Jerarquías de memoria

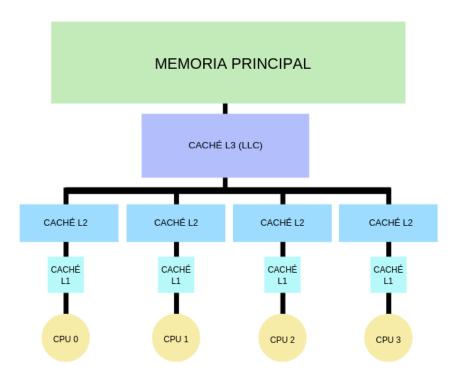

Uno de los mecanismos más utilizados hoy en día para ocultar la latencia de acceso a los datos e instrucciones que emplean los procesadores actuales a la hora de ejecutar aplicaciones son las jerarquías de memoria. Estas consiguen mejorar las prestaciones en la mayoría de los casos, ya que se componen de memorias de tamaños reducidos pero que son extremadamente rápidas. Los procesadores más modernos suelen disponer normalmente de tres niveles de caché organizados de manera jerárquica, como podemos observar en la Figura 3.1. Estas memorias presentan tiempos de acceso menores cuanto más pequeñas son. De esta forma, el primer nivel de caché, integrada en la estructura del procesador, es la más pequeña y rápida de la jerarquía. Siguiendo con esta afirmación, mientras avanzamos por esta jerarquía de memorias cada nivel implica un aumento de la capacidad de estas, sacrificando los tiempos de acceso, que aumentan en cada nivel a medida que se alejan del procesador.

La jerarquía de memoria presenta el funcionamiento que sigue. Cuando el procesador ejecuta una instrucción para acceder a datos en memoria, se hace una búsqueda por todos los niveles de la jerarquía empezando por la caché más cercana al procesador. Si se encuentran los datos en el primer nivel, caché L1 en la Figura 3.1, se produce un acierto (hit en inglés). Por otra lado, si no se encuentran los datos se produce un fallo (miss) en el nivel de caché en el que nos encontremos, y se generaría una petición de búsqueda del dato al nivel adyacente más alejado del procesador, si existe. En el caso de no existir un siguiente nivel, se produciría un acceso a memoria principal, lo que supondría un tiempo de acceso muy elevado que repercutiría negativamente en las prestaciones.

Este problema empeora en procesadores multinúcleo, dónde pueden haber múltiples aplicaciones compitiendo entre ellas por el bus de memoria para acceder a la memoria principal. Esto provoca en los procesadores actuales una perdida de prestaciones impor-

12 Conceptos básicos

tante en la ejecución de aplicaciones, debido a la limitación física de los procesadores actuales para añadir más pines al chip del procesador. Es decir, el número de controladores de memoria que puede incorporar un procesador es limitado.

Figura 3.1: Ejemplo de la estructura de una jerarquía de memoria de tres niveles.

Para evitar las peticiones a memoria principal y conseguir buenas prestaciones, en los ultimos años se han aumentando las capacidades de las memorias cachés de los niveles más alejados del procesador, LLC. Estas cachés se componen de decenas de megabytes teniendo como objetivo aumentar la tasa de aciertos en las cachés, evitando en mayor medida el acceso a memoria principal. Normalmente las cachés de último nivel son compartidas por todos los núcleos del procesador para así tener un mayor aprovechamiento en el caso de que los núcleos vecinos no hagan uso de su espacio, pudiendo utilizarlo otro núcleo que sí lo necesite. A raíz de esto, surge el problema de que se generen interferencias entre núcleos y de esta forma haya un impacto negativo en las prestaciones de las aplicaciones que se esten ejecutando al mismo tiempo. En el caso del procesador empleado en el presente trabajo, el *IBM POWER8*, consta de 80MB empleando la tecnología *embedded DRAM*, eDRAM.

### 3.1.2. Prebúsqueda

El segundo mecanismo de ocultación de la latencia de acceso a memoria y que esta directamente relacionado con el anterior, es el mecanismo de prebúsqueda. Este mecanismo parte de la base de que la mayoría de las veces el uso de las jerarquias de memoria por sí solas no son suficientes para conseguir buenas prestaciones en la ejecución de algunas aplicaciones. A raíz de este problema, surgieron los mecanismos de prebúsqueda. Estos mecanismos intentan predecir qué instrucciones y/o datos va a utilizar el procesador en los siguientes ciclos de ejecución, y trata de traerlos cerca de él (a las cachés más cercanas)

antes de que éste los solicite. En otras palabras, los mecanismos de *prefetch* trabajan de forma paralela a las ejecuciones de las aplicaciones, que mientras están procesando unos datos, los mecanismos de *prefetch* están continuamente realizando peticiones a memoria de datos que posiblemente se vayan a utilizar en los siguientes ciclos y son llevados a las cachés para ocultar el tiempo de acceso a ésta. Esto conlleva, que si se produce un acierto (hit), habrá una reducción importante en la latencia de acceso a los datos. Por otra parte, realizar peticiones mediante especulaciones no siempre termina en aciertos, por lo que las peticiones pueden ser incorrectas o lanzarse demasiado tarde o pronto penalizando en el rendimiento.

Hay dos puntos clave que se deben cumplir en estos mecanismos para que presenten un buen funcionamiento, por un lado qué datos e instrucciones hay que predecir y en segundo lugar, en qué momento deben ser solicitados para que los datos lleguen en el momento idóneo [3].

Generalmente los *prefetchers* se clasifican en función de la tecnología empleada para su implementación. Diferenciamos entre dos tipos:

- Los prefetchers software: Se basan en la implementación de operaciones especiales mediante instrucciones que habitualmente son añadidas por los compiladores. Su objetivo principal es solicitar los datos que se esperan que van a ser necesarios en un momento futuro determinado y de esta forma llevarlos a las cachés. Para poder hacer esto de forma eficiente, el compilador debería conocer la estructura del procesador y el tamaño de las memorias.

- Como es necesario tener de instrucciones específicas en el código de las aplicaciones, se desarrollan compiladores determinados que son capaces de determinar la mejor posición para insertar las instrucciones de *prefetch*. Éstas, no son bloqueantes para el sistema en el caso de fallo (miss), sino que se ejecutan de manera concurrente con las instrucciones de las aplicaciones.

- Los prefetchers hardware: corresponden a lo prefetchers que se basan en una serie de estructuras hardware que son capaces de almacenar las actividades más recientes de las memorias. Hacen uso de hardware dedicado, incluído dentro del procesador, y su función es la de predecir qué datos e instrucciones hay que solicitar a la memoria y llevarlos directamente a las memorias caché. Gracias a la inclusión de este hardware, el cual no se encuentra en una ruta crítica, no contribuye a un incremento de los ciclos del procesador. Por otra parte, también tenemos inconvenientes a la hora de emplear este tipo de prefetcher, como son, la necesidad de disponer del hardware específico y el aumento en el consumo del ancho de banda.

Dado que el procesador *IBM POWER8* empleado en este trabajo dispone de hardware específico para el *prefetcher*, nos centraremos en este último tipo.

# 3.2 Machine learning

### 3.2.1. Definiciones previas

Antes de implementar una red neuronal artificial hay que entender qué son, como funcionan y la base de la que parten. Los conceptos que se describen a continuación han sido extraídos de libro de Jordi Torres [1]

El primer concepto que se debe tener claro para desarrollar una red neuronal artificial es *machine learning* o aprendizaje automático. Éste concepto se define como un subcampo

14 Conceptos básicos

dentro de la inteligencia artificial, en otras palabras, permite a los computadores la capacidad de aprender sin ser programados directamente, para lograr una tarea se indican una serie de reglas que deben seguir, y estos son capaces de aprender de una forma automática. Generalizando, se podría decir que *machine learning* consiste en desarrollar para un problema en particular un algoritmo que sea capaz de predecir respuestas válidas en un escenario determinado. Éstos son capaces de aprender a partir de datos de muestra con el objetivo de encontrar tendencias o patrones, comprender la relación de estos datos, de tal forma que consiguen implementar un modelo capaz de predecir y clasificar elementos. Existen tres grupos principales según el tipo de entrenamiento que reciben para aprender:

- **Aprendizaje supervisado**: cuando los datos que se usan para el entrenamiento incluyen la solución esperada, denominada «etiqueta» (*label* en inglés). Los algoritmos que forman parte de este grupo y más conocidos son *la regresión lineal*, *la regresión logística*, support vector machines, decision trees, random forest y redes neuronales.

- **Aprendizaje no supervisado**: los datos de entrenamiento no incluyen la solución esperada (etiquetas), de tal forma que es tarea del algoritmo clasificar la información. Los algoritmos más populares de este grupo son *clustering* (*K-means*) o *principal component analysis* (*PCA*).

- Reinforcement Learning o aprendizaje por refuerzo: cuando el modelo a implementar, debe explorar un entorno que desconoce y debe determinar que acciones llevar a cabo a modo de prueba y error. Este es capaz de aprender por si solo gracias a las penalizaciones y recompensas que recibe de las acciones que toma. Debe encontrar las mejores estrategias posibles con el fin de obtener una recompensa en tiempo y forma. Este tipo de aprendizaje se puede combinar con los demás tipos.

En segundo lugar, existe el concepto de *Artificial Neural Network* (ANN), o red neuronal artificial, que son sistemas informáticos que se inspiran en las redes neuronales biológicas que constituyen los cerebros, pero no son necesariamente idénticas. Estos sistemas aprenden a realizar tareas considerando ejemplos, generalmente sin ser programados con ninguna regla específica de tareas. Por ejemplo, en el reconocimiento de imágenes, pueden aprender a identificar imágenes que contienen perros analizando imágenes de ejemplo, que se han etiquetado manualmente como «perro» o «no perro», y usar los resultados para identificar perros en otras imágenes distintas. Lo hacen sin ningún conocimiento previo sobre los perros, por ejemplo, que tienen pelaje, colas, bigotes y caras de perros. En su lugar, generan automáticamente características de identificación a partir del material de aprendizaje que procesan.

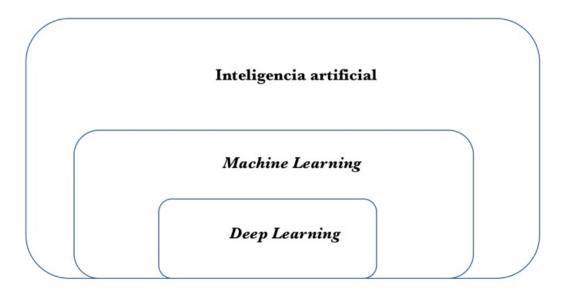

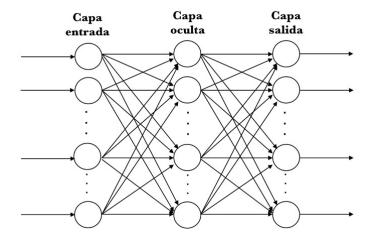

El *deep learning* o aprendizaje profundo es un caso específico del machine learning (Figura 3.2) que emplea redes neuronales artificiales y se define como un algoritmo automático organizado de manera jerárquica o estructural que intenta imitar el aprendizaje humano con el objetivo de obtener unos determinados conocimientos. No requiere ser programado explícitamente, es el propio sistema el cuál es capaz de «aprender» por sí solo para realizar una tarea a través de una de un entrenamiento previo en dicha área. Así mismo, éstos constan de diversas capas de procesamiento para aprender representaciones de datos, con diversos niveles de abstracción que realizan una serie de transformaciones lineales y no lineales sobre estos datos, consiguiendo generar una salida similar a la esperada. En este caso se emplea un aprendizaje supervisado, que consiste en encontrar los parámetros de esas transformaciones (los pesos  $w_i$  y el sesgo b, que veremos en el siguiente punto), consiguiendo que éstas sean lo más óptimas, en otras palabras, la salida generada sea lo más similar a la esperada o que se distancien muy poco. Estos modelos están organizados en tres capas (Figura 3.3):

Figura 3.2: Deep learning es solo una parte de la inteligencia artificial.

Figura 3.3: Una aproximación gráfica simple a una red neuronal artificial.

- Capa de entrada (*Input Layer*): Compuesta por las neuronas que reciben los datos en la entrada, como podría ser un fichero con datos o una imagen .

- Capa oculta (*Hidden Layer*): Consiste en la red que se encarga de realiza los cálculos internos y procesar la información. Puede haber muchas capas en este nivel y con distinsto número de neuronas en cada una de ellas. Además cuantas más neuronas haya en cada capa, más complejos serán dichos cálculos.

- Salida (Output Layer): En última instancia se encuentra la capa de salida que se encarga de entregar cuál es el resultado de los cálculos anteriores.

### 3.2.2. Terminología básica

En este punto se va a describir la terminología básica de *machine learning*, en especial de los algoritmos de *deep learning*, que se emplearan en el desarrollo de la propuesta de este trabajo y que es necesaria conocer previamente al desarrollo de un algoritmo de este tipo.

16 Conceptos básicos

En *machine learning* cuando se habla de *label* (o «etiqueta» en español) se refiere a lo que se está tratando de predecir con un modelo. En cambio, a una variable de entrada se la denomina *feature* («característica» o «variable» en español).

Un modelo define la relación entre *features* y *labels* y tiene dos fases claramente diferenciadas:

- Fase de *training* (entrenamiento o aprendizaje): es cuando se «aprende» o se crea el modelo, a partir de los ejemplos de datos que le mostramos en la entrada y que tiene etiquetados, establece una relación entre ellos de tal forma que consigue aprender iterativamente las relaciones entre los *labels* y las *features* de los ejemplos.

- Fase de *inference* (inferencia o predicción): Consiste en el proceso de realizar predicciones por parte del modelo entrenado anteriormente con ejemplos de datos no etiquetados.

Si consideramos el siguiente ejemplo, consiste en el modelo más simple que expresa la relación lineal entre *labels* y *features*. Éste se expresaría de la forma siguiente:

$$y = wx + b$$

En donde:

- *y*: la etiqueta o *label* de una entrada de ejemplo.

- *x*: la característica o *feature* del ejemplo de la entrada.

- w: representa la pendiente de la recta peso o weigth, constituye uno de los parámetros que el modelo debe aprender durante el proceso de entrenamiento para emplearlo más tarde en el proceso de inferencia.

- *b*: represente el punto de intersección de la recta en el eje sesgo o *bias*. Este es el otro de los parámetros que debe ser aprendido por el modelo.

En el modelo simple presentado anteriormente solamente existe una característica de entrada, en el caso de un algoritmo basado en *deep learning* se pueden presentar muchas variables de entrada, cada una con su peso  $w_i$  asociado. Como ejemplo, mencionaremos un modelo que emplea tres características  $(x_1, x_2, x_3)$ , este podría formularse matemáticamente de la forma siguiente:

$$y = \sum_{i} w_i x_i + b$$

aquí se expresa la suma de los productos escalares entre los vectores X e Y, dónde más tarde se suma el sesgo.

Cuando se entrena un modelo, estos deben aprender los valores idóneos para los parámetros peso y sesgo. En el caso del aprendizaje supervisado, para conseguir dicho objetivo se aplican un algoritmo de aprendizaje automático capaces de obtener los valores para estos. Lo hacen examinando una gran cantidad de ejemplos que habremos etiquetado con la solución e intentará determinar los mejores valores para dichos parámetros minimizando el error entre la predicción y el valor real etiquetado (*loss*).

El *error* o *loss* es un concepto central en *deep learning* que representa la penalización de una mala predicción. Es decir, es un número que indica cuan mala ha sido una predicción

3.2 Machine learning

en un ejemplo concreto (si la predicción del modelo es perfecta, la *loss* es cero). Para determinar este valor, en el proceso de entrenamiento se usan las *funciones de loss*, que es una función matemática que agrega las *loss* individuales obtenidas de los ejemplos de entrada al modelo.

Finalmente, tenemos el concepto de *overfitting* (o «sobreajuste» en español) de un modelo, que se produciría en el caso de que el modelo se ajustara mucho a los ejemplos etiquetados en la entrada, imposibilitando las predicciones correctas por parte de nuestro modelo en ejemplos de datos nuevos que no habría visto antes.

# CAPÍTULO 4

# Entorno de trabajo

En el presente capítulo se describen el hardware y las herramientas utilizadas en el desarrollo de este trabajo.

# 4.1 Arquitectura del sistema

#### 4.1.1. Procesador IBM POWER8

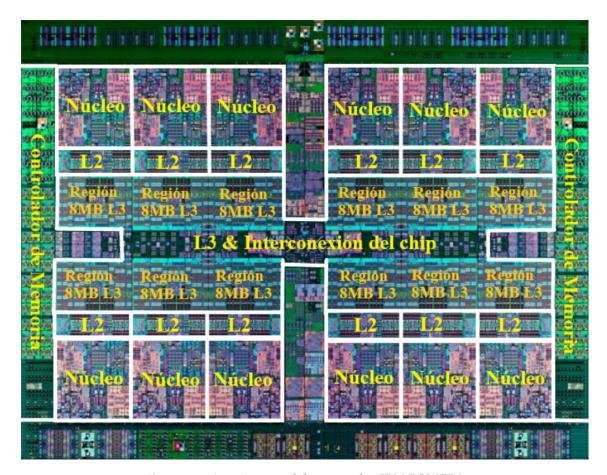

Para el desarrollo del presente trabajo se ha empleado un sistema *IBM Power System S812L*. Este sistema cuenta con un procesador *IBM POWER8*, y da vida a un sistema operativo Ubuntu 14.04¹ con el kernel de Linux 4.0.2. La arquitectura de este procesador puede llegar a soportar doce núcleos funcionando a una frecuencia de 4 GHz con soporte para ejecución simultánea (SMT) de hasta ocho hilos en cada uno de sus núcleos, obteniendo un total de 96 hilos de ejecución simultáneos. En la Figura 4.1 podemos ver cómo se organiza la arquitectura de este procesador.

En nuestro caso no contamos con la versión de doce núcleos, sino que tenemos una versión inferior del procesador que dispone únicamente de diez núcleos funcionando a 3,69 GHz con sólo un módulo de memoria DRAM de 32 GB, aunque comparte la misma arquitectura que la variante de doce núcleos. Como únicamente utiliza uno de los enlaces a memoria principal disponibles, existen núcleos más alejados a la memora principal que otros que están más cerca.

La jerarquía de memoria que ofrece el procesador *IBM POWER8* on-chip, está compuesta por tres niveles:

- **Primer nivel: L1D y L1I.** Este nivel se divide en dos cachés con propósitos diferentes. Una destinada al almacenamiento de datos y la otra para las instrucciones. Cuentan con capacidades de 64KB y 32KB respectivamente y son privadas, es decir, cada núcleo tiene sus propias memorias. Utilizan la tecnología *Static Random Access Memory* (SRAM).

- Segundo nivel: L2. Este nivel cuenta con un tamaño de 512KB y es privado en cada núcleo. Están construidas con la tecnología SRAM al igual que las cachés L1.

- Tercer nivel: L3. Este es el último nivel en la jerarquía de caché on-chip que posee este procesador y cuenta con un tamaño de 80 MB. En este caso, como en la mayoría de procesadores, al ser el último nivel de la jerarquía solo hay una memoria que es

<sup>&</sup>lt;sup>1</sup>Sistema operativo de código abierto basado en GNU/Linux, que actualmente corre en computadores de escritorio y servidores, en arquitecturas Intel, AMD, POWER y ARM.

20 Entorno de trabajo

Figura 4.1: Arquitectura del procesador IBM POWER8.

compartida por todos los núcleos. La tecnología que usa es distinta a la empleada en las mencionadas anteriormente, en este caso utiliza memorias eDRAM, Embedded dynamic random access memory.

### 4.1.2. Mecanismos de prebúsqueda en el IBM POWER8

Prosiguiendo con el subsistema de memoria, el sistema del cual disponemos nos ofrece un sistema de prebúsqueda bastante complejo y sobradamente configurable. El *prefetch* de este procesador dispone de un registro destinado específicamente para la configuración del mismo, este se denomina *Data Streams Control Register*, DSCR. Esta formado por doce campos, como podemos observar en la Tabla 4.1 junto a los bits asociados y la característica que controlan. La complejidad de este *prefetcher* surge de la gran cantidad de configuraciones que existen del mismo, siendo exactos contamos con 2<sup>25</sup> posibles configuraciones distintas, por lo que hacer un uso óptimo de él es una tarea extremadamente complicada.

Seguidamente se se explicarán detalladamente los campos presentados en la Tabla 4.1:

- *Software Transient Enable (SWTE):* Se aplica el atributo de transitorio a los flujos detectados por software.

- *Hardware Transient Enable(HWTE):* Se aplica el atributo de transitorio a los flujos detectados por hardware.

| Nombre del campo                  |

|-----------------------------------|

|                                   |

| Software Transient Enable (SWTE)  |

| Hardware Transient Enable (HWTE)  |

| Store Transient Enable (STE)      |

| Load Transient Enable (LTE)       |

| Software Unit count Enable (SWUE) |

| Hardware Unit count Enable (HWUE) |

| Unit Count (UNITCNT)              |

| Urgency (URG)                     |

| Load Stream Disable (LSD)         |

| Stride-N Stream Enable (SNSE)     |

| Store Stream Enable (SSE)         |

| Default Prefetch Depth (DPFD)     |

|                                   |

Tabla 4.1: Estructura del registro DSCR.

- Store Transient Enable (STE): Se aplica el atributo de transitorio a los flujos de stores.

- *Load Transient Enable (LTE):* Se aplica el atributo de transitorio a los flujos de loads.

- *Software Unit count Enable (SWUE):* Aplica la cuenta de unidades a los flujos definidos por software.

- *Hardware Unit count Enable (HWUE):* Aplica la cuenta de unidades a los flujos definidos por hardware.

- *Unit Count (UNITCNT):* Número de unidades en un flujo de datos. Los flujos de datos que excedan este valor son finalizados.

- **Depth Attainment Urgency (URG):** Representa la velocidad o prioridad con la que las ráfagas de prebúsquedas llegan a la profundidad fijada. De manera equivalente al DPFD, el valor 0 selecciona la urgencia por defecto (urgencia 4). Así pues, la urgencia propiamente dicha varía desde 1 (sin urgencia) hasta 7 (máxima urgencia).

- *Load Stream Disable (LSD)*: Este campo configura la detección e inicialización de ráfagas de loads (load streams).

- *Stride-N Stream Enable (SNSE):* Activa la detección hardware e inicialización de flujos de loads y stores que tienen una separación (stride) mayor que un solo bloque de cache. Estos flujos de loads pueden ser detectados cuando el campo LSD es 0, y los flujos de stores cuando el campo SSE se encuentra a 0 [4].

- Store Stream Enable (SSE): Activa la detección hardware e inicialización de flujos de stores.

- *Default Prefetch Depth (DPFD):* Representa la profundidad de la prebúsqueda en número de bloques. Como se ha comentado anteriormente, un valor 0 selecciona la profundidad por defecto (4 bloques). Por otro lado, el valor 1 indica profundidad nula o prebúsqueda desactivada (independientemente de otros campos de la configuración). Por lo tanto, la profundidad en número de bloques puede ser configurada entre los valores 2 (DPFD=010<sub>2</sub>) y 7 (DPFD=111<sub>2</sub>).

22 Entorno de trabajo

| Configuración | Especificación | Valor |

|---------------|----------------|-------|

| U1P2          | URG=1 DPFD=2   | 66    |

| U1P7          | URG=1 DPFD=7   | 71    |

| U7P2          | URG=7 DPFD=2   | 450   |

| U7P7          | URG=7 DPFD=7   | 455   |

Tabla 4.2: Configuraciones del prefetch utilizadas.

Existen algunos casos especiales dentro de las muchas configuraciones posibles, tales como, cuando tenemos todos los campos de este registro a 0, dicho de otro modo DSCR=0, significa que el *prefetcher* se encuentra en la configuración por defecto. Dicha configuración es equivalente a que los campos de profundidad (DPFD) y urgencia (URG), configurados en el valor 4 para cada uno de ellos. Adicionalmente, estos no son los dos únicos campos se encuentran activos, sino que también existe un campo que al funcionar mediante lógica negativa (LSD), cuando almacena un 0 significa que la característica Load Stream está activada. El resto de campos quedarían desactivados en esta configuración.

Vamos a enfocar el presente trabajo en estudiar la posible viabilidad de una configuración dinámica del *prefetcher*, la cual mejore las prestaciones del sistema respecto a utilizar una única configuración durante toda la ejecución de una aplicación. En otras palabras, que sea capaz de identificar según el tipo de uso del *prefetch* que haga la aplicación durante su ejecución, cual de las posibles configuraciones del *prefetch* sería conveniente utilizar en cada instante de ejecución, cambiando entre ellas cuando sea conveniente. Por esto, se debe estudiar el comportamiento del sistema respecto a las distintas configuraciones posibles. Como hemos dicho antes, la cantidad de posibles configuraciones de este *prefetch* es extremadamente grande, por lo que en este trabajo hemos decidido reducir el análisis y nos hemos centrado en los campos que creemos que pueden resultar más influyentes, como la urgencia (URG) o la profundidad (DPFD). Los demás campos los mantendremos en sus configuraciones por defecto. En la Tabla 4.2 encontramos las configuraciones que emplearemos en el presente estudio.

## 4.1.3. Configuración del mecanismo de prebúsqueda

El registro mencionado anteriormente se puede modificar tanto para un identificador de proceso (*Process Identifier* (PID)) como para el sistema en general. En este trabajo se accede a él de la siguiente forma empleando un código escrito en lenguaje *C* (se expone un programa que posibilita el cambio del valor de dicho registro para un identificador de programa (*PID*) dado):

```

# define _GNU_SOURCE

# include <stdio.h>

# include <stdlib.h>

# include <stdint.h>

# include <unistd.h>

# include <string.h>

# include <sys/ptrace.h>

# include <errno.h>

# define PTRACE_DSCR 44

static int do_dscr_pid(int dscr_state, pid_t pid)

int rc;

```

```

rc = ptrace (PTRACE_ATTACH, pid , NULL , NULL);

14

if(rc) {

15

fprintf(stderr, "Could not attach to process %d to %s the "

16

"DSCR value \n%\n", pid, (dscr_state ? "set" : "get"),

strerror(errno));

18

return rc;

19

20

}

wait (NULL);

rc = ptrace(PTRACE_POKEUSER, pid, PTRACE_DSCR << 3, dscr_state);</pre>

22

23

if (rc) {

fprintf(stderr, "Could not set the DSCR value for pid "

24

" %d\n%s\n", pid, strerror(errno));

25

ptrace(PTRACE_DETACH, pid, NULL, NULL);

26

return rc;

28

rc = ptrace(PTRACE_PEEKUSER, pid, PTRACE_DSCR << 3, NULL);</pre>

29

if (errno) {

30

fprintf(stderr, "Could not get the DSCR value for pid "

31

%d\n%s\n", pid, strerror(errno));

33

rc = -1;

} else {

34

printf("DSCR for pid %d is %d\n", pid, rc);

35

36

ptrace(PTRACE_DETACH, pid, NULL, NULL);

37

return rc;

38

39

int main(int argc, char *argv[])

40

41

pid_t pid = getpid(); //PID del que se tiene que cambiar

42

int dscr_val; //Valor del dscr

43

printf("Executant...\nTinc el pid: %d .\n", pid);

44

printf("Introdueix l'objectiu pid: ");

45

scanf("%d" ,&pid);

46

printf("Introdueix el valor de DSRC: ");

47

48

scanf("%d",&dscr_val);

49

do_dscr_pid(dscr_val, pid);

50

sleep (1);

51

printf("Acabant...\n");

52

```

Para poder utilizar este código se precisa del uso de una función llamada *ptrace*, ésta permite modificar el registro DCSR para cada uno de los procesos que se estén ejecutándo. Dicha función, se describe de la siguiente manera,

```

long ptrace(enum __ptrace_request request, pid_t pid, void *addr, void *data)

```

y permite a un proceso (observador, *tracer*), poder supervisar y controlar la ejecución de otro proceso (observado, *tracee*). Esto nos permite cambiar y examinar la memoria y registros usados por el proceso observado.

Como es necesario emplear la función descrita, hay que asociar los procesos. En las líneas 13-20 se emplea la solicitud *PTRACE\_ATTACH*, que permite empezar el con el control del proceso indicado a partir se su *pid* (identificador de proceso). Una vez asociados los procesos, en las líneas de la 22 a la 28, se realiza una solicitud *PTRACE\_POKEUSER*, que permite acceder al desplazamiento dentro de la pila del proceso que se observa y de este modo poder cambiar el valor por el que indicamos por parámetro. Más tarde, en las líneas 29-36, se comprueba que el valor se escribió correctamente empleando la función *PTRACE\_PEEKUSER*, permitiendo leer parte de la pila en la memoria del proceso que se observa. Por último, en la línea 37, se libera el proceso que se estaba observando

24 Entorno de trabajo

con *PTRACE\_DETACH*, desvinculándolo evitando cualquier tipo de error que pudiese generarse en caso de no hacerlo.

Al final de todo, de las líneas 40 a 52, se expone un pequeño programa de consola para que de manera intuitiva y sencilla, podamos modificar el valor del registro del proceso que indiquemos.

## 4.2 Contadores de prestaciones

Una de las tareas más complejas, aunque importante en los sistemas actuales, es la evaluación de sus prestaciones, debido a que su rendimiento y capacidad de cómputo han sido incrementadas junto con la complejidad de su configuración. Por esto, uno de los temas claves para observar las prestaciones que se obtienen en los sistemas son poder monitorizar el comportamiento de estos, para de esta forma, evaluar la efectividad de las configuraciones o mejoras añadidas.

Esta información de las prestaciones del comportamiento de un sistema se pueden obtener de diversas formas. En primer lugar, mediante el uso de instrucciones dentro del código fuente o en opciones dentro del compilador, lo que conlleva a modificar y aumentar el tamaño del código a evaluar tanto en complejidad como en tamaño. En segundo lugar, se podría medir eventos del sistema empleando contadores de prestaciones, los cuales hacen uso de un <mark>hardware</mark> dedicado dentro del procesador para leer registros destinados a almacenar la información sobre el comportamiento de los sistemas en tiempo de ejecución. Utilizando estos contadores hardware, no precisamos de modificar el código que queremos analizar. Además, son dependientes por completo de la arquitectura del sistema en el que se vayan a usar, por lo que se debe prestar especial atención a los eventos que tengamos disponibles para monitorizar en el sistema que queramos realizar las evaluaciones. Concretamente, el procesador elegido para nuestras pruebas, IBM POWER8, dispone de seis registros dedicados a estos contadores, donde solamente cuatro de ellos pueden ser configurados para monitorizar un evento diferente. Los dos contadores restantes son estáticos y sirven para medir las instrucciones ejecutadas y los ciclos transcurridos. Existen muchísimos eventos que pueden medir infinidad de eventos interesantes, como fallos de caché o fallos de predicción del prefetcher, entre muchos otros.

Existen muchas herramientas para medir estos eventos. En el caso particular de este estudio se ha usado de la herramienta perf<sup>2</sup>, que forma parte del kernel del sistema Linux desde la versión 2.6.31, haciendo uso de la librería *libpfm*<sup>3</sup>. Ésta nos facilita la configuración de los contadores de prestaciones mediante una interfaz genérica, a partir de una lista de eventos. Además, posee traducciones literales de los nombres de los eventos que podemos configurar en los contadores del procesador.

Los eventos monitorizados en este estudio son los que siguen (en el capítulo 5 se comentará la importancia de cada uno de ellos para este trabajo):

- *cycles*: Número de ciclos usados en la ejecución de la aplicación.

- textitinstructions: Número de instrucciones ejecutadas por la aplicación.

- *PM\_L1\_ICACHE\_MISS*: Demandas de instrucciones a caché L1 fallidas.

- *PERF\_COUNT\_HW\_CACHE\_L1D:READ:MISS:* Fallo de lectura en caché L1D debido al *prefetch*.

<sup>&</sup>lt;sup>2</sup>http://man7.org/linux/man-pages/man1/perf.1.html

<sup>&</sup>lt;sup>3</sup>http://perfmon2.sourceforge.net/

- *PERF\_COUNT\_HW\_CACHE\_L1D:WRITE:MISS:* Fallo de escritura en caché L1D debido al *prefetch*.

- *PERF\_COUNT\_HW\_CACHE\_LL:WRITE:MISS:* Fallo de escritura en el último nivel de caché debido al *prefetch*.

- *PM\_DATA\_FROM\_L3*: La memoria caché de datos del procesador se volvió a cargar desde la L3 del núcleo local debido a cargas de demanda.

- *PM\_MEM\_PREF*: Número de accesos a la memoria principal realizados por el *pre- fetcher* en la ejecución de la aplicación.

- PERF\_COUNT\_HW\_CACHE\_L1I:PREFETCH:ACCESS: Accessos del prefetch a lamemoria L1I.

- PERF\_COUNT\_HW\_CACHE\_L1D:PREFETCH:ACCESS: Accessos del prefetch a lamemoria L1D.

- *PM\_MEM\_READ:* Lecturas a memoria principal.

- PM\_L1\_ICACHE\_RELOADED\_PREF: Cuenta todas las recargas debidas al prefeth de la caché L1 de instrucciones.

- *PM\_DATA\_FROM\_MEMORY:* La memoria caché de datos del procesador se volvió a cargar desde una ubicación de memoria que incluye L4 debido a las cargas de demanda.

- *PM\_BR\_MPRED\_CMPL*: Número de predicciones del *prefetch* erróneas.

Para evaluar el rendimiento de las aplicaciones hemos utilizado la siguiente métrica, que nos indica cuantas instrucciones es capaz de ejecutar el procesador en un ciclo de reloj:

■ Instruciones por ciclo (IPC): Número de instrucciones ejecutadas por ciclo de la aplicación.

$$IPC = \frac{Instrucciones\ ejecutadas\ (instructions)}{Ciclos\ usados\ (cycles)}$$

### 4.3 Benchmarks SPEC CPU 2006

En el desarrollo del presente trabajo se han empleado algunos benchmarks de la suite de Standard Performance Evaluation Corporation (SPEC) CPU 2006<sup>4</sup> empleando las entradas reference. Estos benchmarks nos ayudarán a comparar nuestras propuestas o cambios, ya que nos proporcionan una medida estándar o comparable al resto de computadores. Para poder evaluar con el mismo peso todas las aplicaciones de la suite, se ha decidido ejecutar de forma individual, con cada una de las configuraciones del prefetch preseleccionadas (Tabla 4.2), durante 120 segundos. Cuando se han finalizado estas ejecuciones, se ha medido el rendimiento aplicando la métrica anterior y se ha almacenado para su posterior uso.

Se ha empleado esta suite de aplicaciones con el objetivo de obtener una medida comparativa de la intensidad de computación en el amplio rango de opciones del hardware,

<sup>&</sup>lt;sup>4</sup>https://www.spec.org/cpu2006/

**26** Entorno de trabajo

utilizando como base de la aplicación cargas de trabajo desarrolladas por usuarios representativos.

Estas aplicaciones incluidas en el paquete *SPEC CPU2006* [5] usadas en este trabajo, se dividen en dos grupos según el tipo de cálculos que realizan:

- **Aplicaciones de números enteros:** *bzip2, gcc, mcf, hmmer, sjeng, libquantum, h264ref, omnetpp, astar y xalancbmk.*

- **Aplicaciones de coma flotante:** bwaves, gamess, milc, zeusmp,gromacs, cactusAMD, leslie3D, namd, soplex, povray y GemsFDTD.

### 4.4 Herramientas

Para la realización de este trabajo se han usado las siguientes herramientas, además de las mencionadas anteriormente en este capítulo:

• Shell scripts: Se han utilizado estos archivos para agilizar y automatizar el lanzamiento de las aplicaciones mediante comandos, se escriben todos en un mismo fichero y automáticamente se ejecutan unos detrás de otros.

En el ejemplo de arriba, vemos un script que utilizamos para lanzar varias aplicaciones (bucle *for workload*) con diversas configuraciones (bucle *for dscr*), pudiendo guardar los resultados por separado, archivos *trabajo[\${workload}]conf[\${dscr}].txt*, donde *\${workload}* toma el valor de la aplicación que se va a ejecutar y *\${dscr}* toma el valor de la configuración del *prefetch* para esa ejecución. Como se puede observar esto facilita mucho la obtención de datos y su organización de manera automática.

Adicionalmente estos ficheros pueden ejecutar otros shell scripts. Como vemos en el código anterior, existen dos scripts al principio y al final del fichero (l. 1 y l. 11 respectivamente) que son importantes para nuestro trabajo ya que el contenido de dichos scripts hace que la máquina trabaje siempre a la misma frecuencia durante todas las pruebas, con el fin de obtener resultados equiparables.

4.4 Herramientas 27

Programas escritos en lenguaje C: En este trabajo se han empleado programas escritos en lenguaje C para lanzar los benchmarks, así como también poder medir los eventos configurando los contadores de prestaciones mediante la librería libpfm, que hemos mencionado anteriormente, y controlar que su ejecución dure el número de instrucciones correspondiente. Para la ejecución de mezclas se usa un código que también se encarga de controlar el valor de la configuración del prefetcher para cada una de las aplicaciones que la componen. Se ha partido de la infraestructura software base desarrollada por Josué Feliu<sup>5</sup> durante su tesis doctoral. Este software se ha modificado lo suficiente para habilitar el acceso a diferentes contadores de prestaciones, así como hacer posible el acceso a los registros de configuración del prefetcher individual de cada aplicación y permitir la implementación de la propuesta, habilitando adicionalmente, a ejecutar código escrito en Python para llamar a la red neuronal artificial (Anexo B). La versión de código utilizada para el lanzamiento de la propuesta está disponible en el Anexo A. En este código se hace uso de la librería librem, además de la función de cambio de DSCR por código que se mostraba anteriormente.

- **Programas escritos en lenguaje** *Python*<sup>6</sup>: Este lenguaje de programación permite manejar datos de forma muy fácil y rápida, por lo que se ha elegido para implementar programas de procesamiento de datos para su posterior uso en la generación de gráficos, con otras herramientas que mencionaremos más adelante.

- Por otra parte, este lenguaje es compatible con la *API* de *machine lerning* que hemos utilizado para implementar nuestra red neuronal artificial, descrita en el siguiente punto.

- API BigML<sup>7</sup>: Esta API permite realizar en su plataforma online todo el análisis e implementaciones necesarias para resolver un problema de machine learning. Ofrece un amplio abanico de algoritmos tanto supervisados como no supervisados, herramientas para normalización de datos, herramientas para generar nuevos datos, herramientas de entrenamiento y testeo de resultados, almacenamiento en la nube, y lo más importante, procesamiento de datos dedicado para entrenar nuestra red neuronal artificial. Esta API es compatible con algunos lenguajes de programación como Python, Node.js, Ruby, Java, Swift y más.

- Aplicaciones de ofimática *Microsoft Excel*<sup>8</sup> y *Libre Office*<sup>9</sup>: Se han utilizado únicamente para la generación de gráficos a partir de los datos obtenidos.

<sup>&</sup>lt;sup>5</sup>Josué Feliu es el director experimental del presente trabajo.

<sup>&</sup>lt;sup>6</sup>https://www.python.org/

<sup>&</sup>lt;sup>7</sup>https://bigml.com/

<sup>&</sup>lt;sup>8</sup>https://products.office.com/es-es/excel

<sup>&</sup>lt;sup>9</sup>https://es.libreoffice.org/

#### **CAPÍTULO 5**

# Configuración dinámica de prebúsqueda basada en machine learning

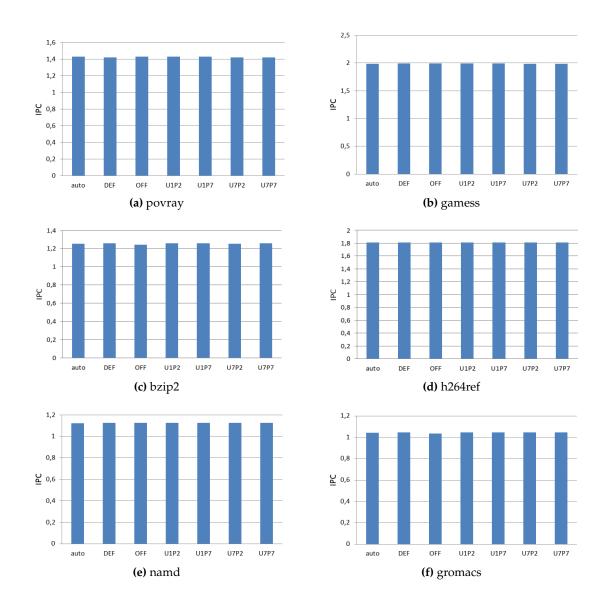

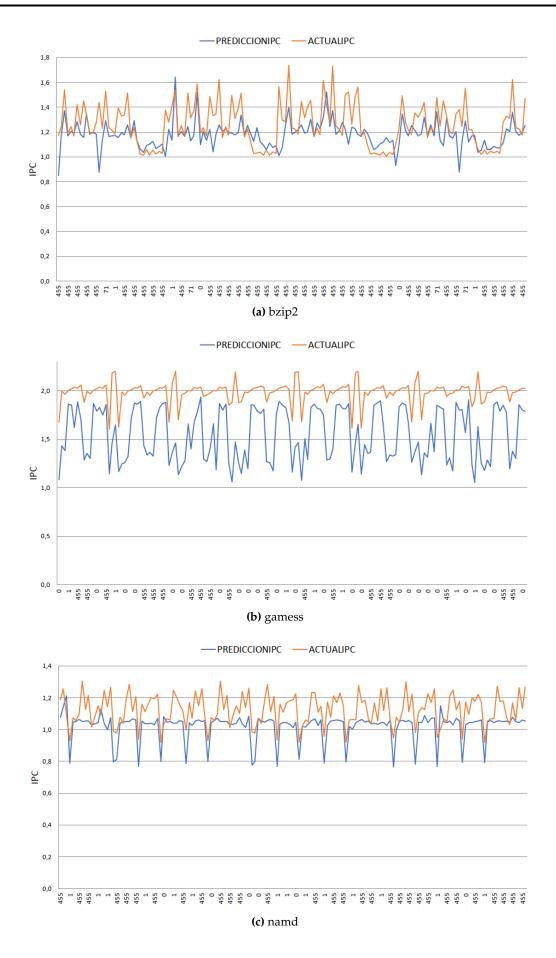

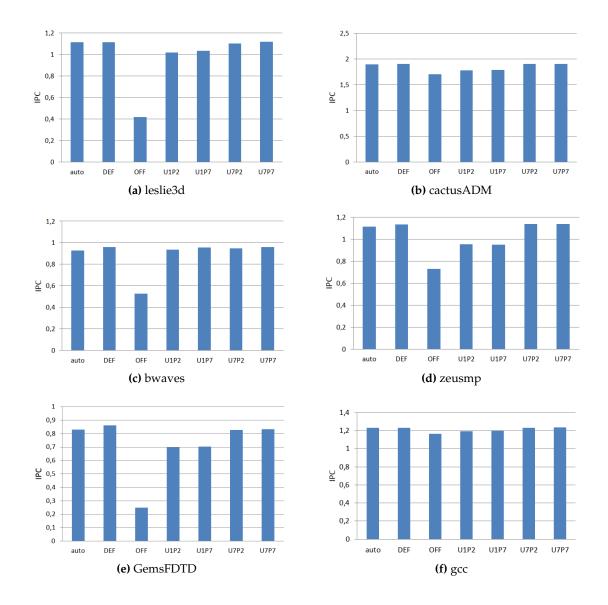

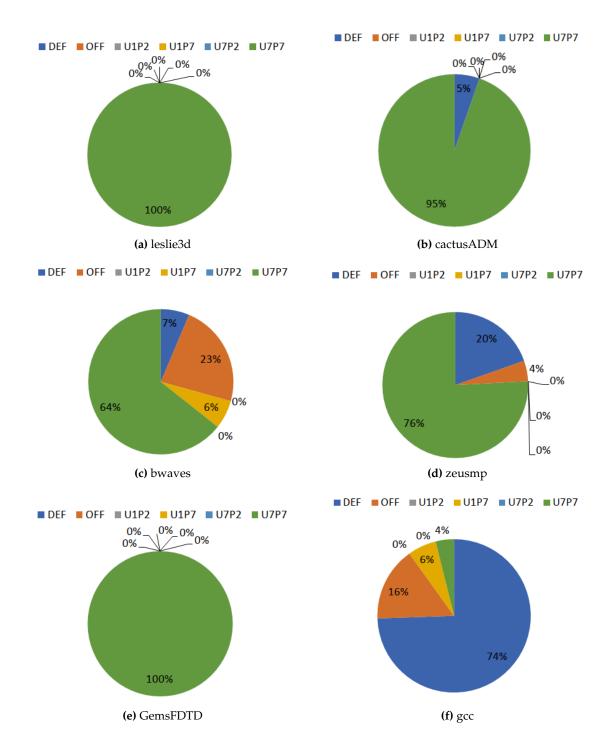

# 5.1 Efectos de las configuraciones del *prefetcher* en cada aplicación

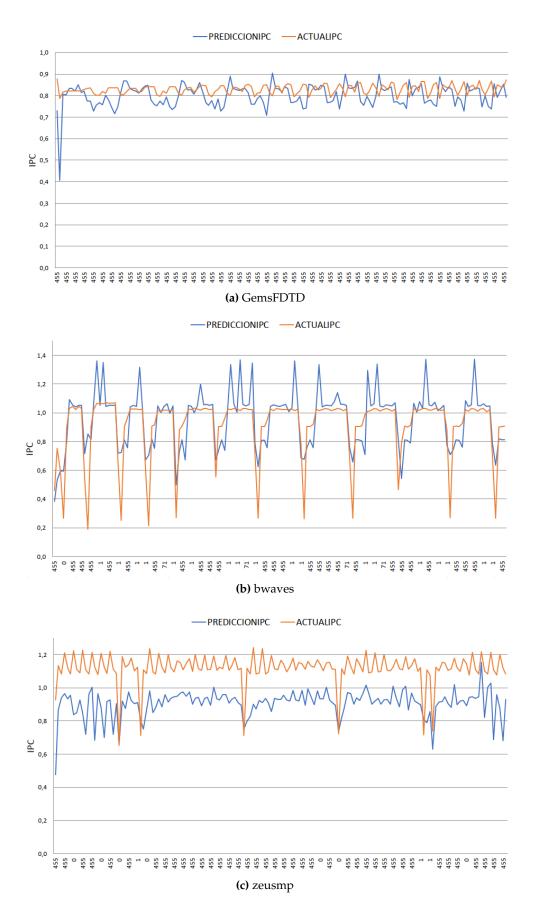

En este capítulo se estudian los efectos que pueden tener las distintas configuraciones del *prefetcher* utilizando como referencia los resultados de los *benchmarks* mencionados anteriormente (*SPEC CPU 2006*) durante la ejecución individual de los mismos. Para estas pruebas se ha ejecutado cada *benchmark* con las seis configuraciones que se han comentado en capítulos anteriores. Las configuraciones que se emplean en estas pruebas son las configuraciones por defecto (*DEF* (DSCR=0)) y no *prefetch* (*OFF*, prebúsqueda desactivada (DPFD=1)), así como cuatro configuraciones adicionales variando la urgencia (*URG*) y la profundidad (*DPFD*) en sus valores máximos y mínimos. Concretamente estas son *U1P2*, *U1P7*, *U7P2* y *U7P7*, donde *UxPy* corresponde a urgencia (*URG*) x y profundidad (*DPFD*) y.