# UNIVERSIDAD POLITECNICA DE VALENCIA

#### ESCUELA POLITECNICA SUPERIOR DE GANDIA

Master en Ingeniería de Sistemas Electrónicos

# "Massive Parallel Decoding of Low-Density Parity-Check Codes Using Graphic Cards."

TESIS DE MASTER

Autor:

**Enrique Monzó Solves**

Director/es:

Dipl. Ing. Laurent Schmalen Dra. Asunción Pérez Pascual

**GANDIA**, 2010

## **Contents**

| 1 | Intr | oducti  | on                                                  | 1  |

|---|------|---------|-----------------------------------------------------|----|

| 2 | The  | oretica | ıl and Technological Background                     | 3  |

|   | 2.1  | Low-D   | ensity Parity-Check Codes                           | 3  |

|   |      | 2.1.1   | Tanner Graph                                        | 4  |

|   |      | 2.1.2   | Belief Propagation                                  | 5  |

|   |      | 2.1.3   | Log-Domain Fourier Transform Decoding               | 6  |

|   | 2.2  | CUDA    | Architecture                                        | 8  |

|   |      | 2.2.1   | Threads Arranging and Execution                     | 8  |

|   |      | 2.2.2   | Device Memory Types                                 | 9  |

|   |      | 2.2.3   | Textures                                            | 10 |

|   |      | 2.2.4   | Performance Considerations                          | 11 |

| 3 | Imp  | lement  | ation                                               | 13 |

|   | 3.1  | LDPC    | GF(2) Decoder                                       | 13 |

|   |      | 3.1.1   | Algorithm Flowchart                                 | 14 |

|   |      | 3.1.2   | Data Structures                                     | 15 |

|   |      | 3.1.3   | Kernel Implementations                              | 17 |

|   |      |         | 3.1.3.1 Initialization of $Q$                       | 17 |

|   |      |         | 3.1.3.2 Parity Check Equations                      | 18 |

|   |      |         | 3.1.3.3 Check if the Parity Equations are Satisfied | 19 |

|   |      |         | 3.1.3.4 Check Node Update                           | 20 |

|   |      |         | 3.1.3.5 Bit Node Update                             | 21 |

|   | 3.2  | LDPC    | GF(q) Decoder                                       | 23 |

|   |      | 3.2.1   | Algorithm Flowchart                                 | 23 |

|   |      | 3.2.2   | Data Structures                                     | 24 |

|   |      |         | 3.2.2.1 Non-constant variables                      | 25 |

|   |      |         | 3.2.2.2 Constant variables                          | 26 |

|   |      |         | 3.2.2.3 Texture Tables                              | 27 |

|   |      | 3.2.3   | Kernel Implementations                              | 27 |

|   |      |         | 3.2.3.1 Input L-Values Initialization               | 28 |

|   |      |         | 3.2.3.2 Input L-values Update                       | 29 |

|   |      |         | 3.2.3.3 Hard Decision                               | 30 |

ii Contents

|    |                                                     |        | 3.2.3.4  | Check Node Equations                          | 31 |  |

|----|-----------------------------------------------------|--------|----------|-----------------------------------------------|----|--|

|    |                                                     |        | 3.2.3.5  | Check Node Equations Satisfied                | 32 |  |

|    |                                                     |        | 3.2.3.6  | Bit Node Update                               | 32 |  |

|    |                                                     |        | 3.2.3.7  | Permutation of $P\_L$ and $Q\_L$              | 34 |  |

|    |                                                     |        | 3.2.3.8  | Log-FFT                                       | 35 |  |

|    |                                                     |        | 3.2.3.9  | Check Node Update                             | 37 |  |

|    |                                                     |        | 3.2.3.10 |                                               | 38 |  |

| 4  | Res                                                 | ults   |          |                                               | 39 |  |

|    | 4.1                                                 | Binary | LDPC I   | Decoder                                       | 39 |  |

|    |                                                     | 4.1.1  | Kernel E | Execution Time                                | 40 |  |

|    |                                                     | 4.1.2  | Summar   | ry CUDA Optimizations                         | 41 |  |

|    |                                                     | 4.1.3  |          | PU Speedup versus Number of Iterations        | 43 |  |

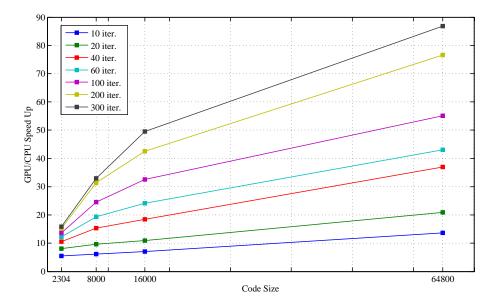

|    |                                                     | 4.1.4  | GPU/CI   | PU Speedup versus Code Size                   | 43 |  |

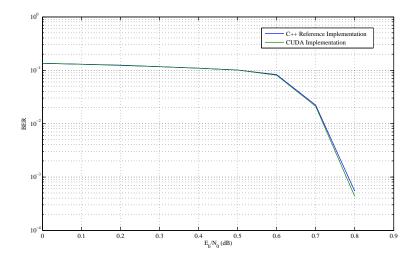

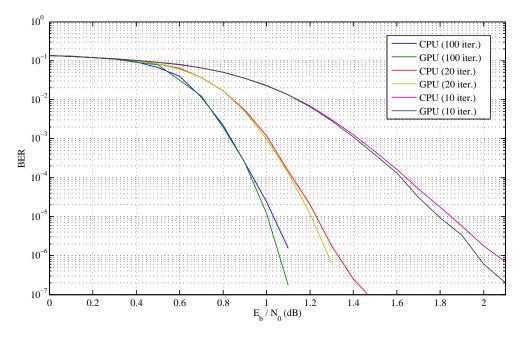

|    |                                                     | 4.1.5  | •        | omparison between CPU and GPU Implementations | 44 |  |

|    | 4.2                                                 | Non-bi | inary LD | PC Decoder                                    | 45 |  |

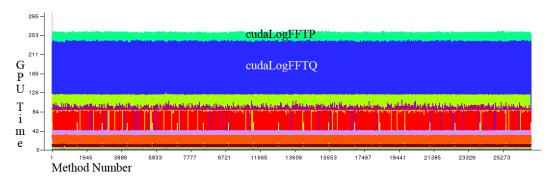

|    |                                                     | 4.2.1  | Kernel E | Execution Time                                | 45 |  |

|    |                                                     | 4.2.2  |          | Optimization Summary                          | 46 |  |

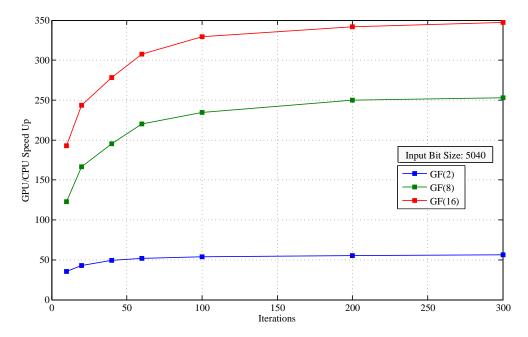

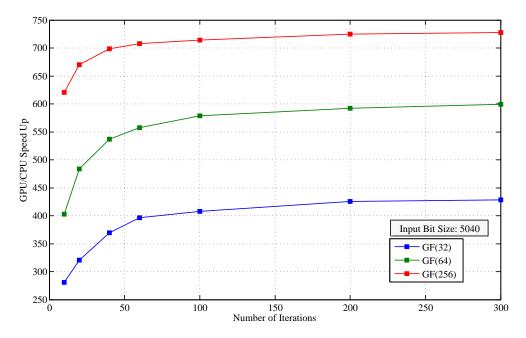

|    |                                                     | 4.2.3  |          | PU Speedup versus Number of Iterations        | 47 |  |

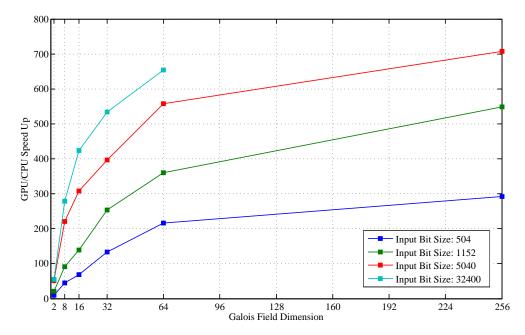

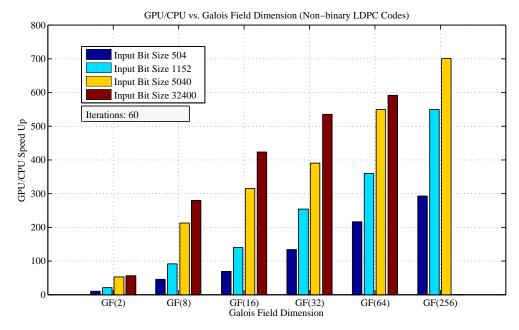

|    |                                                     | 4.2.4  | GPU/CI   | PU Speedup versus Galois Field Dimension      | 50 |  |

|    |                                                     | 4.2.5  | •        | omparison Between CPU and GPU version         | 52 |  |

| 5  | Sun                                                 | nmary  | and Cor  | nclusions                                     | 53 |  |

| 6  | App                                                 | pendix | A GF(2   | 2) CUDA Kernels Source Code                   | 57 |  |

| 7  | Appendix B GF(q) CUDA Kernels Source Code 6         |        |          |                                               |    |  |

| 8  | Appendix C NVIDIA GeForce GTX 275 Specifications 69 |        |          |                                               |    |  |

| Bi | iblios                                              | graphy |          |                                               | 71 |  |

## Introduction

Low-density parity-check (LDPC) codes, first introduced by R. G. Gallager in 1960 [16], are a class of linear block codes characterized by their parity-check matrix, which contains a low density of non-zero elements. The main advantage of LDPC codes is that they provide a performance which is very close to the capacity for many channels. They are suited for implementations that make heavy use of parallelism. However, due to the computational effort in the implementation of these codes, they were mostly ignored until the 90's.

A way to represent LDPC codes is via a Tanner graph representation, which is an effective graphical representation for LDPC codes, because it efficiently helps to describe the decoding algorithm. Tanner graphs are bipartite graphs with nodes that are separated into two different sets and edges connecting the nodes of the two different sets. Each edge represents a non-zero value in the parity-check matrix. The two types of nodes in a Tanner graph are called variable nodes and check nodes.

Iterative suboptimal decoding algorithms are used to decode LDPC codes. Those algorithms perform local calculations and pass those local results via messages. This step is usually repeated several times until convergence is observed.

The most common algorithm for decoding binary LDPC codes is the belief propagation algorithm. For the case of non-binary LDPC codes, the log-domain Fourier transform belief propagation algorithm achieves a good decoding performance. Both algorithms are message passing algorithms.

CUDA (Compute Unified Device Architecture) is a parallel computing architecture developed by NVIDIA Corporation, being present in the current NVIDIA graphics cards. It is accessible to software developers through variants of industry standard programming languages. Thus, it is possible to program CUDA devices using C/C++ with NVIDIA extensions and certain restrictions.

Each chip with CUDA technology is based on a multiprocessor with many cores and hundreds of ALU's, several thousand registers and some shared memory. Besides, a graphics card contains global memory, which can be accessed by all multiprocessors, local memory

2 1 Introduction

in each multiprocessor, and special memory for constants. The several multiprocessor cores in a GPU are SIMD (single instruction, multiple data) cores. This programming style is common for graphics algorithms and many scientific tasks, but it requires specific programming.

Motivated by the parallel computation power of the CUDA architecture, the CUDA implementation of an existing C++ software based LDPC decoding system is studied in this thesis. The main objective is the efficient CUDA implementation of the belief propagation and the log-domain Fourier transform algorithms for the binary and non-binary LDPC decoding processes respectively. A considerable GPU/CPU speedup is expected with the GPU implementation of these algorithms.

Chapter 2 introduces the necessary theoretical background for understanding LDPC codes and the CUDA architecture. The LDPC codes are presented together with their main characteristic, the parity-check matrix, and their graphical representation, the Tanner graph, which is the base for performing the iterative LDPC decoding. The belief propagation and the log-domain Fourier transform algorithms are explained step by step.

Afterwords, the CUDA architecture is introduced as a technology present in the modern graphic cards from NVIDIA. The parallel processing capabilities of these devices are introduced, and a review of the hardware resources and constraints is performed. Some performance considerations are introduced for understanding how to achieve better performance, taking advantage of the device architecture.

The CUDA implementation of the LDPC decoders is detailed in Chapter 3. The belief propagation and the log-domain Fourier transform algorithms are parallelized and assembled in kernels. Each kernel uses the hardware resources in a different way, in order to achieve the best performance.

Chapter 4 shows the results obtained by the CUDA LDPC decoder implementations compared with the respective C++ reference code. The GPU/CPU speedup is measured for different LDCP codes with different code sizes, number of iterations, etc. The results indicate how the massive parallel process capacity of the GPU's can be used for accelerating the decoding algorithms in a very impressive way.

# Theoretical and Technological Background

#### 2.1 Low-Density Parity-Check Codes

Low-density parity-check (LDPC) codes were introduced by Robert G. Gallager in 1963 [16]. These codes were forgotten for a few decades because of the limited ability of computation. LDPC codes were recovered in 1995 by David J.C. MacKay and Radford M. Neal [3]. They realized that these codes offer remarkable performance to allow data transmission rates close to the Shannon limit.

LDPC codes are long linear block codes defined by a generator matrix  $\underline{G}$ , or a parity check matrix  $\underline{H}$  with a low density of non-zero elements. If  $\underline{H}$  has a constant number  $\omega_c$  of non-zero elements in the column and a constant number  $\omega_r$  of non-zero elements in the rows, then the code is called *Regular* LDPC code. Otherwise, it is called *irregular*.

For a block length m, it is said that  $\underline{H}$  defines an  $(m, \omega_c, \omega_r)$  LDPC code. The parity check matrix is said to be *sparse* if less than half of the elements are non-zero. The linear block code encodes n information bits into m coded bits, with a rate r = n/m < 1. Using row vector notation, the coded vector  $\underline{Y}$  is obtained from the information vector  $\underline{X}$  by the vector multiplication  $\underline{Y} = \underline{X} \cdot \underline{G}$ .  $\underline{G}$  is a matrix with dimension  $n \times m$ .

$$\underline{Y} = (y_1, y_2, \dots y_m)$$

$$\underline{X} = (x_1, x_2, \dots x_n)$$

$$\underline{Y} = \underline{X} \cdot \underline{G}$$

Each row of  $\underline{H}$  provides a parity check equation that any code vector  $\underline{Y}$  must satisfy.

$$\underline{Y} \cdot \underline{H}^T = 0$$

Since  $\underline{H}$  can reach huge dimensions, the direct decoding process can have a high complexity. Thus, LDPC codes can be decoded iteratively using message passing algorithms over a Tanner graph. These codes been used in recent digital communications systems standards, such as DVB-S2, DVB-T2, WiMAX (IEEE 802.16), Wireles LAN (IEEE 802.11n).

#### 2.1.1 Tanner Graph

A binary linear code can be represented by a Tanner graph using the parity check matrix  $\underline{H}$ . A Tanner graph is a bipartite graph with variable nodes on the left, corresponding to the different code symbols, and check nodes on the right, one for each check equation, or row in the parity check matrix. Each variable node ( $\underline{H}$  column) is connected in the Tanner graph to the check nodes corresponding to non-zero values in the parity check matrix.

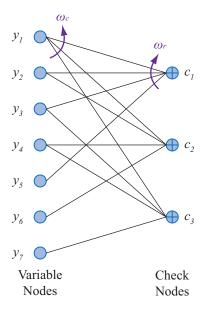

For example, the Tanner graph of the parity check matrix for the (7,4) Hamming code is depicted in Figure 2.1.

$$\mathbf{\underline{H}} = \left(\begin{array}{cccccc} 1 & 1 & 1 & 0 & 1 & 0 & 0 \\ 1 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 0 & 1 & 1 & 0 & 0 & 1 \end{array}\right)$$

**Figure 2.1:** Tanner graph for the (7,4) Hamming code.

In Figure 2.1, the first node  $c_1$  corresponds to the first row of the parity check matrix  $y_1 + y_2 + y_3 + y_5 = 0$ , according to the connections of the variable nodes  $y_1, y_2, y_3$  and  $y_5$  to the check node  $c_1$ .

#### 2.1.2 Decoding Process on Binary LDPC Codes: Belief Propagation

Belief propagation is an extension of the message passing algorithm, where the information in the messages being passed is expressed in terms of logarithmic likelihood values (L-values) [19].

In the variable nodes, the incoming and the updated bits are represented as  $L_i$  and  $\tilde{L}_{ij}$  respectively, and in the check nodes the estimated bits are represented as  $\hat{L}_{ij}$ .

The channel messages  $(L_i)$  are received in the variable nodes and the check equations are applied to them. If the hard decision of these input L-values satisfies the parity check equations, the decoding process is complete since the received bits are a valid codeword. If the check equations are not satisfied, then the iterative decoding process is initialized until the updated word is a valid word or the number of iterations reaches the maximum value. The description of the iterating process is as follows.

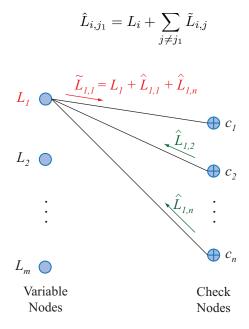

Variable Node Update: On each outgoing edge from the variable nodes, an updated L-value  $\tilde{L}_{i,j}$  is sent out with a value corresponding to the sum of the corresponding node input L-value plus the extrinsic sum of the values coming in on the other edges (Figure 2.2).

**Figure 2.2:** Updating  $\tilde{L}_{i,j}$  values in the variable node connections.

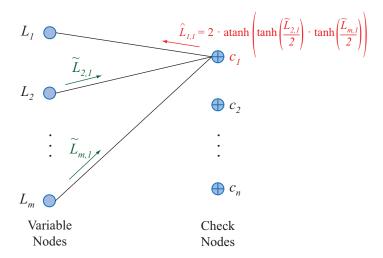

**Check Node Update:** At the check nodes, the outgoing extrinsic L-values  $\hat{L}_{i,j}$  are calculated according to the *box-plus* operation [15] whose expression is

$$\hat{L}_{i_1,j} = 2 \cdot \operatorname{atanh} \left( \prod_{i \neq i_1} \operatorname{tanh} \left( \frac{\tilde{L}_{i,j}}{2} \right) \right)$$

**Figure 2.3:** Updating  $\hat{L}_{i,j}$  values in the check node connections.

After the check node update the iteration is finished. If all the check equations are fulfilled the iterative process is stopped. The decoded bits are obtained from the finally updated variable node L-values.

$$\hat{y}_i = \operatorname{sign}\left\{L_i + \sum_j \hat{L}_{i,j}\right\}$$

where the sum is performed over all incident connections on the corresponding variable node.

## 2.1.3 Decoding Process on Non-Binary LDPC Codes: Log-Domain Fourier Transform Decoding

Non-binary LDPC codes are defined over the finite Galois field  $GF(q=2^p)$ . By encoding over GF(q), each parity check becomes more complex. The decoding of non-binary LDPC codes is not equivalent to the binary case as the non-binary decoder operates on the symbol level, and not on the bit level. The decoding algorithm is based on the probability and log domain versions of the Fourier transform over GF(q), since it reduces the algorithm complexity [8]. The information in the messages being passed is expressed in terms of L-values.

The channel messages  $L_i^a$  are loaded into the variable nodes. These messages represent the prior L-values for the symbol a, where  $a \in GF(q)$ . If the channel messages satisfy the check equations, the decoding process is successful and is finished. If not, the iterative process continues as follows.

Variable Node Update: Each variable node generates outgoing messages for each connection and symbol, and they are calculated as the extrinsic sum of the previously calculated (or initialized) L-values  $\hat{L}_{k,i}$ .

$$\tilde{L}_{i,j}^{a} = L_{i}^{a} + \sum_{j \neq j_{1}} \hat{L}_{i,j} - \alpha_{i,j}$$

$$\alpha_{i,j} = \max \ \tilde{L}_{i,j}^{a}$$

The normalisation value  $\alpha_{i,j}$  is introduced for avoiding numerical overflow problems.

Check Node Update: The check node messages are updated in the Fourier Domain. The fast Fourier transform (FFT) is used for transforming the messages into the spectral domain. The FFT can produce negative numbers. Thus, for handling these negative numbers in the log domain, two dimensions (magnitude and sign) are used.

The messages  $\tilde{L}_{i,j}^a$  are converted to signed L-values, where  $\tilde{Q}_{i,j}^a(mag) = \tilde{L}_{i,j}^a$  and  $\tilde{Q}_{i,j}^a(sig) = 1$ . These are permuted and transformed to the Fourier domain [8] according to

$$\left[\tilde{Q}_{i,j}^{a}(mag),\tilde{Q}_{i,j}^{a}(sig)\right]=\mathcal{F}\left[\Pi\left(\tilde{L}_{i,j}^{a}\right)\right].$$

The outgoing Fourier domain check node messages are updated as follows:

$$\hat{R}^a_{i,j}(sig) = \prod_{i \neq i_1} \tilde{Q}^a_{i,j}(sig)$$

$$\hat{R}^a_{i,j}(mag) = \sum_{i \neq i_1} \tilde{Q}^a_{i,j}(mag)$$

The outgoing check node signed L-values are converted to the log-domain applying an inverse FFT and an inverse permutation [8]

$$\left[\hat{L}_{i,j}^{a}(mag), \hat{L}_{i,j}^{a}(sig)\right] = \mathcal{F}^{-1}\left[\Pi^{-1}\left(\left[\hat{R}_{i,j}^{a}(mag), \hat{R}_{i,j}^{a}(sig)\right]\right)\right].$$

The signed L-values  $\hat{R}^a_{i,j}(mag)$  are converted back to check node messages, where  $\hat{L}^a_{i,j}=\hat{L}^a_{i,j}(mag)$

The check equations are applied to the estimated L-value messages (input L-value plus the sum of all the incoming L-value node connections) such that

$$\hat{y}_i = \operatorname{argmax} L_i^a + \sum \hat{L}_{i,j}^a$$

If the check equations are satisfied the decoding process is finished. If not, the process continues with a new iteration until a valid message word is estimated or the maximum number of iterations is reached.

#### 2.2 CUDA Architecture

The high parallel processing performance of graphics processing units (GPUs) has been used traditionally to transform, light and rasterize triangles in three-dimensional computer graphics applications. In recent architectures, however, the vectorized pipeline for processing triangles has been replaced by a unified scalar processing model based on a large set of streaming processors. This change has initiated a consideration of GPUs for solving general purpose computing problems, and triggered the field of general-purpose computing on graphics-processing units (GPGPU). GPGPU appears to be a natural target for scientific and engineering applications, many of which admit highly parallel algorithms [2].

The hardware abstraction based on the GPU unified scalar processing model is denoted CUDA (Compute Unified Device Architecture) in all the current NVIDIA graphic cards. This technology allows to execute thousands of concurrent threads for the same process, which makes this kind of devices ideal for massive parallel computation. The CUDA devices have special hardware resources (with their respective constraints) and, with a deep knowledge about them, it is possible to achieve high speedup values for a CUDA implementation compared to a non-parallelized CPU version.

The CUDA device and the computer which it is attached to are referred as *device* and *host* respectively. Also, all the CUDA or hardware mentioned specifications in this section are referred to the NVIDIA GeForce GTX 275 model, the one used in this thesis (for more details about the GTX 275 hardware specifications, please refer to Appendix C).

CUDA devices are programmed using a extended C/C++ code and compiled using the NVIDIA CUDA Compiler driver (NVCC). After the compilation process, the serial code is executed on the host and the parallel code is executed on the device using kernel functions.

#### 2.2.1 Threads Arranging and Execution

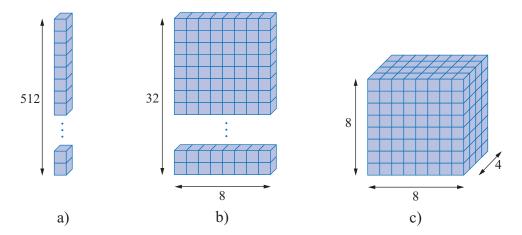

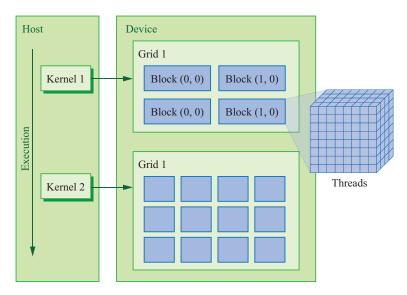

A CUDA device has a limited number of streaming multiprocessors (SM). Each SM is able to execute concurrently up to 1024 threads, which have to be arranged in blocks. A block contains up to 512 threads, arranged with an 1D, 2D or 3D distribution (Figure 2.4).

A SM is able to process simultaneously between 2 and 8 blocks of threads and it is important to have a SM occupancy of 100% for achieving the maximum performance. A power-of-two number of threads per block helps to reach this goal. Finally, the blocks are partitioned in *grids*, where a grid is a 1D or 2D arrangement of the total number of blocks containing all the data to be processed. The threads/block and blocks/grid settings are configured for the execution of each kernel. Thus, each kernel launches the execution of one grid of blocks, which contains all the data to be processed arranged in blocks of a fixed number of threads.

A kernel is launched as a C/C++ function (but with some extensions) from the host and executed on the device. A call to a kernel can be written as <u>\_\_global\_\_</u> kernelName <<<<num Grids, numBlocks>>> (parameters\_list), where <u>\_\_global\_\_</u> indicates to the compiler that the kernel has to be executed on the device, <<<numGrids, numBlocks>>>

2.2 CUDA Architecture 9

Figure 2.4: Different block arrangements for a number of 256 threads.

details the blocks/grid and threads/block settings and *parameters\_list* is the typical parameters list passed to a standard C/C++ function. For more information, please refer to the CUDA programming manual [12].

**Figure 2.5:** Grid organization and execution.

#### 2.2.2 Device Memory Types

CUDA supports several kinds of memory than can be used for achieving high speed performance in the kernels execution. The description of each memory is as follows:

Global memory: This is the largest capacity memory in the device (768 MB in the GTX 275). It is a read and write memory and can be accessed by all the threads during the application execution (the stored data remains accessible between different kernel executions). It is off chip, i.e. slow interfacing has to be used, but it can achieve

good performance if each continuous thread index accesses continuous memory data positions. The global memory is the communication channel between host and device, since the data to be processed have to be sent from the host to the device, and sent back to the host after the application execution.

**Constant memory:** This memory is available to all the threads during the application execution. It is a read-only memory by the device, and only the host is able to write data to it. It is a short-latency, high-bandwidth memory if all threads simultaneously access the same location.

**Shared memory:** This is an on-chip memory available to all the threads in one block. It is a read and write memory, with a size of 16 KBytes per SM. The data is available during the kernel execution and the access can be very fast if the available shared memory banks are accessed in a parallel way.

**Registers:** These are on-chip memory registers available to each independent thread. The local variables in a kernel are usually stored in the registers, performing a full speed access. If a variable can not be allocated in the on-chip hardware registers, then it is stored in the global memory with a slower access.

The variables created in CUDA can be allocated in each of the available memory types, depending on which keyword precedes the variable declaration or where are they declared. Table 2.1 has a summary of the different variables and memory associations.

| Variable declaration      | Memory   | Scope  | Lifetime    |

|---------------------------|----------|--------|-------------|

| Automatic variables       | Register | Thread | Kernel      |

| other than arrays         |          |        |             |

| Automatic array variables | Local    | Thread | Kernel      |

| shared, int SharedVar;    | Shared   | Block  | Kernel      |

| int GlobalVar;            | Global   | Grid   | Application |

| constant                  | Constant | Grid   | Application |

**Table 2.1:** Memory types in a CUDA device.

#### 2.2.3 Textures

The graphic cards are designed for a high performance in the 3D and 2D image processing. There is a special memory where bitmaps or textures are stored for a special processing. This memory is denoted texture memory. The texture memory can only be read by the threads, but it is accessed in a very fast way if continuous thread indexes access to spatially close *texels* (or texture elements). This memory also is optimized for certain functions such as linear interpolation or anti-aliasing.

The texture memory can be used as look-up table, with the extra function of linear interpolation between points. For a high performance access it is required that the stored data has some spatial relation. If not, the penalty is enough for not achieving better performance than the global memory.

2.2 CUDA Architecture 11

#### 2.2.4 Performance Considerations

The execution speed of a kernel depends on the resource constraints of the device. Some considerations have to be taken in mind while programming CUDA devices, in order to achieve the maximum execution performance [11]. These considerations can be summarized as follows:

- Block sizes: For a fast execution speed of a kernel, all the threads in a warp (group of 32 continuous threads) should execute the same instruction. Thus, an important performance factor is that the number of threads per block is proportional to 32.

- **Divergent threads:** When using conditional sentences with the thread index involved, the threads are executed in two different branches. In this way, not all the threads are executing the same instruction and the performance could be slowed down.

- Global memory access: The global memory is the largest memory in the CUDA device, but also it is the slowest one. For achieving a good global memory performance it is extremely important to access the data in a coalesced way. It means, each continuous thread index in a warp has to access continuous memory positions. This can be managed by taking care about the data size and the way the memory is indexed and accessed in the kernels.

- **Shared memory:** Each SM has 16 KB of available shared memory. If the memory access is paralellized, then the access can be as fast as one on-chip register. Shared memory banks are organized such that successive 32-bit words are assigned to successive banks. Thus, if successive 32-bit threads access different shared memory banks, these access are paralellized achieving a high bandwidth. If not, the accesses are serialized (bank conflicts).

- Occupancy: It is clear to understand that if the SM are 100% occupied, the performance is maximized. Thus, all the variables which can limit this occupancy: maximum number of threads per SM and the number of threads per block, the maximum available shared memory per SM and the amount of shared memory used by each kernel.

- **Hardware functions:** CUDA has hardware implemented fast mathematical functions, however with a minor accuracy. If this precision lost is affordable, these functions can be used and the speed improvement is considerable.

For more information about CUDA programming, please refer to [11] [12] [13].

The LDPC decoder algorithms here implemented, are based on the C++ reference code in [10]. The objective of the implementation is to speed up the decoding process, taking advantage of the massive parallel processing offered by the CUDA technology. The reference code can be improved in several ways, depending on its nature. Sometimes the code only needs to be adapted to the CUDA architecture. Other times, the parallelization of the code simplifies the execution and enhances the performance. In occasions, it is better to start the code from zero. And in all these cases, the best option is to use all the specific hardware resources that seriously improve the processing time.

A good knowledge of the source implementation and its theoretical background, and a deep knowledge of the CUDA architecture leads to find the best way for achieving a good performance over the original implementation. This is the goal in this chapter.

The data used in the implementation has single precision, so all the variables involved in the data processing are *floats*. Single precision gives a good compromise between accuracy and performance in CUDA devices of architecture generation 1.3 or below.

The hardware platform used for the implementation is based on an Intel Core 2 Quad Q6600 @ 2.4 GHz / 2 GB RAM system, and a NVIDIA GeForce GTX 275 graphic card.

## 3.1 LDPC GF(2) Decoder

The (binary) LDPC GF(2) decoding is based on a message passing algorithm over the Tanner graph. This graph completely defines the parity check matrix and contains all the necessary information for creating all the variables (information and auxiliary variables) in the decoding algorithm.

The CUDA implementation is focused on a generic decoding algorithm which means that it has to be able to process LDPC codes of whatever parity check matrix size. This reduces the range of possibilities about using different memories in the CUDA device, since the

matrices for storing the message passing L-values  $\tilde{L}$  and  $\hat{L}$  have to be stored in the global memory.

It is necessary to keep in mind some implicit characteristics of the LDPC GF(2) decoding algorithm. First, there are continuous random memory accesses during the decoding. This is not optimal for the CUDA technology, since the hardware could not be able to do coalesced memory data reading or writing. Second, the tanh() and atanh() functions have a high computational cost. The first handicap is not very tractable, because the aleatory memory accesses are in the LDPC codes nature. The second one can be treated in different ways, as it is explained in the next sections.

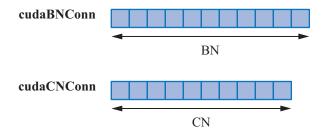

During this section, some recurrent variable names are used. The meaning of these variables is as follows:

BN/CN: Number of Tanner graph bit/check nodes.

cudaBNConn/cudaCNConn: Number of connections for a particular Tanner graph bit/check node.

maxBNConn/maxCNConn: Maximum number of connections of the bit/check nodes.

#### 3.1.1 Algorithm Flowchart

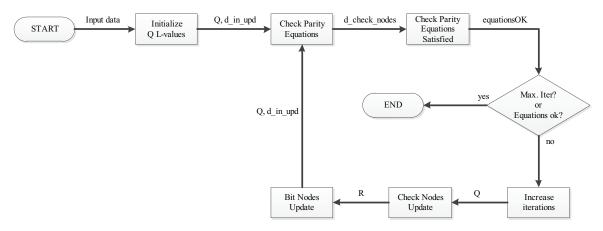

The algorithm flowchart is shown in Figure 3.1. This scheme follows the C++ reference implementation [10].

**Figure 3.1:** Algorithm flowchart.

The description of the variables in Figure 3.1 is as follows:

**d\_in\_upd:** Updated input values with the L-values Q converted to binary information.

d\_check\_nodes: Vector containing the result of the parity check equations in each Tanner graph check node.

equations OK: This variable indicates if all the parity equations are successful.

Q: Outgoing L-values  $(\hat{L})$  from the Tanner graph check nodes.

R: Outgoing L-values  $(\tilde{L})$  from the Tanner graph bit nodes (variable nodes).

Initially, the input data is loaded into the GPU device, and the iterations counter set to zero. Before it starts decoding, the L-values Q (matrix Q) are initialized with the input L-values, and the updated input data vector  $(d_in_upd)$  is initialized to the corresponding input L-value converted to binary. Here the loop starts, and the updated input data is immediately checked. If the checking succeeds, the decoding process is interrupted because the data has not bit errors and is valid. If this is not the case, the number of iterations is increased and the check node update performed. The check node update generates the extrinsic L-values R from the L-values Q initialized before. These values are used by bit node update for generating the new L-values Q and updating the input data again. Here, the loop is closed and performed once again by checking the parity check nodes with the updated input data.

Each process in the flowchart is implemented as a kernel in the CUDA source code. All the kernels are <u>\_\_\_global\_\_\_</u>, since they are executed in the device. The loop itself is controlled on the host device.

#### 3.1.2 Data Structures

The data structures used here are created according to the requirements of the decoding algorithm. The Tanner graph provides all the necessary information.

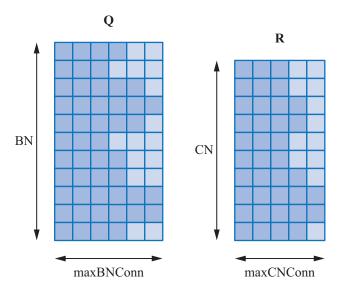

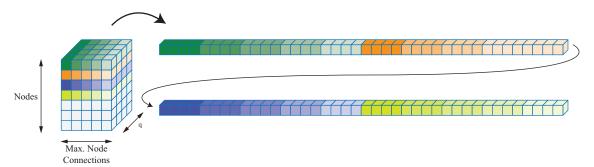

The Tanner graph bit nodes and check nodes share the same node connections, but connected in a random way. The algorithm needs two different matrices for managing the outgoing L-values from the different nodes (Figure 3.2).

The R matrix has as many rows as bit nodes exist in the Tanner graph. The number of columns is equal to the maximum number of bit node connections. The same holds for the Q matrix, but considering the Tanner graph check nodes. As Figure 3.2 shows, an irregular LDPC code has not the same number of connections in each node, so there are some no entries which are not valid. These cells can be avoided for saving processing time. Because of this, two auxiliary variables (cudaBNConn and cudaCNConn) contain the number of connections for each corresponding bit and check node (Figure 3.3)

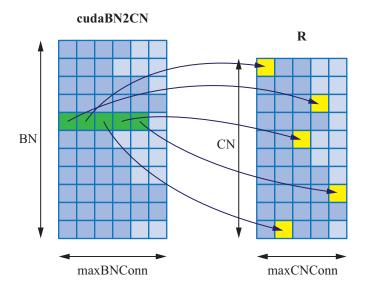

Since R and Q are linked by the same node connections, one position in the R matrix can require to read or write the matching position in the Q matrix, and vice-versa. Thus, it is necessary to know the Q index position for all the R elements, and vice-versa. This is the reason for the creation of the cudaBN2CN and cudaCN2BN matrices (Figure 3.4).

A last auxiliary variable is needed for knowing to which bit node each check node is connected in the Tanner graph. This variable is cudaCheckNodeConnections, a dimension  $CN \times maxCNConn$  matrix. It contains the bit node index for each check node connection.

All these variables are allocated in the global memory. The reason is that the algorithm has to have a general character, and has to be able to decode whatever LDPC code size is used. As the matrices have to be completely loaded in the memory (they can be accessed randomly), the only possible memory is the global memory. The data then has

Figure 3.2: R and Q matrices.

Figure 3.3: Vectors cudaBNConn and cudaCNConn.

to be arranged for being accessed in a coalesced way. Table 3.1 shows a summary of the variables, with the corresponding size and indexing expression. It has to be kept in mind that most of the CUDA variables have a 2D interpretation, but in fact they are 1D arrays.

| Name                     | Dim. $i$ | Dim. $j$  | Indexing                  |

|--------------------------|----------|-----------|---------------------------|

| Q                        | BN       | maxBNConn | $j \cdot \mathrm{BN} + i$ |

| R                        | CN       | maxCNConn | $j \cdot \mathrm{BN} + i$ |

| cudaBNConn               | BN       | -         | i                         |

| cudaBNConn               | CN       | -         | i                         |

| cudaBN2CN                | BN       | maxBNConn | $j \cdot \mathrm{BN} + i$ |

| cudaCN2BN                | CN       | maxCNConn | $j \cdot \mathrm{CN} + i$ |

| cudaCheckNodeConnections | CN       | maxCNConn | $j \cdot \mathrm{CN} + i$ |

Table 3.1: Dimensions and indexing of the variables

Each kernel processes one Tanner graph node. Inside each kernel, a loop processes all the node connections, counting up to the number of connections of the node. When the variables are indexed as  $j \cdot NODES + i$ , they access adjacent memory positions with

**Figure 3.4:** Matrix *cudaBN2CN* pointing the matching indices in *Q*.

adjacent threads: as each thread processes a node, during the loop execution the adjacent threads (nodes) access to coalesced memory positions in each iteration.

#### 3.1.3 Kernel Implementations

The kernels execute one thread per node, with a loop responsible of processing the different node connections. The loop is a good option since the loop count is small and the nodes don't have the same number of connections. Therefore, all the kernels have 1D block and grid configuration.

#### 3.1.3.1 Initialization of Q (cudalnitializeQ)

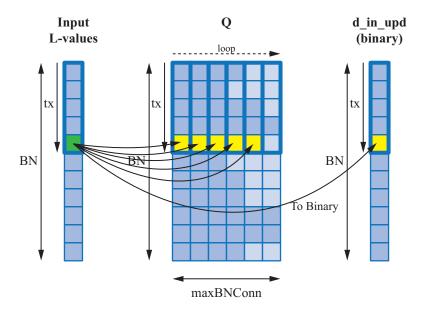

The Q matrix (estimated L-values) has to be initialized before the decoding loop starts. Each thread (Tanner graph bit node) reads the corresponding  $d_in$  input L-value and stores it in a temporal variable. This value is converted to binary and stored in  $d_in_upd$ . An internal loop process all the connections of the current node and assigns to them the input L-value stored in the temporal variable (Figure 3.5).

Each continuous thread index accesses continuous memory positions, optimizing in this way the memory access performance. Table 3.2 shows the block and grid configuration for this kernel.

|               | X Dimension                     |

|---------------|---------------------------------|

| Threads/Block | 256                             |

| Blocks/Grid   | $\lceil \mathrm{BN}/256 \rceil$ |

Table 3.2: Block and grid settings for the cudaInitializeQ kernel

Figure 3.5: Description of the cudaInitializeQ kernel.

#### 3.1.3.2 Check Parity Equations (cudaCheckEquations)

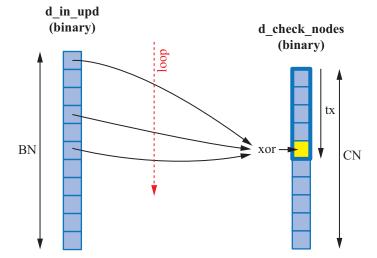

This kernel checks the parity equations in each Tanner graph check node. The input of the kernel is  $d\_in\_upd$ , where the estimated decoded word is stored in binary format.

For each thread (Tanner graph check node) a loop processes the *xor* of all the *d\_in\_upd* values corresponding to all the current check node connections. The *xor* result of each node is stored in the corresponding element of a temporal vector. If all the elements of the temporal vector are zero, then the estimated word is a valid code word.

Figure 3.6: Description of the cudaCheckEquations kernel.

With the 1D block configuration all the read and write memory accesses are coalesced, since each continuous thread index accesses to continuous memory positions. If a 2D block configuration is performed (one thread per node connection), then a shared memory block is required as temporal memory. The shared memory can not be accessed without bank conflicts in this case, slowing down the kernel execution performance.

|               | X Dimension                   |

|---------------|-------------------------------|

| Threads/Block | 256                           |

| Blocks/Grid   | $\lceil \text{CN}/256 \rceil$ |

**Table 3.3:** Block and grid settings for the **cudaCheckEquations** kernel

#### 3.1.3.3 Check Parity Equations Satisfied (cudaCheckEquationsSatisfied)

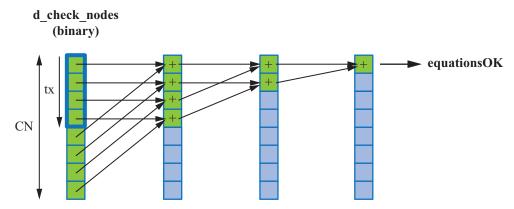

A sum reduction algorithm is applied to  $d\_check\_upd$  in order to verify if all the parity check equations have been satisfied.

A sum reduction algorithm is used taking advantage of the parallel processing. In this way, the sum is processed in  $\log_2 x$  steps, where x is the number of elements of the input vector. The reduction algorithm is efficient for a power-of-two number of elements. So, if the input vector has not power-of-two elements, the necessary zeros are appended to it. After the necessary iterations, the sum reduction algorithm returns 0 in its first index if all the elements of the input vector are zero (Figure 3.7).

Figure 3.7: Description of the cudaCheckEquationsSatisfied kernel.

This is the only one kernel using 512 threads per block as it is faster in most cases. The block and grid configuration is shown in Table 3.4.

|               | X Dimension                   |

|---------------|-------------------------------|

| Threads/Block | 512                           |

| Blocks/Grid   | $\lceil \text{CN}/512 \rceil$ |

Table 3.4: Block and grid settings for the cudaCheckEquationsSatisfied kernel

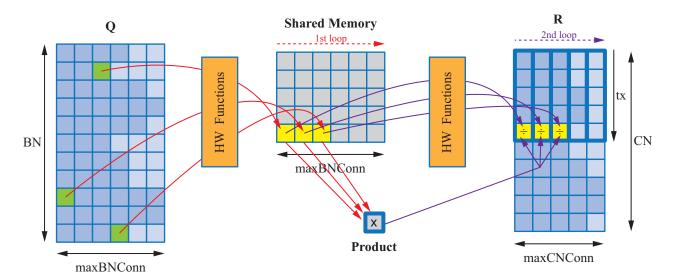

#### 3.1.3.4 Check Node Update (cudaCheckNodeUpdate)

Each thread processes one Tanner graph check node. The objective is to calculate the estimated L-values from the extrinsic sum of the updated L-values coming from the corresponding connections of the bit nodes.

A first loop processes all the current node connections. For each node connection, the matching L-value from Q (random access through cudaCN2BN) is loaded. The tanh operation is applied to the loaded value divided by 2. At the same time, this value is multiplied with a total product temporal variable. Once the loop is finished, the shared memory has stored each of the tanh(x)/2 values, and the product of them is saved in a thread temporary variable.

A second loop processes again all the node connections, but now each value in the shared memory divides the total product (that is, the extrinsic product) and then the *arctanh* is applied and multiplied by 2. The final L-value is written in R (coalesced writing). The process is shown in Figure 3.8.

$$R_{i_1,j} = 2 \cdot \operatorname{atanh}\left(\prod_{i \neq i_1} \operatorname{tanh}\left(\frac{Q_{i,j}}{2}\right)\right)$$

The shared memory indexing is  $i \cdot \text{maxCNConn} + j$ . This indexing eliminates all the bank conflicts, since each adjacent thread operates on a different shared memory bank. A parallel and full speed access is performed to the shared memory.

The standard tanh() and atanh() functions need a lot of processing time. The first option was to use these standard functions, but the kernel execution time was very slow. The second option was to use look-up tables for these functions and to store them in the constant memory or the texture memory. This improved performance, however the random accesses and the non-existent data locality made this option not as fast as expected. The final decision is to use optimized hardware functions in the GPU. Thus, the tanh and atanh functions can be expressed as follows:

$$atanh(x) = \frac{1}{2}ln\frac{1+x}{1-x}, |x<|1$$

$$\tanh(x) = \frac{e^{2x} - 1}{e^{2x} + 1}$$

These expressions are implemented using the  $\_\_expf()$ ,  $\_\_logf()$  and  $\_\_fdividef()$  hardware CUDA functions, leading to a further performance boost at the expenses of less precision.

The block and grid configuration is shown in Table 3.5. The number of threads per block has a maximum value of 256. The used shared memory is, as maximum, 4 KBytes per block.

Figure 3.8: Description of the cudaCheckNodeUpdate kernel.

|               | X Dimension                |

|---------------|----------------------------|

| Threads/Block | [256/maxCNConn]            |

| Blocks/Grid   | CN/[256/maxCNConn]         |

| Shared Mem.   | $\leq 4096 \text{ KBytes}$ |

**Table 3.5:** Block and grid settings for the **cudaCheckNodeUpdate** kernel.

With the current 1D block configuration the occupancy (calculated with the CUDA Occupancy Calculator tool) is not 100%, but it runs faster than with a 2D block arrangement. With a 2D block configuration, each thread corresponds to a different node connection. Thus, each thread needs to access simultaneously several shared memory positions for performing the extrinsic product, resulting in several bank conflicts. In such a case, the result is a low performance in the kernel execution speed.

#### 3.1.3.5 Bit Node Updates (cudaBitNodeUpdate)

This kernel updates Q and  $d_in_upd$  from the recently calculated L-values R. Each Tanner graph bit node connection in Q is updated with the extrinsic sum of the matching L-values R. For each bit node, the updated input value is calculated as the sum of the original input L-value plus the sum of all the matching connections in R.

Each thread processes a Tanner graph bit node and contains a temporal variable for storing the sum of the associated L-values R. A first loop (up to cudaBNConn) processes all the bit node connections for storing them in the shared memory and simultaneously calculating the sum of the L-values. The entries of R are accessed in a random way, using cudaBN2CN. Once the loop is finished, the sum is calculated and the updated input value is converted to a binary value and written in a the output vector (coalesced writing). A

second loop subtracts each imported L-value to the complete sum (extrinsic sum) and writes in a coalesced way this value to Q. The process is shown in Figure 3.9.

Figure 3.9: Description of the cudaBitNodeUpdate kernel.

Using a 2D block arrangement with shared memory, the kernel execution has not a good performance. The cause is that each thread needs to access simultaneously different shared memory positions, performing memory bank conflicts. These bank conflicts cause the serialization of the shared memory accesses, slowing down the kernel execution performance.

|               | X Dimension                |

|---------------|----------------------------|

| Threads/Block | [256/maxBNConn]            |

| Blocks/Grid   | BN/[256/maxBNConn]         |

| Shared Mem.   | $\leq 4096 \text{ KBytes}$ |

Table 3.6: Block and grid settings for the cudaBitNodeUpdate kernel.

The occupancy of the streaming multiprocessor is not 100%, because the use of the shared memory limits the number of blocks per SM. Since the shared memory has to contain

(number of threads · maxBNConn) floats ( $\leq 256$ ), it is only possible to have as many shared memory blocks as can fit in the available memory. This limits the number of threads per block, reducing the occupation to 50%, but it has been found that in this case the performance is superior than in other cases.

### 3.2 LDPC GF(q) Decoder

For the implementation of the LDPC GF(q) it is again necessary to focus the attention to two main different points: the arrangement of the data in the device memory and the use of the capabilities of the hardware for accelerating the data processing.

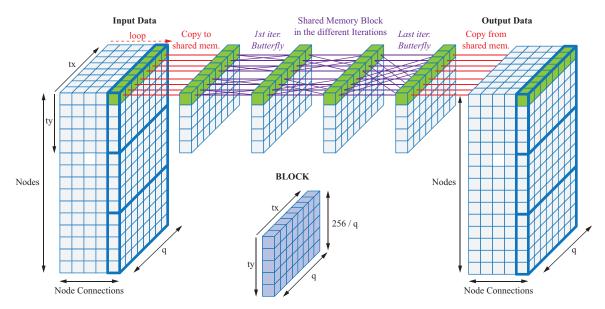

From the point of view of the data arrangement, it is interesting to interpret the variables as three-dimensional matrices, but bearing in mind that CUDA stores and process the data in 1D arrays. In the implemented algorithm, 2D and 3D data structures are needed, but the 3D ones are the most important since they are present in almost all the kernels in the main loop and are used all the time. The arrangement of the data in these 3D matrices is of huge importance since the memory needs to be accessed in a coalesced way for achieving high performance, such that various *float* values are handled in only one read/write memory access.

Some names of variables from the CUDA source code appear throughout this section. Their meaning is explained as follows:

**BN:** Number of bit nodes.

**CN:** Number or check nodes.

maxBNConn: Maximum number of bit node connections.

maxCNConn: Maximum number of check node connections.

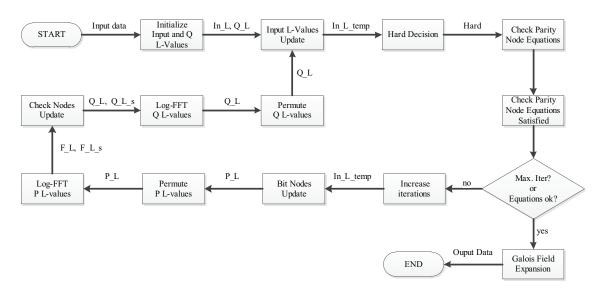

#### 3.2.1 Algorithm Flowchart

The flowchart of the LDPC GF(q) decoding algorithm is shown in Figure 3.10. Each process block represents a basic part of the algorithm and is implemented as a CUDA kernel. The incoming and outgoing variables of each process are also shown in the figure and their name is the same as in the CUDA code for simplicity and for a better understanding of the code.

The diagram of Figure 3.10 follows exactly the algorithm present in the C++ source code implementation in [8]. Initially, the number of iterations is zero and the input data is transferred to the *device* for calculating the initial L-values ( $in\_L$ ). The loop is executed at least once for checking the parity equations. The iterative decoding stops if there are no errors in the decoded data or if the number of iterations reaches the maximum value. When the iterative decoding process finishes, the data is transformed into a binary output and sent back to the *host*. The meaning of the variables and their respective properties are exposed in Section 3.2.2.

**Figure 3.10:** LDPC GF(q) Decoder flowchart.

Almost all the *kernels* follow approximately the C++ source code structure and have been adapted for CUDA parallel processing. The log-FFT algorithm has been completely designed from zero, since the C++ source code is based on the serial implementation [8].

#### 3.2.2 Data Structures

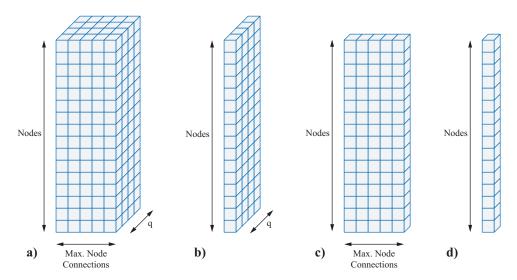

Although the data is stored in the device memory as 1D array, they are interpreted as 1D, 2D or 3D structures, depending on the indexing of each one. This indexing points to the exact position of one element in the structure, and helps to set the grids and blocks configuration of the kernels. The order of the indices in the structures determine the final position of the data and, therefore, the performance of the memory access.

There are three kind of structures for the variables that are shown in Figure 3.11. CUDA needs fixed sizes for data structures, and since irregular LDPC codes have not a constant number of Tanner graph connections, it is obligatory to set the node connections dimension to the maximum value, taking care of not accessing the invalid positions during the processing. This is achieved using some auxiliary variables.

The 1D vectors (Figure 3.11-d) are used for the hard and output variables. The 2D matrices (Figure 3.11-b-c) are used for the  $in\_L$  and  $in\_L\_temp$  variables. Finally, the 3D matrix (Figure 3.11-a) is applied to  $P\_L$ ,  $FP\_L$ ,  $FP\_L$ ,  $FP\_L$ ,  $Q\_L$ ,  $QP\_L$  and  $QP\_L$ , and it becomes the most important data structure in the implementation, since the corresponding variables take part in the iterative loop, the most important part of the decoding algorithm. The first index is pertinent to the node, the second to the node connection and the third to the symbol element. By arranging the data in this order, it is possible to access the memory in a coalesced way. If each q adjacent Galois field elements (indexes defined by the nodes and the node connections) are accessed by q adjacent threads, this

**Figure 3.11:** Data structures used in the LDPC GF(q) CUDA algorithm.

access is coalesced, as it is shown in Figure 3.12. This arrangement boosts the performance with increasing q.

**Figure 3.12:** Continuous data allocation in the global memory.

The different variables present in the algorithm with their respective data structures and indexing expression are described in the following.

#### 3.2.2.1 Non-constant variables

These variables are stored in the global memory because they need to be fully accessible (whichever position could be required in a random memory access) and they could be too huge for fitting in smaller memories (like, e.g., the constant memory or the texture memory). The description of each variable is as follows:

in\_L: Input L-values.

$in\_L\_temp$ : Input L-values updated with the  $Q\_L$  values.

**P\_L**: Outgoing L-values from the bit nodes connections.

$FP\_L$ : log-FFT module of  $P\_L$ .

$FP\_L\_s$ : log-FFT sign of  $P\_L$ .

**Q\_L**: Outgoing L-values from the check nodes connections.

$QP\_L$ : log-FFT module of  $Q\_L$ .

$QP\_L\_s$ : log-FFT sign of  $Q\_L$ .

Their size and indexing properties are shown in Table 3.7.

| Name                      | Dim. $i$ | Dim. $j$  | Dim. $k$ | Indexing                                                                   |

|---------------------------|----------|-----------|----------|----------------------------------------------------------------------------|

| $in\_L$                   | BN       | q         | -        | $i\cdot q+j$                                                               |

| $in\_L\_temp$             | BN       | q         | -        | $i\cdot q+j$                                                               |

| $P\_L$                    | BN       | maxBNConn | q        | $i \cdot \text{maxBNConn} \cdot \mathbf{q} + j \cdot \text{maxBNConn} + k$ |

| $FP\_L$                   | BN       | maxBNConn | q        | $i \cdot \text{maxBNConn} \cdot \mathbf{q} + j \cdot \text{maxBNConn} + k$ |

| $FP\_L\_s$                | BN       | maxBNConn | q        | $i \cdot \text{maxBNConn} \cdot \mathbf{q} + j \cdot \text{maxBNConn} + k$ |

| $\mathbf{Q}_{\mathbf{L}}$ | CN       | maxCNConn | q        | $i \cdot \text{maxCNConn} \cdot \mathbf{q} + j \cdot \text{maxBNConn} + k$ |

| $QP\_L$                   | CN       | maxCNConn | q        | $i \cdot \text{maxCNConn} \cdot \mathbf{q} + j \cdot \text{maxBNConn} + k$ |

| $QP\_L\_s$                | CN       | maxCNConn | q        | $i \cdot \text{maxCNConn} \cdot \mathbf{q} + j \cdot \text{maxBNConn} + k$ |

**Table 3.7:** Properties of the non-constant variables

#### 3.2.2.2 Constant variables

As the size of these variables depends on the size of the parity check matrix and as they are accessed occasionally in an aleatory way, they are stored in the global memory. They are used for obtaining information from the parity check matrix. The following variables are constant:

cudaNumBNConn: Number of connections for each bit node.

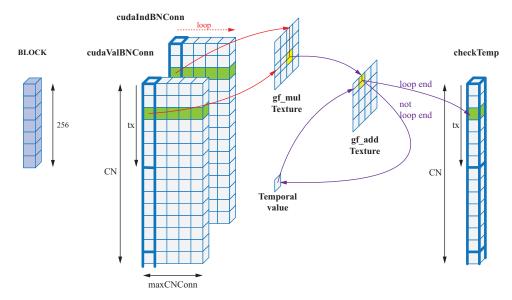

cuda ValBNConn: Value of the parity check matrix for each index.

cudaIndBNConn: Index of the check node to which the actual bit node connection is attached.

cudaBN2CN: Index of the actual bit node connection from the check node point of view.

cudaNumCNConn: Number of connections for each check node.

cuda ValCNConn: Value of the parity check matrix for each index.

cudaIndCNConn: Index of the bit node to which the actual check node connection is attached.

cudaCN2BN: Index of the actual check node connection from the bit node point of view.

Table 3.8 provides information about sizes and indexing of these variables.

| Name             | Dim. $i$ | Dim. $j$  | Dim. $k$ | Indexing                                                             |

|------------------|----------|-----------|----------|----------------------------------------------------------------------|

| cuda Num BN Conn | BN       | -         | -        | i                                                                    |

| cuda ValBNConn   | BN       | maxBNConn | -        | $i \cdot \text{maxBNConn} + j$                                       |

| cuda Ind BN Conn | BN       | maxBNConn | -        | $i \cdot \text{maxBNConn} + j$                                       |

| cudaBN2CN        | BN       | maxBNConn | q        | $i \cdot \text{maxBNConn} \cdot \mathbf{q} + j \cdot \mathbf{q} + k$ |

| cuda Num CN Conn | CN       | -         | -        | i                                                                    |

| cuda Val CN Conn | CN       | maxCNConn | -        | $i \cdot \text{maxCNConn} + j$                                       |

| cuda Ind CN Conn | CN       | maxCNConn | -        | $i \cdot \text{maxCNConn} + j$                                       |

| cudaCN2BN        | CN       | maxCNConn | q        | $i \cdot \text{maxCNConn} \cdot \mathbf{q} + j \cdot \mathbf{q} + k$ |

**Table 3.8:** Properties of the constant variables

#### 3.2.2.3 Texture Tables

Some special functions are required to operate over the  $\mathrm{GF}(q)$ . These functions are addition, multiplication, inversion, decimal to exponential conversion and exponential to decimal conversion. These functions are implemented in tables of dimensions q or  $q \cdot q$ . The tables are allocated in the texture memory (1D or 2D arrangement) for taking advantage of the data locality and the memory speed (the texture memory has special fast access for data in near space). The table values are calculated following the C++ reference implementation [10].

*gf\_inv*: Inversion function.

*gf\_add*: Addition function.

**gf\_mul:** Multiplication function.

gf\_dec2exp: Decimal to exponential conversion.

qf exp2dec: Exponential to decimal conversion.

Table 3.9 shows the size and the arrangement of textures for these functions. The access to the textures is done with the tex1Dfetch() and tex2D() CUDA functions [12].

| Name          | Dim. i | Dim. $j$ | Access                                                              |

|---------------|--------|----------|---------------------------------------------------------------------|

| $gf\_inv$     | q -1   | ı        | $\mathbf{tex1Dfetch}(\mathit{gf\_inv}\;,\mathbf{i})$                |

| $gf\_add$     | q      | q        | $\mathbf{tex2D}(gf\_add, i, j)$                                     |

| $gf\_mul$     | q      | q        | $\mathbf{tex2D}(\mathit{gf\_mul}\;,\mathbf{i},\mathbf{j})$          |

| $gf\_dec2exp$ | q      | -        | $\mathbf{tex1Dfetch}(\mathit{gf\_dec2exp}\ , \mathbf{i})$           |

| $gf\_exp2dec$ | q      | -        | $\mathbf{tex1Dfetch}(\mathit{gf}\_\mathit{exp2dec}\ ,  \mathbf{i})$ |

**Table 3.9:** Properties of the variables allocated in the texture memory

#### 3.2.3 Kernel Implementations

The data structures have specific dimensions, and it is essential to configure the grid and block dimensions on each kernel for an optimal and fast execution. It is also necessary to

keep in mind the constraints of the hardware for achieving high performance: maximum number of threads per SM, maximum number of blocks per SM, shared memory per SM, etc. The number of threads per block is fixed here to 256 because in this way the occupancy is 100% in most cases, using 4 blocks per SM and without exceeding the maximum available shared memory. The number of Galois field elements is a constant power-of-two value. This makes this value a good candidate for one of the block dimensions, because it is easy to achieve power-of-two block of threads in this way. The blocks with a power-of-two size are accessed faster by the hardware. The reason is that for a typical power-of-two value of threads per block (this is 64, 128, 256 or 512) each warp (32 continuous threads) can execute the same instruction.

All the kernels in this section are implemented as  $\underline{global}$  kernels. The threads in the x and y dimensions are referred as tx and tx respectively.

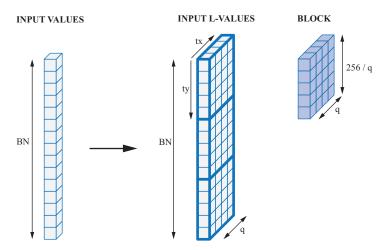

#### 3.2.3.1 Input L-Values Initialization (cudaInLInitialize)

The kernel initializes the input L-values matrix from the main input data of the decoder. It follows the C++ reference implementation [10], but adapted to CUDA.

Figure 3.13: Description of the cudaInLInitialize kernel.

The output values have a 2D structure, as it can be seen in Figure 3.13. Each thread processes a different Galois field element in a particular Tanner graph bit node connection. The width of the block is the number of Galois field elements, which is a power-of-two number. The height of the block corresponds to 256/q threads or nodes. Thus, each ty identifies the Tanner graph variable node, and each tx identifies the Galois field element. Since q is a constant value, the grid is arranged in one dimension, and the number of blocks per grid is the total number of variable nodes divided by the block height (see Table 3.10).

The input values are indexed by index  $\cdot p + k$ , where k is the control variable of an internal loop. So, as the index has not a linear relation with the thread number, the access is not coalesced. Since this kernel is only executed once at the beginning, this is not significant.

|               | X Dimension | Y Dimension |

|---------------|-------------|-------------|

| Threads/Block | q           | 256/q       |

| Blocks/Grid   | BN/(256/q)  |             |

**Table 3.10:** Block and grid settings for the **cudaInLInitialize** kernel.

The output values are indexed by  $ty \cdot q + tx$  as the thread number and the position have a linear relationship, the access to the memory is continuous.

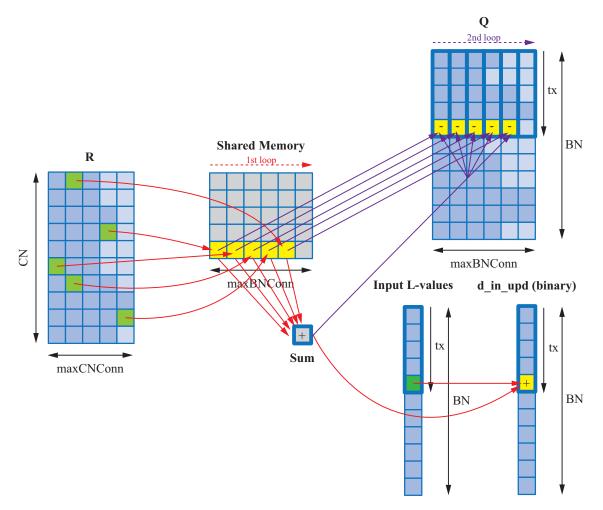

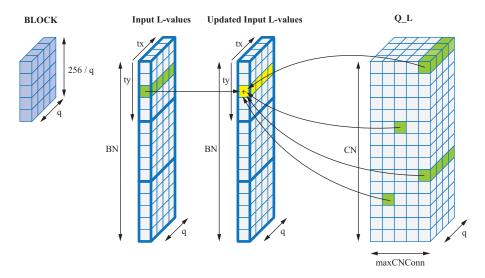

#### 3.2.3.2 Input L-values Update (cudaInLUpdate)

The input L-values are updated with the L-values  $Q\_L$  in each decoding iteration. These updated L-values are used later for the hard decision. Each Galois field element in a variable node is the sum of the corresponding input L-value plus the corresponding  $Q\_L$  values for all the variable node connections.

Figure 3.14: Description of the cudaInLUpdate kernel.

The block has a 2D structure. The width is set to q, because it is a constant power-of-two value, and the height is set to 256/q. Each ty represents the Tanner graph variable node, and each tx represents the Galois field element. A loop is used in each thread for processing all the Tanner graph variable node connections and obtaining the correspondent symbol value.

|               | X Dimension | Y Dimension |

|---------------|-------------|-------------|

| Threads/Block | q           | 256/q       |

| Blocks/Grid   | BN/(256/q)  |             |

Table 3.11: Block and grid settings for the cudaInLUpdate kernel

For each Tanner graph variable node, the loop counts up to the number of variable node connections, given by maxBNConn. For each iteration, the corresponding Galois field element value is read from  $Q_L$  using the corresponding cudaBN2CN index and its value is added to the final sum. Once the loop is completed, the final sum is written to  $in_L$  Temp.

The input and output data are indexed by  $ty \cdot maxBNConn \cdot q + tx$ . Since the index and the thread number have a linear relationship, the global memory is accessed in a continuous way. For the sum, the matrix  $Q_L L$  is indexed  $[BN2CN[ty \cdot maxBNConn \cdot q + iteration \cdot q + tx]$ , which is a random access. Since the random memory access is performed for a given node and node connection combination, there are q continuous memory accesses in every new aleatory indexing.

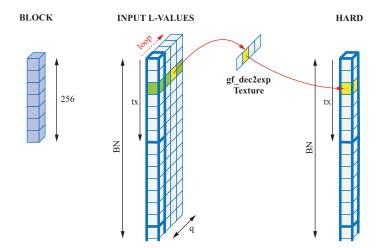

#### 3.2.3.3 Hard Decision (cudaHard)

The updated L-values are required for the hard decision. Each thread processes a given Tanner graph node. In each thread, a loop processes all the Galois field elements searching for the symbol with maximum value. The position of this maximum value is converted to exponential using the  $gf_exp2dec$  texture table, and is written to the output structure.

Figure 3.15: Description of the cudaHard kernel.

The block has only one dimension, and each thread represents a Tanner graph variable node. For each node, a *for* loop processes all the Galois field elements looking for the maximum value and its position.

|               | X Dimension |

|---------------|-------------|

| Threads/Block | 256         |

| Blocks/Grid   | BN/256      |

**Table 3.12:** Block and grid settings for the **cudaHard** kernel

Figure 3.16: Description of the cudaCheckNodeEquations kernel.

This implementation is not optimal since the loop has to perform q iterations, but it is of high computational cost. An improvement can be to search for the maximum value with a reduction algorithm applied to each thread (node), using the shared memory (Figure 3.15).

#### 3.2.3.4 Check Node Equations (cudaCheckNodeEquations)

The kernel checks the parity equations in all the check nodes, obtaining a binary output vector of size CN. After the kernel execution, each element of the vector is 0 if the correspondent parity check equation is satisfied, or 1 if not. The data structures involved in this kernel are cudaValCNConn, cudaIndCNConn,  $gf_mul$  and  $gf_add$ .

Each thread defines a Tanner graph check node, as it is shown in Figure 3.16. Following the C++ reference code, a temporal variable is set to -1 for each check node. A loop processes all the check node connections and increases the temporal variable with some operations in the GF(q) space (refer to the code for detailed information). The variables involved are cudaValCNConn, cudaIndCNConn,  $gf_mul$  and  $gf_add$ .

The indexing of all the variables in the global memory is performed with a linear relationship with the thread index for achieving a fast memory access.

|               | X Dimension |

|---------------|-------------|

| Threads/Block | 256         |

| Blocks/Grid   | CN/256      |

Table 3.13: Block and grid settings for the cudaCheckNodeEquations kernel

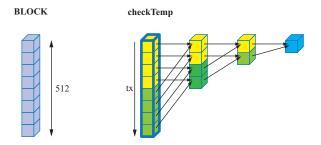

#### 3.2.3.5 Check Node Equations Satisfied (cudaCheckNodeEquationsSatisfied)

An addition reduction algorithm is applied to the temporal vector obtained in the cud-aCheckNodeEquations. The partity equations are fully satisfied if the result of the sum is zero (all the node equations are satisfied), and in this case the decoding process can be interrupted.

Figure 3.17: Description of the cudaCheckNodeEquationsSatisfied kernel.

The reduction algorithm takes advantage of the parallelization, performing the sum in  $log_2(CN)$  iterations, where CN is the number of elements in the input vector. In each iteration, the upper half of the vector is added to the lower half in a simple parallel step. When the reduction is finished, the result is stored in the element with index zero.

The blocks have 1D structure and execute 512 threads for maximizing the performance. The shared memory is used to process the reduction algorithm in a small loop. The memory amount used is 4096KBytes per SM, since only two 512 threads blocks are processed in each SM.

|               | X Dimension |

|---------------|-------------|

| Threads/Block | 512         |

| Blocks/Grid   | CN/512      |

| Shared Memory | 2048 KBytes |

Table 3.14: Block and grid settings for the cudaCheckNodeEquationsSatisfied kernel

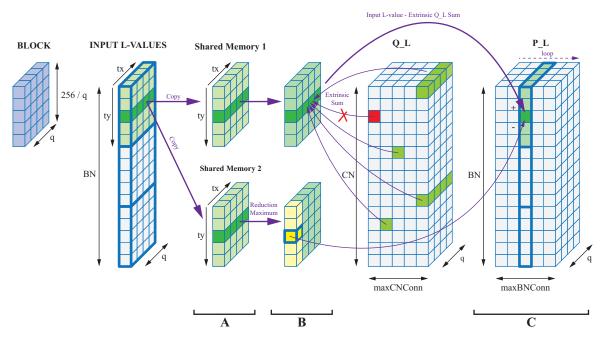

#### 3.2.3.6 Bit Node Update (cudaBitNodeUpdate)

The main function of this kernel is to generate the new updated L-values  $P_L$  from the input L-values  $in_L$  and the estimated L-values  $Q_L$ . The kernel processes one thread per Tanner graph variable node. An internal loop processes all the node connections corresponding to each thread.

Each thread (Tanner graph variable node) reads the corresponding updated input L-values (q Galois field elements) from  $in\_L$ . This initial value is updated with the extrinsic sum of the estimated L-values  $Q\_L$ . For each node connection, the maximum value among the Galois field elements is subtracted from all of them, as indicated in [8].

Figure 3.18: Description of the cudaBitNodeUpdate kernel.

The block width is fixed to q, and the block height is fixed to 256/q. Thus, ty defines the Tanner graph variable node, and tx defines the Galois field element. The internal loop processes all the node connections (Figure 3.18-C). For each loop iteration (each variable node connection), the bit input L-values corresponding to the actual node are copied twice into the shared memory (Figure 3.18-A) in two different memory blocks. The extrinsic sum of the matching values Q L (accessed through cudaBN2CN) is added to the first shared memory block (input L-values plus the extrinsic sum of  $Q_L$  values). At the same time, the second shared memory block performs the search of the maximum Galois field element of the input L-values for each node (Figure 3.18-B) using a reduction algorithm. This reduction algorithm performs a parallel search of the maximum value using a loop with  $log_2(q)$  iterations, where q is the Galois field dimension. After the reduction, the maximum symbol value is present in each zero index position. Finally, each Galois field element of the actual node and iteration (variable node connection) is updated with the values of the first shared memory block minus the maximum value, calculated in the second shared memory block (Figure 3.18-C). The use of the loop is important since it has a few number of looping iterations (not the same number for every node), and achieves a very good performance with this 2D block configuration.

Each block requires 2048 KBytes of shared memory (two shared memory blocks of 256(cells)-4(bytes/cell)). Using 256 threads per block, each SM can manage up to 4 blocks. So, the maximum amount of shared memory required is 8 KBytes.

Each shared memory block is indexed by (block number)  $\cdot 256 + ty \cdot q + tx$ . Since the shared memory operations are inside the node connections loop, continuous thread numbers access to different shared bank memory in each iteration. This avoids bank conflicts and provides maximum performance for the shared memory.

34 3 Implementation

|               | X Dimension | Y Dimension      |

|---------------|-------------|------------------|

| Threads/Block | q           | $256/\mathrm{q}$ |

| Blocks/Grid   | 1           | BN/(256/q)       |

| Shared Mem.   | 2 · 4096    | KBytes           |

Table 3.15: Block and grid settings for the cudaBitNodeUpdate kernel

The input and output variable indexing has a linear relationship with the thread index. This means that the memory is accessed in a continuous way, achieving high performance. Each random access to  $Q\_L$  performs q continuous readings. Thus, the random memory accesses performs better for increasing q values.

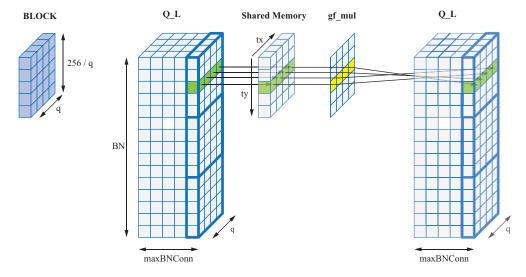

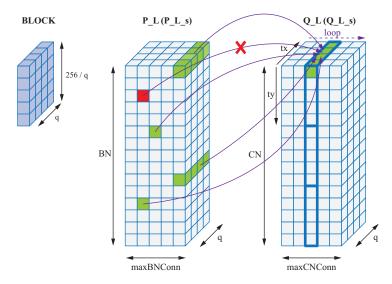

#### 3.2.3.7 Permutation of $P_L$ and $Q_L$ (cudaPermuteP and cudaPermuteQ)

The Galois field elements of the Tanner graph variable node connections in  $P_L$  and the check node connections in  $Q_L$  are permuted by moving the a-th element of the vector to position  $a \cdot H_{i,j}$ , where the multiplication is performed over GF(q) [8]. This process applies to  $P_L$  and  $Q_L$  almost in the same way (the  $Q_L$  permutation is the inverse permutation and uses a slightly different indexing). A shared memory block is used as temporary memory, allowing a parallel implementation of the permute operation. In cudaPermuteP, the shared memory stores the input data using the permuted indices (calculated using  $gf_dec2exp$ ,  $gf_mul$  and  $gf_exp2dec$ ), and writes the output data directly. The cudaPermuteQ only changes the way the permutation is done. In this case, the shared memory reads the input values using the same indices, but the output is written using the permuted indices. Since each thread accesses different shared memory banks, no bank conflicts are generated, performing a full speed memory access.

Figure 3.19: Description of the cudaPermuteP and cudaPermuteQ kernels.

Each ty corresponds to a different Tanner graph node connection, and each tx corresponds to the Galois field element. The  $P\_L$  and  $Q\_L$  data is interpreted as groups of q Galois field elements. The block width is fixed to q and the block height is fixed to q and the block height is fixed to q. Each thread is independent if it uses a shared memory block as temporal memory. The required amount of shared memory per block is 1 KByte. As the number of blocks per SM is 4, the shared memory is not a restriction.

|                              | cudaPermu                | ıteP                         |

|------------------------------|--------------------------|------------------------------|

|                              | X Dimension              | Y Dimension                  |

| Threads/Block                | q                        | 256/q                        |

| Blocks/Grid                  | 1                        | $BN \cdot maxBNConn/(256/q)$ |

| Shared Mem.                  | 4                        | 4096 KBytes                  |

|                              |                          |                              |

|                              | cudaPermu                | iteQ                         |

|                              | cudaPermu<br>X Dimension | teQ<br>Y Dimension           |

| Threads/Block                |                          | •                            |

| Threads/Block<br>Blocks/Grid |                          | Y Dimension                  |

Table 3.16: Block and grid settings for the cudaPermuteP and cudaPermuteQ kernels

The complete Galois field vector is transferred to the shared memory. The new indexes are calculated using the  $gf\_exp2dec$ ,  $gf\_dec2exp$  and  $gf\_mul$  texture tables. The permutation is performed reading the new index from the shared memory and writing the old one in the P L structure.

The input and output data indexing has a linear relationship with the thread index, so the memory access is continuous. The shared memory is mapped for avoiding bank conflicts, at least in the permutation of Q, since the access is not exactly the same in both kernels [10].

#### 3.2.3.8 Log-FFT (cudaLogFFTP and cudaLogFFTQ)

The algorithm for performing the log-FFT is the same for P and Q structures and it follows a butterfly diagram. As explained in [8], two log-FFT executions (one for the module and one for the sign) have to be performed. Both of them are executed simultaneously in the CUDA kernel implementation. Two shared memory blocks are required for this purpose.

The log-FFT is applied to each q Galois field elements group. Thus, each Galois field elements group is independent. The block width is fixed to q and the block height is q and q and

For each Tanner graph node, a loop processes all node connections for processing the log-FFT of the q Galois field elements.

36 3 Implementation

Figure 3.20: Description of the log-FFT process.

|               | $\operatorname{cudaLogFFTP}$ |                   |

|---------------|------------------------------|-------------------|

|               | X Dimension                  | Y Dimension       |

| Threads/Block | q                            | 256/q             |

| Blocks/Grid   | 1                            | BN/(256/q)        |

| Shared Mem.   | 2 · 4096                     | 6 KBytes          |

|               |                              |                   |

|               | ${ m cudaLogFFTQ}$           |                   |

|               | x Dimension                  | Y Dimension       |

| Threads/Block |                              | Y Dimension 256/q |

|               |                              |                   |

Table 3.17: Block and grid settings for the cudaLogFFTP and cudaLogFFTQQ kernels

The execution of the butterfly diagram is supervised by a small loop of  $log_2(q)$  iterations and the control loop variable. The crossed additions and subtractions in the log-domain are performed over the shared memory. Since each continuous thread accesses a different shared memory bank during the butterfly crosses, no bank conflicts are produced. The result is transferred to the original data structure once the loop is finished.

Both kernels, **cudaLogFFTP** and **cudaLogFFTQ**, process log-magnitude and log-sign float values. In the case of **cudaLogFFTP**, only the magnitude is available as input  $(P_L)$ , so the sign variable is initialized to one. The output variables are  $FP_L$  and  $FP_L$ s. In the case of **cudaLogFFTQ**,  $QP_L$  and  $QP_L$ s are the input, and only  $QP_L$  is generated.

The additions and subtractions in the different iterations of the loop are performed over the log-domain, as explained in [8]. Two special \_\_\_device\_\_ kernels (cudaBoxPlusM and cudaBoxPlusS) have been implemented for calculating the signed log-domain addition

and subtraction in the module and sign case respectively. Both functions are called from inside the kernel. The code of those device kernels follows exactly the C++ reference implementation [10]. The exponential and logarithm functions are used in the signed log-domain function. The fast hardware implemented  $\__expf()$  and  $\__logf()$  functions are used for this purpose, achieving the fastest performance in this way.

The transfer of data between the global memory and the shared memory is done in a coalesced way, since the indexing has a linear relationship with the thread number. The shared memory is accessed from within the loop. Thus, the indexing  $(memory\ block) \cdot 256 + ty \cdot q + tx$  performs accesses without bank conflicts.

#### 3.2.3.9 Check Node Update (cudaCheckNodeUpdate)

Each thread processes the extrinsic sum of the  $FP\_L$  and  $FP\_L\_s$  symbol values for all the node connections in each Tanner graph check node.

Figure 3.21: Description of the cudaCheckNodeUpdate kernel.

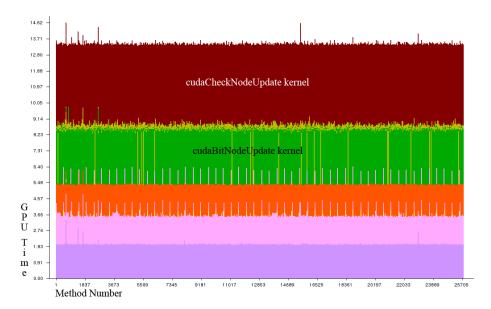

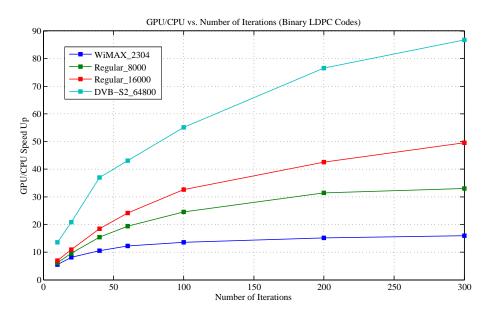

Since this kernel is processed in the frequency log-domain, magnitude and sign calculus are performed separately. For each thread, a first loop processes all the node connections for calculating the total sum of the magnitude values and the total product of the sign values. After this, a second loop processes the node connections again, for individually subtracting the current magnitude value from the total magnitude sum (extrinsic sum), and individually dividing the current sign value from the total sign product (extrinsic product). Shared memory is not required since all the memory accesses ( $QP\_L$  writing and  $FP\_L \& FP\_L\_s$  reading through cudaCN2BN) are coalesced.