Document downloaded from:

http://hdl.handle.net/10251/147545

This paper must be cited as:

Cazorla, FJ.; Kosmidis, L.; Mezzetti, E.; Hernández Luz, C.; Abella, J.; Vardanega, T. (2019). Probabilistic Worst-Case Timing Analysis: Taxonomy and Comprehensive Survey. ACM Computing Surveys. 52(1):1-35. https://doi.org/10.1145/3301283

The final publication is available at

https://doi.org/10.1145/3301283

Copyright Association for Computing Machinery

Additional Information

"© ACM, 2019. This is the author's version of the work. It is posted here by permission of ACM for your personal use. Not for redistribution. The definitive version was published in ACM Computing Surveys, {VOL 52, ISS 1, (February 2019)} https://dl.acm.org/doi/10.1145/3301283"

# Probabilistic Worst-Case Timing Analysis: Taxonomy and Comprehensive Survey

Francisco J. Cazorla<sup>†</sup>, Leonidas Kosmidis<sup>†</sup>, Enrico Mezzetti<sup>†</sup>, Carles Hernandez<sup>†</sup>, Jaume Abella<sup>†</sup>, Tullio Vardanega<sup>‡</sup>

> <sup>†</sup>Barcelona Supercomputing Center (BSC) <sup>‡</sup>University of Padova

#### Abstract

The unabated increase in the complexity of the hardware and software components of modern embedded real-time systems has given momentum to a host of research in the use of probabilistic and statistical techniques for timing analysis. In the last few years, that front of investigation has yielded a body of scientific literature vast enough to warrant some comprehensive taxonomy of motivations, strategies of application, and directions of research. This survey addresses this very need, singling out the principal techniques in the state of the art of timing analysis that employ probabilistic reasoning at some level, building a taxonomy of them, discussing their relative merit and limitations, and the relations among them. In addition to offering a comprehensive foundation to savvy probabilistic timing analysis, this paper also identifies the key challenges to be addressed to consolidate the scientific soundness and industrial viability of this emerging field.

# 1 Introduction

Embedded real-time systems are increasingly interwoven in the control of critical elements of human life, including the health, security and safety concerns of it [42]. The dependence of the latter on the former rests on the ability of the system software to carry out the assigned critical control functions effectively, in conformance with the applicable safety regulations. As part of that trend, software has become the main value-added vector for most embedded real-time products. In consequence of that, the nature of the critical functionalities implemented in software has changed from rather confined procedures to large, articulate, diverse and complex algorithms that oversee multiple information flows between vast arrays of sensors and actuators. In the automotive domain, for instance, the quantity of software embedded in cars already exceeds 100 millions lines of code [29], with performance requirements predicted to rise by two orders of magnitude by 2024 [17]. Similar trends occur in other application domains, cf. e.g. [43] for space.

At the processor level, the use of more advanced acceleration features is the only practical means to sustain the ever-increasing demand of guaranteed

© ACM, 2019. This is the author's version of the work. It is posted here by permission of ACM for your personal use. Not for redistribution. The definitive version was published in ACM Computing Surveys {Volume 52 Issue 1, February 2019} https://dl.acm.org/citation.cfm?doid=3309872.3301283

performance put forward by value-added application software. Not surprisingly, this trend has caused a sweeping transition from simple 8- and 16-bit micro-controllers to more complex processors in new-generation systems for the aerospace, automotive and rail domains. For example, existing 32-bit processors in current automotive subsystems embed accelerator-based multicore units, like in the NVIDIA DrivePX [4], RENESAS R-Car H3 [3], QUALCOMM Snap-dragon 820 [2], and Intel Go [61].

Timing is one of the main non-functional concerns in embedded real-time systems. Timing analysis aims to ascertain whether software programs execute within the bounds assigned to them at specification, which normally regard duration (aka worst-case execution time, WCET) and completion (aka response time). The former type of analysis seeks to upper bound the execution duration of individual software units considered in isolation. The latter assesses whether a feasible (concurrent or parallel) compositional schedule of those software units exists that allows them to complete their work in a timely manner, i.e. within assigned deadlines that respond to high-level needs of the system's functionality, after factoring in the impact of the interference among them. Arguably, the hardest challenge of WCET analysis is to comprehend the extent of executiontime variability (i.e., jitter) that software programs may exhibit when run on their target platform.

- For simple platforms, the sources of jitter (i.e., the features that contribute to the variability of the program's execution time across runs) are limited to the software program's structure and its input data. The former reflects how multiple identical runs of the program may take different durations depending on the execution path taken by the program. The latter reflects how the input data affect programs execution, for instance determining the branch taken in the program path or the duration of jittery operations, e.g., floating point operations.

- As platform complexity increases, new low-level and hard-to-catch sources of jitter emerge, which include cache utilization, bus occupancy, and parallel contention for shared resources in multicores. Those elements may have a dominant impact on the program's jitter.

The increase in complexity at software and hardware level has resulted in a relentless quest for novel timing analysis methods capable of mastering it. The hardness of that challenge has caused a surge of interest in the use of statistical and probabilistic techniques, owing to their ability to reason on (black-box) observations, which are orders of magnitude easier to obtain than (white-box) knowledge on the relevant internals of an execution. A wide range of works exist that extends from tailoring statistical techniques used in other domains to fit the timing analysis problem, to dressing hardware to better match the premises of probabilistically analysable behaviour. Probabilistic techniques have been explored in virtually all aspects and layers of the system overall, including application programs, the operating system, the compilation system and its linker, the processor hardware, and, of course, the very fabric of the timing analysis itself.

While there is growing evidence that probabilistic and statistical techniques may help alleviate some of the limitations that hamper traditional timing analysis solutions, the proliferation of works that have appeared in the last few years is making it hard for interested individuals to understand the forming landscape of research in that area. Arguably, one pressing need for all observers of the present state of the art is to appreciate how those novel techniques relate to one another, to comprehend the assumptions on which they build, and to determine how they contribute to earning industrial acceptance for probabilistic-based timing analysis.

This is what this paper aims to contribute:

- 1. A comprehensive critical taxonomy of the existing works on probabilistic timing analysis, clarifying which specific problems they aim to attack, how probabilistic and statistical techniques are exploited (thereby exposing the limitations of each proposal), and where different proposals overlap or complement one another.

- 2. A scrutiny of the assumptions that each surveyed technique makes on the underlying execution platform and the application timing behaviour, in the intent of clearing the ground for well-founded use of probabilistic analysis.

The remainder of this paper is organized as follows: Section 2 presents the motivation and intuitions behind the application of probabilistic approaches to the timing analysis problem, and proposes a comprehensive taxonomy of the relevant state of the art. Sections from 3 to 8 survey the principal lines of work in that taxonomy. Section 9 concludes by discussing the overall status of probabilistic timing analysis, for theory and technology, and its readiness for industrial use.

# 2 Probabilistic WCET Analyses

### 2.1 Setting the Scene

Deriving high-quality WCET estimates is universally accepted as a challenging task [112]. When facing the WCET problem, industrial practitioners screen the state of the art of solution offerings, to determine which approach best meets their needs and obligations. Ultimately, industrial choice seeks to balance the cost-effectiveness of the solution and the quality of the evidence that it can provide to attain the level of confidence required by the domain prescriptions [9].

Two dominant flavors of timing analysis exist:

- Static methods (STA, in the sequel) seek absolute theoretical rigor, at the cost of complexity in use and pessimism in the results that may inordinately increase as system design becomes more complex. The quality of their results strictly depends on the availability of accurate and sufficient information on the hardware and software internals (and in particular on their timing behaviour) of the system to analyze. For this reason, [50] notes that mathematical rigor per se, while obviously beneficial, is insufficient to assure that the provided estimate always upper-bounds actual execution times.

- Measurement-based methods (MBTA, in the sequel) follow less rigorous approaches (a vulnerability that must be addressed with utmost care), for

much lower cost of use. Those methods seek to provide empirical evidence that the worst-case conditions of interest have been exercised or closely approximated in the measurement observations.

MBTA is the most commonly used technique in industry, owing to its low cost-benefit ratio. Evidence exists that measurements can be also used for functions with the highest criticality level, e.g. DAL-A in avionics [75]. Yet, STA is the preferred solution for the software functions at the highest criticality levels. To contain the costs of qualification (or certification, where required), those functions typically execute on simple processors and represent a modest fraction of the value-added software in the system overall [47].

The advent of high-performance hardware presents STA and MBTA with hard challenges. STA is especially affected in its quest for accurate timing models to compute the cost of individual processor instructions and the basic blocks of software programs. The presence of intellectual property restrictions and the vastness of hardware documentation increases the risk of considering inaccurate or incomplete timing information [9], ultimately causing STA users to depend on measurements and reverse engineering for filling the consequent information gaps [93]. MBTA suffers too, as further sources of jitter appear in hardware resources (e.g., bus occupancy, cache placement) that are difficult to study or observe in isolation, for the lack of sufficient hardware monitors or specification information.

Another problem with high-performance computing systems is that, no matter how deterministic the individual hardware components may be, the fabric of their interaction tends to grow exceedingly complex, causing an explosion in the state space on which the program's timing behaviour depends *together with* a potentially large increase in the overall jitter. The former consequence makes it difficult to determine the worst-case scenario; the latter increases pessimism.

The application of probabilistic reasoning to timing analysis aims at mitigating some of the limitations of the existing techniques.

- The probabilistic variant of MBTA, aka measurement-based probabilistic timing analysis (MBPTA), aims at easing the construction of qualification-worthy arguments that the worst-case scenarios of interest have been captured in observation runs, in a manner that lives up with the increase in hardware complexity.

- The probabilistic variant of STA (SPTA) aims at reducing the pessimism incurred by traditional WCET analysis, while also reducing the information need. SPTA builds on the notion of execution-time profile (ETP) that describes the probabilistic execution-time distribution of individual instructions. ETPs are an attribute of static instructions at binary level as they are assumed to upper-bound all of their (dynamic) instances (that is, the executions of that instruction during program runs).

The application of either variant of PTA requires changes to the system for it to conform with the analysis assumptions. The state of the art includes PTA works that address (i) systems where no hardware or software changes had been applied (COTS), (ii) systems that employed COTS hardware but used software modifications transparent to the application (SWRand), and (iii) systems whose processors had been modified in selected components (HWRand).

# 2.2 The Wisdom of Probabilistic Reasoning on WCET

PTA requires to cease seeking single-valued WCET estimates, as unique definitive upper-bounds to all instances of execution-time duration, to concentrate instead on a distribution function, aka probabilistic WCET (pWCET), thus modelling the maximum probability with which a WCET bound can be exceeded. PTA is a broad paradigm, which encompasses all timing analysis methods that yield pWCET estimates regardless of the specific prerequisites that each such method may impose on the characteristics of the execution platform and its modelling, the measurement collection protocol, the existence and the modelling of dependencies, and the degree of knowledge or control required from the user. To put the PTA paradigm shift in prospective, one should appreciate that the assurance attached to the single-valued product of STA rests on the quality of the information passed to it (e.g., processor model, instruction timing, flow facts), which however cannot be quantified in the general case [50].

In acknowledgment of the lack of absolute certainty, no critical real-time embedded system is conceivably designed assuming absence of timing failures (i.e., task overruns). Instead, systems are designed so that no such event should ever cause the system to enter an unsafe state: If it did, that would be a single point of failure, consequent to inadequate safety-case design. Domainspecific standards require system engineering to encompass a safety process that sanctions the strategy required to mitigate the system-level risk of hardware or software malfunctions. Various mechanisms (e.g., replication, online monitoring, watchdog) are then deployed to detect and react to undesired situations, in accord with the criticality of the system part of interest.

Interestingly, probabilistic reasoning is habitually used in the design of electronic components [13], to model the appearance of certain types of hardware faults such as, for instance, random hardware faults due to particle strikes from the outer Space or other forms of electromagnetic interference. Probabilistic reasoning on WCET bounds matches that reality quite naturally.

# 2.3 A Taxonomy of PTA Works

The initial works on PTA, which date back to the early 2000's, reason theoretically on the problem of probabilistically modelling the timing behaviour, without discussing the mathematical means to derive pWCET estimates and the computing platforms on which PTA could be safely applied. About a decade later, that research area boomed, under the spin of a series of EU-funded projects and a constellation of industrial collaborations born around them. In the last few years, the number of works that address PTA in various guises has risen dramatically, making it difficult to discern the relation that they have with one another. In that vastness, several claims are made that seem to discord. Overall, the current landscape of research in that field has developed into a haphazard territory, ungainly for scientific investigators or industrial practitioners.

This section attempts to categorize all the PTA works known to date. Works with similar goals fall in the same category, although some works span multiple categories as they address several problems at once. Before drawing the taxonomy, we note that probabilistic *and* statistical reasoning take different roles in the application of PTA: probabilistic analysis reasons a-priori on the timing behaviour that the program will exhibit during operation; statistical analysis

Table 1: Terms and acronyms used throughout this paper.

| Term                 | Definition                             |  |  |  |  |

|----------------------|----------------------------------------|--|--|--|--|

| MBPTA                | Measurement-Based Timing Analysis      |  |  |  |  |

| PTA                  | MBPTA and SPTA                         |  |  |  |  |

| EVT                  | Extreme Value Theory                   |  |  |  |  |

| PoT                  | Peak Over Thresholds                   |  |  |  |  |

| $\operatorname{GEV}$ | Generalized Extreme Value Theory       |  |  |  |  |

| COTS                 | Commercial Off the Shelf               |  |  |  |  |

| SWRand               | COTS HW w/ Software Randomization      |  |  |  |  |

| ATD/ATS              | Analysis Time Distribution/Sample      |  |  |  |  |

| SPTA                 | Static Probabilistic Timing Analysis   |  |  |  |  |

| ETP                  | Execution-Time Profile                 |  |  |  |  |

| i.i.d.               | Independent and Identical Distribution |  |  |  |  |

| BM                   | Block Maxima                           |  |  |  |  |

| GPD                  | Generalized Pareto Distribution        |  |  |  |  |

| HWRand               | Time-randomized Hardware               |  |  |  |  |

| pWCET                | probabilistic WCET                     |  |  |  |  |

| OTD                  | Operation Time Distribution            |  |  |  |  |

is performed a-posteriori on a set of execution-time measurements to check whether the hypothesis made on the program's probabilistic timing behaviour cannot be rejected. The union of those techniques (applied either to SPTA or MBPTA) is collectively referred to as PTA. Table 1 lists the main terms and acronyms used in this paper.

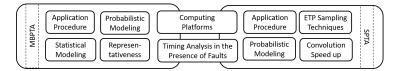

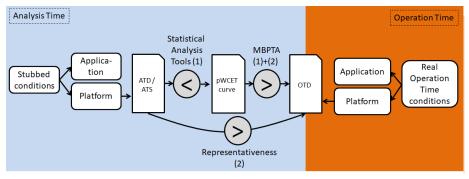

In this paper, we first classify the surveyed works according to whether they pertain to MBPTA or SPTA, and then to each of the related sub-problems. Subsequently, we single out further works of transversal interest. Figure 1 provides a pictorial representation of the proposed taxonomy.

Figure 1: The principal categories in our proposed taxonomy.

The MBPTA category, which we survey in Section 3, further breaks down as follows.

- *Probabilistic Modeling* (Section 3.2) seeks a-priori guarantees that the time-randomized resources used in the execution platform are apt to yield a timing behaviour that allows probabilistic reasoning.

- Statistical Modeling (Section 3.3) discusses how to ascertain the statistical properties of the execution-time distribution of programs obtained from its runs on the target platform. This represents the a-posteriori counterpart of probabilistic modeling.

- Application Procedure (Section 3.4). The works in this category present MBPTA as an orderly set of actions, and illustrate how to apply them.

• Representativeness (Section 4) aims at providing evidence that the executiontime observations captured for a given software unit during analysis are representative of the distribution of program's execution times during operation. To reflect their importance, we survey works in this category in Section 4, outside of Section 3's internal hierarchy.

The SPTA category, which we survey in Section 5, further breaks down as follows (as probabilistic modelling is intrinsic to SPTA, it is not covered as a separated subcategory).

- Application Procedure (Section 5.2). The works in this category present the SPTA application process in general and discuss software-related challenges with it, such as path coverage. This ambit includes the SPTA correspondent of *Probabilistic Modeling* assurance, to confirm that the execution platform offers sufficient randomization to allow probabilistic reasoning. To date, SPTA research has been shown able to meet this requirement only for processor architectures considerably simpler than those amenable to MBPTA.

- ETP Sampling Techniques (Section 5.3). SPTA applies the convolution operator on the ETPs of individual instructions to derive their combined ETP. The number of elements in ETPs increases exponentially with the convolutions performed. Works in this category limit the number of points per ETP while ensuring that the resulting estimates do upper-bound the original non-sampled ETPs.

- Convolution Speed-up (Section 5.3). The works in this category propose techniques to reduce the computation overhead entailed by the use of convolution operators.

Works of transverse concern to MBPTA and SPTA fall in the following categories.

- Computing Platforms (Section 6). The works in this group discuss the main requirements on the design of platform's hardware and software to which PTA can best apply.

- *Timing Analysis in the Presence of (Hardware) Faults* (Section 7). These works address the impact of faulty hardware on program's execution time, including its WCET.

Table 2 relates the categories in our PTA taxonomy and the HWR and, SWR And and COTS platform types (cf. Section 2.1) to the coverage of the corresponding topic in the state of the art.

Table 2: Coverage of the related work for each PTA taxonomy category and platform type (Legend:  $\checkmark$ : covered;  $\bigstar$ : not studied; (-): not relevant).

|          | MBPTA       |               |              |              | SPTA         |               |              |              | Analysis in  |

|----------|-------------|---------------|--------------|--------------|--------------|---------------|--------------|--------------|--------------|

|          | Application | Probabilistic | Statistic    | Represen-    | Application  | Probabilistic | ETP          | Convolution  | the Presence |

| Platform | Procedure   | Modelling     | Modelling    | tativeness   | Procedure    | Modelling     | Sampling     | Speed-up     | of Faults    |

| HWRand   | ~           | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| SWRand   | ~           | $\checkmark$  | $\checkmark$ | $\checkmark$ | ×            | ×             | ×            | ×            | -            |

| COTS     | ✓           | -             | $\checkmark$ | ×            | ×            | ×             | ×            | ×            | ~            |

#### 2.4 Probabilistic Analysis Beyond WCET Estimation

The notion of pWCET has been also explored at higher levels of abstraction, particularly for scheduling and response time analysis: the work by Burns et al. [24] is the main reference in this field. However, since our survey focuses on the use of PTA for pWCET estimation rather than on the use of the obtained pWCET estimates, e.g., for schedulability analysis, we only briefly touch upon the latter in this work.

The works on probabilistic scheduling consider tasks whose execution time follows a probabilistic distribution that can be characterized, without discussing how such a distribution is derived, which instead is of essence to PTA. Other works (e.g., [36], [72]) study system-level effects of scheduling, which have bearing on execution time and therefore on pWCET estimates, specifically the cache evictions that a task may suffer because of preemption. No other system-level effects have been studied so far in the context of PTA research.

To address the scheduling problem from the PTA perspective, it is *not* strictly necessary to create a probabilistic version of it. In fact, instead of exposing the whole pWCET distribution function to the scheduling or response time analysis algorithm, one can simply select a single-valued WCET estimate for each task, at a cut-off probability that meets the safety-case requirements of the system (e.g.,  $10^{-15}$  per execution), and use standard scheduling approaches with them.

# 3 MBPTA

#### 3.1 Introduction

Like any other measurement-based timing analysis method, MBPTA requires collecting execution time measurements as soon as possible in the system development life cycle, thereby avoiding the hazard of costly, late-stage regression determined by unsatisfactory analysis outcomes. Measurements are normally taken at the level of individual program units of variable granularity points in the system hierarchy, as soon as coded, after stubbing their externals. The challenge is to create analysis scenarios that, by virtue of configuration and execution procedure, expose the software program to the maximum extent of variability that may arise during operation, as a result of input received, unit state, and execution conditions (the latter including the contention incurred from co-runners on access to shared hardware resources).

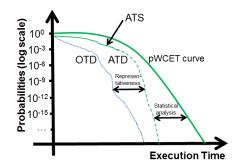

The elements to consider to that effect are referred to as sources of jitter (SoJ). The distinguishing trait of MBPTA is to use analysis-time observations to derive a probabilistic bound on the program's execution time that applies to its behaviour during operation. This ability requires attaining statistical control on the sources of jitter. Figure 2(a) illustrates this notion by contrasting the analysis-time distribution (ATD) of the program's execution time, as determined from very many observations, commensurate with the degree of assurance sought, with the operation-time distribution (OTD) that will begin to emerge after final system integration, too late to serve for WCET analysis. MBPTA aims at ensuring that an ATD, with the upper-bounding characteristics shown in Figure 2(a), can be constructed off a small number of selected observation

samples (ATS), and then used to derive a pWCET distribution function that upper-bounds the ATD.

(a) ATD, ATS, OTD and pWCET estimate.

(b) The space covered by MBPTA, inclusive of the representativeness and statistical concerns that are prerequisite to its application.

Figure 2: The basics of MBPTA.

The MBPTA problem overall can thus be decomposed into two parts:

- 1. To ensure that the ATD upper-bounds the OTD. This requires assuring that the analysis-time conditions are no better (for the emergence of the WCET) than those that can arise during operation. This problem is usually referred to as *representativeness*, to signify the preoccupation that the execution conditions incurred at analysis are representative of those that may occur at operation.

- 2. To soundly apply statistical methods so that an affordably small sample of the ATD (a proper choice of ATS) can be drawn to derive a pWCET estimate that does upper-bound the ATD (and thus the OTD).

In the literature, the MBPTA denomination has often been used indistinctly to address any application of statistical and probabilistic approaches to measurement-based timing analysis. This misclassification matches the statistical part of the MBPTA work flow as understood in this paper, but fails to capture the relevance of having a well-formed MBPTA process to guarantee a sound application of it. The latter is a crucial concern to the correct interpretation of MBPTA. Figure 2(b) provides a pictorial representation of the MBPTA proper process. Accordingly, this survey classifies current MBPTA works into three areas of concern:

- 1. Probabilistic and statistical modelling (Section 3.2 and Section 3.3 respectively), where we discuss the works that address the probabilistic and statistical perspective of the MBPTA process at the high level, without entering its concrete steps of execution;

- 2. MBPTA application procedure (Section 3.4), where we review the works that concentrate on procedural issues, focusing on particular stages of the MBPTA process;

- 3. Representativeness (Section 4), which considers the works that study how to ensure that the platform, for its hardware or software components and the execution conditions that they allow exploring, guarantees that the ATD upper-bounds the OTD. The works in this category either address the program structure (e.g. the coverage of the program's control-flow graph) or concentrate on the execution conditions determined by the processor hardware.

### 3.2 Probabilistic Modeling

To apply probabilistic reasoning to the timing of a software system soundly, the program execution time *must* have a probabilistically-characterizable behaviour. The prime means used by MBPTA research to that end, is to inject randomization in the program's timing behaviour. Different means to do so, however, fare very differently with respect to representativeness: we return to this issue specifically in Section 4. Probabilistic modelling therefore aims to assure that the approach followed to inject randomization adequately yields probabilistic timing behaviour.

MBPTA notably differs from SPTA in the way it addresses probabilistic modelling. As we shall see in Section 5, the latter requires deriving exact or upper-bounding probabilities for each time event that is randomized (e.g., a cache miss). The former may instead follow the design and implementation prescriptions in [70] to assure that the timing events that affect the program's execution-time behaviour have a random nature (and therefore allow probabilistic reasoning on them), so that it does *not* need to know or compute their actual probabilities, for they are bound to emerge through statistically-significant observations.

Overall, MBPTA's probabilistic modelling requires that randomization means are deployed to ensure that each execution time resulting from a program run has a probability of occurrence. MBPTA research has attempted to achieve this goal by randomizing the timing of individual components [70], by randomly sorting or picking from measurements [51, 81], by adding random padding to observed measurement values [78]. Not all randomization means however are equally capable of providing sufficient representativeness guarantees: the user shall therefore thoroughly understand the implications of randomization means on representativeness.

#### 3.3 Statistical Modeling

Broadly speaking, when statistical reasoning enters timing analysis approaches, execution-time observations are sampled according to given criteria, and then used to fit some probability distribution, which yields the pWCET estimation.

To the best of our knowledge, the vast majority of works in this area have used Extreme Value Theory (EVT), paralleling the worst-case execution-time behaviour of a program to an extreme-value probability distribution. A residual fraction of works have explored other theories such as Copulas [22] or Markov models [39, 110]. Owing to this dominance, this section concentrates on EVT and its use for the pWCET estimation problem. It is worth noting that, while MBPTA is *not* intrinsically restricted to yielding continuous distributions, the use of EVT naturally implies delivering them. Conversely, SPTA, albeit not necessarily limited to discrete distributions, often builds on discrete representations of the execution times and their individual probabilities.

#### 3.3.1 Basics on EVT

EVT is a well-established branch of statistics that models the probability of occurrence of extreme events (whether maxima or minima) in a given distribution. EVT has been traditionally applied to meteorological, hydrological, insurance and financial problems [37, 5, 45], to predict extreme behaviour or expectations, such as exceedance probability or return periods.

EVT builds on the Fisher-Tippett-Gnedenko [49] and Pickands-BalkemadeHaan [97] theorems, which stipulate that the asymptotic tail distribution of a sample of independent and identically distributed (i.i.d.) random variables converges to specific families of distributions, known as Generalised Extreme Value (GEV) and Generalized Pareto Distribution (GPD).

To model the tail (hence the extreme) probability distribution, EVT singles out the tail values in the input sample of observations. To select those elements from the sample population and fit them to a (parametric) extreme distribution, EVT uses one of two methods, namely Block Maxima (BM) or Peak over Threshold (PoT), briefly reviewed below. Goodness-of-fit tests or other statistical diagnostic tools eventually determine how well the obtained distribution models the population.

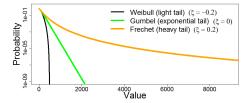

**Block Maxima (BM)** BM filters out non-tail values by splitting the sample into smaller blocks of a given size, and then retaining only the maximum value in each block. EVT then attempts to fit the resulting set of values within the GEV family of distributions, whose parametric form is shown in Equation 1 [32, 73] (where  $1 + \xi \left(\frac{x-\mu}{\sigma}\right) > 0$  must hold), which resolves into a Gumbel, Reversed Weibull, or Fréchet distribution. The parameters  $\mu$ ,  $\sigma$  and  $\xi$  are known as the *location, scale* and *shape* respectively. The shape  $\xi$  determines whether the resulting distribution is a Weibull (aka light or short-tailed), when  $\xi < 0$ , or Gumbel (aka exponential or light-tailed), when  $\xi = 0$ , or Fréchet (aka heavytailed), when  $\xi > 0$ .

$$G(x;\mu,\sigma,\xi) = \begin{cases} exp\left[-\left(1+\xi\frac{x-\mu}{\sigma}\right)^{-1/\xi}\right] & \xi \neq 0\\ exp\left[-exp\left(-\frac{x-\mu}{\sigma}\right)\right] & \xi = 0 \end{cases}$$

(1)

Figure 3: Complementary cumulative distribution function for light, exponential and heavy tail GEV distributions, with  $\xi = -0.2$ ,  $\xi = 0$  and  $\xi = 0.2$  respectively, and ( $\mu = 0$ ,  $\sigma = 100$ ) for all of them.

Figure 3 illustrates example tail shapes: a Weibull distribution with  $\xi = -0.2$ , which has a steep slope and converges to a maximum value (500 in the example, not shown in the plot); a Gumbel distribution with  $\xi = 0$ , which yields a relatively short-tailed slope that however remains asymptotic (outside of the plot); and a Fréchet distribution with  $\xi = 0.2$ , which decreases polynomially.

**Peak-over-Threshold (PoT)** PoT filters out non-tail values by retaining only the observations that exceed a given threshold. EVT then attempts to fit the resulting set of values within the GPD family of distributions, Gumbel, Reversed Weibull, or Pareto, whose parametric form is shown in Equation 2, where the parameters  $\mu$ ,  $\sigma$  and  $\xi$  have a similar meaning as in the GEV formulation (in fact,  $\xi$  is identical), and  $x > \mu$ . The GPD distribution admits also a two-parameter formulation.

$$H(x;\mu,\sigma,\xi) = \begin{cases} 1 - \left[1 + \xi\left(\frac{x-\mu}{\sigma}\right)\right]^{-1/\xi} & \xi \neq 0\\ 1 - \exp\left(-\frac{x-\mu}{\sigma}\right) & \xi = 0 \end{cases}$$

(2)

[32] notes that a strong correlation exists between GEV and GPD: for the same  $\xi$  and similar values for  $\mu$  and  $\sigma$ , GPD and GEV result in the same distribution.

#### 3.3.2 Modeling Extreme Timing Behaviour with EVT

In spite of the remoteness of its original domains of application to the timing analysis problem, EVT has emerged as an apt tool to derive trustworthy pWCET estimates. Numerous studies and considerable effort have contributed to yielding a sound adaptation of it. From the statistical modelling perspective, among the steps that precede the application of EVT, the state of the art literature distinguishes (1) the approach used for the derivation of GEV/GPD parameters, (2) the filtering of tail values from the sample, and (3) the evaluation of the quality of fit.

Edgar and Burns first proposed using EVT – the Gumbel distribution in particular – for pWCET estimation [44]. Their work uses a notion of threshold, referred to as "confidence level", to determine which distribution to use. With that, they fit the full sample of measurement observations to the given Gumbel distribution (without using BM or PoT) to ascertain that the accumulated execution time of individual tasks (assumed to be independent) does not

exceed its pWCET distribution at that confidence level. The authors of [55] apply BM instead, and fit a Gumbel distribution to the resulting selection, using Chi-squared tests [96] to assess its goodness. The soundness of the resulting pWCET estimate is then assessed against a very large sample of measurement observations. [103] compares the use of BM and PoT, also studying their sensitivity to the input parameters. Griffin et al. [51] explain that modelling discrete processes (execution times measured in clock cycles) with continuous distributions such as Gumbel's may lead to pessimistic pWCET estimates. The cited authors also illustrate the difficulties of preserving the i.i.d. properties required for the application of EVT<sup>1</sup>, and propose guidelines to mitigate the corresponding risks and derive reliable pWCET estimates. Lima and Bate [78] elaborate further on the problem posed by the use of discrete data, which may impede a proper use of EVT, and suggest adding random padding to the executiontime measurements to circumvent that problem and apply EVT soundly. Yue et al. [81] address the lack of independence in the data set, by proposing an alternative data collection method. They propose retaining only the highest values from potentially-dependent execution-time measurements, repeating this process until a sufficient number of maxima are obtained that can be shown independent, so that EVT can be reliably applied to them. The same authors also suggest computing multiple pWCET estimates (with repeated applications of the proposed method) and the corresponding confidence interval, so that a given pWCET estimate at the chosen confidence level can be selected. Lima et al. [79] analyze scenarios where the whole GEV family of distributions can be applied: those where the input data come from multiple distributions (i.e., from input values that may cause execution to traverse different program paths), as well as computing platforms with or without time randomization. In order to create a source of randomness and thus obtain sufficient variability in the measurements, the authors apply random sampling across observations. This particular work does not discuss the representativeness of the studied scenarios with respect to the execution conditions expected at operation.

Abella et al. [7] employ the Coefficient of Variation method (CV) [38] to determine all GPD parameters except the shape, and compute the best (presumed) exponential distribution that fits the data, after confirming that the exponentiality assumption cannot be statistically rejected. The CV method differs from that in [34], which selects the parameters that best fit the data regardless of the distribution family, before choosing a shape parameter that matches an exponential distribution.

Statistical Requirements for Data Samples A fundamental statistical requirement in the original formulation of EVT is that the observations need to be independent and identically distributed (i.i.d.) [49, 55, 51]. For the purposes of pWCET estimation, satisfying the independence requirement may be impaired by data collection practices or even inherent effects of the execution platform: [22] studies the effect of dependencies across execution-time measurements of program components. In fact, it has been shown that EVT can be used to analyse stationary processes, where dependence exists across variables, but only as long as the dependencies are managed conveniently to warrant the

$<sup>^1\</sup>mathrm{This}$  work does not consider stationary processes where some degree of dependence can be tolerated.

reliability of the resulting distribution [32, 73]. Santinelli et al. [103] analyze the impact of stationary processes in pWCET estimation, and conclude that dependencies across execution-time measurements may cause pWCET underestimation. Along the same line, Melani et al. [85] single out the individual factors that may lead to dependencies, such as cache state modifications across runs and scheduling policies. That work concludes that, while those factors cause significant dependencies across measurement observations, they can be accounted for in the use of EVT via appropriate independence and correlation tests. The cited authors also suggest that when those factors combine with some random phenomena (such as, e.g., random choice of program input), the dependencies become less important. As noted earlier, [78] shows that adding a random padding to the measured values also decreases dependencies across them. Whilst this may allow preserving the base EVT assumption of i.i.d. random variables, it remains to be proven constructively whether using data padding to model a dependent process as an i.i.d. process does always lead to reliable pWCET estimates.

#### 3.3.3 Other Statistical Approaches

Although preponderant, EVT is not the only statistical and probabilistic technique that has been used with MBTA. Bernat et al. in [22] propose a hybrid MBTA method where empirical execution-time profiles are gathered from observations taken at the level of the program's basic blocks, and then combined together to determine an end-to-end pWCET distribution. While this work predicates on the notion of pWCET distribution, it applies no predictive model to determine it: the pWCET distribution is derived by conservatively combining the execution-time profiles associated to the program's basic blocks over its control-flow graph. In this respect, this work is much closer in concept to SPTA than to MBPTA.

In a similar vein, [110] addresses the problem of determining the execution time of soft real-time systems, where probabilistic deadlines are defined, which can be missed with a given probability. The cited work focuses on application scenarios common to the robotics/image-recognition field, where the computation time depends on the complexity of the current real-world situation. In this case, the i.i.d. property does not hold. To overcome this shortcoming, the authors propose to model the timing behaviour using a hidden Markov model to represent different execution modes (associated to states in the Markov model) and valid transitions across them. In that manner, the authors infer states and transitions directly from sequences of execution-time observations, thus modelling residual dependencies accurately. At that point, the execution-time distribution for each state can be described with an independent random variable.

# 3.4 MBPTA Application Procedure

The EVT-based element of MBPTA requires its application procedure to proceed across four distinct steps, possibly iterated multiple times, while always paying attention to representativeness (which we discuss separately in Section 4).

1. Statistical verification: where the set of collected observations are checked

against the prerequisites for the application of EVT (i.e., i.i.d. and stationarity);

- 2. *Data filtering*: the data set is filtered (with either BM or PoT) to retain only the values that belong to the tail of the execution-time distribution of the program of interest;

- 3. *Parameter selection*: where a specific distribution family is selected, along with the set of parameters that correspond to either the GEV or GPD equations;

- 4. *Distribution fitting*: where the pWCET curve that arises from the above parameter choice is fitted against the data sample.

The MBPTA approaches in the state of the art differ in the specific assumptions that they make and the technique that they use to perform those steps.

A first attempt to establishing a solid and repeatable EVT-based MBPTA application procedure for multi-path programs appeared in [26, 34]. The former work [26] provides a high-level discussion of those requirements; the latter [34] presents a procedural description of the proposed application procedure. Those works build on HWR and platform with explicit enforcement of the worst-case initial state before each measurement to meet the i.i.d. statistical requirements of EVT, while also assuring representativeness; BM is used to sample the collected observations and then the best-fit *location*, *scale* and *shape* GEV parameters are estimated. At that point, the shape parameter is tested against the exponential hypothesis with the Exponential Test (ET) [41]. If passed (when  $\xi \approx 0$ ,  $\xi$  is forced to 0, to match a Gumbel distribution. The cited authors postulate that a *minimum number of observations* [34] can be incrementally determined by checking that the pWCET curve becomes *stable* (that is, it does not change significantly when feeding further observations to the procedure). The Continuous Ranked Probability Score (CRPS) [46] is used to determine the closeness of the distributions obtained at each round of application. The proposed method is then applied to multi-path programs assuming the user is responsible for providing the input data that cause the traversal of all the program paths of interest to the pWCET computation. All those paths are then jointly and indistinctly assumed to contribute to the sought distribution.

For both HWR and and SWR and platforms, the authors of [7] present an MBPTA approach that uses the Coefficient of Variation (MBPTA-CV), already outlined in Section 3.3.2. The authors postulate that the exponential tail can be always used to model the pWCET, backing their claim with the time-bounded nature of real-time programs of interest to WCET analysis, the characteristics of the execution platform, and the granularity level (per path) at which EVT is applied. In contrast with [34], MBPTA-CV uses PoT instead of BM, thus achieving reproducibility (i.e., yielding the same output when applied to the same data). As a further point of difference, MBPTA-CV fits the best exponential tail to the data, instead of fitting the best GEV distribution and then forcing  $\xi = 0$ , which may not be the best exponential fit for the data.

[53] defines a framework for the application of EVT, to ascertain the applicability of EVT to execution COTS platforms that do not employ randomization. [102] follows suit, using PoT (hence GPD) and proposing that an array of statistical tests should be passed with a given confidence level to guarantee a *statistically reliable* application of EVT. The same confidence levels are subsequently used to sustain the *reliability* of the results, in contrast with [34, 7], which assess the quality of the pWCET distribution indirectly, as part of the parameter selection step.

[21] uses EVT to analyze the timing behaviour of highly-parallel applications running on GPGPU. The MBPTA application procedure in the cited work broadly aligns with [34, 26] except that the authors' interest is more centered on the assessment of the EVT statistical requirements, owing to the looser independence conditions of their problem.

Lesage et al. [76] present an evaluation framework to assess the reliability of MBTA. The proposed approach combines timing data with compiler-generated structural information, to guide the construction of synthetic path traversals (random walks) that can be used to test the robustness of the analysis approach, especially when different coverage conditions are met. The authors' framework is then instantiated to the MBPTA context, using a maximum envelope<sup>2</sup> to compute a single pWCET distribution out of observations from multiple program paths. Experimental results confirm that the quality of the results is highly dependent on the attained path coverage.

#### 3.5 Summary

Existing MBPTA approaches prevalently base on EVT and all share similar procedural steps. Individual approaches differ in the assumptions that they rest on and in the statistical tools that they use. At the outermost level, the research proposals divide between those that prescribe the use of randomization in the execution platforms [34, 7] and those that assume unmodified (time-deterministic) platforms [21, 53]. Experimental evidence shows that randomized execution platforms facilitate meeting the statistical prerequisites of EVT. When the alternative approach is pursued, the method used to collect the measurements must be studied with care (cf. Section 4).

The use of BM or PoT appears to be equally valid, when used within sound methods.

Predefined governing assumptions on the timing distribution of the target program generally guide the (GEV or GPD) parameter selection, with the Gumbel (GEV) or Exponential (GPD) distribution being normally regarded as the most appropriate choice for the problem domain [44, 34, 7].

No universal consensus exists to date on how to assess the quality of the pWCET distribution derived with EVT. Some works [53, 102] use the confidence levels obtained from the assessment of statistical prerequisites, to indirectly evaluate the quality of the EVT results, which however postulates a strong correlation between prerequisites and results. The quality of the model is typically ascribed to the goodness of the parameter selection [34, 7], where a more accurate selection is bound to yield better results. Other approaches [79] suggest the adoption of standard statistical diagnostic tools, such as the Quantile-to-Quantile [28] or the Mean-Excess plots [20]. Both solutions are complementary and not really alternative. And yet, any claim on the soundness of the MBPTA

$<sup>^2{\</sup>rm A}$  maximum envelope of a set of distributions stands for the distribution that, for each exceedance probability in a set of input distributions, takes the maximum pWCET value across them.

results (over and above the use of EVT) must address the representativeness concern.

# 4 Representativeness

#### 4.1 Introduction

For all measurement-based analysis techniques, the concern of representativeness regards the ability to assure that the execution conditions encountered when collecting the observations correlate significantly with those that can occur during operation. The umbrella term "execution conditions" refers to all the factors that may affect the timing behaviour of a program when run on a given processor platform, including for example its memory layout (which determines cache mapping and may thus have large impact on the cache behaviour) and the parallel contention load on shared hardware resources in multicores.

The representativeness concern is external to EVT, as EVT treats the system of interest as a black box, without considering the system's internals when the observations are taken. Thus, the EVT projections only hold for the "world" as seen during the analysis. Whereas the events observed at different moments of the same analysis (i.e., in different runs of the same program) may contribute to one combined probability distribution, EVT has nothing to say on unobserved events.

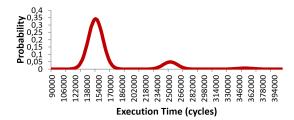

Figure 4: An exemplary Probability Distribution Function of the execution time of a program.

This notion is better understood with Figure 4, which portrays for illustration purposes the *real* (hence conceptual) probability distribution function (PDF) of the execution time that a program can take. An artifact of this kind cannot be obtained in the general case as only a (small) sample of the corresponding observations can really be taken with finite effort, so that an empirical PDF is obtained instead. The PDF presents three peaks with decreasing densities, at 150k, 250k and 355k cycles, respectively. Each such peak is caused by a particular set of (not necessarily disjoint) execution conditions. Assume that the execution conditions that trigger the right-most peak would *not* occur in the analysis sample. In that event, EVT is unable to capture the right-most peak in the tail (which, without seeing sufficient elements of it, could be located arbitrarily far to the right of the abscissa). Applied to this example, the representativeness concern reduces to the need to assure that the analysis observations capture all the execution conditions of interest to pWCET analysis, so that EVT can factor all due peaks in its predictions. While representativeness is acknowledged as a critical issue for EVT predictions [32], a number of works either assume it to be given or outside of scope, or conjecture the execution conditions incurred in the input sample collection *do* suffice for pWCET estimation [44, 55, 51, 81, 103, 79, 78]. [25] notes however that the user may often be unable to control the low-level hardware features that have bearing on representativeness.

Arguably, representativeness plays a key role in the pWCET estimation process. Platform characteristics and means to account for different program paths may lead to obtaining either a single execution-time sample (hence a single execution-time distribution) or multiple ones. In the latter case, different approaches have been followed to obtain a single pWCET estimate (that is, a single execution-time distribution) from the multiple distributions sampled.

# 4.2 Program-Structure Representativeness or Path Analysis

The variable set of program paths that observation runs may traverse is one of the main sources of jitter in the program's execution-time behaviour, which impends on the representativeness concern. Several probabilistic approaches have been proposed to address that challenge.

#### 4.2.1 Applying EVT or Other Statistical Means to Multiple Program Paths

To use MBPTA for multi-path programs, one needs to determine how (i) to apply EVT to those program paths; and (ii) to guarantee that the obtained pWCET results are valid for all the possible path traversals that may occur during the nominal operation of the analysed program.

As we noted in Section 3.3.3, [22] collects execution-time measurements for small program units (basic blocks or functions) that correspond to different execution paths, and uses their frequency of observation to construct an executiontime profile (ETP) for each such structural unit. At that point, the cited work uses appropriate mathematical operators to combine the individual ETPs into a pWCET for the whole program, in a manner that upper-bounds the execution time of any single end-to-end path traversal. The authors use convolutions to combine the ETPs of independent program units and define an extended form of *joint convolution* for units that are known to have dependencies or, conservatively, where dependences cannot be excluded.

Other authors [79, 34] propose merging the execution-time measurements taken across multiple program paths into a single bucket, which is then passed in input to EVT. [102] shows that proceeding in that way does not work in all cases. Milutinovic et al. [91] discuss the risk of the single-bucket approach, which causes the pWCET to reflect the path traversal frequency as occurred during analysis, which the user may have great difficulty at correlating with the operational behaviour of the program. Authors further show that, when using Gumbel distributions, the single-bucket approach may lead to pWCET estimates that either are optimistic (i.e. not upper-bounding) for some, possibly all, individual program paths or exceed all of them, thus incurring unwanted pessimism. [91] recommends the multiple-bucket approach, instead, where each execution path is analysed separately, and a joint pWCET estimate (known as the *maximum*  *envelope*) is obtained as the pWCET profile that upper-bounds the distributions computed for all individual traversed path, and for each exceedance probability of interest. The multiple-bucket method can be adopted by all approaches in the state of the art that originally apply the single-bucket method ([34, 79, 102]).

[7] follows the multiple-bucket approach and pays special attention to the curve fitting step of the MBPTA application procedure. The authors maintain that the Exponential distribution (GPD) or Gumbel distribution (GEV) are always a safe choice for modelling the worst-case execution-time behaviour of a real-time software program, and propose an analysis procedure to be applied on a per-path basis. The authors' method seeks representativeness with a combination of upper-bounding precautions and time randomization in the execution platform.

#### 4.2.2 Assuring MBPTA Results for All Program Paths

This problem is inherent to all measurement-based analysis approaches, which can only speculate on the observations made during the analysis and therefore produce results that are only valid as long as those observations are representative of the worst-case execution conditions (including worst-case path traversal). Curing this problem by requiring the user to achieve full path coverage in the analysis observations is not a tenable option in the general case. This problem, generally referred to as *path-representativeness*, is bypassed in [34] by predicating on the user's ability to discern the *relevant* paths in a program. This assumption however can hardly be generalized. Other works [82, 79] suggest making random picks across all possible input data to the program, to select a random subset of program paths and associated execution conditions. This method however offers no absolute guarantees of coverage.

A number of methods propose to synthetically extend the degree of pathrepresentativeness that the user-provided input data can attain in the general case [66, 114], so that the pWCET distribution obtained with MBPTA is trustworthy, even when the path traversals made during the analysis cannot be guaranteed to have included the worst-case path. [66] presents the Path Upper Bounding (PUB) technique to artificially balance the branches of all individual conditional control flow constructs in the program so that any branch is a safe upper-bound for all the other branches in the same construct. Balancing is obtained with an extended binary version of the target program (used at analysis time only), where additional core and cache access instructions are inserted as needed on the individual branches of the conditional construct. The executiontime measurements collected for the extended version of the program thus are by construction an upper bound to all possible path traversals in the original program, which is the one that is eventually deployed at operation. The degree of over-estimation incurred by balancing depends on the particular structure of the program under analysis. The main drawback of PUB is that it needs a qualified compiler to generate a semantically-preserving extended version of the original program. Indeed, those compiler transformations may be overly difficult for complex programs, for example those that use "goto" or breaks in loops.

With a similar intent, Ziccardi et al. [114] propose the Extended Path Coverage (EPC) technique, a fully automated approach to artificially extend the set of measurements to achieve the same effect of full path coverage. EPC relies on the concept of *probabilistic path independence* to generate a set of *synthetic* observations that complement the set of measurements actually collected. EPC operates at the level of basic blocks whose execution-time observations are synthetically made independent from any specific path in the program, so that they can be used as building blocks to derive end-to-end measurements for unobserved paths. Feeding EVT with the union of measurements from observed and unobserved path traversals achieves the same effect as full-path coverage, without any additional burden on the user. EPC requires that the original observations assure basic-block coverage: this is a realistic requirement in some application domains, certainly lighter than its full coverage alternative.

Both PUB and EPC have been developed for HWR and platforms, but in principle they might be adapted to SWR and platforms too. Instead, their direct use for time-deterministic platforms would either fail or deliver too pessimistic results (e.g. assuming that almost all cache accesses are misses).

### 4.3 Platform-Related Representativeness

The use of complex processors induces hardware-related sources of jitter that need to be accounted for in any claim of representativeness. The MBPTA research in this regard follows two trails: one that addresses time-deterministic platforms, which embed no MBPTA enabler underneath the application; the other that studies how time randomization, transparently implemented in hardware or software or both, helps meet the MBPTA application requirements.

#### 4.3.1 Time-deterministic Platforms

A reliable application of EVT for pWCET estimation requires the user to accurately understand the population of hardware events that may occur during operation [25] and determine whether and how far analysis-time observations can trigger them. Admittedly however, enumerating all sources and all combinations of execution conditions with impact on the program's execution-time behaviour is an intractable problem in the general case. Moreover, the cost and complexity of constructing an input data set that triggers each and every such event is out of reach for most users. In fact, to the best of our knowledge, no work exists to date that solves this problem in a sufficiently general manner.

In [82] authors propose random sampling across program's input values as a means to explore different execution conditions. This approach, however, does not allow drawing solid conclusions on the coverage achieved. Interestingly, an approach of this kind may indeed produce data samples capable of passing i.i.d. tests (except for programs with low variability in execution-time behaviour), and thus lead to mechanically successful applications of EVT but that are *unfit* for pWCET computation, owing to fundamental deficiencies in representativeness.

[83] studies measurement protocols in general, that is, abstract procedures to follow for collecting execution-time measurements, without adapting them to any specific platform. This work suggests that a measurement protocol *converges* when, as more measurements are added to the analysis sample, the closer the resulting pWCET estimate gets to the pWCET that would have been obtained using (ideally) the whole population of execution times. A measurement protocol achieves representativeness if there exists a number k of execution-time observations that allows obtaining a pWCET close enough to the actual (ideal) WCET. Notably, [83] offers only a qualitative argument to support the claim of convergence, which has not been sustained with quantitative evidence.

#### 4.3.2 Time-randomized Platforms

Several works present hardware designs that aim to help achieve representativeness. All those proposals explore ways to control the jitter of certain processor resources. We briefly survey each of them in isolation, noting however that they can be combined opportunistically in accord with the characteristics of the platform and the needs of the application.

**Probabilistic Upper-bounding** Time-randomized processor architectures aim at helping the user achieve representativeness with less effort [70]. This approach attacks the hardware sources of jitter with high-enough impact to justify design change. When the events that they generate become random, then the user problem reduces to assuring that the quantity of observations made is sufficiently large for the whole spectrum of variation to manifest itself. To put it simply, for a random source of jitter with probability of appearance of  $\mathcal{P}_e = 0.1$  per use, the probability of *not* observing it in R = 1,000 single-use runs is  $\mathcal{P}_{no} = (1 - P_e)^R = (1 - 0.1)^{1000} \approx 4.3 \times 10^{-5}$  The domain regulations will then determine whether such a probabilistic assurance level is sufficient.

**Deterministic Upper-bounding** Processor resources whose jitter is low enough to not justify time randomization but not insignificant for the analysis, are modified to allow the user to set them to respond with their worst-case latency during analysis [70]. In that manner, the jitterless timing behaviour of those resources during analysis is assured to upper-bound their jittery behaviour during operation. A typifying example of these resources is the floating point unit (FPU), some of whose operations may take a variable response time depending on the operands. It would be unthinkable for the user to study the probability distribution of operands during operation and to figure how to reproduce it during analysis. The ability to force the FPU to always respond with worst-case jitter per operation type during analysis relieves the user from that burden. An approach of this kind has been used also to study contention effects with hardware shared resources [95][12].

**Padding** An alternative to touching the hardware design is to artificially enlarge the collected execution time values before passing them to EVT [40]. The increment factor is designed, on per processor resource basis, to capture the maximum time overhead that such resource might cause in the observed use. This approach was used in [40] to upper-bound the impact of contention on access to hardware shared resources in a multicore. Unlike deterministic upperbounding, this technique is pessimistic in that the padding may yield jitter costs higher than the absolute maximum.

#### 4.3.3 Cache-centric Solutions

[8] shows that, with time-randomized hardware, all high-impact sources of jitter, except for cache placement, can be observed sufficiently well to apply EVT to them. This is not surprising as caches are one of the processor resources with the highest impact on the program's WCET. As such, the quest for determining the worst-case behaviour of caches has attracted the attention of the WCET research community [56].

For set-associative caches, the de-facto standard in real processors, the events of interest to EVT originate when the number of program's code or data objects mapped to the same set exceeds the set capacity (the number of ways) [8]. In fact, this scenario may cause an abrupt increase in the miss ratio, and a correspondingly large inflation in the program's execution time. If events of this kind can happen with a non-negligible probability during operation, they have to be captured at least once in the observation runs performed during analysis, in order for EVT to account for them [8].

The role of caches in the representativeness problem is discussed in [101] and [88]. [68] and [69] study how that problem changes when the caches use random placement or modulo placement combined with software randomization techniques.

Hardware Randomized Caches In non-parametric random placement caches [104, 109, 23], placement considers only the address of the memory request. As a result, a given memory layout determines a single cache placement, much like with conventional deterministic caches based on modulo placement. The former and the latter therefore have the same limitation with respect to representativeness: they are exposed to highly unlikely but extremely heavy pathological cases.

Time-randomized caches [64, 65, 59], on the other hand, feature parametric placement functions, which allocate data in cache lines based on a combination of the request address and an arbitrary random number. By changing the random parameter across runs, those designs yield a different cache placement for each execution, which allows addressing the representativeness problem by sampling observations across distinct program runs.

[8] shows that, for hash random-placement caches with S sets, it is possible to determine whether at least W + 1 program objects out of the total K under consideration are mapped to the same cache set, by considering all potential mappings of the K objects to the S cache sets and the fraction of those mappings where at least one cache set has W + 1 objects allocated to it. The result of this operation can be approximated with weak compositions. A weak composition of an integer n is a way of writing it as the sum of a sequence of non-negative integers. The cited work studies all the weak compositions of K made of exactly S parts, where at least one part is higher than W. From this analysis, the cited work derives the probability of the cache event of interest,  $P_{ce}$ , and the probability of not observing it in R observation runs,  $\mathcal{P}_{no} = (1 - P_{ce})^R$ . One proposed solution then consists in increasing R until  $P_{no}$  becomes small enough to be acceptably ignored. One other solution is to repeat the analysis with a cache with a smaller number of sets, to increase the probability of occurrence of the cache event of interest to the point of capturing it with higher probability with R observation runs.

[19] presents an alternative to weak compositions using the multinomial coefficient that derives exact results instead of approximations. To mitigate the non-negligible computational costs of using the multinomial coefficient, the cited work proposes Monte Carlo simulations to approximate the probability of the event of interest, with a given precision.

[90] notes that the previous solutions assume that the impact of all addresses on execution time is similar. For instance, given three addresses, A, B, and C, which access a direct-mapped cache, those techniques assume that mapping Aand B, A and C, or B and C to the same set has the same impact on the program's execution time. This might be so when the addresses are accessed homogeneously. Yet, in the general case, not every combination of addresses - when mapped to the same set - results in an execution-time increase of the same magnitude. To address this challenge, the cited work proposes ReVS, a computationally-intensive method to compute exactly the probability and impact that each cache allocation can have on execution time. For sets with Wways, the proposed solution takes in input the sequence of accessed addresses of the program and builds all combinations of W + m addresses (with  $m \ge 1$ ) out of the K addresses in the program. The impact that each such combination can have on the miss count is determined with a cache simulator, whereas their probability is derived analytically. With this analysis, the user can assess whether R observation runs are sufficient to capture the cache allocations with low-probability and high-impact. Otherwise, more runs are needed until the condition is satisfied.

[89] presents a less effort-intensive variant of that solution. Instead of running simulations in the cache simulator for all combinations of W + m or more addresses, it uses a quantitative metric to single out the combinations of W + mthat may have high enough impact.

**Software Randomized Caches** [18] studies the difference between software and hardware randomized caches, for programs with homogeneously accessed objects. The authors show that, for hardware randomized caches, the probability  $\mathcal{P}_S$  of an object to be assigned to a given set for S sets is 1/S. With software randomized caches, dependencies exist among the sets allocated to a given object and those that can be assigned to another. Accordingly, the probability of allocating an object to a given set reduces as more objects are already allocated to it. This dependency causes the probability of the cache events of interest to differ for software-randomized caches from their hardware counterpart.

#### 4.4 Summary

Representativeness is a key concern for all measurement-based timing analysis approaches. Its problem space spans the Cartesian product of all distinct sources of jitter of interest, both high-level, such as program paths, and lowlevel, such as stateful processor resources. The MBPTA results are valid only as long as the execution conditions experienced during analysis are (conservatively) representative of those that may occur during operation.

The quest for sufficient path coverage in the analysis encompasses two contrasting trends. Some authors [66, 114] seek to achieve full path coverage synthetically, adding structural program knowledge to the postulate that the user-provided input data to the program assure basic block coverage. Other authors [82, 79] prefer to soften the requirements and propose sampling randomly from the input data space. While attractive from the user perspective [79, 78], solutions of the latter kind have fundamental weaknesses: they cannot yield solid (upper-bounding) correlation between the program paths traversed in the observation runs and the unseen ones; furthermore, owing to the black-box nature of EVT, they may produce results that are either unreliable or overly pessimistic [91, 102].

The same problem, only grander, presents itself for the processor resources, in the need to assure that the effects of the execution conditions incurred in the observation runs upper-bound those that may occur during operation. Expecting the user to achieve full control of the low-level factors of interest is evidently untenable, and, again, random sampling from the program's input space as proposed in [82] offers only a manner to possibly incur enough variability to satisfy EVT mechanically, but not to warrant a reliable solution for MBPTA. Low-cost hardware modifications, transparent to the application, have been studied extensively to help building arguments of representativeness [8, 90, 89]. To become more industrially viable they have to be extended to COTS processors, which is still work in progress to date.

# 5 SPTA

# 5.1 Introduction

Probabilistic reasoning has also entered the world of static timing analysis, which builds a-priori models of worst-case behaviour. [35] is an early instance of that union, which does not require any form of platform randomization, thus falling into the category of classic static timing analysis. The cited work assumes that probabilities of occurrence can be attached to the outcomes of the conditional branches in a program. By propagating that information along the abstract syntax tree of the program, and assuming that the WCET cost of individual program units be statically known, the authors compute a-priori traversal frequencies for individual runs and consequently for execution-time values.

Conversely, the static analysis techniques that assume (require) some degree of platform randomization fall under the umbrella of Static Probabilistic Timing Analysis (SPTA), which aims to yield probability distributions for the program's execution time. The presence of a randomized cache is the fundamental assumption at the basis of SPTA research and the fundamental enabler to its state of the art solutions. In randomized caches, a random eviction occurs in response to either a cache access (*evict-on-access*) [26] or a cache miss (*evict-on-miss*) [64].

SPTA solutions construct execution-time profiles (ETPs), that is, discrete representations of the *probability mass function* of the time cost of program units, which were considered for the first time in [22]. ETPs can be defined at various levels of abstraction and granularity of program execution, from individual processor instructions in the program binary (*static* view) or their executed instance (*dynamic* view, which carries contextual information akin to *loop unrolling* and *call-context* in classic static timing analysis [112]), to groups thereof. ETPs for static instructions provide a safe over-approximation over all possible executions. ETPs for dynamic instructions, instead, allow constructing a tighter bound to the actual timing behaviour. Representing the timing behaviour of single instructions as an ETP requires a precise micro-architectural model of the execution platform, a common need to static timing analysis [112]. Whether explicitly or implicitly, all current SPTA solutions work at the level of static instructions, which is deemed more robust against the lack of precise timing information, and thus less demanding to the user. Unless explicitly stated, therefore, we assume this choice by default in the sequel.

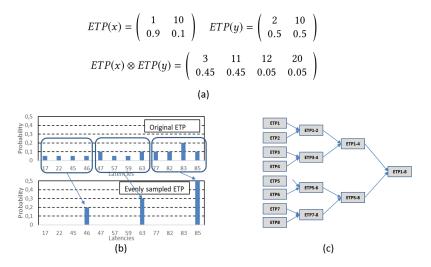

For a given (static) instruction x, the ETP describes the latencies  $\{et_{x_i}\}$  that its execution can incur, and the associated probabilities  $\{\mathcal{P}_{x_i}\}$  of occurrence. Accordingly, the ETP for instruction x can be defined as follows:

$$ETP(x) = \begin{pmatrix} et_{x_1} & et_{x_2} & \cdots & et_{x_n} \\ \mathcal{P}_{x_1} & \mathcal{P}_{x_2} & \cdots & \mathcal{P}_{x_n} \end{pmatrix}, \sum_{i=1}^n \mathcal{P}_{x_i} = 1$$

SPTA postulates that the ETPs of individual instructions can be composed to build up the ETP of any sequence of instructions up to the entire program. The *independence* of the ETPs of individual instructions in a sequence is guaranteed by either making assumptions on guarantees offered by the underlying hardware platform [26] or explicitly removing potential dependencies in the modelling of individual ETPs (e.g., by considering lower bounds to the probability of hitting in cache). On the assumption of independence, SPTA computes the ETP of an instruction sequence by applying *discrete convolution* ( $\otimes$ ) to their individual ETPs. More formally, let  $\mathcal{X}$  and  $\mathcal{Y}$  denote the random variables that describe the execution time of instructions x and y respectively. Their convolution  $\mathcal{Z} = \mathcal{X} \otimes \mathcal{Y}$  is defined as:

$$\mathcal{P}\{\mathcal{Z}=z\}=\sum_{k=0}^{k=+\infty}\mathcal{P}\{\mathcal{X}=k\} imes\mathcal{P}\{\mathcal{Y}=z-k\}$$

Figure 5(a) shows an example convolution of two ETPs. The remainder of this section illustrates the SPTA application procedure and discusses how its computational cost can be mitigated.

Figure 5: SPTA basic concepts: (a) convolution; (b) sampling; (c) inter-ETP parallelization.

# 5.2 SPTA Application Procedure