Document downloaded from:

http://hdl.handle.net/10251/166139

This paper must be cited as:

Pérez-López, D.; Gasulla Mestre, I.; Dasmahapatra, P.; Capmany Francoy, J. (2020). Principles, fundamentals, and applications of programmable integrated photonics. Advances in Optics and Photonics. 12(3):709-786. https://doi.org/10.1364/AOP.387155

The final publication is available at https://doi.org/10.1364/AOP.387155

Copyright Optical Society of America

Additional Information

# Principles, Fundamentals and Applications of Programmable Integrated Photonics

DANIEL PÉREZ<sup>1,2</sup>, IVANA GASULLA<sup>1,2</sup>, PROMETHEUS DAS MAHAPATRA<sup>1,2</sup> AND JOSÉ CAPMANY<sup>1,2,\*</sup>

<sup>1</sup>Photonics Research Labs, ITEAM Research Institute Universitat Politècnica de València, Camino de Vera s/n, 46022 Valencia, Spain

<sup>2</sup>iPronics Programmable Photonics S.L., Camino de Vera s/n, 46022 Valencia, Spain \*jcapmany@iteam.upv.es

**Abstract:** Programmable Integrated Photonics is an emerging new paradigm, which aims at designing common integrated optical hardware resource configurations, capable of implementing an unconstrained variety of functionalities by suitable programming following a parallel but not identical path to that of integrated electronics in the last two decades of the last century. Programmable Integrated Photonics is raising a considerable interest as it is driven by the surge of a considerable number of new applications in the fields of telecommunications, quantum information processing, sensing and neurophotonics calling for flexible, reconfigurable, low-cost, compact and low-power-consuming devices that can cooperate with integrated electronic devices to overcome the limitation expected by the demise of Moore's Law. Integrated photonic devices exploiting full programmability are expected to scale from application specific photonic chips (featuring a relatively low number of functionalities) up to very complex application-agnostic complex subsystems much in the same way as Field Programmable Gate Arrays and microprocessors operate in electronics. Two main differences need to be considered. First, as opposed to integrated electronics, programmable integrated photonics will carry analog operations over the signals to be processed. In second place, the scale of integration density will be several orders of magnitude smaller due to the physical limitations imposed by the wavelength ratio of electrons and lightwave photons. Success of Programmable Integrated Photonics will depend on leveraging on the properties of integrated photonic devices and, in particular, on research into suitable interconnection hardware architectures that can offer a very high spatial regularity as well as the possibility of independently setting (with a very low power consumption) the interconnection state of each connecting element. Integrated multiport interferometers and waveguide meshes provide regular and periodic geometries, formed by replicating unit elements and cells respectively. In the case of waveguide meshes, the cells can take the form of a square, hexagon or triangle, among other configurations. Each side of the cell is formed by two integrated waveguides connected by means of a Mach-Zehnder Interferometer or a tunable directional coupler that can be operated by means of an output control signal as a crossbar switch or as a variable coupler with independent power division ratio and phase shift. In this paper, we provide the basic foundations and principles behind the construction of these complex programmable circuits. We also review some practical aspects that limit the programming and scalability of Programmable Integrated Photonics and provide an overview of some of the most salient applications demonstrated so far.

# 1. Introduction

1.1 Definition and general features of reconfigurable systems

Reconfigurable (or programmable) systems are configurations with soft-definable features that can be tuned, reshaped, or otherwise altered by digital logic to suit the purposes of their users [1]. These systems are usually referred to as "soft hardware", [1, 2]. Reconfigurability is now commonplace in electronics components and circuits with the Field Programmable Gate Array (FPGA) device being the real paradigm of electronic reconfigurable systems.

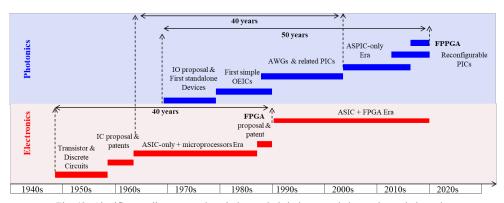

FPGAs were initially conceived to compete with Application Specific Integrated circuits (ASICs). But nowadays, after almost 30 years since their inception, they have practically replaced them in most applications [3]. The increased complexity that can be achieved, fueled by the benefits of Moore's law and reduced non-recurring engineering costs, have propelled FPGAs to a leading position that is further sustained by the trend in fusing practical engineering and design principles. Thanks to FPGAs, one can effectively manage the flexibility required in the so-called software-x approaches, which include among others software-defined radios [4], software-defined networks [5], cloud computing [6] and data center concepts [7]. All in all, the FPGA concept has shown the potential of reconfigurability to become a disruptive technology in information and communication systems according to the requirements described by Christensen [8].

But, going beyond the all-digital FPGA concept, electronic programmable systems are being now developed that encompass as well new subsystems [3], including small sets of resident reconfigurable analog processing blocks as well as digital-to-analog and analog-to-digital conversion stages.

Going even further one may ask if it makes sense to consider the extension of programmable systems to other application scenarios such as reconfigurable circuitry at radio frequencies, antenna structures and, of course, photonics. None of these fields have yet reached the degree of integration maturity of electronics in general and FPGAs in particular.

Broadly speaking, the design of reconfigurable systems needs to consider two important aspects. The first one, known as *designing for reconfigurability*, refers to the set of ideas for embedding flexibility within systems through the methodical incorporation of exploitable switch and configuration mechanisms. The second aspect, known as *designing with reconfigurability*, refers to the processes by which user designs are embedded in reconfigurable fabrics, often through design automation.

Reconfigurable systems are sometimes criticized because they require overhead, which may lower performance and add complexity, possibly reducing reliability. These considerations must be traded-off against their advantages when considering their use for a particular application or field. Nevertheless, they bring a considerable number of benefits, which can be summarized as follows:

- 1. Flexible reshaping of finite resources: A reconfigurable system can be considered as a finite collection of resources that can be reshaped at will, leading to advantages in mass extreme customization, reduction of nonrecurring engineering expenses, economic savings through inventory collapse, design rectification and functional update and iterative refinement to accommodate evolution.

- Robustness and resilience: Reconfigurability results in systems that are tolerant

to faults and manufacturing defects by exploiting unused configurable resources.

Redundancy can be implemented provided that enough spatial resources are

available. Furthermore, by software programming it is possible to create selfhealing and/or cooperative multitasking.

- 3. Achieving "x on demand": Reconfigurability brings the advantage of creating systems quickly. Prebuilt parts can be personalized rapidly overcoming the long fabrication cycles of dedicated systems or chips. This is especially important in electronic microfabrication.

4. *Infinite resources through timesharing*: Reconfigurable systems can be thought as a set of infinitely re-purposeable components leading to temporal reuse.

The interested reader can find a very detailed description of these and other concepts pertaining to the general properties of reconfigurable systems in [1].

# 1.2 Programmable integrated photonics

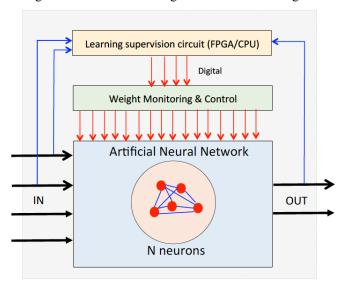

Programmable Integrated Photonics (PIP) [9]-[24] is a new paradigm that aims at designing common integrated optical hardware configurations, which by suitable programming can implement a variety of functionalities that, in turn, can be exploited as basic operations in many application fields. Programmability enables by means of external control signals both chip reconfiguration for multifunction operation as well as chip optimization against non-ideal operation due to fluctuations in environmental conditions and fabrication errors. Programming also allows activating parts of the chip, which are not essential for the implementation of a given functionality but can be of help in reducing noise levels through the diversion of undesired reflections.

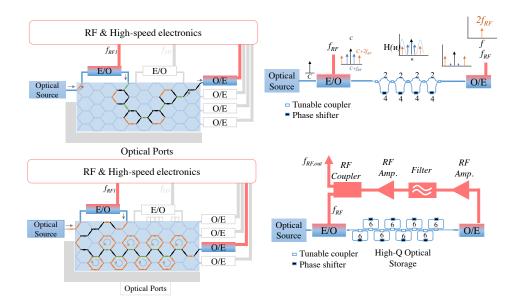

PIP comprises three main families that range from simple reconfigurable Application Specific Integrated Photonics Circuits (ASPICs) to multiport interferometers and, ultimately, integrated waveguide meshes. Figure 1 illustrates the classifications and connection between the different PIP families as well as some of the salient features of each one.

PROGRAMABLE INTEGRATED PHOTONIC FAMILIES

#### Photonic Waveguide Reconfigurable Meshes **ASPICs** Interferometers **Fixed Topology** Application oriented Fixed 2D physical Topology Open 2D physical Topology Optimized for Single Feedforward operation with regular pattern functionality Emulate any linear matrix Feedforward/feedbackward Unoptimized for few transformation operation functionalities Multiple functionalities Emulate any linear circuit. Reconfigurable Multiple spatial circuits Multiple functionalities Multiple spatial circuits fabrication volumes Programmable Non-optimized Partially enable Programmable implementation of FPPGAs Fully enable Suitable for Small/medium implementation of FPPGAs Can emulate some ASPICs Suitable for Small/mediun fabrication volumes Can emulate any multiport interferometer Can emulate any ASPIC

Fig. 1. Classification and features of the main Programmable Integrated Photonic families.

The most basic configuration for PIPs is the reconfigurable ASPIC, which retains most of the main features of fixed designs but bring some degree of reconfigurability whereby the operation and bias points governing the circuit response can be programmed but the overall functionality of the chip is not changed. A second family is formed by multipoint interferometers. These are based on two-dimensional (2D) fixed topologies built from tunable interferometers and can be programmed to emulate any linear feedforward arbitrary unitary matrix transformation. Finally, photonic waveguide meshes, based on open 2D topologies following regular geometric patterns are capable of emulating any reconfigurable ASPIC and multiport interferometer while in addition can implement any feedforward and feedbackward transformation.

PIP aims to provide a complementary approach to that based on fixed ASPICs, which has been dominant during the last years with an ultimate objective of seeking similar advantages as FPGAs bring over ASICs in electronics, including fast time to market, low non-recurring engineering costs, high flexibility and simple design flow. Of the above families, both multiport interferometers and waveguide meshes can support this *optical* FPGA concept and, therefore, will be the subject of this paper.

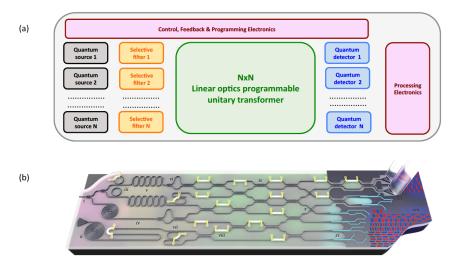

PIP has recently raised the interest of many research groups worldwide, justified by the surge of a number of emerging applications that are and will be calling for true flexibility, reconfigurability as well as low-cost, compact and low-power-consuming devices. One area in which considerable seminal work has been produced is quantum information, where PIP can open avenues to large-scale quantum gates and boson sampling circuits based on unitary matrix transformations [9], [10], [13], [15].

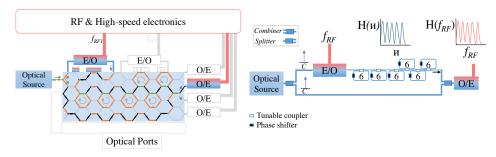

In the field of telecommunications, PIP can be instrumental in a series of signal processing functionalities, such as arbitrary mode converters [25], [26], fiber-wireless interfacing devices [27] and broadband switches [28], which can also form the basis for computer interconnections [29]. In the field of sensing, PIP can lead to a generic class of programmable measuring devices [30], which might be successfully integrated as a building block in the future Internet of Things.

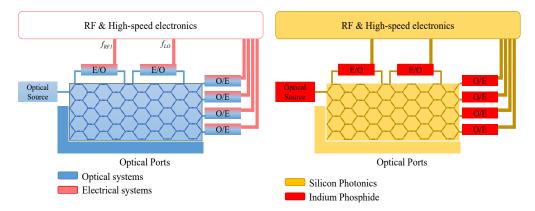

The success of PIP relies on several factors. The first one is the disposal of a suitable material platform that enables the fabrication of complex photonic circuitry. In section 2.1 we review the salient features of the main alternatives that are currently available. As we will see, the most popular platforms feature somehow complementary properties in terms of losses, footprint and capability of incorporating active devices. Therefore, it makes sense to consider hybrid or heterogeneous approaches that leverage on the best of each of them. These approaches will be also briefly covered.

A second key aspect is the possibility of designing suitable basic building blocks able to carry elementary signal processing operations and interconnection architectures that can offer a very high spatial regularity and the possibility of independently setting (with a very low power consumption) the interconnection state of each connecting element. The most attractive and versatile option for the implementation of basic building blocks proposed so far is based on elementary 2x2 arbitrary unitary transformers also known as *rotation matrices*. From these transformers, one can construct 2x2 *reversible gates*. The principles behind these unitary 2x2 reversible gates are provided in section 2.2. An additional advantage of rotation matrix transformers is that they can be readily implemented by combining a set of fairly simple and standard integrated optic components reviewed in sections 2.3 and 2.4, such as beamsplitters, Mach Zehnder Interferometers, directional couplers and phase shifters. Section 2.5 illustrates how 2x2 reversible gates can be built from these components while section 2.6 introduces two basic processing subsystems: *mode converters* and *universal couplers* that can be built by suitable combination of reversible gates and find a considerable room for practical applications.

Complex circuit architectures for the implementation of PIP circuits make use of interconnection architectures for the basic building blocks, which fall broadly into two categories. The first, which is covered in section 3, includes the so-called multiport interferometers and has been historically the first to be developed, in particular to enable unitary linear optical transformations that are at the heart of quantum circuits, reconfigurable neurophotonic systems and Fourier-based optical signal processors [24]. The most popular multiport interferometer designs are the triangular multiport interferometer concept proposed by Reck et al. [21] and subsequently developed for integrated optics by Miller [11], [12]. The more recent rectangular multiport interferometer was proposed by Clements and co-workers [22], [23]. In sections 3.1 and 3.2, we provide a full description of these designs respectively while in section 3.3 we cover the more advanced topic of 3D fast interferometers. Multiport interferometers can enable any kind of linear optics transformations as long as feed-forward-only propagation is assumed. While this covers a wide range of applications, it does not enable

the programming of resonant structures where simultaneous feed-forward and feed-backward propagation is required.

Integrated waveguide meshes [17]-[20], covered in section 4, are the second category of interconnection architectures and overcome this limitation. They provide regular and periodic geometries, formed by replicating a unit cell, which can take the form of a square, hexagon or triangle, among other configurations. Each side of the cell is formed by two integrated waveguides connected by means of a beamsplitter/tunable coupler that can be operated by means of an output control signal as a crossbar switch or as a variable coupler with independent power division ratio and phase shift. A mesh formed by a suitable amount of unit cells can be programmed to implement a wide variety of functionalities much in the same way as a FPGA operates in electronics [17], [20]. In this section we cover the salient features and define the main figures of merit to benchmark the performance of different waveguide mesh designs and provide a comparative analysis.

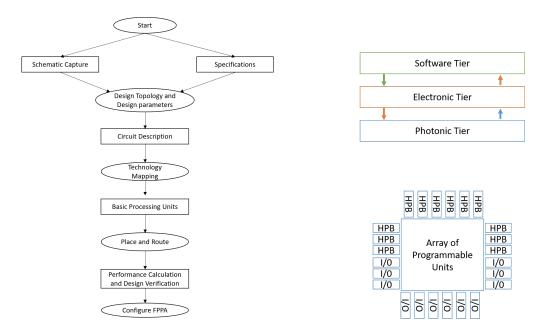

Once we have discussed the possible implementation options for complex photonic architectures, the next logical step is to consider their use as the optical core of a much more flexible and versatile programmable system, the Field Programmable Photonics Gate Array (FPPGA), which is called to play a similar role to that of FPGAs in electronics. In a FPPGA, a common photonics hardware is designed to provide several resources that can be employed to implement different functionalities by means of programming. However, the FPPGA is different from the FPGA in the sense that it does not carry digital logic operations, rather it exploits optical interference to perform very-high-speed analog operations acting over the phase and amplitude of optical signals. We discuss the main features of FPPGAs in section 5, including the basic hardware design principles as well as design flow and technology mapping concepts.

The design, programming and operation of complex programmable integrated photonic circuits and FPPGAs entails addressing a considerable number of challenges and limitations. Some of these reside in the pure physical characteristics of the material platforms employed in their construction and mainly affect their insertion losses through signal coupling efficiency and propagation and scattering losses. Others are connected to the inherent fabrication errors and fluctuations in the operating values of the building blocks parameters and call for active control and monitoring of the waveguide meshes. A third class of challenge is connected to the design and programming of scalable structures containing ever increasing unit cells. These challenges are addressed in detail in section 6, where we also cover some of the most interesting experimental solutions reported so far.

Present and future envisaged applications of PIP are covered in section 7 where we address some applications in emerging quantum systems, including quantum computing and quantum transport simulation, as well as in classical applications such as telecommunications and switching, RF and analog photonics, neurophotonics and artificial intelligence.

# 2. Basic principles, building blocks and technologies

# 2.1 Fundamental material platforms for programmable integrated photonics.

PIP circuits rely principally on optical waveguides and, therefore, the same material platforms and approaches that are employed in the implementation of ASPICs are applicable here. In addition to the low cost implicit in the economies of scale resulting from replicating the same architecture, further cost savings can be ripped by aligning the fabrication processes with current state-of-the-art Generic Integration (GIM) and Generic Foundry (GFM) Models [31]. In the GIM, a small set of standardised basic building blocks are provided to control the basic properties of light and more complex circuits or Compound Building Blocks are then built by connecting several basic building blocks. In the GFM, the foundry provides a shared open access to its generic integration process through multi project wafers, where different designs are combined on the same wafer providing cost sharing and additional advantages such as on-

wafer testing. Since GIM and GFM allow a broad range of functionalities to be synthesized from a small set of basic building blocks, they have been identified as the only path leading to mass production of photonic integrated circuits (PICs), where figures in the order of 10 €/mm<sup>2</sup> can already be reached at volumes of 1000 chips for InP technology [31].

To date, three material platforms: 1) Indium Phosphide (InP), 2) Silicon on Insulator (SOI) and 3) Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>-SiO<sub>2</sub>), have reached the required degree of maturity to be considered as viable options for programmable integrated photonics, either monolithic or hybrid. These operate mainly in the 1.3- and 1.55-μm wavelength regions. We briefly review the salient features of these and refer to the interested reader to the abundant literature in the field.

# 2.1.1 Indium Phosphide PIC technology

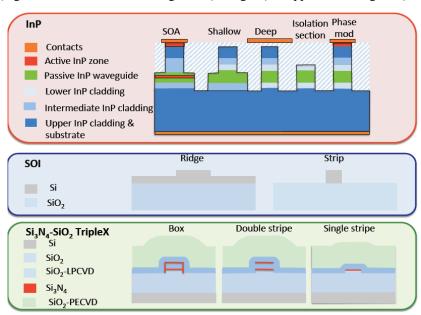

Indium Phosphide is a III-V compound semiconductor material and the only technology capable of the monolithic integration of active (i.e. featuring optical amplification) and passive photonic components [31]-[34]. A variety of techniques, including butt-joint regrowth, selective area growth, offset and dual quantum well placing and quantum well intermixing, can be employed to integrate regions with different absorption/gain properties along a single waveguide. Waveguide types include shallow (low loss and long bending radius) and deeply etched (higher losses and lower bending radius) designs (see upper row in Figure 2).

Fig. 2. Waveguide structures for the InP (upper row) SOI (intermediate row) and Si<sub>3</sub>N<sub>4</sub>-SiO<sub>2</sub> (lower row) platforms.

Shallow waveguides have typical widths of 2 µm and this figure is approximately 1.5 µm for deeply etched designs. Typical losses are around 1.5 and 3 dB/cm for shallow and deeply etched waveguides, respectively, and this is usually quoted as one of the disadvantages of this technology. These losses can be reduced however to figures below 1 dB/cm by removing the p-type top layer in the non-active parts of the chip. Minimum bending radii are in between 10 and 500 µm for deeply etched and shallow etched waveguides, respectively. Another quoted limitation of the InP platform is related to the difficulty of its integration with electronics into the same chip. However, highly promising work is under way towards the integration of the

full photonic functionality in a single InP Membrane on Silicon that could be implemented both in a CMOS or an InP fab, merging InP photonics with silicon electronics.

InP provides the most complete list of available components for integration [32] including: Passives, optical filters, arrayed waveguide gratings, semiconductor optical amplifiers, saturable absorbers, optical sources (Fabry-Perot, distributed Bragg reflector, distributed feedback and mode-locked lasers), detectors (pin single and balanced configurations), amplitude and phase modulators and polarization handling devices. Moreover, it has shown record performance in integrated component count on the same chip with figures exceeding 450 and now targeting 1000 [33].

# 2.1.2 Silicon Photonics PIC technology

Also known as Silicon on Insulator [35]-[38], Silicon Photonics is a semiconductor technology where components are etched/patterned/fabricated in a 180-220 nm Silicon layer placed on top of a 1-3  $\mu$ m insulator layer. Silicon passives are formed by initial few mask layers through partial and/or full Silicon etching steps after which multiple ion implantations are conducted for "active" devices such as Ge photodetectors and Silicon modulators. Coupling into and outside the chip can be performed via edge couplers (with typical losses of 1 dB/facet) or vertically, via Silicon surface gratings (3.5-6 dB/coupler with 40-70 nm 3-dB bandwidth). The main advantage of SOI technology resides in its potential compatibility with CMOS fabrication processes and the infrastructure used in microelectronics and thus in the potential for monolithic integration of the electronic and photonic parts of the chip. Refractive index contrast is over 100% (n = 3.4 for Silicon and n = 1.45 for SiO<sub>2</sub>), leading to small footprint circuits.

Two main types of waveguides are available (see intermediate row in Figure 2): Ridge or shallow (1-8 µm width), which exhibit relatively low losses down to 0.1-0.5 dB/cm, but are limited in bending radius to around 100 µm, and Strip waveguides (500 nm width) that exhibit much higher losses (1-3 dB/cm) but support lower values for minimum bending radius (5-20 μm). Integration density on a chip is currently below 100 components [39], but the component count integration trend is exceeding the rate given by Moore's law indeed. Several basic photonic components are available in monolithic SOI, including passives, such as arrayed waveguide gratings and optical filters, Ge photodetectors, ring and travelling-wave electrorefractive modulators (up to 50 GHz). The main disadvantage of monolithic SOI technology is that it does not support optical sources and other active components such as optical amplifiers. To overcome this limitation, III-V functionalities have to be integrated into the SOI platform by means of either molecular [39] or adhesive [40] wafer bonding. This approach, known as hybrid silicon or hybrid integration technology has succeeded in incorporating amplifiers, saturable absorbers, optical sources (Fabry-Perot, distributed Bragg reflector, distributed feedback and mode-locked lasers, optical amplifiers, electroabsorption (>70 GHz), and Mach-Zehnder (>25 GHz) modulators, photodetectors (>35 GHz) and polarization handling components into SOI chips. However, GFM and GIM have not yet been developed for hybrid integration technology.

# 2.1.3 Silicon Nitride Si<sub>3</sub>N<sub>4</sub>-SiO<sub>2</sub> PIC technology

This waveguide technology is based on a combination of stoichiometric silicon nitride (Si<sub>3</sub>N<sub>4</sub>) as waveguide layers, filled by and encapsulated with silica (SiO<sub>2</sub>) as cladding layers grown on a silicon wafer [41], [42]. SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> layers are fabricated with CMOS-compatible industrial standard low-pressure chemical vapour deposition equipment that enables cost-effective volume production. A special technology known as TriPleX<sup>TM</sup> [34], [41], developed by the Dutch company LioniX International, allows the fabrication of waveguides with minimized surface roughness allowing high refractive index contrast (20-30%) and low scattering losses.

The TriPleX<sup>TM</sup> platform offers seven waveguide cross-sectional geometries [41], some of which are shown in the lower part of Figure 2. Their salient characteristics at 1550 nm are: low

index contrast box-shaped ( $1\mu m \times 1\mu m$ ) that features reduced birefringence,  $\leq 0.2$  dB/cm losses and minimum bending radius ( $R_{min}$ ) around 500 µm and Mode Field Area (MFA) of 3.6 x 3.6  $\mu$ m<sup>2</sup>; high-index contrast featuring  $R_{min}$  of 150  $\mu$ m and MFA of 1.4 x 1.4  $\mu$ m<sup>2</sup>; single-stripe ( $R_{min}$ of 2000  $\mu$ m, <0.03 dB/cm losses and MFA of 4.7 x 2.9  $\mu$ m<sup>2</sup>); double-stripe (1 $\mu$ mx1 $\mu$ m,  $R_{min}$  of 100 μm and MFA of 1.6 x 1.7 μm<sup>2</sup>) obtained by removing the sidewalls of the box configuration, which leads to significant reduction of the waveguide losses that are now in the <0.1 dB/cm range. In/out coupling is achieved by means of adiabatically tapered spot-size converters to low index contrast double-stripe cross-sections with <1 dB coupling loss. Several fundamental building blocks are available including the optical waveguide, tuning elements, directional and multimode interference couplers. From these, more complex subsystems have been demonstrated. For the double-stripe geometry, a library of standard optical components with predictable characteristics is available. The main disadvantage of this technology is that no optical sources, detectors, amplifiers and modulators are available. The integration of these components requires a hybrid approach with separately fabricated InP platform chips [42]. The recent development of InP device stamping techniques [43] and InP membranes on Silicon [44] opens the path for the compact and versatile implementation of this required hybrid integration approach.

# 2.2 Integrated waveguides and phase shifters

Integrated optical waveguides can have, as pointed out in the previous subsection, different geometries and refractive index profiles [45]-[49]. Their main role is to propagate stable electromagnetic field patterns known as guided modes. Although in general we will consider throughout this paper the term "mode" in a very general way as a solution to the Maxwell equations, we will not consider here other alternatives to guided modes such as radiation and leaky modes.

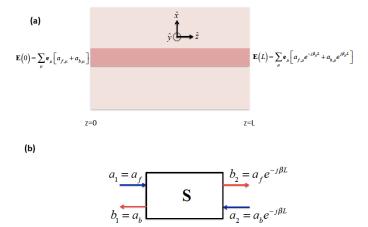

The solution of Maxwell equations for an integrated waveguide at a given frequency  $\omega$  can be expressed as a superposition of guided modes, each characterized by a stable transversal field profile and a propagation constant [45], [46], [49]. In practice, a good approximation is to consider only transversal electric (TE) and transversal magnetic (TM) modes. Figure 3 (a) shows the top view of an integrated optical waveguide including the axes convention 1, TE modes are characterized by having only one non-zero electric field component  $E_x$ ,  $H_y$  being proportional to  $E_x$  and  $|H_z| << |H_y|$ . TM modes are characterized by having only one non-zero magnetic field component  $H_x$  and by  $E_y$  being proportional to  $H_x$  and  $|E_z| << |E_y|$ .

Fig. 3. (a) Top-view representation of a photonic integrated waveguide of length L with input and output fields corresponding to the different propagated modes. (b) Black-box representation of the integrated waveguide action over the fundamental TE<sub>01</sub> mode.

In general, we can write for TE modes the field in the waveguide as [49]:

$$\mathbf{E} = \sum_{\mu} \mathbf{e}_{\mu} \left[ a_{f\mu} e^{-j\beta_{\mu}z} + a_{b\mu} e^{j\beta_{\mu}z} \right],$$

$$\mathbf{H} = \sum_{\mu} \mathbf{h}_{\mu} \left[ a_{f\mu} e^{-j\beta_{\mu}z} - a_{b\mu} e^{j\beta_{\mu}z} \right],$$

(1)

where  $\mu$  is the index representing the mode number,  $a_{f\mu} a_{b\mu}$  the mode amplitudes of the forward and backward propagation components respectively,  $\beta_{\mu}$  is the propagation constant of mode  $\mu$  and  $\mathbf{e}_{\mu}$ ,  $\mathbf{h}_{\mu}$  the field patters of mode  $\mu$ , which can be expressed as:

$$\mathbf{e}_{\mu} = E(x, y)\hat{e}_{\mu},$$

$$\mathbf{h}_{\mu} = H(x, y)\hat{h}_{\mu},$$

(2)

where  $E_{\mu}(x,y)$ ,  $H_{\mu}(x,y)$  represent the field stable transversal profiles of the mode and  $\hat{\mathbf{e}}_{\mu}$  and  $\hat{\mathbf{h}}_{\mu}$  are the polarization vectors of the electric and magnetic fields, respectively. The actual shape of  $E_{\mu}(x,y)$ ,  $H_{\mu}(x,y)$  usually requires a numerical calculation using 2D and/or 3D solvers.

In the case of a singlemode (i.e.,  $TE_{01}$ ) propagation waveguide of length d and referring to Figure 3 (b) we have ( $\mu = 1$ , but we drop the subscript in this case):

$$b_{2} = a_{f} e^{-j\beta d} = a_{1} e^{-j\beta d},$$

$$b_{1} = a_{h} e^{-j\beta d} = a_{2} e^{-j\beta d}.$$

(3)

Hence, the scattering matrix for describing the waveguide action over this mode reads:

$$\mathbf{S} = \begin{pmatrix} 0 & e^{-j\beta d} \\ e^{-j\beta d} & 0 \end{pmatrix}. \tag{4}$$

The matrix can be extended as well to consider *N* propagating modes if needed, although, in the rest of the paper we will be mainly concerned with singlemode waveguides. From (4), we observe that the main action of the propagation along a waveguide consists in a phase shift of the propagated mode. Actually, the phase shift depends on the waveguide length and the mode propagation constant [45]-[49]. More generally, the propagation constant for the TE fundamental mode can be expressed in terms of an effective refractive mode index as:

$$\beta_{TE} = \frac{2\pi n_{TE} d}{\lambda}.$$

(5)

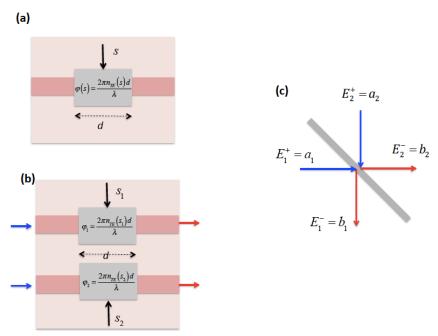

Any change in the value of  $n_{TE}$  for a fixed waveguide length will result in a corresponding change in the phase shift (a similar expression holds for the fundamental TM mode).  $n_{TE}$  depends, upon other factors on the waveguide geometry as well as core and cladding material refractive index n and this in turn can be changed through different mechanisms that include temperature, current injection, electro-optic effect, mechanical stress, and non-volatile phase actuation based on phase-change materials etc. For each one, detailed expressions of these dependences can be found in the literature for the main materials employed in integrated photonics [46]-[49]. Hence, through the application of an external control signal s over a suitable actuating device of length d grown on top of an integrated waveguide as shown in Figure 4(a), one can change the material refractive index in that localized region and therefore the propagation constant of any guided mode in general and the fundamental TE mode in

particular. This means that the control signal s can change the phase shift experienced by the propagating signal. This embodiment of an actuator close to the integrated waveguide is known as a *tunable phase shifter*, and it is a fundamental block of programmable circuits, as we shall see.

Fig. 4. (a) Schematic layout of an integrated phase shifter where an actuator placed on top of the waveguide generates a change in its refractive index  $n_{TE}(s)$  and a subsequent phase shift by means of a control signal s. (b) a two waveguide tunable phase shifter. (c) Representation of bulk beamsplitter including input and output fields corresponding to its two surfaces.

Referring to (4), (5) and our previous discussion, the scattering matrix of a tunable phase shifter is given by:

$$\mathbf{S} = e^{-j\theta(s)} \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}, \qquad \theta(s) = \frac{2\pi n_{TE}(s)d}{\lambda}.$$

(6)

In practice, phase shifters are also implemented over two parallel waveguides in the so-called *differential push-pull* phase shifter scheme, with independent control signals  $s_1$  and  $s_2$  as shown in Figure 4(b). In this case and considering the propagation from left to right in each waveguide one can define the following scattering matrix:

$$\mathbf{S}_{DPP}(\phi_{1},\phi_{2}) = \begin{pmatrix} e^{-j\frac{2\pi n_{TE}(s_{1})d}{\lambda}} & 0\\ 0 & e^{-j\frac{2\pi n_{TE}(s_{2})d}{\lambda}} \end{pmatrix} = e^{-j\frac{(\phi_{1}+\phi_{2})}{2}} \begin{pmatrix} e^{-j\frac{\Delta\phi}{2}} & 0\\ 0 & e^{j\frac{\Delta\phi}{2}} \end{pmatrix},$$

$$\phi_{1} = \frac{2\pi n_{TE}(s_{1})d}{\lambda}$$

$$\phi_{2} = \frac{2\pi n_{TE}(s_{2})d}{\lambda}$$

$$(7)$$

# 2.3 Beam-splitters, tunable directional couplers and 3-dB Mach Zehnder interferometers.

Figure 4(c) illustrates the operation of a bulk beam splitter [49]-[51]. Given an incident optical signal, these devices reflect part of it and transmit the rest. In practice, beam splitters are not employed in integrated programmable photonic circuits, but they are commonly used in their functional description as they play a similar role to integrated waveguide couplers. Our interest here is in the derivation of its scattering matrix as this will be useful to understand the modelling of complex multiport interferometers, which are treated in section 3.

The action of the beam splitter can be described by means of its field reflection and transmission coefficients in each face (i.e.,  $r_{11}$ ,  $t_{21}$  and  $r_{22}$ ,  $t_{12}$  respectively. Referring to Figure 4(c):

$$E_{1}^{-} = r_{11}E_{1}^{+} + t_{12}E_{2}^{+},$$

$$E_{2}^{-} = t_{21}E_{1}^{+} + r_{22}E_{2}^{+}.$$

(8)

Hence, the scattering matrix is:

$$\mathbf{S} = \begin{pmatrix} r_{11} & t_{12} \\ t_{21} & r_{22} \end{pmatrix}. \tag{9}$$

Reciprocity requires that S is symmetric and hence:

$$t_{21} = t_{12} = t. (10)$$

Furthermore, if the beam splitter is assumed to be lossless, then:

$$|r_{11}|^{2} + |t|^{2} = 1,$$

$$|r_{22}|^{2} + |t|^{2} = 1,$$

$$|r_{11}t|e^{j(\phi_{12} - \phi_{11})} + |r_{22}t|e^{j(\phi_{22} - \phi_{21})} = 0.$$

(11)

The first two expressions in (11) imply that:

$$\left|r_{11}\right|^2 = \left|r_{22}\right|^2 = \left|r\right|^2 = 1 - \left|t\right|^2,$$

(12)

while the third, together with (12), imposes a phase shift condition to be fulfilled by the transmission and reflection coefficients:

$$\phi_{12} - \phi_{11} - \phi_{22} + \phi_{21} = \pm (2k+1)\pi, k \in \mathbb{N}, \tag{13}$$

For the sake of simplicity, we take the arbitrary choice  $\phi_{11} = \phi_{22} = 0$  and k = 0, with a positive sign. Hence, we have:

$$2\phi = \pi \Rightarrow \phi = \frac{\pi}{2} \tag{14}$$

Hence, the scattering matrix of the lossless bulk beam splitter is given by:

$$\mathbf{S} = \begin{pmatrix} r & jt \\ jt & r \end{pmatrix}; \ t = \sqrt{1 - r^2}, \tag{15}$$

Integrated couplers are essentially the waveguide equivalent of the beamsplitter and a fundamental building blocks in programmable circuits [12]-[24]. These devices are based on the coupling between field modes propagating within a specific localized region. There are two main types of couplers employed in integrated photonics: the directional coupler [45-51] and the multimode interference coupler (MMI) [52], [53]. Directional couplers are based on the coupling of the evanescent fields corresponding to the fundamental modes of two integrated waveguides in close proximity. This coupling provides a periodic coupling factor varying from zero to complete cross coupling along the direction of propagation. They are especially suitable for the implementation of 2x2 devices. MMI couplers are based on the interference between different modes propagating in a multimode region. The MMI coupler is based on the self-imaging principle, a property of multimode waveguides by which an input field profile is reproduced in single or multiple images at periodic intervals along the propagation direction of the guide. MMI devices are thus suitable for implementing *NxN* couplers. We briefly review the operating principles and main design equations of both types of couplers.

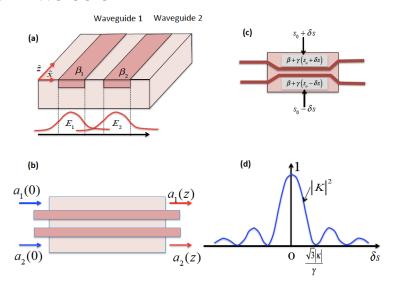

Directional couplers are based on the coupling between the evanescent fields of the copropagating fundamental modes of two waveguides placed in close proximity as shown in Figures 5(a) and 5(b) [45], [49].

Fig. 5. Schematic (a) cross-section and lateral and (b) top view of a directional coupler. (c) Tunable dual drive directional coupler layout including common mode and differential control signals. (d) Tuning curve for the coupling constant value of a reconfigurable directional coupler versus the differential bias signal.

Directional couplers can be designed so a wave launched in one guide can be partially or completely transferred to the other and vice-versa. In this sense, they behave as an integrated beam splitter. Furthermore, this transfer can be controlled by means of an external control signal enabling the so-called tunable directional couplers.

For the description of the directional coupler, we consider Figure 5(a) and two forward propagating modes  $a_1$  and  $a_2$  of waveguides 1 and 2 respectively (i.e., we only take the first member in (1)), which, in absence of coupling have propagating constants  $\beta_1$  and  $\beta_2$  and fulfil the equations [45]-[49]:

$$\frac{da_{1}}{dz} = -j\beta_{1}a_{1} + \kappa_{12}a_{2}

\frac{da_{2}}{dz} = -j\beta_{2}a_{2} + \kappa_{21}a_{1}$$

(16)

where  $\kappa_{12}$  and  $\kappa_{21}$  are the coupling coefficients from waveguide 2 to waveguide 1 and from waveguide 1 to waveguide 2, respectively. The solution of (16) for a coupler with a coupling length region given by z can be found in several classical textbooks [45],[4],[50]: is given by:

$$\begin{pmatrix}

a_{1}(z) \\

a_{2}(z)

\end{pmatrix} = \mathbf{S}_{TCD} \left(\theta = f\left(\beta_{1}, \beta_{2}, \kappa\right)\right) \begin{pmatrix}

a_{1}(0) \\

a_{2}(0)

\end{pmatrix}$$

$$\mathbf{S}_{TCD} \left(\theta = f\left(\beta_{1}, \beta_{2}, \kappa\right)\right) = e^{-j\frac{(\beta_{1} + \beta_{2})z}{2}} \begin{pmatrix}

e^{j\varphi(\Delta\beta)}\cos(\theta/2) & j\sin(\theta/2) \\

j\sin(\theta/2) & e^{-j\varphi(\Delta\beta)}\cos(\theta/2)

\end{pmatrix}$$

$$K = \left(\frac{\kappa \sin\beta_{o}z}{\beta_{o}}\right)^{2} = \sin^{2}(\theta/2)$$

$$\Delta\beta = \beta_{2} - \beta_{1}$$

$$\beta_{o} = \sqrt{\left(\frac{\Delta\beta}{2}\right)^{2} + \kappa^{2}}$$

$$\varphi(\Delta\beta) = \tan^{-1}\left[\frac{\Delta\beta}{2\beta_{o}}\tan\beta_{o}z\right]$$

(17)

with  $\kappa_{12} = \kappa_{21} = j\kappa$ .

In many practical cases, directional couplers are made out by using identical waveguides and therefore  $\Delta\beta = 0$ , which simplifies (17) to the well-known relation:

$$\mathbf{S}_{TDC}(\beta,\theta) = e^{-j\beta z} \begin{pmatrix} \cos(\theta/2) & j\sin(\theta/2) \\ j\sin(\theta/2) & \cos(\theta/2) \end{pmatrix}$$

$$K = \sin^2 \beta_o z = \sin^2 \left(\frac{\theta}{2}\right)$$

(18)

Note however that tunable directional couplers are required for applications in programmable photonics and that tunability is achieved by means of inducing a refractive index asymmetry in the two optical waveguides. Therefore, the matrix form given by (17) needs to be employed. In this case, the coupling constant and overall phase shift of a directional coupler

can be independently tuned by means of two control signals that will induce a propagation constant mismatch between the two waveguides in the coupler as illustrated in Figure 5(c). We assume that:

$$\beta_1 = \beta + \gamma (s_o + \delta s),$$

$$\beta_2 = \beta + \gamma (s_o - \delta s),$$

(19)

where  $s_o$  is a common tunable bias signal and  $\delta s$  is the differential signal applied to the transducers. We further assume that under no applied control signals the coupler length is designed so the device is in cross-state, (i.e.,  $z = \pi/2|\kappa|$ ). Under these conditions, the differential signal change to achieve the transition to the bar state is [46], [50]:

$$\delta s = \frac{\sqrt{3} \left| \kappa \right|}{\gamma}.\tag{20}$$

Hence, the complete transition  $(0 \le K \le 1)$  is achieved for  $(0 \le \delta s \le \sqrt{3} |\kappa| / \gamma)$  as shown in Figure 5(d). Moreover, the overall phase shift is given by:

$$\Delta = \left(\frac{\beta_1 + \beta_2}{2}\right) = \beta + \gamma s_o. \tag{21}$$

Note however that a residual phase shift is experienced by signals that does not change the propagation waveguide. This phase shift is given by:

$$\varphi(\delta s) = \tan^{-1} \left[ \frac{1}{\sqrt{1 + \left(\frac{|\kappa|}{\gamma \delta s}\right)^2}} \tan \left(\frac{\pi \gamma \delta s}{2|\kappa|} \sqrt{1 + \left(\frac{|\kappa|}{\gamma \delta s}\right)^2}\right) \right]. \tag{22}$$

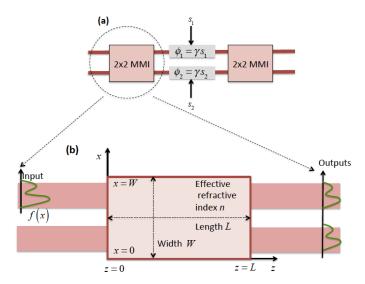

An alternative to tunable directional couplers that is the most widely option employed for the implementation of programmable integrated circuits is the tunable 3-dB balanced Mach-Zehnder interferometer. A layout of this device is shown in Figure 6(a) and it is composed of two 3-dB couplers that form a balanced Mach-Zehnder Interferometer (MZI) [54], where each arm incorporates a tunable phase shifter. The 3-dB splitters are usually implemented using multimode interference couplers (MMIs). The MMI is based on a step-index multimode waveguide shown in Figure 6(b) [52]-[54]. The structure displayed in the figure has a length L, a width W and a refractive index n, with input/output waveguide ports incorporated at the extreme surfaces. 3 dB MMIs splitters have the following 2x2 scattering matrix:

$$\mathbf{S} = \frac{je^{j\varphi_o}}{\sqrt{2}} \begin{pmatrix} 1 & j \\ j & 1 \end{pmatrix},\tag{23}$$

where  $\varphi_0$  is a common phase factor.

Fig. 6. (a) Tunable 3-dB MZI coupler, (b) layout of the 2x2 3-dB Multimode Interference (MMI) coupler used to embed the balanced interferometer.

If we assume that the transduction mechanism leading to the phase shifting in each arm can be described by  $\phi_i = \gamma s_i$ , i = 1, 2, where  $\gamma$  is the transduction coefficient, then calling:

$$\Delta = 2\varphi_o + \frac{\gamma(s_1 + s_2)}{2},$$

$$\theta = \gamma(s_2 - s_1) + \pi,$$

(24)

which leads to:

$$\mathbf{S}_{MZI}(\Delta,\theta) = -je^{j\Delta} \begin{pmatrix} \cos(\theta/2) & \sin(\theta/2) \\ \sin(\theta/2) & -\cos(\theta/2) \end{pmatrix}. \tag{25}$$

Equation (25) represents a tunable coupler where the coupling constant  $K=\sin^2\theta$  and the overall phase shift  $\Delta$  can be independently tuned using the two control signals  $s_1$  and  $s_2$  according to the system of two equations and two unknowns given by (30).

# 2.4 Reversible 2x2 Gates

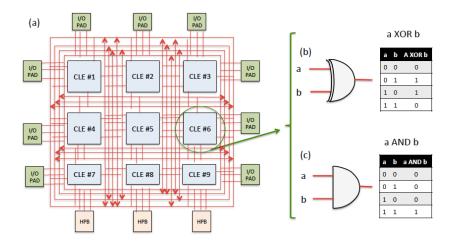

Digital electronic FPGAs are composed of a set of interconnected configurable logic elements (CLEs), input/output devices and high-performance blocks (HPBs), as shown in Figure 7(a). It is customary to employ elementary *irreversible* gates [55], [56] for bit processing using Boolean logic as building blocks for CLEs [4], as shown. These gates are characterized by the fact that the number of input ports is 2 while the number of output ports is 1. Figures 7(b) and (c) show some basic examples of these gates, which are characterized by their so-called truth tables. The term irreversible reflects the fact that the input cannot be deduced from the output unambiguously. By cascading thousands of these gates one can build extremely complex combinatorial and sequential Boolean circuits.

Fig. 7. (a) Schematic layout of an electronic FPGA containing a set of interconnected Configurable Logic Elements (CLEs), Input/output Pads and High-performance Blocks (HPBs) and Examples of irreversible logic Boolean gates employed in the design of CLEs (b) XOR gate, (c) AND gate.

Reversible gates [56], [57] feature the same number of input and output ports and are characterized as well by truth tables. In this case, the input state can be deduced from the gate output as the gate operation can also be described by a unitary matrix transformation U. If I and O denote respectively the input and output vectors, the O = UI, hence  $I = U^{-1}O$ , but since U is unitary its inverse is given by the Hermitian conjugate. Reversible gates can be employed to perform digital Boolean operations but this process is inefficient compared to the use of irreversible gates as it entails the use of fixed or ancilla bits and produces as well garbage bits, which are not useful to the rest of the computation [58]. As a consequence, reversible gates are not employed in digital electronics.

The situation in photonics is however quite different. First, reversible gates have found an application niche in the field of photonics quantum computation [13], [56]-[58]. The two main reasons are firstly that quantum computation does not rely on in Boolean logic but rather on the use of linear unitary transformations as a qubit  $|\psi\rangle = \alpha|0\rangle + \beta|1\rangle$  resembles more an analog than a digital signal as the multiplying complex coefficients  $\alpha$  and  $\beta$  states can be continuously changed. Indeed, the qubit processing by the logic gate is really carried altering its wave-like and not its particle-like properties. The second reason and equally important is that reversible gates can be engineered to exploit the garbage bits as heralding ports [56] to certify the correct operation of the gate. Since programmable integrated photonic circuits for classical signal processing applications handle, as we will see in the next section, analog signals as well it makes sense therefore to consider the use of reversible gates as a basic building block to implement complex circuit structures just much in the same way as they are employed for quantum photonics.

We now briefly consider the formalism for the implementation of complex programmable photonic circuits taking as basic building blocks a special family of 2x2 reversible gates known as rotation gates [56], [57]. We first illustrate how these gates isomorphically correspond to some of the photonic components addressed in the prior subsection, such as directional and 3-dB tunable couplers and push-pull phase shifters. We then show how these can be concatenated in two compact forms to implement tunable arbitrary 2x2 unitary transformers. These unitaries can be in turn, as we will see in section 5, assembled into two-dimensional configurations to feature FPPGAs.

We start by considering the basic 2x2 Pauli matrices given by [56],[57]:

$$\sigma_{o} = I = \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}; \ \sigma_{1} = X = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}$$

$$\sigma_{2} = Y = \begin{pmatrix} 0 & -j \\ j & 0 \end{pmatrix}; \ \sigma_{3} = Z = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}$$

(26)

Two-dimensional rotation matrices (by an angle  $\theta$ ) around axes x, y and z are defined by the following transformations:

$$R_{x}(\theta) = e^{-j\frac{\theta}{2}X}; R_{y}(\theta) = e^{-j\frac{\theta}{2}Y}; R_{z}(\theta) = e^{-j\frac{\theta}{2}Z}.$$

(27)

Using basic operator theory, it can be readily shown that:

$$R_{x}(\theta) = \begin{pmatrix} \cos(\theta/2) & j\sin(\theta/2) \\ j\sin(\theta/2) & \cos(\theta/2) \end{pmatrix}.$$

$$R_{y}(\theta) = \begin{pmatrix} \cos(\theta/2) & -\sin(\theta/2) \\ \sin(\theta/2) & \cos(\theta/2) \end{pmatrix}$$

$$R_{z}(\theta) = \begin{pmatrix} e^{-j(\theta/2)} & 0 \\ 0 & e^{j(\theta/2)} \end{pmatrix}$$

(28)

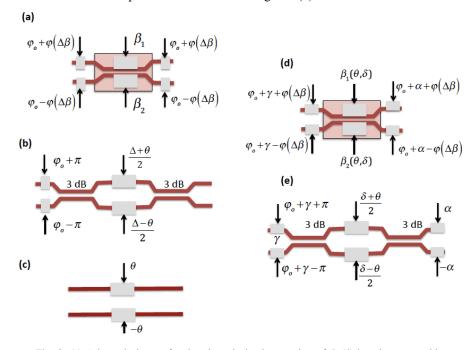

The reader can identify strong similarities between these and (25), (18) and (7) derived in the prior subsection, indicating that these rotations can be implemented in the photonics domain respectively by a directional coupler, a 3-dB Mach-Zehnder tunable coupler and two parallel waveguides including two phase shifters configured in push-pull mode, as shown in Figure 8. This is in fact the case although small modifications need to be introduced into these devices as shown in the figure and which we now outline.

It is immediate to verify that:

$$R_{x}(\theta) = \begin{pmatrix} \cos(\theta/2) & j\sin(\theta/2) \\ j\sin(\theta/2) & \cos(\theta/2) \end{pmatrix} = e^{-j\frac{(\beta_{1}+\beta_{2})z}{2}} e^{j\frac{(\beta_{1}+\beta_{2})z}{2}} e^{j\frac{(\beta_{1}+\beta_{2})z}{2}}$$

$$\begin{pmatrix} e^{j\varphi(\Delta\beta)/2} & 0 \\ 0 & e^{-j\varphi(\Delta\beta)/2} \end{pmatrix} \begin{pmatrix} e^{j\varphi(\Delta\beta)}\cos(\theta/2) & j\sin(\theta/2) \\ j\sin(\theta/2) & e^{-j\varphi(\Delta\beta)}\cos(\theta/2) \end{pmatrix} \begin{pmatrix} e^{j\varphi(\Delta\beta)/2} & 0 \\ 0 & e^{-j\varphi(\Delta\beta)/2} \end{pmatrix} =$$

$$= e^{j\frac{(\beta_{1}+\beta_{2})z}{2}} e^{j2\varphi_{o}} \mathbf{S}_{DPP} (\varphi_{o} + \varphi(\Delta\beta), \varphi_{o} - \varphi(\Delta\beta)) \mathbf{S}_{TDC} (\theta = f(\beta_{1},\beta_{2},\kappa)) \mathbf{S}_{DPP} (\varphi_{o} + \frac{\varphi(\Delta\beta)}{2}, \varphi_{o} - \frac{\varphi(\Delta\beta)}{2})$$

$$(29)$$

Note that since  $\varphi_0$  can be arbitrarily set,  $2\varphi_0 = -(\beta_1 + \beta_2)z/2$ , then:

$$R_{x}(\theta) = \mathbf{S}_{DPP}(\varphi_{o} + \varphi(\Delta\beta), \varphi_{o} - \varphi(\Delta\beta)) \mathbf{S}_{TDC}(\theta = f(\beta_{1}, \beta_{2}, \kappa)) \mathbf{S}_{DPP}(\varphi_{o} + \varphi(\Delta\beta), \varphi_{o} - \varphi(\Delta\beta)). \tag{30}$$

Therefore, a rotation around the *x* axis can be implemented by a tunable directional coupler embedded by two identical push-pull waveguide phase shifters as shown in Figure 8(a). In a similar way:

$$R_{y}(\theta) = \begin{pmatrix} \cos(\theta/2) & -\sin(\theta/2) \\ \sin(\theta/2) & \cos(\theta/2) \end{pmatrix} = je^{-j\Delta} \begin{pmatrix} -je^{j\Delta} \end{pmatrix} \begin{pmatrix} \cos(\theta/2) & \sin(\theta/2) \\ \sin(\theta/2) & -\cos(\theta/2) \end{pmatrix} \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix} =$$

$$= je^{-j\Delta}e^{j\theta_{o}}\mathbf{S}_{MZI}(\Delta,\theta)\mathbf{S}_{DPP}(\varphi_{o} + \pi, \varphi_{o} - \pi)$$

(31)

Note now that since  $\varphi_0$  can be arbitrarily set so  $\varphi_0 = \Delta - \pi/2$  then:

$$R_{\nu}(\theta) = \mathbf{S}_{MZI}(\Delta, \theta) \mathbf{S}_{DPP}(\varphi_{o} + \pi, \varphi_{o} - \pi)$$

(32)

In other words, a rotation around the y axis can be implemented by a 3-dB MZI tunable coupler preceded by a push-pull waveguide phase shifter as shown in Figure 8(b). Finally:

$$R_{z}(\theta) = \begin{pmatrix} e^{-f(\theta/2)} & 0 \\ 0 & e^{f(\theta/2)} \end{pmatrix} = \mathbf{S}_{DPP}(\theta, -\theta)$$

(33)

Hence, a rotation around the z axis can be implemented by a push-pull waveguide phase shifter with zero common phase bias as shown in Figure 8(c).

Fig. 8. (a) Schematic layout for the photonic implementation of  $R_x(\theta)$  based on a tunable directional coupler. (b) Schematic layout for the photonic implementation of  $R_y(\theta)$  based on a tunable 3-dB MZI coupler. (c) Schematic layout for the photonic implementation of  $R_z(\theta)$  based on a differential push-pull phase shifter. (d) Integrated photonic implementation of an arbitrary unitary 2x2 matrix transform using a cascade of  $R_x(\theta)$  and  $R_z(\theta)$  rotations. (e) Integrated photonic implementation of an arbitrary unitary 2x2 matrix transform using a cascade of  $R_y(\theta)$  and  $R_z(\theta)$  rotations.

Rotation operators and their implementations are fundamental since by virtue of the Euler theorem [56], [57] any arbitrary 2x2 unitary matrix U can be expressed in either of the two following sequential rotation matrix concatenation forms:

$$U = e^{j\delta} R_z(\alpha) R_y(\beta) R_z(\gamma),$$

$$U = e^{j\delta} R_z(\alpha) R_x(\beta) R_z(\gamma),$$

(34)

where  $\alpha$ ,  $\beta$ ,  $\gamma$  and  $\delta$  are a set of four real and independent numbers. This means that compact configurations consisting of a preceding and succeeding differential phase shifting units enclosing either a dual-drive directional coupler or a 3-dB MZI unit as shown in Figures 8(d) and 8(e), respectively, can be employed to implement these arbitrary units.

The importance and applicability of reversible gates as basic building blocks in programmable photonics will become clear to the reader in sections 3 to 5.

# 3. Multiport interferometers

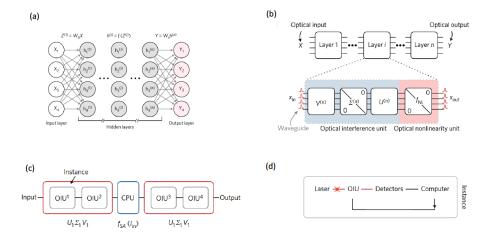

Integrated multiport interferometers were initially conceived and designed to implement fixed feed-forward linear optics unitary transformations between N input and N output ports to support mode transformations. They have been especially employed in quantum optics. However, the rapid development of this field and the possibility of applying these structures to other classical areas, such as deep learning and neurophotonics, stimulated the development of devices capable of supporting any arbitrary linear transformation by suitable programming and furthermore no longer restricted to square matrix transformations and unitary operators. In this section, we first review some basic concepts on unitary NxN matrices and then we will describe in detail the basic design principles and integrated optics implementations of the two most popular designs for multiport interferometers; the triangular and the rectangular designs.

### 3.1 Basic concepts on unitary matrices

Multiport optical interferometers implement unitary transformations between N input and N output ports [21]-[23], [59]. It is useful to review some salient properties of these transformations. If we assume a NxN unitary transformation U, then  $UU^{\dagger} = U^{\dagger}U = I$ , where  $^{\dagger}$  denotes the Hermitian conjugate and I the NxN identity matrix. We shall now describe five important properties of unitary matrices U that are relevant in the design of multiport interferometers. The complete demonstrations of these properties can be found in [59].

<u>Property 1:</u> If all the matrix coefficients in a given row i are zero except  $u_{ii}$ , that is  $u_{ij} = 0$  for  $j \neq I$ , then all the matrix coefficients in column i are zero, except  $u_{ii}$ , that is,  $u_{ji} = 0$  for  $j \neq i$ . Furthermore,  $u_{ii}$  is a modulus one complex number.

<u>Property 2:</u> if all the matrix coefficients in a given column i are zero except  $u_{ii}$ , that is  $u_{ji} = 0$  for  $j \neq i$ , then all the matrix coefficients in row i are zero, except  $u_{ii}$ , that is,  $u_{ij} = 0$  for  $j \neq i$  and, again,  $u_{ii}$  is a modulus one complex number.

One matrix of special interest is the *generalized ZY cascade rotation matrix* in the plane defined by rows m and n:

$$T_{mn}(\varphi,\theta) = \begin{pmatrix} 1 & 0 & \cdots & \cdots & \cdots & \cdots & \cdots & 0 \\ 0 & 1 & \cdots & \cdots & \cdots & \cdots & \cdots & 0 \\ \vdots & \vdots & \ddots & \cdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & \cdots & e^{j\varphi}\cos\theta & \cdots & -\sin\theta & \cdots & 0 \\ \vdots & \vdots & \cdots & \vdots & \ddots & \vdots & \cdots & 0 \\ 0 & 0 & \cdots & e^{j\varphi}\sin\theta & \cdots & \cos\theta & \cdots & 0 \\ \vdots & \vdots & \cdots & \cdots & \cdots & \ddots & \vdots \\ 0 & 0 & \cdots & 0 & \cdots & 0 & \cdots & 1 \end{pmatrix} \begin{pmatrix} 1 \\ 2 \\ \vdots \\ m \\ \vdots \\ N \end{pmatrix}$$

(35)

which, according to (32) and (33), corresponds to a tunable 3-dB MZI coupler between inputs m and n and outputs n and m in this order that performs a y-wise rotation of  $\theta$  radians preceded by a phase shifter performing the z-wise rotation of  $\varphi$  radians. As it can be immediately checked,  $T_{mn}(\varphi, \theta)$  is unitary and its inverse is given by:

$$T_{mn}^{-1}(\varphi,\theta) = \begin{pmatrix} 1 & 0 & \cdots & \cdots & \cdots & \cdots & \cdots & 0 \\ 0 & 1 & \cdots & \cdots & \cdots & \cdots & \cdots & 0 \\ \vdots & \vdots & \ddots & \cdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & \cdots & e^{-j\varphi}\cos\theta & \cdots & e^{-j\varphi}\sin\theta & \cdots & 0 \\ \vdots & \vdots & \cdots & \vdots & \ddots & \vdots & \cdots & 0 \\ 0 & 0 & \cdots & -\sin\theta & \cdots & \cos\theta & \cdots & 0 \\ \vdots & \vdots & \cdots & \cdots & \cdots & \ddots & \vdots \\ 0 & 0 & \cdots & 0 & \cdots & 0 & \cdots & 1 \end{pmatrix} N$$

(36)

and corresponds to a tunable 3-dB MZI coupler between inputs m and n and outputs n and m that performs a y-wise rotation of  $-\theta$  radians succeeded by a phase shifter the z-wise rotation of  $-\varphi$  radians.

<u>Property 3:</u> The product  $UT^{I}_{mn}(\varphi,\theta)$  is a unitary matrix that leaves all the columns in U unaltered with the exception of columns m and n and we can choose values for  $(\varphi,\theta)$  to null whatever (but only one) coefficient in these columns.

<u>Property 4:</u> The product  $T_{mn}(\varphi, \theta)U$  is a unitary matrix that leaves all the rows in U unaltered with the exception of rows m and n and we can choose values for  $(\varphi, \theta)$  to null whatever (but only one) coefficient in these rows.

<u>Property 5:</u> If D is a diagonal matrix with  $d_{ij} = e^{j\alpha_{ij}}$ , then for any  $T^{-1}_{mn}(\varphi, \theta)$  one can find a diagonal matrix D' with  $d_{ij} = e^{j\delta_{ij}}$  and a matrix  $T_{mn}(\varphi', \theta')$  such that  $T^{-1}_{mn}(\varphi, \theta)D = D'T_{mn}(\varphi', \theta')$ .

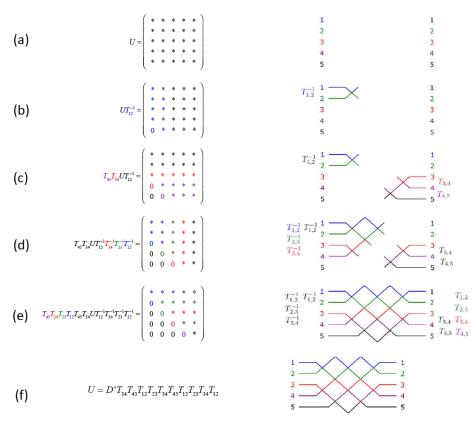

# 3.2 Triangular interferometers

The triangular arrangement for a multiport programmable interferometer was proposed by Reck and co-workers in 1994 [21]. It is based on the iterative use of Property 3 described in the previous subsection to make zero all the off-diagonal elements in the unitary matrix U.

In a first step, U is multiplied from the right by a succession of matrices  $T^{1}_{Nq}(\varphi_{q},\theta_{q})$  with  $q=N-1,\dots 1$ . This product is equivalent to the attachment of successive 2x2 tunable beam splitters to ports q and N. By making use of Property 3 after each product to null element (q,N) and then property 1, we have:

$$U(N)T_{NN-1}^{-1}T_{NN-2}^{-1}\cdots T_{N1}^{-1} = \begin{pmatrix} * & * & * & * & 0 \\ * & * & * & \cdots & 0 \\ * & * & * & * & 0 \\ \cdots & \cdots & \cdots & \cdots & 0 \\ * & * & * & * & 0 \\ 0 & 0 & 0 & 0 & e^{j\alpha_{N}} \end{pmatrix} = \begin{pmatrix} U'(N-1) & \mathbf{0} \\ \mathbf{0} & e^{j\alpha_{N}} \end{pmatrix}.$$

(37)

Note that the effective dimension of the resulting matrix has been reduced to N-1. We can now apply the same procedure based on Property 3, bearing in mind that the elements in the last row will remain zero and thus will not be affected by successive multiplications from the right, to reduce the dimensions to N-2, N-3 and finally to 1, leading to:

$$U(N)T_{NN-1}^{-1}T_{NN-2}^{-1}\cdots T_{N1}^{-1}\cdots T_{32}^{-1}T_{31}^{-1}T_{21}^{-1} = \begin{pmatrix} e^{j\alpha_{1}} & 0 & 0 & 0 & 0\\ 0 & e^{j\alpha_{2}} & 0 & \cdots & 0\\ \cdots & \cdots & \cdots & \cdots & 0\\ 0 & 0 & 0 & e^{j\alpha_{N-1}} & 0\\ 0 & 0 & 0 & 0 & e^{j\alpha_{N}} \end{pmatrix} = D.$$

$$(38)$$

Hence, as D is a diagonal (and unitary) matrix, we have:

$$U^{-1}(N) = T_{NN-1}^{-1} T_{NN-2}^{-1} \cdots T_{N1}^{-1} \cdots T_{32}^{-1} T_{31}^{-1} T_{21}^{-1} D^{-1},$$

(39)

which finally yields:

$$U(N) = DT_{21}T_{31}T_{32}\cdots T_{N-1N-2}T_{N1}\cdots T_{NN-2}T_{NN-1} = D\prod_{i=2}^{N} \left[\prod_{j=1}^{i-1} T_{ij}\right].$$

(40)

Equation (40) provides the desired decomposition of the unitary operator into a set of beam splitter operations completed by a phase shifting operation. Each beam splitter relates two inputs and two outputs of the overall structure.

Reck and co-workers proposed for  $T_{mn}(\varphi_{mn}, \theta_{mn})$  the bulk optics configuration shown in Figure 9 (a), which is represented in chip layouts by the symbol shown in Figure 9 (b). Figures 9 (c) and 9(d) show as an example, the decomposition and the layout for a general 4x4 unitary matrix. The practical implementation of this method involves a triangular array of beam splitters, each diagonal row in the triangle reducing the effective dimension of the Hilbert space by one. The maximum number of required beam splitters to implement U(N) is given by N(N-1)/2. For later comparison with the rectangular design, it is useful to define the *depth* of an interferometer [22] as the longest path through the interferometer, enumerated by counting the number of beam splitters traversed by that path. In the case of the triangular interferometer, this corresponds to the edges of the triangle and is given by (N-1)+(N-2)=2N-3.

Triangular interferometers can be integrated on a chip as suggested by Miller [11], [12] by replacing the tunable bulk optics beam splitter shown in Figure 9 (a) by its equivalent version in integrated optics, which is the tunable basic unit (TBU) shown in Figure 8(a)-(b) or Figures 8 (d)-(e). Up to now, this has been the preferred option for implementing most reconfigurable integrated optical quantum circuits [59], [13], [15], [60], [61] and some classical applications as well [23], [62], [12], [26]. Figure 9 (e) illustrates this equivalence for the 4x4 unitary transformer discussed above. The triangular interferometer has been reported in several material Platforms. We show now some examples and provide further discussion of these and other implementations in section 7, in the context of their applications.

Fig. 9. (a) Bulk optics implementation of a tunable beam splitter (After [21]). (b) Symbol representation of the beam splitter layout. (c) Triangular decomposition implementing a general U(4) 4x4 unitary transformation and layout (d). Colours represent the propagation of a given input port. (e) U(4) layout of Figure 8(d) and its implementation using MZI based TBUs. TBUs in red colour operate as phase shifters.

# 3.2 Rectangular interferometers

The rectangular universal NxN interferometer has been recently proposed [22]. This design is based on an alternative arrangement of U(2) beam splitters and phase shifters and outperforms the triangular arrangement in a series of figures of merit, including the optical depth, which is half of that of the triangular design and robustness against optical losses.

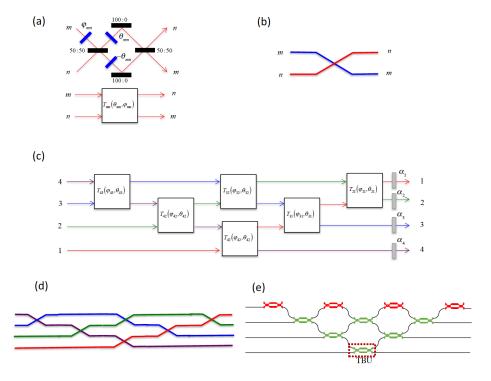

In the triangular decomposition [21], successive columns or rows of the U(N) matrix are nulled using either only matrices (multiplied from the left) or only matrices (multiplied by the right) respectively, making sure that nulled elements of U(N) are not affected by subsequent operations. The rectangular decomposition [22], proceeds by nulling successive diagonals of U(N) by alternating between  $T_{mn}$  and  $T^{-1}_{mn}$  matrices where m = n-1, in such a way that every nulled diagonal in the matrix corresponds to one diagonal line of beam splitters through the interferometer. The sequence of and matrices must both correspond to the desired order of beam splitters in the interferometer and guarantee that the nulled elements of U(N) are not affected by subsequent operations. This is illustrated as an example in Figure 10 for the case of a U(5) interferometer [22].

The process [22], starts by nulling the bottom-left element of U(5) (first diagonal) with the  $T^{-1}_{12}$  matrix, which, according to property 3 causes the first two columns of U(5) to mix. This corresponds to adding the top-left beam splitter in the interferometer as shown in the right hand-side of Figure 10(b). We then null the second diagonal using a  $T_{34}$  matrix followed by a  $T_{45}$  matrix, which correspond to the two bottom-right beam splitters in the interferometer as shown in Figure 10(b). According to property 4,  $T_{34}$  mixes rows 3 and 4, and  $T_{45}$  mixes rows 4 and 5. Note that since both the (4,1) and (5,1) elements of U(5) have been previously nulled, they are

not affected by  $T_{45}$ . We then proceed at every next step to null a successive diagonal of the updated U(5) matrix by alternating between  $T_{mn}$  and  $T^{1}_{mn}$  matrices, which corresponds to adding diagonal lines of beam splitters to the interferometer. This is shown in Figure 10 (d) and (e).

The final expression after the decomposition process is:

$$T_{45}T_{34}T_{23}T_{12}T_{45}T_{34}UT_{12}^{-1}T_{34}^{-1}T_{23}^{-1}T_{12}^{-1} = D. (41)$$

However, taking property 5 into consideration, we finally have:

$$U = D'T_{34}T_{45}T_{12}T_{23}T_{34}T_{45}T_{12}T_{23}T_{34}T_{12}.$$

(42)

The decomposition in (42) corresponds to the multiport interferometer shown in Fig. 10 (f), and the values of the  $\theta$  and  $\phi$  of the  $T_{mn}$  matrices determine the values of the beam splitters and phase shifts that must be programmed to implement U(5).

Fig. 10. Illustration of the algorithm for programming a universal multiport interferometer for U(5) interferometer (After [22]). The left-hand side presents the decomposition procedure, and the right-hand side shows how the decomposition for building up the corresponding interferometer. (a) The starting point is any random unitary matrix U(5) and a blank interferometer. (b)-(e) Successive stages of the implementation algorithm. (f) Final expression for U(5) in terms of a cascade of U(2) interferometers and a diagonal matrix.

The rectangular interferometer requires N(N-1)/2 beam splitters to implement a U(N) transformation, just like the triangular arrangement. However, its depth is only N, which is roughly half of those required for the triangular design and this leads to lower balanced losses, which are related to the propagation loss of the longest path in the interferometer [22]. In

addition, its symmetry leads to improved loss tolerance as related to the unbalanced loss, which is due to the different losses experienced by the signal propagating through the different paths of the interferometer. We provide more information regarding the comparative performance of these and other multiport interferometer later in this chapter.

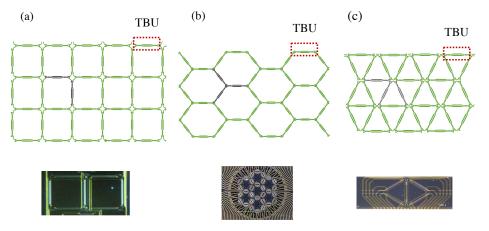

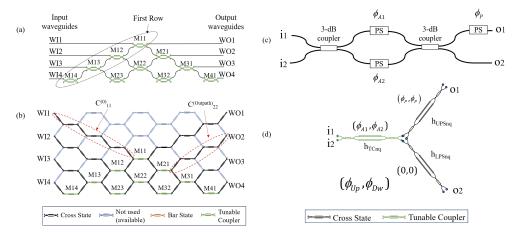

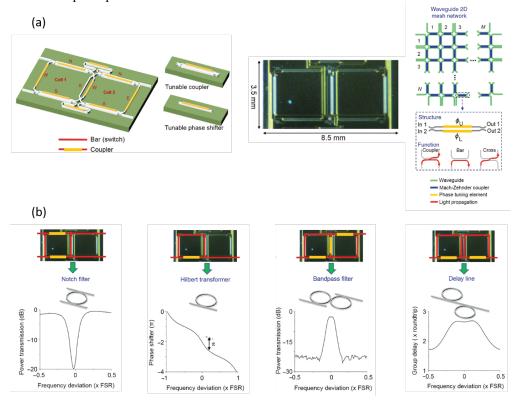

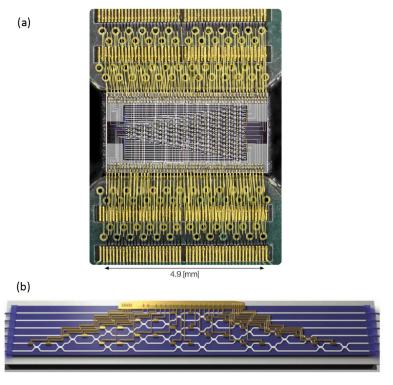

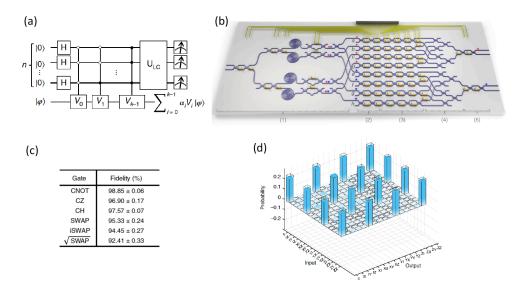

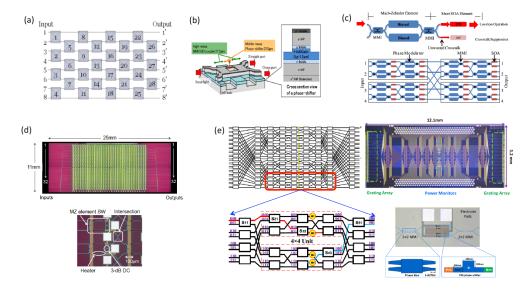

Rectangular interferometers can also be integrated on a chip following a similar procedure to that of the triangular arrangement using, for instance, the tunable basic units of Figure 8. Figures 11 (a) and (b) show the layout of a U(9) interferometer and its integrated optics design using 3-dB MZI TBUs. Due to their recent proposal, there have been few experimental reports of the rectangular interferometer. The first one was reported in [23], where a U(4) interferometer was emulated in a silicon hexagonal waveguide mesh. Specific rectangular interferometer integrated designs have been very recently reported [63]. Figure 11 (c) shows the photograph of a modular set composed of 3 linear optical circuits. Each module consists of ten tunable MZIs placed side by side as shown in Figure 11 (d). Modules are to be tiled to build larger interferometers. For example, as we have seen above, N of such modules with at least N2 MZI wide are enough to perform an arbitrary unitary transformation U(N), with optimal circuit depth. In this case, the circuit was employed to implement up to U(6) transformations for different applications.

Fig. 11. Integrated rectangular interferometers. (a) Design Layout for a U(9) transformer (after [22]) and (b) implementation layout suitable for integrated optics using 3-dB MZIs (after [23]). (c) Photograph of a three-module silica on silicon rectangular interferometer (after [63]). (d) Detail of an individual module showing 10 parallel TBUs (after [63]).

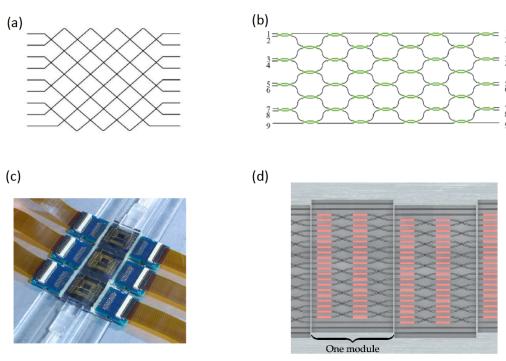

# 4. Integrated photonic waveguide meshes

4.1 Concept of multipurpose Photonic waveguide mesh

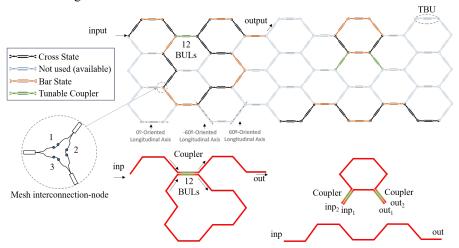

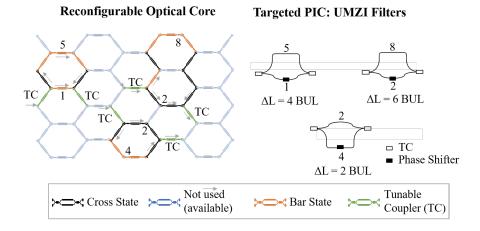

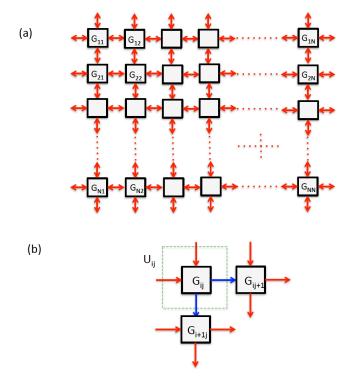

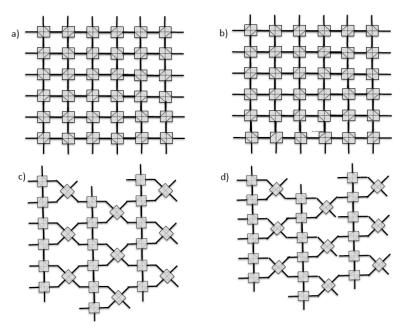

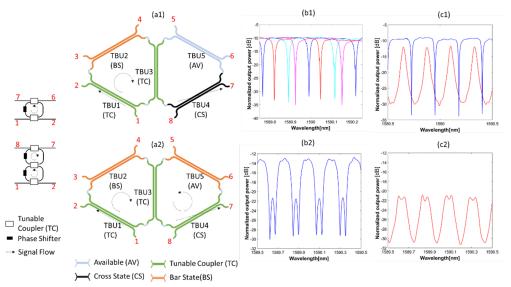

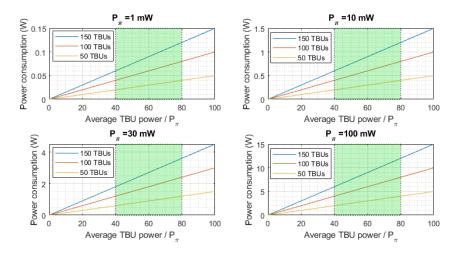

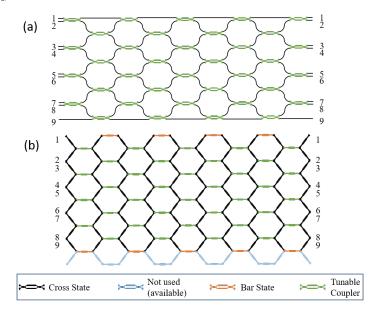

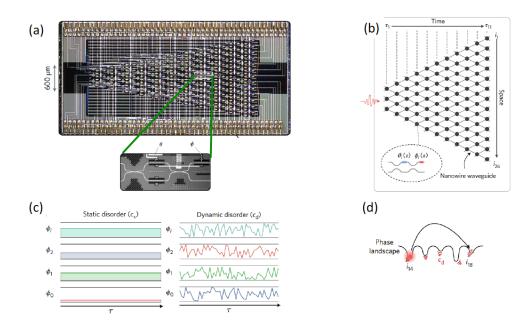

Integrated waveguide meshes are 2D structures where a unitary cell composed of a subset of TBUs is spatially replicated [12]-[20], [64]. Several examples are shown in Figure 12. Each unitary cell is implemented by one or more sets of integrated waveguide pairs coupled by means of a TBU, the core of which can be any of the 2x2 reversible gate designs described in section 2 and shown in Figure 8. The application of external electrical signals to the TBU terminals allows the independent amplitude and phase control of the photonic signals coupled between the two waveguides. In particular, each TBU in the mesh can be configured to operate either as an optical crossbar switch or as an intermediate power divider. In this way, the combination of different TBUs in the 2D grid, -each individually configured as desired-, enables the synthesis of any kind of optical core circuit topology, including finite (FIR) and infinite impulse response (IIR) multiport interferometers and filters. Figures 12 (a) to 12 (c) show the main reported designs for waveguide meshes allowing for both feedforward and feed-backward propagation. Here the unit cell is composed by several TBUs following a geometrical configuration: square, hexagonal and triangular respectively. These are the most flexible waveguide mesh configurations allowing the implementation of both FIR and IIR multiport interferometers and filters. Although each mesh topology has inherent advantages, the hexagonal mesh is potentially the most flexible approach for implementing programmable photonic circuits, as we shall see later.

Fig. 12. Different integrated waveguide mesh arrangements: (a) Squared Feedforward/backward and implementation in  $Si_3N_4$  [17], (b) Hexagonal Feedforward/backward [20], [31] and implementation in SOI, (c) Triangular Feedforward/backward and implementation in  $Si_3N_4$  [18], [64].

# 4.2 Rectangular, triangular and hexagonal waveguide meshes

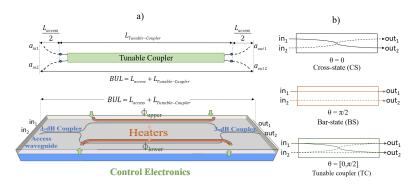

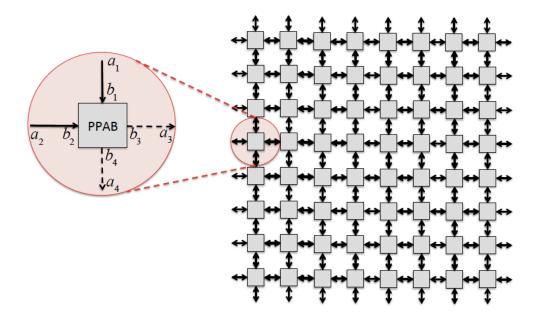

Before considering the different geometries for waveguide meshes and their analysis, it is essential to remember that their primitive block, the TBU is implemented by means of a 2x2 reversible gate that must provide, independently, a complete splitting ratio tuning and phase response, [18], [64], [65]. By setting its control signals, this switching/tapping/dephasing mechanism can be potentially obtained in many different ways (i.e., exploiting thermo-optic, electro-optic of opto-mechanical effects, for example). The different alternatives for 2x2 reversible gates have been considered in section 2 and here, to provide some definitions, we consider, as an example, the case where the TBU is implemented by means of a 3-dB balanced MZI structure loaded with a thermal tuner on each arm, as illustrated in the lower part of Figure 13 (a). Nevertheless, the treatment is not restricted to this case and can be employed for alternative TBU structures and tuning mechanisms.

Fig. 13. (a) (Upper) Labelled schematic of a general tunable coupler acting as the basic building block of the mesh. The Basic Unit Length (BUL) is illustrated as the sum of the tunable coupler length and the arc length of the access waveguides. (Lower) Particular case of an integrated balanced MZI-based tunable coupler. (b) Signal flow for the different TBU configuration states.

The upper part of Figure 13 (a) shows the TBU composed by the tunable coupler and its access (input/output) waveguides. The geometry of the latter is a function of the bending radius and varies for each mesh topology due to different angle between elements. The basic unit length (BUL) is, [18]:

$$BUL = L_{access} + L_{Tunable-Coupler}, (43)$$

where  $L_{access}$  is the overall length of the access waveguide segment and  $L_{Tunable-Coupler}$  is the length that describes the light-path in the tunable coupler. Most importantly, the time that takes the signal to go through the TBU is called the Basic Unit Delay (BUD):

$$BUD = n_g BUL / c, (44)$$

where  $n_g$  is the waveguide group index and c is the speed of light in vacuum. Referring to Figure 13(b), the tunable basic unit can implement 3 different states: cross state switch (light path connects  $in_1$  to  $out_2$  and  $in_2$  to  $out_1$ ), bar state switch (light path connects  $in_1$  to  $out_1$  and  $in_2$  to  $out_2$ ) and tunable splitter.

For a balanced MZI loaded with heaters on both arms, the splitting ratio is obtained by increasing the effective index due to the Joule effect in the upper or lower arm, producing a  $\phi_{upper}$  and  $\phi_{lower}$  phase shift respectively. Once set, a common drive in both heaters will provide a common phase shift, leading to independent control of the amplitude ratio and the phase. The simplified device matrix is given by (25), where  $\theta$  is  $(\phi_{upper}-\phi_{lower})$  and  $\Delta$  is  $(\phi_{upper}+\phi_{lower})$ . A realistic description however must incorporate a general loss term  $\gamma$  that includes the effect of propagation losses in the access waveguides, the tunable coupler waveguide and the insertion losses for both 3-dB couplers. The device performance can be characterized in terms of the optical power by its insertion losses (*IL*) and optical crosstalk parameters ( $CT_{Bar}$  and  $CT_{Cross}$ ):

$$IL(dB) = 20\log_{10}(\gamma) = 10\log_{10}\left(\frac{\left|a_{out}\right|^{2} + \left|a_{out2}\right|^{2}}{\left|a_{in1}\right|^{2} + \left|a_{in2}\right|^{2}}\right),$$

$$CT_{Bar/Cross}(dB)\Big|_{\left|a_{in1}\right|^{2} = 1} = 10\log_{10}\left(\frac{\left|a_{out2,1}\right|^{2}}{\left|a_{out2,2}\right|^{2}}\right).$$

$$(45)$$

These provide valuable information regarding the losses of the tunable units. Since they are connected in cascade configuration to build up the mesh, the overall IL of a certain synthetized device will be the sum of the ILs corresponding to the units across through which the light has travelled. As an example, if we assume overall device losses of 10 dB and IL of 0.2 dB for each TBU, then the longest path will be limited to 50 units. In the case of the optical crosstalk, the figure determines the leaking of signal that might cause optical reflections and undesired interferometric paths coupled to the desired photonic circuit to be programmed. In section 6 we address the impact that non-ideal behaviour of the TBU has over the waveguide mesh design. In order to reduce the footprint of the synthetized circuits, we allow the possibility of using all the TBU ports independently. For example, in a cross state set both  $in_1/out_2$  and  $in_2/out_1$  connections can be employed to configure a conventional crossing unit.

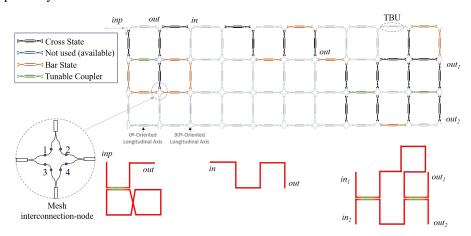

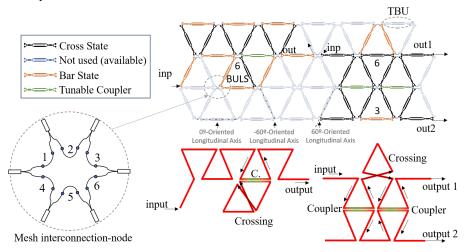

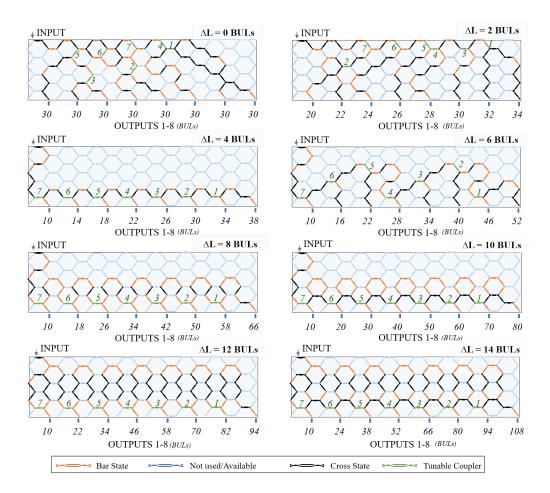

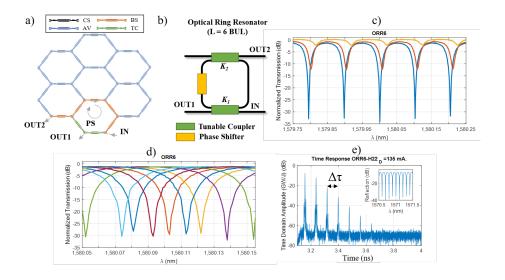

Square waveguide mesh arrangements were the first proposed mesh topology. In his pioneer work, Zhuang and co-workers [17] developed the concept where the interconnection of a large number of integrated balanced MZIs with two actuators could lead to the synthesis of a wide variety of PICs. This is achieved by discretizing conventional circuits into sets of TBUs with specific configurations. The proposed interconnection topology enables the routing of the optical signal path to follow orthogonal directions where the repetition of direction is not allowed for two consecutive TBUs. However, the topology is flexible enough to allow the synthesis of discrete waveguides or delay lines, tunable couplers as well as phase shifters and thus more complex building blocks like optical cavities and unbalanced MZIs. Fig. 14 illustrates the basic configuration of an optical ring resonator defined by a cavity length of 8 BULs, a delay line of 6 TBUs as well as an unbalanced MZI with arm lengths of 3 and 7 TBUs respectively.

Fig. 14. Basic programming of medium-complex circuits in square waveguide mesh topology: delay line, unbalanced MZI and optical ring resonator.

A second option is the triangular waveguide mesh topology proposed in [18]. In this case, three TBUs describing longitudinal orientations of 0° (horizontal plane), 60° and -60° are interconnected through 6 points resulting in a triangular pattern, as illustrated in Figure 15. Notice that the angle described by the longitudinal axis of two connected TBU is always 60°. Again, it can be shown that the interconnection scheme directly impacts on the degrees of freedom that the light has to flow across the structure and consequently the allowed light-paths and circuits that can be implemented inside the arrangement. These are particularly useful to increase the integration density of TBUs, and to implement optical cavities with reduced cavity lengths. The triangular pattern achieves a better discretization resolution of unbalanced filter structures as compared to the square topology. For more details, an in-depth comparative analysis is provided in the next section. The figure illustrates the synthesis of a ring resonator

with a cavity length of 6 BULs and an unbalanced MZI with arm lengths of 3 and 6 BULs respectively. In the latter an internal crossing is implemented.