#### Máster en Ingeniería de Computadores y Redes Trabajo Fin de Máster

# Fusión de los Niveles L1 y L2 de la Jerarquía de Memoria Cache Utilizando DWM.

**Autor:** Hugo Tárrega Sánchez

**Tutor:** Vicente Jesús Lorente Garcés

Director Experimental: Alejandro Valero Bresó

#### Dedicatoria

Cada nuevo científico desempeñando su labor indagadora en el mundo tiene una deuda impagable con todos los científicos que le precedieron. La Ciencia, cómo corpus de saber, constituye la obra colectiva humana más palpable y sincera, a mi parecer. Cada científico aporta según su capacidad y en base a sus recursos sus pequeños avances, que llevan unos pasos más adelante esta gran obra común. Pese a lo difícil y precario de la tarea del investigador en España (que no se puede si no remarcar y denunciar), esta concepción de gran obra común me hace sentir un elemento no imprescindible, pero a la vez terriblemente necesario. Cómo esa idea de gran obra común me ayuda a levantarme por las mañanas, a seguir adelante, a trabajar e incluso a poner a calentar la cafetera, no puedo si no dedicar este trabajo. Así pues, este trabajo va dedicado a todos los científicos que abrieron camino antes que a mí y que permitieron con sus aportaciones que exista hoy mi investigación, mi pequeño granito de arena esforzado. Y es por eso, que, aunque esta deuda de la que hablaba es impagable, dedico este trabajo a aquellos científicos que vinieron antes que yo. Porque la Ciencia es mucho más grande que todos nosotros, pero también somos todos nosotros.

### Agradecimientos

Agradecer primero a Julio Sahuquillo por hacer posible mi investigación. Pese a ser una persona muy ocupada siempre tiene tiempo para buscar opciones para que los investigadores más jóvenes podamos abrirnos camino. Además, su guía a la hora de dirigir mi investigación es imprescindible para que esta llegue a buen puerto. Gracias de corazón. Gracias también a Salva Petit, por ser siempre crítico con el trabajo y siempre proponer nuevas formas de refinar nuestra propuesta.

Congratular a mi tutor Alejandro Valero por la sorprendente exhibición de paciencia que hace día a día conmigo. De él, aparte de un sinfín conocimientos a nivel técnico, estoy aprendiendo la dedicación y la perseverancia. Este trabajo, del que me siento orgulloso, espero que le suponga a él un orgullo también, ya que sin él no existiría. Ojalá la academia reconozca tus méritos y te recompense de forma justa por ellos, porque de verdad lo mereces.

Dar las gracias también a mi tutor Vicent Lorente. Me ha dedicado un tiempo que no tiene y no ceja en el empeño de que afiance mis conocimientos de electrónica. Gracias por el soporte y por el apoyo continuo, por creer en el proyecto desde el principio, por empujarme a leer tanto cómo pueda y no quedarme en la superficie. Finalment, un gràcies grupal als anteriorment citats, són la vostra espenta i passió els que fan possible que en aquest país seguisque sent plausible investigar tot i la carestia de recursos.

#### Resumen

El presente trabajo aborda la necesidad cada vez mayor por parte de la industria de los semiconductores de contar con memorias cache más densas y con un menor consumo energético que las actuales. Debido a que la tecnología actual más utilizada, SRAM, no puede ofrecer estas mejoras, este trabajo propone el uso de las memorias magnéticas DWM (*Domain Wall Memory*) como tecnología emergente sustitutiva.

El presente trabajo aborda principalmente uno de los mayores inconvenientes de DWM como es la latencia variable por acceso a los datos almacenados en una cinta magnética. Este hecho es especialmente crítico en las caches de primer nivel (L1) al encontrarse en el pipeline del procesador y conllevar un impacto directo en el rendimiento del sistema. Para superar este problema, se propone un diseño de cache de datos L1 ascendente. En primer lugar, se diseña una celda de memoria DWM capaz de almacenar múltiples bits y de reducir el impacto de la latencia variable de acceso mediante el uso de múltiples puertos de acceso sobre la cinta, entre otras características. A continuación, se diseña un módulo de cache que integra múltiples celdas DWM, de manera que los conjuntos se organizan de manera entrelazada entre los puertos, favoreciendo la localidad espacial que exhiben las aplicaciones en L1 y por tanto reduciendo la problemática de la latencia variable de acceso. Finalmente, el uso de módulos DWM permite implementar el vector de datos completo de una memoria cache de datos asociativa por conjuntos de n vías. La alta densidad de DWM permite fusionar los niveles L1 y L2 en un sólo nivel DWM con el objetivo de aumentar el rendimiento frente a un diseño de jerarquía de cache convencional SRAM.

La propuesta de cache DWM se implementa y evalúa en el simulador ciclo-a-ciclo Multi2Sim, ampliamente utilizado tanto en la industria como en la academia. Los resultados experimentales muestran que la cache DWM reduce significativamente la penalización media por acceso a memoria, los fallos por kilo-instrucción y los ciclos de parada en el *reorder buffer* frente a un diseño de cache convencional. Todo ello conlleva a una mejora en el rendimiento del sistema de un 10 % en la media no sólo frente a un diseño convencional basado en SRAM sino también frente al diseño DWM del estado-del-arte, referido como TapeCache e implementado como parte del presente trabajo.

Palabras clave: Cache de datos L1, Domain Wall Memory, mononúcleo, Multi2Sim

#### Resum

El present treball aborda la necessitat cada volta més apressant per part de la indústria dels semiconductors de trobar memòries cau més denses i amb un menor consum energètic que les actuals. Com que la tecnologia actual més utilitzada, SRAM, no pot oferir aquestes millores, aquest treball propose l'ús de les memòries magnètiques DWM (Domain Wall Memory com a tecnologia de substitució.)

Aquest treball tracta principalment un dels majors inconvenients de les DWM, com és la latència variable per accés a les dades emmagatzemades en una cinta magnètica. Aquest fet es especialment crític en les memòries cau de primer nivell (L1) al trovar-se en el pipeline del processador i implicar un impacte directe en el rendiment del sistema. Per a superar aquest problema, es propose un disseny de memòria L1 de dades ascendent. En primer lloc, es dissenya una cel·la de memòria DWM capaç d'emmagatzemar múltiples bits i de reduir l'impacte de la latència variable d'accés per mitjà de l'ús de múltiples ports d'accés sobre la cinta, entre altres característiques. A continuació, es dissenya un mòdul de memòria cau que integre múltiples cel·les DWM, de manera que els conjunts s'organitzen de manera entrellaçada entre els ports, afavorint la localitat espacial que exhibeixen les aplicacions en L1 i per tant reduint la problemàtica de la latència variable d'accés. Finalment, l'ús de mòduls DWM permet implementar el vector de dades completes d'una memòria cau de dades associatives per conjunts de n vies. L'alta densitat de DWM permet fusionar els nivells L1 i L2 en un només nivell DWM amb l'objectiu d'augmentar el rendiment enfront d'un disseny de jerarquia de memòria cau convencional SRAM.

La proposta de memòria cau amb DWM s'implementa i avalue en el simulador cicle-a-cicle Multi2Sim, àmpliament utilitzat tant en la indústria com en l'acadèmia. Els resultats experimentals mostren que la memòria cau DWM redueix significativament la penalització mitjana per accés a memòria, les fallades per quilo-instrucció i els cicles de parada en el *reorder buffer* enfront d'un disseny de memòria convencional. Tot això comporta a una millora en el rendiment del sistema d'un 10% en la mitjana no sols enfront d'un disseny convencional basat en SRAM sinó també enfront del disseny DWM de l'estat-del-art, referit com TapeCache i implementat com a part del present treball.

Paraules clau: Cau de dades L1, Domain Wall Memory, mononucli, Multi2Sim

#### **Abstract**

The present work addresses the growing need of the semiconductor industry for denser cache memories with lower power consumption than the current ones. Since the most widely used current technology, SRAM, cannot offer these improvements, this work proposes the use of DWM (Domain Wall Memory) magnetic memories as a substitute emerging technology.

This work mainly addresses one of the major drawbacks of DWM, which is the variable latency for accessing data stored on a magnetic tape. This fact is especially critical in first-level (L1) caches as they are located in the processor pipeline and have a direct impact on the system performance. To overcome this problem, a bottom-up L1 data cache design is proposed. First, it is designed a DWM memory cell capable of storing multiple bits and reducing the impact of the variable access latency by using multiple access ports on the tape, among other features. Next, it is designed a cache module that integrates multiple DWM cells, such that the sets are organized in an interleaved structure between ports, favoring the spatial locality exhibited by applications on L1 and thus reducing the variable access latency issue. Finally, the use of DWM modules allows implementing the complete data array of an associative data cache with n-way sets. The high density of DWM allows merging the L1 and L2 levels into a single DWM level with the goal of increasing performance over a conventional SRAM cache hierarchy design.

The proposed DWM cache is implemented and evaluated on the Multi2Sim cycle-accurate simulator, which is widely used in both industry and academia. Experimental results show that the DWM cache significantly reduces the average memory access penalty, misses per kilo-instruction, and stall cycles in the reorder buffer compared to a conventional cache design. This leads to a 10% improvement in the average system performance not only over a conventional SRAM-based design but also over the state-of-the-art DWM design, referred to as TapeCache and implemented as part of this work.

Key words: Domain Wall Memory, L1 data cache, Multi2Sim, single-core

# Índice general

| Ín     | dice | general<br>de figuras<br>de tablas                           | IX<br>XI<br>XII |

|--------|------|--------------------------------------------------------------|-----------------|

| _<br>1 | Intr | oducción                                                     |                 |

|        | 1.1  | Contexto y Motivación                                        | 1               |

|        | 1.2  | Objetivos                                                    | 2               |

|        | 1.3  | Metodología                                                  | 3               |

|        | 1.4  | Estructura de la Memoria                                     | 4               |

| 2      | Tecı | nologías de Memoria                                          | 7               |

|        | 2.1  | Static Random Access Memory                                  | 7               |

|        | 2.2  | Embedded Dynamic RAM                                         | 7               |

|        | 2.3  | Non-Volatile Memory                                          | 8               |

|        |      | 2.3.1 Spin-Transfer Torque RAM                               | 9               |

|        |      | 2.3.2 Domain Wall Memory                                     | 10              |

|        | 2.4  | Comparativa                                                  | 12              |

| 3      | Ant  | ecedentes                                                    | 13              |

|        | 3.1  | MTJ de Lectura/Escritura                                     | 13              |

|        | 3.2  | Escritura Mediante Shift                                     | 14              |

|        | 3.3  | Comparativa entre Escritura Mediante MTJ y Mediante Shifting | 16              |

|        | 3.4  | Cinta en Anillo                                              | 16              |

|        | 3.5  | Equilibrio entre Puertos y Dominios                          | 16              |

|        | 3.6  | Política de Desplazamiento de Cabezales                      | 17              |

| 4      | Imp  | lementación de DWM Fusionando L1 y L2                        | 19              |

|        | 4.1  | Celda DWM Multi-Bit en Anillo                                | 19              |

|        | 4.2  | Organización de Módulo de Cache                              | 21              |

|        | 4.3  | Organización de Array de Datos de Cache                      | 24              |

| 5      | Dis  | eños de Cache DWM del Estado-del-Arte                        | 27              |

|        | 5.1  | Organizaciones de Cache de Último Nivel                      | 27              |

|        |      | 5.1.1 TapeCache                                              | 27              |

|        |      | 5.1.2 Otras Propuestas                                       | 29              |

|        | 5.2  | Políticas de Gestión de Puertos                              | 30              |

|        | 5.3  | Organizaciones de Cache de Primer Nivel                      | 30              |

| 6      | Ento | orno Experimental                                            | 31              |

|        | 6.1  | Simulador Multi2Sim                                          | 31              |

|        |      | 6.1.1 Estructura de Multi2Sim                                | 32              |

|        |      | 6.1.2 Compilación                                            | 32              |

|        |      | 6.1.3 Ejecución                                              | 33              |

|        |      | 6.1.4 DRAMSim                                                | 34              |

|        | 6.2  | SPEC CPU 2006                                                | 34              |

|        |      | 6.2.1 Descripción de Benchmarks SPEC CPU 2006                | 34              |

|        | 6.3  | GDB                                                          | 38              |

X ÍNDICE GENERAL

|    | 6.4   | Infraestructura de Simulación                               | 38<br>39<br>39 |

|----|-------|-------------------------------------------------------------|----------------|

| 7  | Rest  | ıltados Experimentales y Discusión                          | 41             |

|    | 7.1   | Arquitectura de los Procesadores a Simular                  | 41             |

|    | 7.2   | Distribución de Latencia de Acceso                          | 42             |

|    | 7.3   | Fallos por Kilo Instrucción (MPKI)                          | 44             |

|    | 7.4   | Paradas en el ROB por Accesos a Memoria                     | 44             |

|    | 7.5   | Rendimiento del Sistema                                     | 45             |

| 8  | Con   | clusiones y Trabajo Futuro                                  | 51             |

|    | 8.1   | Relación del Trabajo Desarrollado con los Estudios Cursados | 51             |

|    | 8.2   | Conclusiones                                                | 52             |

|    |       | 8.2.1 Implementación de DWM                                 | 52             |

|    |       | 8.2.2 Resolución de los Problemas Técnicos de la Propuesta  | 53             |

|    | 8.3   | Trabajo Futuro                                              | 53             |

| Bi | bliog | rafía                                                       | 55             |

## Índice de figuras

| 2.1<br>2.2<br>2.3<br>2.4 | Esquema de una celda de memoria 6T SRAM                                                                                                                                                                                                                                                                                                                           | 8<br>9<br>9<br>11               |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 2.5                      | Vista de dominios sobre una cinta [1]                                                                                                                                                                                                                                                                                                                             | 11                              |

| 3.1<br>3.2               | Cinta DWM con dos dominios de escritura prefijados a los valores '0' y '1'. Cinta magnética con representación de la electrónica necesaria para acceder a los bits contenidos                                                                                                                                                                                     | 14<br>14                        |

| 3.3<br>3.4               | Diagrama de una cinta de 32 bits con dos MTJ                                                                                                                                                                                                                                                                                                                      | 17<br>18                        |

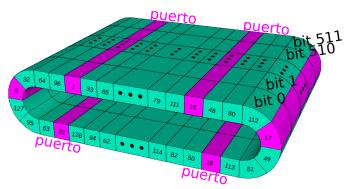

| 4.1<br>4.2               | Propuesta de celda de memoria DWM de 128 bits                                                                                                                                                                                                                                                                                                                     | 20                              |

| 4.3                      | SRAM de 1 bit                                                                                                                                                                                                                                                                                                                                                     | <ul><li>21</li><li>22</li></ul> |

| 4.4                      | Distribución de la latencia de desplazamiento para la organización secuencial de conjuntos (Sec) e intercalada por puertos (Ent) en una cache de datos L1 DWM de 160 KB.                                                                                                                                                                                          | 23                              |

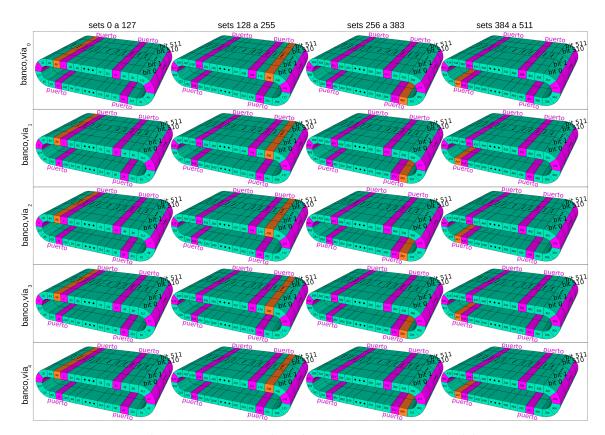

| 4.5                      | Diagrama de una organización de cache DWM con una capacidad de 160 KB, conjuntos de 512 bits y 5 vías. Cada conjunto se expande a 5 anillos, uno por cada vía de cache (filas). Cada columna consta de tantos módulos como vías de cache. Cada vía se expande a 4 columnas (número de conjuntos/128). En color naranja se destaca un par de conjuntos de destino. | 25                              |

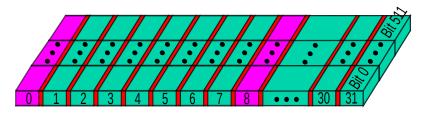

| 5.1                      | Módulo TapeC de 2 KB agrupando 512 cintas con 32 bits cada una. El color cian muestra la ubicación de los puertos de acceso                                                                                                                                                                                                                                       | 28                              |

| 5.2                      | Memoria cache TapeC con 128 KB y 8 vías                                                                                                                                                                                                                                                                                                                           | 28                              |

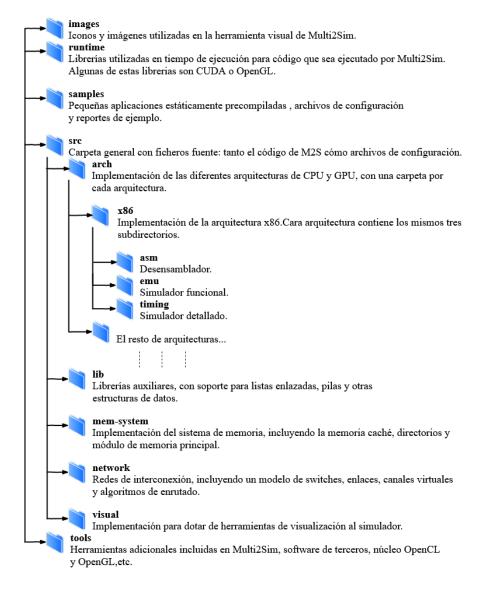

| 6.1                      | Estructura de directorios de Multi2Sim                                                                                                                                                                                                                                                                                                                            | 33                              |

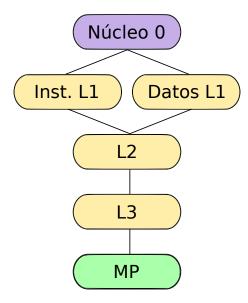

| 7.1                      | Jerarquía de cache convencional utilizada tanto para el diseño convencional SRAM como para TapeC.                                                                                                                                                                                                                                                                 | 42                              |

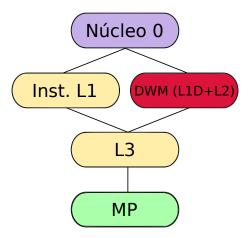

| 7.2                      | Jerarquía de cache propuesta. La cache coloreada en rojo supone la fusión de las caches de datos L1 y L2 originales.                                                                                                                                                                                                                                              | 42                              |

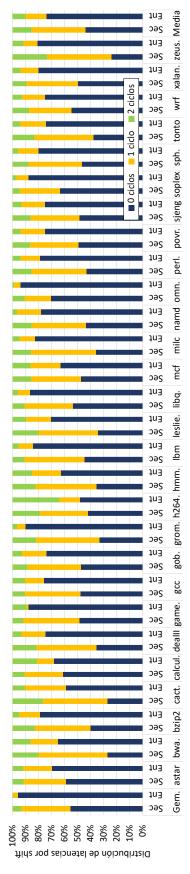

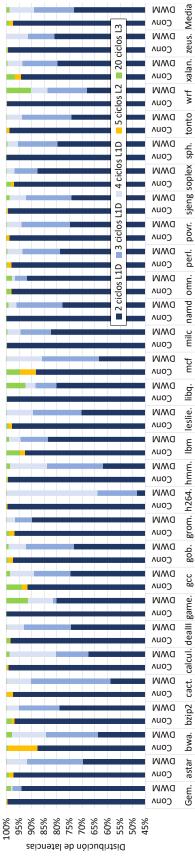

| 7.3                      | Distribución de la latencia de los aciertos en la jerarquía de cache (L1, L2 o L3) para los subsistemas de memoria convencional y el propuesto con tecnología DWM. Los accesos a la memoria principal (no mostrados) representan de media menos del 1 %; sólo 3 de los 29 benchmarks superan el 4 %                                                               | 47                              |

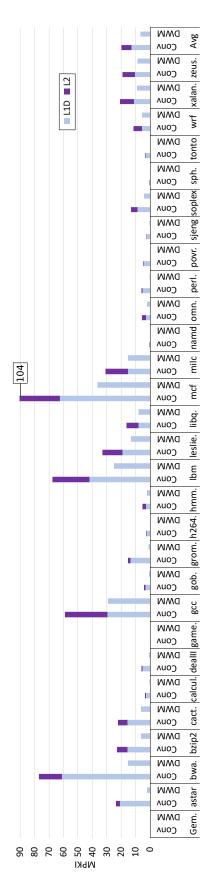

| 7.4                      | Fallos por kilo-instruction (MPKI) en los enfoques convencional y propuesto DWM. El esquema convencional distingue entre MPKI en la cache                                                                                                                                                                                                                         | 1,                              |

|                          | de datos I 1 v en la cache I 2                                                                                                                                                                                                                                                                                                                                    | 48                              |

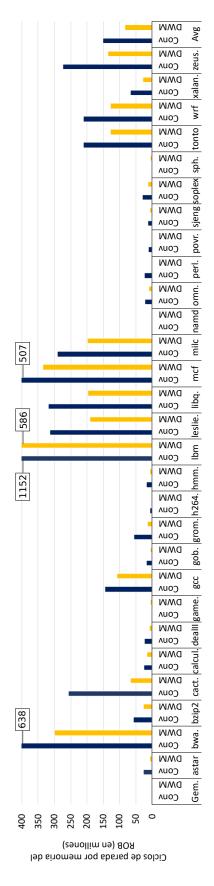

| 7.5 | Millones de ciclos de parada del ROB para los enfoques convencional y  |    |

|-----|------------------------------------------------------------------------|----|

|     | DWM                                                                    | 49 |

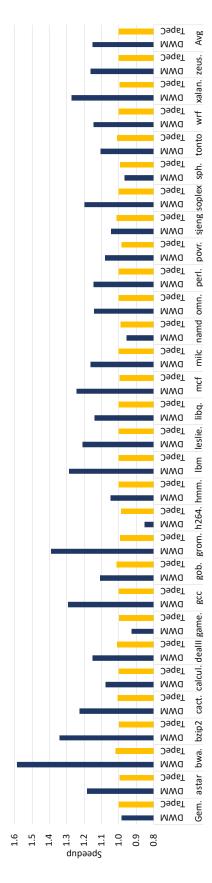

| 7.6 | Aceleración del diseño de caché DWM propuesto y del TapeCache con res- |    |

|     | pecto al enfoque convencional (cuanto más alto, mejor)                 | 50 |

|     |                                                                        |    |

## Índice de tablas

| 2.1        | Comparativa entre diferentes tecnologías de memoria                                                                                                                                       | 12       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1<br>3.2 | Tabla con las diferentes operaciones en una celda DWM                                                                                                                                     | 15<br>16 |

| 6.1        | Características principales de los nodos de Eri1                                                                                                                                          | 39       |

| 7.1        | Parámetros principales del procesador modelado donde se detallan las jerarquías de memoria y que corresponden a la mem-configuration (archivo de configuración de memoria) del simulador. | 43       |

| 7.2        | 1                                                                                                                                                                                         |          |

|            | las aplicaciones, correspondiente a la cpu-configuration (archivo de confi-                                                                                                               |          |

|            | guración del procesador) del simulador                                                                                                                                                    | 43       |

## CAPÍTULO 1 Introducción

Este primer capítulo introduce al lector el contexto, motivación, objetivos, metodología y tareas principales que componen el presente trabajo, así como una descripción de la estructura general de la memoria.

#### 1.1 Contexto y Motivación

« Al principio la Ley de Moore era sólo una observación, un intento de predecir el abaratamiento de la electrónica... pero la industria lo convirtió en una profecía auto cumplida. Ahora, las hojas de ruta de la industria se basan en ese ritmo continuo de mejora, varios nodos tecnológicos aparecen regularmente para mantenernos en esa curva, por lo que todos los participantes en el negocio reconocen que si no se mueven rápido se quedan atrás en la tecnología, por lo que esencialmente de ser sólo una medida de lo que ha sucedido, se ha convertido en un conductor de lo que va a suceder.». Esta cita se atribuye a Gordon Moore en una entrevista para la Universidad de Stanford [2].

La industria de los semiconductores se esfuerza por mantener vigente la Ley de Moore año tras año. Pese a ello, se está alcanzando el límite físico de miniaturización del transistor. Es por esta razón que la industria se encuentra en una pugna constante por ofrecer nuevas tecnologías y mejoras en el diseño del procesador que permitan seguir aumentando la capacidad de cómputo y almacenamiento de estos dispositivos.

En los procesadores comerciales actuales, el subsistema de memoria es una estructura clave para el rendimiento del procesador, puesto que reduce la diferencia de velocidad entre los núcleos del procesador y la memoria principal. Además, el subsistema de memoria ocupa la mayor parte del área del procesador [3]. Normalmente, la jerarquía de memoria se organiza en al menos tres niveles. Estos niveles se organizan de menor a mayor capacidad de almacenamiento, debido a la relación inversa entre la capacidad de una cache y su tiempo de acceso en ciclos de procesador.

Las caches de primer nivel (L1) deben ser lo suficientemente pequeñas como para estar contenidas en una etapa del pipeline del procesador y cumplir con sus restricciones temporales. Para implementar las caches L1, se utiliza tradicionalmente la tecnología de memoria estática de acceso aleatorio (SRAM). Esta tecnología limita la capacidad de almacenamiento en L1 a unas decenas de KB para cumplir con estas restricciones. Por el contrario, las caches L2 se diseñan con una mayor capacidad, del orden de centenas de KB, aunque lo suficientemente pequeñas como para ocultar la latencia de la ejecución fuera de orden. Por último, las caches L3 tienen una mayor capacidad, del orden de unidades o decenas de MB, para evitar los costosos accesos a la memoria principal fuera del chip.

2 Introducción

Teniendo en cuenta las características de cada nivel de la jerarquía de memoria y debido a los problemas intrínsecos de SRAM, están surgiendo nuevas tecnologías que permiten suplir las carencias de SRAM. Una de las tecnologías recientes más destacada es *Domain Wall Memory* (DWM). Frente a SRAM, esta tecnología ofrece un consumo estático prácticamente nulo, un consumo dinámico muy bajo y una densidad de almacenamiento mucho mayor. Su funcionamiento se basa en una cinta magnetizada de nanocables donde se sitúan los bits en forma de dominios magnéticos. Para acceder a esta información, la cinta incluye unos cabezales especiales, hacia los que se desplaza la información para acceder a ella. Este desplazamiento de la información sobre la cinta hasta que se sitúa debajo de un cabezal supone un tiempo de acceso variable a los datos. Debido a esta problemática, algunos trabajos se han centrado en implementar esta tecnología en los niveles L2 y L3, menos sensibles al tiempo de acceso [4, 5, 6].

El presente trabajo propone el uso de la tecnología DWM para implementar una cache de datos L1 que agrupe en un único nivel una cache L2 y la propia cache de datos L1 (L1D). Teniendo en cuenta la mayor densidad de DWM respecto a SRAM, es posible implementar una cache con la misma capacidad que la suma de capacidades de memoria de L1D y L2, pero aún así ocupando menos área. De esta manera se consigue, además de un ahorro de área en el procesador, reducir el tiempo de acceso a los datos en L2 en número de ciclos respecto a una L2 convencional implementada con SRAM. El diseño de cache que se propone en el presente trabajo explota políticas de desplazamiento de los datos del estado-del-arte conjuntamente con una propuesta novedosa de arquitectura y organización de la cache.

Pese a que el presente trabajo centra la línea de investigación en procesadores mononúcleo con un solo *thread* (hilo), cabe destacar que en procesadores multihilo simultáneos (SMT), cada núcleo tiene varios hilos que comparten la cache L1, por lo que, con la solución propuesta, a cada hilo se le podría asignar más capacidad de almacenamiento y reducir el efecto de *cache thrashing* [7]. Esta línea de trabajo se abordará en el futuro y queda fuera del alcance del presente proyecto.

Este trabajo se encuentra dentro del marco de investigación sobre arquitecturas del computador que existe desde hace varios años en el Grupo de Arquitecturas Paralelas (GAP) del Departamento de Informática de Sistemas y Computadores (DISCA) de la *Universitat Politècnica de València*. Nótese que este trabajo supone la continuación natural de la línea de investigación comenzada en el trabajo final de grado [8], donde se propone una implementación preliminar de una arquitectura de cache DWM exclusiva para L1D y los resultados experimentales se limitan a la evaluación de la latencia por operaciones de desplazamiento. En el presente trabajo se fusionan los niveles L1D y L2, presentando un detallado diseño de cache ascendente. Para ello, resulta necesario refinar el diseño y la organización de la propuesta de cache. Además, los resultados experimentales incluyen nuevas métricas del procesador para una evaluación experimental más detallada, así como una comparativa frente a la propuesta DWM del estado-del-arte referida como TapeCache.

#### 1.2 Objetivos

En este trabajo se presentan dos objetivos principales: i) implementar una memoria cache DWM que agrupe L1D y L2 en una única memoria para aprovechar su densidad y bajo consumo energético y ii) resolver los problemas técnicos derivados de este diseño, proponiendo finalmente una arquitectura que permita superar en rendimiento a una cache SRAM convencional y a la propuesta TapeCache. Estos dos objetivos se pueden dividir a su vez en una serie de hitos. Estos hitos permiten, por un lado, clarificar el trabajo

1.3 Metodología 3

realizado; y por otro, establecer y planificar una serie de metas concretas como parte del desarrollo de este proyecto.

Los hitos en los cuales se divide el primer objetivo, ordenados de manera cronológica, son los siguientes:

- Instrumentar un simulador ciclo-a-ciclo para modelar memorias basadas en tecnología DWM.

- Implementar la política de desplazamiento del estado-del-arte que mejores resultados en cuanto a rendimiento del sistema ha demostrado (*Dynamic Lazy*).

- Diseñar e implementar una propuesta de distribución entrelazada de conjuntos que permita aprovechar la localidad espacial de los datos.

- Desarrollar una arquitectura de memoria cache que permita aprovechar las virtudes de la tecnología DWM.

A su vez, los hitos en los que se desglosa el segundo objetivo son los siguientes:

- Implementar la arquitectura de cache del estado-del-arte TapeCache [4], con el fin de presentar una evaluación cuantitativa de rendimiento frente a la propuesta del presente trabajo.

- Cuantificar las mejoras conseguidas confrontando la propuesta de este trabajo con un diseño convencional de memoria cache SRAM.

- Evaluar la mejora de la propuesta en base al análisis de diferentes métricas relativas al rendimiento y específicas de la arquitectura de los computadores.

#### 1.3 Metodología

El proyecto emplea una metodología de trabajo basada fundamentalmente en el uso del simulador ciclo-a-ciclo Multi2Sim [9]. Este simulador ofrece soporte a diversas arquitecturas, entre ellas la arquitectura x86. Una vez configurado e instrumentado según las especificaciones de diseño, es posible lanzar experimentos, para luego realizar un análisis de los resultados arrojados por el simulador y refinar la implementación en iteraciones sucesivas. Teniendo esto en cuenta, podemos organizar el presente trabajo en diversas fases o tareas, que corresponderán a los experimentos realizados:

- Modelado del sistema a simular. Este paso consiste en conocer con detalle la arquitectura y el sistema con el que se va a trabajar para introducir sus parámetros mediante los ficheros de configuración que ofrece Multi2Sim.

- Instrumentación del código fuente del simulador y mantenimiento en un repositorio. Resultará indispensable modificar el simulador para modelar las características que Multi2Sim no ofrece en soporte nativo, principalmente, el uso de la tecnología DWM. Dada la naturaleza compleja del simulador, realizar estas modificaciones ha supuesto una dificultad añadida durante el desarrollo del proyecto.

- Lanzamiento masivo de simulaciones. El lanzamiento de las cargas de trabajo se realizará en un clúster de computadores real. En este sentido, resultarán necesarios conocimientos de Shell, Bash y *scripts* para mantener un entorno de simulación y gestionar una cola de trabajos.

$oldsymbol{4}$  Introducción

• Extracción y tratamiento automático de los datos. Los datos relevantes del resultado de la simulación se deben extraer y tratar mediante el desarrollo de una serie de *scripts* con el objetivo de obtener gráficas comparativas y tablas que permitan visualizar de forma sencilla los resultados. A partir de las tablas y las gráficas se obtendrán las conclusiones sobre los experimentos realizados.

En resumen, para la realización de este trabajo ha sido necesario lidiar con varios problemas que han supuesto un plus de dificultad: i) la complejidad del simulador, cuyo periodo de aprendizaje requiere consultar ampliamente la documentación y el propio código fuente, ii) la gran cantidad de datos volcados por Multi2Sim al acabar cada simulación, que obliga a realizar *scripts* que seleccionen los datos de manera específica, teniendo así que aprender también cómo tratar de forma automatizada grandes volúmenes de datos y iii) realizar los experimentos en un clúster compartido por varios usuarios, lo que obliga al uso de colas de procesos. A pesar de las dificultades expuestas, se han alcanzado los objetivos planteados en el inicio de este trabajo, cuyos resultados y conclusiones más relevantes se presentan en los capítulos finales del mismo.

#### 1.4 Estructura de la Memoria

Sin contar con la presente introducción, el resto de la memoria se organiza en siete capítulos, resumidos a continuación:

- Capítulo 2, Tecnologías de Memoria: exposición de los conocimientos necesarios para el completo entendimiento del proyecto, incluyendo referencias al estado-delarte conforme se detallan las diferentes tecnologías.

- Capítulo 3, Antecedentes: en este capítulo se comentan las aportaciones de otros artículos a la propuesta original de cache DWM así como unaa justificación de la elección de los mismos.

- Capítulo 4, Implementación de DWM Fusionando L1 y L2: se detalla la propuesta de diseño desglosada en las partes que la componen mediante un diseño de cache ascendente.

- Capítulo 5, Diseños de Cache DWM del Estado-del-Arte: este capítulo describe, entre otras, la arquitectura TapeCache, mostrando sus ventajas e inconvenientes. También se detallan los mecanismos que este diseño utiliza para reducir la penalización por desplazamiento de los datos.

- Capítulo 6, Entorno Experimental: se recoge el entorno experimental sobre el cual se valida la propuesta y se obtienen los resultados de este trabajo, incluyendo un simulador de procesadores, cargas de evaluación, depuradores e infraestructura de lanzamiento de simulaciones, entre otras consideraciones.

- Capítulo 7, Resultados Experimentales y Discusión: se muestran y discuten los resultados experimentales. En primer lugar se abordan las características principales del procesador modelado, para a continuación presentar resultados con la distribución de latencia, fallos por kilo-instrucción, ciclos de parada del ROB y el rendimiento de los sistemas de memoria analizados.

- Capítulo 8, Conclusiones y Trabajo Futuro: este capítulo expone una reflexión acerca de cómo las asignaturas del Máster en Arquitectura de Computadores y Redes han posibilitado la elaboración del trabajo, las conclusiones principales y qué

lineas de investigación resultaría interesante explorar en el futuro a partir de los resultados obtenidos.

• Apéndice A, Scripts de Tratamiento de Datos: en este anexo se presentan los *scripts* elaborados con el objetivo de automatizar la extracción de datos. Es importante remarcar que este anexo se encuentra fuera del presente documento, pero se adjunta en el apartado Anexos de la aplicación de gestión de TFM.

#### CAPÍTULO 2

## Tecnologías de Memoria

Las memorias cache son un componente de diseño esencial en los procesadores actuales puesto que permiten ocultar las diferencias de velocidad entre el procesador y la memoria principal. Este capítulo describe las tecnologías utilizadas actualmente en el diseño y fabricación de memorias cache, así como sus características principales.

#### 2.1 Static Random Access Memory

La tecnología *Static Random Access Memory* (SRAM) se ha empleado tradicionalmente para implementar las estructuras de memoria de los procesadores, incluyendo la jerarquía de memoria cache, el banco de registros o las estaciones de reserva, entre otras. Este hecho se debe principalmente a que se trata de la tecnología que ofrece una mayor velocidad de acceso. Esta velocidad de acceso se consigue implementando cada celda de memoria SRAM con hasta 6 transistores (celdas 6T). Debido al gran número de transistores por celda, los dos grandes inconvenientes de la tecnología SRAM son su su baja densidad de integración y su alto consumo energético estático derivado del consumo estático provocado por el biestable y las corrientes de fuga de los transistores. Además, este tipo de consumo tiende a aumentar en sucesivos nodos tecnológicos más pequeños puesto que es proporcional al número de transistores por unidad de superficie. Por estos motivos, y puesto que el tamaño de la jerarquía de memoria aumenta en sucesivas generaciones de procesador, la jerarquía de memoria supone un porcentaje elevado del área y del consumo de los procesadores actuales.

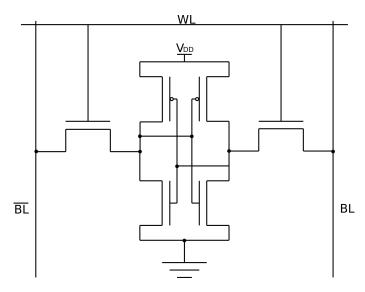

La Figura 2.1 muestra la implementación de una celda 6T. Los cuatro transistores centrales implementan un bucle de inversores que permite almacenar un valor lógico '0' o '1'. El resto de transistores de paso se controlan mediante la señal *wordline* (WL), permitiendo operaciones de lectura y escritura en la celda a través de las señales *bitline* (BL) y su complementaria ( $\overline{BL}$ ). Finalmente,  $V_{dd}$  corresponde al punto de suministro de corriente de la celda. Por ejemplo,  $V_{dd}$  adopta una tensión nominal de 0,7 V en nodos de TSMC de 10 y 7 nanómetros [10].

#### 2.2 Embedded Dynamic RAM

La tecnología *embedded Dynamic* RAM (eDRAM) compatible con CMOS apareció hace algo más de una década como alternativa a SRAM debido a la problemática asociada con las mismas [11]. A diferencia de las celdas SRAM, las celdas eDRAM se implementan utilizando un condensador y un transistor de paso (celdas 1T1C). Este diseño permite que el consumo estático sea mucho menor y el área en torno a 8 veces menor que SRAM, a

Figura 2.1: Esquema de una celda de memoria 6T SRAM.

costa de una velocidad de acceso no tan elevada frente a SRAM. Además, debido a que los valores lógicos en una celda eDRAM se almacenan como carga en el condensador, el valor lógico almacenado no se puede obtener pasado un periodo de tiempo al cual nos referimos como tiempo de retención. En este sentido, son necesarias operaciones de refresco periódicas y frecuentes que permitan retener el valor almacenado. Las operaciones de refresco compiten con los accesos regulares a la cache por parte del procesador, lo cual puede conllevar no sólo a un consumo de energía adicional sino también a una degradación severa de las prestaciones del sistema. Además, las lecturas en las celdas eDRAM son destructivas, es decir, por cada lectura se precisa de una escritura posterior para mantener el valor lógico almacenado.

Por todos los motivos anteriores, el uso de la tecnología eDRAM en procesadores comerciales se ha restringido al último nivel de cache (L3), donde a diferencia de L1, el tiempo de acceso no tiene un impacto directo sobre las prestaciones del sistema. Dos ejemplos de estos procesadores son IBM POWER [12] e Intel Haswell [13]. Por otro lado, algunos trabajos académicos han propuesto el uso de celdas eDRAM en caches L1, realizando modificaciones en el diseño de la celda 1T1C original para disminuir el impacto en el tiempo de acceso y reducir o eliminar por completo la necesidad de operaciones de refresco [14, 15, 16, 17].

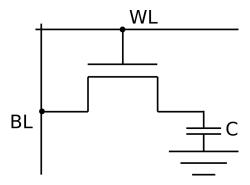

La Figura 2.2 muestra la implementación de una celda 1T1C. La presencia o ausencia de carga en el condensador etiquetado como C se corresponde con un '1' o '0' lógico almacenado, respectivamente. De manera similar al diseño de celda 6T, la señal WL permite realizar operaciones de lectura y escritura a través del transistor de paso y la señal BL.

#### 2.3 Non-Volatile Memory

Las tecnologías *Non-Volatile Memory* (NVM) como la memoria Flash, *Phase Change* RAM (PCRAM), *Resistive* RAM (ReRAM), *Spin-Transfer Torque* RAM (STT-RAM) o *Domain Wall Memory* (DWM) ofrecen múltiples beneficios como una muy alta densidad, consumo estático nulo y la habilidad de retener los valores lógicos almacenados durante largos periodos de tiempo, eliminando la necesidad de operaciones de refresco cómo ocurre con la tecnología eDRAM. Entre estas tecnologías, destacan STT-RAM y DWM

Figura 2.2: Esquema de una celda de memoria 1T1C eDRAM.

por su compatibilidad con CMOS, su resistencia y sus tiempos de lectura competitivos en comparación con los de la tecnología SRAM.

#### 2.3.1. Spin-Transfer Torque RAM

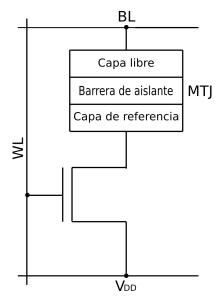

La Figura 2.3 ilustra el diseño de una celda de memoria STT-RAM. Estas celdas están compuestas por un elemento *Magnetic Tunnel Junction* (MTJ) y un transistor de paso. El MTJ es el dispositivo de almacenamiento de la celda. Consiste en dos capas ferromagnéticas (capa libre y de referencia) separadas por una barrera aislante ultra-fina de óxido de magnesio. La orientación magnética de la capa libre (paralela o anti-paralela respecto a la capa con orientación fija de referencia) define el valor lógico almacenado [18].

Figura 2.3: Esquema de una celda de memoria STT-RAM.

Comparada con SRAM, la tecnología STT-RAM adolece de un tiempo de acceso lento y un consumo dinámico elevado durante las operaciones de escritura. Debido a esta problemática, gran parte de las investigaciones relacionadas con esta tecnología se han centrado en la cache de último nivel, donde la mayoría de las operaciones de escritura son filtradas por los niveles de cache anteriores [19, 20, 21, 18, 22, 23]. Otras líneas de investigación han empleado STT-RAM en propuestas de diseño de cache L1. Estos diseños disminuyen el tiempo de retención de las celdas STT-RAM, lo cual alivia las ineficiencias de las operaciones de escritura a expensas de incorporar operaciones de re-

fresco [24, 25, 26], o proponen diseños de cache híbrida SRAM/STT-RAM, cuya porción SRAM limita la alta densidad y bajo consumo estático de STT-RAM [27, 28].

#### 2.3.2. Domain Wall Memory

Domain Wall Memory (DWM) es una tecnología NVM emergente que ha atraído un amplio interés debido a su altísima densidad y eficiencia energética respecto a las anteriores tecnologías NVM. Al contrario que STT-RAM, la tecnología DWM, también conocida como Racetrack Memory (RTM), permite compartir los costosos puertos de acceso o cabezales (una capa del MTJ y un transistor de paso) con múltiples bits de memoria. Esto se logra mediante el uso de una fina banda magnética de nanocables, conocida como racetrack o cinta, y dividida en sucesivos dominios. Un dominio consiste en un campo magnético polarizado en torno a un átomo o un grupo de átomos. Cada dominio representa un bit de información, donde la dirección de magnetización determina el estado binario almacenado. Para poder acceder a ellos, los dominios se desplazan en un sentido u otro de la cinta aplicando una corriente a lo largo de la misma, alineándose debajo de un cabezal, el cual se mantiene estático, y formando un MTJ. Cabe destacar que, cuando no se requiere de una operación de desplazamiento para acceder a la dirección solicitada (los datos requeridos se encuentran debajo del cabezal), el tiempo de acceso de DWM es comparable con el de SRAM. Al integrar múltiples bits en un nanocable, la tecnología DWM ofrece una densidad de almacenamiento aproximadamente 12 y 28 veces más alta en comparación con STT-RAM y SRAM, respectivamente [29].

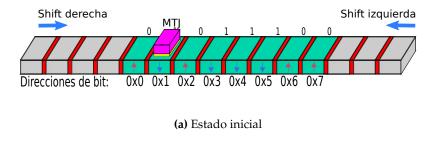

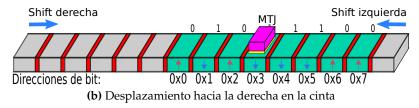

La Figura 2.4 muestra un esquema con el desplazamiento de los dominios sobre una cinta. Las flechas rojas y azules en cada dominio representan la polarización, es decir, el valor lógico almacenado. El estado inicial (mostrado en la Figura 2.4a) sitúa el dominio correspondiente en la dirección de memoria 0x1 debajo del cabezal. Supongamos que deseamos acceder a la dirección 0x3 (Figura 2.4b). El desplazamiento necesario para llevar a cabo este acceso se produce desplazamdo previamente la cinta en dos dominios hacia la derecha. Normalmente, cada desplazamiento de un dominio tiene una penalización temporal de un ciclo de procesador [5]. En definitiva, el mecanismo de desplazamiento, ya sea hacia la izquierda o derecha, se implementa mediante una serie de transistores que permiten mediante pulsos desplazar los dominios sobre la cinta hasta que el dominio en cuestión se posiciona debajo del cabezal.

Respecto a la forma en que se realiza la lectura/escritura, depende del método de que elijamos para realizar estas operaciones, ya que existen diversas formas de hacerlo atendiendo a la literatura existente. Es por ello que en el Capítulo 3 se discute y elije la forma de lectura y escritura que se adopta en este trabajo, ya que no se trata de una decisión trivial.

Como se aprecia en la Figura 2.4, el desplazamiento de los bits sobre la cinta requiere dominios adicionales, los cuales no forman parte de la capacidad de almacenamiento en bits, para que el desplazamiento no sea destructivo. De no disponer de estos dominios adicionales, los bits podrían perderse en los extremos de la cinta al realizar desplazamientos. Estos dominios adicionales se muestran en color gris. Al desplazarse por la cinta, los bits ocupan progresivamente los dominios adicionales sin perderse por los extremos. La necesidad de estos dominios implica que una cinta de 16 dominios sólo pueda almacenar 8 bits. Generalizando, se necesita una cinta con una capacidad de 2N dominios para almacenar N bits.

La Figura 2.5 muestra la implementación física de una cinta. Las formas triangulares oscuras que se pueden observar en las cintas de la Figura 2.5a son los dominios. En este ejemplo, el color oscuro de los dominios indica una polarización anti-horaria, lo cual se

2.4 Comparativa 11

Figura 2.4: Esquema con el desplazamiento de dominios sobre una cinta.

Figura 2.5: Vista de dominios sobre una cinta [1].

interpreta como un '1' lógico. Por el contrario, la Figura 2.5b muestra varios dominios con un color claro, polarizados en sentido horario, lo cual se interpreta como un '0' lógico. La Figura 2.5c muestra cómo se desplazan los dominios sobre la cinta. Concretamente, se puede apreciar el desplazamiento de un '1' lógico hacia el extremo derecho de la cinta, para luego retornar hasta la posición inicial. En la parte superior de esta figura vemos un pequeño dibujo esquemático del inyector de pulsos responsable del desplazamiento de los bits sobre la cinta. Finalmente, en la Figura 2.5d se observa la progresión de posiciones en la cinta para ambos valores lógicos '0' y '1'.

| Tecnología | Velocidad | Densidad | Consumo<br>estático | Consumo<br>dinámico | Lectura<br>destructiva | Refresco |

|------------|-----------|----------|---------------------|---------------------|------------------------|----------|

| SRAM       | Alta      | Baja     | Alto                | Medio               | No                     | No       |

| DRAM       | Baja      | Alta     | Bajo                | Medio               | Sí                     | Sí       |

| STT-RAM    | Media     | Alta     | Nulo                | Alto                | No                     | No       |

| DWM        | Variable  | Muy alta | Nulo                | Bajo                | No                     | No       |

Tabla 2.1: Comparativa entre diferentes tecnologías de memoria.

#### 2.4 Comparativa

Como se ha comentado en las secciones anteriores, cada tecnología de memoria presenta sus ventajas e inconvenientes. La Tabla 2.1 resume las características principales de cada una de ellas.

Las tecnologías alternativas a SRAM ofrecen en mayor o menor medida una reducción del consumo estático, así como una mayor densidad de integración. Entre las tecnologías de memoria discutidas, DWM ofrece por diseño un consumo estático nulo, un consumo dinámico bajo y una muy alta densidad. Esto se consigue compartiendo los cabezales entre distintos dominios en una cinta. De hecho, el número de transistores en una memoria DWM no depende tanto de la capacidad de almacenamiento en número de bits sino del número de cabezales por cinta y del número de cintas en la memoria, asumiendo que cada cinta tiene asociado un mecanismo independiente para realizar operaciones de desplazamiento.

El principal inconveniente de las tecnologías alternativas a SRAM es su reducción de velocidad en el acceso a los datos. En el caso de DWM, el tiempo de acceso a los datos es variable y depende de la posición de los cabezales con respecto a los datos solicitados. Por esta razón, resulta necesario explorar organizaciones de cache y políticas de desplazamiento de los bits que reduzcan el impacto del tiempo de acceso variable.

# CAPÍTULO 3 Antecedentes

La cache que se propone en el presente trabajo tiene como objetivo integrarse en el primer nivel de cache de datos (L1D). Esto implica que esta memoria debe tener una características específicas como son ocupar un área suficientemente pequeña para integrarse en el pipeline del procesador y reducir el tiempo de acceso a un rango adecuado para este nivel de cache (e.g., 1-3 ciclos). También es necesario resolver problemas específicos de esta tecnología, como la necesidad de 2N dominios para almacenar N bits, lo que perjudica la densidad de la propuesta. Además, resulta necesario elegir entre diferentes propuestas de lectura y escritura para esta tecnología, ya que cada una presenta unas características asociadas.

El presente capítulo detalla algunas aportaciones de otros artículos a este trabajo para adecuar el uso de la tecnología DWM en L1D.

#### 3.1 MTJ de Lectura/Escritura

Las operaciones de lectura y escritura en la tecnología DWM se pueden realizar de manera sencilla a través de un MTJ. Esta sección detalla cuales son los componentes principales que intervienen en estas operaciones y sus inconvenientes, en particular en las operaciones de escritura.

La lectura del valor lógico almacenado en un dominio se realiza midiendo la magnetorresistencia del túnel del MTJ, que cambia según la dirección de magnetización del dominio. Esto permite distinguir entre '0' y '1', utilizando para ello un circuito que actúe como sense amplifier¹, según la resistencia variable en el MTJ [30]. De esta forma, es posible realizar una lectura del bit situado debajo del MTJ en un único ciclo de reloj y con un circuito relativamente sencillo, lo que permite ahorrar área. Es por estas razones que este método de lectura se mantendrá en todo el trabajo.

En cuanto al método de escritura mediante MTJ, consiste en hacer pasar una gran cantidad de corriente a través del MTJ con el objetivo de cambiar la polarización de la capa libre sobre el que se encuentra. Esta forma de escritura presenta dos problemas principales: por una parte una latencia alta, ya que requiere sostener una gran cantidad de corriente durante varios ciclos y por otra, un gran coste energético derivado de la necesidad de esta gran cantidad de corriente [24, 25, 26].

<sup>&</sup>lt;sup>1</sup>Circuito electrónico que permite ampliar la corriente de un circuito a valores concretos a partir de rangos de voltaje fijados previamente.

14 Antecedentes

Figura 3.1: Cinta DWM con dos dominios de escritura prefijados a los valores '0' y '1'.

**Figura 3.2:** Cinta magnética con representación de la electrónica necesaria para acceder a los bits contenidos.

#### 3.2 Escritura Mediante Shift

La escritura mediante shift constituye una alternativa frente a la escritura tradicional mediante un MTJ. Esta alternativa resulta más eficiente en términos de rendimiento y consumo energético. Esta sección detalla el funcionamiento de la escritura mediante shift a partir de la organización de cinta DWM mostrada en la Figura 2.4 del capítulo anterior.

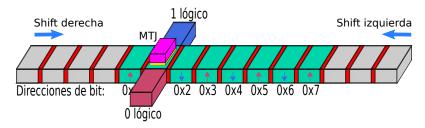

La Figura 3.1 muestra los componentes necesarios añadidos al diseño de cinta DWM para poder realizar escrituras mediante shift. El diseño añade a la cinta dos dominios a los lados del MTJ. Estos dominios tienen una polarización fija. Esta polarización está representada en la imagen en rojo el '0' lógico y en azul el '1' lógico. La escritura se realiza mediante un desplazamiento de los valores lógicos fijos en estos dominios laterales hacia el dominio debajo del MTJ. De esta manera se consigue escribir un '0' o un '1' en un sólo ciclo de reloj (que es lo que cuesta a nivel temporal un shift). Nótese que como la polarización magnética de los dominios laterales es fija, se consigue escribir en el dominio debajo del MTJ sin perder la polarización de los dominios laterales.

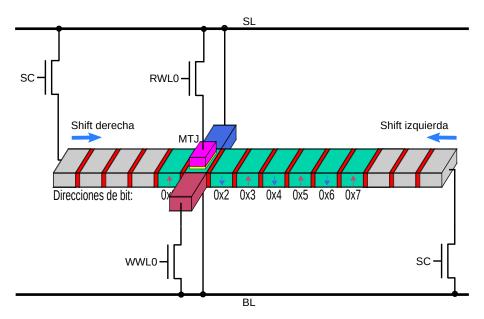

La Figura 3.2 muestra la electrónica necesaria para realizar las operaciones de lectura mediante MTJ y de escritura mediante shift. El MTJ puede proporcionar acceso de lectura a diferentes dominios en la misma cinta y está conectado a su correspondiente transistor de paso accionado por la línea de palabra (RWL0), formando un puerto de acceso. Obsérvese que el número máximo de impulsos de corriente necesarios para colocar cualquier

| Operación       | RWL0     | WWL0     | SC       | BL       | SL                  |

|-----------------|----------|----------|----------|----------|---------------------|

| Lectura         | $V_{dd}$ | Gnd      | Gnd      | Gnd      | $\overline{V_{dd}}$ |

| Escribir '0'    | Gnd      | $V_{dd}$ | Gnd      | $V_{dd}$ | Gnd                 |

| Escribir '1'    | Gnd      | $V_{dd}$ | Gnd      | Gnd      | $V_{dd}$            |

| Shift derecha   | Gnd      | Gnd      | $V_{dd}$ | $V_{dd}$ | Gnd                 |

| Shift izquierda | Gnd      | Gnd      | $V_{dd}$ | Gnd      | $V_{dd}$            |

| Inactividad     | Gnd      | Gnd      | Gnd      | X        | X                   |

Tabla 3.1: Tabla con las diferentes operaciones en una celda DWM.

dominio bajo el MTJ es en este caso es 7. Considerando que el MTJ está situado sobre 0x1, serían necesarios 6 ciclos para acceder a 0x7.

Para la lectura, se proporciona un pulso a nivel alto en la línea RWL0 consiguiendo con esto que la corriente pueda transitar desde BL hacia SL, pasando por el MTJ. A su vez, se transmite corriente desde BL a SL. Cuando la corriente pasa a través del MTJ este ofrece una resistencia que varia en función de la dirección en que esté magnetizado el dominio, consiguiendo de esta forma distinguir entre un '0' y un '1'. Una vez esta corriente circula por BL, se conecta a un sense amplifier, como se ha comentado anteriormente, que permite conocer si se trata de un '0' o un '1' lógico.

La escritura se realiza de forma diferente según se requiere almacenar un '1' o un '0'. Para escribir un '1' en el dominio sobre el que está el MTJ, SL se conecta a  $V_{dd}$  y BL se conecta a tierra (Gnd) para hacer pasar una corriente de SL hacia BL, lo que provocará un desplazamiento vertical hacia abajo, desplazando el '1' del dominio fijo al dominio libre. De esta manera la corriente circula desde SL hacia BL, y si el transistor WWL0 que actúa como interruptor recibe  $V_{dd}$ , se consigue un shift de la polarización magnética presente en el dominio azul al dominio sobre el que se sitúa el MTJ. De esta manera, se escribe de manera efectiva un '1' lógico en un sólo ciclo (el ciclo necesario para realizar el shift).

La escritura de un '0' lógico ocurre de manera similar, pero en sentido contrario. De nuevo, la señal WWL0 se conecta a  $V_{dd}$  para que el transistor de paso conduzca, actuando como interruptor cerrado, dejando pasar corriente. Esta vez se persigue que la corriente circule desde BL hacia SL, así que BL se conecta a  $V_{dd}$  y SL se conecta a  $G_{dd}$ . De esta manera se provoca un shift del dominio en rojo hacia el dominio debajo del MTJ polarizándose igual que este, con el equivalente magnético a un '0' lógico.

Además del puerto de acceso, la celda está conectada a dos puertos de desplazamiento, que consisten en un par de transistores accionados por la línea de desplazamiento SC. Si se conecta tanto SC como BL a  $V_{dd}$  y SL a Gnd, se consigue hacer circular la corriente provocando un shift hacia la derecha. Si por el contrario, es BL la que se conecta a Gnd y SL a  $V_{dd}$ , se provoca un desplazamiento hacia la izquierda. Estas líneas permiten generar pulsos de corriente para realizar operaciones de desplazamiento en el sentido de las agujas del reloj o en sentido contrario cuando se le suministra corriente a SC, de manera que este permita que circule la corriente.

Nótese que las líneas de bits (BL) y de origen (SL) se ajustan a diferentes tensiones en función de la operación (es decir, lectura, escritura, desplazamiento en el sentido de las agujas del reloj y desplazamiento en sentido contrario a las agujas del reloj) que se va a realizar. La Tabla 3.1 resume las condiciones de tensión para todas las operaciones. Con fines visuales se muestra en rojo la conexión a tierra y en verde la tensión de alimentación. Con una X se representa indiferencia entre ambas.

16 Antecedentes

## 3.3 Comparativa entre Escritura Mediante MTJ y Mediante Shifting

Teniendo en cuenta lo expuesto en las dos secciones anteriores, la presenta sección justifica el motivo por el cual en este trabajo se elige la escritura mediante shift para implementar la propuesta. A modo de resumen se muestra la Tabla 3.2 donde se compara la forma de escritura mediante MTJ y la que utiliza shift.

|              | Latencia de escritura | Consumo | Transistores                       |

|--------------|-----------------------|---------|------------------------------------|

| Convencional | Varios ciclos         | Alto    | 4 por celda (2 shift, 4 cabezales) |

| Con shift    | 1 ciclo de reloj      | Bajo    | 6 por celda (2 shift, 4 cabezales) |

Tabla 3.2: Tabla comparativa con las dos formas de escritura en la celda DWM.

En definitiva, sacrificando un poco de área (6 transistores para realizar operaciones frente a 4) se consigue una memoria con mucha menor latencia y sin necesidad de tanto consumo dinámico. Al haber dos transistores más, el consumo estático por corrientes de fuga aumenta en la escritura mediante shift, pero este resulta insignificante comparado con el consumo dinámico de la escritura convencional. Teniendo esto en cuenta, en el resto del documento, la escritura asumida será mediante shift.

#### 3.4 Cinta en Anillo

La implementación de DWM en forma de cinta magnética tiene el inconveniente de la necesidad de dominios extra (dominios en color gris en las Figuras 3.1 y 3.2) para asegurar que la lectura de los datos no sea destructiva. Este problema implica que para poder almacenar N bits de forma efectiva son necesarios 2N dominios.

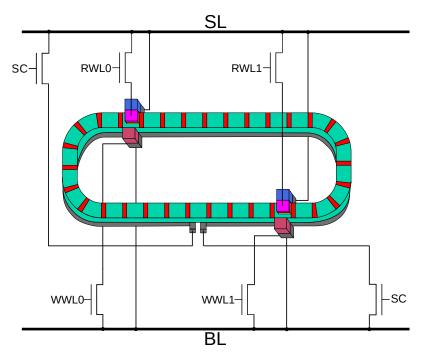

Una posible solución para el inconveniente de los dominios auxiliares es implementar las cintas magnéticas en forma de anillo [30]. Esta solución presente en varios trabajos sobre DWM permite un desplazamiento de los datos sobre los dominios sin necesidad de dominios extra. La Figura 3.3 parte de las anteriormente citadas pero añade un MTJ extra y los dominios en una estructura circular en vez de lineal. En ella se muestra una cinta en forma de anillo con 32 dominios efectivos.

Este trabajo asume la implementación de cintas circulares, ya que utilizando este diseño se consigue representar N bits con N dominios, en vez de 2N como era necesario anteriormente.

#### 3.5 Equilibrio entre Puertos y Dominios

El número de puertos de acceso (MTJ) y los dominios son dos de los principales parámetros que afectan a la latencia, la energía y el área de un diseño de cache basado en la tecnología DWM [31]. La celda DWM original en forma de anillo está adaptada a las caches de último nivel, donde se desea una alta densidad por encima de una latencia de acceso reducida en número de ciclos de desplazamiento. De esta forma, los accesos a un anillo de 128 bits se realizan a través de 4 puertos de acceso.

Por otro lado, trabajos anteriores centrados en caches L1 sacrifican la densidad DWM para eliminar por completo el requisito de desplazamiento [32, 4]. Esto se consigue con un diseño de disposición de celdas que consiste en un mismo número de dominios y puertos

Figura 3.3: Diagrama de una cinta de 32 bits con dos MTJ.

de acceso, donde cada dominio tiene un puerto de acceso dedicado, asemejándose a un diseño de STT-RAM. Este diseño se denomina celda DWM de 1 bit. A diferencia de los trabajos anteriores, en este trabajo se propone un diseño de celda DWM de varios bits que cumple los requisitos de alta densidad y latencia de acceso media reducida deseados en la cache L1.

#### 3.6 Política de Desplazamiento de Cabezales

Como ya se ha mencionado, el acceso a un bit en DWM requiere de una operación de desplazamiento previa para alinear el bit solicitado bajo un puerto MTJ. Dado que las operaciones de desplazamiento implican una latencia de acceso variable en un DWM, es imperativo minimizar el número de ciclos de desplazamiento tanto como sea posible. Para ello se han propuesto diversas políticas de desplazamiento.

Venkatesan *et al.* proponen diferentes políticas de gestión de puertos para una memoria DWM multipuerto atendiendo a dos criterios diferentes: selección de puertos y actualización de puertos [4]. La selección de puertos establece cual es el puerto adecuado para acceder a los datos solicitados. Existen dos enfoques, denominados estático y dinámico. El enfoque estático determina de antemano a qué bits se debe acceder a través de un puerto específico, mientras que el enfoque dinámico calcula el puerto más cercano en tiempo de ejecución. Por otra parte, la actualización de puertos define la posición del cabezal con respecto a los puertos tras la finalización de un acceso. Existen dos políticas, denominadas *eager* y *lazy*. La política *eager* restaura la cinta a la posición por defecto después de un acceso, mientras que la política *lazy* mantiene la última posición de la cinta hasta el siguiente acceso. Este trabajo asume una selección dinámica de puertos para minimizar el número de ciclos requeridos en una operación de desplazamiento y una actualización de puertos *lazy* para explotar la localidad espacial presente en las caches de datos L1. La sobrecarga de la lógica requerida para implementar tal política de gestión de puertos es insignificante.

18 Antecedentes

Figura 3.4: Desplazamiento de los datos para realizar una lectura utilizando DL.

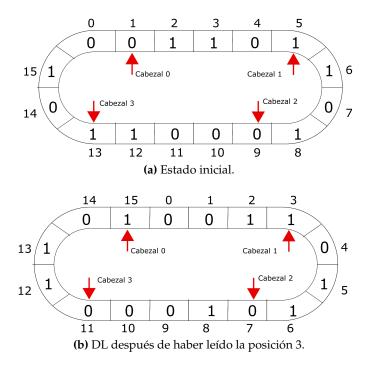

A modo de ejemplo ilustrativo del funcionamiento de la estrategia dinámica y *lazy*, también referida como *Dynamic Lazy* (DL), la Figura 3.4a muestra el estado inicial de una cinta circular simplificada de 16 bits con 4 cabezales o puertos MTJ. Considerando que se quiere acceder al dominio 3, DL elegirá el cabezal más cercano a este dominio. En este caso concreto, podrían elegirse tanto el cabezal 0 como el 1, pero como se puede observar en la Figura 3.4b se ha elegido el cabezal 1. Ante una situación como esta, este trabajo asume la elección del cabezal con mayor número identificador.

El lector puede consultar [4] para más detalles o [8] donde se ofrece una justificación teórica y experimental acerca de por qué DL es la política que más reduce la penalización por desplazamiento.

## CAPÍTULO 4 Implementación de DWM Fusionando L1 y L2

Este capítulo detalla la propuesta de cache de datos L1 fusionada con L2 y adaptada para que resulte competitiva comparada con una cache convencional SRAM. Para ello, se presenta un diseño de cache ascendente. En primer lugar, se diseña específicamente una celda DWM de múltiples bits con forma de anillo para cumplir los requisitos de alta densidad y latencia de acceso media reducida. A continuación, la celda propuesta se utilizará para implementar un módulo DWM compuesto por un número de líneas de cache de diferentes conjuntos. Además, se propondrá una organización de conjuntos para reducir aún más la penalización de la latencia por desplazamiento. Por último, el módulo propuesto se utilizará para implementar las vías y todos los conjuntos de un array de datos completo.

#### 4.1 Celda DWM Multi-Bit en Anillo

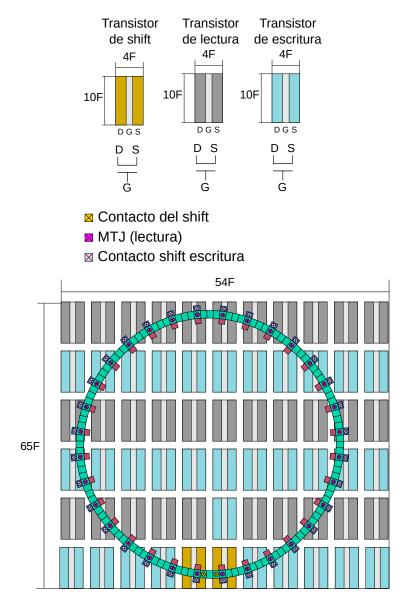

La latencia de acceso en una celda DWM está determinada por la corriente que pueden proporcionar los transistores de acceso. Se ha demostrado que un tamaño de transistor de  $10F^1$  ofrece un buen compromiso en cuanto a rendimiento y ocupación de área de la cache [33, 34]. Por otro lado, la latencia por desplazamiento está influida tanto por el número de dominios (longitud de la cinta magnética) como por el tamaño de los transistores que controlan el desplazamiento. Cintas más largas requieren más corriente para desplazar todos los dominios y, por tanto, transistores de desplazamiento más grandes. Para un tamaño de transistor de desplazamiento dado, para desplazar los datos sobre la cinta más rápidamente, esta debe ser lo más corta posible [30]. Este trabajo limita la longitud de la cinta en forma de anillo a 128 dominios para establecer transistores de desplazamiento con un tamaño de 10F y una latencia de desplazamiento dentro de un ciclo de reloj.

Para optimizar la disposición de los componentes en la celda, tanto los transistores de desplazamiento como los de acceso se sitúan bajo la cinta. El número de transistores de desplazamiento se limita a 2 para garantizar los movimientos de desplazamiento en sentido horario y antihorario. El número de transistores de acceso está determinado por el número de dominios entre dos puertos consecutivos por encima de la cinta. Este trabajo limita dicho número de dominios a 4. De este modo, se necesitan 32 puertos para una cinta de 128 dominios, lo que se traduce en 64 transistores de acceso (se necesitan dos transistores de acceso para implementar un puerto). Obsérvese también que, suponiendo

<sup>&</sup>lt;sup>1</sup>F responde a *feature size* y se refiere a la distancia mínima en nanómetros entre la fuente y el drenaje de un transistor.

Figura 4.1: Propuesta de celda de memoria DWM de 128 bits.

una gestión *Dynamic Lazy* (DL) de los puertos, una distancia de 4 dominios entre puertos sucesivos define una latencia de desplazamiento máxima de 2 ciclos para acceder al bit más lejano de un puerto.

La Figura 4.1 muestra la organización de la celda para la cache propuesta. La celda consta de  $11\times6$  transistores. Los transistores de desplazamiento están situados en la última fila de arriba a abajo. De acuerdo con el tamaño definido para los transistores y asumiendo un espacio entre transistores adyacentes de 1F, el área de la celda es de  $54F\times65F=3510F^2$ .

Partiendo de las explicaciones de la sección anterior, vamos a mostrar de forma simple la justificación de la gran densidad que presentan las DWM sobre SRAM.

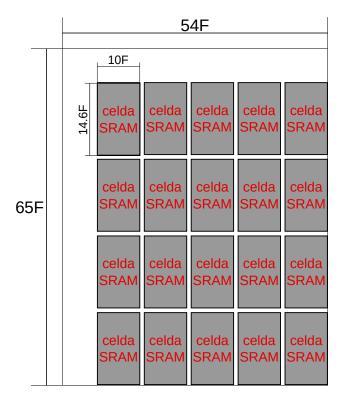

La Figura 4.2 pone de manifiesto la mayor densidad de la tecnología DWM frente a SRAM, mostrando el número de celdas SRAM que puede contener la celda DWM definida. Teniendo en cuenta que una celda SRAM 6T típica ocupa una área de  $10F \times 14$ ,  $6F = 146F^2$  [35], pueden caber hasta 20 celdas SRAM dentro del área que delimita la celda DWM. De este modo, la densidad de la celda propuesta es 6,4 veces superior a SRAM

Figura 4.2: Comparación del área ocupada por la celda DWM de 128 bits y celdas SRAM de 1 bit.

(i.e., 128/20). Por el contrario, una celda DWM de 1 bit incluiría sólo 32 bits de acuerdo con el número de puertos definido con anterioridad, lo que limitaría la densidad a 2,67x con respecto a SRAM.

Al igual que en [30], este trabajo asume una longitud de 40 nm para cada dominio y una anchura de pared de dominio (*domain wall*) de 5 nm entre dos dominios adyacentes, por lo que cada unidad de almacenamiento tiene una longitud de 45 nm. Considerando un nodo tecnológico de 40 nm, las dimensiones de altura y anchura de la celda propuesta permitirían hasta 48 y 57 dominios, respectivamente, lo que se ajustaría a una longitud ideal de cinta en forma rectangular de 210 dominios. Sin embargo, como se ha comentado anteriormente, la longitud de la cinta se limita a 128 dominios no sólo para establecer una penalización por desplazamiento de un dominio dentro de un ciclo, sino también para simplificar el direccionamiento asumiendo una potencia de 2.

#### 4.2 Organización de Módulo de Cache

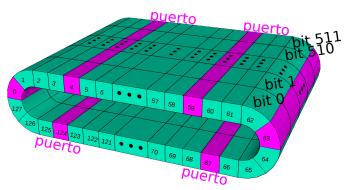

La celda DWM sirve para implementar un módulo de memoria. Suponiendo un tamaño de línea de cache de 64 B, un módulo consta de 512 celdas DWM. Las posiciones del bit *i*-ésimo de cada celda implementan la línea *i*-ésima del módulo. A su vez, la línea *i*-ésima se refiere a una línea de un conjunto con identificador *i*. De este modo, un módulo se refiere a 128 conjuntos, cada uno de los cuales consta de una sola línea de 64 B. Todos los bits que implementan una línea comparten la señal de desplazamiento (SC) y las líneas de palabra (RWL y WWL), lo cual permite desplazar todas las celdas de un módulo al mismo tiempo y acceder en paralelo a todos los bits que conforman una línea.

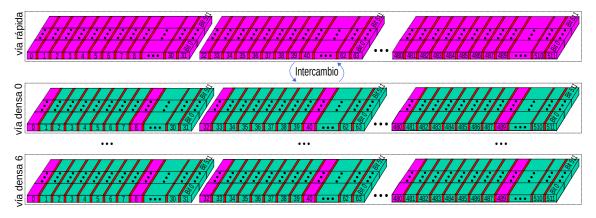

(a) Organización secuencial de los conjuntos.

(b) Organización entrelazada de los conjuntos.

**Figura 4.3:** Organización de un módulo DWM en 512 celdas. Un módulo se organiza en 128 conjuntos, cada uno de los cuales contiene una sola línea de 512 bits.

La Figura 4.3a muestra la distribución de las 512 celdas (anillos) para implementar un módulo. El número dentro de un dominio se refiere al identificador de conjunto. A efectos ilustrativos, sólo se destacan algunos conjuntos<sup>2</sup>.

En una organización de conjuntos secuencial, los conjuntos están distribuidos consecutivamente a lo largo de un anillo. De esta manera, con una distancia de 4 conjuntos entre puertos consecutivos, los conjuntos 0, 4, 8, 12, 16, y así sucesivamente, se alinean bajo un puerto, representando un estado inicial. Independientemente de la dirección de desplazamiento, se mantiene una distancia de 4 conjuntos entre puertos consecutivos.

Esta distribución de conjuntos no aprovecha la localidad espacial que presentan las caches de datos L1. Por esta razón, este trabajo propone una organización de conjuntos alternativa que coloca los conjuntos de forma intercalada en los puertos, correspondiente a la función *id conjunto* % *num. puertos*. De este modo, los conjuntos consecutivos se alinean con los puertos. La Figura 4.3b muestra un estado en el que los conjuntos de 0 a 31 están alineados con los 32 puertos. De este modo, un acceso a los conjuntos vecinos no implica ninguna operación de desplazamiento. Obsérvese que, en la estrategia propuesta, el acceso a cualquier conjunto del rango 32-63 implicaría sólo una penalización de desplazamiento de un ciclo. Tras este desplazamiento, todos los conjuntos dentro de dicho rango permanecerían alineados bajo un puerto. De esta manera se consigue explotar la localidad espacial para mejorar el tiempo de acceso a los datos.

A efectos de cuantificar la mejora de la estrategia de distribución de conjuntos entrelazada con los puertos, la Figura 4.4 muestra un desglose de la latencia de desplazamiento en número de ciclos para ambas estrategias secuencial (Sec) y propuesta (Ent). Una la-

<sup>&</sup>lt;sup>2</sup>También cabe remarcar que con propósito ilustrativo y para facilitar su visualización en una figura tridimensional, la cinta tiene forma ovalada en vez de puramente circular

**Figura 4.4:** Distribución de la latencia de desplazamiento para la organización secuencial de conjuntos (Sec) e intercalada por puertos (Ent) en una cache de datos L1 DWM de 160 KB.

tencia de 0 ciclos significa que no se requiere ninguna operación de desplazamiento, ya que el bloque solicitado se encuentra alineado bajo un puerto. Los resultados se muestran para una cache de datos L1 DWM de 160 KB donde se ejecutan todas las aplicaciones del conjunto de pruebas SPEC CPU 2006 [36]<sup>3</sup>.

Como se puede observar, al explotar la localidad espacial de los datos, la organización de conjuntos propuesta mejora en gran medida la latencia de desplazamiento respecto a la organización secuencial en todas las aplicaciones estudiadas. El porcentaje de latencia de 0 ciclos mejora especialmente en aplicaciones con una alta localidad espacial como *GemsFDTD*, *gamess*, o *gromacs*, donde dicho porcentaje supera un 80 %. En general, la organización de conjuntos propuesta evita que se produzca una operación de desplazamiento en un 76 % de los accesos a la cache. Este porcentaje se reduce a un 43 % para el enfoque secuencial. En el resto del documento se asume la organización de conjuntos entrelazados con los puertos en los módulos de DWM.

#### 4.3 Organización de Array de Datos de Cache

Un módulo compuesto por 128 conjuntos y una sola línea de 64 B por conjunto implementa un array de datos modesto consistente en 8 KB con mapeo directo. Sin embargo, la alta densidad de la tecnología DWM permite implementar una capacidad de memoria cache mucho mayor con respecto a una cache SRAM convencional en una limitación de área determinada. Esta sección explora la posibilidad de aumentar tanto el número de conjuntos como el de vías bajo la restricción de área definida por el diseño convencional de cache.

Para aumentar el número de conjuntos más allá de 128, este trabajo propone utilizar múltiples módulos DWM para implementar una cache. Cada módulo contiene un subconjunto de 128 conjuntos adyacentes de la cache. Esta distribución de conjuntos en módulos beneficia la localidad espacial, ya que las operaciones de desplazamiento sólo afectan al módulo de destino donde reside el conjunto solicitado. Esto evita que los módulos restantes realicen una operación de desplazamiento, manteniendo el mismo estado de acuerdo a su último acceso. El número total de conjuntos de cache se limita a un múltiplo de 128 para explotar todos los dominios disponibles de un módulo.

Al contrario que las caches de bajo nivel, las caches L1 asociativas por conjuntos de n vías suelen acceder en paralelo a las n etiquetas y a las n vías del conjunto de destino para reducir el tiempo de acceso. Teniendo en cuenta este comportamiento, las diferentes vías de la cache DWM propuesta están físicamente separadas en diferentes bancos implementados con diferentes módulos. Esta decisión de diseño proporciona un tiempo de acceso mínimo porque una misma operación de desplazamiento se lleva a cabo en todas las vías del conjunto de destino al mismo tiempo con la comparación de etiquetas.

De acuerdo con la mayor capacidad de almacenamiento que ofrece la tecnología DWM, este trabajo explora combinar la cache de datos L1 y la cache L2 para implementar una única cache de datos L1. Así, la cache L2 SRAM se elimina por completo de la jerarquía de memoria en chip propuesta. Bajo esta consideración, se exploran dos posibles estrategias de diseño denominadas iso-área e iso-capacidad.

El enfoque iso-área intenta implementar una DWM que ocupe la misma área que la cache de datos L1 original más el área de la cache L2. En este sentido, teniendo en cuenta que la densidad de la celda DWM propuesta es 6,4x con respecto a SRAM (ver Sección 4.1), se podría implementar una cache de aproximadamente 1 MB en lugar de una cache de datos L1 de 32 KB y una cache L2 de 128 KB. Sin embargo, el principal reto

<sup>&</sup>lt;sup>3</sup>Se remite al lector al Capítulo 6 para más detalles sobre el entorno experimental.

**Figura 4.5:** Diagrama de una organización de cache DWM con una capacidad de 160 KB, conjuntos de 512 bits y 5 vías. Cada conjunto se expande a 5 anillos, uno por cada vía de cache (filas). Cada columna consta de tantos módulos como vías de cache. Cada vía se expande a 4 columnas (número de conjuntos/128). En color naranja se destaca un par de conjuntos de destino.

del enfoque iso-área es mantener una velocidad de acceso rápida. Esto se debe principalmente a una mayor sobrecarga de tiempo de los circuitos periféricos en una área mucho mayor en comparación con una cache L1 convencional. Por este motivo, este trabajo deja el diseño iso-área como trabajo futuro.