## Development of advanced closed-loop brain electrophysiology systems for freely behaving rodents

Dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electronic Engineering

Author: Aarón Cuevas López

Supervisors: Prof. Dr. David Moratal Pérez

Center for Biomaterials and Tissue Engineering

Universitat Politècnica de València

Valencia, Spain

Dr. Santiago Canals Gamoneda

Instituto de Neurociencias

Consejo Superior de Investigaciones Científicas

Universidad Miguel Hernández San Juan de Alicante, Spain

November 2021

Supervisor Prof. Dr. David Moratal Pérez

Universitat Politècnica de València

Co-Supervisor Dr. Santiago Canals Gamoneda

Instituto de Neurociencias de Sant Joan - CSIC, Universidad Miguel Hernández

Members of the Jury Vicent Manuel Teruel Martí

Universitat de València

Francisco Javier García Casado Universitat Politècnica de València

Gonçalo Cardoso Lopes NeuroGEARS Ltd.

Members of the Javier Primitivo Collado Ruiz

reviewers committee Instituto de Física Corpuscular - CSIC

Universitat de València

Oscar Benito Herreras Espinosa

Instituto Cajal - Consejo Superior de Investigaciones Científicas

Vicent Manuel Teruel Martí Universitat de València

The research described in this thesis was carried out at the Polytechnic University of Valencia (Universitat Politècnica de València), Valencia, Spain in an extremely close collaboration with the Neuroscience Institute - Spanish National Research Council - Miguel Hernández University (Instituto de Neurociencias - Consejo Superior de Investigaciones Científicas - Universidad Miguel Hernández), San Juan de Alicante, Spain. The projects described in chapters 3 and 4 were developed in collaboration with, and funded by, Open Ephys, Cambridge, MA, USA and OEPS - Eléctronica e produção, unipessoal lda, Algés, Portugal.

## Acknowledgements

Quisiera comenzar agradeciendo David Moratal y Santiago Canals por confiar en mi y abrirme todas las puertas que me han llevado hasta aquí. Muchas grandes historias comienzan con un "¿y si...?" y el suyo, hace ya más de diez años, acabó llevándome al camino que ahora recorro. Este trabajo no existiría sin ellos.

I would like to sincerely thank the Open Ephys/OEPS team for all the support over the years. Josh and Jakob for starting the project and welcoming me on it. Filipe and Lídia, for founding OEPS and their help through bureaucracy. Jon, for being a fellow tech sould and our regular discussions. And Alex, for her help with wiring, her way with people and her weekly rankings.

Me gustaría también agradecer a todas la gente que me ha acompañado todos estos años. A mis amigos LEDC y asociados, Carlotes, Alejandro, Andrés, Paw, Alex, Estefi, Dani, Mayte, Marco, Natalia, Álvar, Roca, Álvaro, Marc, Víctor, Juan, Juanito, Iván y Patri. A aquellos con los que me he inmerso en mundos fantásticos, Jorge, Dani, Dimitri, Iván, Janha, Víctor, Bruji, Amaia... A la escuela Ruz Ryu por todo lo que me ha enseñado y ayudado a mejorar a muchos niveles así como a Toni, su fundador. Y a Javi, incluido en todos los grupos anteriores. Amigo, compañero de historias, aventuras y tecnologías y sensei.

También a todos los que están fuera y no veo tanto como me gustaría. Lucía, Lorena, Pau, Maripaz, Manu, Nieves, Nacho, Jorge, Xermo y Miguel Ángel. A mis amigos de la Kei Party, Iwa, Keikun, Xanko, Vero y Angelique. A

Darío, por años de compañerismo ¡Te debo un ramen! A Régel, con quien he compartido penurias telequiles y alegrías prácticamente desde que empecé la carrera. A Kelly, que me ha enseñado a ser fuerte aún en la cara de la adversidad. Y a Kitsu, que me ha aguantado durante tantísimos años.

Por último, pero no menos importante, a mi familia, que ha estado siempre a mi lado. A mis padres, a los que se lo debo todo. A mis hermanos, Aitor, Tamara y Aida, que bien sabe lo que es la carrera académica. Y en especial a mi sobrinita Atenea.

### Abstract

Extracellular electrophysiology is a technique widely used in neuroscience research. It can offer insights on how the brain works by measuring the electrical fields generated by neural activity. This is done through electrodes implanted in the brain and connected to amplification and digitization electronic circuitry. Of the many animal models used in electrophysiology experimentation, rodents such as rats and mice are among the most popular species thanks to their small size, breeding speed and strong social and exploratory behaviors.

Modern electrophysiology experiments seek increasingly complex conditions that are limited by acquisition hardware technology. Two particular aspects are of special interest: Closed-loop feedback and naturalistic behavior. In this thesis, we present developments aiming to improve on different facets of these two problems.

Closed-loop feedback encompasses all techniques in which stimuli is produced in response of an event generated by the animal. Latency, the time between trigger event and stimuli generation, must adjust to the biological timescale being studied. While modern acquisition systems feature latencies in the order of 10ms, response to fast events such as high-frequency electrical transients created by neuronal activity require latencies under 1ms. In addition, algorithms for triggering or generating closed-loop stimuli can be complex, integrating multiple inputs in real-time. Integration of algorithm development into acquisition tools becomes an important part of experiment design.

For electrophysiology experiments featuring naturalistic behavior, animals must be able to move freely in ecologically meaningful environments, mimicking natural conditions. Experiments featuring elements such as large arenaa, environmental objects or the presence of another animals are, however, hindered by the wired nature of acquisition systems. Other physical constraints, such as implant weight or power restrictions can also affect experiment time, limiting their duration. Beyond the technical limits, complex experiments are enriched when electrophysiology data is integrated with multiple sources, for example animal tracking or brain microscopy. Tools allowing mixing data independently of the source open new experimental possibilities.

The technological advances presented on this thesis addresses these topics. We have designed devices with closed-loop latencies under  $200\mu s$  while featuring high-bandwidth interfaces. These allow the simultaneous acquisition of hundreds of electrophysiological channels combined with other heterogeneous data sources, such as video or tracking. The control software for these devices was designed with flexibility in mind, allowing easy implementation of closed-loop algorithms. Open interface standards were created to encourage the development of interoperable tools for experimental data integration.

To solve wiring issues in behavioral experiments, we followed two different approaches. One was the design of light headstages, weighing less than 2 grams, coupled with ultra-thin coaxial cables and active commutator technology, making use of animal tracking. This allowed to reduce animal strain to a minimum allowing large arenas and prolonged experiments with advanced headstages featuring high channel counts and extra features.

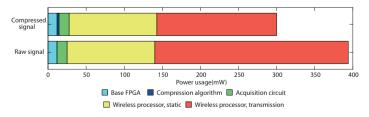

A different, wireless headstage was also developed. We created a digital compression algorithm specialized for neural electrophysiological signals able to reduce data bandwidth to less than 65.5% its original size without introducing distortions. Bandwidth has a large effect on power requirements. Thus, this reduction allows for lighter batteries and extended operational time. The algorithm is designed to be able to be implemented in a wide variety of devices, requiring low hardware resources and adding negligible power requirements to a system.

Combined together, the developments we present open new possibilities for neuroscience experiments combining electrophysiology acquisition with natural behaviors and complex, real-time, stimuli.

### Resumen

La electrofisiología extracelular es una técnica ampliamente usada en investigación neurocientífica, la cual permite estudiar el funcionamiento del cerebro mediante la medición de campos eléctricos generados por la actividad neuronal. Esto se realiza a través de electrodos implantados en el cerebro y conectados a dispositivos electrónicos para amplificación y digitalización de las señales. De los muchos modelos animales usados en experimentación electrofisiológica, las ratas y los ratones se encuentran entre las especies más comúnmente utilizadas, gracias a su pequeño tamaño, velocidad reproductiva y sus fuertes comportamientos sociales y exploratorios.

Actualmente, la experimentación electrofisiológica busca condiciones cada vez más complejas, limitadas por la tecnología de los dispositivos de adquisición. Dos aspectos son de particular interés: Realimentación de lazo cerrado y comportamiento en condiciones naturales. En esta tesis se presentan desarrollos con el objetivo de mejorar diferentes facetas de estos dos problemas.

La realimentación en lazo cerrado se refiere a todas las técnicas en las que los estímulos son producidos en respuesta a un evento generado por el animal. La latencia, el tiempo transcurrido entre el evento desencadenante y la estimulación, debe ajustarse a las escalas temporales bajo estudio. Los sistemas modernos de adquisición presentan latencias en el orden de los 10ms,. Sin embargo, para responder a eventos rápidos, como pueden ser los transitorios de alta frecuencia creados por la actividad neuronal, se requieren latencias por debajo de 1ms. Además, los algoritmos para detectar los eventos desencadenates o generar los estímulos pueden ser complejos, integrando varias entradas

de datos en tiempo real. Integrar el desarrollo de dichos algoritmos en las herramientas de adquisición forma parte del diseño de los experimentos.

Para que experimentos electrofisiológicos incluyan comportamientos naturales, los animales deben ser capaces de moverse libremente en entornos ecológicamente significativos, emulando condiciones naturales. Experimentos de este tipo, que incluyen elementos como espacios amplios, objetos en el entorno o la presencia de otros animales, se ven dificultados por la naturaleza cableada de los sistemas de adquisición. Otras restricciones físicas, como el peso de los implantes o limitaciones en el consumo de energía, pueden también afectar a la duración de los experimentos, limitándola. Más allá de los límites tecnológicos, la experimentación puede verse enriquecida cuando los datos electrofisiológicos se ven complementados con datos procedentes de múltiples fuentes distintas. Por ejemplo, seguimiento de los animales o miscroscopía. Herramientas capaces de integrar datos independientemente de su origen abren la puerta a nuevas posibilidades experimentales.

Los avances tecnológicos presentados en esta tesis abordan estas limitaciones. Se han diseñado dispositivos con latencias de lazo cerrado inferiores a  $200\mu s$ . Estos presentan además interfaces de elevado ancho de banda, lo que permite la adquisición de cientos de canales electrofisiológicos combinados con otras fuentes de datos de naturaleza heterogénea, como vídeo o seguimiento. El software de control para estos dispositivos se ha diseñado manteniendo la flexibilidad como objetivo, permitiendo una fácil implementación de algoritmos de lazo cerrado. Se han desarrollado interfaces y estándares de naturaleza abierta para incentivar el desarrollo de herramientas compatibles entre ellas, para facilitar la integración de de datos experimentales.

Para resolver los problemas de cableado en experimentos conductuales se siguieron dos métodos distintos. Uno fue el desarrollo de *headstages* ligeros, con pesos inferiores a los 2 gramos, combinados con cables coaxiales ultra finos y conmutadores activos, posibles gracias al seguimiento de animales. Este desarrollo permite reducir el esfuerzo impuesto a los animales al mínimo, permitiendo espacios amplios y experimentos de larga duración, al tiempo que permite el uso de *headstages* con elevado número de canales y características avanzadas.

Paralelamente se desarrolló un tipo diferente de headstage, con tecnología inalámbrica. Se creó un algoritmo de compresión digital especializado para señales electrofisiológicas neuronales capaz de reducir el ancho de banda a menos del 65% de su tamaño original, sin introducir distorsiones. Dado que el ancho de banda juega un papel fundamental en los requisitos energéticos, esta reducción permite baterías más ligeras y mayores tiempos de operación. El algoritmo fue diseñado para ser capaz de ser implementado en una gran variedad de dispositivos, requiriendo pocos recursos de *hardware* y una cantidad nimia de energía.

Combinados, los desarrollos presentados en esta tesis abren la puerta a nuevas posibilidades experimentales para la neurociencia, combinando adquisición elextrofisiológica con estudios conductuales en condiciones naturales y estímulos complejos en tiempo real.

## Resum

L'electrofisiologia extracel·lular és una tècnica àmpliament utilitzada en la investigació neurocientífica, aquesta tècnica permet estudiar el funcionament del cervell mitjançant el mesurament de camps elèctrics generats per l'activitat neuronal. Això es realitza a través d'elèctrodes implantats al cervell, connectats a dispositius electrònics per a l'amplificació i digitalització dels senyals. Dels molts models animals utilitzats en experimentació electrofisiològica, les rates i els ratolins es troben entre les espècies més utilitzades, gràcies a la seu reduïda grandària, velocitat reproductiva i forts comportaments socials i exploratoris.

Actualment, l'experimentació electrofisiològica busca condicions cada vegada més complexes, limitades per la tecnologia dels dispositius d'adquisició. Dos aspectes són d'especial interès: La realimentació de sistemes de llaç tancat i el comportament en condicions naturals. En aquesta tesi es presenten desenvolupaments amb l'objectiu de millorar diferents aspectes d'aquestos dos problemes.

La realimentació de sistemes de llaç tancat es refereix a totes aquestes tècniques on els estímuls es produeixen en resposta a un esdeveniment general per l'animal. La latència, el temps transcorregut entre l'esdeveniment desencadenant i l'estimulació, ha d'ajustar-se a les escales temporals sota estudi. Els sistemes moderns d'adquisició presenten latències en l'ordre dels 10ms,. No obstant això, per a respondre a esdeveniments ràpids, com poden ser els transitoris d'alta freqüència creats per l'activitat neuronal, es requereixen latències per davall de 1ms. A més a més, els algoritmes per a detectar els esdeveni-

ments desencadenants o generar els estímuls poden ser complexos, integrant varies entrades de dades a temps real. Integrar el desenvolupament d'aquests algoritmes en les eines d'adquisició forma part del disseny dels experiments.

Perquè els experiments electrofisiològics incloguen comportaments naturals, els animals han de ser capaços de moure's lliurement en ambients ecològicament significatius, emulant condicions naturals. Experiments d'aquest tipus, que inclouen elements com grans espais, objectes en l'entorn o la presència d'altres animals, es veuen limitats per la natura cablejada dels sistemes d'adquisició. Altres restriccions físiques, com el pes dels implants o les limitacions al consum d'energia, poden també afectar a la duració dels experiments, limitant-los. Més enllà dels límits tecnològics, l'experimentació es pot enriquir quan les dades electrofisiològiques es complementen amb dades de múltiples fonts. Per exemple, el seguiment d'animals o microscòpia. Eines capaces d'integrar dades independentment del seu origen obrin la porta a noves possibilitats experimentals.

Els avanços tecnològics presentats a aquesta tesi tracten aquestes limitacions. S'han dissenyat dispositius amb latències de llaç tancat inferiors a  $200\mu s$ . Els quals presenten també interfícies d'elevada amplada de banda, la qual cosa permet l'adquisició de centenars de canals electrofisiològics combinats amb altres fonts de dades de naturalesa heterogènia, com vídeo o seguiment. El software de control per a aquests dispositius s'ha dissenyat mantenint la flexibilitat com a objectiu, permetent una fàcil implementació d'algorismes de llaç tancat. S'han desenvolupat interfícies i estàndards de naturalesa oberta per a incentivar el desenvolupament d'eines compatibles entre elles, per a facilitar la integració de dades experimentals.

Per a resoldre els problemes de cablejat a experiments conductuals es van seguir dos mètodes diferents. Un va ser el desenvolupament de headstages lleugers, amb pesos inferiors als 2 grams, combinats amb cables coaxials ultra fins i commutadors actius, possibles gràcies al seguiment d'animals. Aquest desenvolupament permet reduir al mínim l'esforç imposat als animals, permetent espais amplis i experiments de llarga durada, al mateix temps que permet l'ús de headstages amb elevat nombre de canals i característiques avançades.

Paral·lelament es va desenvolupar un tipus diferent de headstage, amb tecnologia sense fil. Es va crear un algorisme de compressió digital especialitzat per a senyals electrofisiològiques neuronals capaç de reduir l'amplada de banda a menys del 65% de la seua grandària original, sense introduir distorsions. Atès que l'amplada de banda juga un paper fonamental en els requisits energètics, aquesta reducció permet bateries més lleugeres i majors temps d'operació.

L'algorisme va ser dissenyat per a ser capaç de ser implementat a una gran varietat de dispositius, requerint pocs recursos de hardware i una quantitat nímia d'energia.

Combinats, els desenvolupaments presentats en aquesta tesi obrin la porta a noves possibilitats experimentals per a la neurociència, combinant l'adquisició electrofisiològica amb estudis conductuals en condicions naturals i estímuls complexos en temps real.

# Contents

| A            | cknc | owleagements                                      | 111 |

|--------------|------|---------------------------------------------------|-----|

| A            | bstr | act                                               | v   |

| R            | esun | nen                                               | ⁄ii |

| $\mathbf{R}$ | esun | n                                                 | xi  |

| $\mathbf{C}$ | onte | nts                                               | ۲V  |

| Li           | st o | f Figures x                                       | ix  |

| Li           | st o | f Tables x                                        | xi  |

| A            | bbre | eviations and Acronyms xx                         | iii |

| 1            | Int  | roduction                                         | 1   |

|              | 1.1  | Extracellular electrophysiology                   | 2   |

|              | 1.2  | Extracellular electrophysiology recording systems | 5   |

|              | 1.3  | Rodents in electrophysiology research             | 8   |

|              | 1.4  | Closed-loop feedback experiments                  | 9   |

|              | 1.5  | Field-Programmable Gate Array (FPGA) devices      | 10  |

| <b>2</b>     | Mo   | tivation and Objectives                           | 13  |

|              | 2.1  | Motivation                                        | 13  |

|              | 22   | Objectives                                        | 15  |

| _       | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -       |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -       |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -       |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Results |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3.1   |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3.2   |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3.3   | Open Ephys Software                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3.4   | Performance                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Discuss | ion                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Conclus | sions                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| en Nei  | ro Interface: High performance acquisition                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1.1   |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1.2   |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1.3   |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1.4   |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Materia |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2.1   |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2.2   |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2.5   | 0                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 1                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2.7   |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | <del>_</del>                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | -                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.0.0   | JL Haukiiiz                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | Introdu<br>Materia<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Results<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Discuss<br>Conclus<br>en Neu<br>Introdu<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Materia<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7 | 3.2.2 Xilinx FPGA 3.2.3 Connectors 3.2.4 JUCE Library Results 3.3.1 Headstages 3.3.2 Open Ephys acquisition board 3.3.3 Open Ephys Software 3.3.4 Performance Discussion Conclusions  en Neuro Interface: High performance acquisition Introduction 4.1.1 High-bandwidth heterogeneous systems 4.1.2 Tether issues 4.1.3 Latency in closed-loop experiments 4.1.4 Overview Materials and Methods 4.2.1 Bus standards 4.2.2 FPD-Link III devices 4.2.3 FPGA devices 4.2.4 3D Tracking 4.2.5 Acquisition devices 4.2.6 Stimulation devices 4.2.7 Software Results Results 3.2 ONIX hardware 4.3.3 Tethers and torque-free commutator 4.3.4 ONIX firmware 4.3.5 Acquisition performance |

| 5.1 | Introd         | $\operatorname{uction}$                 | . 76  |

|-----|----------------|-----------------------------------------|-------|

|     | 5.1.1          | Wireless electrophysiology devices      | . 76  |

|     | 5.1.2          | Data compression methods                | . 78  |

|     | 5.1.3          | Objectives                              | . 80  |

| 5.2 | $_{ m Materi}$ | ials                                    | . 80  |

|     | 5.2.1          | Huffman Coding                          | . 80  |

|     | 5.2.2          | Delta compression                       | . 83  |

|     | 5.2.3          | Low-power FPGA                          | . 83  |

|     | 5.2.4          | Wireless processor                      | . 84  |

|     | 5.2.5          | Sample signals and acquisition hardware | . 85  |

|     | 5.2.6          | Development hardware and software       | . 86  |

| 5.3 | Metho          | ${ m ds}$                               | . 88  |

|     | 5.3.1          | Software model                          | . 88  |

|     | 5.3.2          | Hardware design and validation          | . 89  |

|     | 5.3.3          | In Vivo testing                         | . 90  |

| 5.4 | Result         | s                                       | . 90  |

|     | 5.4.1          | Compression algorithm                   | . 90  |

|     | 5.4.2          | Low-memory, Low-resource compression    | . 91  |

|     | 5.4.3          | Compression performance                 | . 94  |

|     | 5.4.4          | Effect of dictionary on compression     | . 96  |

|     | 5.4.5          | Transmission protocol                   | . 96  |

|     | 5.4.6          | Wireless prototype                      | . 98  |

|     | 5.4.7          | Power usage                             | . 104 |

|     | 5.4.8          | Resource usage                          | . 105 |

| 5.5 | Discus         | ${f sion}$                              | . 105 |

| 5.6 | Conclu         | isions                                  | . 107 |

| Co  | nelusie        | ons and Outlook                         | 109   |

| 6.1 |                | ations for neuroscience research        |       |

| 0.1 | 6.1.1          | Effect of tools in the experiments      |       |

|     | 6.1.2          | Closed-loop and brain timescales        |       |

|     | 6.1.3          | Multi-source acquisition                |       |

|     | 6.1.4          | Modular approach                        |       |

| 6.2 | -              | ations for the academic community       |       |

| 6.3 | _              | esteps                                  |       |

|     |                |                                         |       |

|     | ntribu         |                                         | 119   |

| 7.1 |                | orations in the scope of the Thesis     |       |

| 7.2 |                | ations                                  |       |

| 7.3 |                | ng                                      |       |

| 7.4 | Confer         | ence posters                            | . 121 |

6

7

Bibliography 123

# List of Figures

| 1.1  | Neurons visible through Golgi-Cox method                                  | 2       |

|------|---------------------------------------------------------------------------|---------|

| 1.2  | Action potential                                                          | 4       |

| 1.3  | Measured potential                                                        | 5       |

| 1.4  | Diagram of an extracellular electrophysiology system                      | 6       |

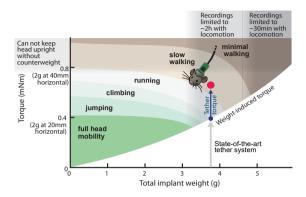

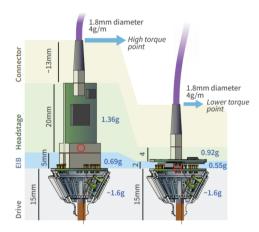

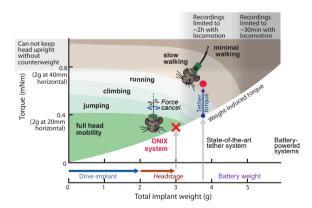

| 2.1  | Torque, weight and animal mobility                                        | 14      |

| 2.2  | Common failure events that limit experiment duration                      | 14      |

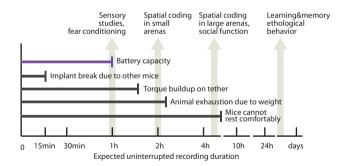

| 3.1  | Sharing closed loop algorithms                                            | 21      |

| 3.2  | 32-channel Intan headstage                                                | $^{24}$ |

| 3.3  | Omnetics connectors                                                       | 25      |

| 3.4  | Open Ephys headstages                                                     | 27      |

| 3.5  | Torque comparison between headstages                                      | 27      |

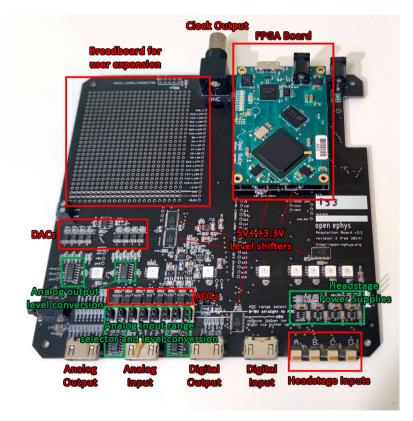

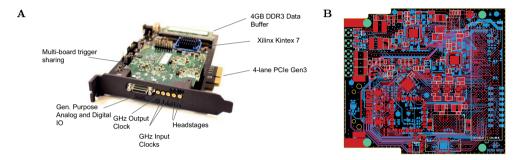

| 3.6  | Open Ephys acquisition board and its components                           | 28      |

| 3.7  | Open Ephys Input/Output (I/O) board $\dots \dots \dots \dots \dots \dots$ | 29      |

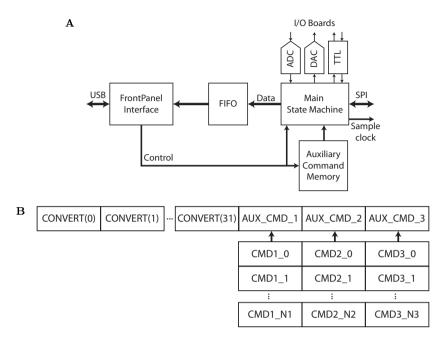

| 3.8  | Rhythm firmware diagram                                                   | 31      |

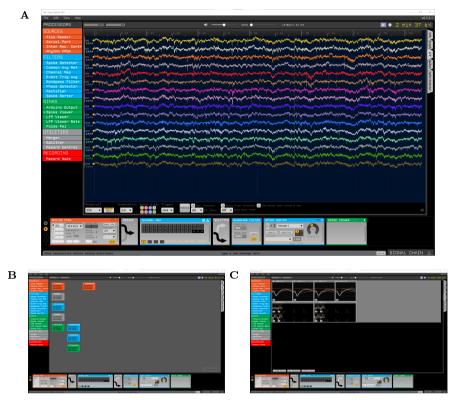

| 3.9  | Open Ephys GUI                                                            | 32      |

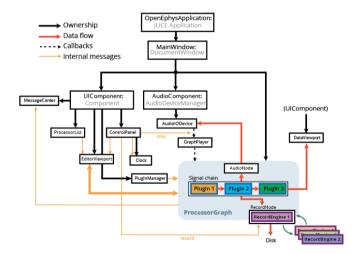

| 3.10 | Class structure of the Open Ephys software. From [96]                     | 33      |

| 3.11 | Example code for an Open Ephys GUI processor                              | 34      |

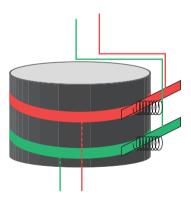

| 4.1  | Rotary commutator internals                                               | 41      |

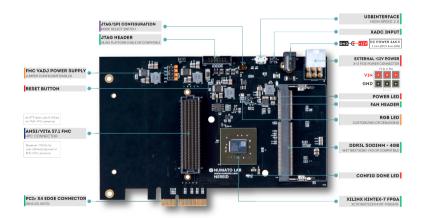

| 4.2  | Numato board overview                                                     | 45      |

| 4.3  | SteamVR overview                                                          | 47      |

| 4.4  | Lighthouse plane sweeps                                                   | 47      |

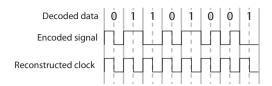

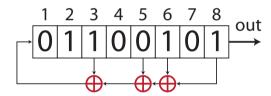

| 4.5  | Differential manchester encoding                                          | 49      |

| 4.6  | Example 8-bit LFSR                                                            | 49  |

|------|-------------------------------------------------------------------------------|-----|

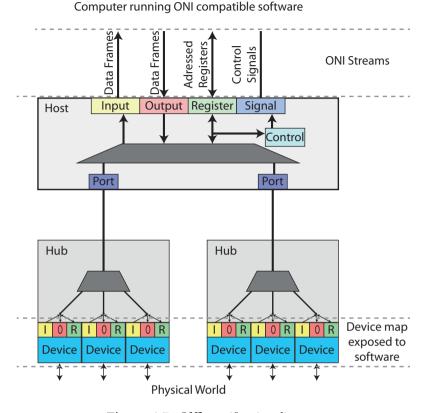

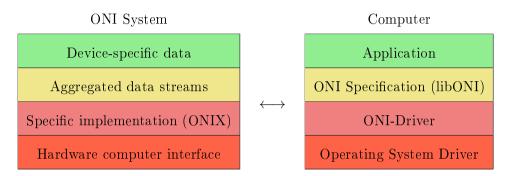

| 4.7  | ONI specification diagram                                                     | 53  |

| 4.8  | OSI-Style relation of layers in an ONI system                                 | 56  |

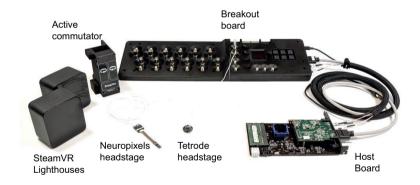

| 4.9  | Overview of all the components developed for the ONIX system                  | 57  |

| 4.10 | ONIX host board                                                               | 58  |

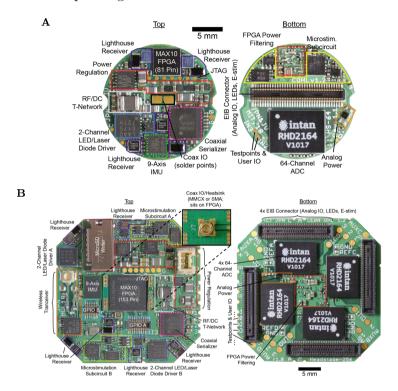

| 4.11 | ONIX 64-channel headstage                                                     | 59  |

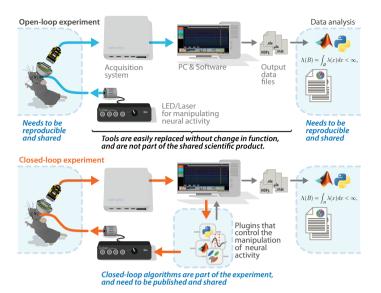

| 4.12 | ONIX headstages PCBs                                                          | 60  |

| 4.13 | ONIX Neuropixels headstage                                                    | 61  |

| 4.14 | PCB layout of the breakout board                                              | 61  |

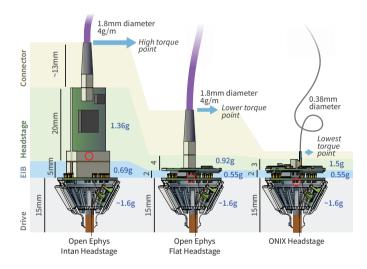

| 4.15 | ONIX and Open Ephys headstage comparison                                      | 62  |

| 4.16 | Commutator actively following headstage orientation.                          | 63  |

| 4.17 | Weight-torque diagram on ONIX system                                          | 63  |

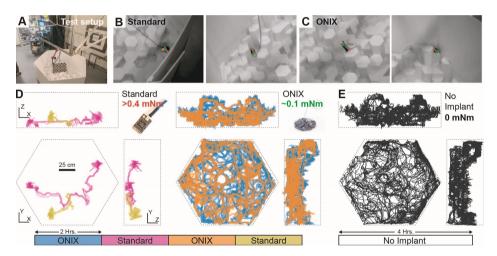

| 4.18 | Difference in exploratory behavior in mice using standard and ONIX headstages | 64  |

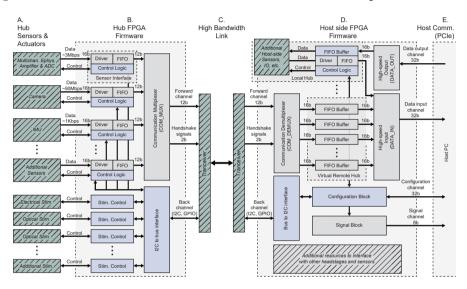

| 4.19 | ONIX firmware diagram                                                         | 65  |

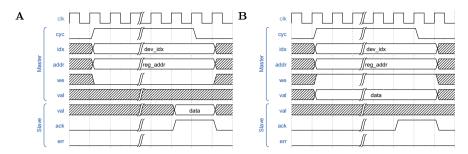

| 4.20 | ONIX internal bus chronograms                                                 | 68  |

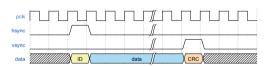

| 4.21 | Communication protocol between serializer and deserializer.                   | 70  |

| 4.22 | Bus over $I^2C$ chronograms                                                   | 71  |

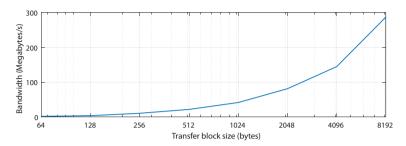

| 4.23 | ONIX system bandwidth                                                         | 72  |

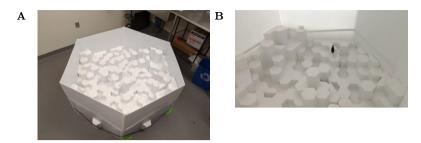

| 4.24 | 3D experimentation environment                                                | 73  |

| 4.25 | Environment occupancy heat map                                                | 73  |

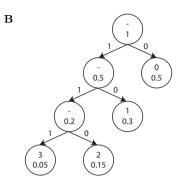

| 5.1  | Huffman dictionary creation                                                   | 82  |

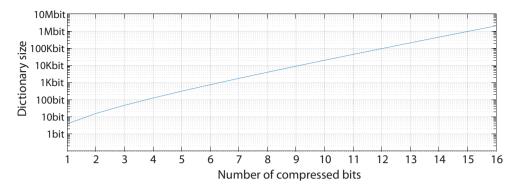

| 5.2  | Huffman dictionary size                                                       | 83  |

| 5.3  | Hardware development boards                                                   | 87  |

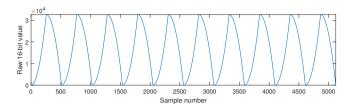

| 5.4  | Generated synthetic signal for testing                                        | 90  |

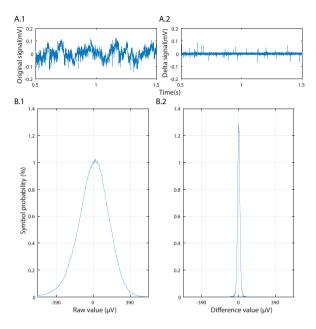

| 5.5  | Comparison between raw and delta-coded signals                                | 91  |

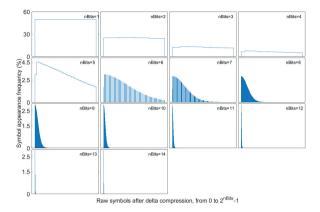

| 5.6  | Symbol appearance distribution in delta-coded signals                         | 93  |

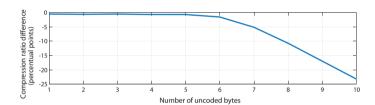

| 5.7  | Degradation of compression efficiency with uncompressed bits                  | 93  |

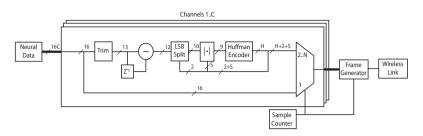

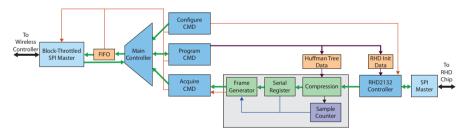

| 5.8  | Algorithm diagram                                                             | 94  |

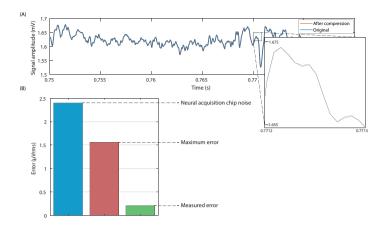

| 5.9  | Effect of compression on signal integrity                                     | 96  |

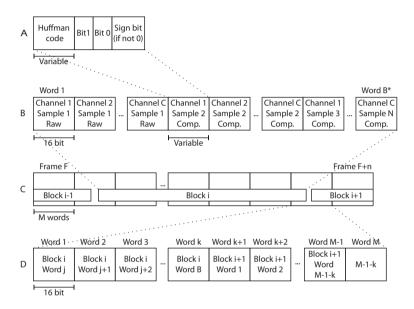

| 5.10 | Transmission protocol structure                                               | 98  |

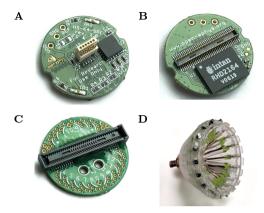

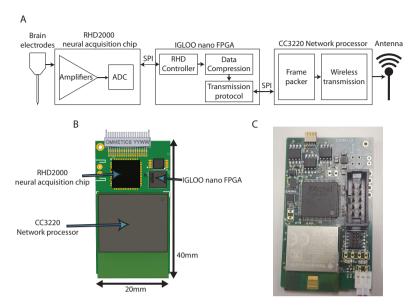

| 5.11 | Hardware prototype                                                            | 99  |

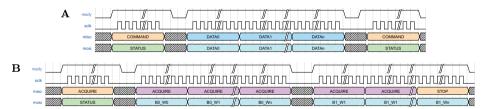

| 5.12 | - v -                                                                         | 100 |

| 5.13 |                                                                               | 101 |

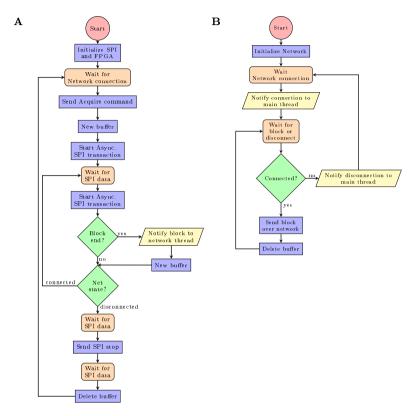

| 5.14 |                                                                               | 103 |

| 5.15 | •                                                                             | 104 |

|      |                                                                               |     |

# List of Tables

| 3.1 | Characteristics of Intan RHD2000 integrated circuits                                |  |  |  |  |  |

|-----|-------------------------------------------------------------------------------------|--|--|--|--|--|

| 4.1 | Year of introduction and speed of the different current PCI-Express (PCIe) versions |  |  |  |  |  |

| 4.2 |                                                                                     |  |  |  |  |  |

|     | Lighthouse v1 activation Timings                                                    |  |  |  |  |  |

| 4.3 | Required registers in the ONI specification                                         |  |  |  |  |  |

| 5.1 | Symbol appearance frequency in delta-coded signals                                  |  |  |  |  |  |

| 5.2 | Compression ratios                                                                  |  |  |  |  |  |

| 5.3 | Effect of dictionary on compression                                                 |  |  |  |  |  |

| 5.4 | FPGA logic usage                                                                    |  |  |  |  |  |

## Abbreviations and Acronyms

**ADC** Analog-Digital converter. 7, 8, 10, 22, 29, 30, 52, 53, 58, 69, 76, 77, 92

AIS axon initial segment. 3

**API** Application Programming Interface. 24, 30, 34, 40, 42, 56, 57, 85, 102

**ARM** A computer processor architecture developed by Arm Ltd. (Cambridge, UK). 85

ASIC Application-Specific Integrated Circuit. 11, 78, 105, 106

$\mathbf{C}++$  A low-level, object-oriented programming language. 25, 34

CMRR Common-Mode Rejection Ratio. 7

$\mathbf{CPU}$  Central Processing Unit. 42, 43, 100, 113

**DAC** Digital-Analog converter. 29, 51, 58, 69

**DCT** Discrete Cosine Transform. 78

DDR Double Data Rate. 22-24, 45

**DMA** Direct Memory Acess. 46, 85, 102, 103

**DSP** Digital Signal Processor. 11, 24, 45, 46, 84, 91, 105, 117

EIB Electrode Interface Board. 26, 27, 50

**FFT** Fast Fourier Transform. 78

FIFO First In, First Out. A type of memory queue in which data can be read in the same order it was written, removing it from the queue once read. 30, 66–68, 70, 101

FMC FMC Mezzanine Card. 43, 45, 58

**FPGA** Field-Programmable Gate Array. xv, 10–12, 24, 28–30, 43–46, 51, 58–60, 65, 83, 84, 86–90, 99–105, 117, 119

FSM Finite State Machine. 29, 30

GPIO General Purpose Input/Output. 44, 46, 68, 85, 86

GPU Graphical Processing Unit. 10, 11, 42, 113

**GUI** Graphical User Interface. 19, 26, 31–33, 37, 88, 115, 116

**HDL** Hardware Description Language. 12, 24, 51, 87–90

I<sup>2</sup>C Inter-Integrated Circuit. 44, 50, 67, 68, 70, 71, 85

$\mathbf{I/O} \ \, \mathbf{Input/Output.} \ \, \mathbf{xix}, \ 21, \ 28, \ 29, \ 36, \ 43, \ 58, \ 60, \ 61, \ 69, \ 70, \ 84, \ 110, \ 112, \\ 114$

IC Integrated Circuit. 7, 11, 12, 22, 23, 40, 51, 84–86, 89, 98, 99

**IDE** Integrated Development Environment. 12, 52, 87

**IMU** Inertial Measurement Unit. 40, 46, 50, 59, 60

JTAG Joint Test Action Group. A standard for debugging interfaces. 12, 51

**LFP** Local Field Potentials. 4, 5, 15, 32, 79, 113

LFSR Linear Feedback Shift Register. 49

LVDS Low-Voltage Differential Signaling. 7, 22, 35, 36, 41

MCU MicroController Unit. 10, 85, 99–102

**MEMS** Micro-Electro-Mechanical System. 50

MISO Master-In Slave-Out. 100, 101

MOSI Master-Out Slave-In. 100

**ONI** Open Neuro Interface. xvi, xx, xxi, 16, 39, 42, 52–59, 61, 66, 68–70, 73, 110, 114–117, 119

**OOP** Object-Oriented Programming. 25, 34

**PCA** Principal Component Analysis. 5

**PCB** Printed circuit board. 24–26, 28, 43–45, 51, 58, 59, 84, 85, 88

**PCIe** PCI-Express. An high-speed evolution of the PCI (Peripheral Component Interconnect) bus used to connect expansion boards in computer systems. xxi, 43, 45, 46, 51, 56–58, 70, 74, 117

**RAM** Random Access Memory. 11, 24, 30, 45, 46, 84, 85

**ROM** Read-Only Memory. 91

**RTOS** Real-Time Operating System. 102

SoC System-on-Chip. 85

**SPI** Serial Peripheral Interface. 22, 28, 30, 36, 41, 45, 85, 99–103

SSD Solid-State Drive. 35

TTL Transistor to Transistor Logic. A standard for digital circuits. When not using to describe a device it refers to the signaling these devices use: logic communication with simple on-off signaling and 5V levels. 29, 30, 33

**USB** Universal Serial Bus. 8, 24, 30, 35, 36, 56, 57, 113, 117

VR Virtual Reality. 9, 40, 47, 74, 112

### Chapter 1

## Introduction

The brain, its functions and how its physiological processes relate to behavior and cognition has been a research topic since ancient times, with multiple techniques and tools created devoted to its study. Even so, no complete theory on how the brain works has yet been formulated [1].

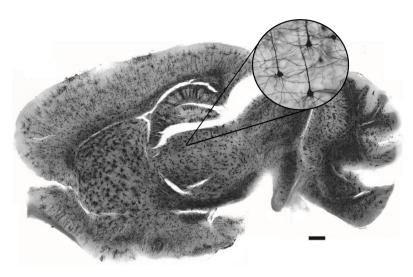

Modern neuroscience understanding can be traced to the late nineteenth century. The Golgi stain method [2], [3] allowed individual neurons to be visualized (Figure 1.1). Santiago Ramón y Cajal created the neuron doctrine [4], which describes the nervous system as a collection of individual neurons. The notion of different areas of the brain being responsible for specific functions was pioneered by Jean Pierre Flourens and Paul Broca, with Korbinian Brodmann publishing the first map of cerebral regions [5]. While some of these hypotheses have been updated, for example with compound neural activity now being considered important, opposed to only individual activation[6], most of these principles hold and have been verified by modern techniques, such as electrophysiology or neuroimaging [7].

The twentieth century gave rise to an increased understanding of the neuron molecular structure and how they communicate. Edgar Adrian was among the first to notice signals transmitted through individual nerves, related to specific stimuli. He measured a series of electric potential changes, called action potentials or *spikes*, and surmised the existence of a common neural

Figure 1.1: Neurons easily visible through the Golgi-Cox staining method. Modified from Zaquot et Al. [3].

communication method [8]. A mathematical model for these action potentials was later presented by Alan Loyd Hodgkin and Andrew Huxley by studying their initiation and propagation in a squid axon, creating the Hodgkin-Huxley model [9].

Research on spike and cell activity in living animals has led to discoveries about brain function [10]–[12] and remains an important tool for neuroscience research.

### 1.1 Extracellular electrophysiology

Electrophysiology refers to the set of techniques able to measure the electrical properties generated by cell activity. Extracellular electrophysiology in particular measures the electric potential created in the extracellular space by transmembrane ionic flows related to neuron activation.

Neurons in rest state are held in an electrochemical equilibrium governed by the ionic concentrations in the intracellular and extracellular fluids. The resting electric potential across the membrane of a neuron, referred to its exterior, is approximately -70mV[13], meaning that the ionic concentration is more negatively charged in the intracellular side of the membrane than in the extra-

cellular space. This ionic concentration is maintained by a molecular structure present in the membrane called Sodium-Potassium pump which continuously expends energy to ensure that ionic concentrations are not equalized between the intracellular end extracellular mediums [14], creating a chemical gradient in addition to the electrical potential.

Neurons can communicate with each other through the release of chemical messengers called neurotransmitters. These bind to selective receptors on the synapses of the receiving cell, which can open ion channels, a molecular structure in the cellular membrane. These structures allow ions, often  $Na^+$  or  $Ca^{2+}$  to flow from the extracellular to the intracellular space, where their concentration is higher. The change on charge distribution provoked by this ion influx causes a local change, or depolarization, of the membrane electric potential. This change in the electrical field propagates through the membrane and can trigger the opening of a different structure, voltage-gated  $Na^+$  channels, present through all the cell membrane. These structures open when exposed to a voltage over a certain threshold, reinforcing the propagation.  $Na^+$  channel distribution is not homogeneous, its density being significantly higher in the axon initial segment (AIS) than in the cell body or dendrites [15].

Potentials initiated in the synapses are attenuated along the way to the AIS [16]. However, multiple simultaneous stimuli can overlap, resulting in a summed potential enough to trigger voltage-sensitive  $Na^+$  channels at the AIS [17]. Due to the higher channel density, this process initiates a fast cascade effect which propagates through the axon, creating a fast influx of  $Na^+$  ions. This flow continues until the membrane potential crosses a positive threshold triggering the opening of a different structure, voltage-dependent  $K^+$  channels open. These allow a flow of  $K^+$  ions from the intracellular medium, where their concentration is higher, to the extracellular space. This results in an electric current in the opposite direction, repolarizing the cell. Repolarization overshoots the original resting potential, creating a period of hyperpolarization. The continuous effect of the Sodium-Potassium pump eventually returns the cell to its resting state, when the process can be triggered again. While this process is considered the main effect of cell activation, other molecular events contribute to the electrical currents flowing through the cellular membrane, such as  $Ca^{2+}$ spikes [18].

While the individual transmembrane currents can be measured [19], their compound effect can be observed in the extracellular space as variations on the electric field potential. The effect is described in Equation 1.1 [20]–[22]:

$$V_n(r_m, t) = \frac{1}{4\pi\rho} \sum_{n=1}^{N} \frac{I_n(t)}{|r_m - r_n|}$$

(1.1)

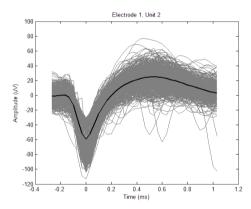

In which  $V_n$  is the electric potential, with respect to a point in the infinite according to Coulomb's law,  $\rho$  the extracellular medium conductivity value,  $r_m$  the position in which the measurement is taking place and  $I_n$  and  $r_n$  the different individual currents. The resulting waveforms from an action potential have the topology seen in Figure 1.2, where the initial slope is created by the  $Na^+$  ion influx, then followed by the reverse polarity of the outwards  $K^+$  ion flow before finally settling back into the resting potential.

Figure 1.2: Extracellular action potentials from the visual cortex of a rat. The darker line represents the mean waveform.

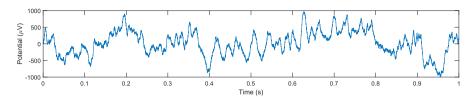

It is important to note that at any given time, hundreds of neurons are spiking simultaneously. Thus, for any given sensing site, the measured potential is theoretically the sum of the activity of every single cell, resulting in a signal similar to the one see in Figure 1.3. Due to the inverse distance factor, the conductivity value  $\rho$  being dependent on frequency and the interference of different neurons firing off-phase, only the spikes of cells located physically close to the recording site can be extracted. Contrariwise, synchronized activity of multiple neurons in the area surrounding the site result in low-frequency, high-amplitude oscillations, referred to as Local Field Potentials (LFP) [23]. While the former gives information about individual cells, LFPs mostly represent the aggregated synaptic activity and active dendritic currents in the tissue. [23]–[26].

Figure 1.3: Combined measured potential in an extracellular site. Recorded from the hippocampal region on a rat.

Since a single site detects action potentials from different neurons, analyzing spike activity requires multiple steps. First, the signals are high-pass filtered to remove the compound LFP elements, leaving only high frequency spike waveforms. An amplitude threshold method can be used to locate individual events by detecting the large depolarization peaks [27]. While this detects the spikes, extra steps are needed to differentiate events originating in distinct neurons, a process called spike sorting. While there are multiple algorithms to separate spikes into clusters of common neuron origin [28], many of them take advantage of measured waveforms from different neurons being non-identical due by both biological and geometrical differences. Most such algorithms use windowing methods to detect specific waveform features that cross with time-amplitude areas [29] or perform mathematical component extraction such as Principal Component Analysis (PCA) [30] to separate events in a projected space.

#### 1.2 Extracellular electrophysiology recording systems

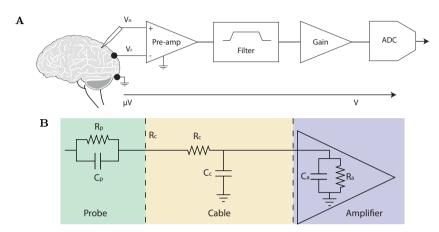

Since no electronic circuit can be physically tied to infinity, measuring an electric potential implies measuring the potential difference between two points. In the case of electrophysiological signals, a recording probe is inserted next to the cells of interest with the potential  $V_n$  created by their transmembrane currents, and a reference electrode is placed far from the region interest, located at a potential  $V_r$ . The actual measured voltage  $V_m$  is thus the difference  $V_m = V_p - V_r$ , assuming there is no current flow through the electrodes which would provoke voltage drops resulting in measurement distortions.

The challenge of recording extracellular potentials reside on the small scale required, both physical and electrical. As previously discussed, the signals are in the range of  $\mu V$ , which require amplification to be properly recorded an analyzed. Moreover, to reduce tissue damage, probes inserted into the brain must have a thickness measured in  $\mu m$  [31]. Figure 1.4.B shows the equivalent

circuit of a probe, the input of an amplifier and the wire connecting both. To avoid a potential drop in the order of the interest signal, amplifier input impedance must be as high as possible, while wire and probe impedances must be kept low.

Figure 1.4: A: Diagram of an extracellular electrophysiology circuit. B: Equivalent circuit of the probe-wire-amplifier path