# UNIVERSITAT POLITÈCNICA DE VALÈNCIA

# Escuela Técnica Superior de Ingeniería Industrial

# RESEARCH OF THREE PHASE INVERTERS

Trabajo Fin de Máster

Máster Universitario en Ingeniería Industria

AUTOR/A: Guillem Carrillo, Sergio TUTOR/A: Trujillo Ruiz, Francisco de Borja CURSO ACADÉMICO: 2022/2023

### VILNIUS GEDIMINAS TECHNICAL UNIVERSITY

### FACULTY OF ELECTRONICS DEPARTMENT OF ELECTRONICS

## DESIGN AND ESEARCH OF THREE-PHASE HIGH-POWER INVERTER

Master's degree Thesis

Sergio Guillem Carrillo Dr Gediminas Staigvila

## VILNIUS 2023 VILNIUS GEDIMINAS TECHNICAL UNIVERSITY

### FACULTY OF ELECTRONICS DEPARTMENT OF ELECTRONICS

#### SERGIO GUILLEM

## Design and research of Three-phase high-power inverter

Master's degree Thesis

Electrical Energetics Systems Engineering 2023, 6211EX049 Generation of energy Electrical Engineering

Supervisor dr Gediminas Staigvila

Vilnius, 2023

# Annotations (in Lithuanian and in English) must be printed from <u>mano.vgtu.lt</u>. Also, one copy of the annotations (in Lithuanian and in English) must be presented to the department.

Vilnius Gediminas Technical University

**Electronics** Faculty

**Electrical Engineering** Department

ISBN ISSN Copies No. 2 Date ....-....

Electrical engineering engineering / Automatics study program master's thesis

#### Title: Design and research of Three-phase high-power inverter

Author Sergio Guillem Academic supervisor Prof. Dr Gediminas Staigvila

| Thesi | s language        |  |  |  |  |  |

|-------|-------------------|--|--|--|--|--|

|       | Lithuanian        |  |  |  |  |  |

| Х     | Foreign (English) |  |  |  |  |  |

#### Annotation

The final master's thesis deals with the study os the three-phase inverters and their importance in today's electrical market, being crucial into the development of renewable energies and the energy transition. Diferrent types of inverters and their modulation techniques are explained. Circuits of these inverters and their modulation techniques are provided and analyzed. Having analyzed theoretical and practical aspects, the conclusions and suggestions of the final thesis are presented

Structure: introduction, Descrptive part, Practical part, conclusions and references.

Thesis consist of: 95 p. text without appendixes, 89 pictures, 10 tables, 33 bibliographical entries.

Keywords: VSI, PWM, three-phase inverters, filter, waveform, sinusoida, load, voltage, current.

#### VILNIUS GEDIMINAS TECHNICAL UNIVERSITY FACULTY OF ELECTRONICS DEPARTMENT OF ELECTRONICS

Electrical engineering Electrical Energetics Systems Engineering 2023, 6211EX049 Generation of energy

#### **OBJECTIVES FOR MASTER THESIS**

Vilnius

For student Sergio Guillem

Master Thesis title: Design and research of Three-phase high-power inverter

The Final work has to be completed by xxxx, 2023

THE OBJECTIVES:

Research about the different types of inverters and modulation techniques. Study the different components to improve the quality of the work of the inverters. Create, design and analyse different circuis and how they work through different changes.

Consultants of the Master Thesis: None Academic Supervisor: Dr Gediminas Staigvila

Objectives accepted as a quidance for my Master Thesis

(Student's Name, Surname)

# **TABLE OF CONTENTS**

| IND  | EX                                                      |      |

|------|---------------------------------------------------------|------|

| INTF | RODUCTION                                               | 6    |

| 1.   | DESCRIPTIVE PART                                        | 8    |

|      | 1.1. Voltage Source Inverters                           | 8    |

|      | 1.1.1. Diodes                                           |      |

|      | 1.1.2. Transistors                                      |      |

|      | 1.1.3. IGBT                                             |      |

|      | 1.1.4. MOSFET                                           |      |

|      | 1.2. Single-phase Voltage Source Inverters              |      |

|      | 1.3 Half-Bridge VSI                                     |      |

|      | 1.3.1. PWM technique                                    |      |

|      | 1.3.2. Square wave modulating technique.                |      |

|      | 1.3.3. Selective harmonic elimination (SHE)             |      |

|      | 1.4 Full-Bridge VSI                                     |      |

|      | 1.4.1. Bipolar PWM technique                            |      |

|      | 1.4.2. Unipolar switching technique                     |      |

|      | 1.5 Three-Phase VSI                                     |      |

|      | 1.6 Multilevel inverters                                |      |

|      | 1.7 Multilevel inverters topologies                     | . 25 |

|      | 1.7.1 Diode clamped multilevel inverter                 |      |

|      | 1.7.2 Flying capacitor multilevel inverter              |      |

|      | 1.7.3 Cascaded H-bridge multilevel inverters (CHB-MLI)  |      |

|      | 1.8. Modulation techniques.                             |      |

|      | 1.8.1 Selective harmonic elimination PWM (SHE-PWM)      | . 33 |

|      | 1.8.2 Sinusoidal PWM (SPWM)                             | . 34 |

|      | 1.8.3 Space vector PWM (SPV)                            | . 35 |

|      | 1.8.4 Sigma delta PWM (SDM)                             |      |

|      | 1.8.5 Closed loop PWM control techniques                | . 38 |

|      | 1.8.6 Comparison of the topologies and control scheme   |      |

|      | 1.9 Passive filters.                                    | . 41 |

|      | 1.10 L-Filter                                           | . 42 |

|      | 1.11 LC-Filter.                                         | . 44 |

|      | 1.12 LCL-Filter.                                        | . 46 |

|      | 1.13 Active power filters.                              | . 50 |

|      | 1.14 Types of active power filters.                     |      |

|      | 1.15 Shunt active power filters                         |      |

|      | 1.15.1 Basic components of shunt active power filters   | . 54 |

|      | 1.15.2 Shunt active power filters control algorithms.   | . 54 |

|      | 1.15.3 Harmonic extraction algorithm.                   |      |

|      | 1.15.4. DC-Link Capacitor Voltage Regulation Algorithm. |      |

|      | 1.15.5. Current control algorithm.                      | . 57 |

|      | 1.16 Series active power filters                        |      |

|      | 1.16.1 Control algorithm.                               | . 60 |

|      | 1.17 Hybrid active power filters.                       |      |

|      | 1.17.1 Control scheme.                                  | . 62 |

| 2.   | PRACTICAL PART                            | 65 |

|------|-------------------------------------------|----|

|      | 2.1 Half-Bridge VSI                       | 65 |

|      | 2.2. Full-Bridge VSI                      |    |

|      | 2.2.1. PWM Modulation technique           |    |

|      | 2.3. Three-phase VSI.                     |    |

|      | 2.4. SPWM Case 1.                         |    |

|      | 2.4.1. Fast Fourier Transformation (FFT). |    |

|      | 2.4.2. Total Harmonic Distortion (THD)    |    |

|      | 2.5. SPWM Case 2.                         |    |

|      | 2.5.1 Fast Fourier Transformation (FFT)   |    |

|      | 2.5.2 Total Harmonic Distortion (THD)     |    |

|      | 2.6. Changing Load.                       |    |

|      | 2.7. Use of filters.                      |    |

|      | 2.7.1 Total Harmonic Distortion (THD)     | 86 |

| CON  | ICLUSION                                  | 88 |

| REFI | ERENCES                                   | 89 |

## **LIST OF FIGURES**

| Figure 1. Diode quadrant                                                                     |            |

|----------------------------------------------------------------------------------------------|------------|

| Figure 2. Device symbol. Carries in one direction, blocks in the other                       | 9          |

| Figure 3. Transistorized VSI                                                                 | 10         |

| Figure 4. IGBT unit cell.                                                                    | 11         |

| Figure 5. Device symbol                                                                      | 12         |

| Figure 6. Quadrant operation. Carries or blocks current in one direction                     | 12         |

| Figure 7. Vertical cross-sectional view for a power MOSFET                                   |            |

| Figure 8. Device symbols: (a) n-channel enhancement-mode; (b) p-channel enhancement-         |            |

| mode; (c) n-channel depletion-mode; and (d) p-channel depletion-mode                         | 14         |

| Figure 9. MOSFET quadrant operation. Carries in one direction or blocks in both directions.  |            |

|                                                                                              |            |

| Figure 10. Single-phase half-bridge VSI                                                      |            |

| Figure 11. Carrier and modulating signals.                                                   |            |

| Figure 12. Q1 switch state (left) Q2 switch state (right)                                    |            |

| Figure 13. AC output current.                                                                |            |

| Figure 14. Normalized fundamental ac component of the output voltage in a half-bridge VSI    |            |

| SPWM modulated                                                                               |            |

| Figure 15. Unipolar output voltage with notches per quarter-wave cycle                       |            |

| Figure 16. Switching angle trajectories when nine angles are eliminated.                     |            |

|                                                                                              |            |

| Figure 17. Single-phase full-bridge VSI                                                      |            |

| Figure 18. Bipolar Switching scheme.                                                         |            |

| Figure 19. Unipolar Switching scheme.                                                        |            |

| Figure 20. Conventional Three-phase VSI topology                                             |            |

| Figure 21. Classification of multilevel inverter topologies according to the voltage source  |            |

| Figure 22. Three-phase five-level topology of a diode clamped multilevel inverter.           |            |

| Figure 23. Three-phase five-level topology of a flying capacitor multilevel inverter         |            |

| Figure 24. Three-phase five-level topology of cascaded H-bridge multilevel inverter          | 30         |

| Figure 25. Phase output voltage waveforms of a five-level topology CHB-MLI with two          | 20         |

| separate DC sources.                                                                         |            |

| Figure 26. Classification of multilevel inverter control scheme based on switching frequency |            |

|                                                                                              |            |

| Figure 27. Control schemes of multilevel inverters.                                          |            |

| Figure 28. Multi-carrier SPWM control strategies: (a) PD, (b) POD, (c) APOD, (d) PS          |            |

| Figure 29. Space vector diagram of a three-level inverter with sector and subsectors         | 36         |

| Figure 30. Block diagrams of delta modulation: (a) simple delta modulator, (b) sigma-delta   | ~ <b>-</b> |

| modulator                                                                                    |            |

| Figure 31. SDM control of a multilevel inverter.                                             | 38         |

| Figure 32. Hysteresis current control: (a) block diagram of a H-bridge cell with hysteresis  |            |

| controller, (b) hysteresis current band and voltage curves of load feedback.                 |            |

| Figure 33. The block diagram of stationary linear current controller                         |            |

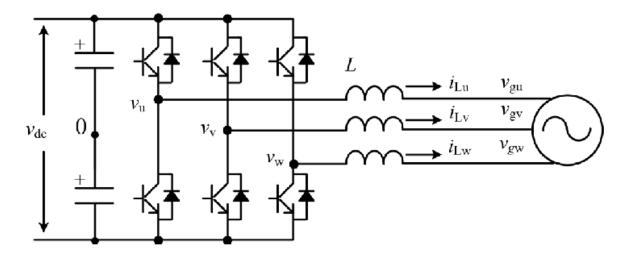

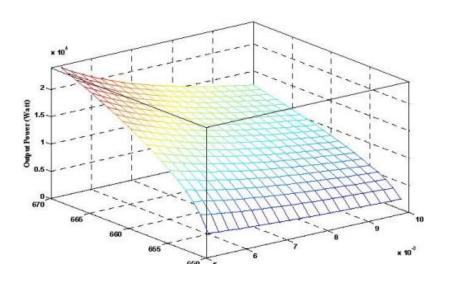

| Figure 34. Traditional three phase grid connected inverter with L-Filter                     |            |

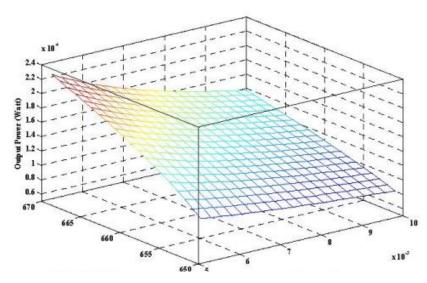

| Figure 35. Output power as function of DC link voltage and inductor inductance               | 43         |

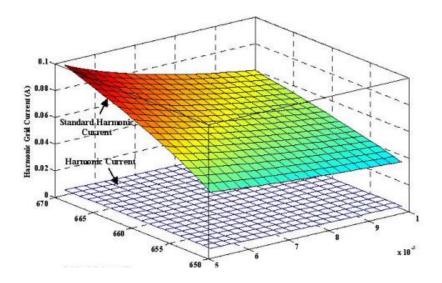

| Figure 36. (a) harmonic current as function of DC link voltage and inductor inductance (b)   |            |

| harmonic current as function of switching fequency and inductor inductance                   |            |

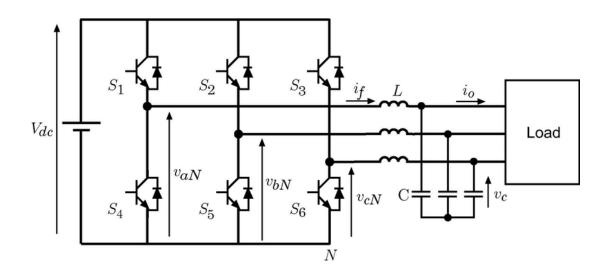

| Figure 37. Three-phase inverter with output LC filter                                        |            |

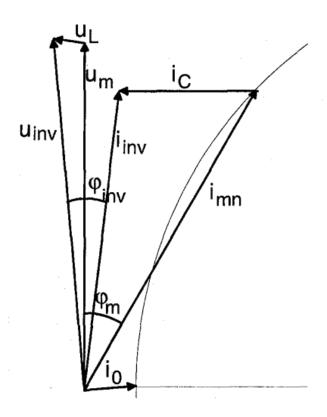

| Figure 38. Vector diagram of motor and inverter current and voltage.                         |            |

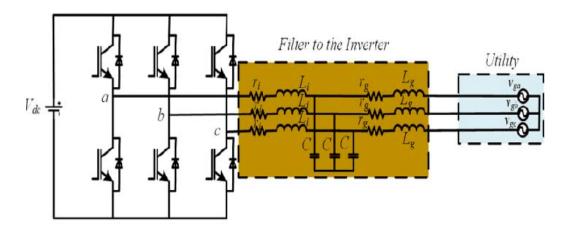

| Figure 39. Three-Phase inverter with a LCL-filter.                                           |            |

| Figure 40. Output power as function of DC link voltage and inductor inductance               | 47         |

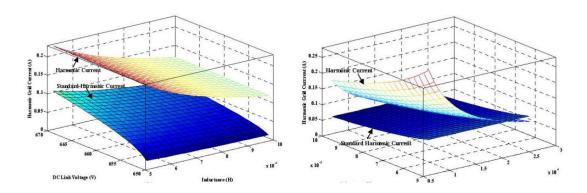

| Figure 41. Harmonics current as fuction of DC link voltage and inductor inductance           |            |

|                                                                                              | 48         |

| Figure 42. Harmonic current as function of switching frequency and inductor inductance       |            |

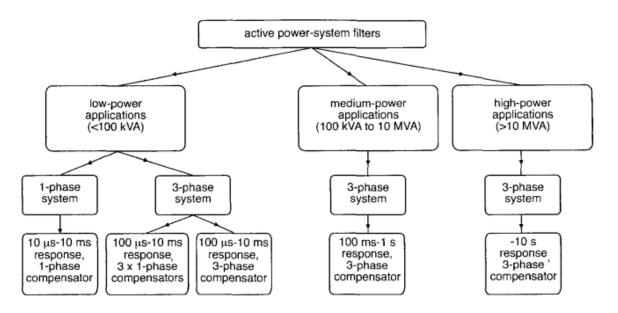

| Figure 44. Rated and harmonic currents as a function of switching<br>Figure 45. Harmonic current as a function of inductance at different<br>Figure 46. Subdivison of power system filters according to power rating and speed of |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| response                                                                                                                                                                                                                          | 52   |

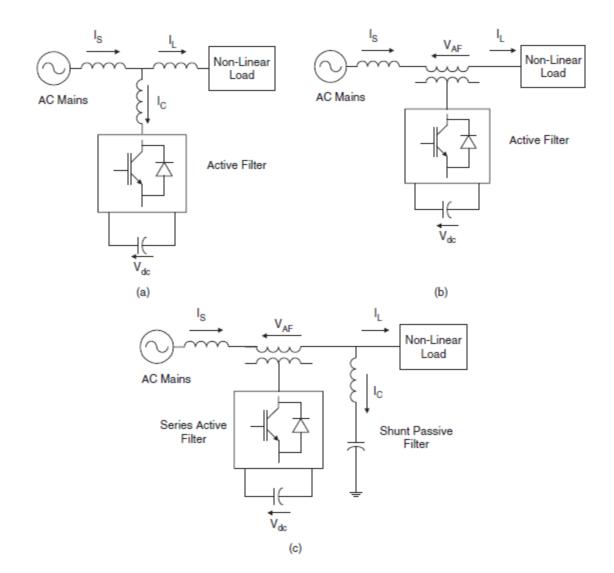

| Figure 47. Active power filter topologies implemented with PWM-VSI: (a) shunt active                                                                                                                                              | . 52 |

| power filter; (b) series active power filter; and (c) hybrid.                                                                                                                                                                     | . 53 |

| Figure 48. Compensation characteristics of a shunt active power                                                                                                                                                                   |      |

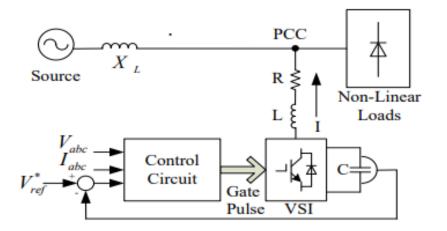

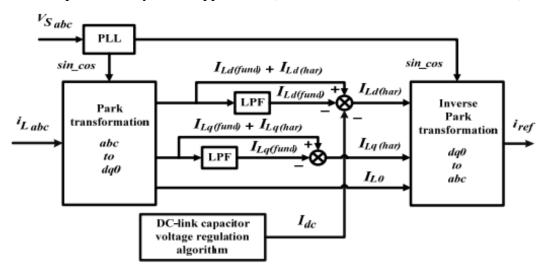

| Figure 49. Control structure of a typical synchronous reference frame (SRF) algorithm                                                                                                                                             |      |

| Figure 50. Control structure of a typical pq theory algorithm.                                                                                                                                                                    |      |

| Figure 51. Conceptual model of direct current control (DCC) scheme.                                                                                                                                                               |      |

| Figure 52. Conceptual model of an indirect current control (ICC) scheme.                                                                                                                                                          |      |

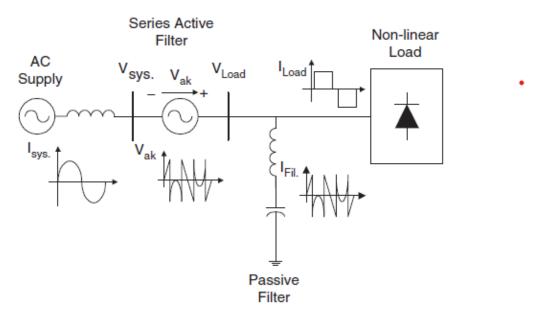

| Figure 53. The series active power filter operating as a voltage compensator                                                                                                                                                      |      |

| Figure 54. Combination of series active power filter and passive filter for current harmonic                                                                                                                                      |      |

| compensation.                                                                                                                                                                                                                     |      |

| Figure 55. The series active power filter topology.                                                                                                                                                                               |      |

| Figure 56. Control scheme for the series active filter                                                                                                                                                                            |      |

| Figure 57. The hybrid active power filter configuration.                                                                                                                                                                          |      |

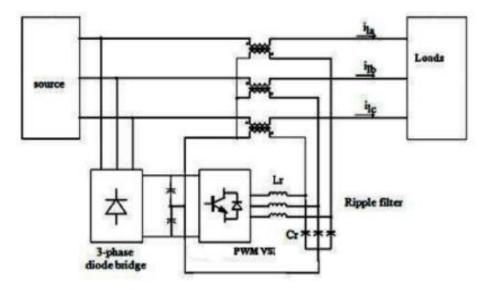

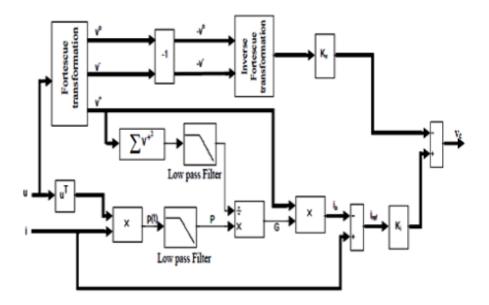

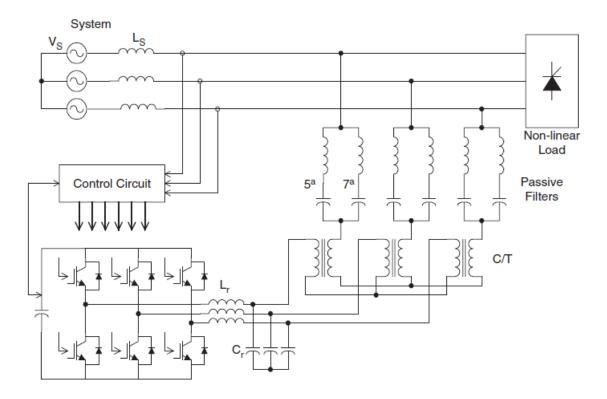

| Figure 58. The hybrid active power filter topology and associated control scheme                                                                                                                                                  |      |

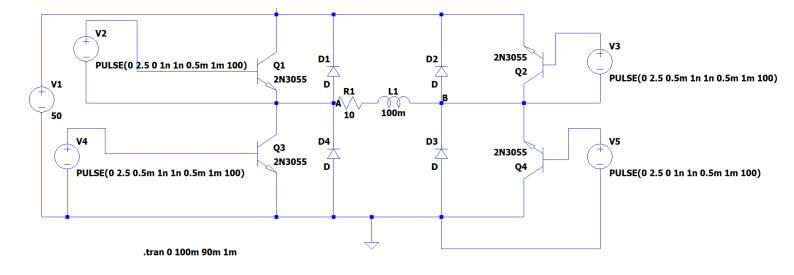

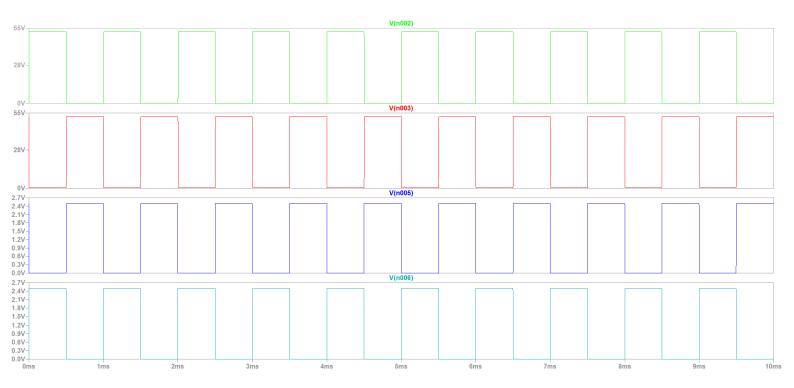

| Figure 59. Single-Phase half bridge VSI.                                                                                                                                                                                          |      |

| Figure 60. Voltage passing through the switches.                                                                                                                                                                                  | . 66 |

| Figure 61. Current and voltage passing through the line.                                                                                                                                                                          | . 66 |

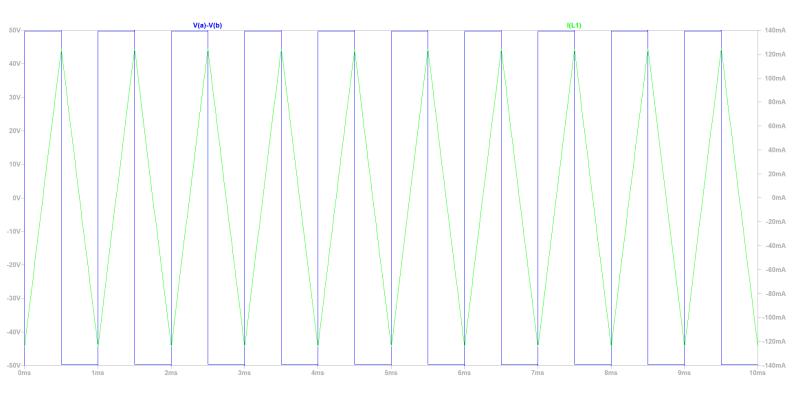

| Figure 62. Single-Phase full bridge VSI.                                                                                                                                                                                          |      |

| Figure 63. Voltage passing through the switches.                                                                                                                                                                                  |      |

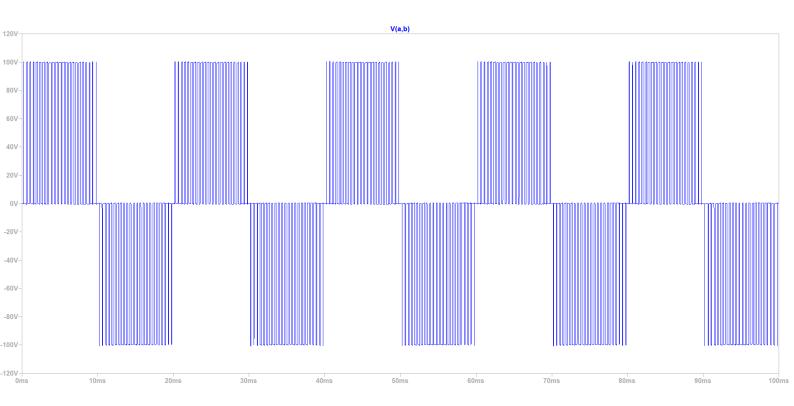

| Figure 64. V(a)-V(b) and current passing through the line                                                                                                                                                                         | . 68 |

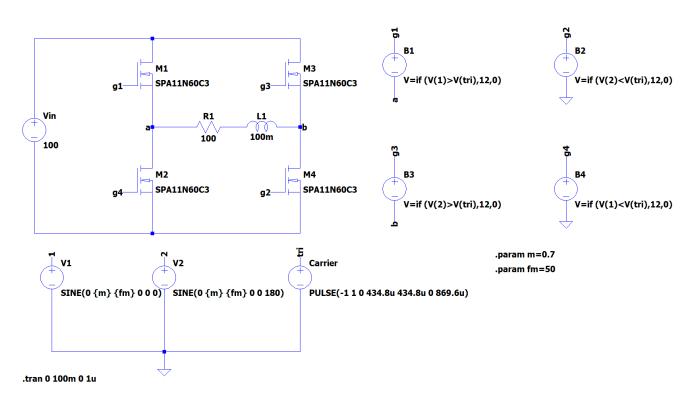

| Figure 65. Full-Bridge VSI with PWM modulation.                                                                                                                                                                                   |      |

| Figure 66. Graph of voltage across the RL load.                                                                                                                                                                                   | . 70 |

| Figure 67. RMS of the load voltage is around 66.556 V.                                                                                                                                                                            | . 70 |

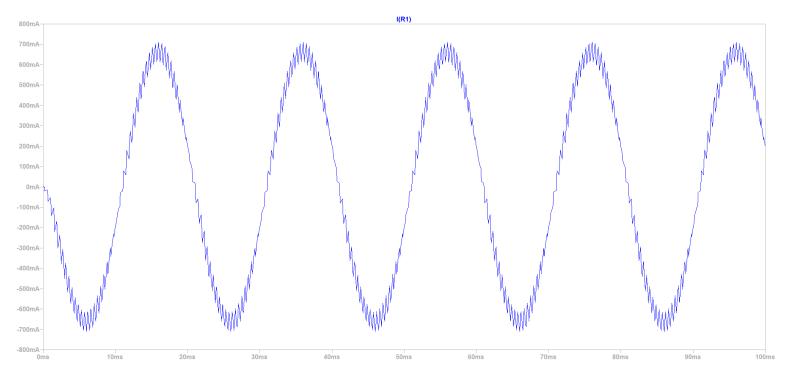

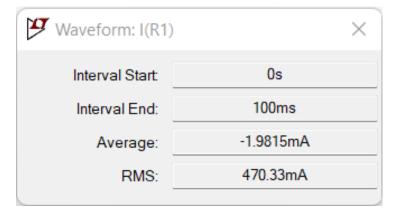

| Figure 68. RL load current.                                                                                                                                                                                                       |      |

| Figure 69. RMS of load current is 470.32 mA.                                                                                                                                                                                      | . 71 |

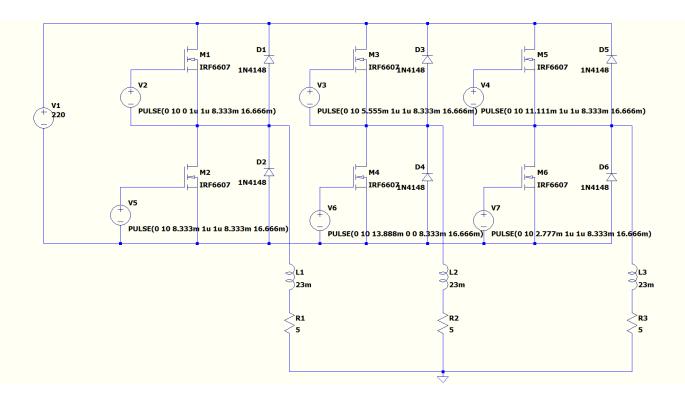

| Figure 70. Three-phase VSI.                                                                                                                                                                                                       | . 72 |

| Figure 71. Current passing through the lines                                                                                                                                                                                      | . 73 |

| Figure 72. Voltage passing through the lines.                                                                                                                                                                                     |      |

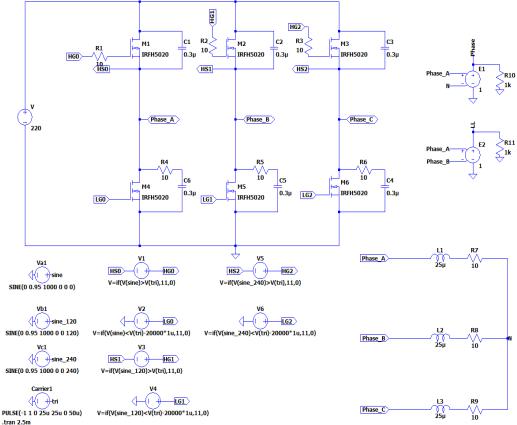

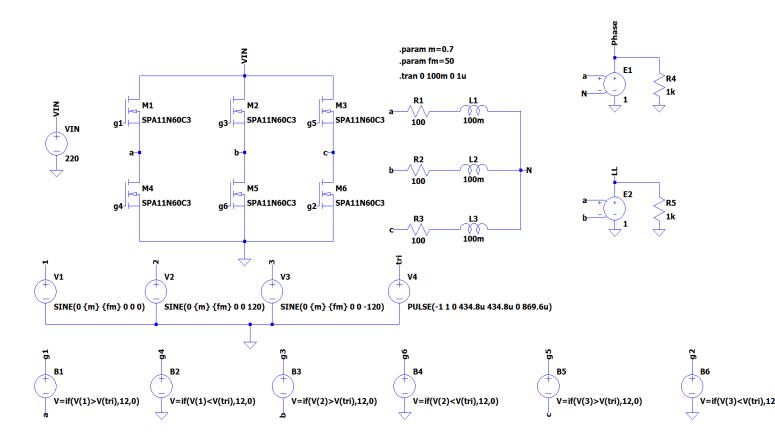

| Figure 73. Three-Phase VSI with SPWM technique.                                                                                                                                                                                   | . 74 |

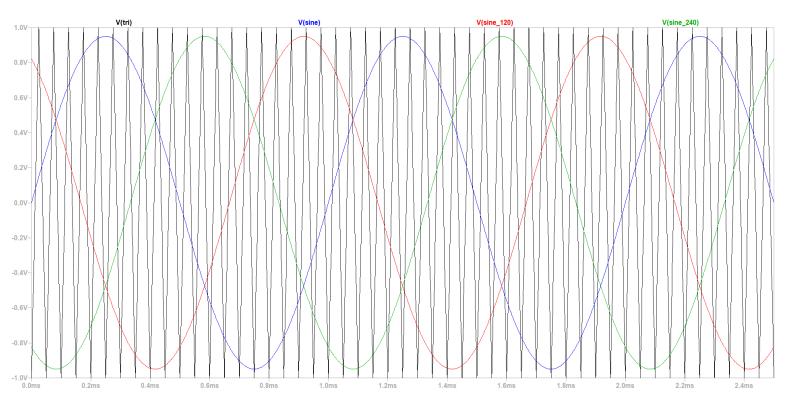

| Figure 74. Carrier signal compared with the three sinusoidal waves.                                                                                                                                                               | . 75 |

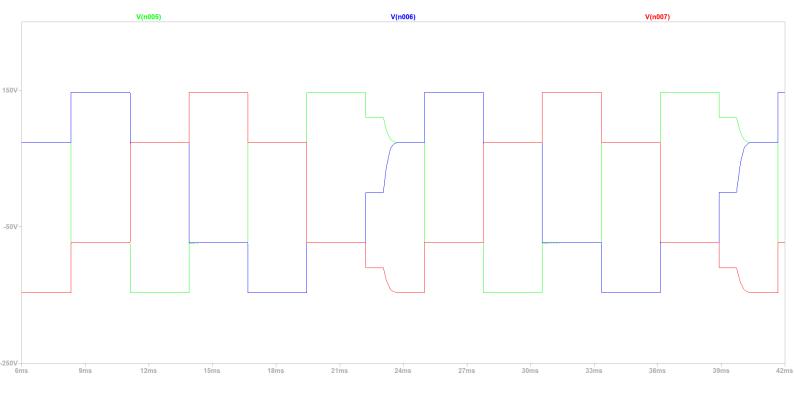

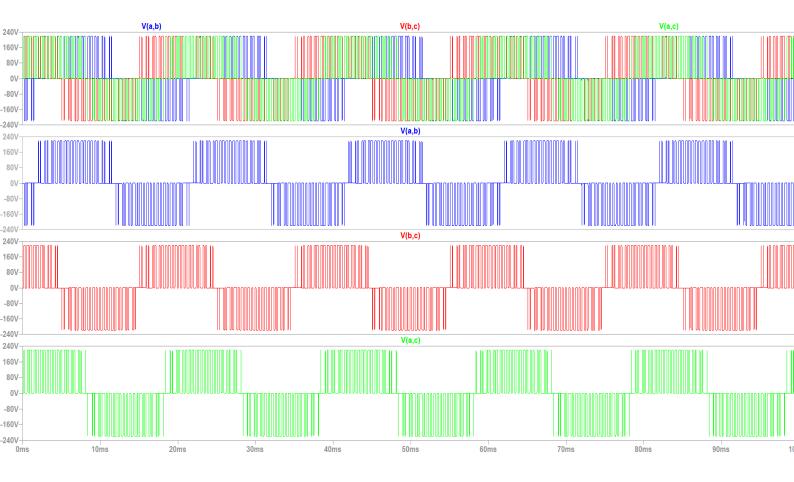

| Figure 75. Voltage passing through the lines.                                                                                                                                                                                     | . 75 |

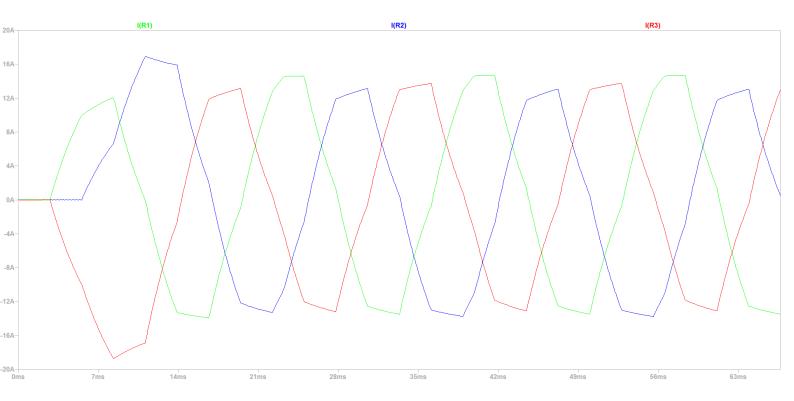

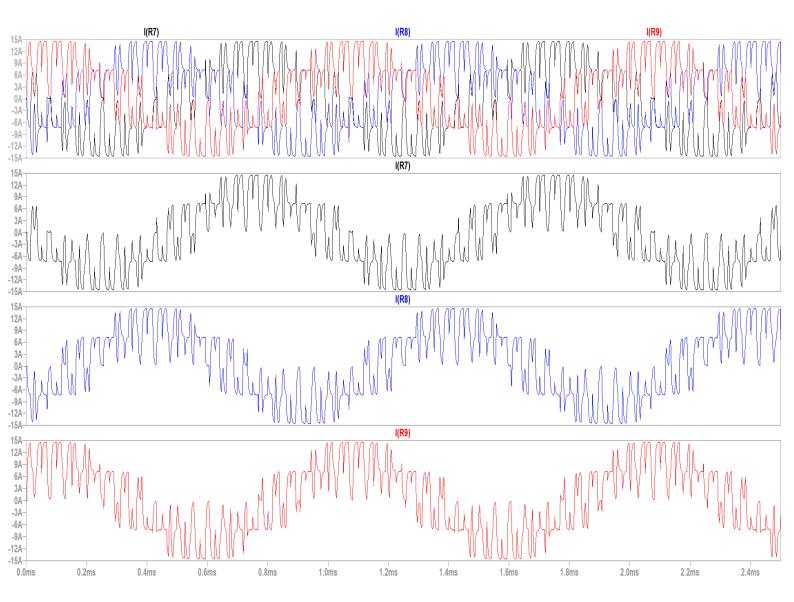

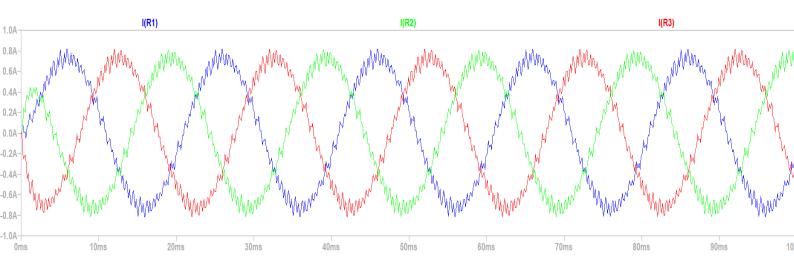

| Figure 76. Current passing through the lines                                                                                                                                                                                      | . 76 |

| Figure 77. Current passing through the lines                                                                                                                                                                                      | . 77 |

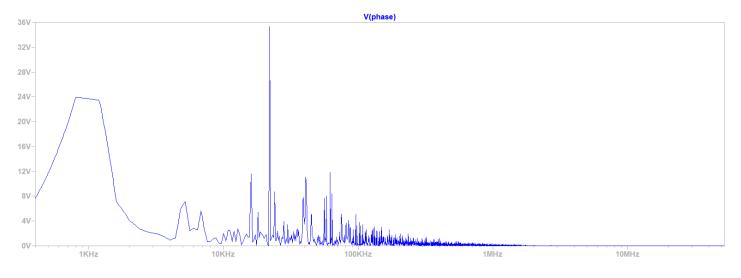

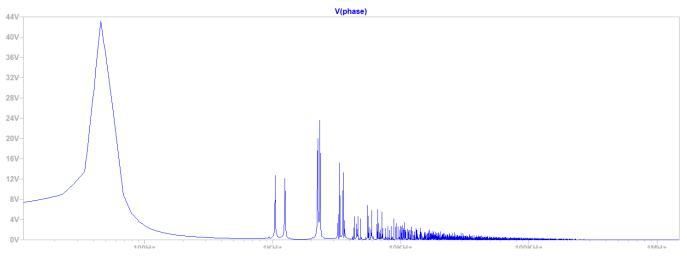

| Figure 78. FFT on V(Phase) SPWM Case 1.                                                                                                                                                                                           |      |

| Figure 79. SPWM Case 1 THD.                                                                                                                                                                                                       | . 79 |

| Figure 80. Three-Phase inverter with SPWM case 2                                                                                                                                                                                  | . 80 |

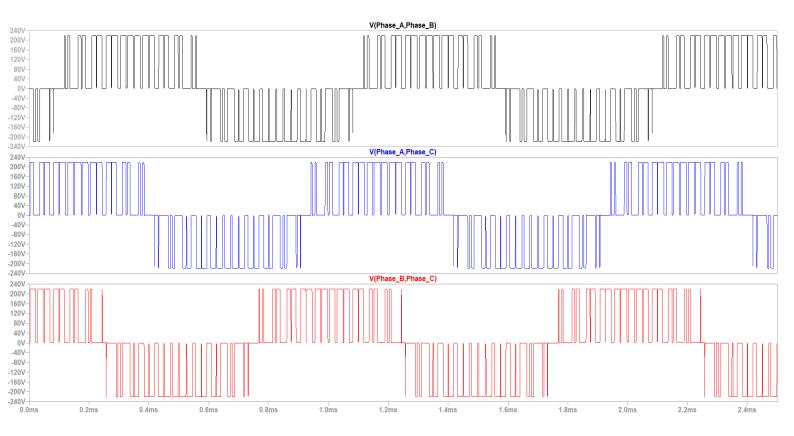

| Figure 81. Voltage passing through the 3 phases.                                                                                                                                                                                  | . 80 |

| Figure 82. Current passing through the lines                                                                                                                                                                                      | . 81 |

| Figure 83. FFT SPWM Case 2.                                                                                                                                                                                                       |      |

| Figure 84. THD of SPWM case 2                                                                                                                                                                                                     |      |

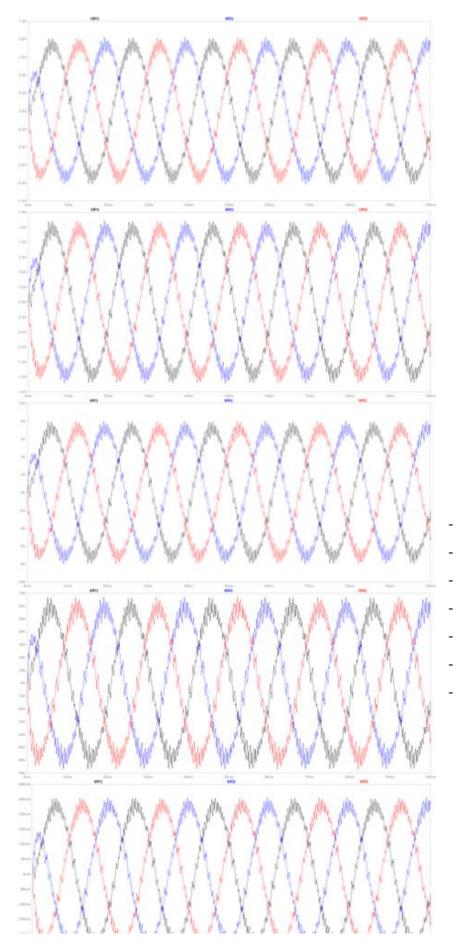

| Figure 85. Comparison of the resultant waveform with different loads. a) load 1 b) load 2 c                                                                                                                                       | )    |

| load 3 d) load 4 e) load 5                                                                                                                                                                                                        |      |

| Figure 86. Comparison of the THD results with different loads. a) load 1 b) load 2 c) load 3                                                                                                                                      |      |

| load 4 e) load 5                                                                                                                                                                                                                  |      |

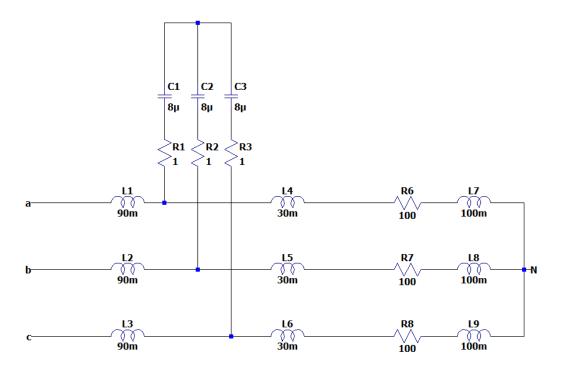

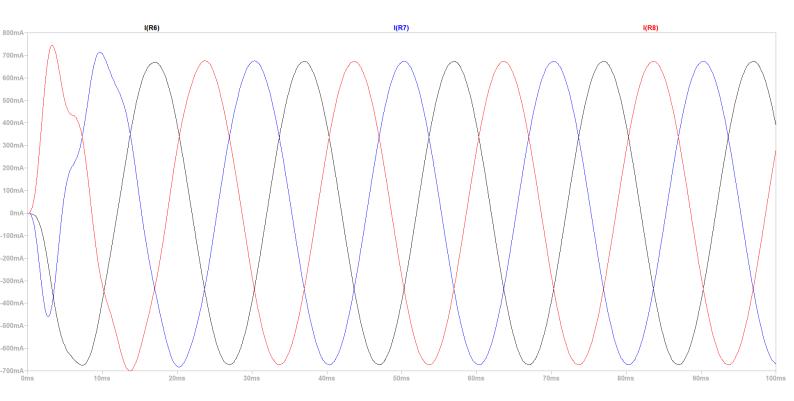

| Figure 87. LCL filter.                                                                                                                                                                                                            |      |

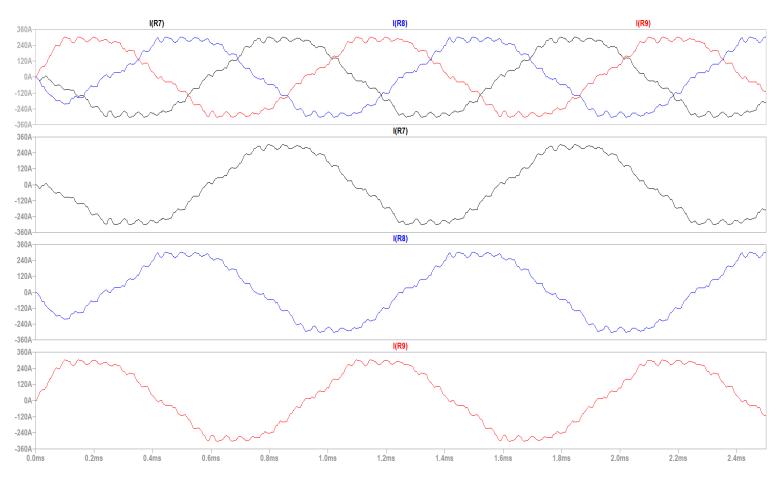

| Figure 88. Resultant waveform with a LCL filter.                                                                                                                                                                                  |      |

| Figure 89. THD of the inverter with a LCL filter                                                                                                                                                                                  | . 86 |

# LIST OF TABLES

| Table 1. Switching states for a half-bridge single-phase VSI.                           | 15 |

|-----------------------------------------------------------------------------------------|----|

| Table 2. Switching angles when $ma = 0.9$                                               | 19 |

| Table 3. Switching states for a Full-Bridge single-phase VSI.                           | 20 |

| Table 4. Valid switch states for a three-phase VS                                       | 24 |

| Table 5. Comparison of traditional and multilevel inverter                              | 24 |

| Table 6. Voltage levels of five-level DC-MLI and switching states.                      | 27 |

| Table 7. Voltage levels of five-level DC-MLI and switching states.                      | 29 |

| Table 8. Comparison between three basic Multi-level topologies.                         | 31 |

| Table 9. Switching states and definitions                                               | 37 |

| Table 10. The most appropriate control scheme and application matching diagram accordin | ng |

| to topologies.                                                                          | 40 |

#### **INTRODUCTION**

**Relevance of the topic.** In the field of the power electronics the Voltage Source Inverters (VSI) play a key role in a variety of applications, specially three-phase inverters, from generation systems to electric motor control. The main objective of static power converters is to produce an ac output waveform from a dc power supply. The basic operation of a three-phase inverter is based on the principle of switching semiconductor devices, such as power transistors, to control the direction and amplitude of the current in each phase. This is achieved through different modulations, which will be explained and discussed in this paper, including circuits to show how they work. The most important one is PWM which consists of varying the duration of the current pulses as a function of a reference signal.

A fundamental aspect in the design of a three-phase inverter is the generation of the PWM modulation signal. There are different modulation techniques, such as Space Vector Pulse Width Modulation (SVPWM) and Triangle Carrier Modulation (PWM). These techniques allow to control the output amplitude and frequency of the alternating current generated by the inverter.

Three-phase inverters find applications in various sectors, such as the generation and distribution of electric power, renewable energy systems, electric motor drive, electric vehicle traction systems, among others. In power generation systems, three-phase inverters are used to convert power generated by renewable sources, such as solar panels or wind turbines, into alternating current synchronized with the electrical grid. Due to the green transition accelerated in the last years and specially with the war in Russia, three-phase inverters are becoming more important, and they will play an even more important role in the future as solar energy is becoming one of the most promising and installed renewable energy.

One of the most prominent benefits of three-phase inverters is their ability to supply higher power compared to single-phase inverters. In addition, the three-phase connection allows a better balance of the load and a greater efficiency in the transmission of energy. This makes them an ideal choice in applications that require high power levels, such as heavy industry.

The design and control of three-phase inverters have also benefited from advances in power electronics and high-power semiconductor devices. The use of technologies such as IGBTs (insulated gate transistors with high voltage and high current blocking capacity) has allowed improving the efficiency and reliability of inverters, as well as reducing their size and associated costs.

In summary, three-phase inverters are fundamental devices in the field of power electronics, allowing the conversion of direct current into three-phase alternating current. Their ability to supply power to three-phase loads efficiently and reliably makes them indispensable in various applications.

**Research object** – High power three-phase inverters.

**Aim** – The aim of the works is to study and the importance of three-phase inverters in the grid system and to analyse how their beahaviour through practical work.

#### Tasks:

- 1. Study the different types of inverters and their different uses.

- 2. Study the most important modulation techniques and explain how they work.

- 3. Investigate the elements that can be added to the imnverters to improve their operation.

- 4. Create different circuits changing some elements and parameters to analyze its behaviour.

**Research Methods.** Electrical books, scientific papers and softwares to create electrical circuits.

#### **1. DESCRIPTIVE PART**

#### **1.1. Voltage Source Inverters**

Voltage source inverters (VSI's) basically convert DC voltage into AC voltage. The shape of the ideal VSI output voltage waveform should be independent of the load connected to the inverter, they are extensively necessitated for the commercial purpose as well as for the industrial applications these include adjustable speed drives (ASD), uninterruptable power supplies (UPS), active filters, Flexible AC transmission systems (FACTS), voltage compensators, and photovoltaic generators (S. Kharjule, 2015). Voltage source inverters can be used practically in both single-phase and three-phase applications.

To work as a switches VSI's are composed with semiconductor devices. These devices tend to approximate ideal switches, but they differ in some aspects:

- Limits on the amount and direction of on-state current.

- a nonzero on-state voltage drops (such as a diode forward voltage).

- some levels of leakage current when the device is supposed to be off.

- limitations on the voltage that can be applied when off.

- Operating speed. The transition between on-state and off-state, this is one of the key aspects of the different semiconductor devices.

Many different types of semiconductors have been applied in VSI's. In general, these fall into two groups:

• Diodes, widely used in rectifiers and in supporting roles.

• Transistors, suitable for control of single-polarity circuits, in this work we will focus in IGBT and MOSFET.

#### 1.1.1. Diodes

Among all the static switching devices used in power electronics, the power diode is perhaps the simplest.

It is a two-terminal device, and terminal A is known as the anode whereas terminal K is known as the cathode. If terminal A experiences a higher potential compared to terminal K, the device is said to be forward biased, and a current called forward current  $(I_f)$  will flow through the device in the direction as shown. This causes a small voltage drop across the device (<1V), which in ideal condition is usually ignored. On the contrary, when a diode is reverse biased, it does not conduct and a practical diode do experience a small current flowing in the reverse direction called the leakage current. Both the forward voltage drop and the leakage current are ignored in an ideal diode. Usually in power electronics applications a diode is an ideal static switch (Rashid, 2017).

Current ratings from under 1 A to more than 5000 A. Voltage ratings from 10V to 10 kV or more. The fastest power devices switch in less than 10 ns, whereas the slowest require 100µs or more.

Figure 1. Diode quadrant.

Current ratings from under 1 A to more than 5000 A. Voltage ratings from 10V to 10 kV or more. The fastest power devices switch in less than 10 ns, whereas the slowest require 100µs or more.

Among all the static switching devices used in power electronics, the power diode is perhaps the simplest.

Figure 2. Device symbol. Carries in one direction, blocks in the other.

#### 1.1.2. Transistors

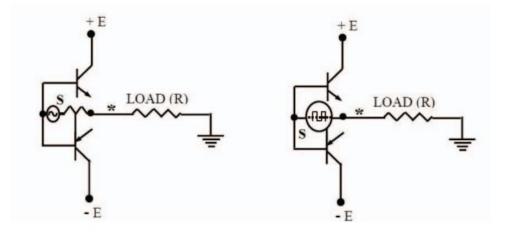

Initially the DC to AC conversion is carried out by using the transistors. The basic circuit of the DC to AC conversion consist of two transistors. One is pnp transistor and the other is npn transistor.

Figure 3. Transistorized VSI

As shown in the Fig. 3 the transistors are connected in push-pull manner and operates in common emitter configuration. The base and emitter of both the transistors are shorted. Collector of npn transistor is connected to positive DC supply (E+), and collector of the pnp transistor is connected to the negative DC supply (E-). The resistive load is connected between the emitter shortening point and the power supply ground. For the positive voltage the npn transistor conducts and we get the positive pulse at the output and for the negative supply voltage pnp transistor conducts and we get the negative pulse at the output voltage.

There exist different types of transistors and depending on the characteristics of the circuit and the application of the VSI they are used. The most important are IGBT and MOSFET.

#### 1.1.3. IGBT

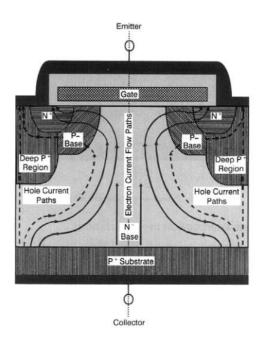

IGBT comprises a repetitive array of millions of cells arranged, in a topological layout, providing a large aspect ratio: with versus length (W/L). Fig. 4 shows a three-dimension image of the transistor.

Figure 4. IGBT unit cell.

IGBT devices have the following characteristics (Khanna & kumar, 2004):

- Two-carrier device.

- Operates by minority carrier diffusion.

- Current driven.

- Collector current  $\alpha$  emitter length and area.

- Higher breakdown voltage requires lightly doped collector region.

- Current density for given voltage drop is medium and severe trade-off exists with

switching speed.

- Positive temperature coefficient of collector current.

- Charge stored in based and collector.

- Low input impedance.

- Devices cannot be easily paralleled.

- Lower switching speed tan MOSFETs.

- Ratings from 10 A to more than 600 A, with voltages of 600 to 2500V.

- The IGBT is popular in inverters from about 1 to 200kW or more. It is found almost exclusively in power electronics applications.

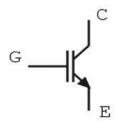

Figure 5. Device symbol

Figure 6. Quadrant operation. Carries or blocks current in one direction.

#### 1.1.4. MOSFET

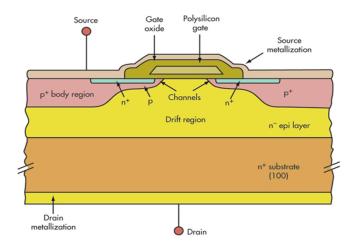

MOSFET is the fastest power switching device with a high switching frequency, up to 1MHz. Unlike other types of MOSFET power MOSFET use vertical channel structure in order to increase the device power rating (USA Department of Energy, 2009). In the vertical channel structure, the source and drain are in opposite side of the silicon waver. Figure 7 shows vertical cross-sectional view for a power MOSFET.

Figure 7. Vertical cross-sectional view for a power MOSFET

The P–N junction between p-base (also referred to as body or bulk region) and the ndrift region provide the forward voltage blocking capabilities. The source metal contact is connected directly to the p-base region through a break in the n+ source region in order to allow for a fixed potential to p-base region during the normal device operation. When the gate and source terminal are set the same potential ( $V_{GS} = 0$ ), no channel is established in the p-base region. The lower doping in the n-drift region is needed in order to achieve higher drain voltage blocking capabilities. For the drain–source current,  $i_D$ , to flow, a conductive path must be established between the n+ and n–regions through the p-base diffusion region.

MOSFET devices have the following characteristics:

- Single-carrier devices.

- Voltage driven.

- Less drive power needed than IGBT.

- Higher breakdown is achieved using lightly doped drain region.

- Current density is high at low voltages and low at high voltages.

- Negative temperature coefficient of drain current.

- No charge store.

- High input impedance.

- More linear operation and less harmonics.

- Sharing current in parallel devices is possible.

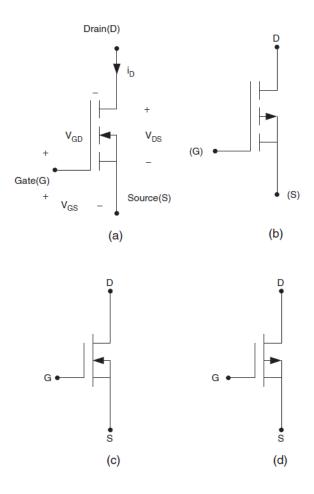

Figure 8. Device symbols: (a) n-channel enhancement-mode; (b) p-channel enhancement-mode; (c) nchannel depletion-mode; and (d) p-channel depletion-mode

Figure 9. MOSFET quadrant operation. Carries in one direction or blocks in both directions.

### 1.2. Single-phase Voltage Source Inverters

Single-Phase VSI can be found as half-bridge and full-bridge topologies. The power range that the can cover is the low one, however they are widely use in different fields as power supplies or single-phase ups (Xue, Chang, Kjaer, Bordonau & Shimizu, 2004). In the following chapters the most important configurations will be discussed.

#### **1.3 Half-Bridge VSI**

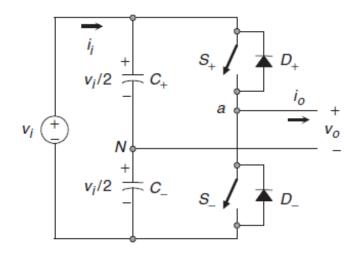

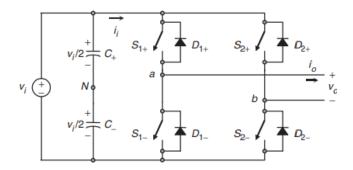

Fig. 10 shows the standard topology of a half-bridge VSI, in this circuit, two capacitors are needed to give a neutral point N, these capacitors are needed to keep a constant voltage  $v_i/2$ . How the current harmonics injected by the operation of the inverter are low-order harmonics, a set of large capacitors (C+ and C-) is required. Looking at the circuit is obvious that both switches cannot be on at the same time, in that case a short circuit across the dc link voltage source  $v_i$  would appear.

Figure 10. Single-phase half-bridge VSI.

There are two defined (states 1 and 2) and one undefined (state 3) switch state as shown in the table. With the aim to avoid short circuit across the dc bus and the undefined state mentioned before, the modulation technique used should always ensure that at any instant either the top or the bottom switch of the inverter leg is on.

| State                        | State# | $v_0$  | Components conducting  |

|------------------------------|--------|--------|------------------------|

| $S_+$ is on and $S$ is       | 1      | $v_1$  | $S_{+}$ if $i_{0} > 0$ |

| off                          |        | _      | $D_1$ if $i_0 < 0$     |

| $S_{-}$ is on and $S_{+}$ is | 2      | $-v_2$ | $D_2$ if $i_0 > 0$     |

| off                          |        | _      | $S_{-}$ if $i_0 > 0$   |

| $S_+$ and $S$ are all        | 3      | $v_1$  | $D_2$ if $i_0 > 0$     |

| off                          |        |        | $D_1$ if $i_0 < 0$     |

|                              |        | $-v_2$ |                        |

**Table 1.** Switching states for a half-bridge single-phase VSI.

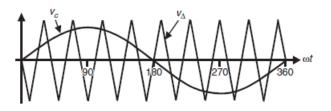

The carrier-based PWM technique fulfills such a requirement as it defines the on- and off-states of the switches of one leg of a VSI by comparing a modulating signal  $v_c$  (desired ac output voltage) and a triangular waveform  $v_{\Delta}$  (carrier signal). When  $v_c > v_{\Delta}$  the switch  $S_+$  is on and the switch  $S_-$  is off, at the same time when  $v_c < v_{\Delta}$  the switch  $S_+$  is off and the switch  $S_-$  is on.

A different case is when the modulating signal  $v_c$  is a sinusoidal at frequency  $f_c$  and amplitude  $\nabla_c$ , and the triangular signal  $v_{\Delta}$  is at frequency  $f_{\Delta}$  and amplitude  $\nabla_{\Delta}$ . This is the sinusoidal PWM (SPWM) scheme. In this case, the modulation index  $m_a$  (also known as the amplitude-modulation ratio) is defined as:

$$m_a = \frac{\nabla_c}{\nabla_\Delta} \tag{1}$$

and the normalized carrier frequency  $m_f$  (also known as the frequency-modulation ratio) is:

$$m_f = \frac{f_\Delta}{f_c} \tag{2}$$

he PWM technique permits an ac output voltage to be created that cracks a given modulating signal. When the modulating signal is sinusoidal, the SPWM provides, in the linear region, an ac output voltage that varies linearly as a function of the modulation index, and the harmonics are at well-defined frequencies and amplitudes. These characteristics help to simplify the design of filtering components.

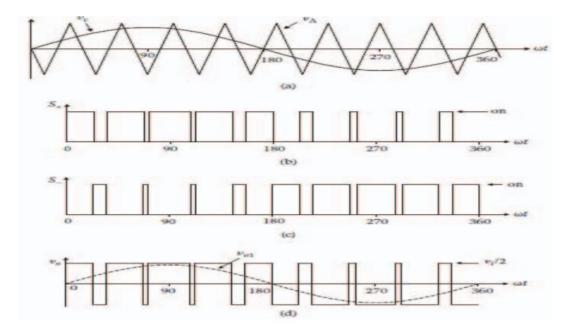

In the following figures we have the half-bridge VSI Ideal waveforms for the SPWM  $(m_a = 0.8, m_f = 9)$ :

Figure 11. Carrier and modulating signals.

Figure 12. Q1 switch state (left) Q2 switch state (right).

Figure 13. AC output current.

for large values of  $m_f$  ( $m_f > 21$ ), the subharmonics are negligible if an asynchronous PWM technique is used, however, due to potential very low-order subharmonics, its use should be avoided; finally, in the overmodulation region ( $m_a > 1$ ) some intersections between the carrier and the modulating signal are missed, which leads to the generation of low-order harmonics but a higher fundamental ac output voltage is obtained.

The PWM technique allows an ac output voltage to be generated that tracks a given modulating signal.

#### 1.3.2. Square wave modulating technique.

In this case, both switches  $S_+$  and  $S_-$  are on for one half-cycle of the ac output period. This technique is very similar to SPWM but with an infinite modulation index  $m_a$ .

Figure 14. Normalized fundamental ac component of the output voltage in a half-bridge VSI SPWM modulated.

The normalized ac output voltage harmonics are at frequencies h = 3,5,7,9... and for a given dc link voltage we can obtain the ac output voltage features an amplitude given by:

$$\nabla_{o1} = \nabla_{aN1} = \frac{4}{\pi} \frac{v_i}{2} \tag{3}$$

And the harmonics feature an amplitude given by:

$$\nabla_{oh} = \frac{\nabla_{o1}}{h} \tag{4}$$

The ac output voltage cannot be changed by the inverter. However, by controlling the dc link voltage  $v_i$  it could be changed (Youssef, 2020).

#### 1.3.3. Selective harmonic elimination (SHE).

In SHE technique, low-order unwanted harmonics are eliminated by determining the angle of the gating pulse of the switch. The inverter voltage equation is expressed in Fourier series as in (5)

$$V(\omega t) = \sum_{n=1}^{\infty} [a_n \sin(n\omega t) + b_n \cos(n\omega t)]$$

(5)

Owing to the PWM waveform characteristics of odd functions and quarter-wave symmetry,  $a_n=0$ , for all *n*, and the output voltage reduces to:

$$V(\omega t) = \sum_{n=1}^{\infty} b_n \sin(n\omega t)$$

(6)

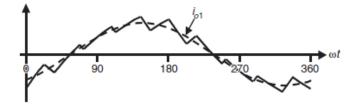

Where  $\omega$  is the radian frequency of the output voltage. Based in the equation above  $b_n$  is expanded regards to number of switching angles and fundamental output voltage, as we can see in (7). Fig.15 shows the sample of output voltage with few notches per quarter-wave cycle.

$$b_n = \frac{2V_{dc}}{n\pi} \left[2\sum_{k=1}^{N} (-1)^{k-1} \cos n\alpha_k - 1\right]$$

(7)

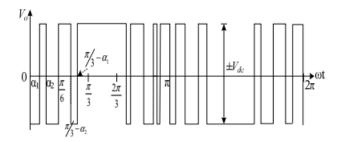

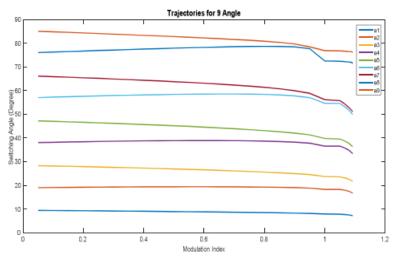

With the use of pre-determined lookup table, the trajectories of switching angles over a  $\frac{1}{2\pi}$  period lie between 0° and 90° when  $3^{rd}$ ,  $5^{th}$ ,  $7^{th}$ ,  $9^{th}$ ,  $11^{th}$ ,  $13^{th}$ ,  $15^{th}$ ,  $17^{th}$  harmonic orders are eliminated (Azmi, Shukor & Rahim, 2018)

Figure 15. Unipolar output voltage with notches per quarter-wave cycle.

Fig.16 shows the trajectories of switching angles with varying modulation index. Table 2 lists the switching angles plotted in Fig.15 when  $m_a$  is 0.9.

Figure 16. Switching angle trajectories when nine angles are eliminated.

**Table 2.** Switching angles when ma = 0.9.

|   | α1   | α2    | α3    | $\alpha_4$ | $\alpha_5$ | α <sub>6</sub> | $\alpha_7$ | α <sub>8</sub> | α9    |

|---|------|-------|-------|------------|------------|----------------|------------|----------------|-------|

| 8 | 3.29 | 19.06 | 24.98 | 38.22      | 42.05      | 57.75          | 59.95      | 78.42          | 79.66 |

#### 1.4 Full-Bridge VSI

Fig. 17 shows the power topology of a full-bridge VSI. Is quite similar to the Halfbridge inverter but with two extra switches.

Figure 17. Single-phase full-bridge VSI

In all inverters, if the load is pure resistive, the current waveform is the same as the voltage waveform, with the corresponding scale. However, when the load has reactive components, the intensity will be positively or negatively outdated against the voltage. At intervals where the current and voltage do not coincide in sign, the switches shall be cut in need of the incorporation of diodes in antiparallel, to enable a bidirectional switch in current.

In the table below the switch states of a full-bridge inverter are shown.

| State                                                          | State# | $v_0$          | Components conducting                         |

|----------------------------------------------------------------|--------|----------------|-----------------------------------------------|

| $S_{1+}$ and $S_{2-}$ are on and $S_{1-}$ and $S_{2+}$ are off | 1      | $v_0$<br>$v_1$ | $S_{1+}$ and $S_{2-}$ if $i_0 > 0$            |

|                                                                |        | •1             | $D_1$ and $D_4$ if $i_0 < 0$                  |

| $S_{1-}$ and $S_{2+}$ are on and $S_{1+}$ and $S_{2-}$ are off | 2      | $-v_1$         | $D_3$ and $D_2$ if $i_0 > 0$                  |

|                                                                |        |                | $S_{1-}$ and $S_{2+}$ if $i_0 < 0$            |

| $S_{1+}$ and $S_{2+}$ are on and $S_{1-}$ and $S_{2-}$ are off | 3      | 0              | $S_{1+}$ and $D_2$ if $i_0 > 0$               |

|                                                                |        |                | $D_1 \text{ and } S_{2+}  \text{if } i_0 < 0$ |

| $S_{1-}$ and $S_{2-}$ are on and $S_{1+}$ and $S_{2+}$ are off | 4      | 0              | $D_3$ and $S_{2-}$ if $i_0 > 0$               |

|                                                                |        |                | $S_{1-}$ and $D_4$ if $i_0 < 0$               |

| $S_{1+}, S_{2+}, S_{1-}$ and $S_{2-}$ are all off              | 5      | $v_1$          | $D_3$ and $D_2$ if $i_0 > 0$                  |

|                                                                |        |                | $D_1$ and $D_4$ if $i_0 < 0$                  |

|                                                                |        | $-v_1$         |                                               |

**Table 3**. Switching states for a Full-Bridge single-phase VSI.

Keeping  $S_{1+}$  and  $S_{2-}$  excited (state 1), the a-end of the charge is connected to the positive pole of the battery and the b end to the negative pole, leaving the charge subjected to the VS voltage of the battery. By blocking  $S_{1+}$  and  $S_{2-}$  and exciting  $S_{2+}$  and  $S_{1-}$  (state 3), the tension in the load is reversed. Alternatively, the load is subjected to a square alternating voltage of the amplitude equal to the VS battery voltage, which is an advantage over the inverter with a medium battery. In contrast, double semiconductors are needed here (Soomro, Memon, Tayab & Shah, 2016).

Several modulating techniques have been developed that are applicable to full-bridge VSIs. Among all of them are the PWM (bipolar and unipolar) techniques.

#### 1.4.1. Bipolar PWM technique.

A bipolar switching scheme implemented on full bridge inverter is called a two-level inverter, since output voltage switches between two states either positive or negative value of applied voltage as shown in fig. 18(d).

In bipolar switching scheme, carrier and modulating signal are compared. The inverter switches are turned on whenever the reference signal is greater than the carrier signal and vice versa.

This resulting gate pulse shown in fig. 18(b) is applied to switches  $S_{1+}$  and  $S_{2-}$  of the inverter while its inverted gate pulse is applied to switches  $S_{2+}$  and  $S_{1-}$  as shown in fig. 18(c).

Figure 18. Bipolar Switching scheme.

The ac output voltage waveform in a full-bridge VSI consists basically in a sinusoidal waveform that faces a fundamental component of amplitude  $\nabla_{o1}$  that accomplishes the expression:

$$\nabla_{o1} = \nabla_{ab1} = \nabla_i \mathbf{m}_a \tag{8}$$

in the linear region of the modulating technique ( $m_a \le 1$ ), which is twice that obtained in the half-bridge VSI. Identical conclusions can be drawn for the frequencies and the amplitudes of the harmonics in the ac output voltage and dc link current, and for operations at smaller and larger values of odd mf (including the overmodulation region ( $m_a > 1$ ), than in half-bridge VSIs, but considering that the maximum ac output voltage is the dc link voltage  $v_i$ . Thus, in the overmodulation region the fundamental component of amplitude  $\nabla_{o1}$  satisfies the expression:

$$v_i < \nabla_{o1} = \nabla_{ab1} < \frac{4}{\pi} v_i \tag{9}$$

#### 1.4.2. Unipolar switching technique.

A unipolar switching scheme implemented on full bridge inverter is called a two-level inverter, since output voltage switches between two states either positive or negative value of applied voltage as shown in fig. 19(d).

In unipolar PWM, two sinusoidal signals having  $180^{\circ}$  phase shift are taken having same magnitude and frequency. The two sinusoidal signals are compared with same triangular pulse. The gate signal for switch  $S_{1+}$  is generated by comparing positive reference signal and triangular signal as shown in fig. 19(b) while comparing 180 phase shifted reference signal and triangular signal results in gate signal for switch  $S_{1-}$  as shown in fig. 19(c).

The switch  $S_{2+}$  has complementary switching as compared to  $S_{1+}$  and similarly switch  $S_{2-}$  has complementary switching as compared to  $S_{1-}$ .

Figure 19. Unipolar Switching scheme.

This feature is considered to be an advantage because it allows the use of smaller filtering components to obtain high-quality voltage and current waveforms while using the same switching frequency as in VSIs modulated by the bipolar approach.

#### 1.5 Three-Phase VSI

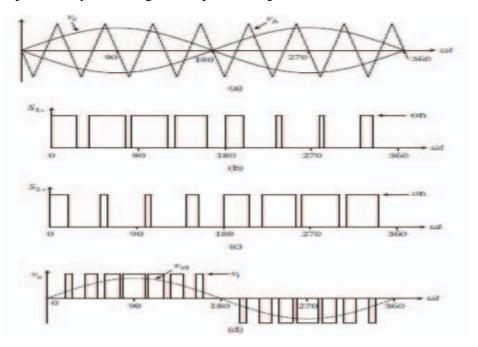

While single-phase VSIs cover low-range power applications and three-phase VSIs cover medium- to high-power applications. The main purpose of these topologies is to provide a three-phase voltage source, where the amplitude, phase, and frequency of the voltages should always be controllable. Although most of the applications require sinusoidal voltage waveforms (e.g. ASDs, UPSs, FACTS, var compensators), arbitrary voltages are also required in some emerging applications (e.g. active filters, voltage compensators). The standard three-phase VSI topology is shown in Fig. 20.

Figure 20. Conventional Three-phase VSI topology

The switching estates are given in Table 4. It is likely to single-phase VSI, the switches of any leg of the inverter ( $S_1$  and  $S_4$ ,  $S_3$  and  $S_6$  or  $S_5$  and  $S_2$ ) cannot be witched at the same time, since it would result in a short-circuit across the dc link voltage supply. Similarly, in order to avoid undefined states in the VSI, and thus undefined ac output line voltages, the switches of any leg of the inverter cannot be switched off simultaneously as this will result in voltages that will depend upon the respective line current polarity.

Two of the states from the table produce zero ac line voltages (7 and 8) the remaining states produce non-zero ac line voltages. In order to generate a given voltage waveform, the inverter moves from one state to another. Thus, the resulting ac output line voltages consist of discrete values of voltages that are  $v_i$ , 0, and  $-v_i$  for the topology shown in Fig. 20. The selection

of the states in order to generate the given waveform is done by the modulating technique that should ensure the use of only the valid states.

| State                                      | State | $v_{ab}$ | $v_{bc}$ | $v_{ca}$ | Space vector                         |

|--------------------------------------------|-------|----------|----------|----------|--------------------------------------|

|                                            | #     |          |          |          |                                      |

| $S_1, S_2, S_6$ on and the rest, off       | 1     | $v_i$    | 0        | $-v_i$   | $\overrightarrow{v_1} = 1 + j0.577$  |

| $S_2$ , $S_3$ , $S_1$ on and the rest, off | 2     | 0        | $v_i$    | $-v_i$   | $\overrightarrow{v_2} = j1.155$      |

| $S_3$ , $S_4$ , $S_2$ on and the rest, off | 3     | $-v_i$   | $v_i$    | 0        | $\vec{v_3} = -1 + j0.577$            |

| $S_4$ , $S_5$ , $S_3$ on and the rest, off | 4     | $-v_i$   | 0        | $v_i$    | $\overrightarrow{v_4} = -1 + j0.577$ |

| $S_5$ , $S_6$ , $S_4$ on and the rest, off | 5     | 0        | $-v_i$   | $v_i$    | $\overrightarrow{v_5} = -j1.155$     |

| $S_1, S_5, S_6$ on and the rest, off       | 6     | $v_i$    | $-v_i$   | 0        | $\overrightarrow{v_6} = 1 - j0.577$  |

| $S_1$ , $S_3$ , $S_5$ on and the rest, off | 7     | 0        | 0        | 0        | $\overrightarrow{v_7} = 0$           |

| $S_4$ , $S_2$ , $S_6$ on and the rest, off | 8     | 0        | 0        | 0        | $\overrightarrow{v_8} = 0$           |

#### **1.6 Multilevel inverters**

Conventional two-level inverter produces only two levels in the output voltage and PWM is used to form the AC output waveform. Even though the AC output waveform is produced it includes harmonics and these causes the high rate of change of voltage as compared to the multilevel inverter (Krishna & Padma, 2016). Some devices requests for low rate of change in voltage.

Multilevel inverters generate more than two voltage levels with almost pure sinusoidal voltage waveform, all of this with a low dv/dt and low harmonic distortions (Nordwall, 2011). Multiple voltage levels in the output waveform turns this smoother but with increasing levels the circuit becomes more complex due to the addition of the extra valves. Because of the complexity of the circuit a complicated control is also required.

In the following table we have a brief comparison of conventional and multilevel inverter (Kosti, Amol and Rao, 2017).

| TRADITIONAL                        | MULTILEVEL                              |  |  |  |

|------------------------------------|-----------------------------------------|--|--|--|

| High rate of change of voltage     | Low range of change of voltage          |  |  |  |

| Switching losses are high          | Switching losses are low                |  |  |  |

| For low voltage application        | For high voltage application            |  |  |  |

| Voltage stress is more on switches | Voltage is less on switches             |  |  |  |

| High switching frequency           | Low switching frequency                 |  |  |  |

| Multiple voltage levels cannot be  | Multiple voltage levels can be produced |  |  |  |

| produced                           |                                         |  |  |  |

| More harmonics                     | Less harmonics                          |  |  |  |

Table 5. Comparison of traditional and multilevel inverter.

#### **1.7 Multilevel inverters topologies**

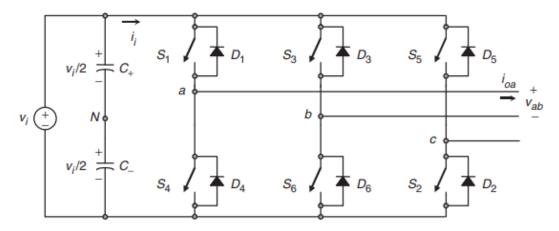

Three major multilevel inverter structures have been mostly applied in industrial applications classified according to the voltage source used in the inverter. Fig.21 shows them. Moreover, different hybrid multilevel inverters have been developed (Bendre, Krstic Meer, Venkataramanan, 2005).

Figure 21. Classification of multilevel inverter topologies according to the voltage source

#### 1.7.1 Diode clamped multilevel inverter.

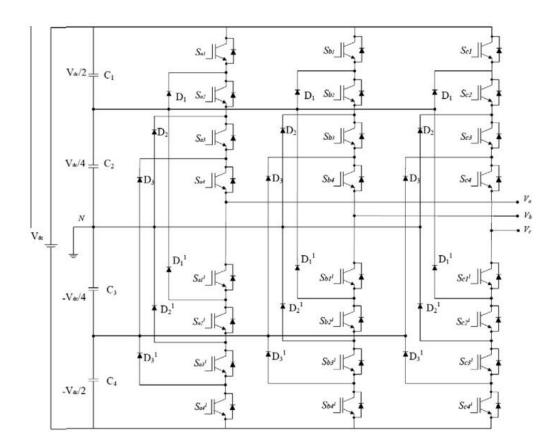

There exist DC-MLIs with three, four five and six levels for different uses like static VAR compensators, high voltage grid interconnections, and variable speed motor drives.

In the Fig. 22 a three-phase five-level DC-MLI topology is shown. Each of the threephase outputs of inverter shares a common DC bus voltage that has been divided into five levels over four DC bus capacitors. The capacitors have been subscripted from  $C_1$  to  $C_4$ . The middle point of  $C_2$  and  $C_3$  capacitors constitute the neutral point of inverter and output voltages have five voltage states referring to neutral point. The voltage across each capacitor is  $V_{dc}$  /4 and the voltage stress on each switching device is limited to  $V_{dc}$  through the clamping diodes that have been named as  $D_{1.3}$  and  $D_{1.3^*}$ .

Figure 22. Three-phase five-level topology of a diode clamped multilevel inverter.

Clamping diodes are the key components that differ this topology from a conventional two-level inverter. The neural point n has been assumed as the output phase voltage reference and the switching combinations have been analyzed for phase A output voltage  $V_{an}$  as we can observe in Table 6.

For the five-level DC-MLI in Fig. 22, a set of four switches is ON at any given period and they are S\_a1 to S\_a4 for voltage level of  $V_{an} = V_{dc}/4$ . The second switching state shows the voltage level of  $V_{an} = V_{dc}/4$  and  $S_{a2}$  to  $S_{a1}$  switches should be triggered. The remaining switching states that constitute 0 and negative outputs can be seen in Table 6. The clamping diodes require different voltage ratings for reverse voltage-blocking due to each triggered switch is only required to block a voltage level of  $V_{dc}/(m-1)$ . By assuming the switches from  $S_{a1}$  to  $S_{a4}$  are triggered as seen in first line of Table 6,  $D_1$  blocking diode needs to block a voltage at the rate of  $3V_{dc}/4$  that is generated by three DC bus capacitors.

Since each blocking diode voltage rating is the same as the active device voltage rating, the number of diodes required for each phase will be calculated as  $(m-1)\times(m-2)$ , where m represents number of inverter levels. The following equations are used to determine the e required device numbers to form a given level of a diode clamped MLI. If m is assumed as the number of levels, the number of capacitors at the DC side (*c*) can be known by using Eq. (10). The number of freewheeling diodes (*d*) per phase, and the number of clamping diodes (*j*) can be calculated by using Eqs. (11) and (12) respectively.

$$c = m - 1 \tag{10}$$

$$d = 2(m - 1) \tag{11}$$

$$j = (m - 1) \times (m - 2) \tag{12}$$

| Voltage V <sub>an</sub> | Switching state |          |          |          |            |              |              |              |

|-------------------------|-----------------|----------|----------|----------|------------|--------------|--------------|--------------|

|                         | $S_{a1}$        | $S_{a2}$ | $S_{a3}$ | $S_{a4}$ | $S_{a1^*}$ | $S_{a2^{*}}$ | $S_{a3^{*}}$ | $S_{a4^{*}}$ |

| $V_4 = V_{dc}/2$        | 1               | 1        | 1        | 1        | 0          | 0            | 0            | 0            |

| $V_{3} = V_{dc}/4$      | 0               | 1        | 1        | 1        | 1          | 0            | 0            | 0            |

| $V_2 = 0$               | 0               | 0        | 1        | 1        | 1          | 1            | 0            | 0            |

| $V_1 = -V_{dc}/4$       | 0               | 0        | 0        | 1        | 1          | 1            | 1            | 0            |

| $V_0 = -V_{dc}/2$       | 0               | 0        | 0        | 0        | 1          | 1            | 1            | 1            |

**Table 6.** Voltage levels of five-level DC-MLI and switching states.

The DC-MLIs are quite efficient in fundamental switching applications, however the number of clamping diodes needed is quadratically related to the number of levels. Fundamental switching will cause an increment o voltage and current THD, while increased number of clamping diodes makes the topology bulky (Swarmy & Venkatesan, 2019) also in this case the cost and size of the system increases. To design more level inverter, DCI produces fewer harmonics. In this topology filters are not required (Çolak & Kabalci, 2008).

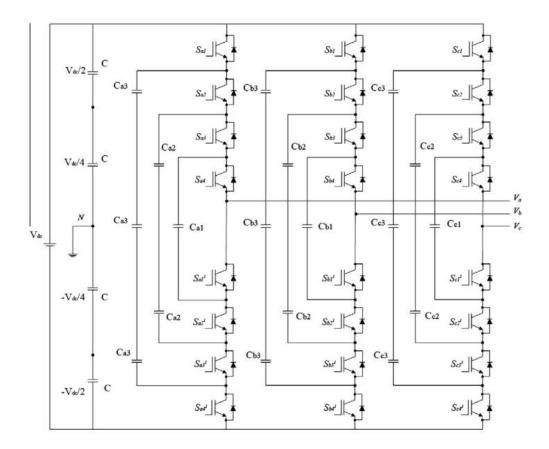

#### 1.7.2 Flying capacitor multilevel inverter

This type of inverter was introduced as an alternative to DC-MLI. In Fig.23 a threephase five-level topology of this inverter is shown. Main structure of this topology is similar to DC-MLI but the inverter uses DC side capacitors in a ladder form instead of clamping diodes. The voltage change between two adjoining capacitor legs gives the size of the voltage steps in the output waveform. In an m level structure, the FC-MLIs require (*m*-1) DC link capacitors and  $(m-1) \times (m-2)/2$  auxiliary capacitors per phase comparing to DC-MLI topology (Song, Kim, Lai, Seong, Kim & Park, 2001). By using a huge quantity of storage capacitors be able to ridethrough abilities throughout a power outage

In Fig. 23, each of the three-phase outputs of inverter shares a common DC bus voltage that has been divided into five levels over four DC bus capacitors like DC-MLI topology. The auxiliary capacitors ( $C_{a1}$ ,  $C_{a2}$ ,  $C_{a3}$ ) are pre-charged to the voltage levels of  $V_{dc}/4$ ,  $V_{dc}/2$ ,  $3V_{dc}/4$  V respectively. The pre-charge operation ensures the effectiveness of the inverter allowing it to generate multilevel voltage waveforms. Voltage synthesis in a five-level FC-MLI has more flexibility than a DC-MLI. The FC-MLI topology also consists of complementary switch pairs as ( $S_{a1} - S_{a1^*}$ )), ( $S_{a2} - S_{a2^*}$ )), ( $S_{a3} - S_{a3^*}$ )), and ( $S_{a4} - S_{a4^*}$ )) as seen in Fig. 23. The switching

pairs may differ as asymmetrically according to control strategies, but both pair selection strategy will cause the switching state redundancy that can be used to achieve voltage balancing in FC-MLIs (Kuhn, Ruger & Mertens, 2007).

Figure 23. Three-phase five-level topology of a flying capacitor multilevel inverter.

In table 7 we can observe the switching combinations for phase voltage output  $(V_{an})$  which is relative to neutral point of n. The optional switching states for voltage levels of  $V_{dc}/4$ , 0,  $-V_{dc}/4$  shows the phase redundancies of FC-MLI as an advantage to line-to-line redundancies of DC-MLI. This advantage allows the user to select charging and discharging orders of capacitors by constituting proper switching algorithms.

FC-MLI topology has introduced quite significant advantages, the most important are preventing the filter demand, and controlling the active and reactive power flow besides phase redundancies. Despite these advantages, the increment of m level will restrain the accurate charging and discharging control of capacitors. The cost of inverter will increase and device will be more enlarged due to increased number of capacitors. For real power transmission controlling of this topology is very difficult making switching losses and switching frequency losses are bigger (Rodriguez, Lai & Peng, 2002)

| Voltage V <sub>an</sub>           | Switching state |          |          |          |            |                                |                                |              |

|-----------------------------------|-----------------|----------|----------|----------|------------|--------------------------------|--------------------------------|--------------|

|                                   | $S_{a1}$        | $S_{a2}$ | $S_{a3}$ | $S_{a4}$ | $S_{a1^*}$ | <i>S</i> <sub><i>a</i>2*</sub> | <i>S</i> <sub><i>a</i>3*</sub> | $S_{a4^{*}}$ |

| $V_4 = V_{dc}/2$ $V_3 = V_{dc}/4$ | 1               | 1        | 1        | 1        | 0          | 0                              | 0                              | 0            |

| $V_{3} = V_{dc}/4$                | 1               | 1        | 1        | 0        | 1          | 0                              | 0                              | 0            |

|                                   | 0               | 1        | 1        | 1        | 0          | 0                              | 0                              | 1            |

|                                   | 1               | 0        | 1        | 1        | 0          | 0                              | 1                              | 0            |

| $V_2 = 0$                         | 1               | 1        | 0        | 0        | 1          | 1                              | 0                              | 0            |

|                                   | 0               | 0        | 1        | 1        | 0          | 0                              | 1                              | 1            |

|                                   | 1               | 0        | 1        | 0        | 1          | 0                              | 1                              | 0            |

|                                   | 1               | 0        | 0        | 1        | 0          | 1                              | 1                              | 0            |

|                                   | 0               | 1        | 0        | 1        | 0          | 1                              | 0                              | 1            |

|                                   | 0               | 1        | 1        | 0        | 1          | 0                              | 0                              | 1            |

| V <sub>1</sub>                    | 1               | 0        | 0        | 0        | 1          | 1                              | 1                              | 0            |

| $= -V_{dc}/4$                     | 0               | 0        | 0        | 1        | 0          | 1                              | 1                              | 1            |

|                                   | 0               | 0        | 1        | 0        | 1          | 0                              | 1                              | 1            |

| $V_0 = V_{dc}/2$                  | 0               | 0        | 0        | 0        | 1          | 1                              | 1                              | 1            |

Table 7. Voltage levels of five-level DC-MLI and switching states.

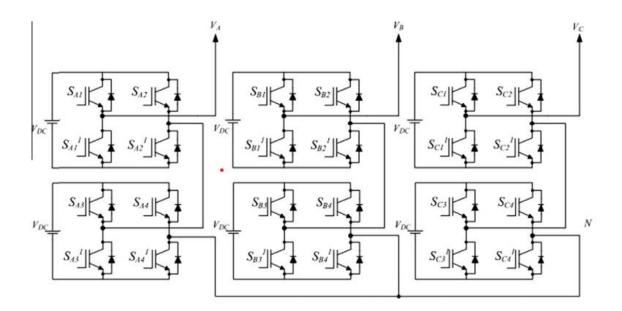

#### 1.7.3 Cascaded H-bridge multilevel inverters (CHB-MLI)

An alternative multilevel inverter topology with less power devices requirement compared to previously mentioned topologies is known as cascaded H-bridge multilevel inverter (CHB-MLI) and the topology is based on the series connection of H-bridges with separate DC sources. Since the output terminals of the H-bridges are connected in series, the DC sources must be isolated from each other. Owing to this property, CHB-MLIs have also been proposed to be used with fuel cells or photovoltaic arrays in order to achieve higher levels (Kuhn, Ruger & Mertens, 2007).

The resulting AC output voltage is synthesized by the addition of the voltages generated by different H-bridge cells. Each single-phase H-bridge generates three voltage levels as  $+V_{dc}$ , 0,  $-V_{dc}$  by connecting the DC source to the AC output by different combinations of four switches,  $S_{A1}$ ,  $S_{A1^*}$ ,  $S_{A2}$ ,  $S_{A2^*}$  as seen in first cell of Fig. 24. The CHB-MLI that is shown in Fig. 24 utilizes two separate DC sources per phase and generates an output voltage with five levels. To obtain  $+V_{dc}$ ,  $S_{A1}$  and  $S_{A2^*}$  switches are turned on, whereas  $-V_{dc}$  level can be obtained by turning on the  $S_{A2}$  and  $S_{A1^*}$ . The output voltage will be 0 by turning on  $S_{A1^*}$  and  $S_{A2}$  switches or  $S_{A1^*}$  and  $S_{A2}$  switches. If n is assumed as the number of modules connected in series, m is the number of output levels in each phase as seen in Eq. (13). The switching states of a CHB-MLI (*sw*) can be determined by using Eq. (14)

$$m = 2n + 1 \tag{13}$$

$sw = 3^n \tag{14}$

Figure 24. Three-phase five-level topology of cascaded H-bridge multilevel inverter

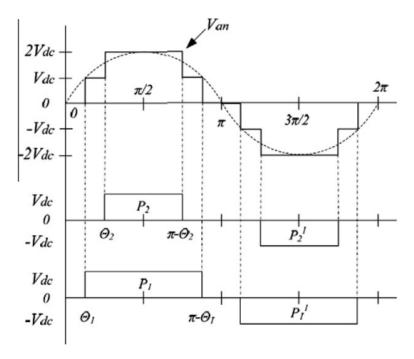

In Fig. 24 we can see that the first leg phase voltage  $(V_{an})$  is continued by multiplying  $V_{a1}$  and  $V_{a2}$  values of series connected H-bridge cells and will generate a stepped waveform as seen in Fig. 25.

Negative output pulses are indicated as  $P_{1^*}$  and  $P_{2^*}$  while the positive output pulses are shown  $P_1$  and  $P_2$ . The equation 15 shows the Fourier series expansion of the general multilevel stepped output voltage. In equation 16 *n* is the harmonic number of the output voltage of inverter.

Figure 25. Phase output voltage waveforms of a five-level topology CHB-MLI with two separate DC sources.

$$V(\omega t) = \frac{4V_{dc}}{\pi} \sum_{n=1,3,5...}^{\infty} [\cos(n\theta_1) + \cos(n\theta_1) + ... + \cos(n\theta_5)] \frac{\sin(n\omega t)}{n}$$

(15)

$$V(\omega t) = \frac{4V_{dc}}{\pi} \sum_{n=1,3,5...}^{\infty} \left[\cos(n\theta_1) + \cos(n\theta_1)\right] \frac{\sin(n\omega t)}{n}$$

(16)

CHB-MLIs have been previously designed for static VAR compensators and motor drives, but the topology has been prepared an interface with renewable energy sources due to using separate DC sources. There are numerous studies have been performed on CHB-MLIs for connecting renewable energy sources with AC grid and power factor correction.

They require lower number of components associated with all other converters to reach a similar number of output levels. For real power conversions required isolated dc sources for cascaded H-Bridge MLI. Table 8 indicates the comparison between three basic multi-level topologies.

| Topologies        | DC- MLIs           | FC- MLIs     | H-Bridge<br>MLIs |

|-------------------|--------------------|--------------|------------------|

| DC bus capacitors | (m-1)<br>m- Levels | (m-1)        | (m-1)/2          |

| Switching devices | 2(m-1)             | 2(m-1)       | 2(m-1)           |

| Clamping Diodes   | (m-1)(m-2)         | -            | -                |

| Flying capacitors | -                  | (m-1)(m-2)/2 | -                |

Table 8. Comparison between three basic Multi-level topologies.

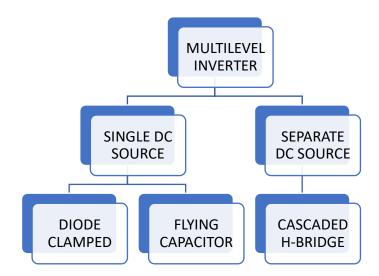

#### **1.8. Modulation techniques.**

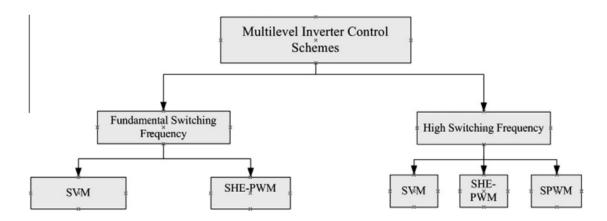

The efficiency parameters of a multilevel inverter such as switching losses and harmonic reduction are principally depended on the modulation strategies used to control the inverter. Multi-level inverter control techniques are based on fundamental and high switching frequency as we can see in Fig. 26

Figure 26. Classification of multilevel inverter control scheme based on switching frequency.

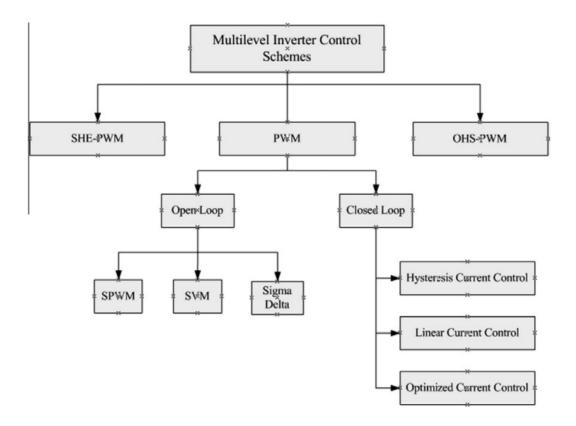

There exists also another popular classification for the multi-level inverters based on open loop and closed loop concepts as we can see in Fig. 27.

Figure 27. Control schemes of multilevel inverters.

Three main control techniques of multilevel inverters are SHE-PWM, PWM, and optimized harmonics stepped pulse width modulation (OHS–PWM). The open loop PWM techniques are SPMW, space vector PWM, sigma–delta modulation, while closed loop current control methods are defined as hysteresis, linear, and optimized current control techniques.

Among various control schemes, the sinusoidal PWM (SPWM) is the most used control scheme for the control of multilevel inverters. In SPWM, a sinusoidal reference waveform is compared with a triangular carrier waveform to generate switching sequences for power semiconductor in inverter module.

SVM results to be one of the most promising methods in three-phase systems, the only problem is that is quite complex due to the increased number of power semiconductors. One of the most important methods to optimize control of the inverter is to select and design appropriate PWM modulation according to inverter topology.

Fundamental switching frequency methods shall be selected to reduce switching losses for high voltage modules, while multi-carrier SPWM is selected to control low voltage modules.

#### 1.8.1 Selective harmonic elimination PWM (SHE-PWM)

The main idea of this method is based on defining the switching angles of harmonic orders to eliminate and obtaining the Fourier series expansion of output voltage. An example output voltage Fourier expansion of an 11-level inverter can be written as in Eq. (15), which we have seen previously. The required switching angles to eliminate 5th, 7th, 11th, and 13th harmonic orders at fundamental switching frequency for an 11-level multilevel inverter can be calculated as given in Eq. (17).

$$\cos(\theta_1) + \cos(\theta_2) + \dots \cos(\theta_5) = 5 * m_a$$

$$\cos(5\theta_1) + \cos(5\theta_2) + \dots \cos(5\theta_5) = 0$$

$$\cos(7\theta_1) + \cos(7\theta_2) + \dots \cos(7\theta_5) = 0$$

$$\cos(11\theta_1) + \cos(11\theta_2) + \dots \cos(11\theta_5) = 0$$

$$\cos(13\theta_1) + \cos(13\theta_2) + \dots \cos(13\theta_5) = 0$$

The switching angles of  $\theta_1$ ,  $\theta_2$ ,  $\theta_3$ ,  $\theta_4$  and  $\theta_5$  can be determined to minimize voltage THD ratio, while m\_a defines the modulation index of modulator. The values are obtained using Newton-Raphson iterations (explained earlier in this paper) due to the nonlinearity of the parameters. The switching angles can be obtained at the values of  $\theta_1 = 6.57$ ,  $\theta_2 = 18.94$ ,  $\theta_3 = 27.18$ ,  $\theta_4 = 45.14$  and  $\theta_5 = 62.24$  by assuming  $m_a$  as 0.8 and solving with Newton–Raphson Iteration. Possible switching angles are calculated previously and saved to look-up tables in an independent memory or microprocessor. The main drawback of SHE-PWM is the requirement of calculations to determine switching angles as in fundamental frequency switching method. Increased DC sources or switching angles will prevent to obtain the most accurate solution (Smail, Taib, Saad, Isa & Hadzer, 2002).

#### 1.8.2 Sinusoidal PWM (SPWM)

SPWM technique is one of the most popular modulation techniques among the others applied in power switching inverters. In SPWM, a sinusoidal reference voltage waveform is compared with a triangular carrier waveform to generate gate signals for the switches of inverter. Power dissipation is one of the most important issues in high power applications.

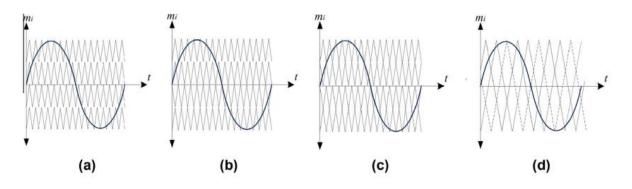

The fundamental frequency SPWM control method was proposed to minimize the switching losses. The multi-carrier SPWM control methods also have been implemented to increase the performance of multilevel inverters and have been classified according to vertical or horizontal arrangements of carrier signal. The vertical carrier distribution techniques are defined as Phase Dissipation (PD), Phase Opposition Dissipation (POD), and Alternative Phase Opposition Dissipation (APOD), while horizontal arrangement is known as phase shifted (PS) control technique. In fact, PS-PWM is only useful for cascaded H-bridges and flying capacitors, while PD-PWM is more useful for NPC (Çolak, Bayindir & Kabalci, 2011).

Each of the mentioned multi-carrier SPWM control techniques have been illustrated in Fig. 28, respectively. SPWM presents a lot of advantages among other modulations including easy implementation, lower harmonic outputs according to other techniques, and low switching losses. In SPWM control, a high frequency triangular carrier signal is compared with a low frequency sinusoidal modulating signal in an analog or logic comparator devices. The frequency of modulating sinusoidal signal defines the desired line voltage frequency at the inverter output (Gupta & Khambadkone, 2006)

Figure 28. Multi-carrier SPWM control strategies: (a) PD, (b) POD, (c) APOD, (d) PS.

In SPWM control technique, the output voltage is obtained in linear modulation range,

$$V_{AB} = V_{BC} = V_{CA} = m_i \frac{\sqrt{3}V_d}{2} \quad 0 < m_i \le 1$$

(18)

and the output voltage value is defined for the over-modulation range as seen in Eq. (19).

$$\frac{\sqrt{3}V_d}{2} < V_{AB} = V_{BC} = V_{CA} < \frac{4}{\pi} \frac{\sqrt{3}V_d}{2} \quad m_i \ge 1$$

(19)

#### 1.8.3 Space vector PWM (SPV)

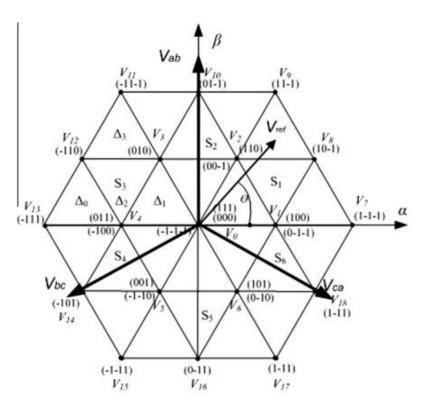

An alternative popular control method for multilevel inverters is defined as space vector PWM (SVM) that directly uses the control variable given by the control system and identifies each switching vector as a point in complex space of  $(\alpha, \beta)$ .

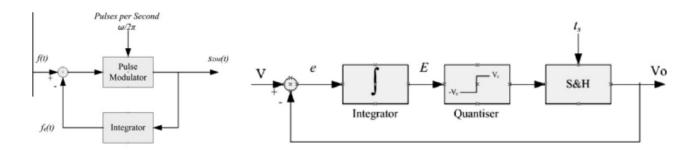

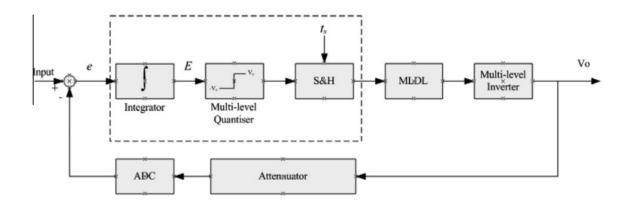

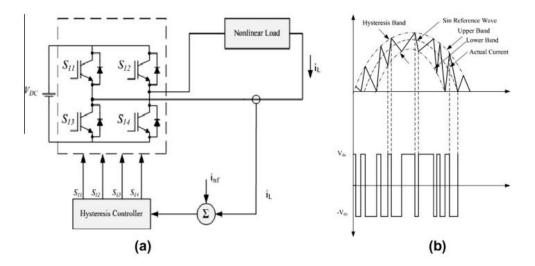

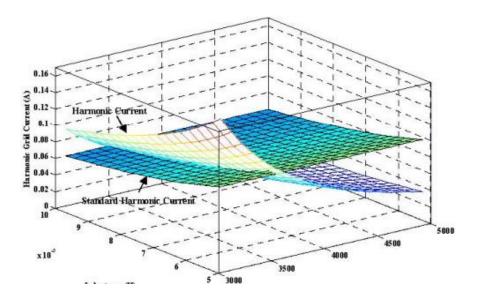

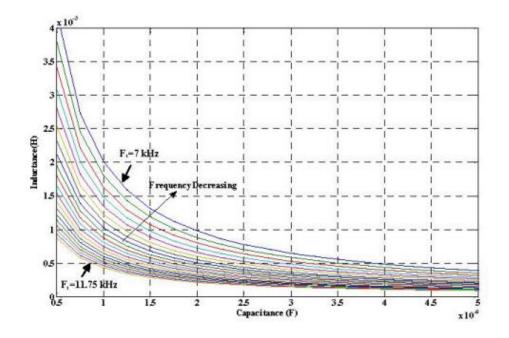

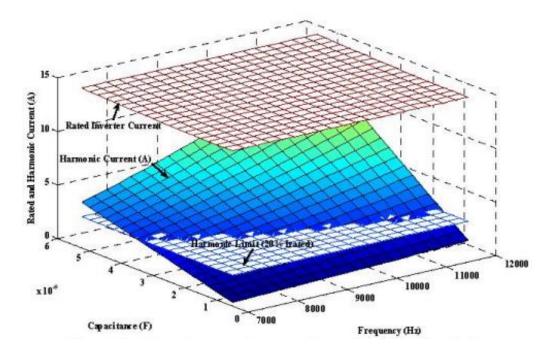

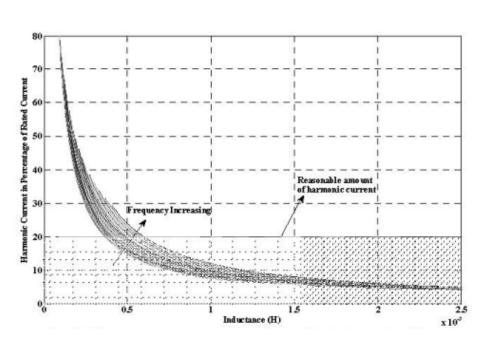

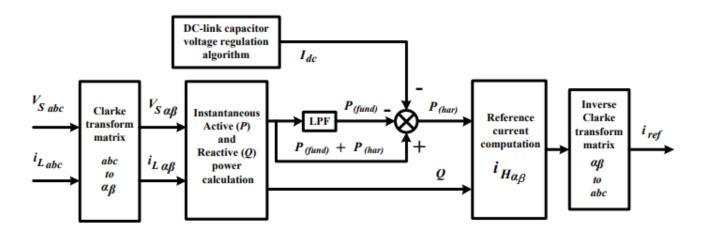

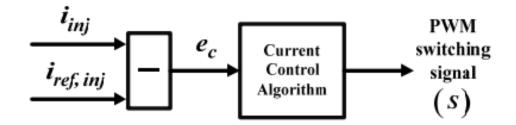

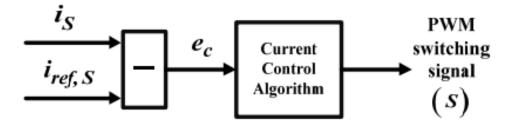

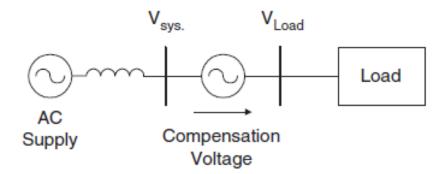

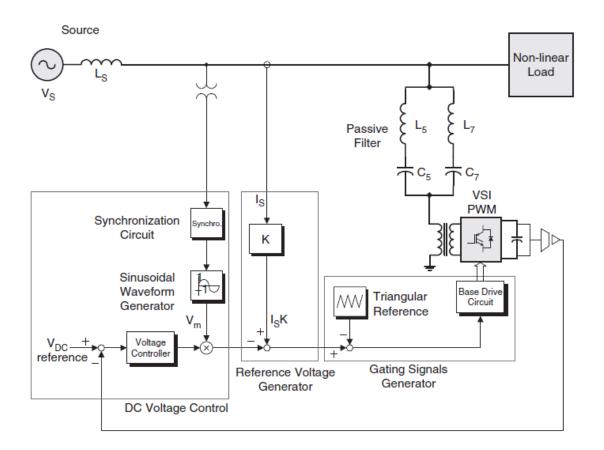

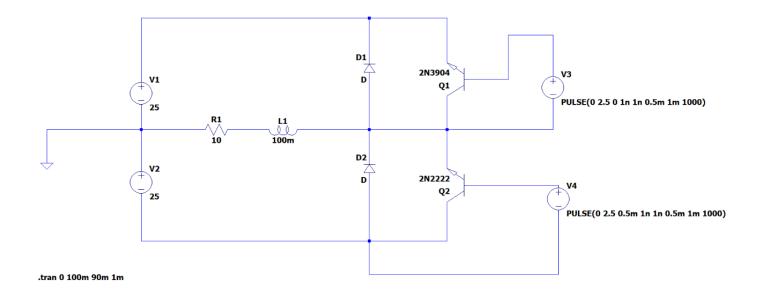

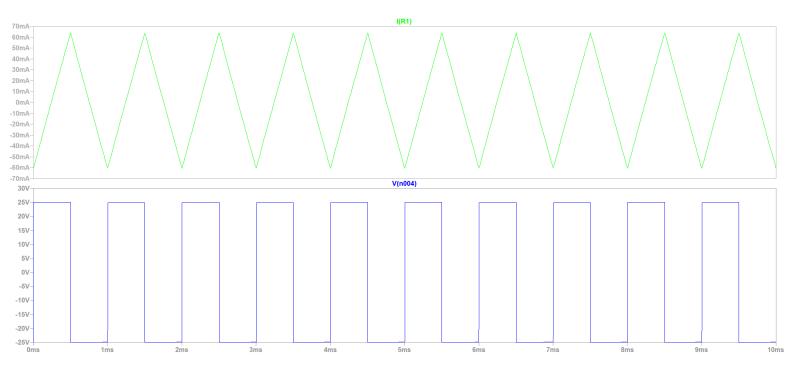

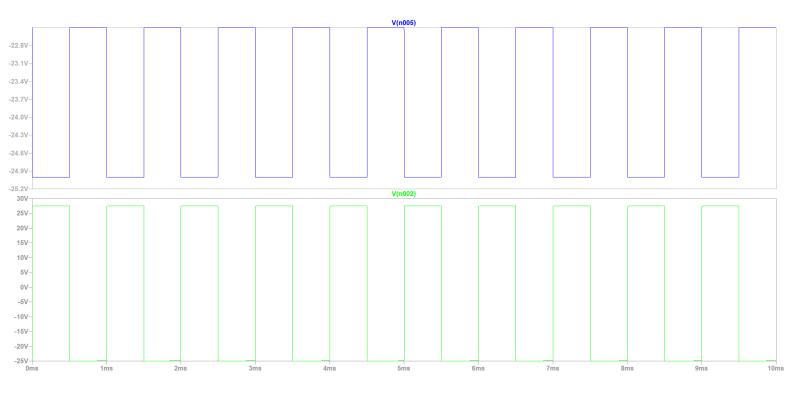

The harmonic elimination and fundamental voltage ratios in SVM schemes are obtained in better values compared to SPWM schemes. In addition to this, the maximum peak value of the output voltage is 15% greater than triangular carrier-based modulation techniques. Sector identification and look-up table requirement to determine the switching intervals for all vectors make SVM method quite complicated. Although the difficulty of determining sectors and switching sequences according to increased n-level of inverter, DSP and microprocessor implementations provide proper solution while preparing the algorithms.