# UNIVERSITAT POLITÈCNICA DE VALÈNCIA

# School of Telecommunications Engineering

Development of a system for monitoring and control of the sensors in the data processing module of the Hyper-Kamiokande neutrino detector.

End of Degree Project

Bachelor's Degree in Telecommunication Technologies and Services Engineering

AUTHOR: Martínez Sánchez, Borja

Tutor: Ballester Merelo, Francisco José

ACADEMIC YEAR: 2023/2024

### Resumen

Este TFG se realiza en el marco del proyecto internacional Hyper-Kamiokande, que tiene por objetivo construir el detector más avanzado y de mayor tamaño de neutrinos basado en la detección de luz de Cherenkov en agua ultrapura. Este detector será construido en Japón, en la antigua mina de Kamioka (prefectura de Gifu) y será el sucesor de Super-Kamiokande. El principal cambio de Super-Kamiokande a Hyper-Kamiokande es el uso de sensores PMT mucho más sensibles para captar el fenómeno conocido como "luz de Cherenkov". Esto provoca que la electrónica de conversión tenga que ponerse cerca de los PMT, en las propias vasijas. Por tanto, se hace necesario que la propia electrónica sea capaz de monitorizar su estado a través de diversos sensores y reportarse a través de un enlace *Ethernet* a los servidores situados en un *data center* encima del observatorio. Este TFG trata sobre la implementación de estas funcionalidades, conocidas como slow control para la DPB, que es el módulo que la UPV tiene como tarea diseñar y enviar estos datos a través de un enlace de *Ethernet*. Además, estas medidas también serán muy útiles a la hora de realizar tests con los prototipos para llegar a un diseño y fabricación finales de unos módulos que serán montados en el observatorio durante el año 2026.

### Resum

Aquest TFG es realitza en el marc del projecte internacional *Hyper-Kamiokande*, que té per objectiu construir el detector més avançat i de major grandària de neutrins basat en la detecció de llum de Cherenkov en aigua ultrapura. Aquest detector serà construït al Japó, en l'antiga mina de Kamioka (prefectura de Gifu) i serà el successor de Super-Kamiokande. El principal canvi de Super-Kamiokande a Hyper-Kamiokande és l'ús de sensors PMT molt més sensibles per a captar el fenomen conegut com a "llum de Cherenkov". Això provoca que l'electrònica de conversió haja de posar-se prop dels PMT, en els propis atuells. Per tant, es fa necessari que la pròpia electrònica siga capaç de monitorar el seu estat a través de diversos sensors i reportar-se a través d'un enllaç *Ethernet* als servidors situats en un *data center* damunt de l'observatori. Aquest TFG tracta sobre la implementació d'estes funcionalitats, conegudes com *slow control* per a la DPB, que és el mòdul que la UPV té com a tasca dissenyar i enviar aquestes dades a través d'un enllaç de *Ethernet*. A més, estes mesures també seran molt útils a l'hora de realitzar tests amb els prototips per a arribar a un disseny i fabricació finals d'uns mòduls que seran muntats en l'observatori durant l'any 2026.

### Abstract

This TFG is carried out in the framework of the international project Hyper-Kamiokande, which aims to build the most advanced and largest neutrino detector based on the detection of Cherenkov light in ultrapure water. This detector will be built in Japan, in the former Kamioka mine (Gifu prefecture) and will be the successor of Super-Kamiokande. The main change from Super-Kamiokande to Hyper-Kamiokande is the use of much more sensitive PMT sensors to capture the phenomenon known as "Cherenkov light". This results in the conversion electronics having to be placed close to the PMTs, in the vessels themselves. Therefore, it is necessary for the electronics themselves to be able to monitor their status through various sensors and report through an *Ethernet* link to the servers located in a data center on top of the observatory. This TFG is about the implementation

of these functionalities, known as slow control for the DPB, which is the module that UPV has the task to design and send these data through an *Ethernet* link. In addition, these measurements will also be very useful when testing the prototypes to reach a final design and manufacture of modules that will be mounted in the observatory during the year 2026.

#### **RESUMEN EJECUTIVO**

La memoria del TFG del GTIST debe desarrollar en el texto los siguientes conceptos, debidamente justificados y discutidos, centrados en el ámbito de la IT

| CONCEPT (ABET)                                                                        | CONCEPTO (traducción)                                                                                                             | ¿Cumple?<br>(S/N) | ¿Dónde?<br>(páginas)       |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------|--|

| 1. IDENTIFY:                                                                          | 1. IDENTIFICAR:                                                                                                                   |                   |                            |  |

| 1.1. Problem statement and opportunity                                                | 1.1. Planteamiento del problema y oportunidad                                                                                     | S                 | 1                          |  |

| 1.2. Constraints (standards, codes, needs, requirements & specifications)             | 1.2. Toma en consideración de los condicionantes<br>(normas técnicas y regulación, necesidades,<br>requisitos y especificaciones) | S                 | 1                          |  |

| 1.3. Setting of goals                                                                 | 1.3. Establecimiento de objetivos                                                                                                 | S                 | 2                          |  |

| 2. FORMULATE:                                                                         | 2. FORMULAR:                                                                                                                      |                   |                            |  |

| 2.1. Creative solution generation (analysis)                                          | 2.1. Generación de soluciones creativas (análisis)                                                                                | S                 | 55, 59,70,<br>73,79,83, 87 |  |

| 2.2. Evaluation of multiple solutions and decision-making (synthesis)                 | 2.2. Evaluación de múltiples soluciones y toma de decisiones (síntesis)                                                           | S                 | 27, 59,68,<br>70,73,79, 83 |  |

| 3. SOLVE:                                                                             | 3. RESOLVER:                                                                                                                      |                   |                            |  |

| 3.1. Fulfilment of goals                                                              | 3.1. Evaluación del cumplimiento de objetivos                                                                                     | S                 | 95-96                      |  |

| 3.2. Overall impact and significance<br>(contributions and practical recommendations) | 3.2. Evaluación del impacto global y alcance (contribuciones y recomendaciones prácticas)                                         | S                 | 95-96                      |  |

Escuela Técnica Superior de Ingeniería de Telecomunicación Universitat Politècnica de València Edificio 4D. Camino de Vera, s/n, 46022 Valencia Tel. +34 96 387 71 90, ext. 77190 www.etsit.upv.es

I would like to take this opportunity in my TFG to thank all those who have accompanied me during these 4 years of my studies for putting up with me and making this period of my life enjoyable. I would also like to thank Francisco Ballester and the I3M team for trusting me and providing me with my first professional experience as an engineer. Specifically, I want to express my gratitude to Alejandro Gómez Gambín for his time and guidance as my mentor during my internship, and for everything I have learned while working with him- Lastly, I must thank my family and parents for their unwavering emotional and financial support, and for always believing in me.

# Contents

| Ι | Intr | oduction: Hyper-Kamiokande Project |    |

|---|------|------------------------------------|----|

| 1 | TFG  | goals                              | 1  |

| 2 | The  | neutrino itself                    | 3  |

| 3 | HKI  | K project                          | 5  |

|   | 3.1  | HKK project structure              | 5  |

|   | 3.2  | HKK physics basis                  | 8  |

|   | 3.3  | HKK predecessor, Super-Kamiokande  | 9  |

|   | 3.4  | HKK objectives                     | 10 |

|   | 3.5  | HKK project organization           | 12 |

### II Leveraged technology

| 1 | DPE  | SoM election 1                                    | 5 |

|---|------|---------------------------------------------------|---|

|   | 1.1  | Understanding System-on-Module                    | 5 |

|   |      | 1.1.1       Advantages of SoM Technology:       1 | 5 |

| 2 | DPE  | 2 Prototype 1                                     | 7 |

|   | 2.1  | Zynq UltraScale+ Architecture                     | 7 |

|   |      | 2.1.1 Difference between PS and PL                | 8 |

|   |      | 2.1.2 JTAG interface                              | 9 |

|   |      |                                                   | 0 |

|   |      |                                                   | 1 |

|   |      |                                                   | 2 |

|   |      |                                                   | 5 |

|   |      |                                                   | 6 |

| 3 | Peta | zinux embedded OS 2                               | 7 |

|   | 3.1  | Unix/Linux environment and OS election            | 7 |

|   |      |                                                   | 8 |

|   | 3.2  | ······································            | 9 |

| 4 | Dev  | opment environments used 3                        | 1 |

| ľ | 41   | Vivado Design Suite                               |   |

|   | 4.1  | Vitis IDE         3                               |   |

|   |      |                                                   |   |

|   | 4.3  | Robot Framework                                   | 4 |

### III DPB sensors capabilities descriptions for *slow control* tasks

| 1 | I <sup>2</sup> C devices           | 37   |

|---|------------------------------------|------|

|   | 1.1 INA3221 Current sensor         | . 37 |

|   | 1.2 MCP9844 Temperature sensor     | . 42 |

|   | 1.3   AFBR-5715ALZ SFP Transceiver | . 44 |

| 2 | Xilinx AMS gathered data           | 49   |

### IV Tasks Development and Results

| 1   | Preparation of the environment to be used on the board1.1Platform setup and configuration1.2Vitis Project Creation                                                                                               | <b>55</b><br>55<br>56       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 2   | Application workflow                                                                                                                                                                                             | 59                          |

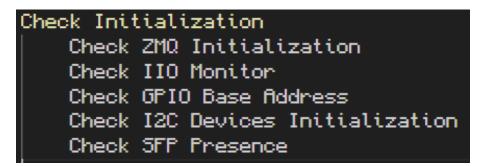

| 3   | Application initialization                                                                                                                                                                                       | 67                          |

| 4   | Monitoring thread development         4.1       Sensor data readout functions         4.2       Parse monitoring data into JSON string and send it to the DAQ                                                    | <b>73</b><br>73<br>74       |

| 5   | Alarms threads development5.1Configure shared memory segment and synchronization semaphores5.2Detection and handling sensors alarms functions5.3Parse alarms data into JSON string and send it to the DAQ        | <b>79</b><br>80<br>81<br>81 |

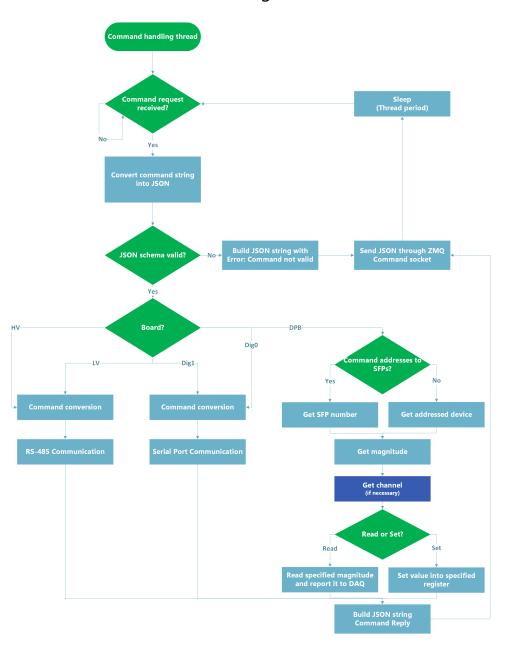

| 6   | <ul> <li>Command handling thread development</li> <li>6.1 Parse commands from the DAQ into JSON string for processing</li> <li>6.2 Define the command cases and develop functions to handle each case</li> </ul> | <b>83</b><br>84<br>85       |

| 7   | Develop manufacturing test software7.1Adapt previously developed software for manufacturing test7.2Automation of the tests using Robot framework                                                                 | <b>87</b><br>87<br>89       |

| V   | Conclusions and future work                                                                                                                                                                                      |                             |

| 1   | Lessons learned                                                                                                                                                                                                  | 95                          |

| 2   | Future work                                                                                                                                                                                                      | 97                          |

| Bil | bliography                                                                                                                                                                                                       | 99                          |

| VI  | Annexes                                                                                                                                                                                                          |                             |

| A   | Additional Listings                                                                                                                                                                                              | 103                         |

# **List of Figures**

| 3.1 | HKK water tank concept sketch                                                                                                     | 6  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Cross-section of the Hyper-Kamiokande                                                                                             |    |

| 3.3 | PMT structure                                                                                                                     |    |

| 3.4 | Interior of the vessel                                                                                                            |    |

| 3.5 | How a PMT detects <i>Cherenkov light</i> phenomenon                                                                               | 8  |

| 3.6 | Interior of the Super-Kamiokande, predecessor of the Hyper-Kamiokande                                                             | 9  |

| 3.7 | Hyper-Kamiokande neutrino oscillation investigation fields [5]                                                                    | 11 |

| 3.8 | Diagram of communication between the different modules of the vessel                                                              | 12 |

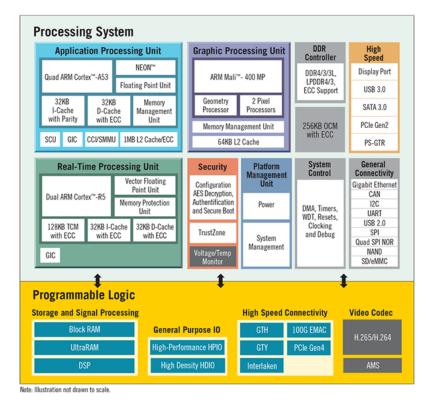

| 2.1 | Zynq UltraScale+ PS and PL blocks                                                                                                 | 19 |

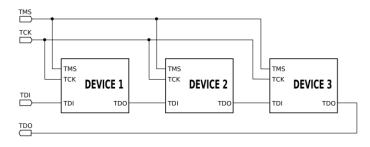

| 2.2 | Daisy-chained JTAG                                                                                                                | 20 |

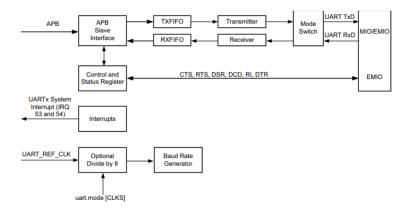

| 2.3 | UART Controller schema                                                                                                            |    |

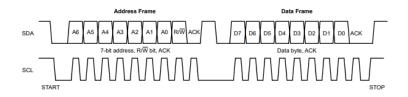

| 2.4 | Addressing and data frames $I^2C$                                                                                                 |    |

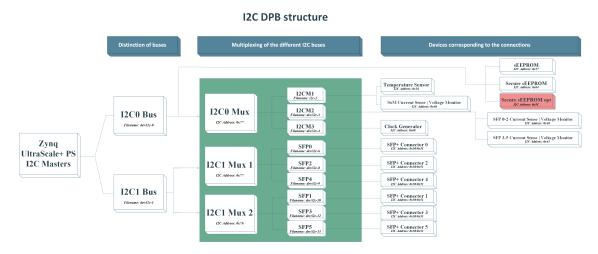

| 2.5 | Structure of the $I^2C$ of our DPB                                                                                                | 24 |

| 2.6 | SDA and SCL I <sup>2</sup> C communication signals $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 25 |

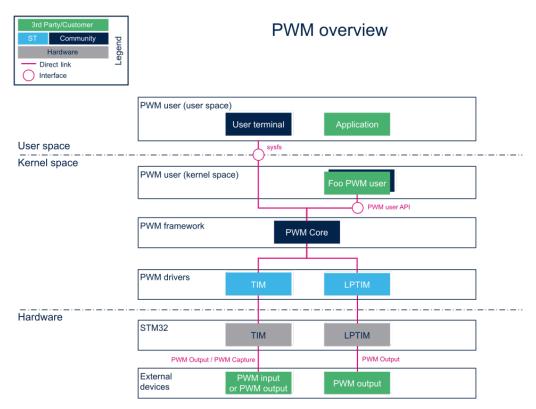

| 3.1 | Role of sysfs in user-hardware communication                                                                                      | 30 |

| 4.1 | Vivado GUI                                                                                                                        | 32 |

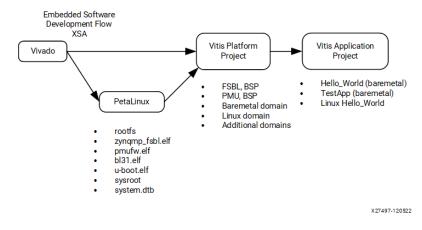

| 4.2 | Vitis Embedded Software Development Flow [18]                                                                                     | 33 |

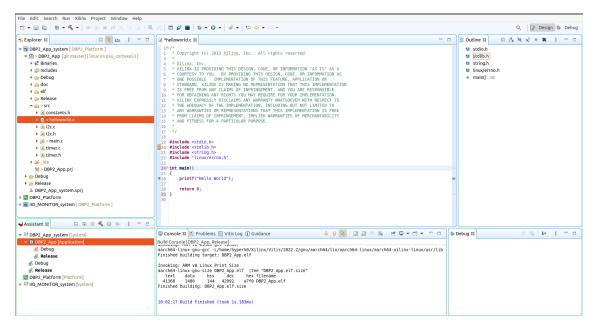

| 4.3 | Vitis GUI                                                                                                                         | 33 |

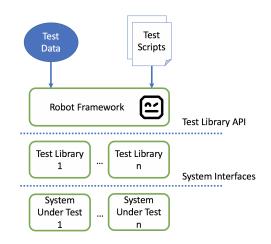

| 4.4 | Robot framework workflow [20]                                                                                                     | 34 |

| 4.5 | Example of keyword driven test                                                                                                    | 34 |

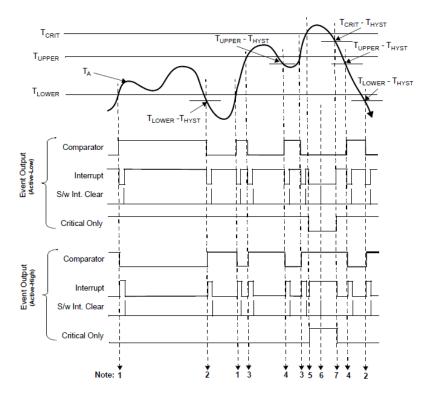

| 1.1 | Operation of the alarms MCP9844 Temperature Sensor                                                                                | 42 |

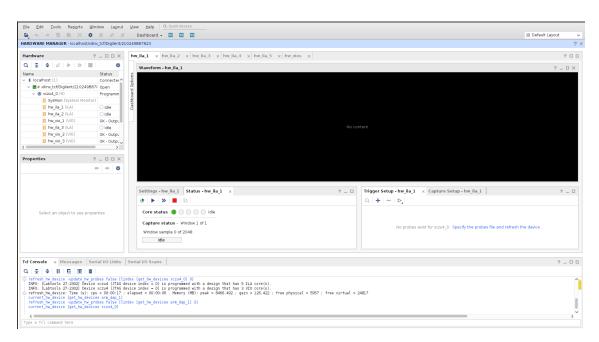

| 1.1 | Vitis IDE Platform project wizard                                                                                                 | 57 |

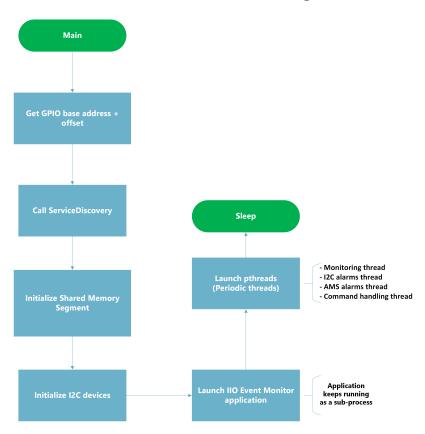

| 2.1 | Main application execution flow                                                                                                   | 59 |

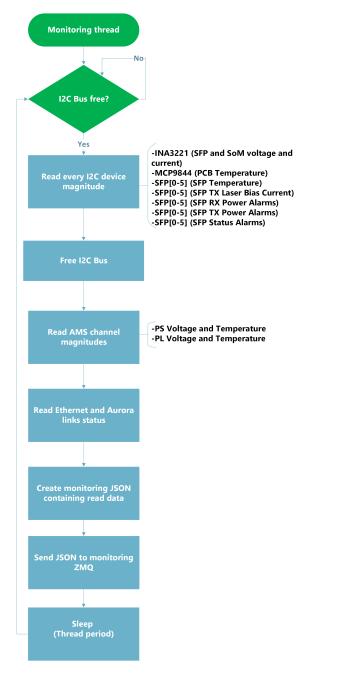

| 2.2 | Monitoring thread execution flow                                                                                                  | 61 |

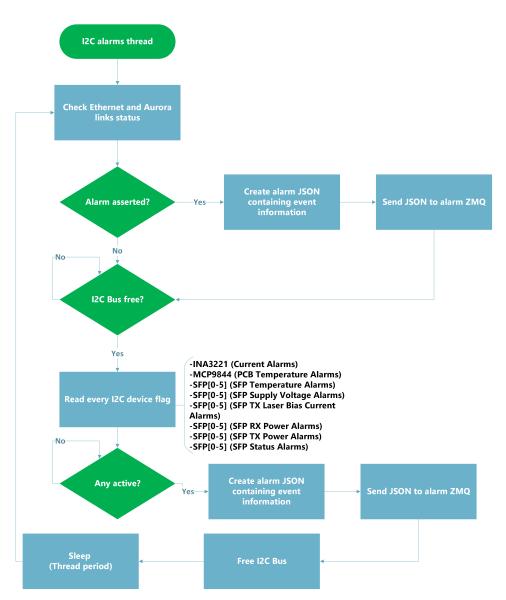

| 2.3 | $I^2C$ alarms execution flow                                                                                                      | 62 |

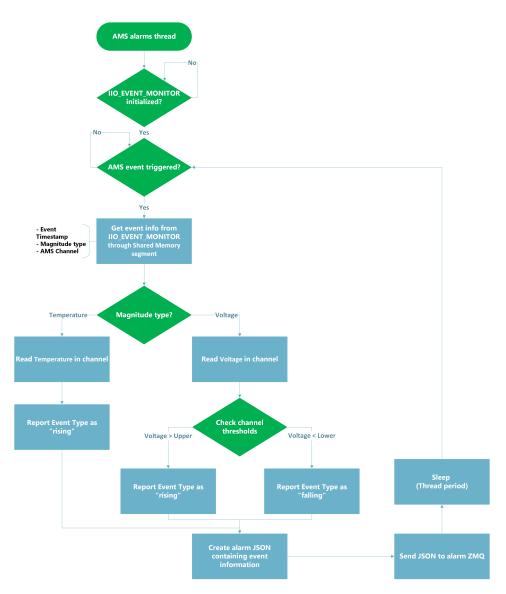

| 2.4 | AMS alarms thread execution flow                                                                                                  | 63 |

| 2.5 | Slow Control thread execution flow                                                                                                |    |

| 4.1 | Monitoring thread value                                                                                                           | 74 |

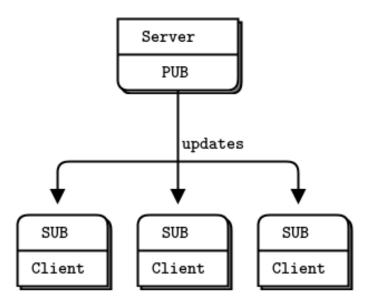

| 4.2 | ZeroMQ Publisher-Subscriber simple pattern [28]                                                                                   |    |

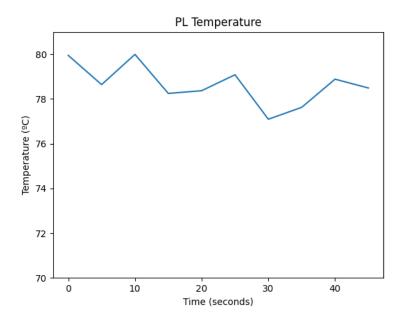

| 4.3 | PL Temperature monitored evolution                                                                                                | 77 |

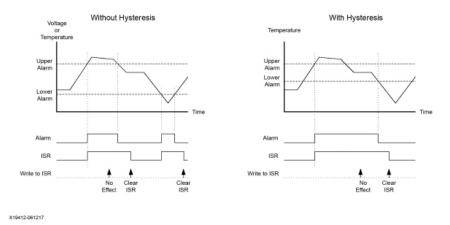

| 5.1 | Difference between AMS temperature alarm with hysteresis on and hysteresis off                                                    | 80 |

| 5.2 | JSON strings received in Python application after triggering alarms                                                               | 82 |

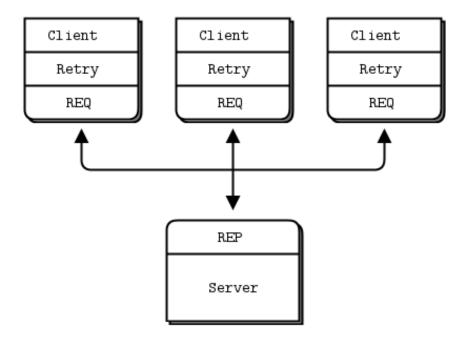

| 6.1 | Request-Reply pattern [29]                    | 83 |

|-----|-----------------------------------------------|----|

|     | Example of keyword-driven test                |    |

| 7.2 | Example of data-driven test                   | 90 |

| 7.3 | Basic example of successful Robot test report | 91 |

# **List of Tables**

| 3.1 | SK Phases                                         | 9   |

|-----|---------------------------------------------------|-----|

| 2.1 | DPB GPIO pin distribution                         | 26  |

| 1.1 | INA3221 Current Sensor Registers                  | 41  |

| 1.3 | MCP9844 Temperature Sensor Registers              | 43  |

| 1.4 | SFP transceiver EEPROM page 1 registers           | 45  |

| 1.5 | F-O-O-O-O-O-O-O-O-O-O-O-O-O-O-O-O-O-O-O           | 47  |

| 1.6 | Breakdown of SFP transceiver status bits          | 47  |

| 1.7 | Breakdown of the <i>flags</i> of SFP transceivers | 48  |

| 2.1 | SYSMON channels and their details                 | 50  |

| 2.2 | AMS alarms register set                           | 51  |

| 7.1 | Basic data structures in ctypes, C y Python       | 88  |

| A.1 | Setting DPB command list                          | 103 |

| A.2 | Reading DPB command list                          |     |

# Acronyms

- ACK Acknowledgment.

- ADC Analog-to-Digital Converter.

- AMD Advanced Micro Devices.

- AMS Analog Mixed-Signal.

- APB Advanced Peripheral Bus.

- API Application Programming Interface.

- APU Accelerated Processing Unit.

- ARM Advanced RISC Machine.

- AXI Advanced eXtensible Interface.

- **COM** Computer on Module.

- **CP** Charge Conjugation and Parity.

- CPU Central Processing Unit.

- DAQ Data Acquisition Centre.

- DHCP Dynamic Host Configuration Protocol.

- **DMA** Direct Memory Access.

- DPB Data Processing Board.

- **DSP** Digital Signal Processor.

- **DUT** Device Under Testing.

- **EEPROM** Electrically Erasable Programmable Read-Only Memory.

- **EMIO** Extended Multiplexed I/O.

- eMMC embedded Multi-Media Card.

- **FD** Far Detector.

#### Acronyms

FIFO First In First Out. **FinFET** Fin Field-Effect Transistor. FPD Full Power Domain. FPGA Filed Programmable Gate Array. GCC GNU Compiler Collection. GEM Gigabit Ethernet Module. GMII Gigabit Media Independent Interface. GND Ground. GPIO General Purpose I/O. GUI Graphical User Interface. HKK Hyper-Kamiokande. HV High Voltage. I/O Input/Output. I3M Institute for Molecular Imaging Instrumentation. I<sup>2</sup>C Inter-Integrated Circuit. IC Integrated Circuit. **ID** Inner Detector. **IDE** Integrated Development Environment. **IEEE** Institute of Electrical and Electronics Engineers. **IIO** Industrial I/O. IOP I/O Processor. **IP** Internet Protocol. JSON JavaScript Object Notation. JTAG Joint Test Action Group. LPD Low Power Domain. LSB Least Significant Bit. LV Low Voltage.

MAC Media Access Control.

- **MDIO** Management Data I/O.

- MIO Multiplexed I/O.

- MPSoC Multi-Processing System on Chip.

- MSB Most Significant Bit.

- NACK Negative Acknowledgment.

- **OS** Operating System.

- PCB Printed Circuit Board.

- PHY Physical Layer.

- PL Programmable Logic.

- PLL Phase-Locked Loop.

- PMT Photo-multiplier Tube.

- **POSIX** Portable Operating System Interface uniX.

- **PS** Processing System.

- **PS-GTR** Processing System-Gigabit Transceiver.

- RAM Random Access Memory.

- RGMII Reduced Gigabit Media Independent Interface.

- **RISC** Reduced Instruction Set Computer.

- ROM Read Only Memory.

- RPU Real-time Processing Unit.

- **RS** Recommended Standard.

- SCL Clock Signal.

- SDA Data Signal.

- SDK Software Development Kit.

- SFP Small Form-factor Pluggable.

- SK Super-Kamiokande.

- SMARC Smart Mobility ARChitecture.

- SoC System on Chip.

- **SoM** System on Module.

SSH Secure SHell.

#### SYSMON SYStem MONitor.

TAP Test Access Port.

- Tcl Tool command language.

- TCO Total Cost of Ownership.

- TCP Transmission Control Protocol.

- TFG Final Degree Project.

- TO Time Out.

- TSMC Taiwan Semiconductor Manufacturing Company.

UART Universal Asynchronous Receiver-Transmitter.

- UPV Polytechnic University of Valencia.

- UUID Universally Unique Identifier.

- VHV Very High Voltage.

- VLAN Virtual Local Area Network.

- **XPPU** Extended Peripheral Protection Unit.

# Part I

# Introduction: Hyper-Kamiokande Project

## **Chapter 1**

# **TFG goals**

It is well known that telecommunications have played a pivotal role in the course of society since its emergence, being a discipline that nowadays is necessary for almost everything, whether for 2-person telephone communication or military applications.

The field of telecommunications encompasses several branches of knowledge, one of them being electronic systems, where I specialize. Therefore, this Final Degree Thesis of the Degree in Telecommunication Technologies and Services Engineering is clear evidence of the importance of electronic systems in the advancement of human beings to explore and investigate the behaviour of the universe in all of its aspects. Specifically, this thesis will deal with the design of software for an embedded system, a type of electronic system that is very recurrent during the degree in telecommunications engineering and indispensable in a vast majority of electronic components worldwide.

This TFG is part of the Hyper-Kamiokande (HKK) project, which will be described in more detail in the following chapters. It is a massive global project that started in 2018 with around 300 researchers from 22 different countries, and over time the number has grown, which means that project coordination is crucial in the development of the whole project. The responsibilities of the UPV form the nucleus of the experiment's electronics, given the module's design originating from the UPV, particularly the Institute for Molecular Imaging Technologies (I3M).

It has to be taken into account that the electronics of this project have to be inaccessible for at least 10 years as they will be sealed in a vessel, so this thesis can be considered a step forward in the development of the DPB software through the design of an application that will allow to control the state of the electronic components inside the vessel and to communicate the DPB with the DAQ. In addition, it will serve as a basis for the development of automated manufacturing tests for the larger-scale production of the final version of the DPB. All this has to be developed taking into account that most of the processing capacity and memory of the DPB is destined for the data captured by the PMTs, so I have to try to optimize the designed software. Not to mention, I must detect and correct any possible bug that could cause any memory leak or lead the application to crash since neither the vessel nor the DPB will be accessible for at least 10 years and a failure to manually manipulate the electronics in a vessel would lead to the loss of that vessel until the next emptying of the observatory and a great amount of valuable information would be lost. This software will be developed on a Linux platform already designed by project colleagues.

The objectives of this dissertation are summarized as follows:

- **Develop DPB software** in order to allow us to read the information gathered from the sensors or other modules, process commands coming from the DAQ, and transmit the gathered data as packets to the DAQ.

- Learn how to work in embedded environments using the AMD Vitis IDE, which allows us to develop C or C++ application code that will run on Xilinx products. Therefore, we will be able to debug and run code on our DPB SoM.

- **Program software in Linux** for our DPB as it runs on an embedded OS derived from Linux, PetaLinux. Therefore, to develop software that will run on this OS, Linux drivers will be used and modified if necessary to achieve the desired functionality. The operation and execution flow of the drivers themselves must be understood in order to be used.

- **Develop** *slow control system* with the aim of precisely monitoring and managing lowfrequency signals or events from the DPB, prioritizing stability and accuracy over real-time responsiveness.

- **Create data structures** using JavaScript Object Notation (JSON) format to parse the gathered information and be able to communicate with the DAQ by following these data structures.

- **Manage alarm systems** asserted by the sensing components on the board to be able to act and report in case any of the components is operating outside manufacturer's margins and may compromise the operation or reliability of the DPB.

- Test preparation and automation using the Robot framework for testing the mass production of boards (about 900 will be produced for the detector). The aim is to integrate the previously designed software into the test software and to prepare and enumerate the test cases in the Robot framework in order to be able to verify all necessary test cases automatically.

## **Chapter 2**

# The neutrino itself

**P** rior to the development of the HKK project, it is useful to know more about the main particle to be detected during this project, the neutrino. Therefore, in this chapter a brief explanation of the knowledge about the neutrino throughout history, and the configurations and phenomena used for the detection of the neutrino and the study of its nature.

Within the field of physics there are countless subfields that study different aspects of everything around us. The project on which this dissertation is based is based on the speciality of physics called *Particle physics* [1], which is also known as high-energy physics, because many of these particles can only be seen in large collisions provoked in particle accelerators. This discipline of physics is responsible for demonstrating the existence of particles classified according to certain characteristics as bosons or fermions. Nonetheless, it also encounters the difficulty of having been able to demonstrate particles that are almost non-detectable to this day.

Within these elusive particles lies the neutrino, a subatomic entity generated during a radioactive decay and scattering phenomenon. In this instance, the neutrino arises from beta decay, as proposed in Fermi's theory, wherein a sizeable neutral particle  $(n^0)$  disintegrates into a proton  $(p^+)$ , an electron  $(e^-)$ , and a neutrino  $(\bar{\nu_e})$ .

$$n^0 \to p^+ + e^- + \bar{\nu_e}$$

(2.1)

The first person to postulate the existence of the neutrino theoretically was Wolfgang Pauli [2] in 1930, but it remained undetected for 25 years because this hypothetically predicted particle had to be massless, chargeless and without strong interaction. Finally, in 1956, Clyde Cowan, Frederick Reines, Francis B. "Kiko" Harrison, Herald W. Kruse, and Austin D. McGuire were able to demonstrate the existence of the neutrino experimentally by using a beam of neutrons to pump a tank of pure water. By observing the subsequent emission of the protons, they were able to demonstrate the existence of the neutrino. This test was called the neutrino experiment.

Over the years, different types of radioactive decays have been discovered that can give rise to neutrinos, such as natural and artificial nuclear reactions, supernova events or the spin-down of a neutron star. Furthermore, it has been discovered that there are different leptonic flavours of neutrinos originating from the weak interactions, electron neutrino, muon neutrino and tau neutrino, each flavor is associated with the correspondingly named charged lepton and similar to some other neutral particles, neutrinos oscillate between different flavors in flight as a consequence.

#### CHAPTER 2. THE NEUTRINO ITSELF

I have done a terrible thing: I have postulated a particle that cannot be detected.

#### - Wolfgang Pauli, 1930

This quote comes from Wolfgang Pauli when he postulated the existence of the neutrino as a particle without electric charge or mass to balance the equation, and it is that the discipline that studies the phenomena caused by neutrinos from space has been encountering great difficulties in detecting it for years detecting neutrinos because they interact with almost nothing or only weakly.

A configuration for detecting a decent amount of neutrinos, based on the *Cherenkov light* phenomenon, will be explained in further detail in the following sections. This precise configuration is the physics basis of the project on which this TFG has been developed.

## **Chapter 3**

# **HKK project**

T his chapter aims to present the structure and objectives of the HKK project, the evolution of its predecessor, SK, and the physics phenomena on which the project is based.

### 3.1 HKK project structure

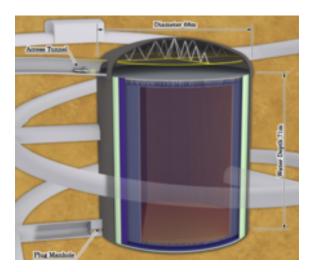

Hyper-Kamiokande [3] is a neutrino detector project still under construction (estimated to start operation in 2027), which takes place in the Kamioka mines in Japan, surpassing the performance of its predecessor, Super-Kamiokande. Although the project is based in Japan, it involves research institutes from 22 different countries. The aim of the project is to search for anti-neutrinos coming from supernovas, proton decays and detect neutrinos from natural sources such as the Earth, the atmosphere, the Sun and the cosmos, as well as to study neutrino oscillations from the neutrino beam of the artificial accelerator.

Hyper-Kamiokande is planned to be the world's largest neutrino detector, surpassing its predecessor Super-Kamiokande, which is 71 meters high and 68 meters in diameter. The detector, filled with ultrapure water, will have about 40,000 photomultiplier tubes as detectors inside the detector and 10,000 detectors outside the detector. Although HKK is bigger than SK, by including almost 4 times the number of PMTs of its predecessor, HKK achieves a 40% photo-cathode coverage, the same as SK.

Figure 3.1: HKK water tank concept sketch

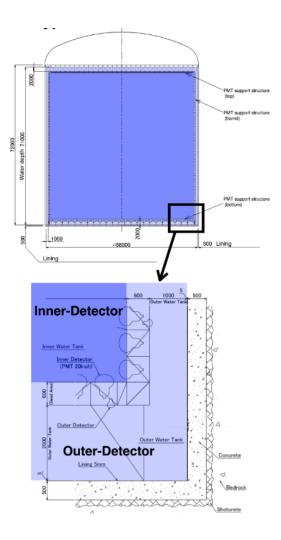

Figure 3.2: Cross-section of the Hyper-Kamiokande

6

The detector design comprises a cylindrical tank with outer dimensions of 71 meters in height and 68 meters in diameter. It is filled with 260,000 metric tons of ultrapure water to create a water Cherenkov detector. This tank will be surrounded by highly sensitive photodetectors, which boast a 50% higher efficiency compared to the SK ones, thus allowing for greater precision in measuring light intensity and detection time. These photomultiplier tubes (PMTs), specifically the Hamamatsu R12860 model, will enhance the detection of signatures such as those produced in neutrino interactions. Consequently, this setup will enable researchers to more accurately measure the direction and velocity of neutrinos passing through the detector.

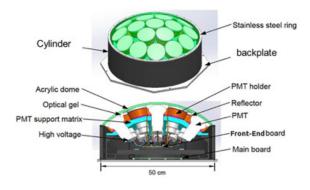

Figure 3.3: PMT structure

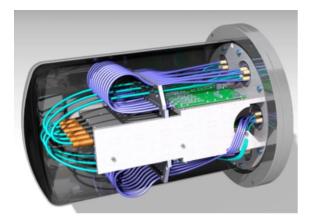

The PMTs, along with the rest of the electronics, will be housed in hermetically sealed vessels submerged in the water inside the detector, following the same structure as the SK.

**Figure 3.4: Interior of the vessel**

As can be seen in the previous figure, the electronics are concentrated inside the vessel, where the information from the PMTs is sampled in the digitizers and then sent to the DPB. The DPB is responsible for communicating the different modules both outside and inside the vessel, it acts as a hub inside the vessel.

Since the electronics are located in a place that is difficult to access, as it would mean emptying the detector of water, high reliability is required in this project, at least 10 years. For this reason, robust systems have been chosen and the electronics used must be monitored.

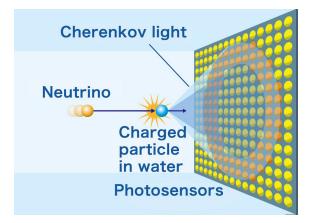

### 3.2 HKK physics basis

The physics apparatus used to study neutrinos is referred to as a neutrino detector, built to be isolated from any other influence like cosmic rays or background radiation. These neutrino detectors are huge structures that work following a neutrino detection technique of the existent ones let it be scintillators (like in the Cowan-Reines neutrino experiment), radiochemical methods, radio detectors or *Cherenkov light* detectors. The experiment that gives name to this chapter is based on the latter: the *Cherenkov light* detection [4].

These detectors are huge water-filled tanks enriched with deuterium and gadolinium. This environment is ideal for neutrino interaction as the interaction of one of these subatomic particles with the electrons or nuclei of water can produce a charged particle faster than the speed of light in water. This produces a cone of light called *Cherenkov light* and can be defined as the equivalent of light to a sonic boom in acoustic waves.

The water tank is surrounded by photosensible sensors called Phototubes, a cell filled with gas or a vacuum tube sensitive to light. The most used kind of phototube is the PMT due to its high sensitivity.

This PMT detects the *Cherenkov light* produced by the neutrino interaction. By sensing the pattern of light, a lot of information of the neutrino can be inferred, such as direction, energy and sometimes the flavor information of the incident neutrino.

Figure 3.5: How a PMT detects Cherenkov light phenomenon

These detections are exceedingly rare due to the low probability of a neutrino interacting with matter. Therefore, the larger the water tank and the greater the number of PMTs, the more interactions can be detected within the same time-frame. Furthermore, the concept of *fiducial volume* must be taken into account, a recurring concept in particle physics experiments that involves considering only results from a specific region of the detector, as results outside of that zone may be confusing or of limited validity for several reasons. Increasing this valid detection zone is the key to increasing detection possibilities

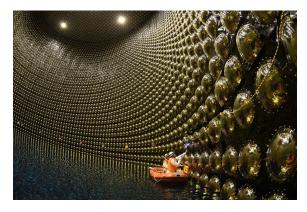

### 3.3 HKK predecessor, Super-Kamiokande

The largest neutrino detector currently in operation is the Super-Kamiokande. "Kamiokande" is a fusion of several words: KAMIOKA Neutrino Detection Experiment. Situated beneath Mount Ikeno near the city of Hida in the Gifu Prefecture, Japan, Kamioka is the facility that oversees this detector. The SK consists of a 36.2m high and 33.3m diameter ultrapure water tank with PMT detectors for inner and outer tank detection, and the operation of this neutrino detector also relies on the *Cherenkov light* phenomenon captured by PMTs to collect data.

The main difference with its successor (HKK) lies in the size of the ultrapure water tank and the amount of PMTs. It is estimated that this increase in tank size and number of PMTs will make it possible to capture with HKK in 10 years an amount of data that would take 100 years to capture in SK.

Figure 3.6: Interior of the Super-Kamiokande, predecessor of the Hyper-Kamiokande

The detector has undergone up to four revisions for various reasons, such as cascade failures or the replacement of the 6000 PMTs, along with upgrades to electronics in the latest iteration, Super-Kamiokande IV. These phases have not led to an increase in the number of PMTs or their percentage of coverage, but rather to measures to protect the technology used.

| Phase                    |       | SK-I        | SK-II      | SK-III      | SK-IV          |

|--------------------------|-------|-------------|------------|-------------|----------------|

| Period                   | Start | 1996 Apr.   | 2002 Oct.  | 2006 Jul.   | 2008 Sep.      |

|                          | End   | 2001 Jul.   | 2005 Oct.  | 2008 Sep.   | 2018 Jun.      |

| Number of PMTs           | ID    | 11146 (40%) | 5182 (19%) | 11129 (40%) | ID 11129 (40%) |

|                          | OD    |             | 1885       |             |                |

| Anti-implosion container |       | No          | Yes        | Yes         | Yes            |

| OD segmentation          |       | No          | No         | Yes         | Yes            |

| Front-end electronics    |       | ATM (ID)    | ATM (ID)   | ATM (ID)    | QBEE           |

|                          |       | QTC (OD)    | QTC (OD)   | QTC (OD)    |                |

Table 3.1: SK Phases

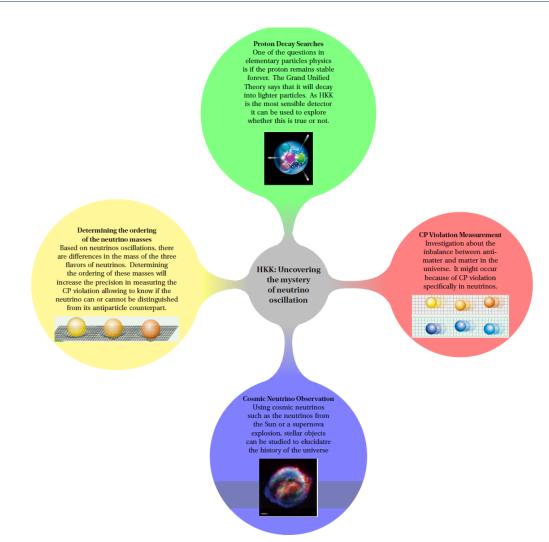

### 3.4 HKK objectives

The HKK experiment stands at the forefront of contemporary neutrino research, poised to unlock profound insights into the fundamental properties of these elusive particles. With its innovative design and enhanced capabilities, HKK ventures into uncharted territories of particle physics, aiming to shed light on mysteries ranging from neutrino oscillations to the enigmatic nature of dark matter.

In the realm of neutrino oscillation measurements, HKK endeavours to employ both accelerator and atmospheric neutrinos to unravel mysteries such as determining the mass hierarchy, investigating CP violation in the lepton sector, and precisely measuring oscillation parameters. Additionally, it aims to explore phenomena such as sterile neutrinos and potential violations of Lorentz invariance.

In solar neutrino measurements, HKK aims to address discrepancies observed between solar and reactor neutrino measurements, particularly focusing on the  $\theta_{12}$  sector. It intends to achieve this by studying day-night asymmetry in solar neutrino flux and exploring novel avenues such as monitoring solar fusion reactions and observing higher-energy neutrino flux.

HKK seeks to build upon the nucleon decay research legacy of Kamiokande and SK (Super-Kamiokande) by significantly enhancing limits on proton decays. It plans to utilize advanced PMT technology to improve performance, especially in detecting gamma rays from neutron capture, which is crucial for reducing neutrino backgrounds in proton decay searches.

In terms of supernova burst neutrinos, HKK aims to detect and analyze a substantial number of neutrinos from Galactic supernovae, allowing for detailed studies of these explosive events. It complements other experiments such as DUNE in its sensitivity to various types of supernova neutrinos.

For supernova relic neutrinos, HKK could contribute significantly by focusing on higher energy regions, complementing the efforts of SK. Introducing gadolinium enhances sensitivity by distinguishing neutrino interactions from background events.

In dark matter searches, HKK aims to improve upon SK's capabilities in detecting dark matter through neutrino signals, particularly from neutralino annihilation in regions of high dark matter density like the core of the Sun and the Galactic center. It also seeks to detect low-mass neutralinos, which are challenging to detect in direct-detection experiments.

In the pursuit of understanding the universe at its most fundamental level, the HKK experiment represents a beacon of scientific exploration. Through its multifaceted approach and collaborative efforts, HKK is poised to unravel some of the most profound mysteries of the cosmos, shaping our understanding of particle physics for generations to come.

Figure 3.7: Hyper-Kamiokande neutrino oscillation investigation fields [5]

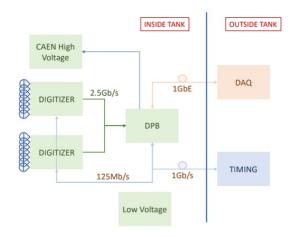

### 3.5 HKK project organization

As it has been mentioned previously, the HKK project involves research institutes from all over the world, which are in charge of different tasks within the project whether they are related to physics, electronics or any other relevant field. The project tasks have been divided in 7 different FD (Far Detector) groups [6]. Apart from the Far Detector groups, there are also the Near Detector and Beam Facility groups.

This TFG is developed inside of the FD4 group as our group in the I3M at the UPV belongs to this FD group. FD4 group tasks focus on developing electronics front-end inside the vessel for the inner sensors of the neutrino detector so as to be able to gather information from the sensors, transform it in order to allow the processing unit to process the data properly for sampling and sending the data from the inner sensors of the detector to a data-center.

#### Figure 3.8: Diagram of communication between the different modules of the vessel

As it can be seen in the previous figure, the electronics inside the vessel consists of high and low voltage modules used as power supplies for the rest of the components, digitizers and the DPB, and communicate outside the vessel with the DAQ. In the case of the power boards, the HV supplies the PMTs while the LV supplies the rest of the electronics inside the vessel.

The UPV is in charge of the development of the DPB of the ID focusing on collecting and transmitting information to the DAQ and on employing redundancy to maximise reliability. This is because the DPB, being the hub of the front-end electronics inside the vessel, is responsible for communicating all the modules and as the vessel is submerged in water, the electronics must be reliable enough to last for more than 10 years without needing to be repaired or replaced.

To achieve these goals, our group has to take care of designing the different parts of the DPB up to the final version, develop a software platform where we can develop the necessary software to communicate the DPB with the relevant modules and carry out the slow control tasks with reliability as a top priority in this project.

# Part II

Leveraged technology

## **Chapter 1**

# **DPB SoM election**

I n the realm of embedded systems development, System-on-Module (SoM) form factor has emerged as a transformative solution, particularly for academic institutions such as universities engaged in research and development projects. SoM refers to a compact, integrated circuit board that encapsulates essential components such as processors, memory, and I/O interfaces within a single package.

This chapter will therefore explain the definition of SoM and the advantages of choosing a SoM for the design of the DPB.

### 1.1 Understanding System-on-Module

System-on-Module (SoM) is a comprehensive computing platform condensed into a small, modular package. These modules typically include a microprocessor or System-on-Chip (SoC), memory components (both RAM and ROM), storage options, power management circuitry, and various peripheral interfaces. SoM modules are standardized in form factors such as COM Express, SMARC, and Qseven, facilitating easy integration into diverse hardware configurations.

#### 1.1.1 Advantages of SoM Technology:

#### 1. Cost Efficiency:

- Reduced Development Costs: One of the primary advantages of SoM technology for universities lies in its ability to lower development costs. Instead of investing resources in designing custom PCBs and integrating individual components, universities can procure pre-built SoM modules. While the upfront cost of SoM modules may seem higher compared to standalone chips, the overall development expenditure, including labour and prototyping, is significantly reduced.

- Lower Total Cost of Ownership (TCO): Despite initial investment differences, SoM technology often leads to a lower Total Cost of Ownership (TCO) over the project lifecycle. This is attributed to reduced development time, minimized risk of errors during hardware integration, and streamlined maintenance processes.

#### 2. Time Efficiency:

- Accelerated Development Cycles: SoM modules expedite the development process by eliminating the need for designing intricate hardware configurations from scratch. This acceleration is particularly beneficial for universities engaged in time-sensitive research projects or academic initiatives with strict deadlines.

- **Rapid Prototyping:** SoM technology facilitates rapid prototyping, allowing researchers and students to quickly iterate through design concepts and experiment with various configurations. This agility fosters innovation and enables timely validation of hypotheses.

#### 3. Risk Mitigation:

- Enhanced Reliability: SoM modules undergo rigorous testing and validation procedures during manufacturing, ensuring high levels of reliability and performance. By leveraging pre-tested and validated modules, universities mitigate the risk of hardware failures and associated costs, safeguarding project budgets and timelines.

- **Quality Assurance:** SoM vendors adhere to industry standards and quality control measures, providing universities with assurance regarding the integrity and functionality of the modules. This reliability is crucial for academic endeavours where consistency and reproducibility are paramount.

#### 4. Resource Optimization:

- Focused Resource Allocation: By adopting SoM technology, universities can reallocate resources previously dedicated to hardware design towards other aspects of research and development, such as software development, data analysis, and experimentation. This focused resource allocation enhances overall project efficiency and productivity.

- Skills Utilization: SoM technology reduces the dependency on specialized hardware design expertise within university research teams. Instead, academic resources can be channelled towards leveraging domain-specific knowledge and interdisciplinary collaboration, fostering a conducive environment for innovation and knowledge exchange [7], [8].

## Chapter 2

# **DPB2** Prototype

The DPB2 we are currently working with is only a prototype of what will become the final DPB. It is a combination between a SoM and a carrier board. The choice of the SoM is motivated by the reasons mentioned in the previous chapter, since for us as a university institution it means a saving in engineering costs to be able to insert the SoM in a carrier board and not having to design the entire PCB from scratch and solder the processing unit to the board.

Regarding the carrier board, it was designed by Enclustra with the assistance and supervision of our group to obtain a design according to our needs and Enclustra itself was responsible for manufacturing the board. This is because Enclustra is a company dedicated to the manufacture of these plates. Therefore, delegating the design and manufacturing process of the board to Enclustra represented engineering costs savings and provided us with a guarantee against possible manufacturing defects. Among the components of the board we can highlight current and temperature sensors, 6 SFP ports, UART or JTAG ports among others.

Zynq UltraScale+ Architecture has been chosen as the SoM architecture due to its processing capacity, efficiency and the integration of PetaLinux, a reduced version of Linux for embedded systems which offers us a very complete embedded software development platform.

This chapter will discuss this selected SoM architecture and review the features it offers and their usefulness for the HKK project.

### 2.1 Zynq UltraScale+ Architecture

The Zynq UltraScale+ MPSoC platform offers designers the first truly all-programmable, heterogeneous, multiprocessing system-on-chip (SoC) device. Smart systems are increasing in complexity with applications in the automotive industry, large database deployments, and even space exploration, pushing the requirements of each new generation of SoC to its limits. Requirements for increased power control, real-time applications, intensive graphical capabilities, and processing power demand a platform with maximum flexibility. The Zynq UltraScale+ MPSoC platform provides leading-edge features that modern systems designers demand. [9]

Built on the next-generation 16 nm FinFET process node from Taiwan Semiconductor Manufacturing Company (TSMC), the Zynq UltraScale+ MPSoC contains a scalable 32 or 64-bit multiprocessor CPU, dedicated hardened engines for real-time graphics and video processing, advanced high-speed peripherals, and programmable logic. The platform delivers maximum scalability through either dual or quad-core APU devices, offloading of critical applications like graphics and video pipelining to dedicated processing blocks, and the ability to turn blocks on and off through efficient power domains and gated power islands. With a wide range of interconnect options, digital signal processing (DSP) blocks, and programmable logic choices, the Zynq UltraScale+ MPSoC has the flexibility to fit a diverse set of user application requirements.

To effectively harness the power of the Zynq UltraScale+ MPSoC, AMD has the SoC-strength tools with Vivado Design Suite, and PetaLinux, and can further accelerate development using the Vitis unified software platform for design abstraction. [10]

#### Architecture's Essential Elements:

- 64-bit Quadcore ARM Cortex-A53 Processors

- Dualcore ARM Cortex-R5 Real-Time Processors

- ARM Mali<sup>™</sup>-400MP Graphics Processor

- H.265/264 Video Codec Unit

- · Advanced Dynamic Power Management Unit

- Configuration Security Unit

- DDR4/LPDDR4 Memory Interface Support

- 16FinFET+ Performance/Watt

- Vitis unified software platform for Design Abstraction

- Next-Generation AXI Interconnect

- Compatible with the Zynq 7000 SoCs, Software, and Ecosystem

#### 2.1.1 Difference between PS and PL

When we refer to a SoM, we must be clear about the two main blocks that conform it, PS and PL. The PS encompasses pre-designed and non-programmable components such as CPUs, memory controllers, and peripheral interfaces. Its main purpose is to handle computing tasks and manage the interface with the external world, facilitating communication with peripherals, memory access, and system-level operations.

Meanwhile, the PL offers a flexible and customizable hardware fabric that enables users to implement custom logic and tailor the functionality of the module to specific application requirements. Contrary to the PS, the PL consists of programmable hardware, typically in the form of FPGA or similar devices along with embedded transceivers and memory blocks, among others. This adaptable hardware fabric enables developers to create and implement bespoke hardware accelerators, interfaces, or custom processing pipelines, thus elevating the flexibility and performance capabilities of the SoM.

The PL functions in tandem with the PS, enabling hardware acceleration, real-time processing, and seamless integration of tailored peripherals to meet the distinct requirements of the specific application at hand.

Figure 2.1: Zynq UltraScale+ PS and PL blocks

### 2.1.2 JTAG interface

JTAG is an industry standard used for verifying designs, testing PCB after being manufactured and programming FPGAs or similar devices by using boundary-scan technology. Signals are scanned into and out of the I/O cells of a device serially to control its inputs and test the outputs under various conditions.

The JTAG port consists of the following pins:

- Test Data In (TDI)

- Test Data Out (TDO)

- Test Clock (TCK)

- Test Mode Select (TMS)

- Test Reset (TRST) (optional)

Figure 2.2: Daisy-chained JTAG

The data transmission is serial since there is only one wire of transmission in each direction. Therefore, one bit of data is transmitted every rising clock edge and the direction depends on the mode select pin.

In the case of the Zynq UltraScale+ architecture, it enables a JTAG interface to the user that allows debugging features for software and PL configuration since it features PS and PL TAP and ARM debugging of the RPU and APU.

In particular, we have used the JTAG interface to load the PetaLinux image and the necessary boot files onto the eMMC using the Vivado development environment.

#### 2.1.3 UART interface

The Zynq UltraScale+ architecture also count with an UART controller that functions as a fullduplex asynchronous receiver and transmitter, supporting a broad range of programmable baud rates and I/O signal formats. It offers capabilities for automatic parity generation and multi-master detection mode. The configuration and mode registers control UART operations, while the status, interrupt status, and modem status registers are used to monitor FIFO states, modem signals, and other controller functions.

The controller comprises separate RX and TX data paths, each featuring a 64-byte FIFO. It handles data serialization and deserialization within the TX and RX FIFOs, and includes a mode switch to support various loop-back configurations for RxD and TxD signals. FIFO interrupt status bits allow for either polling or interrupt-driven handling. Data bytes are read and written using RX and TX data port registers.

In modem-like applications, the modem control module manages modem handshake signals and controls receiver and transmitter paths according to the handshaking protocol.

Key features of the UART controller include:

- · Programmable baud rate generator

- Configurable receive and transmit FIFOs, with byte, two-byte, or four-byte APB access mechanisms

- Options for 6, 7, or 8 data bits

- Support for 1, 1.5, or 2 stop bits

- · Parity options including odd, even, space, mark, or no parity

- · Detection of parity, framing, and overflow errors

- · Line break generation and detection

- · Automatic echo, local loop-back, and remote loop-back channel modes

- Interrupt generation

- Modem control signals

- Dual clocks: advanced peripheral bus (APB) clocks up to 100 MHz and uart\_ref\_clock ranging from 1 MHz to 100 MHz

Figure 2.3: UART Controller schema

In our case, the UART interface has been used to communicate with the DPB and access its file system. Although the main communication with the DPB has been established via the Ethernet interface, the UART interface has been used mainly for debugging drivers and OS elements, since we can see kernel messages via UART, but not via Ethernet.

#### 2.1.4 Ethernet interface

Zynq UltraScale+ counts with the gigabit Ethernet controller (GEM), which implements a 10/100/1000 Mb/s Ethernet MAC that is compatible with the IEEE Standard for Ethernet (IEEE Std 802.3-2008) and capable of operating in either half or full-duplex mode in 10/100 mode and full-duplex in 1000 mode. The processing system (PS) is equipped with four gigabit Ethernet controllers. Each controller can be configured independently. Each controller uses a reduced gigabit media independent interface (RGMII) v2.0.

Access to the programmable logic (PL) is through the EMIO which provides the gigabit media independent interface (GMII). Other Ethernet communications interfaces can be created in the PL using the GMII available on the EMIO interface. GEM supports the serial gigabit media-independent interface at 1000 Mb/s using the PS-GTR interface.

Registers are used to configure the features of the MAC, select different modes of operation, and enable and monitor network management statistics. The DMA controller connects to memory through the advanced eXtensible interface (AXI). It is attached to the controller's FIFO interface of

the MAC to provide a scatter-gather capability for packet data storage in an embedded processing system.

Each GEM controller provides management data input/output (MDIO) interfaces for PHY management.

Each gigabit Ethernet MAC controller has the following features:

- Compatibility with IEEE Standard 802.3-2008, supporting various transfer rates.

- Flexibility in operation modes: full/half duplex.

- Multiple I/O options for connectivity.

- MDIO interface for managing external PHY.

- · Powerful DMA capabilities with scatter-gather support.

- APB slave interface for control register access.

- Comprehensive interrupt system for event notification.

- · Automatic frame integrity checks and error handling.

- Configurable inter-packet gap and flow control.

- Advanced address checking and VLAN tagging capabilities.

- · Support for loopback mode and checksum offloading.

- Recognition of IEEE Precision Time Protocol frames.

- Statistics counters for monitoring network performance.

- Jumbo frame support for efficient data transfer.

- Priority support for enhanced traffic management.

We have used the Ethernet interfaces to establish a connection to the DPB that is faster and more practical than JTAG and also allows us to implement interface redundancy techniques to maximise the reliability of the link.

#### 2.1.5 I<sup>2</sup>C interface

Furthermore, Zynq UltraScale+ provide us with an I<sup>2</sup>C controller which allows us to communicate with the sensors and SFPs installed in the DPB via 2 different I<sup>2</sup>C buses. The I<sup>2</sup>C controllers are versatile, capable of operating as either a master or a slave within a multi-master setup, with a clock frequency range of up to 400 kb/s. They support multi-master mode for both 7-bit and extended 10-bit addressing formats.

In master mode, transfers are initiated solely by the processor writing the slave address into the I<sup>2</sup>C address register. The processor is then alerted to any incoming data via either a data interrupt or a transfer complete interrupt. If the hold bit is activated, the I<sup>2</sup>C interface keeps the clock signal

(SCL) Low after transmitting data, facilitating smooth operation for slower processors. Master configuration allows for the use of both standard and extended addressing modes, with the latter exclusive to master mode [11].

In slave monitor mode, the I<sup>2</sup>C interface acts as a master, persistently attempting a transfer to a designated slave until either an acknowledgement (ACK) is received or a timeout occurs.

The controller also supports repeated start functionality, wherein the master can generate a subsequent start condition following the initial one, typically followed by the slave's I<sup>2</sup>C address.

A shared feature between master and slave modes is the timeout mechanism, indicated by the TO interrupt flag. If, at any stage, the SCL clock signal remains Low for a duration exceeding that specified in the timeout register, a TO interrupt is triggered to prevent operational stalls.

There are two I<sup>2</sup>C controllers located in the LPD IOP section of the PS. They adhere to I<sup>2</sup>C bus specification version 2 and feature a 16-byte FIFO buffer. Key features include programmable normal and fast bus data rates, support for multi-master configurations, and versatile operation modes.

In master mode, the controllers facilitate read and write transfers, with support for both seven and 10-bit addressing formats. They incorporate clock stretching functionality to accommodate slow processor operation, preventing stalls with a TO interrupt bit. Additionally, they offer repeated start capability and slave monitor mode.

When operating in slave mode, the controllers can transmit and receive data and feature fully programmable slave response addresses. They include a HOLD bit to mitigate overflow conditions and utilize clock stretching to manage communication delays when data isn't readily available.

Furthermore, the controllers can be polled for status by software or function as interrupt-driven devices, with programmable interrupt generation capabilities.

To achieve communication between the different components on the board and the terminal, the I<sup>2</sup>C protocol is used, a communication protocol based on a Master-Slave system where the communication bus is divided into 2 lines, SCL for the clock and SDA for the data, which are connected to a pull-up resistor each, so the default level is high level.

The operation of this protocol consists of the start of the transmission by the Master which jointly indicates the address of the slave to which it is directed with an address of 7 bits, even though we have sensors that have an address of 6 bits plus a reserved bit, which can be configured to differentiate each slave in a physical way, in addition, it is indicated with a bit if the operation to be carried out is reading or writing. The data transmission is guided by the clock line and the data is transmitted in byte size, transmitting from MSB to LSB.

Figure 2.4: Addressing and data frames I<sup>2</sup>C

For the write operation on the slave, once communication has been established, the register to be

written to and the data to be written must be indicated. The master is responsible for receiving the corresponding ACK and NACK during communication and the end of communication sequence.

The read operation follows a similar process to the write operation, indicating the register to be read and the master is in charge of sending the corresponding ACKs and NACKs during the communication and at the end of communication sequence.

In our case the communication process will be based on the functions provided by the Linux libraries that allow us to open/close the communication and read/write registers simply by calling defined functions and indicating the necessary arguments. In addition, these functions allow us to operate with vectors in order to read or write consecutive data with a single function.

Figure 2.5: Structure of the I<sup>2</sup>C of our DPB

In the previous block diagram you can see how the  $I^2C$  buses of our DPB are structured, the corresponding filename of each of the  $I^2C$  bus outputs designated by the multiplexers and the slave addresses of each module with which we intend to communicate.

As can be seen, the current sensors, the SFP connectors and the temperature sensor that we intend to use all use the  $I^2C$  protocol to communicate. However, the temperature sensor and the current sensors use 16-bit registers, while the SFPs use 1-byte sized registers. The  $I^2C$  protocol carries byte-sized frames, so in the case of 16-bit registers it involves performing 2 consecutive operations (either read or write) on the same register address, whereas for 8-bit registers it will involve a single operation per register address.

Moreover, as it can be seen in our  $I^2C$  devices datasheets, reading and writing operations are performed differently since for the read operation you have to write the address of the register you want to read in the register pointer and then read the contents in separate operations, whereas for the write operation you have to indicate the address of the register you want to write to and the data you want to write consecutively. In our case, the Linux  $I^2C$  driver will make it much easier to perform any  $I^2C$  operations.

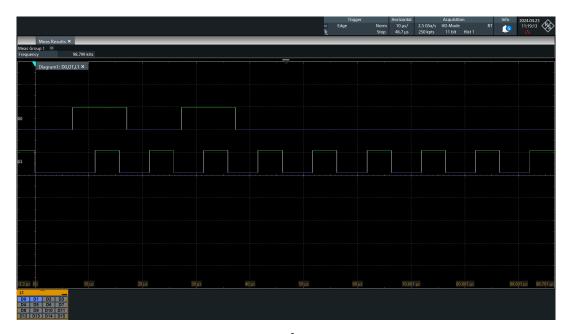

Figure 2.6: SDA and SCL I<sup>2</sup>C communication signals

As can be seen in the figure 2.6, SDA and SCL signals generated by the Linux driver to achieve I<sup>2</sup>C communication are as expected and the clock signal works in the standard mode of 100kHz and it has been successfully measured using an oscilloscope that the I<sup>2</sup>C transmission speed we are working with is 100kHz.

#### 2.1.6 GPIO interface

The Zynq UltraScale+ architecture incorporates the General Purpose Input/Output (GPIO) controller, which is a collection of input/output signals available for software applications. The GPIO comprises the MIO with 78 pins and the Extended Multiplexed Input/Output Interface (EMIO) with 288 signals, divided into 96 inputs from the Programmable Logic (PL) and 192 outputs to the PL. The GPIO is organized into six banks of registers that group related interface signals.

Each GPIO channel is independently and dynamically programmed as input, output, or interrupt sensing. Software applications can read all GPIO values within a bank using a single load instruction or write data to one or more GPIOs using a single store instruction. The GPIO control and status registers for the Zynq UltraScale+ architecture are memory-mapped beginning at base address 0xFF0A\_0000 and are protected by the XPPU [12].

Key features of the GPIO peripheral are summarized as follows:

- 78 GPIO interfaces to the device pins, routed through the MIO multiplexer, with programmable I/O drive strength, slew rate, and 3-state control.

- 96 GPIO interfaces to the PL (four allocated by software to reset PL logic), routed through the EMIO interface, providing data inputs, data outputs, and output enables.

- I/O interface organized into six banks (3 MIO and 3 EMIO).

- Interface control registers grouped by bank {0:5}.

- Input values read using the six DATA\_RO\_x registers.

- Two types of data ports for writing: full bank write using the DATA\_x registers, and split bank maskable write using the MASK DATA x LWS, MWS register pairs.

- The function of each GPIO can be dynamically programmed on an individual or group basis.

- Enable, bit or bank data write, output enable, and direction controls.

- Programmable interrupts on an individual GPIO basis, with status read of raw and masked interrupt, and selectable sensitivity (Level-sensitive: High or Low, or edge-sensitive: positive, negative, or both).

In our case, the GPIO pins have been used for various functions, such as enabling Aurora links with the digitizers or SFPs transmission, or even controlling SFP status. In table 2.1, we can see our DPB GPIO pin distribution.

| DIR    | PIN#    | PIN NAME            | PIN NAME            | PIN NAME            | PIN NAME            |

|--------|---------|---------------------|---------------------|---------------------|---------------------|

| OUTPUT | (65:64) |                     |                     | DMA TIMEOUT ENABLE  | DMA FORCE TLAST     |

| OUTPUT | (63:60) | AURORA_RST_DIG1_SEC | AURORA_RST_DIG1_PRI | AURORA_RST_DIG0_SEC | AURORA_RST_DIG0_PRI |

| OUTPUT | (59:56) | DMA_PAUSE           | DMA_BUF_SIZE        | DMA_ENABLE          | EN_HVLV_DRV         |

| OUTPUT | (55:52) | EN_CPU_HV_1         | EN_CPU_HV_0         | EN_CPU_LV_1         | EN_CPU_LV_0         |

| OUTPUT | (51:48) | TIMING_RST          | XVC_DISABLE         | DMA_SOURCE          | GLOBAL_AURORA_RST   |

| INPUT  | (47:44) | AURORA AFIFO FULL   | DIG_STREAM_ERR      | PLL_LOL_n           | PLL_INTR_n          |

| INPUT  | (43:40) | LINK_UP(DIG1,SEC)   | LINK_UP(DIG1,PRI)   | LINK_UP(DIG0,SEC)   | LINK_UP(DIG0,PRI)   |

| INPUT  | (39:36) | DIG1_PWR_GOOD       | DIG0_PWR_GOOD       | DIG1_FPGA_DONE      | DIG0_FPGA_DONE      |

| INPUT  | (35:32) | SFP_PWR_GOOD(5)     | SFP_RX_LOS(5)       | SFP_MOD_ABS(5)      | SFP_TX_FAULT(5)     |

| INPUT  | (31:28) | SFP_PWR_GOOD(4)     | SFP_RX_LOS(4)       | SFP_MOD_ABS(4)      | SFP_TX_FAULT(4)     |

| INPUT  | (27:24) | SFP_PWR_GOOD(3)     | SFP_RX_LOS(3)       | SFP_MOD_ABS(3)      | SFP_TX_FAULT(3)     |

| INPUT  | (23:20) | SFP_PWR_GOOD(2)     | SFP_RX_LOS(2)       | SFP_MOD_ABS(2)      | SFP_TX_FAULT(2)     |

| INPUT  | (19:16) | SFP_PWR_GOOD(1)     | SFP_RX_LOS(1)       | SFP_MOD_ABS(1)      | SFP_TX_FAULT(1)     |

| INPUT  | (15:12) | SFP_PWR_GOOD(0)     | SFP_RX_LOS(0)       | SFP_MOD_ABS(0)      | SFP_TX_FAULT(0)     |

| OUTPUT | (11:8)  | TX_DIS(5)           | TX_DIS(4)           | TX_DIS(3)           | TX_DIS(2)           |

| OUTPUT | (7:4)   | TX_DIS(1)           | TX_DIS(0)           | PWR_EN(5)           | PWR_EN(4)           |

| OUTPUT | (3:0)   | PWR_EN(3)           | PWR_EN(2)           | PWR_EN(1)           | PWR_EN(0)           |

#### Table 2.1: DPB GPIO pin distribution

#### 2.1.7 RS-485 communication protocol

RS-485 is an established standard initially introduced in 1983. It outlines the electrical characteristics of drivers and receivers for use in serial communication systems. The signaling is balanced, supporting multi-point systems. The standard is jointly managed by the Telecommunications Industry Association and the Electronic Industries Alliance. RS-485 facilitates effective digital communication networks over extended distances and in electrically noisy environments. It enables the connection of multiple receivers to a linear, multi-drop bus, making it valuable in industrial control systems and similar applications.

RS-485 facilitates cost-effective local networks and multi-drop communication links, utilizing the same differential signaling over twisted pair as RS-422.

We use two RS-485 drivers which are connected are connected to the UARTLite cores of the HV and LV boards instantiated in the PL to be able to communicate with these boards.

### **Chapter 3**

## **PetaLinux embedded OS**

I n this chapter, we intend to give an introduction to the OS chosen, PetaLinux, as the platform on which the DPB works, its characteristics, and the advantages of its use.

#### 3.1 Unix/Linux environment and OS election

It is well known that nowadays there are plenty of OS options available. Nevertheless, Linux has established itself as the ideal choice for a large part of the worldwide server market and is also extending its reach to personal computers and embedded systems, the latter including our DPB.

Its success is mostly due to its open-source nature, which allows software developers to fully customize and optimize it for specific applications. At a time when it is essential to reduce resource consumption as much as possible, being able to configure the technology you have available to extract its maximum performance for your particular application is ideal [13].

In addition, thanks to being an open source OS, this has led to the creation of a huge community that is dedicated to developing and supporting software such as drivers and libraries to provide a higher level of abstraction over the control of peripherals or any other component achieved by the Linux kernel in the form of functions [14]. This can be an advantage when applied to generic applications since the driver or library may not be suitable for a specific application and may require custom adaptation.

However, Linux offers a huge variety of different distributions and not all are suitable for embedded systems. Therefore, Xilinx offers two options for running Linux on its Zynq UltraScale+ boards: PetaLinux and Ubuntu Desktop. For this project, PetaLinux has been chosen for the following reasons:

- Customizability: PetaLinux provides a comprehensive SDK that allows for tailoring the

operating system to specific hardware and software requirements. This is crucial in the DPB

as both hardware and software must serve a very specific purpose, namely reliability. With

PetaLinux, it's possible to customize the operating system to meet the specific demands of

the Zynq MPSoC, optimizing performance and minimizing resource usage.

- Size: PetaLinux enables the creation of a highly optimized, minimalist system image, ideal

for embedded systems. This is significant in the DPB, where one strategy to enhance reliability is to have redundant booting images. The smaller the image, the more copies can be placed in memory. In contrast, Ubuntu Desktop is designed for desktop computers and typically includes a plethora of applications and features unnecessary for an embedded system, resulting in a larger image size.

• Flexibility: PetaLinux offers a high level of flexibility in terms of package selection, configuration, and even customization of the kernel's source code, allowing for on-the-fly patches before compiling the boot image. This makes it well-suited for use in a system where hardware and software are designed together, ensuring that any device-specific bugs, such as those related to SFP modules or sensors, can be patched without much difficulty. Ubuntu Desktop, on the other hand, is a more general-purpose operating system that lacks the same level of flexibility and customization, as the image provided by Xilinx is already pre-compiled.

#### 3.1.1 Used Linux libraries, drivers and applications

As mentioned in the previous section, Linux libraries and drivers are outstanding tools that can considerably ease the task of software development on a Linux-based OS.

During the course of the tasks of this TFG, several drivers and libraries have been used, in addition to those specific to the C programming language, and the following is intended to name and explain the most significant drivers and libraries used in order to understand their usefulness in the developed software.

• **Pthreads** (pthreads(7)): It allows us to segment the execution of the code into different threads that run in parallel and thus be able to divide and perform different tasks independently. These threads are known as POSIX threads, an API designed by the IEEE standards for Unix systems. The main difference between these threads is with those in Windows, which we find in the API designed by Microsoft and in their behaviour, as they differ in how they handle signals or synchronize at the kernel level.

By including a lightweight application called a timer to define the period of the thread and send it to sleep during this period, we achieve the periodical execution threads that have been used to perform the constant tasks of slow control, monitoring and communication of the DPB.

- **I**<sup>2</sup>**C driver** (I<sup>2</sup>C application source): The I<sup>2</sup>C application abstracts and uses the Linux I<sup>2</sup>C driver itself, reducing it to different functions so that allow us to perform the necessary operations using the I<sup>2</sup>C interface, either initiating communication with the device, reading from a register or writing to it. This is a great help when dealing with the I<sup>2</sup>C devices available in the DPB since we only have to apply the functions accurately, indicating the necessary parameters and following the instructions in the datasheet of each component, but we do not have to worry about the communication process internally since this will be taken care of by the driver.

- Xilinx AMS (Xilinx AMS driver): The Xilinx AMS driver has been included in the Linux kernel so as to be able to access all the relevant data gathered by the AMS SYSMON. The driver provides us access to this information through the sysfs file system, the information

is encoded in ADC code and its conversion to the corresponding magnitude is done by following the guidelines of the Xilinx documentation.

In addition, the driver provides us an alarm system depending on value thresholds. Since the driver treats alarms as IIO device events, we can use the generic Linux kernel tool IIO Event Monitor, which will be explained in more detail in the next section, as a background process that will capture alarms and report them to the main application.