## UNIVERSITAT POLITÈCNICA DE VALÈNCIA

Dpto. de Ingeniería Electrónica

Diseño e Implementación de un Bandgap modular con múltiples salidas en una tecnología CMOS 180nm

Trabajo Fin de Máster

Máster Universitario en Ingeniería de Sistemas Electrónicos

AUTOR/A: García Barrena, Jara

Tutor/a: Herrero Bosch, Vicente

CURSO ACADÉMICO: 2023/2024

#### Resumen

Los bandgaps son componentes imprescindibles en el desarrollo de circuitos integrados, ya que permiten obtener referencias de tensión compensadas en temperatura (y en ocasiones en variaciones del proceso) que se emplean ampliamente en muchas aplicaciones tales como convertidores AD y DA. Habitualmente su diseño se basa en el uso de transistores bipolares parásitos, sin embargo esto presenta ciertas contrapartidas tales como una mayor influencia del ruido de sustrato. En este trabajo se pretende emplear únicamente transistores CMOS en inversión débil, cuyo comportamiento es muy similar a los bipolares y permiten una mejor integración con el resto de los elementos del diseño. Por otra parte, se plantea otro objetivo novedoso, que consiste en el desarrollo del bandgap de una forma modular que permita la creación de múltiples salidas y que dichas salidas tengan la capacidad de soportar un mínimo de carga necesario para su conexión con otros elementos del diseño. Las especificaciones general del Bandgap deberán de ser similares a las de los disponibles comercialmente (en librerías IP) para una tecnología CMOS típica de 180nm.

#### Resum

Els bandgaps són components imprescindibles en el desenvolupament de circuits integrats, ja que permeten obtenir referències de tensió compensades en temperatura (i a vegades en variacions del procés) que s'empren àmpliament en moltes aplicacions com ara convertidors AD i DA. Habitualment el seu disseny es basa en l'ús de transistors bipolars paràsits, tanmateix això presenta unes certes contrapartides com ara una major influència del soroll de substrat. En aquest treball es pretén emprar únicament transistors CMOS en inversió feble, el comportament de la qual és molt similar als bipolars i permeten una millor integració amb la resta dels elements del disseny. D'altra banda, es planteja un altre objectiu nou, que consisteix en el desenvolupament del bandgap d'una forma modular que permeta la creació de múltiples eixides i que aquestes eixides tinguen la capacitat de suportar un mínim de càrrega necessari per a la seua connexió amb altres elements del disseny. Les especificacions general del Bandgap hauran de ser similars a les dels disponibles comercialment (en llibreries IP) per a una tecnologia CMOS típica de 180nm.

#### **Abstract**

Bandgaps components are key elements in the development of integrated circuits, since they allow to obtain temperature compensated voltage references (sometimes they also can provide process compensation) which are widely used in many applications such as AD and DA converters. Usually their design is based in parasitic bipolar transistos, however these components pick more noise from the substrate. This works aims at fully weak inversion CMOS based design with a very similar behavior to a bipolar based one but with a better integration with the rest of the design elements. On the other hand a novel objective is proposed for this work: the development of a modular scheme which allows to create several voltage outputs with a minimum driving capability to enable their direct connection to other design elements. Other general specifications should be similar to commercially available bandgaps (from IP libraries) for a 180nm CMOS technology.

#### **RESUMEN EJECUTIVO**

La memoria del TFM del MUISE debe desarrollar en el texto los siguientes conceptos, debidamente justificados y discutidos, centrados en el ámbito de la IT

| CONCEPT (ABET)                                                                     | CONCEPTO (traducción)                                                                                                       | ¿Cumple?<br>(S/N) | ¿Dónde?<br>(páginas) |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|

| 1. IDENTIFY:                                                                       | 1. IDENTIFICAR:                                                                                                             |                   |                      |

| 1.1. Problem statement and opportunity                                             | 1.1. Planteamiento del problema y oportunidad                                                                               | S                 | 1-2                  |

| 1.2. Constraints (standards, codes, needs, requirements & specifications)          | 1.2. Toma en consideración de los condicionantes (normas técnicas y regulación, necesidades, requisitos y especificaciones) | S                 | 9-20                 |

| 1.3. Setting of goals                                                              | 1.3. Establecimiento de objetivos                                                                                           | S                 | 2-3                  |

| 2. FORMULATE:                                                                      | 2. FORMULAR:                                                                                                                |                   |                      |

| 2.1. Creative solution generation (analysis)                                       | 2.1. Generación de soluciones creativas (análisis)                                                                          | S                 | 21-38                |

| 2.2. Evaluation of multiple solutions and decision-making (synthesis)              | 2.2. Evaluación de múltiples soluciones y toma de decisiones (síntesis)                                                     | S                 | 21-38                |

| 3. SOLVE:                                                                          | 3. RESOLVER:                                                                                                                |                   |                      |

| 3.1. Fulfilment of goals                                                           | 3.1. Evaluación del cumplimiento de objetivos                                                                               | S                 | 39-59                |

| 3.2. Overall impact and significance (contributions and practical recommendations) | 3.2. Evaluación del impacto global y alcance (contribuciones y recomendaciones prácticas)                                   | S                 | 61-61                |

Aunque esta memoria es el segundo trabajo de final de máster que presento este mes, considero injusto para todas las personas a las que tengo que reconocer su apoyo repetirles los mismos agradecimientos que les dediqué en el primero, ya que son gente que se merece recibir todas las palabras bonitas posibles, en cualquiera de sus formas y expresiones.

Gracias a mis padres, mamá y papá, por proporcionarme la mejor de las energías, por quitarme todos los agobios y por recordarme que yo podía.

Gracias a mis hermanas, Izarbe y Leyre, por cuidarme, animarme y formar conmigo el vínculo más bonito que pueda tener siempre.

Gracias a Vicente, por inspirarme a ser mejor y a valorarme, a demostrarme que valgo para lo que me gusta hacer y por ser más que un tutor, un amigo y compañero para todo.

Gracias a todos mis amigos, los de siempre y los que han aparecido este año, por ser tan especiales y darme apoyo a base de los mejores abrazos que he recibido nunca.

Gracias a todas estas personas por creer en mí, ser parte de mi confianza y animarme a continuar para alcanzar mis metas. Con este trabajo se cierra una etapa que recordaré con muchísimo cariño, tanto los momentos malos como los buenos, que fueron muchos más.

# Índice general

Bibliografía

| I | Memoria                                                                                                                                                                                                                                                                                                     |                                                          |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1 | Introducción1.1 Efecto de la temperatura en semiconductores1.2 Objetivos del diseño1.3 Metodología y Fases del Proyecto                                                                                                                                                                                     | 1<br>1<br>2<br>4                                         |

| 2 | Estado del arte                                                                                                                                                                                                                                                                                             | 9                                                        |

| 3 | Implementación del diseño  3.1 Condicionantes de diseño  3.2 Principio de funcionamiento  3.3 Arquitectura propuesta  3.3.1 Núcleo  3.3.2 Etapa de salida multitensión para cargas elevadas  3.3.3 Circuito de Start-Up  3.3.4 Análisis de ruido  3.5 Topología propuesta                                   | 21<br>22<br>25<br>25<br>27<br>31<br>32<br>36<br>38       |

| 4 | Resultado de simulación  4.1 Compensación de corrientes  4.2 Tensión de salida compensada  4.3 Tensión de Referencia. Análisis de continua  4.4 Tensión de referencia. Montecarlo  4.5 TEMPCO. Montecarlo  4.6 Transitorio del circuito Start-Up  4.7 PSRR  4.8 Ruido. Valor Nominal  4.9 Ruido. Montecarlo | 39<br>40<br>42<br>44<br>46<br>48<br>52<br>54<br>56<br>58 |

| 5 | Conclusiones                                                                                                                                                                                                                                                                                                | 61                                                       |

| 6 | Trabajo a futuro                                                                                                                                                                                                                                                                                            | 63                                                       |

65

# Índice de figuras

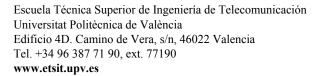

| 1.1        | Sistema de polarización a través de una corriente de referencia                                                                                                        | 3  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

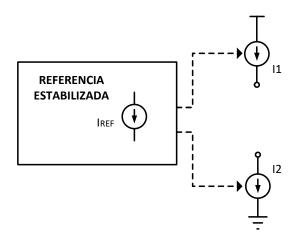

| 1.2<br>1.3 | Flujos de diseño digital y analógico                                                                                                                                   | 7  |

| 2.1        | Copia de una corriente de referencia con un espejo de corriente                                                                                                        | 10 |

| 2.2        | Soluciones implementadas para conseguir una independencia con la tensión de alimentación.                                                                              | 10 |

| 2.3        | Circuito para realizar la compensación de temperatura con dimensionamiento de                                                                                          |    |

|            | BJTs y resistencia.                                                                                                                                                    | 11 |

| 2.4<br>2.5 | Gráfica de las tendencias de las tensiones $V_{BE}$ de ambas ramas con la temperatura. Circuito final que consigue un componente con un coeficiente en temperatura es- | 12 |

|            | table [4]                                                                                                                                                              | 13 |

| 2.6        | Circuito que permite establecer y fijar una tensión de salida deseada mayor                                                                                            | 14 |

| 2.7        | Circuito que permite establecer y fijar una tensión de salida deseada menor [5].                                                                                       | 15 |

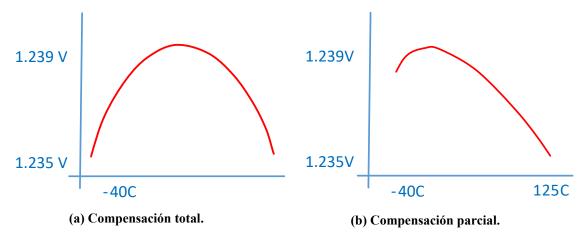

| 2.8        | Compensación del primer orden (componente lineal)                                                                                                                      | 16 |

| 2.9        | Gráfica del segundo orden al compensar el primer orden                                                                                                                 | 17 |

| 2.10       | Compensación del segundo orden.                                                                                                                                        | 17 |

| 2.11       | Gráfica del tercer orden al compensar el segundo orden                                                                                                                 | 18 |

| 2.12       | BJT parásito formado con la unión PNP que existe dentro de la estructura interna                                                                                       |    |

|            | de un MOSFET [7]                                                                                                                                                       | 19 |

| 2.13       | Cambio de topología del circuito que consigue un coeficiente en temperatura estable que utiliza transistores BJT parásitos                                             | 19 |

| 3.1        | Combinación de resistencias para obtener un determinado valor de TEMPCO de-                                                                                            |    |

| J.1        | seado.                                                                                                                                                                 | 22 |

| 3.2        | Circuito de un <i>bandgap</i> que se ha usado como referencia [11].                                                                                                    | 24 |

| 3.3        | Lazo de realimentación de la etapa de salida del <i>bandgap</i>                                                                                                        | 27 |

| 3.4        | Circuito equivalente de la red $\beta$ según el tipo de realimentación.                                                                                                | 27 |

| 3.5        | Circuito de la segunda etapa del <i>bandgap</i> con la red $\beta$ diseñada                                                                                            | 28 |

| 3.6        | Respuesta en frecuencia de la impedancia de salida.                                                                                                                    | 30 |

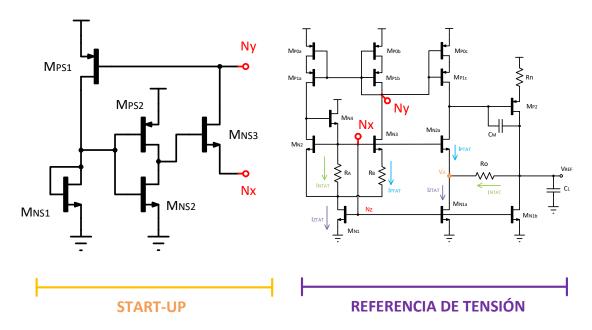

| 3.7        | Circuito de <i>Start-Up</i> y conexiones con el <i>bandgap</i>                                                                                                         | 32 |

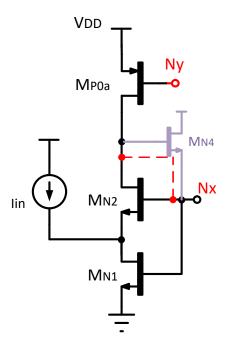

| 3.8        | Modelo equivalente del núcleo formado por los transistores MP0a, MN1, MN2 y                                                                                            |    |

| 5.0        | MN4                                                                                                                                                                    | 33 |

| 3.9        | Apertura del lazo del modelo equivalente del núcleo.                                                                                                                   | 34 |

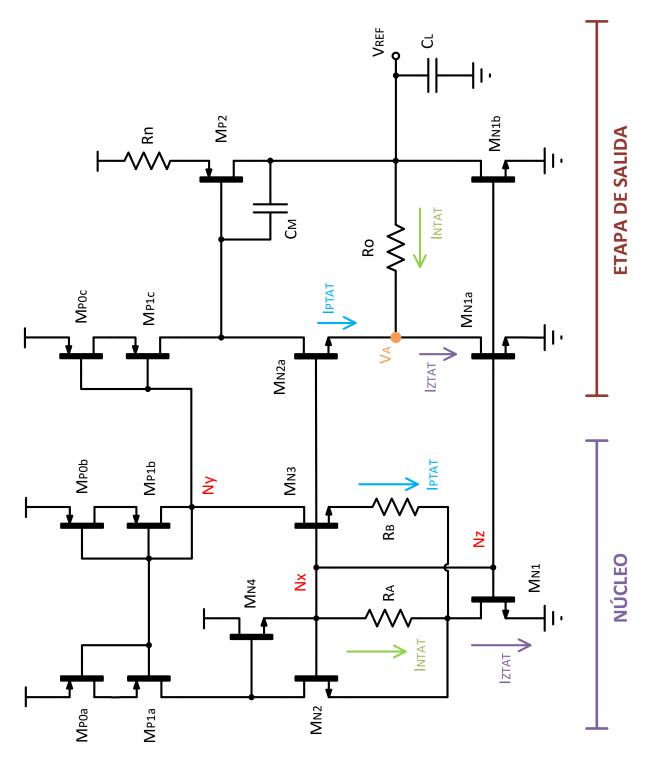

| 3.10       | Esquemático completo del <i>bandgap</i>                                                                                                                                | 38 |

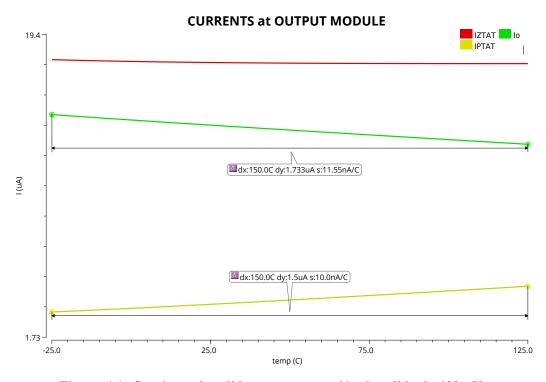

| 4.1        | Corriente de salida para una tensión de salida de 400mV                                                                                                                | 40 |

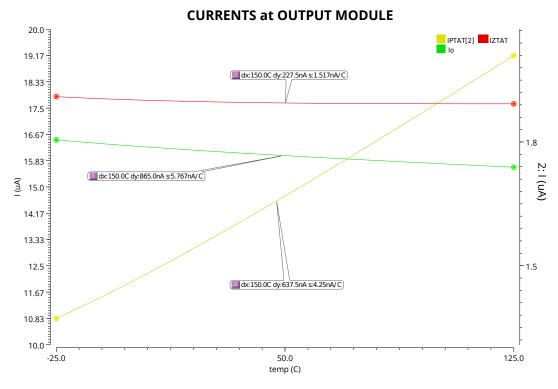

| 4.2        | Corriente de salida para una tensión de salida de 1V                                                                                                                   | 41 |

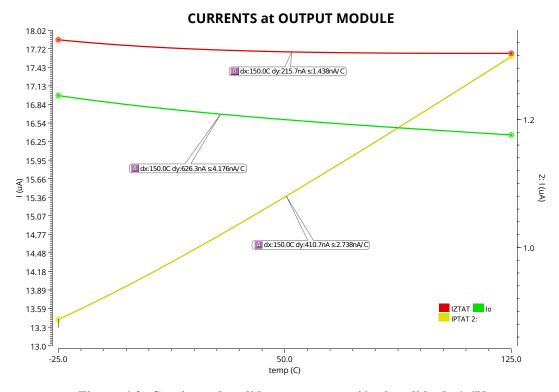

| 4.3         | Corriente de salida para una tensión de salida de 1.4V                                         | 41 |

|-------------|------------------------------------------------------------------------------------------------|----|

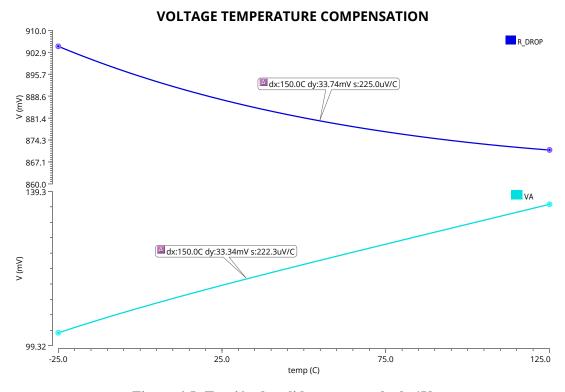

| 4.4         | Tensión de salida compensada de 400mV                                                          | 42 |

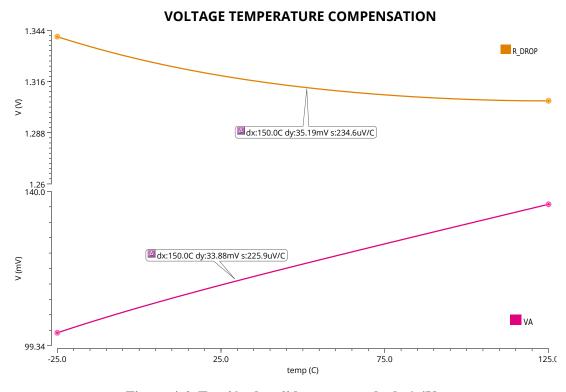

| 4.5         | Tensión de salida compensada de 1V                                                             | 43 |

| 4.6         | Tensión de salida compensada de 1.4V                                                           | 43 |

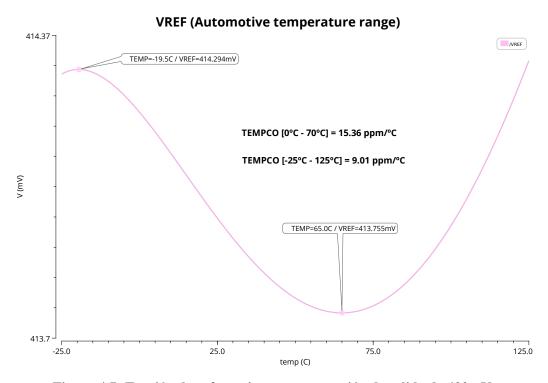

| 4.7         | Tensión de referencia para una tensión de salida de 400mV                                      | 44 |

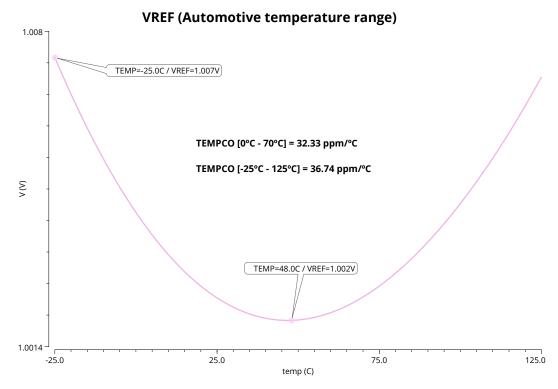

| 4.8         | Tensión de referencia para una tensión de salida de 1V                                         | 45 |

| 4.9         | Tensión de referencia para una tensión de salida de 1.4V                                       | 45 |

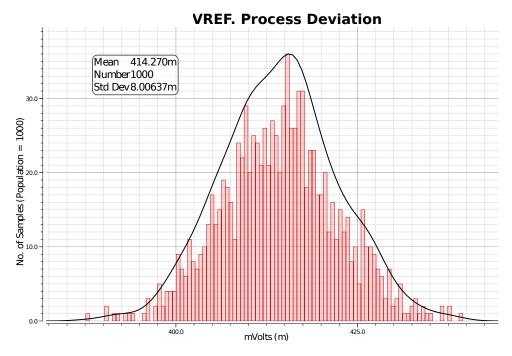

| 4.10        | Análisis de Montecarlo de la tensión de referencia para una tensión de salida de 400mV         | 46 |

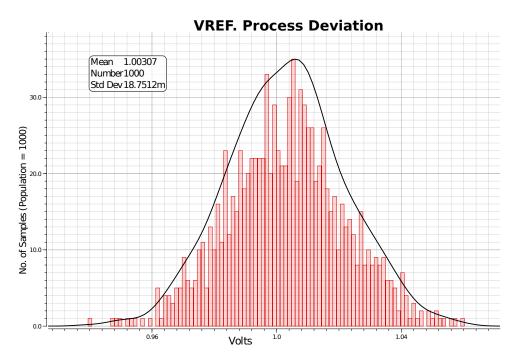

| <u>4</u> 11 | Análisis de Montecarlo de la tensión de referencia para una tensión de salida de 1V.           | 47 |

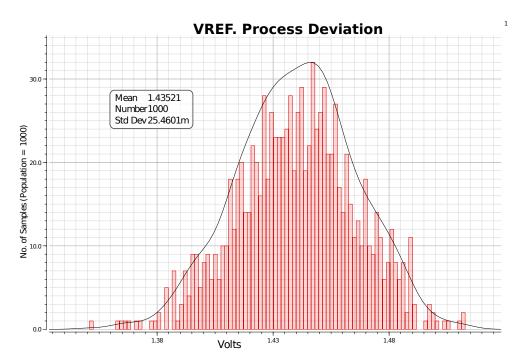

|             | Análisis de Montecarlo de la tensión de referencia para una tensión de salida de               | 7/ |

| 1.12        | 1.4V                                                                                           | 47 |

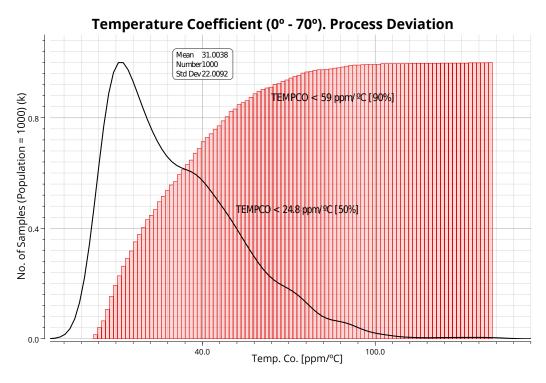

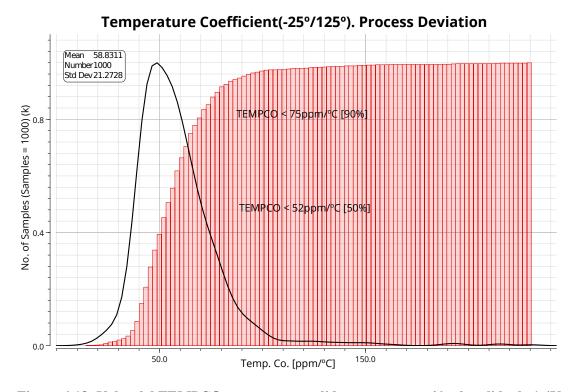

| <b>4</b> 13 | Valor del TEMPCO comercial para una tensión de salida de 400mV                                 | 48 |

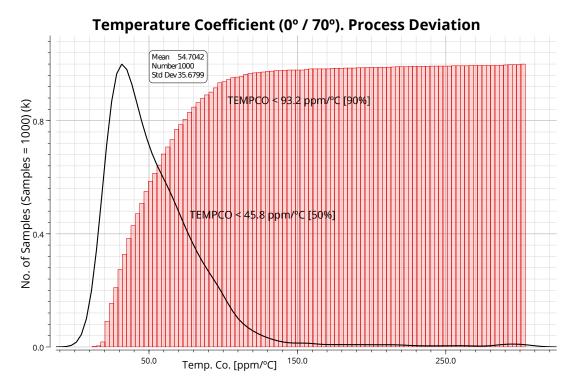

|             | Valor del TEMPCO comercial para una tensión de salida de 1V                                    | 49 |

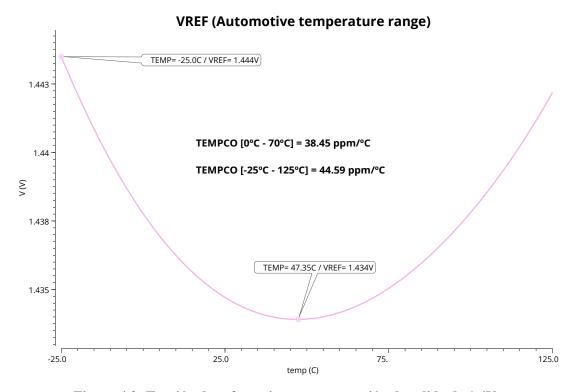

|             | Valor del TEMPCO comercial para una tensión de salida de 1.4V                                  | 49 |

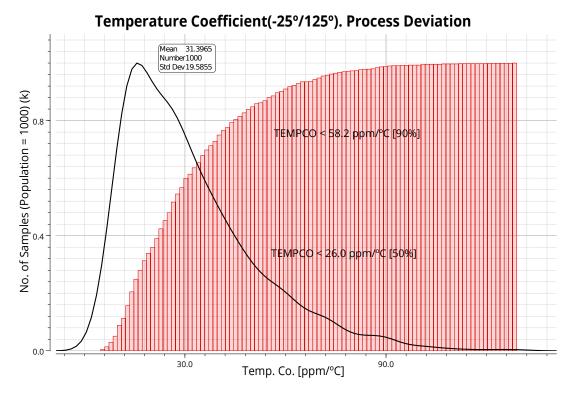

|             | Valor del TEMPCO en rango extendido para una tensión de salida de 400mV                        | 50 |

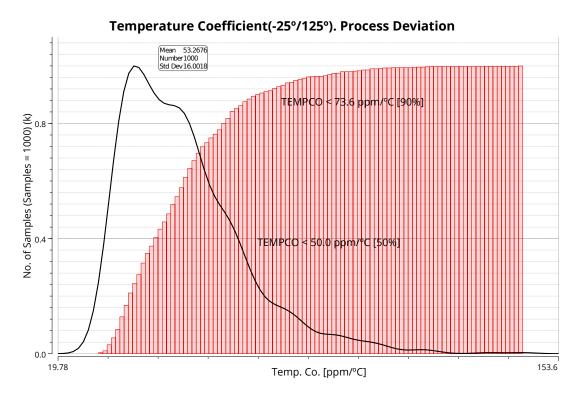

|             | Valor del TEMPCO en rango extendido para una tensión de salida de 1V                           | 51 |

|             | Valor del TEMPCO en rango extendido para una tensión de salida de 1.4V                         | 51 |

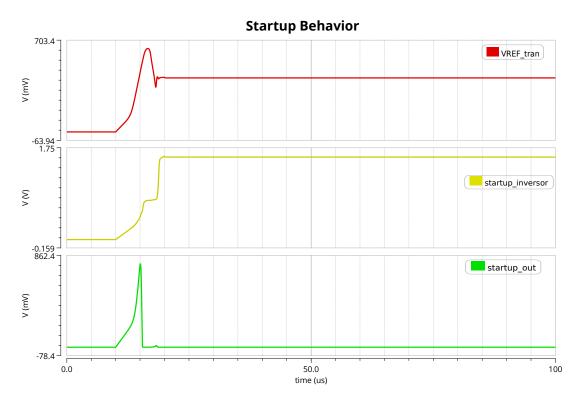

|             | Simulación del transitorio del circuito de <i>Start-Up</i> para una tensión de salida de 400mV | 52 |

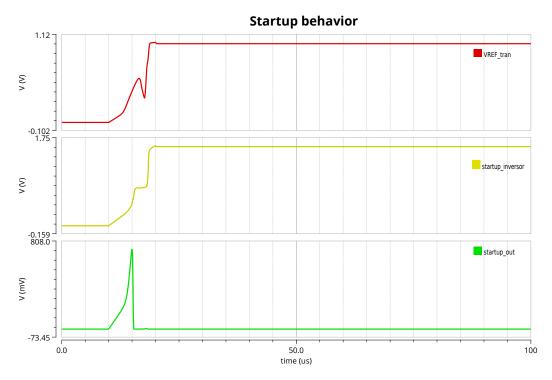

| 4 20        | Simulación del transitorio del circuito de <i>Start-Up</i> para una tensión de salida de 1V.   | 53 |

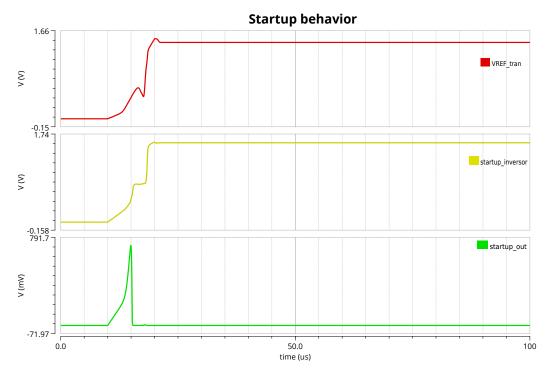

|             | Simulación del transitorio del circuito de <i>Start-Up</i> para una tensión de salida de       | 55 |

|             | 1.4V                                                                                           | 53 |

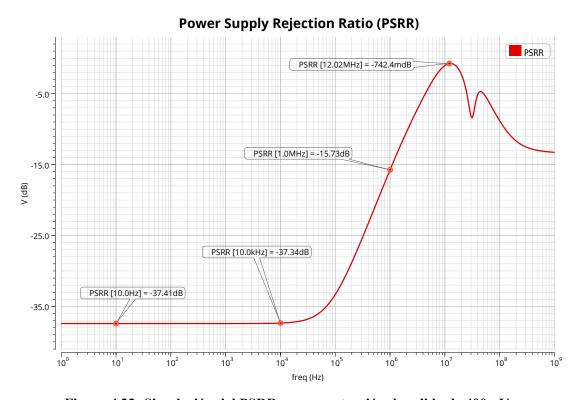

| 4.22        | Simulación del PSRR para una tensión de salida de 400mV.                                       | 54 |

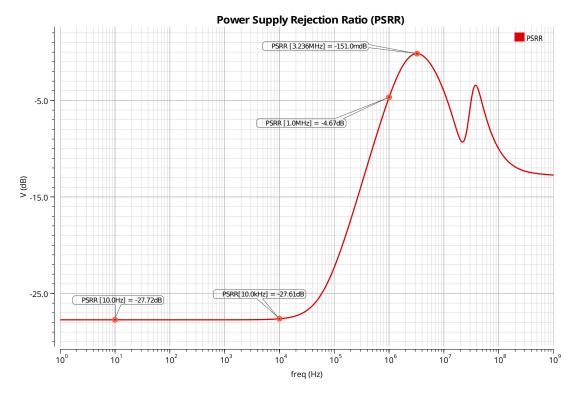

|             | Simulación del PSRR para una tensión de salida de 1V                                           | 55 |

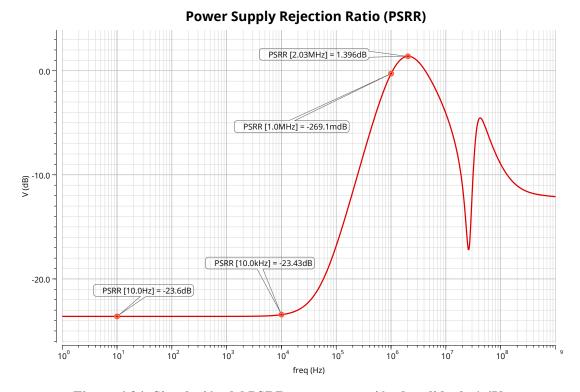

| 4.24        | •                                                                                              | 55 |

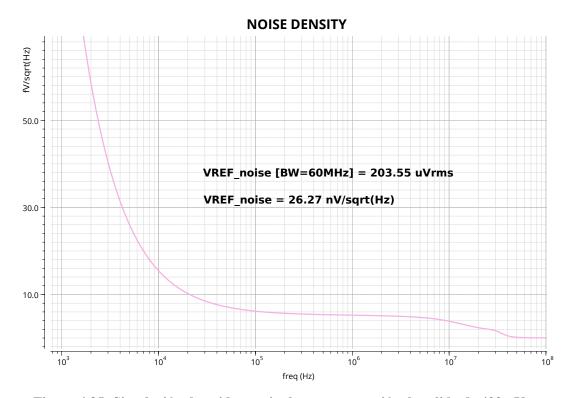

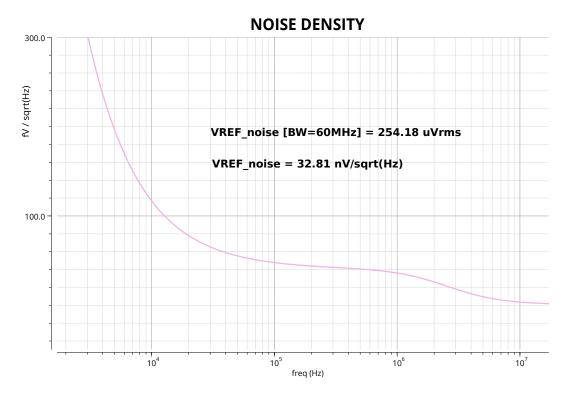

| 4.25        | Simulación de ruido nominal para una tensión de salida de 400mV                                | 56 |

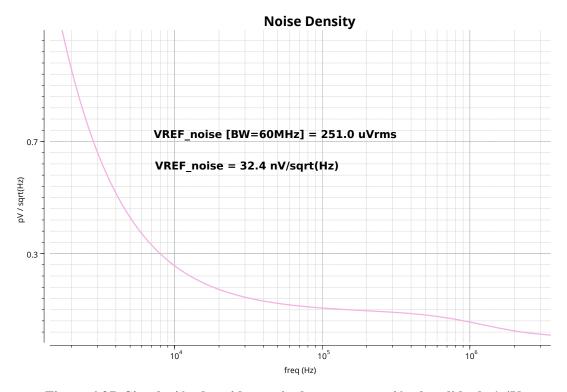

|             | Simulación de ruido nominal para una tensión de salida de 1V                                   | 57 |

| 4.27        | <u>*</u>                                                                                       | 57 |

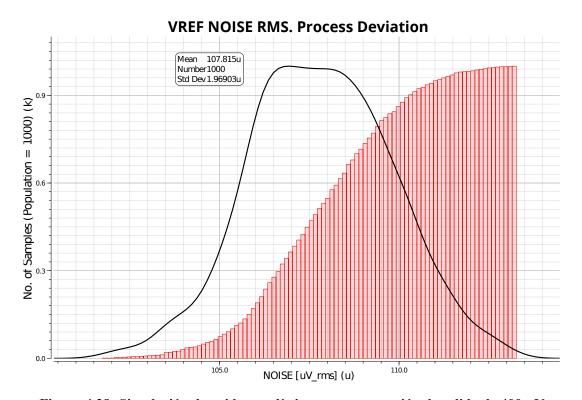

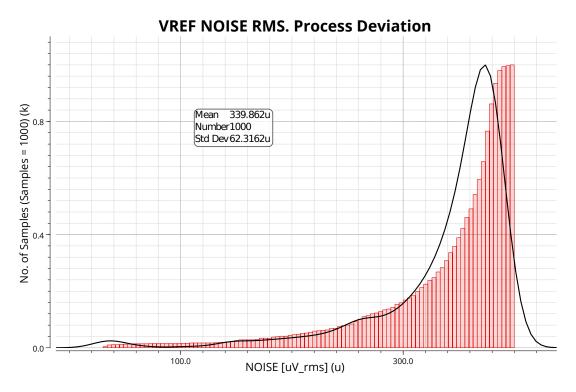

| 4.28        | Simulación de ruido estadístico para una tensión de salida de 400mV                            | 58 |

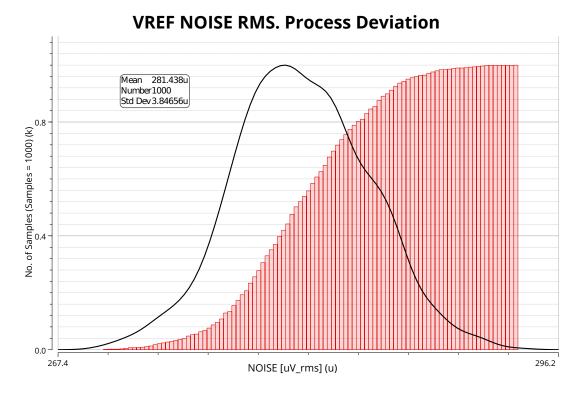

|             | Simulación de ruido estadístico para una tensión de salida de 1V                               | 59 |

|             | Simulación de ruido estadístico para una tensión de salida de 1.4V                             | 59 |

|             |                                                                                                |    |

# Índice de tablas

| 1.1 | Especificaciones objetivo a conseguir con el diseño del bandgap                                 | 4  |

|-----|-------------------------------------------------------------------------------------------------|----|

| 1.2 | Características de los componentes del kit                                                      | 5  |

| 3.1 | Características de los componentes del kit                                                      | 22 |

| 3.2 | Valores ajustados de las resistencias $R_A$ y $R_B$ para conseguir una corriente $I_{ZTAT}$ .   | 37 |

| 3.3 | Valores ajustados de la resistencia R <sub>o</sub> para los diferentes valores de salida que se |    |

|     | quieren alcanzar.                                                                               | 37 |

| 3.4 | Valores establecidos para los componentes CM, CL y Rn                                           | 37 |

# Listado de siglas empleadas

**BJT** Bipolar Junction Transistor.

**CMOS** Complementary Metal-Oxide-Semiconductor.

GBP Gain Bandwidth Product.

**LDO** Low-dropout regulator.

**MOSFET** Metal Oxide Semiconductor Field-Effect Transistors.

**NTAT** Negative to Absolute Temperature.

**NVM** Non-Volatile Memory.

**OPAMP** Operational Amplifier.

PDK Process Design Kit.

**PSRR** Power Supply Rejection Ratio.

**PTAT** Positive to Absolute Temperature.

**TEMPCO** Temperature Coefficient.

**ZTAT** Zero to Absolute Temperature.

# Parte I Memoria

# Capítulo 1

## Introducción

En este Trabajo de Final de Máster se ha implementado un *bandgap* modular con múltiples salidas. Este tipo de circuito tiene como objetivo principal proporcionar una referencia de tensión constante con alta estabilidad térmica. Además, esta estructura se caracteriza por ser de bajo ruido.

#### 1.1. Efecto de la temperatura en semiconductores

El circuito que se va a presentar en este trabajo resuelve una problemática bastante recurrente en los componentes o circuitos que se forman por semiconductores; la variación de sus prestaciones con respecto a la temperatura. Los semiconductores son materiales que tienen una conductividad eléctrica cuyas características se encuentran entre las de un material conductor y uno aislante. Dicha conductividad puede ser modificada mediante la adición de impurezas en un proceso llamado dopado, creando regiones con exceso de electrones (tipo n) o de huecos (tipo p). La dependencia de las características de estos elementos con la variación de la temperatura hace que el diseño y optimización de circuitos sean cruciales para garantizar un buen rendimiento y buenas prestaciones en condiciones de temperatura cambiantes.

El comportamiento de la temperatura en los componentes pasivos se suele expresar en función de un coeficiente de temperatura (ver ec. 1.1), el cual demuestra la variación en la temperatura de la resistencia o capacidad de un componente pasivo (X) en relación con la temperatura. Cabe destacar que este coeficiente suele expresarse en partes por millón de °C (ppm/°C), multiplicándolo por 10<sup>6</sup> [1].

$$TC_F = \frac{1}{X} \cdot \frac{dX}{dT} \tag{1.1}$$

Los principales parámetros que afectan a los dispositivos activos y que producen los cambios debidos a la temperatura son la movilidad ( $\mu$ , ver ec. 1.2) y la tensión umbral ( $V_T$ , ver ec. 1.3).

$$\mu = K_{\mu} T^{-1,5} \tag{1.2}$$

$$v_T(T) = V_T(T_0) - \alpha(T - T_0) \tag{1.3}$$

También es interesante estudiar la tendencia de la temperatura en una unión pn. Esta, presenta una relación con la temperatura que resulta muy interesante al ser lineal, resolviendo la ecuación 1.6 (donde  $V_{G0}$  es la tensión del *bandgap* del silicio y  $V_t$  es la tensión térmica descrita en la ecuación 1.4) al mantener constante la corriente en la ecuación 1.5.

$$V_t = \frac{kT}{q} \tag{1.4}$$

$$\frac{1}{i_D} \cdot \frac{dI_D}{dT} = \frac{1}{I_s} \cdot \frac{dI_s}{dT} - \frac{V_D}{TV_t} = \frac{3}{T} + \left[\frac{V_{G0} - V_D}{TV_t}\right]$$

(1.5)

$$\frac{dv_D}{dT} = \frac{v_D}{T} - V_t (\frac{1}{I_s} \cdot \frac{dI_s}{dT}) = -(\frac{V_{G0} - V_D}{T}) - \frac{3V_t}{T}$$

(1.6)

Así como los componentes activos varían su comportamiento con la temperatura, los activos también pueden sufrir este efecto. Las resistencias compuestas de polisilicio ofrecen un coeficiente de temperatura muy elevado, lo que se traduce en una gran inestabilidad de prestaciones conforme varía la temperatura. En cambio, en resistencias fabricadas con metal, el TEMPCO es muy bajo, por lo que pueden considerarse bastante más estables en temperatura. Por último, las capacidades, si bien tienen una delgada capa de dieléctrico en su estructura, basado en óxido de silicio, están compuestas en su mayoría por metal, por lo que también se consideran elementos robustos ante las variaciones de temperatura.

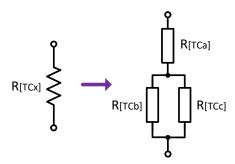

Como en este diseño se va a hacer uso de resistencias hechas de polisilicio, habrá que buscar y formar combinaciones de distintas resistencias cuyos TEMPCOs se cancelen entre ellos, de manera que se consiga una estructura lo más estable posible en temperatura.

Otro parámetro que afecta a los semiconductores a parte de la temperatura es el ruido. Este ruido se genera a causa de las pequeñas fluctuaciones de la señal analógica dentro de los propios componentes. Dichas fluctuaciones provocan una dispersión en las magnitudes de tensión y corriente de los dispositivos, añadiendo una incertidumbre que limitará la relación señal a ruido (SNR) que puede alcanzarse en un diseño analógico.

#### 1.2. Objetivos del diseño

La polarización es un proceso elemental aplicado a circuitos integrados que permite que estos funcionen correctamente. Las diferentes estructuras de un circuito pueden ser polarizadas directamente por corriente, la cual debe permitir que el circuito permanezca constante ante variaciones de temperatura para que los posibles desajustes provocados por estos cambios no se propaguen por el circuito. Hay que tener en cuenta que la corriente destinada a polarizar el circuito debe ser de tipo PTAT (evoluciona de manera positiva con la temperatura), ya que, como se ha explicado en el apartado anterior, la movilidad (ver ec. 1.2) tiene una tendencia negativa con la temperatura, y dicho parámetro se relaciona proporcionalmente a su raíz con la componente gm de los transistores a polarizar. Es decir, la *gm*tiene una tendencia negativa con la temperatura, por lo que se utiliza en los transistores una corriente positiva para poder compensar en temperatura los comportamientos de ambas partes.

Los bandgaps son capaces de llegar a este objetivo y, por ello, son utilizados como referencia de

corriente para llevar a cabo los procesos de polarización descritos. A partir de dicha referencia, se forman espejos de corriente utilizando MOSFETs en configuración diodo.

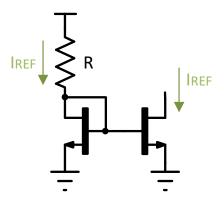

Figura 1.1: Sistema de polarización a través de una corriente de referencia.

Se pretende diseñar una estructura que se comporte como un *bandgap*, proporcionando, además de una corriente de polarización PTAT, una referencia de tensión constante ante variaciones de temperatura e independiente ante parámetros como la tensión de alimentación o incluso las desviaciones del proceso de fabricación. En la implementación de este circuito se buscará alcanzar una serie de características con el fin de conseguir el comportamiento deseado.

En primer lugar, el circuito será modular, es decir, se dividirá en dos partes diferenciadas: la primera se comportará como el núcleo del sistema, el cual proporcionará una corriente de tipo *ztat* (coeficiente de temperatura nulo), que se copiará en la segunda parte del circuito. Cabe destacar que, aunque esta corriente no se utilice directamente, podría llegar a ser útil en otro tipo de aplicaciones (como en los DACs) pudiendo llegar a sacarse como otra posible salida de la célula. También se puede obtener de esta parte del circuito una corriente de tipo PTAT que se puede utilizar como referencia para el proceso de polarización antes explicado. La siguiente etapa será la encargada de producir la tensión de referencia de salida compensada y protegida ante cualquier carga que pueda conectarse a ella. La etapa en sí misma se compone de una realimentación que funciona como un *buffer*, haciendo que la salida no se vea afectada por las cargas que se conecten. Es importante tener en cuenta que este *buffer* debe añadirse como parte del circuito para que pueda estar compensado en temperatura igualmente. Otro de los objetivos del circuito es tener varias referencias de tensión, por lo que la segunda etapa explicada se replicará tantas veces como salidas se quiera tener. Se han establecido como salidas a diseñar las tensiones 0.4V, 1V y 1.4V.

Además, se ha optado por utilizar componentes MOSFETs y no BJT (como es habitual usar en este tipo de estructuras) ya que ayudan a mejorar las prestaciones del circuito, como se explicará más adelante.

En la Tabla 1.1 se muestran las especificaciones iniciales y objetivo que se van a buscar al diseñar el circuito presentado en este trabajo. Tal y como se ha explicado en el apartado anterior, se han fijado como especificaciones los fenómenos que afectan al comportamiento de los semiconductores: temperatura y ruido.

| Especificación                      | Valor | Unidades      |

|-------------------------------------|-------|---------------|

| Coeficiente de temperatura (TEMPCO) | 100   | ppm/°C        |

| Ruido                               | 500   | $\mu V_{rms}$ |

Tabla 1.1: Especificaciones objetivo a conseguir con el diseño del bandgap.

#### 1.3. Metodología y Fases del Proyecto

La metodología llevada a cabo en este trabajo para conseguir el diseño de altas prestaciones presentado sigue un flujo de diseño típico utilizado en un proyecto de microelectrónica.

En primer lugar, hay que diferenciar entre un diseño microelectrónico digital y uno analógico, ya que, dependiendo del diseño en el que se quiera trabajar, el flujo de diseño a seguir es presenta diferencias fundamentales (ver Fig. 1.2).

El diseño en un dominio digital se realiza de una manera más automática. Se utilizan lenguajes de descripción de hardware (*HDL*) para modelar el sistema digital desde distintos niveles de abstracción, bien a alto nivel o a bajo nivel (código RTL, *Register Transfer Layer*). A través de un proceso de síntesis automático, se traduce dicho código en puertas lógicas. Por último, se genera una implementación física (proceso automatizado de extracción) para realizar el *tape out* (fabricación del diseño).

Sin embargo, en el dominio analógico el circuito a diseñar se implementa desde cero, es decir, no existe ningún proceso de trabajo automático. En primer lugar y antes de utilizar software, se plantea una primera propuesta de topología de circuito que se prevé pueda cumplir las especificaciones del diseño. Para esta fase se realiza una revisión bibliográfica y en caso de ser necesario, se plantean alternativas originales que puedan mejorar las existentes en algún aspecto. Posteriormente se establecen las ecuaciones de la topología en los distintos ámbitos de funcionamiento (AC, DC, gran señal etc.). Dichas ecuaciones permitirán ligar las especificaciones del diseño con el dimensionamiento, en términos de geometría y niveles de polarización, de los distintos componentes del mismo, tanto activos como pasivos. Después, el diseño se lleva a la herramienta de CAD y se estudia su comportamiento real a través de herramientas de simulación; tanto simulaciones con valores nominales, como simulaciones que estudiando los posibles resultados que se pueden encontrar tras el proceso de fabricación. Estas últimas jugarán un gran papel a la hora de estudiar el comportamiento del circuito diseñado en este trabajo, pudiendo ser de tipo corner o estadísticas. La simulación de *corners* pretende evaluar las variaciones extremas del proceso de fabricación bajo todas las condiciones posibles, incluyendo temperaturas a lo largo del rango de uso comercial. En el caso de las simulaciones estadísticas (como Montecarlo) que consiste en definir un modelo con variables de entrada, asignar distribuciones de probabilidad a estas variables, y luego realizar numerosas iteraciones en las que se muestrean aleatoriamente los valores de las variables para calcular el resultado del modelo.

Una vez comprobado que el esquemático funciona como se espera, el siguiente paso consiste en la elaboración de *layout*, basado en una estructura *common centroid* para que se consiga un buen *matching* entre os componentes y el diseño funcione correctamente. Una vez comprobado que el esquemático funciona como se espera, el siguiente paso consiste en la elaboración del *layout*. En este paso, es muy importante intentar minimizar los efectos de la dispersión de los valores nominales de los componentes debido al proceso de fabricación. Con esa finalidad se emplearán estructuras basada en el principio *common centroid* que permiten conseguir un buen *matching* entre los

distintos componentes, optimizando el funcionamiento del diseño.

Las herramientas utilizadas a lo largo del circuito presentado en esta memoria son el *Virtuoso Schematics* para la realización de esquemáticos y el *Spectre* y *ADEXL* para la simulación de resultados (nominales y estadísticas, respectivamente). Una funcionalidad característica del Virtuoso de *Cadence* es que permite trabajar de manera jerárquica, es decir, se pueden crear librerías donde se van diseñando distintas células independientes. Dentro de esas células, es posible crear diferentes vistas (esquemático, simulación, *layout...*) que trabajan con dicha célula realizando distintas acciones, lo que permite mantener un orden y coherencia en el diseño. En el caso del *layout* se utiliza el *Virtuoso Layout*, el cual dispone de herramientas de verificación física (*PVS - DRC*) y de extracción automática (*Quantus - QRC*).

Todas estas herramientas funcionan con la información que proporciona el kit de diseño de fabricación (PDK) que indica las reglas de diseño y fabricación indicadas por la fundición. En este trabajo se ha utilizado el PDK XP018 1.8V/5V de XFAB. El proceso XP018 es una tecnología modular CMOS de señal mixta analógica de alto rendimiento de  $0.18\mu m$ . Este PDK se basa en un proceso estándar industrial de un solo polisilicio con hasta seis capas metálicas de  $0.18\mu m$  de puerta. Emplea un pozo de tipo N (N-well), e integra módulos de alto voltaje y memoria no volátil (NVM), la plataforma está diseñada para aplicaciones que necesitan una solución integrada y un proceso rentable para circuitos integrados de alto rendimiento [2]. En cuanto a los componentes característicos en este kit, se pueden encontrar en la Tabla 1.2.

| Componente    | Características                                  |

|---------------|--------------------------------------------------|

| Transistores  | 12V - 60V HV                                     |

| Resistencias  | Medium R P-doped polysilicon 960ohm/sq           |

| Resistencias  | HR P-doped polysilicon 6.7kohm/sq                |

| Condensadores | MIM (1fF/ $\mu m^2$ ) o MIMH (2.3fF/ $\mu m^2$ ) |

| Memorias      | EEPROM (basadas en SONOS)                        |

Tabla 1.2: Características de los componentes del kit.

Figura 1.2: Flujos de diseño digital y analógico.

Teniendo en cuenta la metodología descrita anteriormente, se pueden definir de manera clara y concisa las diferente fases del proyecto que se han seguido para alcanzar el objetivo establecido con las especificaciones iniciales.

#### Documentación y Bibliografía

- Búsqueda de información sobre *bandgaps* y posibles estructuras.

- Búsqueda de información sobre el estudio de la compensación en temperatura.

#### Proceso de diseño del circuito

Planteamiento teórico del circuito: análisis de bloques y planteamiento de ecuaciones generales y de las diferentes etapas.

#### Esquemático y simulación en Virtuoso

- Esquemático de la estructura planteada del bandgap.

- Búsqueda de valores para sacar tres salidas compensadas en temperatura: 0.4V, 1V y 1.4V.

- Simulación de valores nominales del esquemático.

- Simulación de corners.

- Simulación estadística de tipo Montecarlo.

#### Redacción

- Redacción de la memoria del proyecto, la cual demuestre todo el trabajo realizado.

- Procesamiento de datos y elaboración de esquemáticos para complementar las explicaciones de la memoria, haciendo uso del software Visio.

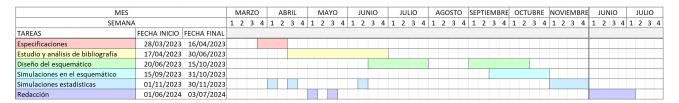

Figura 1.3: Diagrama de Gantt del proceso de realización del presente trabajo.

## Capítulo 2

### Estado del arte

Los *bandgaps* son estructuras que proporciona una tensión de salida constante con la temperatura y de las que se puede obtener también una componente de corriente de referencia constante PTAT para permitir una polarización independiente de la temperatura. Además, se busca que estos tipos de componentes también sean independientes a la tensión de alimentación del circuito y al proceso de fabricación. Si bien esta última es más difícil de conseguir, la independencia a la alimentación puede conseguirse implementando distintas soluciones.

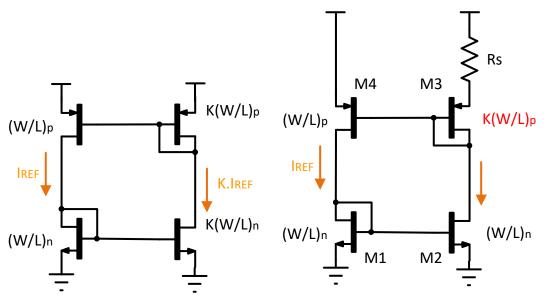

En la Figura 2.1 se muestra un espejo de corriente que copia una corriente de referencia generada en una resistencia. Este circuito no es independiente a la alimentación, ya que si Vdd llegara a cambiar de valor, la corriente también lo haría. Si se implementa el mismo espejo pero realimentado (ver Fig. 2.2a), sí se consigue que la alimentación quede aislada de la corriente al estar esta encerrada en el lazo formado por la realimentación. Sin embargo, el problema reside en que no se puede fijar la corriente, por lo que no se sabe con qué corriente se podrá trabajar. La única manera de fijar la corriente consistiría en introducir un interruptor que proporcionara al circuito una corriente establecida, y rápidamente se cerrara para dejar a la corriente capturada en el bucle (formando un *latch* de corriente), lo cual no es fácil de implementar.

Otra solución en la que se podría fijar la corriente de manera más sencilla sería la mostrada en la Figura 2.2b. La resistencia fija la corriente deseada (ver ec. 2.2) y se consigue controlar este parámetro, haciendo que, en el caso de que la alimentación varíe, la corriente se mantenga constante. En cambio, en este circuito no se consigue una independencia con la temperatura, ya que hay que ésta afecta a varios de los parámetros descritos en la ecuación 2.2.

$$V_{GS4} = V_{GS3} + I_{out}R_s \tag{2.1}$$

$$I_{out} = \frac{2}{K_{pp}(W/L)_4} \frac{1}{R_S^2} (1 - \frac{1}{\sqrt{K}})^2$$

(2.2)

Figura 2.1: Copia de una corriente de referencia con un espejo de corriente.

- (a) Realimentación de un espejo de corriente.

- (b) Realimentación de un espejo de corriente con una resistencia.

Figura 2.2: Soluciones implementadas para conseguir una independencia con la tensión de alimentación.

Para conseguir un circuito del que se pueda obtener una tensión constante en temperatura, es necesario disponer de un componente con un coeficiente en temperatura estable y conocido, a ser posible con una buena linealidad. Un transistor bipolar (BJT) ofrece una  $V_{BE}$  con una dependencia en temperatura muy precisa y de tendencia negativa, operando a corriente de colector constante, la cual es muy parecida a la de un diodo (ver ec. 1.6).

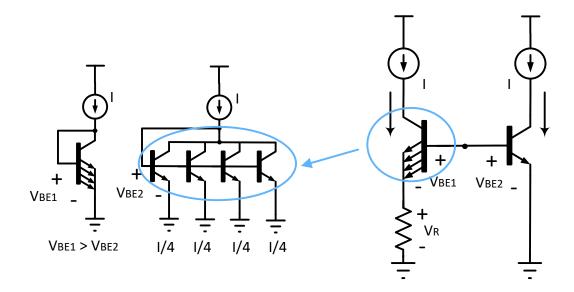

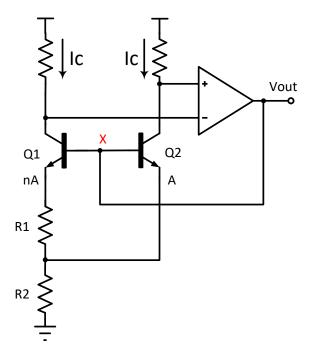

En primer lugar, se plantea el circuito de la Figura 2.3, el cual consta de dos ramas con dos BJT, por las que pasa una determinada corriente. En una de las ramas se ha añadido una resistencia con la que poder generar una caída de tensión de la que se podrá aprovechar su tendencia también. A la hora de fijar las caídas de tensión en ambas ramas, hay que tener en cuenta que por la rama que contenga la resistencia, la  $V_{BE}$  deberá ser menor que la del transistor de la rama opuesta, ya que la misma caída de tensión tendrá que ser repartida por las ramas de manera equitativa (en una se tiene que tener en cuenta la caída de tensión de la resistencia y en otra no). Por ello, se puede establecer la corriente de dos formas distintas; se puede hacer pasar una corriente I por la rama sin resistencia, y una corriente I/n por la rama con la resistencia, o hacer pasar por ambas ramas la misma corriente, pero dimensionando el BJT con la resistencia de manera correcta. Cabe destacar que el dimensionamiento de corriente en un BJT es diferente al que se puede realizar en un MOSFET. En la Figura 2.3 se puede observar una estructura que implementa n BJT en paralelo, de manera que la corriente se repartirá por los n caminos que forman los colectores de los bipolares,

consiguiendo rebajar la corriente n veces, tal y como quiere conseguirse en la rama del BJT con la

resistencia.

Figura 2.3: Circuito para realizar la compensación de temperatura con dimensionamiento de BJTs y resistencia.

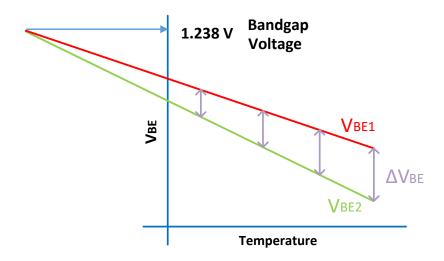

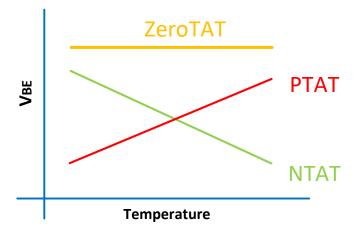

Como ya se ha explicado, la tensión  $V_{BE}$  tiene una tendencia NTAT con la temperatura, por lo que se necesitará otra tendencia positiva que la contrarreste para poder obtener la tensión compensada. Al ser la corriente de una rama menor que la otra, las  $V_{BE}$  variarán en temperatura como lo mostrado en la gráfica 2.4 (a mayor corriente, mayor dependencia con la temperatura). cabe destacar que si se extrapola la relación entre  $V_{BE}$  y la temperatura hasta 0K, las curvas tiene un origen común en  $V_{BE}\approx 1,238V$ . Como puede observarse, la diferencia entre ambas es positiva y creciente con la temperatura (ver ec. 2.5), por lo que la caída en la resistencia será PTAT y, por consiguiente, la corriente que pase por la misma también (ver ec. 2.6). Teniendo una tendencia positiva en corriente, y otra negativa en tensión, se puede conseguir una tensión compensada al combinar ambas tendencias.

Añadiendo una segunda resistencia (ver Fig. 2.5) por la que pase dos veces la corriente PTAT que

pasa por una rama (ver ec. 2.7), se consigue una tensión PTAT, que sumada a la tensión  $V_{BE2}$  puede conseguirse la compensación en la tensión alcanzada en el punto x, que sigue la expresión mostrada en la ecuación 2.8 (haciendo uso de un operacional) [3].

Cabe destacar que esta solución presenta dos lazos de realimentación; uno negativo, formado por el transistor Q2 y el terminal positivo y salida del OPAMP y uno positivo formado por el transistor Q1, con la R1, y el terminal negativo y salida del OPAMP. El lazo de realimentación negativa presenta una ganancia mayor (ver ec. 2.3) que la realimentación positiva (ver ec. 2.4), por lo que el sistema asegura que nunca podrá llegar a un estado de inestabilidad.

$$A_{-} = -\frac{R}{R_2} \tag{2.3}$$

$$A_{+} = \frac{R}{R_1 + R_2} \tag{2.4}$$

$$V_{R1} = V_{BE2} - V_{BE1} \rightarrow PTAT \tag{2.5}$$

$$I_{R1} = \frac{V_{R1}}{R_1} \to PTAT \tag{2.6}$$

Figura 2.4: Gráfica de las tendencias de las tensiones  $\mathbf{V}_{BE}$  de ambas ramas con la temperatura.

$$I_{R2} = I_{R1} + I_C \approx 2I_C \tag{2.7}$$

$$V_{out} = V_{BE2} + V_{R2} = V_{BE2} + 2\frac{\Delta V_{BE}}{R_1}R_2$$

(2.8)

Figura 2.5: Circuito final que consigue un componente con un coeficiente en temperatura estable [4].

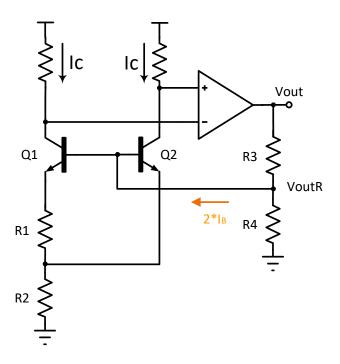

Cabe destacar que el circuito presentado proporciona una tensión constante en temperatura pero su valor no puede fijarse o modificarse. Es posible introducir una serie de modificaciones que permitan controlar dicha tensión de salida, y configurarla a un valor específico de interés.

En la Figura 2.6 se presenta el circuito anteriormente analizado, al que se le ha añadido un divisor resistivo a la salida del OPAMP, formado por las resistencias R3 y R4. Al añadir a la ecuación anterior 2.8 el efecto de dichas resistencias, se obtiene una nueva ecuación que define la tensión resultante de aplicar el divisor (ver ec. 2.9). A partir de esta ecuación, se puede deducir la expresión de la  $V_{out}$  de salida compensada (ver ec. 2.11), con la que se puede comprobar que la tensión resultada puede configurarse a partir de las resistencias del divisor y, además, la tensión siempre será mayor que la que se puede obtener en el circuito 2.5.

$$V_{outR} = V_{BE2} + V_{R2} = \left(V_{BE2} + 2\frac{\Delta V_{BE}}{R_1}R_2\right) \cdot \left(1 + \frac{R_3}{R_4}\right) \tag{2.9}$$

$$V_{out} - V_{outR} = 2I_B \cdot R_3 \tag{2.10}$$

$$V_{out} = (V_{BE2} + 2\frac{\Delta V_{BE}}{R_1}R_2) \cdot (1 + \frac{R_3}{R_4}) + 2I_B \cdot R_3$$

(2.11)

Figura 2.6: Circuito que permite establecer y fijar una tensión de salida deseada mayor.

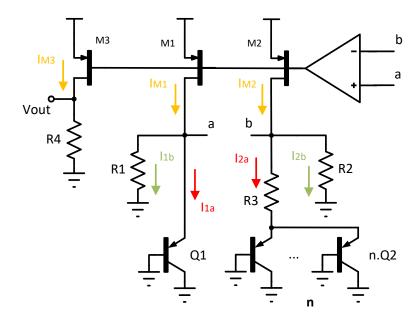

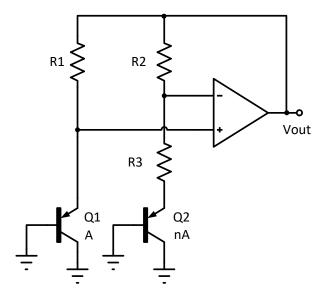

Por otra parte, el circuito de la Figura 2.7 permite conseguir una tensión configurable menor [5]. Esta estructura añade las resistencias R1 y R2 para crear corrientes  $I_{1b}$  e  $I_{2b}$  de tipo NTAT a partir de las tensiones  $V_a$  y  $V_b$  (de tipo NTAT, ver ec. 2.12) que combinadas con las ya obtenidas corrientes  $I_{1a}$  e  $I_{2a}$  PTAT (del ejemplo anterior) consiguen proporcionar una corriente compensada, ya que se diseña para para tener coeficientes con el mismo módulo pero signo contrario (ver ec. 2.13). Las sumas de los pares de las corrientes a y b son recogidas a través de los transistores M1 y M2 (se obtiene la misma corriente compensada por todas las ramas, ver ec. 2.14) que junto con el OPAMP forman un lazo de realimentación que garantiza el funcionamiento del *bandgap*. El transistor M3 actúa como un espejo de corriente de copia (y escala si es necesario) la corriente de M1 y M2 inyectándola en R4 para generar la tensión de salida compensada.

$$V_a = V_b = V_T \cdot \ln \frac{I_{1a}}{I_s} \to NTAT \tag{2.12}$$

$$I_{1a} = I_{2a} = \frac{V_T}{R_3} \ln n \to PTAT$$

,  $I_{1b} = I_{2b} = \frac{V_{F1}}{R_2} \to NTAT$  (2.13)

$$I_{out} = I_{M2} = I_{M1} = I_{1a} + I_{2b} = \frac{V_T}{R_3} \ln n + \frac{V_{F1}}{R_2}$$

(2.14)

$$V_{out} = I_{out}R_4 \tag{2.15}$$

Figura 2.7: Circuito que permite establecer y fijar una tensión de salida deseada menor [5].

Hasta este punto, para conseguir una compensación en temperatura se ha presentado como solución una idea basada en combinar un comportamiento PTAT con uno NTAT, de manera que estas tendencias se cancelen y obtener un TEMPCO nulo. En la práctica, no es posible obtener un comportamiento totalmente igual en ambas tendencias, ya que estas componentes sufren una distorsión no lineal (curvatura del bandgap), y la  $V_{BE}$  no es una magnitud que evolucione linealmente. De la ecuación real de la tensión  $V_{BE}$  (ver ec. 2.16), se puede deducir otra expresión (ver ec. 2.17) donde se diferencien dos partes importantes: la componente lineal y la componente no lineal [6].

$$V_{BE}(T) = V_{G0}(1 - \frac{T}{T_f}) + V_{BE}(T_f)\frac{T}{T_f} - \rho \frac{kT}{q} \ln \frac{T}{T_f} + \frac{kT}{q} \ln \frac{I_C(T)}{I_C(T_f)}$$

(2.16)

$$V_{BE}(T) = V_{lineal}(T) + V_{nolineal}(T)$$

(2.17)

$$V_{lineal}(T) = V_{G0} + (V_{BE}(T_f) - V_{G0})\frac{T}{T_f}$$

(2.18)

$$V_{nolineal}(T) = (\rho - \emptyset) \frac{kT}{q} \ln \frac{T}{T_f}$$

(2.19)

Aplicando este nuevo enfoque de  $V_{BE}$ , el desarrollo presentado del circuito 2.5 puede modificarse, de manera que se introduzca a su comportamiento la componente no lineal que caracteriza a la  $V_{BE}$ .

$$V_{out} = V_{BE2} + 2\frac{\Delta V_{BE}}{R_1}R_2 = V_{BE2} + 2\frac{R_2}{R_1}V_T \ln n$$

(2.20)

$$V_{out}(T) = V_{G0} + V_{ntat} + V_{ptat} - V_{nolineal}$$

(2.21)

Se diseñará el circuito de manera que las componentes lineales PTAT y NTAT se anulen, y la tensión de salida depende únicamente de la componente no lineal:

$$V_{ntat} + V_{ptat} = (V_{BE}(T_f) - V_{G0})\frac{T}{T_f} + 2\frac{R_2}{R_1}V_T \ln n \rightarrow se \ anulan$$

(2.22)

$$V_{nolineal} = (\rho - \emptyset) \frac{kT}{q} \ln \frac{T}{T_f}$$

(2.23)

La expresión 2.23 tiene un comportamiento complejo formado por distintos órdenes, cuyo efecto en el mecanismo de compensación es difícil de visualizar.

Por ello, se plantea otra forma de representar la expresión de  $V_{BE}$  empleando una aproximación por serie de Taylor (ver ec. 2.24), con la que se puede identificar de manera diferenciada los términos que se corresponden a cada orden.

$$V_{BE}(T) = a_o + b_o(T - T_o) + c_o(T - T_o)^2 + \dots + n_o(T - T_o)^n$$

(2.24)

El término que viene dado por el coeficiente  $b_o$  es el término de primer orden. Teniendo en cuenta el desarrollo llevado a cabo anteriormente, dicho término se correspondería a la parte lineal (ver ec. 2.18) que, haciendo uso del diseño, podría llegar a compensarse (ver Fig. 2.8).

Figura 2.8: Compensación del primer orden (componente lineal).

Al eliminar el primer orden de la ecuación 2.24, las componentes que definen la  $V_{BE}$  son el segundo orden y siguientes, los cuales ya son partes no lineales de la expresión, por lo que se corresponderían con el comportamiento del resultado obtenido en el anterior desarrollo (ver ec. 2.23). Como el término predominante en la ecuación sería, en este punto, el segundo orden, la respuesta de  $V_{BE}$  mostraría el comportamiento de esta componente (ver Fig. 2.9a). En el caso de no conseguir una compensación lineal total como la mostrada en la Figura 2.8 (consiguiendo una ZTAT), el segundo orden se mostrará como en la Figura 2.9b.

Figura 2.9: Gráfica del segundo orden al compensar el primer orden.

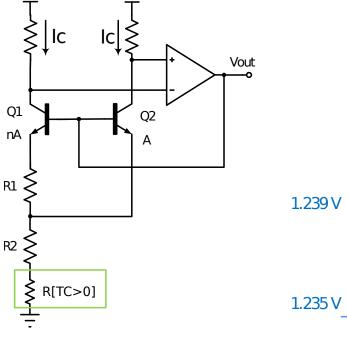

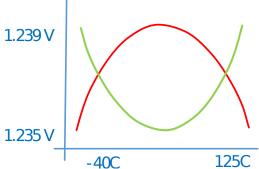

Siguiendo el mismo razonamiento que en la compensación del primer orden, se podría compensar el segundo consiguiendo sumar otro segundo orden con el mismo módulo pero signo contrario. Esta tendencia opuesta puede conseguirse añadiendo al circuito 2.5 una resistencia con un coeficiente de temperatura propio diferente a cero (hasta ahora, en todos los desarrollos se ha supuesto que las resistencias empleadas eran ideales y constantes en temperatura). Para compensar el segundo orden con tendencia negativa mostrado en la gráfica 2.9a, se debería introducir una resistencia de TEMPCO cóncavo (positivo de segundo orden) (ver Fig. 2.10a).

(a) Circuito que compensa el segundo orden con una resistencia de TEMPCO positivo (curva cóncava).

(b) Compensación del segundo orden con dos tendencias opuestas.

Figura 2.10: Compensación del segundo orden.

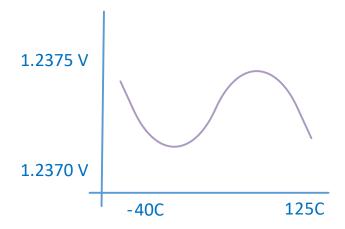

De la misma manera que al compensar el término lineal, en la gráfica se podía observar la influencia principal del segundo orden, al compensar este último con la gráfica mostrada en 2.10b se pasa a observar la siguiente componente, la de tercer orden (ver Fig. 2.11). Es importante prestar especial atención al eje de las gráficas que describe el rango de tensión de los órdenes representados. A mayor orden, el rango de tensiones es menor y, por tanto, la tensión está más compensada en temperatura.

Figura 2.11: Gráfica del tercer orden al compensar el segundo orden.

Las estructuras anteriormente presentadas consiguen proporcionar a su salida una tensión constante con la temperatura, pero según su configuración, también introducen una serie de problemas que pueden afectar al comportamiento del circuito y las demás prestaciones que ofrece.

Por una parte, el uso de un OPAMP tiene una serie de inconvenientes que se han de tener en cuenta. El más importante de ellos es el *offset* que aparece entre los terminales del operacional. En el circuito 2.5, esta diferencia de tensión puede causar un desbalanceo de las corriente  $I_C$  y, al no ser iguales, no poder llegarse a dar la compensación de la tensión de salida. Existen algunos circuitos que consiguen solucionar este problema [7], pero en este trabajo se ha optado por no utilizar el OPAMP debido a que, a parte del problema del offset, también puede acarrear valores elevados de ruido. Además, se busca diseñar una estructura que pueda "autopolarizarse", es decir, comenzar a funcionar por ella misma (proporcionándose una corriente que le permita encenderse) y polarizarse de manera correcta sin utilizar una referencia como las anteriormente explicadas.

Por otra parte, diseñar circuitos basados en transistores bipolares (BJTs) como los empleados en las estructuras de compensación ya analizadas, puede traducirse en un problema si se quiere fabricar el circuito utilizando tecnología CMOS. El número de máscaras necesarias para crear un transistor bipolar incrementa mucho la complejidad del proceso y su coste.

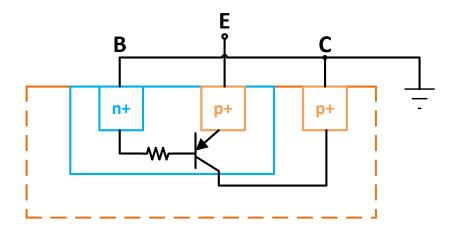

Una posible solución sería aprovechar la unión PNP de un MOSFET para formar un BJT parásito (ver Fig. 2.12), aprovechando el pozo y el contacto de sustrato. Sin embargo, para que funcione, es necesario conectar la base y el colector a tierra, por lo que habría que introducir una serie de modificaciones en el circuito 2.5 para poder utilizar los BJTs parásitos. La Figura 2.13 muestra este cambio de topología.

Considerando que las dos resistencias R1 y R2 son iguales, se puede deducir la expresión de  $V_{out}$  del circuito presentado (ver ec. 2.20). Dicha ecuación es similar a la obtenida en el caso del uso de

BJT comunes (ver ec. 2.26) por lo que se demuestra que con la utilización de transistores bipolares parásitos también se puede conseguir una compensación en temperatura.

Figura 2.12: BJT parásito formado con la unión PNP que existe dentro de la estructura interna de un MOSFET [7].

$$V_{BE1} - V_{BE2} = V_T \ln n \tag{2.25}$$

$$V_{out} = V_{BE1} + V_T \ln n \frac{R_2}{R_3}$$

(2.26)

Figura 2.13: Cambio de topología del circuito que consigue un coeficiente en temperatura estable que utiliza transistores BJT parásitos.

No obstante, el aprovechamiento de esta unión PNP tiene un gran inconveniente, ya que el ruido proveniente del resto del circuito tiene una gran influencia sobre esta estructura al poder introducirse por el contacto del sustrato hacia el pozo, provocando que el *bandgap* capture interferencias de otras partes del diseño y las envíe a su salida.

Por ello, se ha optado por utilizar en el diseño de este trabajo un circuito basado en dispositivos MOSFETs únicamente para evitar los problemas y complejidad que supone usar los BJT parásitos. Si se consigue un índice de inversión adecuado (muy débil, ver ecs. 2.27 y 2.28) en los transistores MOSFET, estos pueden llegar a tener un comportamiento muy similar al de los BJT, permitiendo que sea posible diseñar circuitos que proporcionen una referencia de corriente o tensión compensadas en temperatura [8].

$$I_{Cbjt} = I_s \ e^{\frac{V_{BE}}{V_T}} \tag{2.27}$$

$$I_{Cmosfet} = I_o \frac{W}{L} \left( e^{\frac{V_{GS} - V_{th}}{nV_T}} \right)$$

(2.28)

# Capítulo 3

# Implementación del diseño

Tras haber explicado en el capítulo anterior el comportamiento del sistema que se quiere diseñar y la teoría que reside detrás del mismo, se va a desarrollar en el presente capítulo las ecuaciones generales de las distintas partes del circuito que se utilizan como punto de partida en el diseño.

#### 3.1. Condicionantes de diseño

Como ya se ha presentado en el capítulo anterior, se han tomado una serie de decisiones al estudiar la teoría que reside detrás de los bandgaps, en cuanto qué componentes utilizar en el diseño del circuito.

Se ha optado por no implementar una estructura que contenga un OPAMP, con el fin de evitar los problemas que introduce. En este diseño, se ha preferido llevar a cabo un circuito de dos etapas, la primera que se encargue de la compensación de temperatura, y la segunda que proteja la salida de los posibles cambios de carga y al mismo tiempo complete dicha compensación de la primera parte. Es decir, esta última etapa simularía el comportamiento del operacional, estando éste implícito en el propio *bandgap*, por lo que no se pierde la compensación en temperatura, y se evitan los problemas característicos del OPAMP y su polarización.

Además, el *bandgap* se diseñará utilizando transistores MOSFETs para evitar los problemas que aparecen en el circuito al utilizar BJTs (ver explicación en 2.12).

También hay que tener en cuenta que en el *kit* que se está utilizando, las resistencias válidas para este diseño son las compuestas por polisilicio, ya que las de metal tienen valores demasiado pequeños. Como ya se introdujo anteriormente, las resistencias de polisilicio presentan un TEMPCO distinto a cero (positivo o negativo), y dependiendo de su dopado (P o N), las curvas son distintas (no son puramente lineales). En la Tabla 3.1 se muestran las características de las resistencias de polisilicio disponibles en el kit. Se observa que tanto los valores nominales como el signo de los TEMPCOs son distintos.

Aprovechando que las diferencias de los coeficientes, se utilizarán combinaciones variadas de resistencias en paralelo y en serie (ver Fig. 3.1) para conseguir los valores de resistencia necesarios en cada punto del circuito, y unos TEMPCOs controlados [9]. Concretamente, las resistencias que se han utilizado en estas combinaciones para conseguir el comportamiento requerido en el diseño son las rpp1k y las rdp.

Figura 3.1: Combinación de resistencias para obtener un determinado valor de TEMPCO deseado.

| Tipo de Resistencia | R[Ohms/□] | TCR (ppm) |

|---------------------|-----------|-----------|

| rnp1h               | 6513.66   | -4016.18  |

| rpp1k1              | 988.46    | -855.88   |

| rnp1                | 339.26    | -1384.19  |

| rpp1                | 290.28    | -117.13   |

| rdp                 | 137.16    | 1293.38   |

| rdn                 | 66.48     | 1419.98   |

| rpp1s               | 7.42      | 2911.05   |

Tabla 3.1: Características de los componentes del kit.

#### 3.2. Principio de funcionamiento

Antes de explicar el funcionamiento del circuito que se ha diseñado en este trabajo, se va a proceder a presentar una serie de desarrollos en los que se ha encontrado una manera adecuada de justificar y solucionar el diseño del *bandgap* debido a la similitud entre la bibliografía que se va a exponer y lo que se quiere conseguir.

La estructura a diseñar se basará en componentes MOSFET únicamente, pero cabe destacar que la tensión de interés de este tipo de transistores, la  $V_{GS}$  no puede aproximarse de la misma manera que la tendencia en temperatura anteriormente solucionada de la  $V_{BE}$  en los transistores BJT. Para demostrar que un transistor MOSFET en inversión débil (ver ec. 2.28) se comporta de forma equiparable a un BJT en cuanto a evolución en temperatura se refiere, se ha utilizado el modelo de simulación BSIM3v3 [10]. Según este modelo, el comportamiento de la  $I_D$  de un transistor MOSFET se rige de la aproximación de la fórmula 3.1. Esta corriente  $I_D$  también se puede expresar a través de una aproximación física de los potenciales del sustrato (ver ec. 3.2). Haciendo uso de las dos posibles aproximaciones, aunque no se conozca el comportamiento en temperatura de la tensión  $V_{GS}$ , sí se puede igualar a los potenciales de la aproximación física de los cuales se conoce su tendencia para poder sacar conclusiones (ver ec. 3.3).

$$I_D = S\mu U_T^2 \sqrt{\frac{q\epsilon_{si}N_{CH}}{4\phi_B}} \exp(\frac{V_{GS} - V_{TH} - V_{OFF}}{nU_T})$$

(3.1)

$$I_D = S\mu U_T^2 \sqrt{\frac{q\epsilon_{si}N_{CH}}{4\phi_B}} \exp(\frac{\phi_s - 2\phi_B}{U_T})$$

(3.2)

$$\frac{V_{GS} - V_{TH} - V_{OFF}}{n} = \phi_s - 2\phi_B \tag{3.3}$$

Donde:

- $I_D$  es la corriente de drenador.

- S es la relación de aspecto del transistor (W/L).

- $\mu$  es la movilidad de los portadores del canal.

- $U_T$  es la tensión térmica.

- $\epsilon_{si}$  es la permitividad del silicio.

- $N_{CH}$  concentración de dopaje del canal.

- $\phi_s$  es el potencial de superficie.

- $\phi_B$  es el potencial de Fermi del sustrato.

- $V_{TH}$  es al tensión umbral.

A partir de lo explicado, se procede a estudiar la tendencia en temperatura de los potenciales del sustrato,  $\phi_s$  y  $\phi_B$  (ver ecs. 3.4 y 3.5).

$$\phi_s(T) = \phi_s(T_o) \frac{T}{T_o} - \frac{3kT}{q} \ln\left(\frac{T}{T_o}\right) + \frac{E_g(T)}{q} - \frac{E_g(T_o)}{q} \frac{T}{T_o}$$

(3.4)

$$\phi_B(T) = \phi_B(T_o) \frac{T}{T_o} - \frac{3kT}{q} \ln{(\frac{T}{T_o})} + \frac{E_g(T)}{2q} - \frac{E_g(T_o)}{2q} \frac{T}{T_o}$$

(3.5)

Realizando la resta de los dos potenciales de la ecuación 3.3, se obtiene:

$$\phi_s(T) - 2\phi_B(T) = (\phi_s(T_o) - 2\phi_B(T_o)) \cdot \frac{T}{T_o}$$

(3.6)

Utilizando los potenciales deducidos en función de la temperatura y despejando  $V_{GS}$  se puede obtener una expresión (ver ec. 3.7) que defina la tendencia de dicha magnitud con la temperatura y de la que podamos sacar conclusiones sobre su comportamiento.

$$V_{GS} = V_{th}(T) + V_{OFF} + \frac{n(T)}{n(T_o)} (V_{GS}(T_o) - V_{th}(T_o) - V_{OFF}) \frac{T}{T_o}$$

(3.7)

Realizando las aproximaciones mostradas en 3.9, 3.10 y 3.11 se obtiene la ecuación final de la  $V_{GS}(T)$ . Para un valor típico de  $K_T$ ,  $V_{OFF}$  y  $V_{GS}$ - $V_{TH}$ ,  $K_G$  se define con un valor negativo y, por tanto, hace que la  $V_{GS}$  tienda a disminuir con la temperatura (ver ec. 3.8) para un valor fijo de

corriente  $I_D$  [11]. Al tener la misma tendencia que la  $V_{BE}$  de un transistor BJT se demuestra que la  $V_{GS}$  en un MOSFET puede tratarse de la misma manera y se comportará igual que los desarrollos llevados a cabo en el capítulo 2 anterior basados en BJTs.

$$V_{GS}(T) \approx V_{GS}(T_o) + K_G(\frac{T}{T_o} - 1) \quad \frac{\partial V_{GS}}{\partial T} < 0$$

(3.8)

$$n(T) \approx n(T_o) \tag{3.9}$$

$$V_{th}(T) = V_{th}(T_o) + K_T(\frac{T}{T_o} - 1)$$

(3.10)

$$K_G = K_T + V_{GS}(T_o) - V_{th}(T_o) - V_{OFF}$$

(3.11)

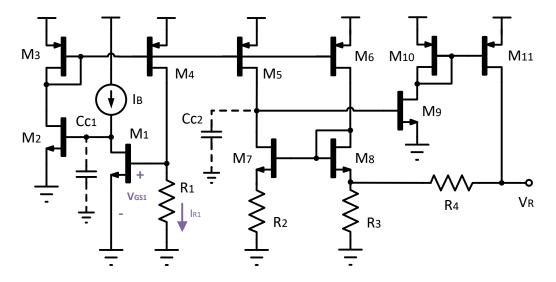

A partir de esta conclusión, se ha analizado el circuito de la Figura 3.2 con el fin de utilizarlo como base a la hora de desarrollar el circuito del *bandgap* de este trabajo. Este desarrollo plantea una serie de ecuaciones que relacionan los parámetros más importantes con el fin de conseguir una cancelación del primer orden. Para ello se adaptan dichas ecuaciones de manera que se agrupan en unos coeficientes que proporcionen una tensión compensada.

Figura 3.2: Circuito de un bandgap que se ha usado como referencia [11].

$$I_{R1} = \frac{V_{GS1}(I_B)}{R_1} \tag{3.12}$$

$$V_R = R_4 I_{R4} + V_{R3} = R_4 \left(\frac{V_{R3}}{R_3} - I_{R1} \frac{S_6}{S_4}\right) + V_{R3}$$

(3.13)

$$V_{R3} = \frac{S_5}{S_4} \cdot \frac{R_2}{R_1} V_{GS1}(I_B) + U_T \ln \frac{S_8 S_5}{S_7 S_6}$$

(3.14)

$$V_R = \alpha V_{GS1}(I_B) + \beta U_T \tag{3.15}$$

$$\alpha = \left(\frac{R_4}{R_3} + 1\right) \frac{S_5}{S_4} \frac{R_2}{R_1} - \frac{S_5}{S_6} \frac{R_4}{R_1} \tag{3.16}$$

$$\beta = (\frac{R_4}{R_3} + 1) \ln \left( \frac{S_8 S_5}{S_7 S_4} \right) \tag{3.17}$$

$$V_{GS}(T) \approx V_{GS}(T_o) + K_G(\frac{T}{T_o} - 1)$$

(3.18)

La solución que se plantea en la ecuación 3.15 se basa en utilizar los dos coeficientes  $\alpha$  y  $\beta$  para compensar la tensión de referencia.

El coeficiente  $\alpha$  acompaña al término negativo en temperatura,  $V_{GS1}(I_B)$  (ver ec.3.19) y el coeficiente  $\beta$ , el término con el que se relaciona es el positivo,  $U_T$  (ver ec. 3.20). El objetivo de estos coeficientes es que al hacer la derivada en temperatura de la tensión de referencia  $V_R$ , el resultado de la suma de ambos términos sea nulo (ver ec. 3.21).

$$\frac{\partial V_{GS1}}{\partial T} < 0 \tag{3.19}$$

$$\frac{\partial U_T}{\partial T} > 0 \tag{3.20}$$

$$\frac{\partial U_T}{\partial T} = \alpha \frac{\partial V_{GS1}}{\partial T} + \beta \frac{\partial U_T}{\partial T} = 0$$

(3.21)

El análisis del circuito que se va a plantear en el siguiente apartado seguirá la misma línea de desarrollo que el anteriormente demostrado.

#### 3.3. Arquitectura propuesta

Como ya se ha indicado en los objetivos, el circuito que se ha diseñado utiliza tecnología MOSFET y se dividirá en dos parte diferenciadas: el núcleo y la etapa de salida que proporcionará tres tensiones distintas compensadas. Además, se añadirá un circuito de *Start-Up* que permitirá al diseño salvar los problemas de arranque característicos de los *bandgaps*.

#### 3.3.1. **Núcleo**

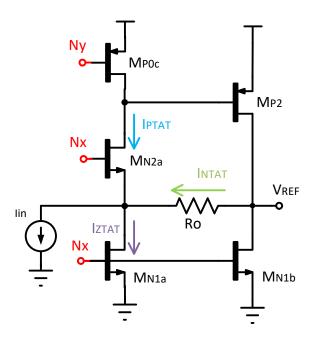

El núcleo es la primera parte del circuito (ver Fig. 3.10), la cual se encarga de generar y proporcionar una corriente constante en temperatura (TEMPCO nulo) a la segunda etapa del *bandgap*.

Para ello, se genera una corriente PTAT (ver ec. 3.22) en la resistencia  $R_B$  a través de la diferencia de las  $V_{GS}$  de los transistores MN2 y MN3 (de la misma forma con la que se creó una  $I_{PTAT}$  en el circuito de la Figura 2.5 y la diferencia de tensión de las  $V_{BE}$ ). Dicha corriente, se copia a través de

la estructura de espejos formada por los transistores MP0a, MP0b, MP1a, MP1b, y será conducida hacia el transistor MN2, por el que pasará una versión escalada de la corriente  $I_{PTAT}$  creada en la resistencia  $R_B$ , la  $I_{PTAT2}$  (ver ec. 3.23). Además, el transistor MN4 alimenta a  $R_A$  con la corriente que fija la tensión  $V_{GS-MN2}$ , de la misma manera que en el circuito 2.7, se genera una corriente  $I_{NTAT}$  (ver ec. 3.24). El punto clave de esta etapa es el drenador del transistor MN1, en el cual se mezclan las tres corrientes mencionadas, donde se busca alcanzar una corriente  $I_{ZTAT}$  (TEMPCO nulo) a través de dicha mezcla (ver ec. 3.25).

$$I_{PTAT} = U_T \, n \ln \left( \frac{S_{P0A}}{S_{P0B}} \cdot \frac{S_{MN3}}{S_{MN2}} \right) \cdot \frac{1}{R_B}$$

(3.22)

$$I_{PTAT2} = I_{PTAT} \frac{S_{P0A}}{S_{P0B}} (3.23)$$

$$I_{NTAT} = \left[V_{GS2}(T_o) + K_{MN2}(\frac{T}{T_o} - 1)\right] \cdot \frac{1}{R_A}$$

(3.24)

$$I_{ZTAT} = I_{PTAT} + I_{PTAT2} + I_{NTAT}$$

$$(3.25)$$

Para saber cuáles son las variables que modificarán el coeficiente de temperatura de la corriente, se ha aplicado la compensación de primer orden dimensionando unos coeficientes  $\alpha$  y  $\beta$  según lo explicado en el apartado . Introduciendo las ecuaciones 3.22, 3.23 y 3.24 en la expresión 3.26, se pueden identificar los coeficientes  $\alpha$  (ver ec. 3.27, positivo en temperatura),  $\beta$  (ver ec. 3.28, negativo en temperatura) y el término constante de la ecuación (ver ec. 3.29). Teniendo en cuenta las ecuaciones estudiadas, se ajustarán los valores de las resistencias  $R_A$  y  $R_B$  (ver valores en la Tabla 3.2) y de los transistores que forman los espejos de corriente (MP0A y MP0B). Una vez conseguida la corriente constante en temperatura, el núcleo se dejará como parte fija del circuito, proporcionando siempre la misma corriente  $I_{ZTAT}$ , independientemente de la tensión de salida que se pretenda conseguir.

$$I_{ZTAT} = \alpha T + \beta T + K_{cte} \tag{3.26}$$

$$\alpha = \left(1 + \frac{S_{P0A}}{S_{P0B}}\right) \cdot n \ln\left(\frac{S_{P0A}}{S_{P0B}} \cdot \frac{S_{MN3}}{S_{MN2}}\right) \cdot \frac{k}{qR_B}$$

(3.27)

$$\beta = \frac{K_{MN2}}{R_A} \cdot \frac{1}{T_o} \tag{3.28}$$

$$K_{cte} = \frac{V_{GS2}(T_o)}{R_A} - \frac{K_{MN2}}{R_A}$$

(3.29)

#### 3.3.2. Etapa de salida multitensión para cargas elevadas

En la segunda parte del circuito se busca obtener una tensión de salida compensada en temperatura, a la vez de proteger al circuito de posibles cambios de carga a su salida (ver Fig. 3.10). Para lograr esto, se crea una etapa que introduzca un lazo de realimentación (ver Fig. 3.3).

Cabe destacar que, según el estudio de tendencias mostrado en la ecuación 3.30, abriendo el lado por el punto Vx, se puede demostrar que la realimentación es negativa.

Figura 3.3: Lazo de realimentación de la etapa de salida del bandgap.

$$V_x \uparrow \Rightarrow V_{GSP2} \downarrow \Rightarrow i_{dP2} \downarrow \Rightarrow I_{Ro} \downarrow \Rightarrow i_{dN2a} \uparrow \Rightarrow Vx' \downarrow$$

(3.30)

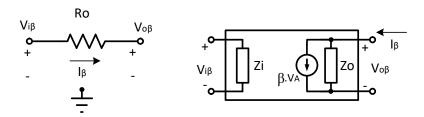

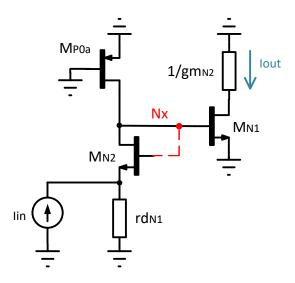

Llevando a cabo el estudio del tipo de realimentación del lazo, se puede identificar como red  $\beta$  a la resistencia de salida  $R_o$ . De esta manera, el tipo de realimentación sería de sensado de tensión y mezcla de corriente.

Teniendo en cuenta estas primeras consideraciones, se plantean los modelos equivalentes de la Figura 3.4 y el sistema de ecuaciones 3.31. De dicho sistema se deducen los valores de los elementos que conformarán la red  $\beta$  (ver ecs. 3.31, 3.33 y 3.34), despreciando el efecto de la realimentación inversa  $\beta_{rev}$ .

Figura 3.4: Circuito equivalente de la red  $\beta$  según el tipo de realimentación.

$$i_{o\beta} = \beta V_{i\beta} + Z_o^{-1} V_{o\beta}$$

$$i_{i\beta} = Z_i^{-1} V_{i\beta} + \beta_{rev} V_{o\beta}$$

(3.31)

$$\beta = \frac{i_{o\beta}}{V_{i\beta}} \Big|_{V_{o\beta} = 0} = \frac{-1}{R_o} \tag{3.32}$$

$$Z_o^{-1} = \frac{i_{o\beta}}{V_{o\beta}} \Big|_{V_{i\beta} = 0} = \frac{1}{R_o}$$

(3.33)

$$Z_i^{-1} = \frac{i_{i\beta}}{V_{i\beta}} \Big|_{\beta_{rev} = 0} = \frac{1}{R_o}$$

(3.34)

El objetivo de este procedimiento es llegar a desarrollar la expresión de la ganancia completa del sistema (ver ec. 3.35), siendo la  $A\beta$  la ganancia de lazo formada por la realimentación y la  $A^*$  la ganancia del amplificador cargado con la red  $\beta$  pero sin realimentación.

$$A = \frac{A^*}{1 + A\beta} \tag{3.35}$$

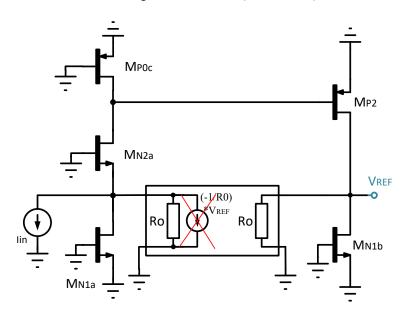

A continuación, se plantea el nuevo circuito insertando la red  $\beta$  diseñada (ver Fig. 3.5). Con este nuevo modelo, se estudia la ganancia de lazo (ver ec. 3.38).

Figura 3.5: Circuito de la segunda etapa del bandgap con la red  $\beta$  diseñada.

$$V_{REF} = \beta \ V'_{REF} \ rd_{P0C} \ gm_{P2} \ R_o = V'_{REF} \ rd_{P0C} \ gm_{P2}$$

(3.36)

$$Z_o = rd_{MP2} // rd_{MN1b} // R_o \approx R_o \tag{3.37}$$

$$A\beta = \frac{V_{REF}}{V'_{REF}} = rd_{P0C} \ gm_{P2} \tag{3.38}$$

Por otro lado, se plantea el circuito, esta vez sin los efectos de la red  $\beta$ , es decir, anulando el parámetro  $\beta$  (ver Fig. 3.5 con la cruz roja).

Con este circuito, se deduce la expresión de la ganancia del amplificador cargado (ver ec. 3.39).

$$A^* = \frac{V_o}{I_i} = rd_{P0C} \ gm_{P2} \ R_o \tag{3.39}$$

Sustituyendo en la ecuación 3.35 los términos obtenidos en los cálculos anteriores, se obtiene la expresión final mostrada en la ecuación 3.40.

$$A = \frac{rd_{P0C} \ gm_{P2} \ R_o}{1 + rd_{P0C} \ gm_{P2}} \approx R_o \tag{3.40}$$

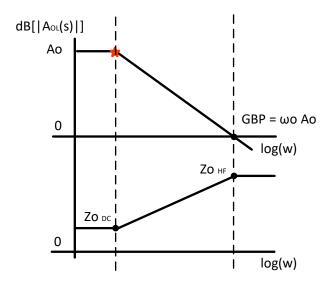

Es interesante estudiar el comportamiento de la impedancia de salida al cerrar el lazo, ya que con ello se puede comprobar que esta etapa que se está analizando trabaja como una protección ante cambios de carga (como si fuera una especie de *buffer*). Siendo la impedancia de salida en lazo abierto la  $R_o$ , se puede obtener la impedancia de salida en lazo cerrado en continua (ver ec. 3.41) y en alta frecuencia (ver ec. 3.42). La variación de la impedancia de salida con la frecuencia se puede observar en la Figura 3.6, donde se demuestra que la impedancia de salida mejora con el efecto de la realimentación.

$$Z_{o_{DC}} = \frac{Z_{o_{OL}}}{1 + A_o} = \frac{R_o}{1 + rd_{P0C}gm_{P2}}$$

(3.41)

$$Z_{o_{HF}} = Z_{o_{OL}} \tag{3.42}$$

Figura 3.6: Respuesta en frecuencia de la impedancia de salida.

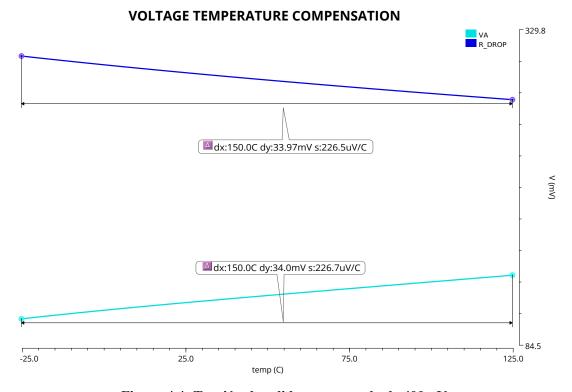

Una vez entendido cómo funciona el lazo de realimentación, se pueden deducir los comportamientos y ecuaciones de las tensiones y corrientes que van a verse implicadas en el proceso de compensación. En primer lugar, se copia la corriente  $I_{ZTAT}$  a través del espejo de corriente formado por los transistores MN1 y MN1a (de las mismas dimensiones). Por otra parte, se copia la corriente  $I_{PTAT}$  de la primera etapa del *bandgap* por los transistores MP0C y MP1C, de manera que por el transistor MN2a se consiga hacer pasar una corriente positiva en temperatura. Por último, la tensión  $V_A$ , la cual es positiva en temperatura, se consigue con la diferencia de tensión formada por la  $V_{GSN1}$  y la  $V_{GSN2a}$  (ver ec. 3.43), de manera similar con la que se conseguía la corriente  $I_{PTAT}$  en la resistencia  $R_B$ .

$$V_A = V_{GSN1}(T_o) + K_{N1}(\frac{T}{T_o} - 1) - V_{GSN2a}(T_o) - K_{N2}(\frac{T}{T_o} - 1)$$

(3.43)

Teniendo en cuenta que en el punto  $V_A$  se mezclan una corriente  $I_{PTAT}$  con la  $I_{ZTAT}$  conseguida en el núcleo, se puede deducir que la corriente que pasa por la resistencia  $R_o$  será de carácter NTAT, para poder conseguir la corriente de TEMPCO nulo al sumar la  $I_{PTAT}$  y dicha corriente de salida (ver ec. 3.44).

$$I_o = I_{ZTAT} - \frac{S_{P0C}}{S_{P0B}} \cdot I_{PTAT} \tag{3.44}$$

Teniendo en cuenta que la  $I_{PTAT}$  anterior es la mostrada en la ecuación 3.22, se desarrolla la corriente  $I_o$  de salida de la siguiente manera, observando que es una  $I_{NTAT}$ :

$$I_o = I_{ZTAT} - \frac{S_{P0C}}{S_{P0B}} \cdot U_T \, n \ln \left( \frac{S_{P0A}}{S_{P0B}} \cdot \frac{S_{MN3}}{S_{MN2}} \right) \cdot \frac{1}{R_B}$$

(3.45)

Con el análisis de las ecuaciones anteriores (ecs. 3.43 y 3.44), se puede desarrollar la expresión de la tensión de salida compensada en temperatura (ver ec. 3.46). Siguiendo la misma solución del planteamiento de unos coeficientes que ayuden a compensar el primer orden, se obtiene la ecuación 3.47, la cual, a su vez, se puede dividir en un término constante en temperatura (ver ec. 3.49), el coeficiente  $\alpha$  (ver ec. 3.50) y el coeficiente  $\beta$  (ver ec. 3.51).

$$V_{REF} = V_A + I_o R \tag{3.46}$$

$$V_{REF} = V_{GSN1}(T_o) - V_{GSN2a}(T_o) + (K_{N1} - K_{N2})(\frac{T}{T_o} - 1) + RI_{ZTAT} - R\frac{S_{P0C}}{S_{P0R}} \cdot U_T \, n \ln\left(\frac{S_{P0A}}{S_{P0R}} \cdot \frac{S_{MN3}}{S_{MN2}}\right) \cdot \frac{1}{R_B}$$

(3.47)

$$V_{REF} = K_{CTE} - \alpha T + \beta T \tag{3.48}$$

$$K_{CTE} = V_{GSN1}(T_o) - V_{GSN2a}(T_o) + RI_{ZTAT} - (K_{N1} - K_{N2})$$

(3.49)

$$\alpha = R \frac{S_{P0C}}{S_{P0B}} \cdot \frac{k}{q} n \ln \left( \frac{S_{P0A}}{S_{P0B}} \cdot \frac{S_{MN3}}{S_{MN2}} \right) \cdot \frac{1}{R_B}$$

(3.50)

$$\beta = \frac{K_{N1} - K_{N2}}{T_0} \tag{3.51}$$

#### 3.3.3. Circuito de Start-Up

Un circuito de *Start-Up* es un circuito externo que se utiliza para hacer que otro comience a funcionar y consiga llegar al valor de salida nominal de interés.

En el caso de que el *bandgap* diseñado en este trabajo se encuentre en un estado de apagado, el circuito no podrá comenzar a funcionar por su cuenta, ya que no hay manera de que en los espejos formados por MP0a, MP1a, MP0b, MP1b, MP0c y MP1c se genere una corriente que haga funcionar al resto del circuito.

Para ello, se utiliza el circuito de *Start-Up* de la Figura 3.7. Dicha estructura le proporciona a la primera etapa del sistema un camino por el que pase una corriente y poder cargar los nodos a una determinada tensión. Al conectar la alimentación, la tensión de entrada del inversor formado por los transistores MPS2 y MNS2 es nula o muy baja, por lo que su salida será alta, permitiendo al MNS3 funcionar. Este transistor conecta el núcleo del espejo formado por los transistores en modo diodo MP0b y MP1b con el nodo Nx, de manera que asegure dicho camino de corriente. Los transistores MP0b y MP1b comienzan a funcionar en el momento en el que se conecte la alimentación (ya que están configurados en modo diodo) y hacen pasar una corriente por el transistor MNS3 hacia el nodo Nx. Al inyectar corriente en el nodo, se carga su capacidad parásita haciendo que la tensión del nodo aumente linealmente. Por otro lado, el transistor MPS1 del *Start-Up* funciona como espejo del núcleo MP0b y MP1b, haciendo pasar una corriente hasta MNS1, el cual convierte dicha corriente en la tensión de entrada del inversor. Por ello, cuando el inversor alcance

una tensión que supere el umbral de funcionamiento, proporcionará una salida baja que hará que el transistor MNS3 se apague, cortando la conexión con el circuito principal.

Figura 3.7: Circuito de Start-Up y conexiones con el bandgap.

#### 3.3.4. Análisis de ruido

El estudio del ruido del circuito se ha llevado a cabo en cada etapa del *bandgap* por separado, con el fin de abordar el problema con mayor facilidad.

En primer lugar, se ha analizado el ruido de la etapa de salida. La contribución de ruido a la salida del sistema será la suma de las contribuciones de cada etapa del circuito (ver ec. 3.52).

$$\overline{v_{no_{etapa2}}^2} = \overline{v_{nN1ao}^2} + \overline{v_{nP0co}^2} + \overline{v_{nP2o}^2} + \overline{v_{nN1bo}^2}$$

(3.52)

$$\overline{v_{nN1ao}^2} = \overline{v_{nN1a}^2} \cdot g m_{nN1a}^2 \cdot r d_{P0c}^2 \cdot g m_{P2}^2 \cdot R_o^2$$

(3.53)

$$\overline{v_{nP0co}^2} = \overline{v_{P0c}^2} \cdot g m_{P0c}^2 \cdot r d_{P0c}^2 \cdot g m_{P2}^2 \cdot R_o^2$$

(3.54)

$$\overline{v_{nP2o}^2} = \overline{v_{nP2}^2} \cdot g m_{P2}^2 \cdot R_o^2 \tag{3.55}$$

$$\overline{v_{nN1bo}^2} = \overline{v_{nN1b}^2} \cdot g m_{N1b}^2 \cdot R_o^2 \tag{3.56}$$

Para obtener el ruido equivalente en corriente en la entrada de la etapa de salida (ver ec. 3.57) estudiada, basta con dividir el ruido equivalente a la salida por la ganancia del amplificador cargado

de dicha etapa (ver ec. 3.39). Por último, se puede conseguir llegar a la expresión de la contribución de ruido de la segunda etapa a la salida del circuito del *bandgap* completo multiplicando la contribución en corriente a la entrada de la etapa por la ganancia total de dicha etapa (ver ec. 3.40).