## UNIVERSITAT POLITÈCNICA DE VALÈNCIA

## Dpto. de Ingeniería Electrónica

Desarrollo de un interfaz electrónico de señalización digital para el control rápido de cavidades aceleradoras de RF

Trabajo Fin de Máster

Máster Universitario en Ingeniería de Sistemas Electrónicos

AUTOR/A: Fernández Ortega, Juan Carlos

Tutor/a: Torres Carot, Vicente

Cotutor/a externo: Boronat Arévalo, Marçà

CURSO ACADÉMICO: 2023/2024

## DESARROLLO DE UN INTERFAZ ELECTRÓNICO DE SEÑALIZACIÓN DIGITAL PARA EL CONTROL RÁPIDO DE CAVIDADES ACELERADORAS DE RF

Autor: Juan Carlos Fernández Ortega

**Tutor: Dr. Vicente Torres Carot**

Tutor: Dr. Marçà Boronat Arevalo

Trabajo Fin de Máster presentado en el Departamento de Ingeniería Electrónica de la Universitat Politècnica de València para la obtención del Título de Máster Universitario en Ingeniería de Sistemas Electrónicos

Curso 2023-24

Valencia, Julio de 2024

#### Resumen

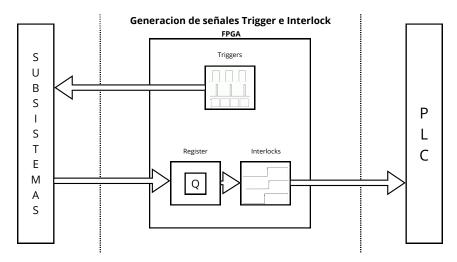

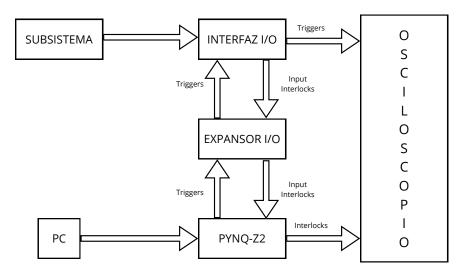

El presente trabajo de final de máster trata acerca de la implementación de un sistema de sincronización a través de señales de disparos (trigger) y señales de interbloqueos (interlock) basado en un SoC para la seguridad de una zona controlada. Esta zona puede variar, pero en este caso es una zona de radiación.

Los principales objetivos de este proyecto son programar un SoC diseñando varios core IP que generará las señales triggers y las señales interlock cuyos parámetros son variables y controlables.

Además, se estudia una pcb de entradas y salidas ya diseñada anteriormente. En concreto se realiza un estudio de disipación térmica y fiabilidad, y un estudio del ensamblaje donde irá conectado. Con este sistema se puede comprobar las señales de triggers e interlocks en un osciloscopio.

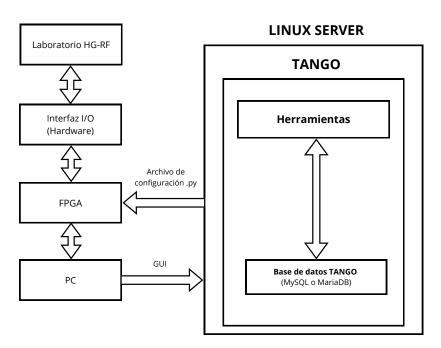

De forma definitiva, se configurará un sistema de control distribuido TANGO de código libre que controlará todas las señales del core IP ya que la duración, prioridad... de los pulsos puede variar, y con este sistema TANGO se podrá ir cambiando los parámetros sin tener que modificar el core ip. Finalmente se implementará una interfaz gráfica para que el usuario pueda realizar estos cambios directamente desde un PC de laboratorio.

El proyecto tiene como tarea principal el diseño de varios core IP para el funcionamiento sobre una FPGA, pero como se ha comentado se realizarán otras tareas de vital importancia como es el caso del estudio térmico de la PCB y el sistema de control distribuido que tiene una complejidad elevada y puede conllevar a una curva de aprendizaje larga.

Todo esto, formará parte de un sistema de seguridad de un laboratorio de radiación donde es imprescindible que el sistema responda de forma fiable y segura, pues de ello depende la seguridad del personal y la maquinaria. Se implementará en el laboratorio de RF del IFIC donde se estudian cavidades en aceleradores de partículas con la finalidad de mejorar la eficiencia en la radioterapia para el tratamiento contra el cáncer.

#### Resum

El present treball de final de màster tracta sobre la implementació d'un sistema de sincronització a través de senyals de dispar (trigger) i senyals d'interbloqueig (interlock) basat en un SoC per a la seguretat d'una zona controlada. Aquesta zona pot variar, però en aquest cas és una zona de radiació.

Els principals objectius d'aquest projecte són programar un SoC dissenyant diversos core IP que generaran les senyals triggers i les senyals interlock, els paràmetres dels quals són variables i controlables.

A més, s'estudia una PCB d'entrades i sortides ja dissenyada anteriorment. En concret es realitza un estudi de dissipació tèrmica i fiabilitat, i un estudi de l'assemblatge on anirà connectada. Amb aquest sistema es pot comprovar les senyals de triggers i interlocks en un oscil·loscopi.

De manera definitiva, es configurarà un sistema de control distribuït TANGO de codi lliure que controlarà totes les senyals del core IP ja que la durada, prioritat... dels polsos pot variar, i amb aquest sistema TANGO es podrà anar canviant els paràmetres sense haver de modificar el core IP. Finalment s'implementarà una interficie gràfica perquè l'usuari pugui realitzar aquests canvis

directament des d'un PC de laboratori.

El projecte té com a tasca principal el disseny de diversos core IP per al funcionament sobre una FPGA, però com s'ha comentat es realitzaran altres tasques de vital importància com és el cas de l'estudi tèrmic de la PCB i el sistema de control distribuït que té una complexitat elevada i pot portar a una corba d'aprenentatge llarga.

Tot això, formarà part d'un sistema de seguretat d'un laboratori de radiació on és imprescindible que el sistema respongui de forma fiable i segura, ja que d'això depèn la seguretat del personal i la maquinària. Es implementarà al laboratori de RF de l'IFIC on s'estudien cavitats en acceleradors de partícules amb la finalitat de millorar l'eficiència en la radioteràpia per al tractament contra el càncer.

#### **Abstract**

The present Master's thesis focuses on the implementation of a synchronization system using trigger and interlock signals based on a SoC for the safety of a controlled area. This area may vary, but in this case, it is a radiation zone.

The main objectives of this project are to program a SoC by designing various IP cores that will generate the trigger and interlock signals, whose parameters are variable and controllable.

Additionally, an already designed input and output PCB is studied. Specifically, a thermal dissipation and reliability study is conducted, as well as an assembly study of where it will be connected. With this system, the trigger and interlock signals can be checked on an oscilloscope.

Ultimately, a TANGO distributed control system, an open-source code, will be configured to control all the signals of the IP cores since the duration, priority, etc. of the pulses may vary. With this TANGO system, parameters can be changed without modifying the IP core. Finally, a graphical interface will be implemented so that the user can make these changes directly from a laboratory PC.

The main task of the project is the design of various IP cores for operation on an FPGA. However, as mentioned, other tasks of vital importance will be carried out, such as the thermal study of the PCB and the distributed control system, which has high complexity and may involve a long learning curve.

All of this will be part of a security system for a radiation laboratory where it is essential that the system responds reliably and safely, as the safety of personnel and machinery depends on it. It will be implemented in the RF laboratory of the IFIC where cavities in particle accelerators are studied with the aim of improving efficiency in cancer radiotherapy treatment.

Muestro mi agradecimiento de haber podido realizado la tesis gracias a esas personas que me han acompañado a lo largo de estos meses.

A Vicente Torres por los consejos y correcciones de cada capítulo. Aunque el trabajo ha sido realizado fuera de la UPV me ha ayudado mucho y se lo agradezco.

A Marçà Boronat por la ayuda diaria sobre el conocimiento del laboratorio de RF y la ayuda en la escritura del trabajo.

Al IFIMED ya que han aportado su granito de arena a este trabajo con recomendaciones y ayuda en algunas partes del trabajo.

A mi pareja por apoyarme cada día y buscar la positividad en todo momento.

A mis padres por confiar en mí y levantarme en los malos momentos, y sobre todo alegrarse por mí en los buenos.

# Índice general

| I  | Introducción                                                                                                                                                                                                                                    |                                                    |  |  |  |  |  |  |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| 1. | Objetivos                                                                                                                                                                                                                                       |                                                    |  |  |  |  |  |  |  |  |  |  |

| 2. | Antecedentes Estructura del proyecto                                                                                                                                                                                                            |                                                    |  |  |  |  |  |  |  |  |  |  |

| 3. |                                                                                                                                                                                                                                                 |                                                    |  |  |  |  |  |  |  |  |  |  |

| 4. | Dificultades y retos                                                                                                                                                                                                                            | 1                                                  |  |  |  |  |  |  |  |  |  |  |

| II | Sistema. Hardware y software                                                                                                                                                                                                                    |                                                    |  |  |  |  |  |  |  |  |  |  |

| 1. | Selección hardware                                                                                                                                                                                                                              | 15                                                 |  |  |  |  |  |  |  |  |  |  |

|    | 1.1. Servidor linux 1.2. Interfaz I/O  1.2.1. Diseño y descripción PCB  1.2.2. Ensamblado PCB  1.2.3. Disipación térmica  1.2.4. Medidas térmicas  1.2.5. Cálculo teórico a nivel de PCB  1.2.6. Posibles mejoras y soluciones  1.3. FPGA y SoC | 1:<br>10<br>17<br>18<br>19<br>20<br>22<br>20<br>27 |  |  |  |  |  |  |  |  |  |  |

| 2. | Selección software  2.1. Vivado                                                                                                                                                                                                                 | 3:<br>3:<br>3:<br>3:<br>3:<br>3:<br>3:             |  |  |  |  |  |  |  |  |  |  |

| 3. | Pruebas experimentales de la PCB                                                                                                                                                                                                                | 4                                                  |  |  |  |  |  |  |  |  |  |  |

|    | 3.1. Generador de funciones y fuente de alimentación                                                                                                                                                                                            | 4                                                  |  |  |  |  |  |  |  |  |  |  |

|    | 3.2. Pruebas en FPGA y SoC                                                                                                                                                                                                                      | 4.<br>4.                                           |  |  |  |  |  |  |  |  |  |  |

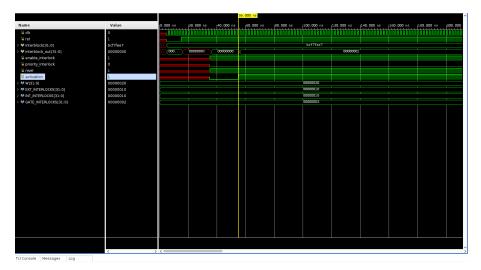

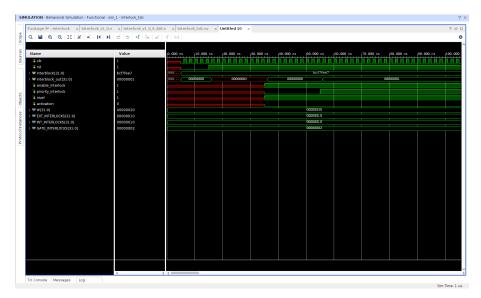

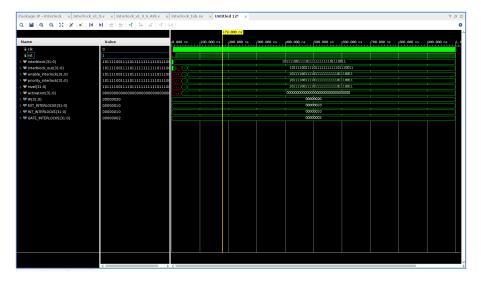

|    | 3.2.2. Simulaciones                                                                                                                                                                                                                             | 4.                                                 |  |  |  |  |  |  |  |  |  |  |

|    | 3.3.                | Conclusiones de las pruebas         | 47       |

|----|---------------------|-------------------------------------|----------|

| 4. | Ensa                | amblaje del sistema                 | 49       |

| Ш  | Do                  | esarrollo y resultados              |          |

| 1. | Cres                | ación del proyecto                  | 55       |

| •• |                     | Descripción general de las señales  | 55       |

|    |                     | 1.1.1. Señal de interbloqueo        | 55       |

|    |                     | 1.1.2. Señal de disparo             | 57       |

|    |                     | 1.1.3. Registro                     | 59       |

|    | 1.2.                | Verificación de bloques             | 60       |

|    |                     | 1.2.1. Señal de interbloqueo        | 60       |

|    |                     | 1.2.2. Señal de disparo             | 62       |

|    | 1.3.                |                                     | 63       |

|    | 1.4.                | $\varepsilon$                       | 64       |

| _  | <b>.</b> .          |                                     |          |

| 2. |                     | gración bus AXI y Sistema Operativo | 69       |

|    | 2.1.                | $\epsilon$                          | 69<br>72 |

|    | 2.2.                | Sistema Operativo Embebido          | 72       |

|    | 2.3.                | Demostración final                  | 72       |

| 3. | Tang                | go-Controls                         | 75       |

|    | •                   |                                     |          |

|    | 3.1.                |                                     | 75       |

|    |                     | Pogo                                | 75<br>78 |

|    |                     | Pogo                                | 78       |

|    | 3.2.                | Pogo                                |          |

| IV | 3.2.<br>3.3.        | Pogo                                | 78       |

|    | 3.2.<br>3.3.        | Pogo                                | 78       |

| 1. | 3.2.<br>3.3.<br>Con | Pogo                                | 78<br>79 |

## Índice de figuras

| I  | Intr                                                                 | oducción                                                                                                                                                                        |                                              |

|----|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|    | 1.1.<br>1.2.<br>1.3.                                                 | Laboratorio HG-RF del IFIC-UV. Fuente: propia                                                                                                                                   | 1<br>2<br>3                                  |

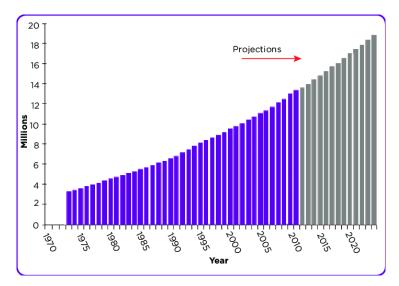

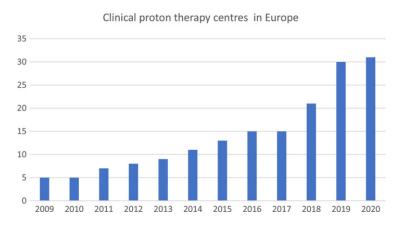

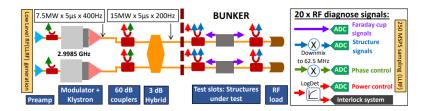

|    | <ul><li>2.1.</li><li>2.2.</li></ul>                                  | Número estimado de supervivientes de cáncer en los Estados Unidos. Información del Instituto Nacional del Cáncer. Fuente: [2]                                                   | 5                                            |

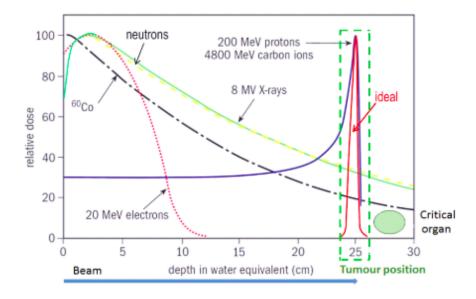

|    | 2.3.<br>2.4.                                                         | Fuente: [5]                                                                                                                                                                     | 6<br>7<br>7                                  |

|    | 3.1.                                                                 | Diagrama de Gantt al principio del proyecto. Fuente: propia                                                                                                                     | 10                                           |

| II | Sist                                                                 | tema. Hardware y software                                                                                                                                                       |                                              |

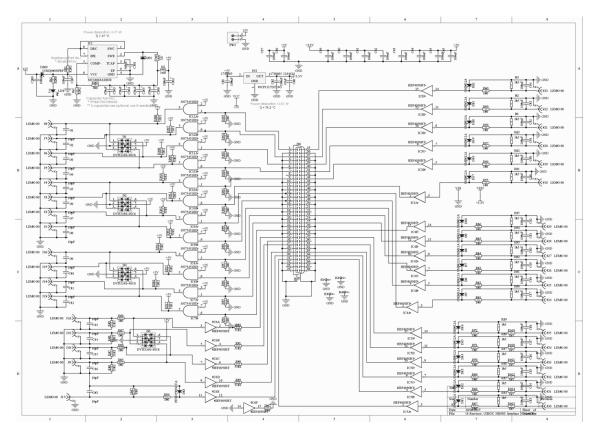

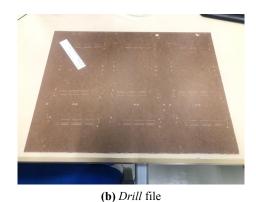

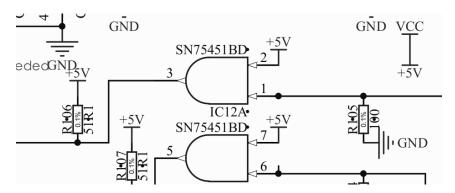

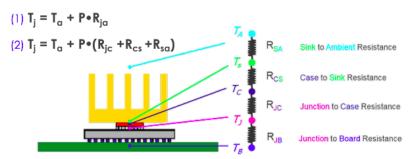

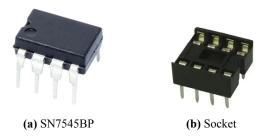

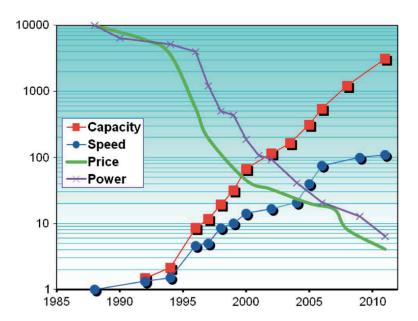

|    | 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9. | Capacity son el número de celdas lógicas. Speed es el rendimiento. Price por celda lógica. Power por celda lógica. Price y power son escalados en un factor 10000. Fuente: [15] | 16<br>18<br>19<br>20<br>21<br>21<br>23<br>25 |

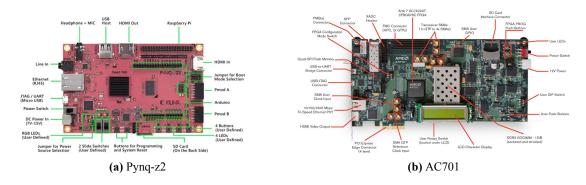

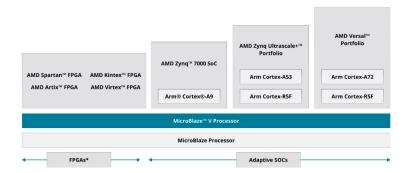

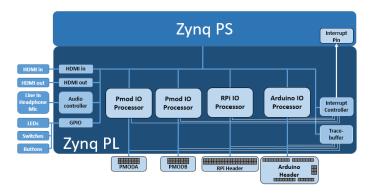

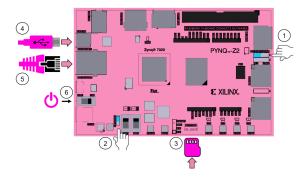

|    | 1.11.                                                                | FPGAs utilizadas en este trabajo fin de máster. Fuente: Xilinx Esquema SoC-FPGA. Fuente:                                                                                        | 28<br>29<br>29                               |

|    | 2.1.<br>2.2.<br>2.3.                                                 | Setup de pynq-z2 para iniciar por la SD. Fuente: tango-controls                                                                                                                 | 32<br>34                                     |

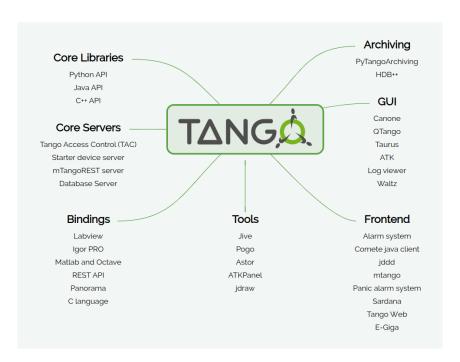

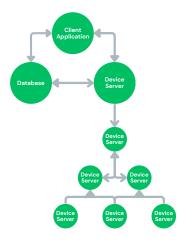

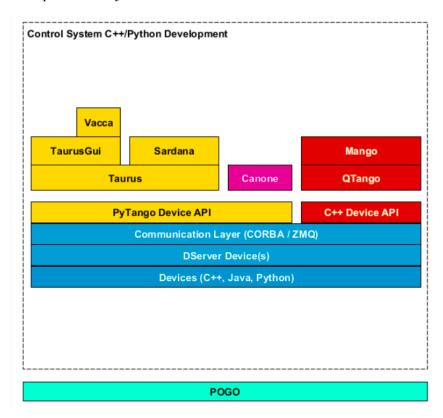

|    | 2.4.                                                                 | tango-controls                                                                                                                                                                  | 35<br>35                                     |

| 2.5.                                                                                                              | Herramientas de tango-controls. Fuente: [18]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36                                                                         |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

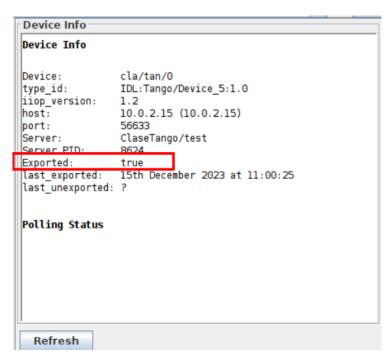

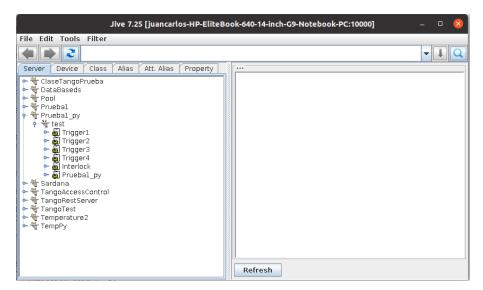

| 2.6.                                                                                                              | Prueba de puesta en marcha de <i>Device</i> en jive. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38                                                                         |

| 2.7.                                                                                                              | Sensor de temperatura Seeed Studio Grove-Temperature Sensor - 101020015. Fuen-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

|                                                                                                                   | te: rs-online                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                                                                         |

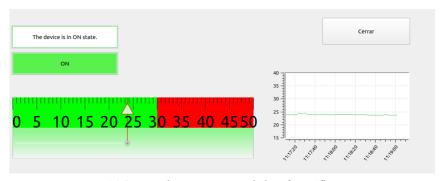

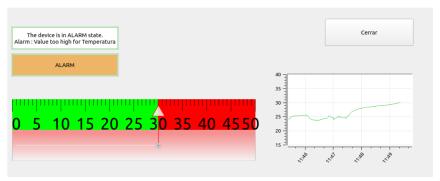

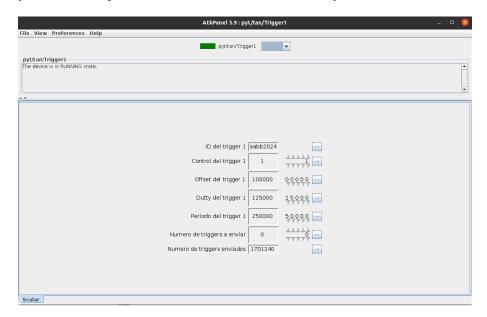

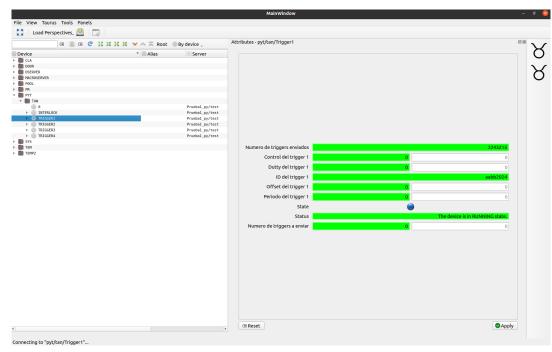

| 2.8.                                                                                                              | Interfaz gráfica realizada por Qt-Designer. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39                                                                         |

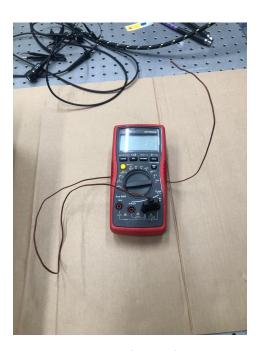

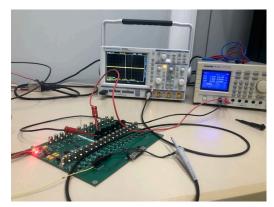

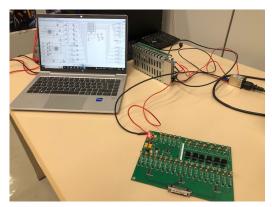

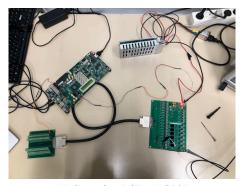

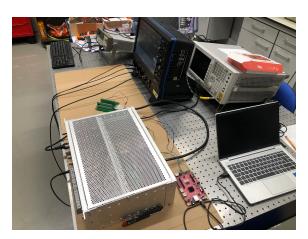

| 3.1.                                                                                                              | Instrumentación electrónica utilizada en el laboratorio para las pruebas. Fuente:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|                                                                                                                   | propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42                                                                         |

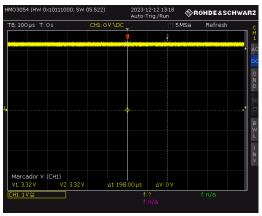

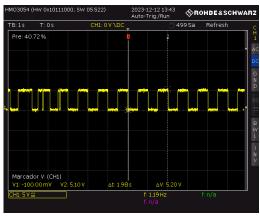

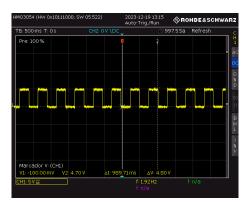

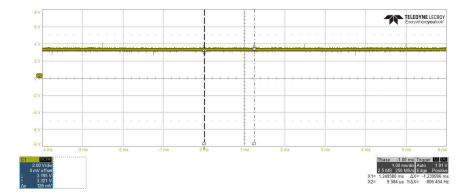

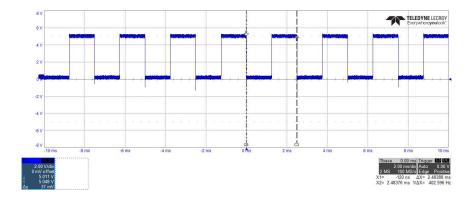

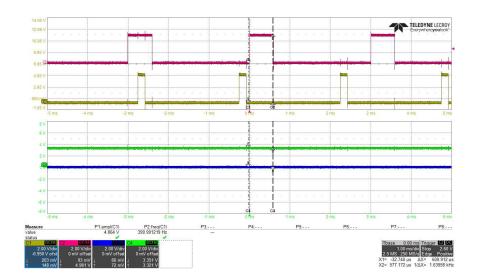

| 3.2.                                                                                                              | Medida en osciloscopio del sistema. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42                                                                         |

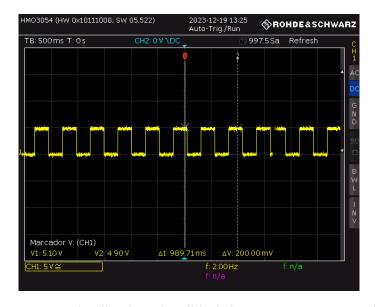

| 3.3.                                                                                                              | Pruebas realizadas en los distintos drivers de la PCB. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43                                                                         |

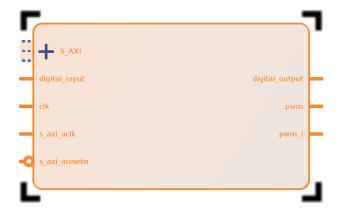

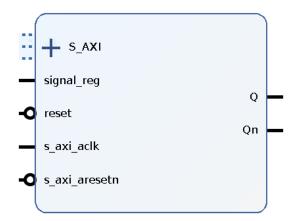

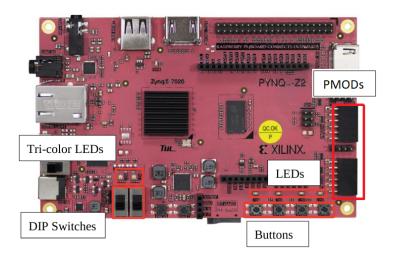

| 3.4.                                                                                                              | Bloque PWM en <i>IP Integrator</i> . Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44                                                                         |

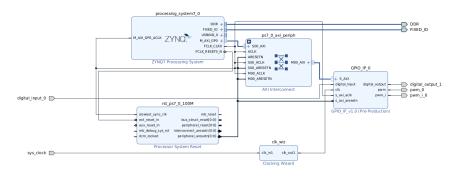

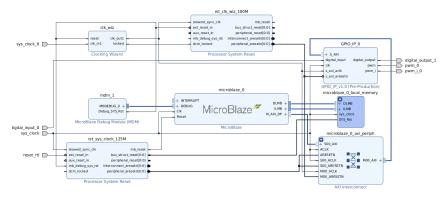

| 3.5.                                                                                                              | Diseños de bloques en Vivado. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45                                                                         |

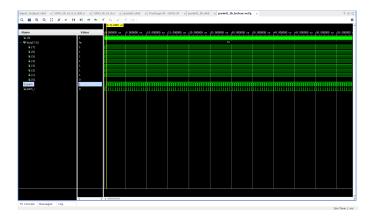

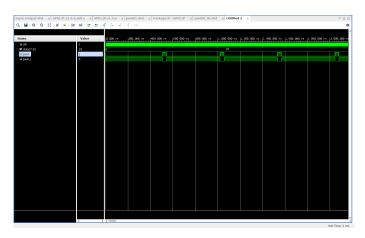

| 3.6.                                                                                                              | Bloque PWM en <i>IP Integrator</i> . Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                         |

| 3.7.                                                                                                              | Bloque PWM en <i>IP Integrator</i> . Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                         |

| 3.8.                                                                                                              | Setup de instrumentación electrónica en el laboratorio para las pruebas. Fuente:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70                                                                         |

| 3.0.                                                                                                              | propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 47                                                                         |

| 2.0                                                                                                               | Visualización a la salida de la pynq-z2. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47                                                                         |

| 3.9.                                                                                                              | visualización a la sanda de la pynq-zz. Fuente, propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4/                                                                         |

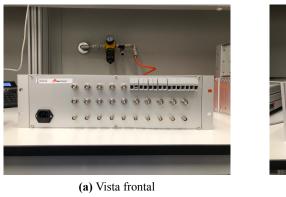

| 4.1.                                                                                                              | Armario rack. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                         |

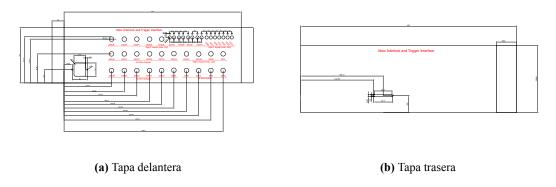

| 4.2.                                                                                                              | Chasis 3U. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50                                                                         |

| 4.3.                                                                                                              | Modificaciones AutoCAD del chasis. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                         |

| 4.4.                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                                                         |

| 4.5.                                                                                                              | Vistas del chasis montado. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51                                                                         |

|                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

|                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| TIT D                                                                                                             | 77 7. 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| III De                                                                                                            | sarrollo y resultados                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

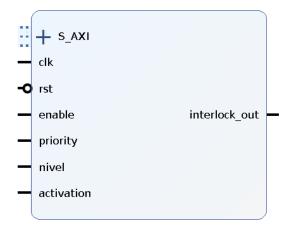

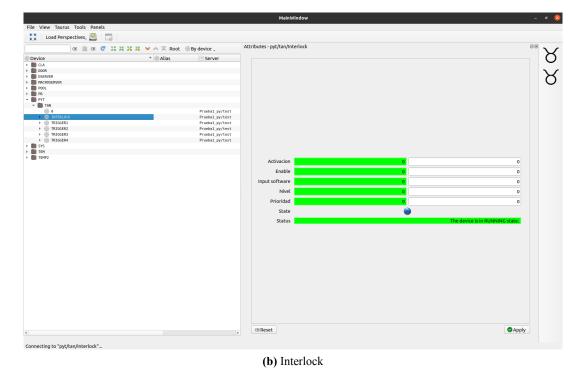

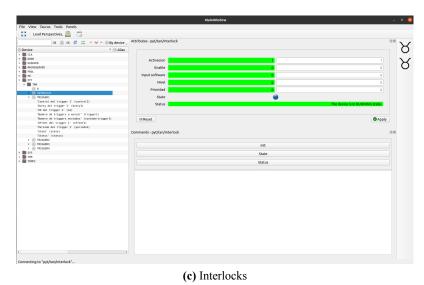

| 1.1.                                                                                                              | Sarrollo y resultados  Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57                                                                         |

|                                                                                                                   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

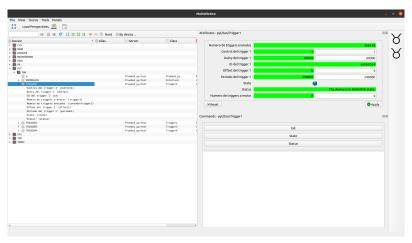

| 1.1.                                                                                                              | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57<br>58<br>59                                                             |

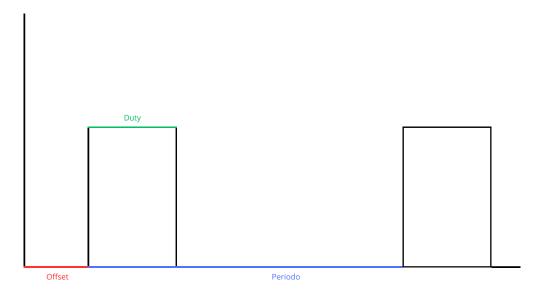

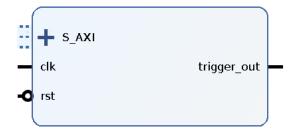

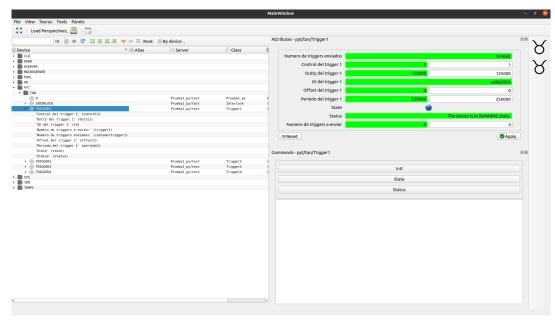

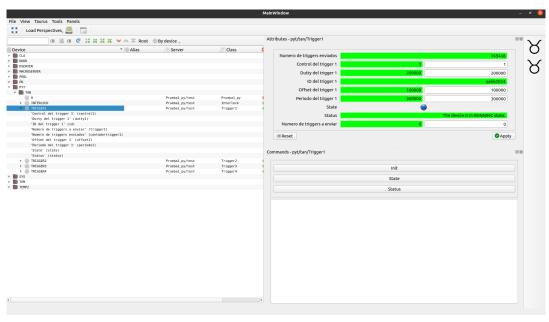

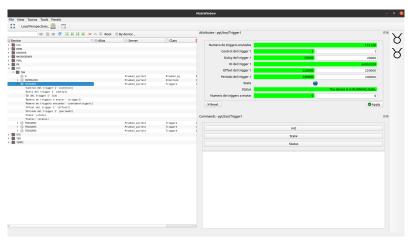

| 1.1.<br>1.2.                                                                                                      | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58                                                                         |

| 1.1.<br>1.2.<br>1.3.                                                                                              | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>59<br>60                                                             |

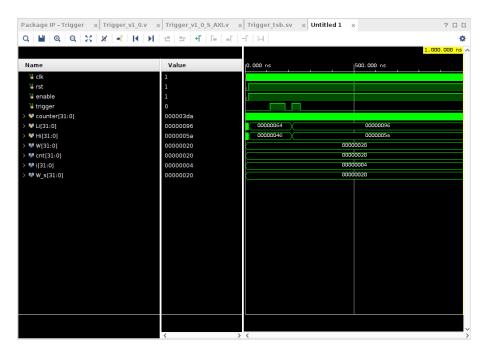

| 1.1.<br>1.2.<br>1.3.<br>1.4.                                                                                      | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>59<br>60<br>60                                                       |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.                                                                              | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>59<br>60<br>60<br>61                                                 |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.                                                              | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>59<br>60<br>60<br>61<br>61                                           |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.                                                              | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>59<br>60<br>60<br>61<br>61<br>62                                     |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.                                                      | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>59<br>60<br>60<br>61<br>61<br>62<br>62                               |

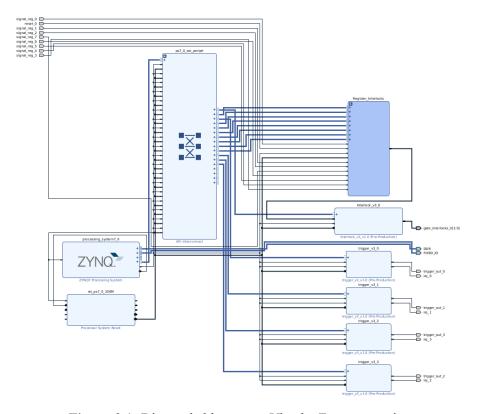

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.                                              | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>59<br>60<br>61<br>61<br>62<br>62<br>63                               |

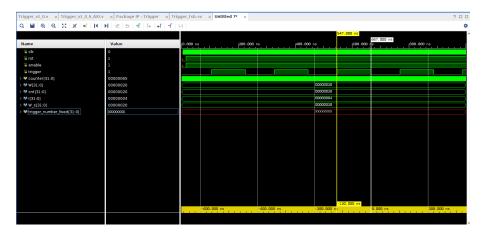

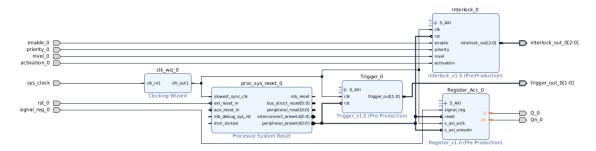

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.                                     | Interfaz gráfica de usuario del core Interlock. Fuente: propia  Funcionamiento básico de la señal de disparo. Fuente: propia  Interfaz gráfica de usuario del core Trigger. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Primer caso para la verificación de la señal de interbloqueo. Fuente: propia  Segundo caso para la verificación de la señal de interbloqueo. Fuente: propia  Tercer caso para la verificación de la señal de interbloqueo. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Leds, botones, interruptores y PMODs. Fuente: [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58<br>59<br>60<br>60<br>61<br>61<br>62<br>62<br>63<br>64                   |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.<br>1.11.                            | Interfaz gráfica de usuario del core Interlock. Fuente: propia  Funcionamiento básico de la señal de disparo. Fuente: propia  Interfaz gráfica de usuario del core Trigger. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Primer caso para la verificación de la señal de interbloqueo. Fuente: propia  Segundo caso para la verificación de la señal de interbloqueo. Fuente: propia  Tercer caso para la verificación de la señal de interbloqueo. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Block design. Fuente: propia  Leds, botones, interruptores y PMODs. Fuente: [19]  Esquema de la conexión realizada. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                       | 58<br>59<br>60<br>61<br>61<br>62<br>62<br>63<br>64<br>65                   |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.<br>1.11.<br>1.12.<br>1.13.          | Interfaz gráfica de usuario del core Interlock. Fuente: propia  Funcionamiento básico de la señal de disparo. Fuente: propia  Interfaz gráfica de usuario del core Trigger. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Primer caso para la verificación de la señal de interbloqueo. Fuente: propia  Segundo caso para la verificación de la señal de interbloqueo. Fuente: propia  Tercer caso para la verificación de la señal de interbloqueo. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Block design. Fuente: propia  Leds, botones, interruptores y PMODs. Fuente: [19]  Esquema de la conexión realizada. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                       | 58<br>59<br>60<br>61<br>61<br>62<br>62<br>63<br>64                         |

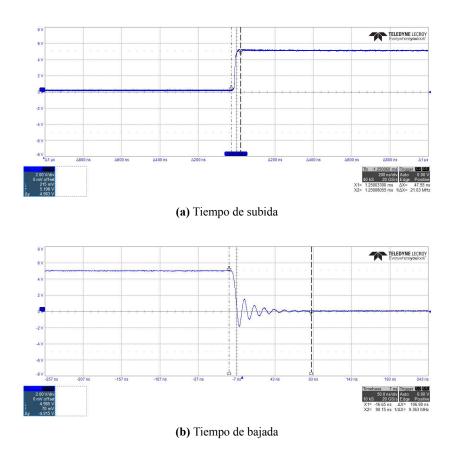

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.<br>1.11.<br>1.12.<br>1.13.          | Interfaz gráfica de usuario del core Interlock. Fuente: propia  Funcionamiento básico de la señal de disparo. Fuente: propia  Interfaz gráfica de usuario del core Trigger. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Primer caso para la verificación de la señal de interbloqueo. Fuente: propia  Segundo caso para la verificación de la señal de interbloqueo. Fuente: propia  Tercer caso para la verificación de la señal de interbloqueo. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Block design. Fuente: propia  Leds, botones, interruptores y PMODs. Fuente: [19]  Esquema de la conexión realizada. Fuente: propia  Sistema montado. Fuente: propia  Visualización en el osciloscopio de la entrada a la interfaz I/O (DIO18). Fuente:                                                                                                                                                                                                                                                   | 58<br>59<br>60<br>61<br>61<br>62<br>63<br>64<br>65<br>65                   |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.<br>1.11.<br>1.12.<br>1.13.          | Interfaz gráfica de usuario del core Interlock. Fuente: propia  Funcionamiento básico de la señal de disparo. Fuente: propia  Interfaz gráfica de usuario del core Trigger. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Primer caso para la verificación de la señal de interbloqueo. Fuente: propia  Segundo caso para la verificación de la señal de interbloqueo. Fuente: propia  Tercer caso para la verificación de la señal de interbloqueo. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Block design. Fuente: propia  Leds, botones, interruptores y PMODs. Fuente: [19]  Esquema de la conexión realizada. Fuente: propia  Sistema montado. Fuente: propia  Visualización en el osciloscopio de la entrada a la interfaz I/O (DIO18). Fuente: propia                                                                                                                                                                                                                                            | 58<br>59<br>60<br>61<br>61<br>62<br>63<br>64<br>65<br>65                   |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.<br>1.11.<br>1.12.<br>1.13.<br>1.14. | Interfaz gráfica de usuario del core Interlock. Fuente: propia  Funcionamiento básico de la señal de disparo. Fuente: propia  Interfaz gráfica de usuario del core Trigger. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Primer caso para la verificación de la señal de interbloqueo. Fuente: propia  Segundo caso para la verificación de la señal de interbloqueo. Fuente: propia  Tercer caso para la verificación de la señal de interbloqueo. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Block design. Fuente: propia  Leds, botones, interruptores y PMODs. Fuente: [19]  Esquema de la conexión realizada. Fuente: propia  Sistema montado. Fuente: propia  Visualización en el osciloscopio de la entrada a la interfaz I/O (DIO18). Fuente: propia                                                                                                                                                                                                                                            | 58<br>59<br>60<br>61<br>61<br>62<br>63<br>64<br>65<br>65<br>66             |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.<br>1.11.<br>1.12.<br>1.13.<br>1.14. | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>59<br>60<br>61<br>61<br>62<br>63<br>64<br>65<br>65<br>66             |

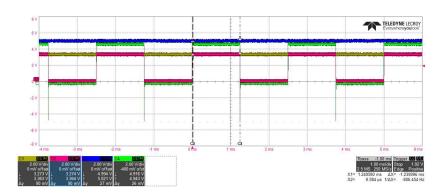

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.<br>1.11.<br>1.12.<br>1.13.<br>1.14. | Interfaz gráfica de usuario del core Interlock. Fuente: propia  Funcionamiento básico de la señal de disparo. Fuente: propia  Interfaz gráfica de usuario del core Trigger. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Primer caso para la verificación de la señal de interbloqueo. Fuente: propia  Segundo caso para la verificación de la señal de interbloqueo. Fuente: propia  Tercer caso para la verificación de la señal de interbloqueo. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Interfaz gráfica de usuario del core registro. Fuente: propia  Block design. Fuente: propia  Leds, botones, interruptores y PMODs. Fuente: [19]  Esquema de la conexión realizada. Fuente: propia  Sistema montado. Fuente: propia  Visualización en el osciloscopio de la entrada a la interfaz I/O (DIO21). Fuente: propia  Visualización en el osciloscopio de la salida a la interfaz I/O (DIO21). Fuente: propia  Visualización en el osciloscopio de varias entradas y salidas de la interfaz I/O. | 58<br>59<br>60<br>61<br>61<br>62<br>63<br>64<br>65<br>65<br>66<br>66<br>67 |

| 1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.<br>1.11.<br>1.12.<br>1.13.<br>1.14. | Interfaz gráfica de usuario del core Interlock. Fuente: propia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58<br>59<br>60<br>61<br>61<br>62<br>63<br>64<br>65<br>65<br>66             |

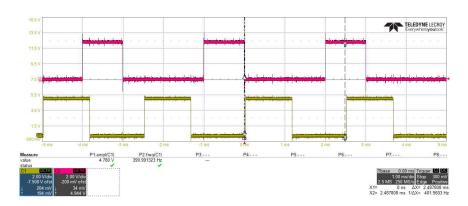

| 2.2. | Señal de disparo a 400 Hz (verde) y a 333.33 Hz (rojo). Fuente: propia          | 73 |

|------|---------------------------------------------------------------------------------|----|

| 2.3. | Señales de disparo a 450 Hz y 333.33 Hz, y señales de interbloqueo activadada y |    |

|      | a desactivada. Fuente: propia                                                   | 74 |

| 3.1. | Creación de la plantilla con POGO. Fuente: propia                               | 76 |

|      | Creación de servidor con Jive. Fuente: propia                                   | 78 |