# UNIVERSITAT POLITÈCNICA DE VALÈNCIA

# **School of Informatics**

Implementing high-performance interpreted languages through the use of FPGAs. A proof of concept.

End of Degree Project

Bachelor's Degree in Informatics Engineering

AUTHOR: González Castiñeiras, Daniel Tutor: Lucas Alba, Salvador Cotutor: Gutiérrez Gil, Raúl ACADEMIC YEAR: 2023/2024

# Abstract

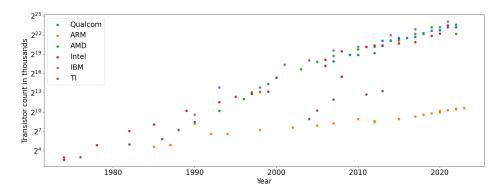

The exponential growth of hardware resources in recent decades has led to substantial software bloat, fostering the development of high-level programming languages that prioritize development efficiency over execution time and resource optimization. However, as the physical limits of transistor miniaturization are reached, this growth is slowing.

This presents a challenge for the software industry. As writing efficient, resourceconscious code is complex and time-consuming, while modern development paradigms focus on speeding up the process.

This thesis explores the use of reprogrammable hardware to bridge the gap between high-level abstractions and hardware. To this end, we developed LWVCG (Light-Weight Verilog Compiler Generator), a Python framework for specifying and generating hardware interpreters in Verilog. Using this framework, we implemented a hardware-based Just-In-Time (JIT) compiler for the SIMPLER language, a modification of SIMPL. Tested on two low-cost FPGAs (2x Lattice ICE40UP5K), this solution achieved 2x compilation speedup compared to the JavaScript V8 JIT compiler while operating at 1/250th of the clock frequency and consuming 1/16th of the power of an Intel i5-13400 CPU core.

**Key words:** Compilation, FPGA, Computing, CPU, Interpreted Programming Languages, Computational Efficiency, Energy Efficiency, Performance, Rust, Go, Javascript, Zig, Python, Verilog, Custom Hardware, Distributed Software Systems

# Resumen

El crecimiento exponencial de los recursos de hardware en las últimas décadas ha provocado un considerable hinchamiento del software, lo que ha fomentado el desarrollo de lenguajes de programación de alto nivel que priorizan la eficiencia del desarrollo sobre el tiempo de ejecución y la optimización de recursos. Sin embargo, a medida que se alcanzan los límites físicos de la miniaturización de los transistores, este crecimiento se ralentiza.

Esto supone un reto para la industria del software: escribir código eficiente y consciente de los recursos es complejo y requiere mucho tiempo, mientras que los paradigmas de desarrollo modernos se centran en acelerar el proceso.

Esta tesis explora el uso de hardware reprogramable para salvar la distancia entre las abstracciones de alto nivel y el hardware. Para ello, desarrollamos LWVCG (Light-Weight Verilog Compiler Generator), un marco de trabajo en Python para especificar y generar intérpretes de hardware en Verilog. Utilizando este marco, implementamos un compilador Just-In-Time (JIT) basado en hardware para el lenguaje SIMPLER, una modificación de SIMPL. Probada en dos FPGAs de bajo coste (2x Lattice ICE40UP5K), esta solución consiguió una velocidad de compilación 2 veces superior a la del compilador JIT JavaScript V8, a la vez que funcionaba a 1/250 de la frecuencia de reloj y consumía 1/16 de la potencia de un núcleo de CPU Intel i5-13400.

**Palabras clave:** Compilación, FPGA, Computación, CPU, Lenguajes de Programación Interpretados, Eficiencia computacional, Eficiencia Energética, Rendimiento, Rust, Go, Javascript, Zig, Python, Verilog, Custom Hardware, Sistemas

# Resum

El creixement exponencial dels recursos de maquinari en les darreres dècades ha provocat un inflament considerable del programari, cosa que ha fomentat el desenvolupament de llenguatges de programació d'alt nivell que prioritzen l'eficiència del desenvolupament sobre el temps d'execució i l'optimització de recursos. No obstant això, a mesura que s'assoleixen els límits físics de la miniaturització dels transistors, aquest creixement s'alenteix.

Això suposa un repte per a la indústria del programari: escriure codi eficient i conscient dels recursos és complex i requereix molt de temps, mentre que els paradigmes de desenvolupament moderns se centren a accelerar el procés.

Aquesta tesi explora lús de maquinari reprogramable per salvar la distància entre les abstraccions dalt nivell i el maquinari. Per això, desenvolupem LWVCG (Light-Weight Verilog Compiler Generator), un marc de treball a Python per especificar i generar intèrprets de maquinari a Verilog. Utilitzant aquest marc, implementem un compilador Just-In-Time (JIT) basat en maquinari per al llenguatge SIMPLER, una modificació de SIMPL. Provada en dues FPGAs de baix cost (2x Lattice ICE40UP5K), aquesta solució va aconseguir una velocitat de compilació 2 vegades superior a la del compilador JIT JavaScript V8, alhora que funcionava a 1/250 de la freqüència de rellotge i consumia 1/16 de la potència dun nucli de CPU Intel i5-13400.

**Paraules clau:** Compilació, FPGA, Informàtica, CPU, Llenguatges de programació interpretats, Eficiència computacional, Eficiència energètica, Rendiment, Rust, Go, Javascript, Zig, Python, Verilog, Personalitzat Desenvolupament de maquinari, programari distribuït Sistemes

# Dedication

I dedicate this final thesis, as well as all the works that will follow, to all the people this world dares to call misfits.

To those who spend their free time embracing their uniqueness, studying, and learning. To those who fell in love with knowledge and were labeled as nerds for it. Not everyone has the courage to be different, so don't let the words of those who live a life you wouldn't want discourage you.

"Being different makes a person unforgettable. History doesn't remember the forgettable; it honors the unique minority that the majority can neither forget nor dare to be."

– Suzy Kassem

# Contents

| Li |      | its<br>Figures<br>Tables | 5                                                  | vi<br>viii<br>x |

|----|------|--------------------------|----------------------------------------------------|-----------------|

| 1  | Intr | oductio                  | on                                                 | 1               |

|    | 1.1  |                          | ration                                             | . 2             |

|    | 1.2  |                          | sal and goals                                      |                 |

|    | 1.3  | Struct                   | rure of this document                              | . 3             |

| 2  | Fun  | damen                    | tals                                               | 4               |

|    | 2.1  | Histor                   | rical context of the problem                       | . 4             |

|    |      | 2.1.1                    | The Moore era: Bottom optimizations                |                 |

|    |      | 2.1.2                    | The post-Moore era: Top optimizations              |                 |

|    | 2.2  | Progr                    | amming languages and compilers                     | . 8             |

|    |      | 2.2.1                    | Structure of a compiler                            | . 8             |

|    |      | 2.2.2                    | Approaches to translate programs into machine code | . 9             |

|    |      | 2.2.3                    | Lexical analysis                                   | . 10            |

|    |      | 2.2.4                    | Syntactic analysis                                 | . 10            |

|    |      | 2.2.5                    | Semantic analysis                                  | . 11            |

|    |      | 2.2.6                    | Intermediate code generation                       |                 |

|    |      | 2.2.7                    | Code optimization                                  |                 |

|    |      | 2.2.8                    | Code generation                                    |                 |

|    | 2.3  |                          | luction to FPGAs and HDL                           |                 |

|    | 2.4  |                          | of the art and current solutions                   |                 |

|    |      | 2.4.1                    | High-level based abstractions                      |                 |

|    |      | 2.4.2                    | Synthesizing high-level languages into HDL         |                 |

|    |      | 2.4.3                    | Design custom processors and interpreters          |                 |

|    | 2.5  | Tools                    | and programming languages used                     | . 17            |

| 3  | Des  |                          |                                                    | 18              |

|    | 3.1  |                          | m requirements                                     |                 |

|    | 3.2  | -                        | m design                                           |                 |

|    | 3.3  |                          | age specification (SIMPLER)                        |                 |

|    |      | 3.3.1                    | Lexical specification of SIMPLER                   |                 |

|    |      | 3.3.2                    | Syntax specification of SIMPLER                    |                 |

|    |      | 3.3.3                    | Semantic specification of SIMPLER                  |                 |

|    |      | 3.3.4                    | Examples                                           |                 |

|    | 3.4  | 0                        | -Weight Verilog Compiler Generator (LWVCG)         |                 |

|    | 3.5  | -                        | preter design                                      |                 |

|    | 3.6  |                          | ssor design                                        | . 29            |

| 4  | Imp  | lemen                    | tation                                             | 31              |

|    | 4.1  | Lexica                   | al analysis                                        |                 |

|    |      | 4.1.1                    | Algorithms and data structures used                |                 |

|    |      | 4.1.2                    | Hardware implementation                            | . 34            |

|    |                 | 4.1.3   | LWCVG Verilog code generation       | 36 |  |  |  |

|----|-----------------|---------|-------------------------------------|----|--|--|--|

|    | 4.2             | Syntax  | x analysis                          | 38 |  |  |  |

|    |                 | 4.2.1   | Used algorithms and data structures | 38 |  |  |  |

|    |                 | 4.2.2   | Hardware implementation             | 44 |  |  |  |

|    |                 | 4.2.3   | LWVCG Verilog code generation       | 48 |  |  |  |

|    | 4.3             | Semar   | ntic analysis                       | 49 |  |  |  |

|    |                 | 4.3.1   | Hardware implementation             | 50 |  |  |  |

|    |                 | 4.3.2   | LWVCG Verilog code generation       | 51 |  |  |  |

|    | 4.4             | Machi   | ne code Generation                  | 52 |  |  |  |

|    |                 | 4.4.1   | Algorithms and data structures used | 52 |  |  |  |

|    |                 | 4.4.2   | Hardware implementation             | 54 |  |  |  |

|    |                 | 4.4.3   | LWVCG Verilog code generation       | 57 |  |  |  |

|    | 4.5             | Code    | execution and Source code uploader  | 58 |  |  |  |

| 5  | Test            | ing and | 1 Validation                        | 59 |  |  |  |

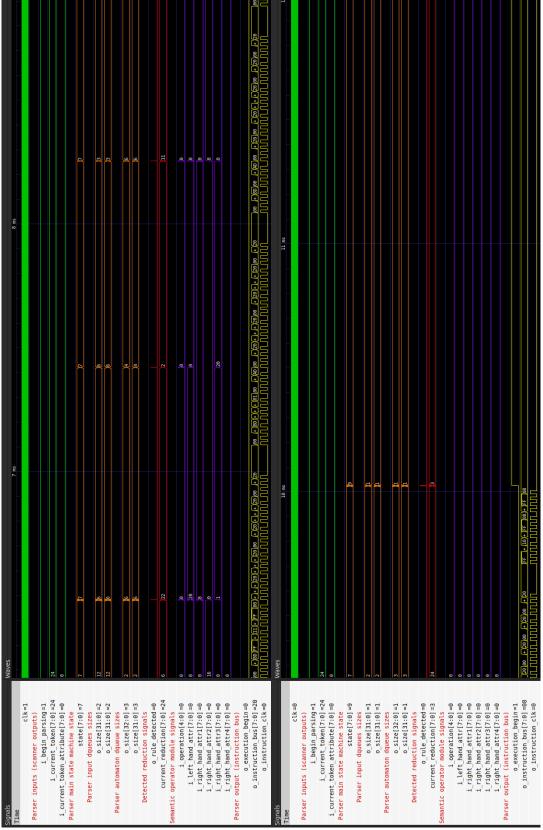

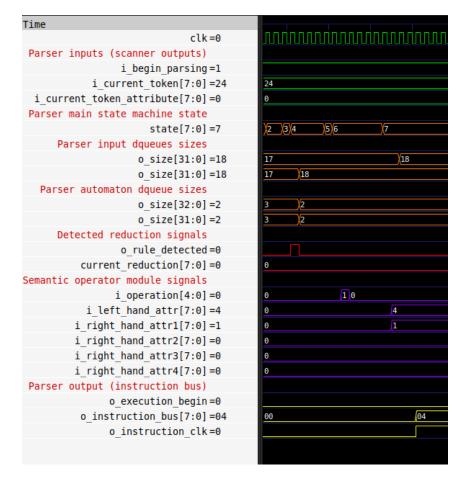

|    | 5.1             | Simula  | ations in GTKWave                   | 59 |  |  |  |

|    |                 | 5.1.1   | Scanner results                     | 60 |  |  |  |

|    |                 | 5.1.2   | Parser results                      | 62 |  |  |  |

|    |                 | 5.1.3   | Code execution results              | 72 |  |  |  |

|    | 5.2             | On-pr   | emise tests                         | 76 |  |  |  |

|    |                 | 5.2.1   | Testing setup                       | 76 |  |  |  |

|    |                 | 5.2.2   | Results                             | 78 |  |  |  |

| 6  | Con             | clusion | 15                                  | 80 |  |  |  |

|    | 6.1             | Impac   | t on time/space efficiency          | 80 |  |  |  |

|    | 6.2             | -       | t on energy efficiency              | 81 |  |  |  |

|    | 6.3             |         | e work                              | 81 |  |  |  |

| 7  | Rela            |         | ith completed studies               | 82 |  |  |  |

| -  | 1               |         |                                     |    |  |  |  |

| DI | Sibliography 83 |         |                                     |    |  |  |  |

# List of Figures

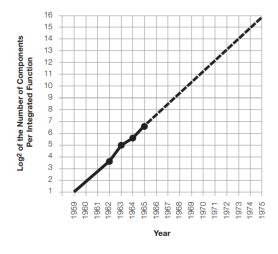

| 2.1  | Moore prediction number of Components per Integrated circuit          | 5   |

|------|-----------------------------------------------------------------------|-----|

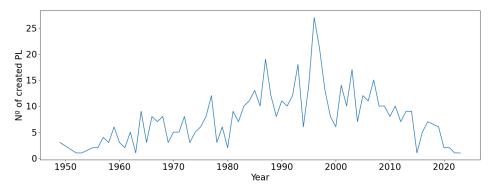

| 2.2  | $N^{\circ}$ of created PLs by year (from Wikipedia scrapped data)     | 5   |

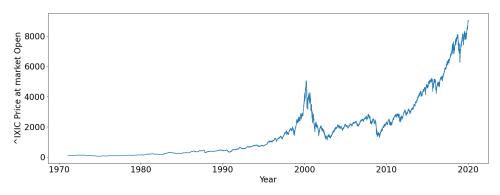

| 2.3  | Nasdaq Composite index                                                | 6   |

| 2.4  | StackOverflow language popularity survey 2024                         | 6   |

| 2.5  | Programming language performance comparison (matrix-multiplication)   | 7   |

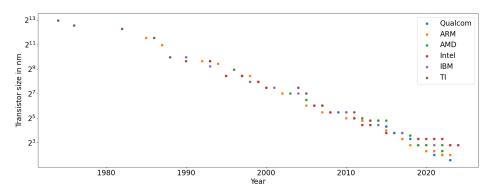

| 2.6  | Transistor size of main CPU manufacturers                             | 7   |

| 2.7  | Transistor count of main CPU manufacturers                            | 8   |

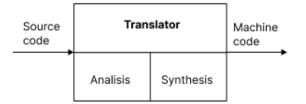

| 2.8  | Basic compiler diagram                                                | 8   |

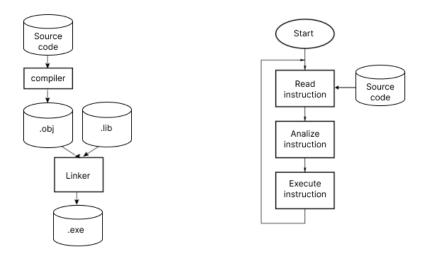

| 2.9  | Difference between compilers and interpreters                         | 9   |

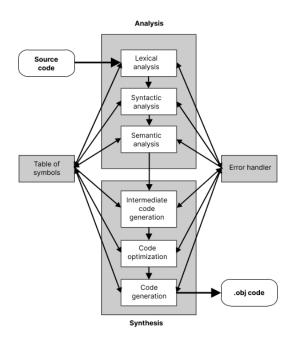

| 2.10 | Detailed view of the classical compilation process                    | 10  |

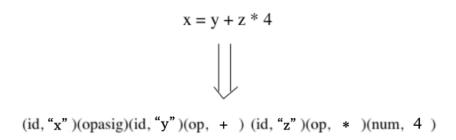

|      | Example of lexical analysis for " $x = y + z * 4$ "                   | 10  |

| 2.12 | Example of syntactical analysis for 2.11.                             | 11  |

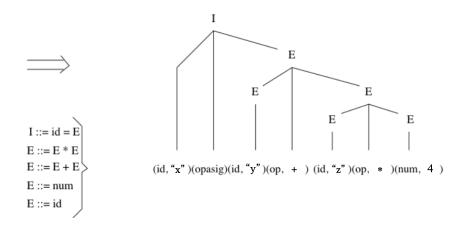

| 2.13 | Example of semantic analysis for 2.12.                                | 11  |

| 2.14 | Example of intermediate code generation for 2.13.                     | 12  |

|      | Example of intermediate code optimization for 2.14.                   | 12  |

|      | Example of code generation for 2.15.                                  | 12  |

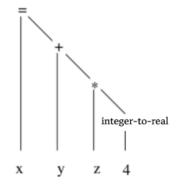

|      | ICE40LP/HX diagram                                                    | 13  |

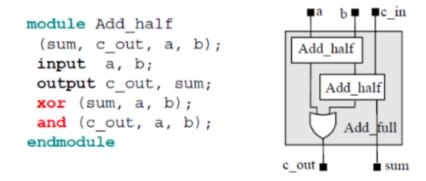

|      | Example of half adder implementation in Verilog                       | 14  |

| 2.19 | PYNQ Example                                                          | 15  |

| 2.20 | PYQN, C and OpenCV comparison                                         | 15  |

|      | Hot&Spicy results .                                                   | 15  |

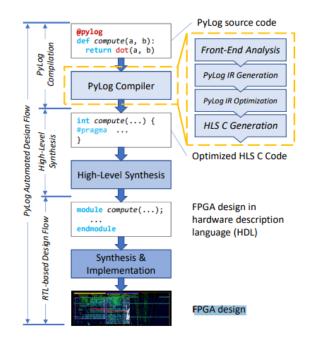

|      | FPGA Design Flow with PyLog                                           | 16  |

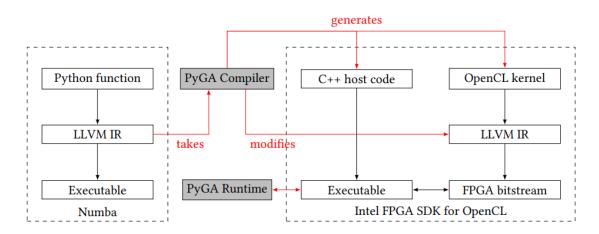

|      | FPGA Design Flow with PyGa                                            | 16  |

|      | JOP and 486SX15 performance comparison                                | 17  |

|      | ,                                                                     |     |

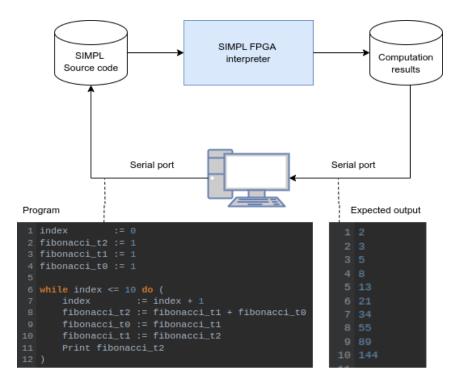

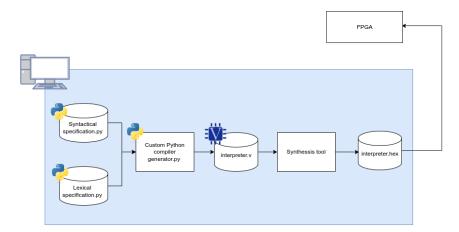

| 3.1  | System diagram during code execution                                  | 19  |

| 3.2  | Interpreter synthesis process                                         | 19  |

| 3.3  | ICE40-UP5K Specifications                                             | 20  |

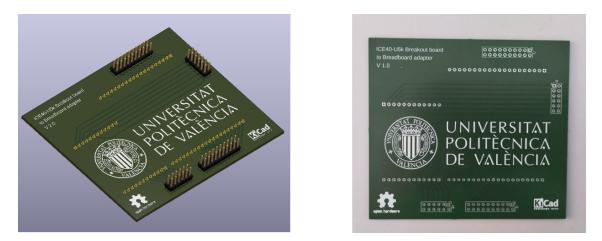

| 3.4  | ICE40-UP5K Breakout Boards                                            | 20  |

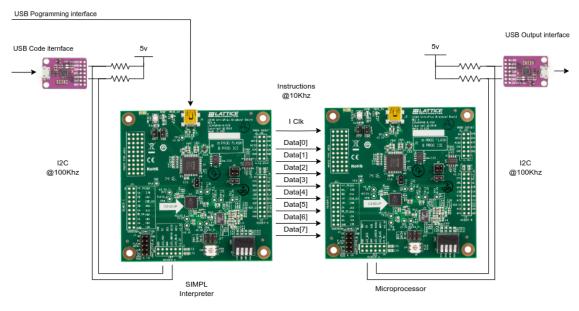

| 3.5  | I2C to USB device used                                                | 21  |

| 3.6  | System hardware diagram                                               | 21  |

| 3.7  | Specifications of the Lattice Certus-NX family                        | 22  |

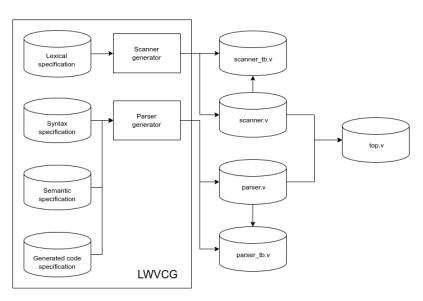

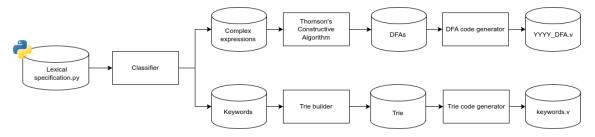

| 3.8  | LWVCG Module diagram                                                  | 26  |

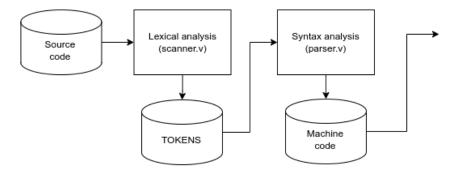

| 3.9  | Interpreter process                                                   | 28  |

| 3.10 | @vsilchuk MIPS implementation supported instructions                  | 30  |

|      |                                                                       | 0.1 |

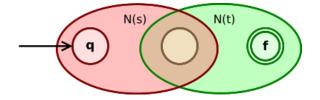

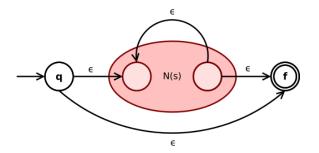

| 4.1  | Rule applied for emtpy expression                                     | 31  |

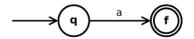

| 4.2  | Rule applied for a symbol a                                           | 32  |

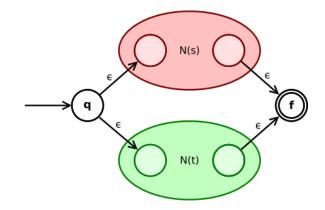

| 4.3  | Rule applied for s   t                                                | 32  |

| 4.4  | Rule applied to concatenation expression                              | 32  |

| 4.5  | Rule applied to "s*" expression                                       | 32  |

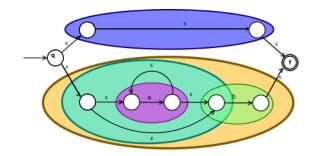

| 4.6  | NFA resulting of converting the expression " $(\epsilon \mid a^*b)$ " | 33  |

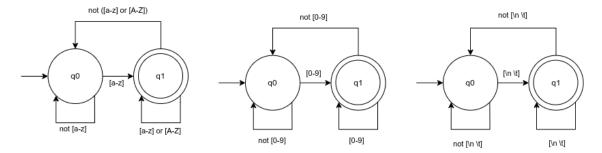

| 4.7  | DFNs resulting to apply Thomoson's algorithm to IDs, CONSTs and BLANK |     |

|      | expressions                                                           | 33  |

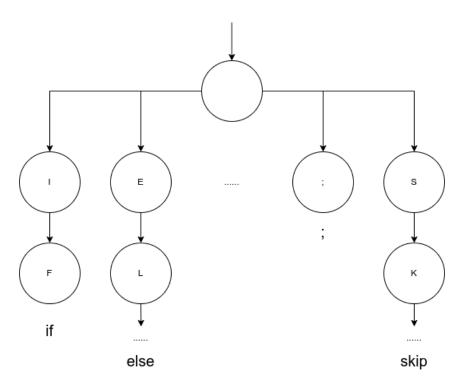

|                                                                                                                                                                                                   | Example of Trie for the keyworkds "if", "else", ";" and "skip"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

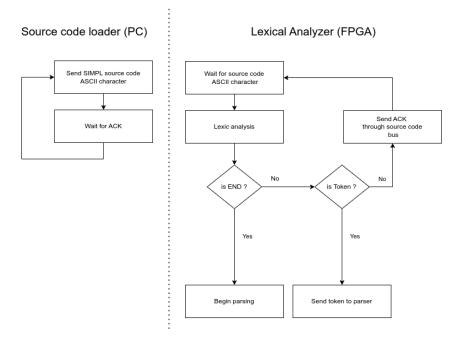

| 4.9                                                                                                                                                                                               | Communication workflow with the lexical analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                                                                                         |

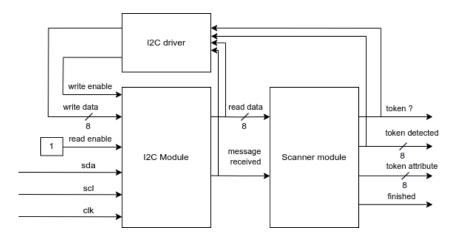

| 4.10                                                                                                                                                                                              | Lexical analyzer's hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35                                                                                                                         |

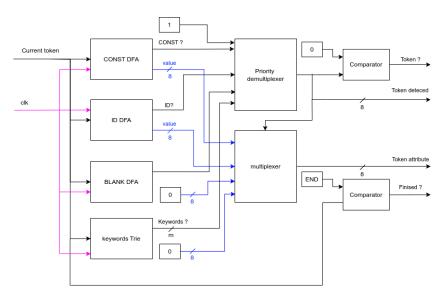

|                                                                                                                                                                                                   | Scanner module's hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36                                                                                                                         |

| 4.12                                                                                                                                                                                              | LWVCG workflow for generating the scanner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36                                                                                                                         |

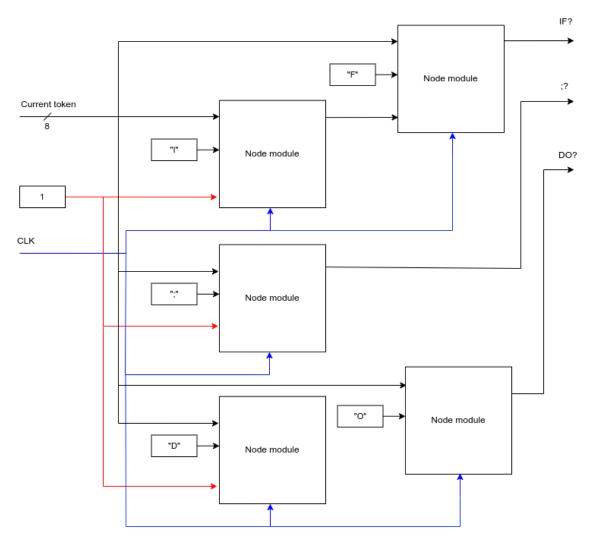

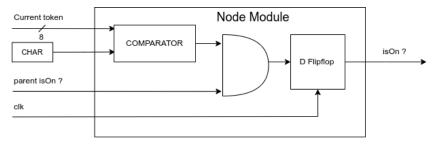

| 4.13                                                                                                                                                                                              | Trie's implementation hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37                                                                                                                         |

| 4.14                                                                                                                                                                                              | Trie's node hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37                                                                                                                         |

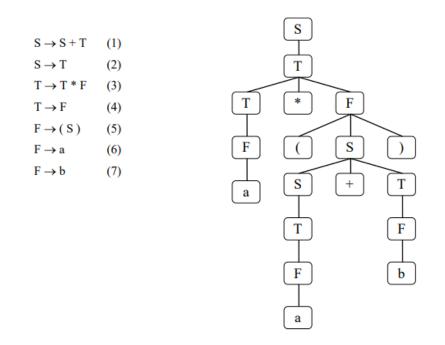

|                                                                                                                                                                                                   | Example of language and parse tree for the expression "a * (a + b)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                                                                                         |

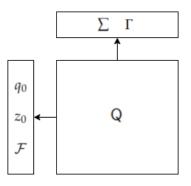

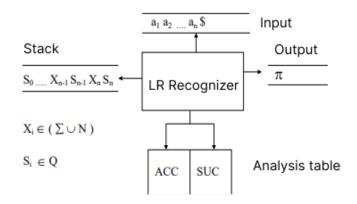

|                                                                                                                                                                                                   | Structure of a Pushdown Automaton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40                                                                                                                         |

| 4.17                                                                                                                                                                                              | Enter Caption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                                                                                                                         |

| 4.18                                                                                                                                                                                              | Example of SLR(1) analysis table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42                                                                                                                         |

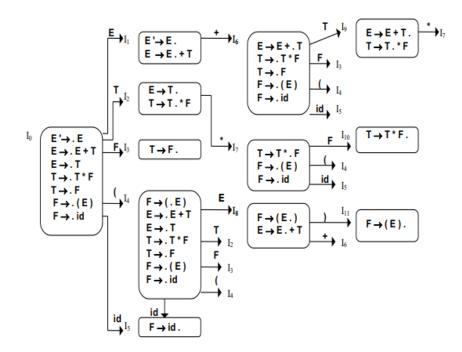

|                                                                                                                                                                                                   | Canonical collection of LR(0) item sets example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44                                                                                                                         |

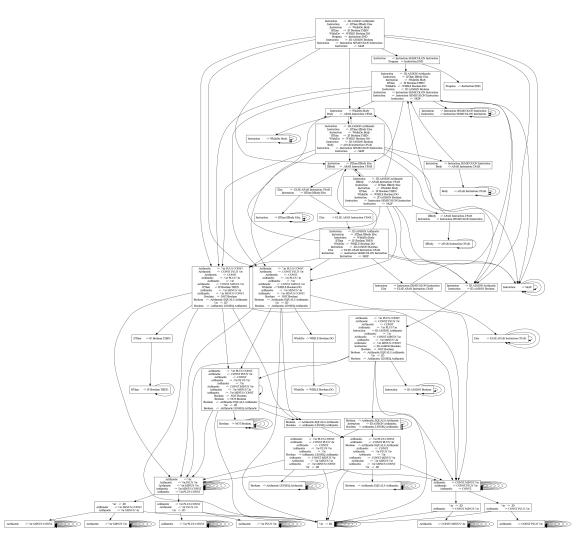

|                                                                                                                                                                                                   | SIMPLER canonical collection of LR(0) item sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45                                                                                                                         |

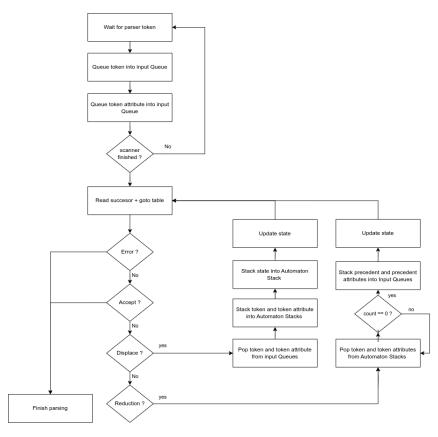

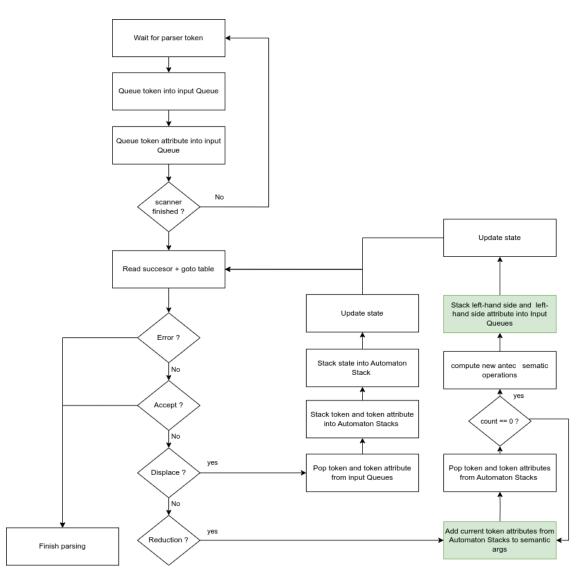

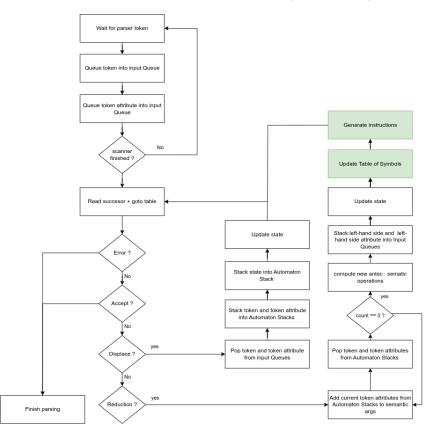

| 4.21                                                                                                                                                                                              | Parser's workflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46                                                                                                                         |

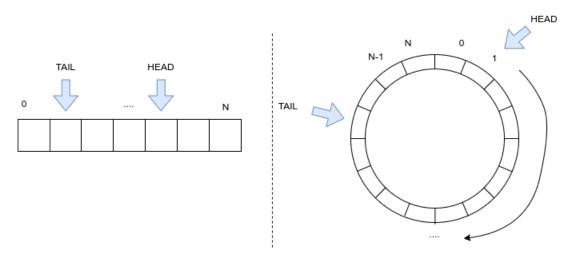

| 4.22                                                                                                                                                                                              | Circular buffer visualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                                                         |

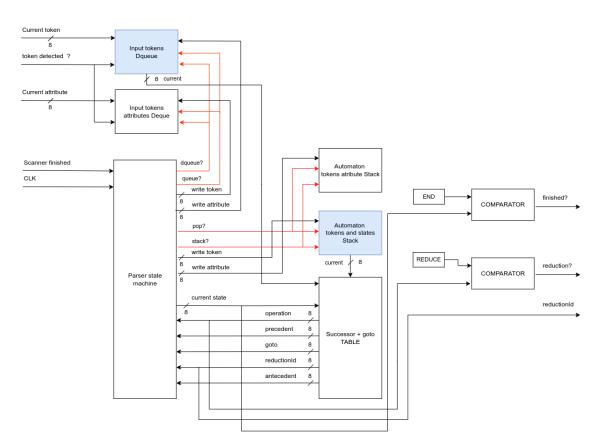

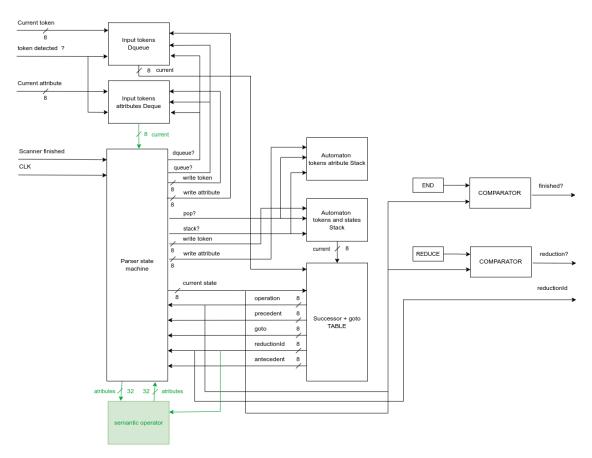

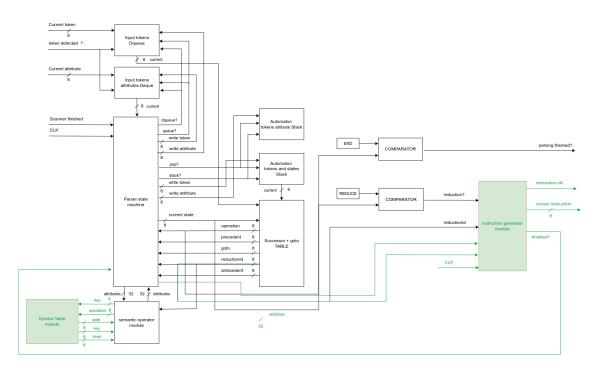

|                                                                                                                                                                                                   | Parser hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                                                         |

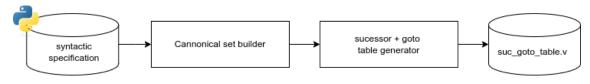

|                                                                                                                                                                                                   | LWVCG workflow to generate parser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48                                                                                                                         |

|                                                                                                                                                                                                   | Implementation of successor and goto table in Verilog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49                                                                                                                         |

|                                                                                                                                                                                                   | Modifications to the parser workflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                                                         |

|                                                                                                                                                                                                   | Modifications to the parser hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51                                                                                                                         |

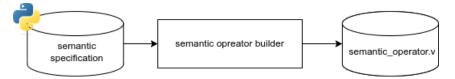

| 4.28                                                                                                                                                                                              | Semantic operator code generation workflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51                                                                                                                         |

|                                                                                                                                                                                                   | LWVCG generated contents of semantic operator module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52                                                                                                                         |

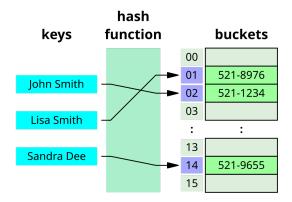

|                                                                                                                                                                                                   | Hash table visualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53                                                                                                                         |

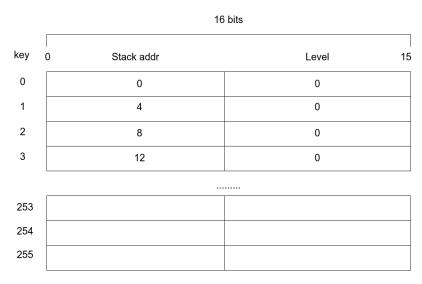

|                                                                                                                                                                                                   | Symbol Table structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53                                                                                                                         |

|                                                                                                                                                                                                   | Parsing workflow modifications for generating machine code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54                                                                                                                         |

|                                                                                                                                                                                                   | Semantic operator pack of reduction's token attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56                                                                                                                         |

|                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

| 4.34                                                                                                                                                                                              | Machine code generation modifications in parsing hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56                                                                                                                         |

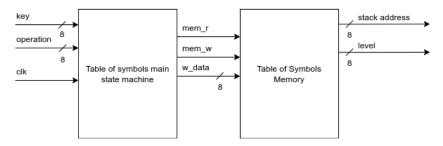

|                                                                                                                                                                                                   | Machine code generation modifications in parsing hardware block diagram<br>Symbol table hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56<br>56                                                                                                                   |

| 4.35                                                                                                                                                                                              | Symbol table hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

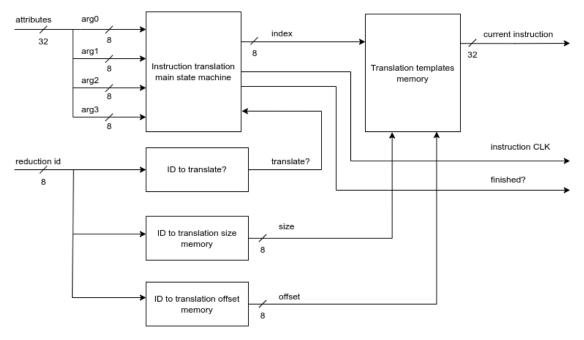

| 4.35<br>4.36                                                                                                                                                                                      | Symbol table hardware block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56                                                                                                                         |

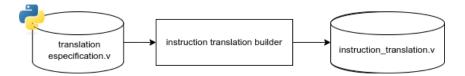

| 4.35<br>4.36<br>4.37                                                                                                                                                                              | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56<br>57<br>57                                                                                                             |

| 4.35<br>4.36<br>4.37<br>5.1                                                                                                                                                                       | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56<br>57<br>57<br>60                                                                                                       |

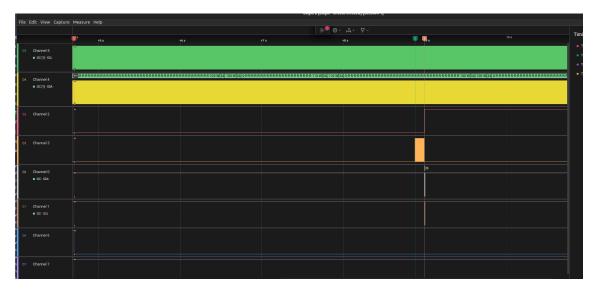

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2                                                                                                                                                                | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56<br>57<br>57<br>60<br>61                                                                                                 |

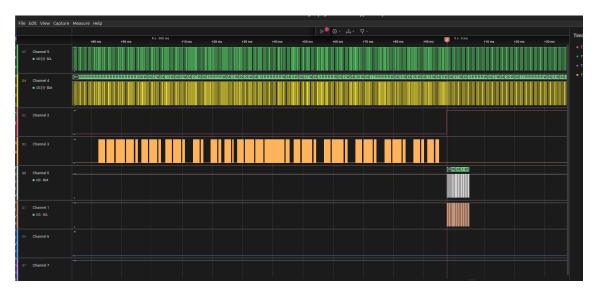

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2<br>5.3                                                                                                                                                         | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2Parser Verilog test bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56<br>57<br>57<br>60<br>61<br>62                                                                                           |

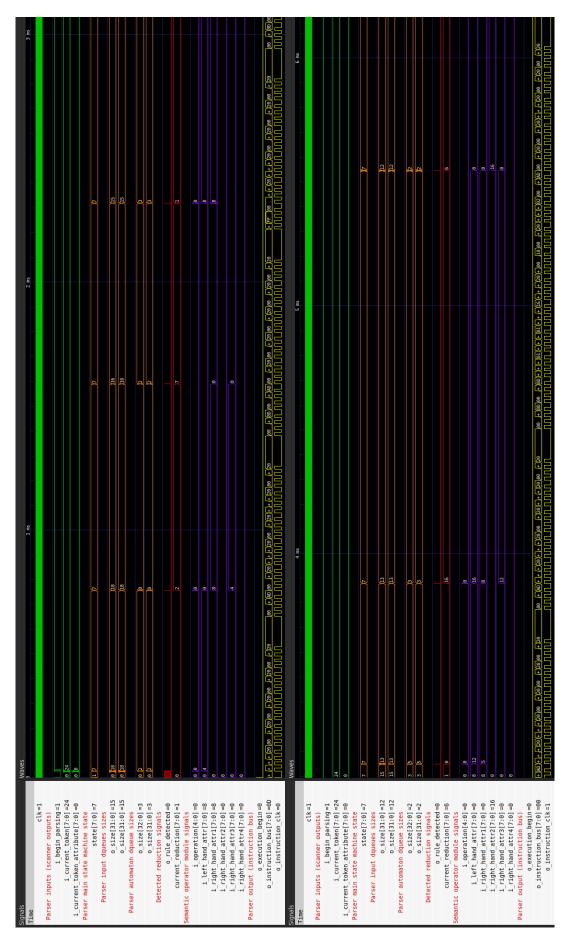

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2<br>5.3<br>5.4                                                                                                                                                  | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2Parser Verilog test benchFirst half of the parser test bench GTKWave results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56<br>57<br>57<br>60<br>61<br>62<br>64                                                                                     |

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                                                                                                           | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2Parser Verilog test benchFirst half of the parser test bench GTKWave resultsSecond half of the parser test bench GTKWave results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56<br>57<br>57<br>60<br>61<br>62<br>64<br>65                                                                               |

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                                                                    | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2Parser Verilog test benchFirst half of the parser test bench GTKWave resultsSecond half of the parser test bench GTKWave resultsLWVCG results for generating parser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56<br>57<br>57<br>60<br>61<br>62<br>64<br>65<br>66                                                                         |

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                                                                                             | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2Parser Verilog test benchFirst half of the parser test bench GTKWave resultsSecond half of the parser test bench GTKWave resultsLWVCG results for generating parserSemantic operator operation codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56<br>57<br>57<br>60<br>61<br>62<br>64<br>65<br>66<br>67                                                                   |

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                                                                                                      | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2Parser Verilog test benchFirst half of the parser test bench GTKWave resultsSecond half of the parser test bench GTKWave resultsMIPS emulator interpretation of the generated code up to iteration 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56<br>57<br>60<br>61<br>62<br>64<br>65<br>66<br>67<br>69                                                                   |

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                                                                               | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2Parser Verilog test benchFirst half of the parser test bench GTKWave resultsSecond half of the parser test bench GTKWave resultsLWVCG results for generating parserSemantic operator operation codesMIPS emulator interpretation of the generated code up to iteration 4Apio synthesis report for timing analysis on parser and scanner module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56<br>57<br>57<br>60<br>61<br>62<br>64<br>65<br>66<br>67<br>69<br>70                                                       |

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                                                                                       | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2Parser Verilog test benchFirst half of the parser test bench GTKWave resultsSecond half of the parser test bench GTKWave resultsLWVCG results for generating parserSemantic operator operation codesMIPS emulator interpretation of the generated code up to iteration 4Apio synthesis report for timing analysis on parser and scanner module.Parser main state machine during a single step (worst case scenario)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56<br>57<br>57<br>60<br>61<br>62<br>64<br>65<br>66<br>67<br>69<br>70<br>71                                                 |

| 4.35<br>4.36<br>4.37<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                                                               | Symbol table hardware block diagramInstruction generation module hardware block diagramCode generation LWVCG workflowScanner Verilog test benchGTKWave and Apio results for Algorithm 5.2Parser Verilog test benchFirst half of the parser test bench GTKWave resultsSecond half of the parser test bench GTKWave resultsMIPS emulator interpretation codesMIPS emulator interpretation of the generated code up to iteration 4Apio synthesis report for timing analysis on parser and scanner module.Parser main state machine during a single step (worst case scenario)Apio synthesis hardware consumption report for parser and scanner module.                                                                                                                                                                                              | 56<br>57<br>57<br>60<br>61<br>62<br>64<br>65<br>66<br>67<br>69<br>70<br>71<br>22<br>72                                     |