### Ph.D. Thesis

# Efficient Home-Based Protocols for Reducing Asynchronous Communication in Shared Virtual Memory Systems

### Salvador Petit Martí

#### **Advisors:**

Dr. Julio Sahuquillo Borrás

Dr. Ana Pont Sanjuán

Valencia, Spain. February 2003.

### A Montse

### Agradecimientos

Sin el apoyo y la ayuda de muchas otras personas, éste trabajo no hubiera sido posible. Esta página va dedicada a todas ellas.

En primer lugar, a mis directores de tesis, Ana Pont y Julio Sahuquillo, por su dedicación inestimable en todos estos años. Sin la motivación que Ana supo insuflarme, y el optimismo y seguridad expresados por Julio, seguramente yo no habría sido capaz de terminar este trabajo.

A los profesores Veljko Milutinovic y David Kaeli, por su ayuda en diversas etapas de esta investigación. Veljko me ayudó durante mi estancia en Belgrado en los comienzos de este trabajo, ofreciéndome su hospitalidad, y aportando excelentes ideas a lo largo de estos años. David ha sido una magnifica ayuda técnica y un importante aporte como persona a este trabajo en el último año.

Agradezco al Área de Coordinación de Lenguas Extranjeras de la Universidad Politécnica de Valencia por su ayuda en la traducción de algunas partes de este trabajo.

A mis compañeros y amigos en el trabajo: Silvia, Vicent, Patricia, Marian, Raúl, José Luis, Josep, Pau, Juan Carlos, Juan Luis, Ismael, Sergio y Alberto. Siempre han estado ahí cuando he necesitado su ayuda o su compañía.

Mas allá de la vida laboral, he tenido la suerte de contar con magníficas personas como mis amigos, cada una de las cuales con cualidades personales e irrepetibles, con las que he disfrutado, sufrido y sobre todo, crecido durante un montón de años. Perdonadme, no tengo espacio aquí para nombraros a todos, pero sabéis que os tengo siempre presentes.

Y finalmente, a mis padres, Vicenta y Salvador, y a mi hermano Vicente, sin olvidar a todo el resto de mi familia, por su paciencia, aguante e interés por mi trabajo durante todo este tiempo.

### Resumen

En la presente tesis se realiza una evaluación exhaustiva de los Sistemas de Memoria Distribuida conocidos como Sistemas de Memoria Virtual Compartida. Este tipo de sistemas posee características que los hacen especialmente atractivos, como son su relativo bajo costo, alta portabilidad y paradigma de programación de memoria compartida.

La evaluación consta de dos partes. En la primera se detallan las bases de diseño y el estado del arte de la investigación sobre este tipo de sistemas. En la segunda, se estudia el comportamiento de un conjunto representativo de cargas paralelas respecto a tres ejes de caracterización estrechamente relacionados con las prestaciones en estos sistemas. Mientras que la primera parte apunta la hipótesis de que la comunicación asíncrona es una de las principales causas de pérdida de prestaciones en los Sistemas de Memoria Virtual Compartida, la segunda no sólo la confirma, sino que ofrece un detallado análisis de las cargas del que se obtiene información sobre la potencial comunicación asíncrona atendiendo a diferentes parámetros del sistema.

El resultado de la evaluación se utiliza para proponer dos nuevos protocolos para el funcionamiento de estos sistemas que utiliza un mínimo de recursos hardware, alcanzando prestaciones similares e incluso superiores en algunos casos a sistemas que utilizan circuitos hardware de propósito específico para reducir la comunicación asíncrona. En particular, uno de los protocolos propuestos es comparado con una reconocida técnica hardware para reducir la comunicación asíncrona, obteniendo resultados satisfactorios y complementarios a la técnica comparada. Todos los modelos y técnicas usados en este trabajo han sido implementados y evaluados utilizando una nuevo entorno de simulación desarrollado en el contexto de este trabajo.

### Resum

En la present tesi, es realitza una avaluació dels Sistemes de Memòria Distribuïda coneguts com Sistemes de Memòria Virtual Compartida. Este tipus de sistemes posseeix característiques que els fan especialment atractius, com són el seu relatiu baix cost, alta portabilitat i paradigma de programació de memòria compartida.

L'avaluació consta de dues parts. En la primera es detallen les bases de disseny i l'estat de l'art de la investigació sobre este tipus de sistemes. En la segona, s'estudia el comportament d'un conjunt representatiu de càrregues paral·leles respecte a tres eixos de caracterització estretament relacionats amb les prestacions en estos sistemes. Mentre que la primera part apunta la hipòtesi que la comunicació asíncrona és una de les principals causes de perduda de prestacions en els Sistemes de Memòria Virtual Compartida, la segona no sols la confirma, sinó que ofereix una detallada anàlisi de les càrregues de què s'obté informació sobre la potencial comunicació asíncrona atenent a diferents paràmetres del sistema.

El resultat de l'avaluació s'utilitza per a proposar dos nous protocols per al funcionament d'estos sistemes que utilitzen un mínim de recursos hardware, aconseguint prestacions semblants i superiors en alguns casos a sistemes que fan us de hardware de propòsit específic per a reduir la comunicació asíncrona. En particular un dels protocols proposts és comparat amb una reconeguda tècnica hardware per a reduir la comunicació asíncrona, obtenint resultats satisfactoris i complementaris a la tècnica comparada. Tots els models i tècniques usats en este treball han sigut avaluats utilitzant un nou entorn de simulació desenvolupat en el context d'este treball.

### **Abstract**

In this thesis, an exhaustive evaluation of Distributed Shared Memory Systems known as Shared Virtual Memory Systems is performed. This kind of systems has characteristics that made them specially attractive, like their relatively low cost, high portability and shared memory programming paradigm.

The evaluation is performed in two parts. In the first part, the design principles and the state of the art of the research related with this kind of systems is performed. In the second part, it is studied the behavior of a representative set of parallel workloads regarding to three axes of characterization intimately related with the performance of this kind of systems. While the first part points to the hypothesis that asynchronous communication is one of the main causes of performance loss, the second does not only confirm it, but also offers a detailed analysis of the workloads that shows useful information about the potential asynchronous communication attending to different system parameters.

The evaluation results are used to propose two new protocols for this kind of systems that uses minimal hardware resources, reaching similar and in some cases superior performance to that obtained by systems that make use of specific hardware for reducing asynchronous communication. In particular, one of the proposed protocols is compared with a well-known hardware technique for reducing asynchronous communication, obtaining satisfactory and complementary results to the compared technique. All the modeled systems and techniques used in this work have been implemented and evaluated using a new simulation environment developed in the context of this work.

# **Contents**

| CHAPTER 1. INTRODUCTION                          | 1  |

|--------------------------------------------------|----|

| 1.1. SOFTWARE DISTRIBUTED SHARED MEMORY          | 2  |

| 1.2. RELAXED MEMORY CONSISTENCY MODELS           | 4  |

| 1.3. Thesis Overview                             | 7  |

| CHAPTER 2. SHARED VIRTUAL MEMORY SYSTEMS         | 9  |

| 2.1. A SIMPLE SVM SYSTEM EXAMPLE                 | 10 |

| 2.2. MEMORY CONSISTENCY MODELS                   | 14 |

| 2.2.1. Performing Order                          | 14 |

| 2.2.2. Sequential Memory Consistency Model       | 17 |

| 2.2.3. Release Memory Consistency Model          |    |

| 2.2.4. Lazy Release Memory Consistency Model     |    |

| 2.3. MULTIPLE WRITER PROTOCOLS                   | 21 |

| 2.3.1. Invalidating versus Updating              | 23 |

| 2.3.2. Eager Release Consistency Protocol        | 24 |

| 2.3.3. Lazy Release Consistency Protocol         | 25 |

| 2.3.4. Home Lazy Release Consistency Protocol    | 28 |

| 2.4. ASYNCHRONOUS COMMUNICATION                  | 29 |

| 2.4.1. Asynchronous Communication Implementation | 30 |

| 2.4.2. Types of Asynchronous Requests            | 31 |

| 2.5. CONCLUSIONS                                 | 34 |

| CHAPTER 3. THE SIMULATION ENVIRONMENT: LIDE      | 37 |

|--------------------------------------------------|----|

| 3.1. LIMES                                       | 38 |

| 3.2. SIDE                                        | 40 |

| 3.3. CONNECTING AND EXECUTING LIMES WITH SIDE    | 41 |

| 3.4. Block Structure                             | 44 |

| 3.5. Conclusions                                 | 45 |

| CHAPTER 4. WORKLOAD CHARACTERIZATION             | 47 |

| 4.1. Axes of the Characterization                | 48 |

| 4.1.1. Performance Synergies                     | 49 |

| 4.2. WORKLOAD DESCRIPTION                        | 50 |

| 4.2.1. Regular Applications                      | 50 |

| 4.2.2. Irregular Applications                    | 51 |

| 4.3. Sources of Performance Loss                 | 52 |

| 4.3.1. Critical Section Dilation                 | 53 |

| 4.3.2. Sharing Pattern Conversion                | 54 |

| 4.4. WORKLOAD CHARACTERIZATION ANALYSIS          | 56 |

| 4.4.1. Simulation Environment                    | 57 |

| 4.4.2. Frequency of Sharing                      |    |

| 4.4.3. Granularity of Sharing                    | 63 |

| 4.4.4. Sharing Pattern                           | 66 |

| 4.5. CONCLUSIONS                                 | 71 |

| CHAPTER 5. THE HLRC-DU AND THE HLRC-CU PROTOCOLS | 73 |

| 5.1. A Preliminary Study                         | 74 |

| 5.1.1. The Baseline HLRC Protocol                |    |

| 5.1.2. Simulation Environment                    |    |

| 5.1.3. Results                                   |    |

| 5.2. PROPOSED PROTOCOLS                          |    |

| 5.2.1. The HLRC-DU Protocol                      |    |

| 5.2.2. The HLRC-CU Protocol                      | 82 |

| 5.2.3. HLRC-DU versus HLRC-CU                    | 84 |

| 5.3. SENSITIVITY TO THE THRESHOLD SIZE           | 88 |

| 5.3.1. Results                                   | 88 |

| 5.4. Performance versus Hardware techniques      | 92 |

| 5.5. CONCLUSIONS                                 | 93 |

| CHAPTER 6. CONCLUSIONS                             | 97  |

|----------------------------------------------------|-----|

| 6.1. WORKLOAD CHARACTERIZATION IN SVM SYSTEMS      | 98  |

| 6.2. DEVELOPED PROTOCOLS                           | 99  |

| 6.3. SIMULATION ENVIRONMENT                        | 100 |

| 6.4. FUTURE LINES OF RESEARCH                      | 100 |

| 6.5. Publications Related with This Dissertation   | 101 |

| APPENDIX A. PRELIMINARY WORKLOAD STUDIES           | 103 |

| A.1. Experimental Framework                        | 104 |

| A.2. Sharing Patterns                              | 106 |

| A.2.1. Serial and Concurrent Data Sharing          | 106 |

| A.2.2. Writing Localities                          | 109 |

| A.3. IMPLEMENTATION IDEAS TO IMPROVE SVM PROTOCOLS | 112 |

| A.3.1. Reducing Multiple Writer Overhead           | 112 |

| A.3.2. Reducing Diff Overhead                      | 115 |

| A.4. Conclusions                                   | 116 |

| REFERENCES                                         | 119 |

# **Figures**

| FIGURE 1 – STATE TRANSITION DIAGRAM OF A PAGE.                            | 12 |

|---------------------------------------------------------------------------|----|

| FIGURE 2 – OS INTERRUPT HANDLERS                                          | 13 |

| FIGURE 3 – CODE EXAMPLE                                                   | 15 |

| FIGURE 4 – BEGIN FENCE ( $F_B$ ) AND END FENCE ( $F_E$ )                  | 16 |

| FIGURE 5 – FENCES IN MEMORY CONSISTENCY MODELS                            | 18 |

| FIGURE 6 – CODE EXAMPLE                                                   | 20 |

| FIGURE 7 – HAPPENED-BEFORE ORDER                                          | 21 |

| FIGURE 8 – ERC PROTOCOL                                                   | 25 |

| FIGURE 9 – LRC PROTOCOL                                                   | 26 |

| FIGURE 10 – HLRC PROTOCOL                                                 | 29 |

| FIGURE 11 – SVM SEMAPHORE MANAGEMENT EXAMPLE                              | 33 |

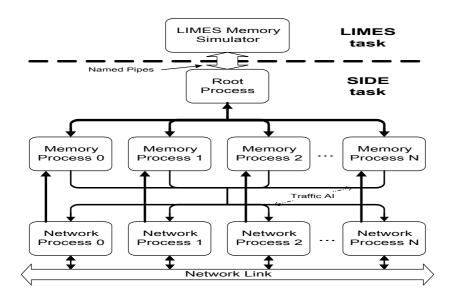

| FIGURE 12 – BLOCK DIAGRAM OF THE LIDE SIMULATION ENVIRONMENT              | 38 |

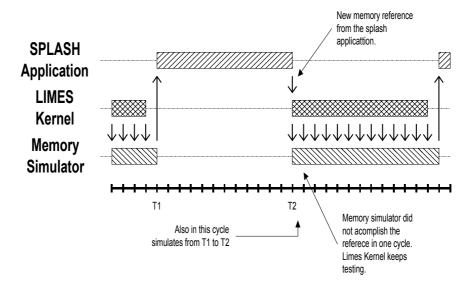

| FIGURE 13 – TEMPORAL RELATION BETWEEN                                     | 39 |

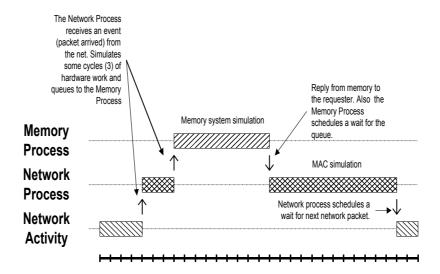

| FIGURE 14 – TEMPORAL SIMULATION EXAMPLE IN THE SIDE SIMULATOR             | 41 |

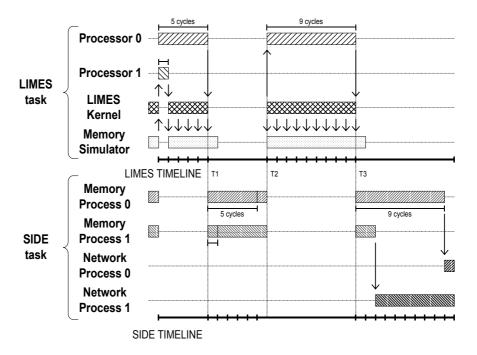

| FIGURE 15 – LIMES AND SIDE WORKING TOGETHER                               | 43 |

| FIGURE 16 – LIDE SYNCHRONIZATION PATHS AND PROCESSES                      | 44 |

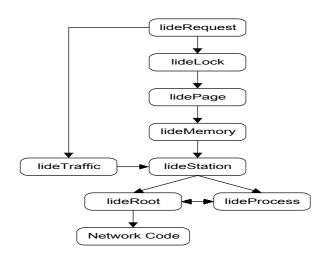

| FIGURE 17 – LIDE MODULE DEPENDENCIES                                      | 45 |

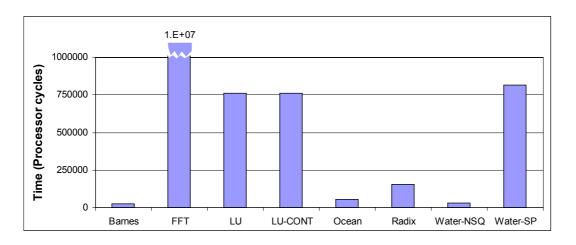

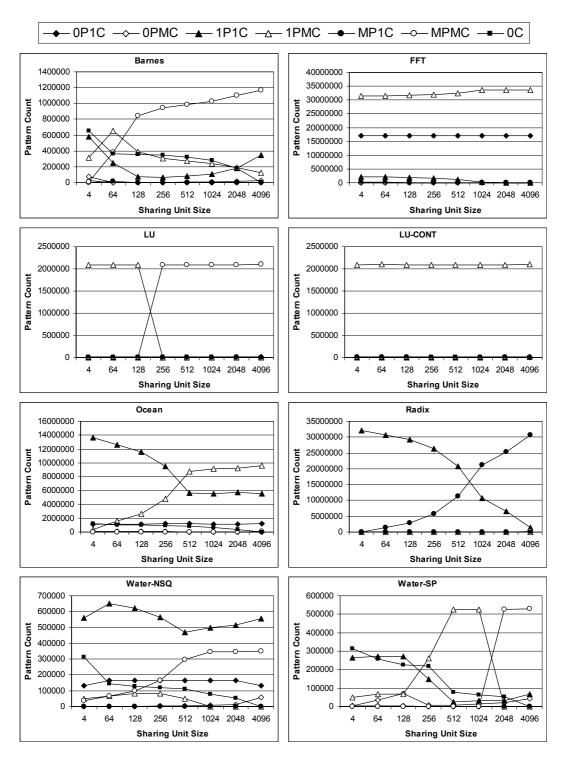

| FIGURE 18 – CYCLES BETWEEN SYNCHRONIZATIONS                               | 58 |

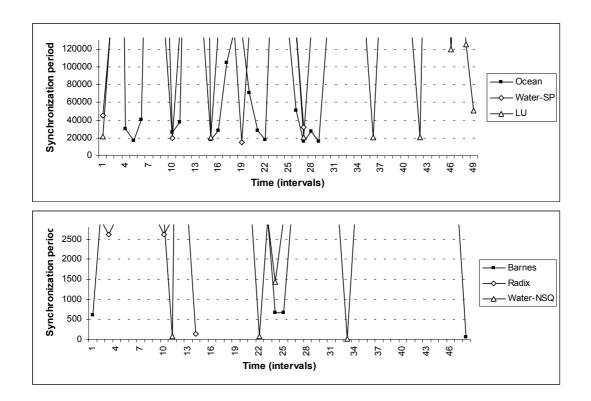

| FIGURE 19 – SYNCHRONIZATION PERIOD MEASURED BY INTERVAL                   | 60 |

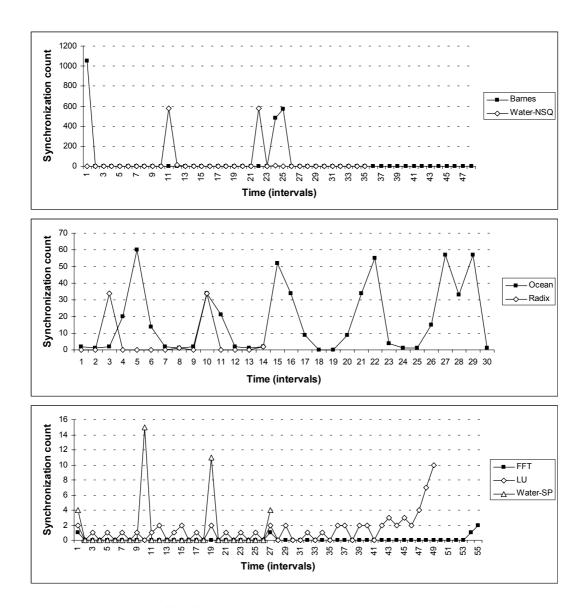

| FIGURE 20 – SYNCHRONIZATION COUNT MEASURED BY INTERVAL                    | 62 |

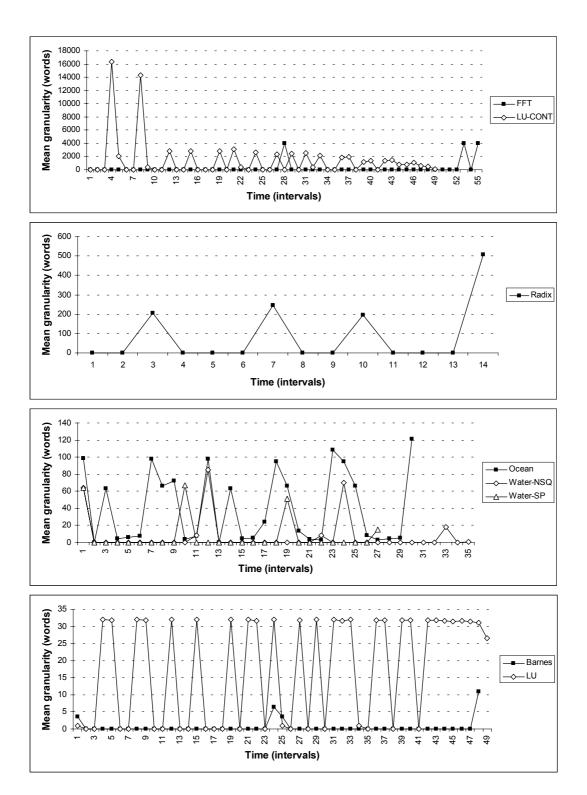

| FIGURE 21 – MEAN GRANULARITY MEASURED BY INTERVAL                         | 64 |

| FIGURE 22 – TOTAL WRITTEN DATA BETWEEN SYNCHRONIZATIONS FOR EACH INTERVAL | 65 |

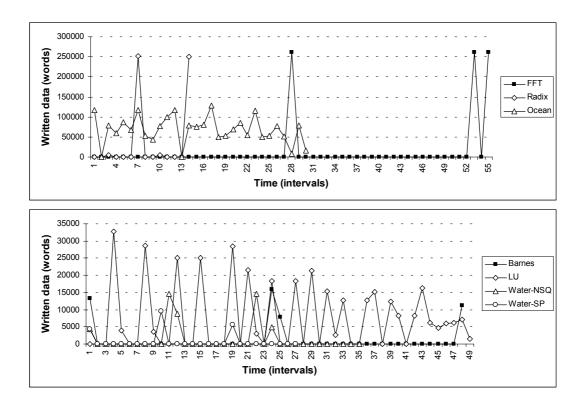

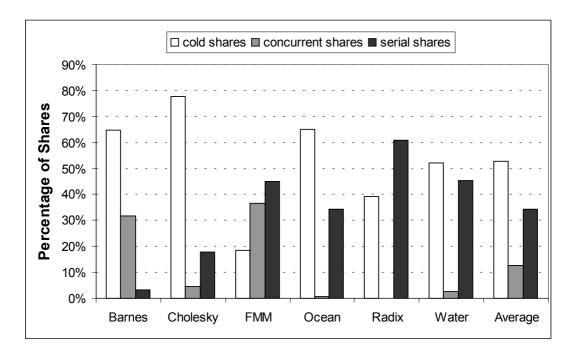

| FIGURE 23 – SHARING PATTERN COUNT                                                   | 68  |

|-------------------------------------------------------------------------------------|-----|

| FIGURE 24 – FRAGMENTATION EFFECT                                                    | 69  |

| FIGURE 25 – BASELINE PROTOCOL                                                       | 76  |

| Figure 26 – Breaking down received write notices.                                   | 80  |

| FIGURE 27 – HLRC-DU PROTOCOL                                                        | 81  |

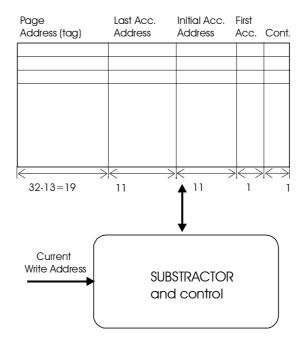

| Figure 28 – Page information table                                                  | 83  |

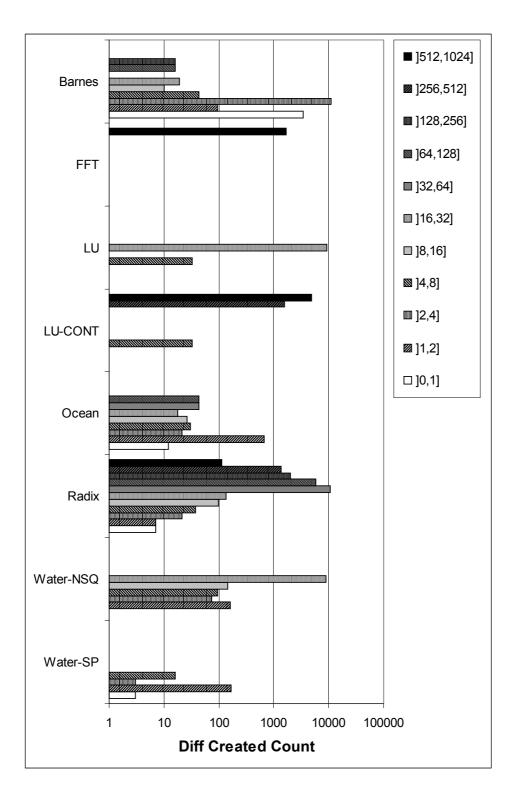

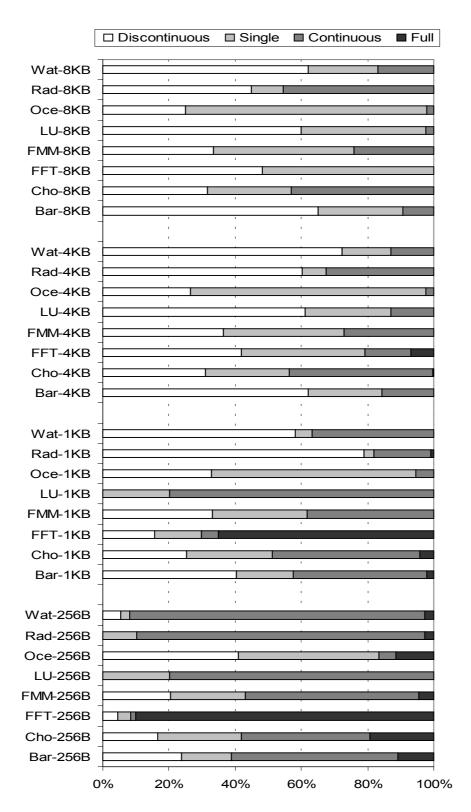

| Figure 29 – Distribution of diff sizes                                              | 86  |

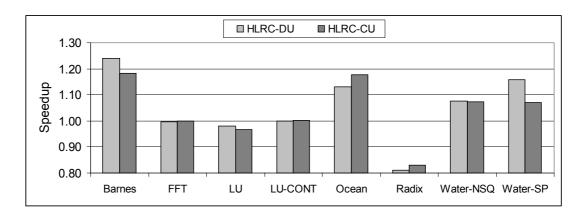

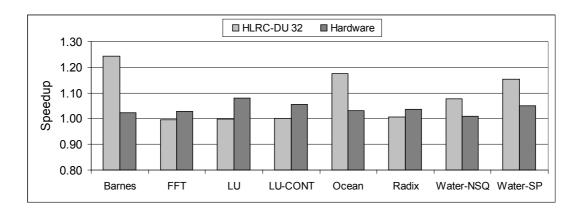

| FIGURE 30 – SPEEDUP OVER THE BASELINE PROTOCOL                                      | 87  |

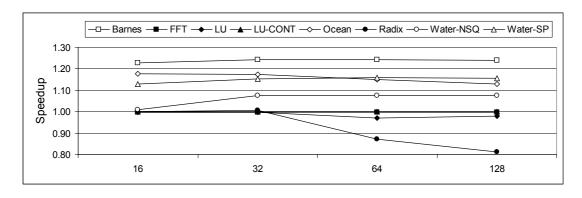

| FIGURE 31 – SPEEDUP RELATIVE TO THE BASELINE PROTOCOL                               | 90  |

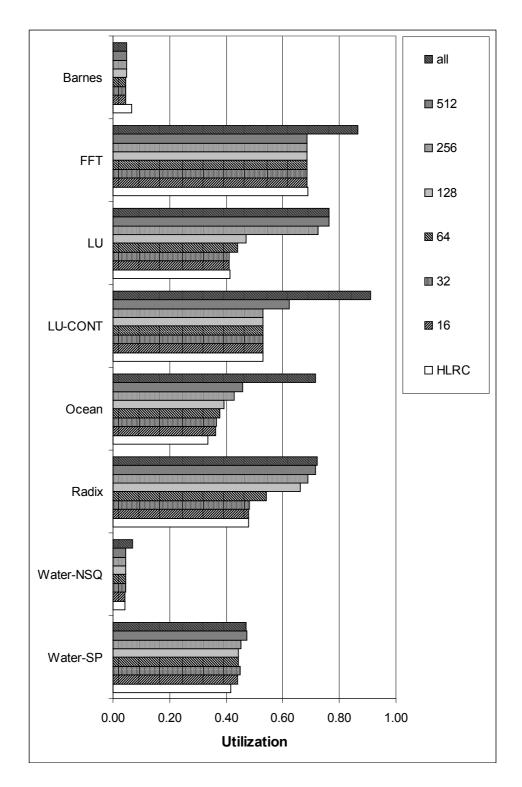

| Figure 32 – Network utilization                                                     | 91  |

| FIGURE 33 – SPEEDUP RELATIVE TO THE BASELINE PROTOCOL                               | 92  |

| FIGURE 34 – SOFTWARE FILTER TO CLASSIFY SHARED DATA ACCESSES INSIDE THE SEMAPHORES. | 108 |

| FIGURE 35 – PERCENTAGE OF SHARES                                                    | 108 |

| Figure 36 – Software filter to classify page writes                                 | 110 |

| FIGURE 37 – PERCENTAGE OF WRITE PATTERNS                                            | 111 |

| FIGURE 38 – SEMAPHORES SERIALIZING THE WRITERS TO A PAGE.                           | 113 |

# **Tables**

| Table 1 – Vector timestamps calculation                                                                                  | 27           |

|--------------------------------------------------------------------------------------------------------------------------|--------------|

| $\label{thm:conditional} Table  2 - Workload  \text{Characteristics according to the three axes of characteristics}  \\$ | ERIZATION 52 |

| Table 3 - Transition from the inherent pattern to the induced pattern                                                    | 56           |

| Table 4 – Benchmark problem sizes                                                                                        | 57           |

| Table $5$ – Average and standard deviation in frequency of sharing                                                       | 59           |

| Table 6 – Benchmark Characteristics                                                                                      | 78           |

| Table 7 – Distribution of diff sizes                                                                                     | 79           |

| Table 8 – Maximum number of required entries in the PIT                                                                  | 84           |

| Table 9 – Increment of diffs updated by HLRC-DU versus HLRC-CU                                                           | 85           |

| Table 10 – Percentage of Saved Home page requests                                                                        | 89           |

| Table 11 – Speedup relative to the baseline protocol                                                                     | 93           |

| Table 12 – Benchmark Characteristics                                                                                     | 105          |

| TABLE 13 – CONCURRENT VERSUS SERIAL SHARES                                                                               | 109          |

| Table 14 – Chunk size distribution                                                                                       | 112          |

| Table 15 – Mean number of writers per page varying the page size                                                         | 115          |

# Chapter 1

### Introduction

Parallel workloads executed on distributed systems, multiprocessors or multicomputers, are usually based on two distributed programming paradigms: message passing and shared memory. In the first paradigm, parallel processes have separate memory address spaces and they communicate with the other processes explicitly by means of message passing. In the second paradigm, the processes share (partially or totally) the memory address space and, in a dynamic and transparent way for the programmer, write actions on the shared memory from a process are perceived later by other parallel processes.

Traditionally, message passing distributed programming has been used to parallelize and execute workloads in low cost distributed computer environments, such as those made up by Networks of Workstations (NOW) [AND95]. The main reasons for this phenomenon are:

- There are standard libraries such as PVM [SUN90] and MPI [HAN98] that have been developed for different operating systems and hardware, assuring platform independence for the workload execution.

- The message-passing paradigm can be adapted to almost any environment because the interface it offers to the parallel workload is independent of the supporting hardware, which can be even a heterogeneous NOW.

- As the interface is independent of any specific hardware, system maintenance is

facilitated because it becomes open and independent of the manufacturer (as long

as it follows a standard, such as Ethernet). This reduces costs since the nodes and

the interconnection network can be easily replaced and upgraded.

- Communication between processes is mainly carried out by software, with practically no hardware restrictions (any network is valid, even those which are non-specifically designed for parallel computing).

On the other hand, the main disadvantages of the message-passing paradigm are:

- It is much less intuitive for the programmer than the shared memory paradigm, so to parallelize code is more difficult than in Shared Memory Multiprocessor (SMP) systems [CUL99] or Distributed Shared Memory (DSM) systems [PRO98].

- A great amount of the code that is currently executed in monoprocessor systems

may easily be parallelized by means of the shared programming paradigm; for

example, the code in multimedia software, databases, and the Internet. This is

because several threads (multithread), which share the same memory address

space, carry out the execution.

The parallelization of the execution of shared memory workloads has been carried out by means of a hardware specifically designed to allow this type of programming. Usually, SMP or DSM systems are used. SMP systems are inexpensive but they lack scalability (only less than 16 nodes are feasible) as a consequence of their use of a shared medium for communication, which is not easily expandable because it saturates quickly, so becoming a bottleneck. DSM systems allow higher scalability and are more easily expandable, but they require a higher cost in hardware and design.

### 1.1. Software Distributed Shared Memory

Software Distributed Shared Memory (SDSM) systems [LI\_86] are an inexpensive alternative, scalable above SMP systems, easier to maintain, and open. This kind of systems can be implemented by means of two methods:

- Supported by the programming language or by extensions of the language in which

the workload is programmed. The compiler or the preprocessor generates the

necessary code to establish the communication. This assumes that the programmer

should somehow mark the memory zones or objects to be shared.

- Supported by the operating system: The Operating System (OS) detects write operations in memory zones and carries out the communication. Typically, virtual memory mechanisms, which are present in all modern operating systems, are used for this case. This scheme is transparent for the programmer.

This work is aimed at the study of the latter type of SDSM systems, the Shared Virtual Memory (SVM) systems.

Li and Hudak suggested first the SVM system concept in [LI\_86], and their implementation details were published in [LI\_88]. Four main features define an SVM system:

- a) Nodes share a common virtual memory address space, by using the virtual memory system provided by the supporting OS.

- b) The page is the sharing unit.

- c) The supporting software (OS, libraries, etc.) takes charge of guaranteeing coherence maintenance of the shared pages (when necessary).

- d) The parallel workload is independent of the interconnection network and the hardware supporting it.

These features make SVM systems especially attractive because they allow the use of shared memory code without modifications, allowing its execution in heterogeneous and decoupled networks.

In general, SVM systems are usually composed of several inexpensive nodes (single processors or SMP systems) connected by a commodity network. In addition, SVM systems are cheaper than other alternatives. As in the case of NOWs that use the message

passing paradigm, this approach enables fault tolerance and offers good flexibility when maintaining and upgrading the processing nodes of the system, since these are physically independent.

On the other hand, these features become the source of the main problems in these systems:

- False sharing: Since the page size is usually large (4 or 8 Kbytes), the probability of false sharing rises, so increasing the communication traffic. The effect of false sharing is that coherence actions are performed between nodes that are not sharing data. False sharing may have adverse effects for the system such as the ping-pong effect of pages among writers [TOR94].

- High latency: Usually, coherence messages are triggered by page faults detected by the OS, which uses the appropriate software to inject them in the interconnection network. Therefore, their latency penalties are usually very high.

Both problems are related, since false sharing produces additional messages to maintain the coherence, which introduce their own latency affecting the whole system performance.

### 1.2. Relaxed Memory Consistency Models

To lessen these problems, much research has focused on relaxed memory consistency models [IFT99]. Memory consistency models specify when a memory reference can be carried out and become visible to the memory system, so that the rest of network nodes can see it. Depending on whether the model is more or less restrictive, better or worse performances will be achieved. The most restrictive model is called sequential and it is simpler to implement, but it offers the worst performance. To improve performance, research has focused on reducing the restrictions in order to increase performance. The answer has been the release memory consistency models, which allow reordering of memory references according to certain rules specified by the model. In SVM systems, the release memory consistency models most frequently used are Release Consistency (RC) model [GHA90] and Lazy Release Consistency (LRC) model [KEL95].

Most parallel workloads use synchronization methods when several processes access

shared data. In this chapter we will assume that the primitives used are semaphores, as semaphores can implement any synchronization primitive.

The main idea behind release memory consistency models is that if a parallel workload is correctly programmed, it must be exempt from race conditions [ADV93]. A race condition occurs when a possible execution of the program may allow a write access and another access at the same time (read or write). If race conditions are not allowed, writing accesses to shared data will be performed serially using any synchronization primitive (for instance, semaphores). This implies that it is only necessary to send coherence messages when a given process leaves a section protected by a semaphore.

When these models were introduced, new techniques were added to allow multiple writers on a page. As race conditions are not allowed, writes carried out at the same time by different writers refer to different variables. Therefore, multiple writers carry out modifications at the same time on different addresses in the page. These techniques face the problems derived from false sharing, as there is no conflict between writers accessing the same page.

The implementation of a given memory consistency model (with single or multiple writers) is called memory consistency protocol. The first memory consistency protocol implementing the RC model with multiple writers was the Eager Release Consistency (ERC) protocol [GHA90] and it was implemented on the Munin system [CAR91]. The model carries out the coherence actions when the semaphore is released. Its advantage is that it reduces the number of coherence messages by delaying the coherence actions (several coherence actions are compressed in one message). In addition, the software overhead is reduced (only one message is sent) and the probability of coherence actions due to false sharing is also reduced. A more recent implementation can be found in the Quarks system [SWA98].

Many of the messages that the ERC protocol sends are unnecessary. As we will see in Chapter 2, only the next process accessing the semaphore needs to apply coherence actions before entering the semaphore. In fact, it is not necessary to carry out the coherence actions until the next process accessing the semaphore is known. The Lazy Release Consistency (LRC) [KEL95] model exploits this idea. The first protocol implementing it was proposed

in the TreadMarks system [KEL94]. Other implementation can be found in [BIA96].

The most frequently used memory consistency protocol that implements the LRC model is called Home Lazy Release Consistency (HLRC) [ZHO96] protocol. The main difference between the Treadmarks LRC protocol and the HLRC protocol is that in the latter there is a home node for each page, which concentrates the modifications. In this way, when a process needs a copy of the updated page it only interrupts the home node (in the Treadmarks LRC protocol, multiple nodes can be interrupted). In addition, if the home node is chosen carefully it is possible to reduce the number of page faults, as it is continuously updated. Because of these advantages, some recent systems have implemented the HLRC protocol [STE00][BIL98], and for this reason it is used as the baseline protocol in this dissertation.

However, SVM systems are far from obtaining performances close to those reached by hardware based shared memory systems. The main reason is that the software characteristics of SVM systems interact adversely with the parallel workloads, thus reducing the performance [IFT96][JIA97][ZHO97]. This is because parallel workloads are usually optimized for hardware systems. In general, there is a performance loss if the workload has frequent synchronizations and the granularity of the shared data is small. Release memory consistency protocols generate coherence actions as a consequence of synchronizations and, as it has been already said, the coherence messages have high latencies in SVM systems. On the other hand, if the granularity of the shared data is small, false sharing and fragmentation occur and the number of required coherence actions increases. The HLRC protocol mitigates these problems, but introduces new ones:

- Readers interrupt writers asynchronously to update their data. The asynchronous communication is a critical factor in the performance of current SVM systems due to its high cost.

- The complexity of the release memory consistency protocols adds computing time to each message, thus increasing its latency.

- Release memory consistency protocols tend to arrange the coherence actions at synchronization points, causing contention points during the execution.

#### 1.3. Thesis Overview

This thesis focuses mainly on the problems of reducing both asynchronous communication traffic and latency. To mitigate these problems so improve the system performance, new and efficient protocols are suggested. The proposed protocols are based on the understanding of the main characteristics of the workload at runtime. The main contributions of the thesis are:

- Characterization of several parallel workloads from the SPLASH-2 suite [WOO95] in those aspects that can negatively impact the performance of SVM systems. The characterization quantifies the sources of performance loss by measuring three axes that are related to latency in asynchronous communication: frequency of sharing, granularity of sharing, and entropy in sharing patterns. The results illustrate the impact of the sharing granule size, quantifying the relationship between page size and fragmentation/false sharing. The effects of sampling across fixed intervals are also studied, showing how many applications exhibit distinct phases during execution. Some of the results found in those studies have been published in [PET02]. Others have been submitted and are pending revision [PET03].

- Implementation of a new simulation environment for SVM systems. The developed tool is an execution-driven simulator [PET00] aimed at studying the behavior of memory consistency models. This tool can take as input any of the SPLASH-2 benchmark suites or can use the real workloads. It simulates the detailed behavior of these systems, varying both memory consistency models and the local area network configuration.

- Design of two new SVM memory consistency protocols (HLRC-CU and HLRC-DU protocols) that use the results of the SPLASH-2 characterization to improve the baseline HLRC protocol. The HLRC-DU protocol is a pure software protocol while the HLRC-CU protocol uses a specific hardware table. Both protocols use a specific message (referred to as write update) to update written data, reducing asynchronous communication. The HLRC-CU protocol also reduces latency caused by multiple writer protocol overhead by focusing on those write operations that perform over small

continuous areas. The behavior of both protocols is also characterized in function of the maximum write update size. The characteristics of both protocols and studies of their performance metrics have been published in [PET01][PET01b].

This thesis has been structured in chapters as follows: Chapter 2 introduces SVM systems and describes an important subset of the memory consistency models and protocols found in the open literature. It also describes the latest contributions from recent research by explaining asynchronous communication design and implementation in SVM systems. Chapter 3 describes the LIDE simulation environment for SVM systems. Chapter 4 characterizes SPLASH-2 parallel workloads from the SVM point of view and discusses the main sources of performance loss in current SVM systems. Chapter 5 proposes two new consistency protocols designed from the results obtained in Chapter 4. The performance of the proposed protocols is compared with other classical solutions. Finally, Chapter 6 presents the most relevant conclusions of the thesis and the open research lines for future works.

# **Chapter 2**

### **Shared Virtual Memory Systems**

As we introduced in Chapter 1, SVM systems allow shared memory programming at a low design and maintenance cost due to their software implementation; nevertheless, as hardware implementations work faster, their performance are still far from that achieved by hardware based distributed shared memory (DSM) systems. Nowadays, SVM systems use relaxed memory consistency models and multiple writer protocols as techniques to reduce latencies and false sharing respectively; however, these techniques induce additional overheads that reduce performance. The four main characteristics that define the SVM systems are:

- Shared virtual address space: The processes access the same memory areas through logic memory addressing. This virtual address space is split up into pages. This relies on the same mechanism that allows several processes to share pages in single processor systems. However, in an SVM system each node has its own local physical memory. In other words, different nodes do not map their virtual addresses to the same physical memory. Thus, the OS needs to maintain the memory coherence among the local memories of the nodes.

- Page as sharing unit: The sharing unit of the system is the virtual memory page. Usually, the most commonly page size is used is 4 KB.

- Software maintained coherence: The OS updates or invalidates the non-coherent pages. Thus, coherent actions are usually performed by software.

- Heterogeneous interconnection network: Coherence actions can be performed

using message passing because the OS performs the coherence actions. This allows

a high degree of independence from the supporting hardware, as happens in

message passing parallel systems. In other words, the shared memory

programming paradigm is accomplished by a message passing architecture.

In this chapter a general overview of the SVM systems is presented. The remainder of the chapter is organized as follows. Section 2.1 describes a simple SVM system as an example to illustrate the characteristics mentioned and how they affect the design and implementation of this kind of systems, section 2.2 explains memory consistency models, in particular relaxed memory consistency models, section 2.3 discusses the memory consistency protocols implementing relaxed memory consistency models, section 2.4 details asynchronous communication in SVM systems. Finally, section 2.5 concludes with some remarks linking the different concepts introduced in this chapter.

### 2.1. A Simple SVM System Example

We use a simple example to show the main characteristics and the software nature of SVM systems. For the sake of simplicity, we suppose that the interconnection network is a bus for two main reasons: i) it is the simplest network topology and, ii) each node connected to the bus can snoop all the traffic on the bus, so monitoring all the transmitted messages.

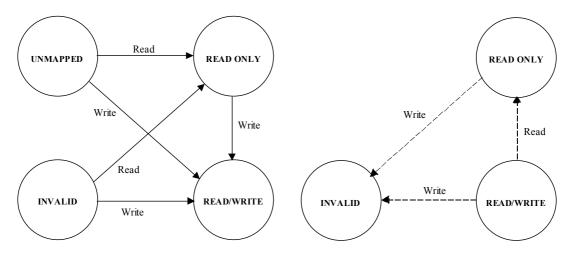

Let us assume that the pages in memory can be in three different states:

- *Invalid*: Any access to the page sends an interrupt to the local OS of the node. It is used for pages whose content has been invalidated by a previous writer.

- *Read-only*: Any write access to the page sends an interrupt to the local OS of the node. It is used in order to detect writings to the page.

- Read-write: Reads or writes to the page can be performed without interrupts. This

happens when a process of the node has performed at least one write to the page.

We assume that each node connected to the interconnection network can host one or several processes. As processes in a node share the same physical memory (for example, an SMP system), page states are set per node, instead of per process. This reduces memory overhead for storing page tables and allows local modifications in a node to be seen by all the local processes of the node without need of SVM coherence actions. An implementation of this technique can be found in [SAM98].

Whenever an interrupt is produced, the local OS of the interrupted node takes control and performs the corresponding coherence actions:

- If the page is invalid, it performs the necessary correspondent actions to make it coherent.

- If the page is read-only, the writing is detected, and an invalidation is generated for other remote processes sharing the page.

Initially, only the process 0 owns a copy of all the shared pages in read-write access mode. Let us assume that this process is running in node 0. All the other nodes do not have a mapped copy of the shared pages.

In the initial scenario, if a process in a node other than 0 (we can call it remote node) tries to read a page, the access will result in an unmapped page and it will generate an interrupt due to a page fault. Then, the local OS requires a copy of the page to the node that has the page in read-write access mode (in this case, node 0). When the update is accomplished, both node 0 and the node of the reader process will have a read-only copy of the page. This state is maintained in all the copies of the page while there are only reader processes.

When a remote process tries to write a shared page, it will have a page miss and will produce an interrupt. Then, the local OS requires a copy of the page to the node that has the page in the read-write access mode (in this case, node 0), then invalidates all the other node copies, and sets its copy to a read-write state. This node will serve future remote accesses to that page. Note that both nodes that have an invalid copy of the page and the node that

has the page in the read-write state are known by all the nodes, because we assume that all the nodes monitor the messages transmitted through the bus. In systems that do not broadcast the coherence actions, a directory of nodes sharing the page is needed. This directory can be maintained centralized or distributed.

Figure 1 shows the state transition diagram. This graphic summarizes how local and remote pages change their state due to read and write accesses to the page. The continuous arrows on the left represent state transitions due to local accesses; the dotted arrows on the right represent state transitions due to remote accesses. For example, a read-write to read-only transition is triggered by a remote read, and a local write triggers a read-only to a read-write transition, invalidating remote copies of the page.

- a) Transitions due to local accesses

- b) Transitions due to remote accesses

Figure 1 – State transition diagram of a page

Figure 2 shows the handler code of both page faults and remote message requests. Each page has an associated lock that assures atomicity for the code executed by the handlers between the processes running in a given node.

If a given process in a node N has a read page fault on page P, its OS will execute the *read* fault handler. This handler sends a message to the node that has a read-write copy of the page P ( $rw\_node$ ). On receiving this message, the  $rw\_node$  executes the read message handler, which returns an up-to-date copy of the page P to node N and sets its copy to the read-only state. The node N receives the up-to-date copy of page P and sets it to the read-

only state.

```

Read fault handler:

lock(page);

send(page.rw node, READ, page.address);

recv(page.address);

page.state = READ_ONLY;

unlock(page);

Read message handler:

lock(page);

reply(page.address);

page.state = READ ONLY;

unlock(page);

Write fault handler:

lock(page);

send(ALL, WRITE, page.address);

recv(page.address);

page.state = READ WRITE;

page.rw_node = this_node;

unlock(page);

Write message handler:

lock(page);

if (page.rw node == this node) then reply(page.address);

page.state = INVALID;

page.rw node = sender node;

unlock(page);

```

Figure 2 – OS interrupt handlers

If a given process in a node N has a write page fault on page P, its OS will execute the write fault handler. This handler broadcasts a message to all the nodes in the system, including the node that has a read-write copy of the page P ( $rw\_node$ ). On receiving this message, all nodes execute the write message handler, which sets their copies of the page P to the invalid state. Only the  $rw\_node$  returns an up-to-date copy of the page P to node N, which receives the copy and sets it to read-write state. Finally, all the nodes set the  $rw\_node$  of the page P to the node N.

From this example it is noticeable that the software nature of the protocol handlers (executed by the OS) and the large size of the coherence (a page) are the root of the main performance drawbacks that a simple system like the above described will suffer:

The example behaves similarly to an SMP snoopy cache invalidation protocol. This means that it will send a message each time a process in a node writes to a read-only page. As message latency is much higher in SVM systems than in SMP systems due to their software nature and the commodity network, the performance will decrease enormously. In addition, as a consequence of the big size of pages, the number of messages sent due to false sharing increases.

To solve these problems, the design and implementation focused on new relaxed memory consistency models, which are detailed in the next section.

### 2.2. Memory Consistency Models

Parallel programmers wish a shared memory system behavior that is formally defined by the memory consistency models (regardless of whether the system architecture is centralized or distributed). Intuitively, programmers assume the sequential memory consistency model (see section 2.2.2), which disables some optimizations that improve SVM performance. Although the first SVM proposal followed the sequential consistency model [LI\_86], it is not used in current implementations. The SVM systems focus on relaxed memory consistency models [IFT99] because these models enable to delay coherence actions, thus reducing the number of coherence messages, and so saving latency. In addition, these models allow the design of multiple writer protocols, which enormously reduce the number of messages sent due to false sharing.

There are two main concepts related with consistency models: the performing order and the fence. Both are described in the next following sections.

### 2.2.1. Performing Order

Memory consistency models define the order in which memory operations from one process can perform with regard to other processes.

#### Formally:

- A memory operation issued by a process *i performs* with regard to a process *j* when the result of the memory operation is visible by the process *j*.

- The *performing order* of a process i with regard to a process j is the order in which memory operations of process i perform with regard to process j.

Depending on the memory system, the performing order can be unique or dependent on *j*. For instance, in an SMP system all the processes see the same performing order because they all read the same information from the bus, which serializes shared memory operations. However, in a DSM system, different orders can be seen at different points of the interconnection network.

In a monoprocessor system, the performing order of memory operations is quite flexible and it can be easily reordered when it affects different addresses without violating the program semantics. This enables improvements in performance, for example, by adding write buffers and/or caches. However, reordering is less flexible when a parallel program is running in several processors, because it can violate the program semantics. Figure 3 shows an example of a code running in two different processors (A and B). The two instructions of processor A write different variables, so processor A does not need to monitor which instruction is performed first if the code is only running in one processor (there are not data dependencies). However, if this code is a fragment of a parallel program with the code of processor B, the order is important because the value assigned to the variable B in processor B depends on the *performing order* of processor A with regard to processor B.

| a=1;   | while (x==0) {}; |  |

|--------|------------------|--|

| x=1;   | b=a;             |  |

| A code | B code           |  |

Figure 3 – Code example running in two different processors

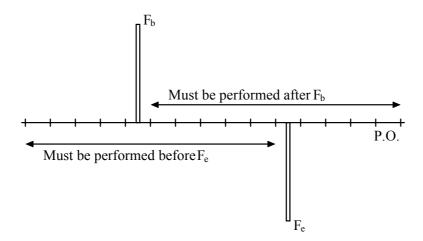

This example shows that to guarantee parallel program semantics, memory systems need to

restrict the order in which memory operations from a process can perform with regard to other processes. We define a *fence* as a new operation in the program flow that delimits the begin and/or the end of a possible area of reordering. In particular, we can distinguish two types, as shown in Figure 4:

- Begin Fence  $(F_b)$ : Ensures that all the operations issued by a process i that are located after the fence in program order, perform after the fence with regard to any process j.

- End Fence  $(F_e)$ : Ensures that all the operations issued by a process i that are located before the fence in program order, perform before the fence with regard to any process j.

Figure 4 – Begin fence  $(F_b)$  and end fence  $(F_e)$

Both types are not exclusive so the same point may act both as begin and end fence. We refer to such points as *total fence* or simply a *fence*.

Memory consistency models differ depending on what instructions set a fence in the parallel program execution and what is the type of that fence. Below, we describe the memory consistency models, from the most to the least restrictive.

## 2.2.2. Sequential Memory Consistency Model

Prohibiting changes in the performing order is the most straightforward manner to prevent semantic problems caused by reordering. This is accomplished by considering each memory operation as a total fence. This defines the *sequential memory consistency model* [LI\_86] where memory operations issued from a process perform with regard to any other processes in program order.

Formally, the condition for sequential consistency is:

A read, write, or synchronization operation can perform with regard to any other process if all previous reads, writes and synchronization operations have already been performed.

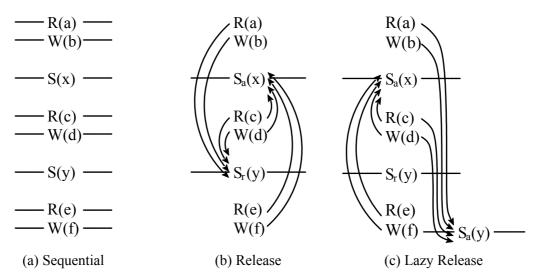

Figure 5(a) describes a possible sequence of memory operations issued by a parallel process. Each memory operation is issued to a different, unrelated memory address (a, b, c, d, e, f, x, and y). Under the sequential memory consistency model, reordering is not allowed and so the performing order matches the program order.

The main drawback of the sequential model is that it does not allow reordering. This implies that each memory operation has to wait that the previous instructions in program order have performed. In SVM systems, this restriction would force the transmission of a coherence message through the network each time a shared memory operation is issued, dramatically reducing the performance. Thus, the sequential memory consistency model is not implemented and some degree of reordering is allowed.

By allowing reordering the system cannot assure that the performing order matches the program order. Consequently, the semantics of a parallel program cannot depend on the program order of the memory operations. To solve this problem, the programmer uses synchronization operations (i.e., locks, unlocks and barriers) to impose order restrictions.

Figure 5 – Fences in memory consistency models

It can be shown that if the parallel workload is assumed to be *data-race-free* [ADV93] and *correctly labeled* [GHA90] by synchronization operations, the performing of the memory operations can be postponed to the next synchronization point in program order.

For example, we can specify that the synchronization operations execute in program-order, although memory operations located between such synchronization operations can be reordered. The systems working in this way follow relaxed memory consistency models [IFT99]. We can consider several models according to the level of relaxation. Below, the release and lazy release memory consistency models, which are the most commonly used in SVM systems, are described.

## 2.2.3. Release Memory Consistency Model

The *release memory consistency model* [GHA90] allows more reordering than the sequential model by using two types of synchronization operations: *acquire* and *release*. The former behave as begin fences, and the latter as end fences. In this manner, all the memory operations following an acquire operation in program order must perform after the acquire operation, and all the memory operations prior to a release operation in program order must perform before the release operation.

Under release consistency, acquire operations can be conveniently mapped to the lock

synchronization operation because a lock precludes the following operations being performed before the lock. Release operations are associated with the unlock synchronization operation, which means that when the process leaves the critical section all the previous writes have been performed. Acquire and release operations can also be mapped to other synchronization operations. In particular, barrier operations can be associated with an acquire and a release operation because writings prior to the barrier in program order are expected to perform before the barrier, and writings following the barrier in program order cannot perform before the barrier. In this manner, barriers still behave like total fences.

Formally, the conditions for release consistency are:

- A read or write can perform with regard to any other process if all previous acquires have already been performed.

- A release can perform with regard to any other process if all previous reads and writes have already been performed.

- Synchronization operations cannot be reordered.

Figure 5(b) shows how release consistency allows reordering. R(a) and W(b) can be reordered but they cannot perform after  $S_r(y)$  because it is a release operation (end fence). On the other hand, R(e) and W(f) cannot perform before  $S_a(x)$  because it is an acquire operation (begin fence). Finally, R(c) and W(d) have both reordering limits.

## 2.2.4. Lazy Release Memory Consistency Model

Applying release consistency, the parallel program shown in the previous example of Figure 3, must rely on synchronization primitives to share data. Figure 6 shows the new code.

| a=1;       | lock(x) |  |

|------------|---------|--|

| unlock(x); | b=a;    |  |

| A code     | B code  |  |

Figure 6 – Code example

Release consistency ensures that the write issued by A to variable a performs with regard to the process B before unlock(x). This condition is sufficient to make consistent the read of variable a by process B but it is not necessary. The necessary condition is that the write issued by A performs with regard to B before the lock(x) performs. Thus, the write issued by A only needs to perform with regard to process B, even if more processes exist. Thus, although the protocol had non-coherent data copies in different nodes of the system, it maintains the consistency. The model that permits this kind of reordering is called the lazy release memory consistency model [KEL95].

Formally, the conditions for lazy release consistency are:

- A read or a write can perform with regard to another process if all previous acquires have already been performed with regard to that process.

- A release can perform with regard to another process if all previous reads and writes have already been performed with regard to that process.

- Synchronization points cannot be reordered.

Figure 5(c) showed the possible reorderings under lazy release consistency. As release consistency, acquires behave as begin fences, so R(c), W(d), R(e), W(f) cannot perform before  $S_a(x)$ . The difference is that the performing of memory operations can be postponed until other process acquires the same synchronization variable than the following release in program order. In other words, the variable (y) used by the following release  $(S_r(y))$  can be acquired  $(S_a(y))$  by other process. In such a case, that acquire operation states the latest time a memory operation can be postponed until. When the acquire operation performs, previous writes must only perform with regard to the acquirer process.

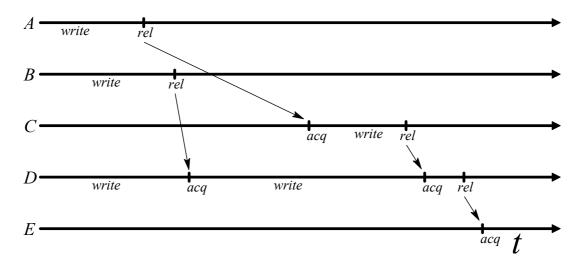

The memory operations that must perform with regard to a given acquirer are those occurring before following a specified order, called *happened-before* [KEL95]. This order marks as previous all the memory operations issued by the process that released the same semaphore or barrier before the current acquire. It also means (in a recursive way) the memory references performed by the processes releasing the semaphores or barriers accessed by the process that issued the last release. Figure 7 shows a hypothetical sequence of acquires and releases between different processes. According to the happened-before order all the writes in the figure occurred before process *E* executed the acquire.

Figure 7 – Happened-before order example

## 2.3. Multiple Writer Protocols

To enable the reordering of memory operations under the lazy release memory consistency model an important piece of research has focused on multiple writer protocols, which allow several writers on a page at the same time, hiding most of the false sharing effects. In general, multiple-writer protocols store and send page differences (also called *diffs*) instead of the whole page to detect which parts of a given page each node has written to. Below, we discuss some details of the implementation.

In the sequential memory consistency model shared pages only can be written at a given time by a single processor. In other words, write operations must be serialized between processors. Protocols working in this manner are called single writer protocols and they are the most intuitive way to guarantee the single and strict ordering of operations that the sequential model requires. Relaxed memory consistency models allow reordering of non-synchronization operations, which supposes different processors may see different orderings. Moreover, in the lazy release consistency model, write operations are not globally seen, so writers on the same page do not need to carry out coherence actions (for example, page invalidations) among them, allowing several writers to write simultaneously on different parts of the page.

False sharing was the main reason because SVM system designers introduced multiple writer protocols. Its impact on performance is higher in SVM systems than in hardware DSM systems, because in the former it is more probable that two or more processes write to the same coherence unit, because of the larger page size. When false sharing occurs in a single writer protocol the well-known *ping-pong* effect is produced, which is magnified in SVM systems because of their software nature and the high latencies of the commodity network. Multiple writer protocols reduce this problem.

The main problem to solve when designing multiple writer protocols is how to prevent local modifications of a given page from being overwritten by those page modifications of a concurrent remote writer. In other words, if process A modifies a piece of its local page copy, an update to the same page from other process B will overwrite the whole page, and so local modifications of process B are lost. To prevent this problem multiple writer protocols work as follows: i) the OS labels all the shared pages as read-only in order to detect the write operations; ii) when the underlying virtual memory system detects the first write to a page (due to a page fault), it creates a copy of the page before the write is done—referred to as a *twin*-, and marks the page as read-write; iii) then, if another node requires the page, the twin and the page are compared to obtain the differences between them. The comparison results are stored in a table, called diff; and, iv) only the diff is updated, instead of the whole page, so avoiding that remote updates overwrite local modifications.

Diffs enable multiple nodes to write in parallel to the same page so reducing write latency. In addition, the coherence actions do not apply immediately (as occurs in SMP systems), and memory operations can be postponed (as occurs in relaxed memory consistency

models). This fact implies that several coherence actions can be packed in just one message; thus, reducing the total number of coherence action messages.

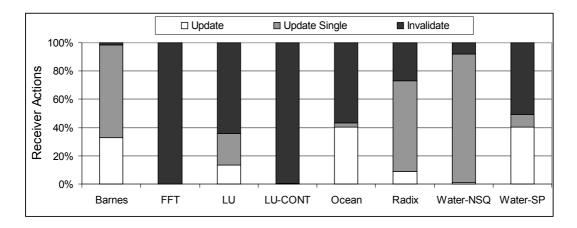

## 2.3.1. Invalidating versus Updating

Two kinds of multiple writer protocols are distinguishable depending on how they handle coherence actions: invalidation and update protocols. The relative performance of invalidation versus update protocols strongly depends on two important workload characteristics: the *granularity of sharing* and the *frequency of sharing*. These are explained below:

#### **Granularity of Sharing**

This characteristic quantifies the mean amount of data transferred when an update occurs. It is computed with regard to the granularity of the system (i.e., the page size, which is typically 4 or 8 Kbytes). The granularity of sharing is classified as *fine-grained* (FG) when only a few words (less than 30%) of the page are shared, *medium-grained* (MG) when at least 30% of the page is shared, and *coarse-grained* (CG) if more than 60% of the page is shared. The granularity of sharing can be further broken down depending on the type of memory operation performed on the shared data (i.e., *granularity of reading* and *granularity of writing*). Both granularities are commonly present in different sizes.

#### **Frequency of Sharing**

In SVM systems, coherence actions are carried out at synchronization points; therefore, the frequency of the synchronization operations matches the frequency of sharing. The frequency of sharing metric is calculated as the average computation time between two consecutive synchronization events [ZHO97]. We assume we are performing *fine-grained* synchronization (FGS) if the average computation time is close to the average synchronization time. Otherwise, we assume synchronization is *coarse-grained* (CGS).

The larger the granularity of sharing and frequency of sharing are, the larger the network utilization. When both are relatively large, the network saturates and becomes a congestion

point. This point establishes the performance border between invalidate and update protocols.

Update protocols usually achieve a better performance than invalidate protocols before the network saturates. When this occurs, their performance dramatically drops, offering poorer performance than invalidate protocols. That is because invalidate protocols generate less traffic and so they saturate the network later.

On the other hand, the performances of invalidate protocols in SVM systems are limited by the frequency of sharing. This happens because page requests must be performed using asynchronous communication in SVM systems, which has a high latency, and the number of page requests grows as the frequency of sharing increases. For this reason, in general, invalidate protocols offer worse performance than update protocols when the frequency of sharing is high.

The multiple writer protocols commonly used in SVM (with the exception of those needing additional hardware or compiler support) are: Eager Release Consistency (ERC) protocol, the Lazy Release Consistency (LRC) protocol and the Home Lazy Release Consistency (HLRC) protocol. The ERC protocol is implemented as an update protocol, while both LRC and HLRC protocols are usually implemented as invalidate protocols, although they can be implemented in either way.

## 2.3.2. Eager Release Consistency Protocol

The multiple writer protocol implementation of the release memory consistency model is known as ERC protocol. It is implemented by updating diffs in those nodes sharing the page when the release is executed. Typical implementations of this kind of protocol can be found in [CAR91] and [SWA98].

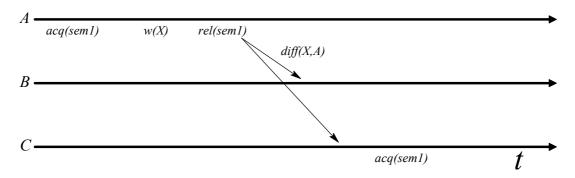

Figure 8 shows a working example of an ERC protocol. When a process in node A executes the release that frees the semaphore sem1, the OS of node A must calculate and send the diff(X,A) containing the writes performed in page X by the processes in node A. The diff must be sent before the release operation ends in order to be applied in those nodes sharing the page. In this way, when a process in a remote node acquires the semaphore sem1 it will

have the page updated.

Figure 8 – ERC protocol example

In the release memory consistency model, memory operations perform releases globally. Therefore, implementations of the ERC protocol allow multiple writers by using update operations. This means that the ERC protocol is very sensitive to the granularity of sharing, because it broadcasts all the previous writes at the release. The frequency of sharing also affects the number of broadcasts (one per release operation). Nevertheless, the ERC protocol has been used in recent pure software SVM implementations [SWA98] because the absence of invalidations reduces most asynchronous communication.

## 2.3.3. Lazy Release Consistency Protocol

The ERC protocol performs poorly when the broadcasts saturate the available network bandwidth. In this case, it is a better to relax the memory consistency model to allow point-to-point messages instead of broadcasting to carry out the coherence actions through the network. The LRC protocol [KEL94] (which implements the lazy release memory consistency model) applies the coherence actions just to those nodes accessing a semaphore or barrier, instead of broadcasting the coherence actions to the other nodes as the protocol ERC does.

As these coherence actions are only applied to a given node, invalidation protocols can be implemented allowing multiple writers because the rest of nodes in the network will not be affected by the action. In this context, the invalidation information is called *write notice*.

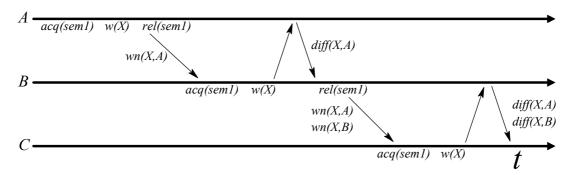

Figure 9 shows an example of an invalidate LRC protocol. The writes produced by

processes in nodes A and B to page X produce write notices (wn(X,A)) and wn(X,B). When a process in node B has a page miss, it receives the diff of page X from node A (diff(X,A)). So, when a process in node C has a page miss, it only needs to contact with node B to obtain the two diffs (diff(X,A)) and diff(X,B).

Figure 9 – LRC protocol example

It is not necessary to communicate all the previous write notices to the process acquiring the semaphore or barrier, but only those that have not been applied yet. The mechanism to know at the moment of the acquire operation which coherence actions have been applied and which must be applied is based on *intervals* and *timestamps vector*. Each time a process in a node executes an acquire operation or a release operation; the node increases its interval number. The timestamp vector contains the intervals of each node known to the node of the process that performs the acquire operation (through coherence actions). By comparing the timestamps with that of the node that performed the release, it is possible to know what coherence actions must be applied: those corresponding with the intervals unknown to the node that performs the acquire operation and known to the node that performed the previous release operation.

Table 1 shows an example of a node calculating the new vector timestamp when some of its processes execute an acquire operation. To handle the calculation, the node uses its current vector timestamp and the vector timestamp of the node of the last process that executed the corresponding release operation. The node that performs the acquire operation must apply all the coherence actions associated with the intervals of other nodes that are not in its vector timestamp, but are in the vector timestamp of the node that performed the

release. For example, if we consider A as the node acquiring a semaphore, it will apply the actions from the intervals 2 to 10 of B and the interval 12 of D. The intervals of C are not applied because A has applied more intervals than the node releasing the semaphore.

| Node | Release | Acquire |        |  |

|------|---------|---------|--------|--|

|      |         | After   | Before |  |

| A    | 0       | 5       | 6      |  |

| В    | 10      | 1       | 10     |  |

| С    | 7       | 9       | 9      |  |

| D    | 12      | 11      | 12     |  |

Table 1 – Vector timestamps calculation example

After applying the intervals, node A updates its own vector timestamp with the intervals applied and increases its own interval (from 5 to 6) because it has just finished the acquire operation.

When a node invalidates a page due to a write notice, it will obtain updates from the writers at the moment of a page miss. Because it is impossible to know the moment when the diffs will be needed, they must be stored until the moment they are applied in all the nodes. Generally, they are not stored indefinitely but they are broadcasted at the same time than barriers and later discarded.

The performance drops in the LRC protocol when there are many page faults, because the faulting node starts asynchronous communication sessions to fetch the corresponding diffs. Asynchronous communication has a high operational cost in SVM systems, because it adds latency to the update fetch. Thus, given sufficient bandwidth, the frequency of sharing is a key performance factor even more important than the granularity of sharing in invalidation based LRC protocols.

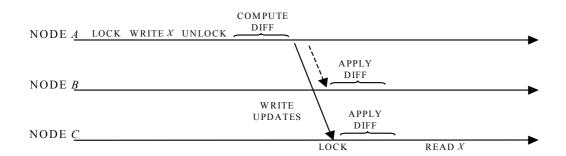

## 2.3.4. Home Lazy Release Consistency Protocol

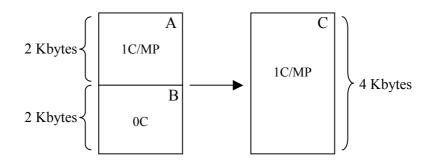

The HLRC protocol [ZHO96], like previous protocols, implements the lazy release memory consistency model. In this protocol each page has associated a *home* node that concentrates all the diffs. When a node writes in a page, it supplies the diffs only to the home node. Then, diffs can be removed from the writing node. The remaining nodes invalidate the page by applying write notices following the same happened-before order as the LRC protocols.

In the case of a page miss, due to write notices, the OS of the faulting node asks the home node for an updated page. Because of network delays, the needed diffs may have not yet arrived at the home node. In this case, the request is queued until the diffs arrive. Vector timestamps are used to discover if the page of the home node is sufficiently updated. The vector timestamp associated with a page encodes the number of intervals updated by each node.

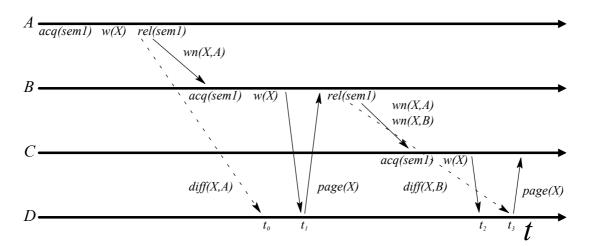

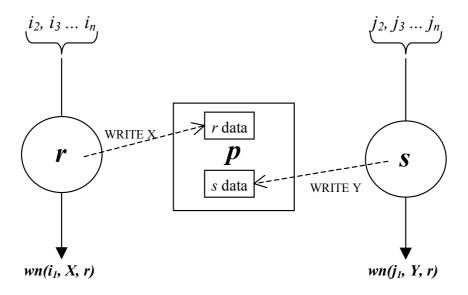

Figure 10 shows a write sequence equivalent to that of Figure 9 but following an HLRC protocol. The diffs generated by nodes A and B are gathered by node D because it is the home node of page X. Write notices are distributed in the same way than in the LRC protocol. As nodes B and C have their page invalidated by the write notices (wn(X,A)) and wn(X,B) respectively) they ask the home node for an updated page version. The request message of node B arrives  $(t_1)$  after the diff of the node A  $(t_0)$  therefore the OS of node D can immediately satisfy the request. But, the request from node C  $(t_2)$  must wait to be satisfied until the diff of B arrives  $(t_3)$ .

Processes running in the home node of a page never have a fault for that page, because they always have the page updated by diffs produced by remote writers. Thus, if the home is properly chosen (for example, by profiling), asynchronous communication is reduced. This fact mitigates the importance of the frequency of sharing. The granularity of sharing is not as important as under the ERC protocol because writers only update the home. For this reason, HLRC multiple writer protocols are the most used in SVM system implementations.

Figure 10 – HLRC protocol example

Recent research in SVM systems has attempted to further reduce the impact of asynchronous communication in SVM systems, which is a key factor in improving their performance and one of the most problematic points in their design. The next section explains asynchronous communication, detailing the most recent research in this area.

## 2.4. Asynchronous Communication

Most current parallel workloads have been optimized to run on distributed hardware systems (e.g., symmetric multiprocessors) or supercomputers. SVM systems lack hardware support for a lot of tasks supported by these hardware systems. This lack is the reason why SVM systems can experience performance losses and why they must be implemented using asynchronous communication [BIL98].

Basically, in all asynchronous communication, a *client* node initiates a request and a *server* node services the request. For example, the client node can require the server node to read a given page or to lock a given semaphore. Then, the server node is interrupted to service the request. This asynchronous communication involves a context switch in the server node, which introduces both high service latencies and overhead in the server. This implies a high operational cost that produces high service latencies and wastes precious computing time in the server [BIA96].

An important piece of recent research in SVM systems is aimed at reducing asynchronous communication by several methods. Some mechanisms include hardware support that partially, or totally, avoids this kind of communication [BIA96][BIL98][BLU98][STE00]. Others try to reduce this communication, or hide its latency using software techniques [BIL97][SPE98][SWA98].

The section below discusses asynchronous communication implementation in SVM systems, as well as the kinds of asynchronous communication that can be found in the design of a memory consistency protocol. We also analyze and discuss some techniques used to reduce the impact on performance for each particular kind.

## 2.4.1. Asynchronous Communication Implementation

Asynchronous communication can be implemented by using polling or interrupt techniques. Polling periodically wastes some processor cycles (usually, close to 10) when checking if there are new messages to serve. However, the service time of polling techniques is much lower (several orders of magnitudes [ZHO97]) than that offered by interrupts. Therefore, in general, polling is preferable. On the other hand, processor cycles are spent in polling whatever the communication is. Consequently, if there is little communication, interrupt techniques are preferable.

The use of interrupts or polling depends on the OS the nodes are executing. The Brazos system [SPE98] uses the Windows NT operating system, which incurs too much overhead dealing with interrupts. To solve this problem, Brazos (designed using multithreading) dedicates one thread to poll the requests. On the other hand, systems like Quarks [SWA98], implemented under UNIX, are based in interrupts. These systems often enter in busy waiting mode when the node is blocked waiting an answer from other node. If the nodes are multiprocessors, this technique is more effective, because it is more likely to find a blocked processor than it is in single processor nodes [KAR96].

In general, in multiprocessor nodes, only one processor serves asynchronous communication. When using interrupts, the balancing of this overhead, for example by using a round-robin scheme, can incur longer interrupt service times [BIL97]. If the system uses polling it is sufficient that one process in the node deals with this overhead

[SAM98][STE97].

## 2.4.2. Types of Asynchronous Requests

In the SVM protocols, there are several kinds of client requests that produce asynchronous communication. A possible classification is: data request, data receive, semaphore request, and barrier request.

#### **Data Request**

Data requests need to be served with a high priority. They appear in protocols that use invalidations as coherence actions. When a client node tries to access an invalid page, it starts an asynchronous communication with the server to fetch the data. In HLRC based protocols the server answers submitting the whole page while the action the server performs on LRC based protocols as a response is to submit the correspondent diffs.

Software techniques update the data avoiding the consequent asynchronous request. The Quarks system [SWA98] uses an ERC update protocol, but most cases use a hybrid protocol that behaves like an invalidation protocol, switching to an update policy when certain conditions occur. The Brazos system [SPE98] uses multicast to update other nodes in the copyset of the page if they have a data request for the same page, as well as to update predicted clients before they leave the barriers. Stets *et al.* [STE00] measure the performance of a multicast protocol based on a history record, but with hardware support.

The hardware techniques can update the data like the software techniques or can serve data requests automatically without processor intervention [BIA96][BIL98]. In [BIA96], a hardware support for an LRC based protocol that serves data requests is proposed, but the processor is still interrupted to perform metadata maintenance tasks of the data structures related to intervals. In [BIL98] the NI processor of the Myrinet is used to serve pages automatically in a HLRC based protocol.

#### **Data Receive**

As mentioned in section 2.3.1, some protocols update data in order to avoid data requests. In a data receive request, a client produces the data and pushes it into a repository server

(for example, the home of the page), producing asynchronous communication.

This asynchronous communication can be easily removed by software. Swanson *et al.* [SWA98] proposed a remote deposit mechanism based on low latency software messages. This mechanism can be also implemented by hardware [BLU98][BIL98][STE00]. Software implementation leaves the data in a low priority queue, that is later checked by the server but hardware mechanisms go a step further, allowing data updates directly in memory.

#### **Semaphore Request**

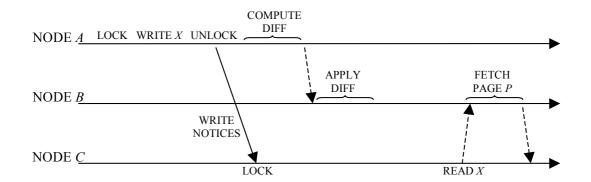

SVM semaphores are implemented by mapping lock and unlock calls to message requests. Because they have high priority, a semaphore request must be served as soon as it arrives at the server. In SVM systems, each semaphore has a *home* node, which maintains a queue of semaphore requests. The *home* also forwards lock requests between nodes to maintain a distributed list of semaphore requesters. An unlock request is performed without home intervention using this distributed list.

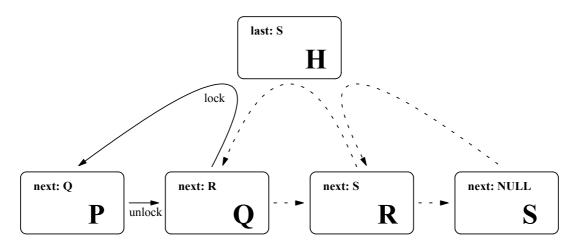

SVM semaphores work as shown in Figure 11. Semaphores are managed in a FIFO distributed queue. Each node in the queue points to, by means of a *next* field, the following node that requests the semaphore. To do this, a node sends a *lock* message (arc solid line) to the *home* of the semaphore (node H), which redirects it to the last queued node (node P). This node will update its *next* field to point to the new requester (node Q). When a node releases the semaphore, it leaves the queue and grants the semaphore to the node pointed to by its *next* field by sending an *unlock* message (straight solid line). Following requesters (nodes Q, R, and S) will follow the same rules (dotted lines).

Relaxed memory consistency models together with multiple writer protocols increase the service latency of semaphore requests. The overhead includes the maintenance of interval lists and write notices, as well as diff calculation if the protocol starts some automatic update at synchronization points (as occurs in ERC and HLRC based protocols).

There are software techniques that try to reduce the impact of this overhead. Some models such as [STE00] and [BIL98] broadcast the write notices as soon as they are generated, uncoupling their transmission from the synchronization. This technique is effective due to the low bandwidth cost the write notices have. Although in both cases hardware is used to

broadcast (remote deposit) the write notices, it is possible to do the same using software as is performed in [SWA98]. If the protocol updates the data at synchronization points (updating the home as in HLRC, or broadcasting the modifications as in ERC), the overhead is avoided by updating the data after the semaphore release [BIL97]. In [SWA98], data updates are also performed in semaphore acquire operations, overlapping the updates with semaphore waiting time.

Figure 11 – SVM semaphore management example

Hardware support can automatically serve the semaphore. This can be implemented in different ways. For example, in [BIL98] the Myrinet NI serves the semaphore following the mapping of semaphores over the message passing scheme shown in Figure 11. Stets *et al.* [STE00] use the total ordering capabilities of the network to implement spinlocks.

#### **Barrier Request**

Barrier requests do not have priorities as high as semaphore requests because they require all the nodes of the system to be involved in the communication. Thus, there is no need to start any asynchronous communication each time a barrier request is received. This can be done without additional hardware [BIL97]. When the server enters the barrier, it checks the incoming message queue. If it has a request from each node in the system, the server releases it. Otherwise, it polls for the barrier requests of the missing nodes.

#### 2.5. Conclusions