# **Coupling of a Powerline Communication Modem to an Industrial Fieldbus Network**

Jose Puche Planells

Supervisor: Dipl. –Ing. Joao Daniel Lopes

Universität Stuttgart

Institut für Steuerungstechnik der Werkzeugmaschinen und

Fertigungseinrichtungen

Prof. Dr.-Ing. Dr. h.c. mult. Alexander Verl

June 2014

# Acknowledgment

I would like to give special thanks to the entire institute for supporting this project during this time and especially to my supervisor Joao Daniel Lopes who always trusted me and from who I have learnt a lot. I would want also to thank to my mother and my closer family, which always are supporting me and are always aware of me. To my girlfriend Patri, who always has been there supporting me and cheering me up in the bad moments. Finally I want to thank to all my friends. Especially all these friends that I have made during the last 18 months in Stuttgart and with I have spent such incredible moments.

# **Table of Contents**

| 1. Motivation                                                        | 11       |

|----------------------------------------------------------------------|----------|

| 2. Industrial Communication Levels and Requirements                  | 13       |

| 3. State of the art                                                  | 15       |

| 3.1. Commercial Powerline Communication.                             | 15       |

| 3.1.1. Main issues with Powerline                                    |          |

| 3.1.2. Commercial Ethernet Powerline in the industrial communication |          |

| 3.1.3. Benefits of Powerline Communication?                          |          |

| 3.2. Developed Industrial Powerline Communication.                   |          |

| •                                                                    |          |

| 4. Design concept                                                    | 17       |

| 4.1. FPGA-based OFDM Modem                                           |          |

| 4.1.1. Orthogonal Frequency Division Multiplexing                    | 17       |

| 4.1.2. FPGA-based Powerline Modem                                    |          |

| 4.2. Hardware Design                                                 | 20       |

| 4.2.1. FPGA                                                          | 20       |

| 4.2.2. Analog-to-Digital and Digital-to-Analog Transceiver Boards    | 23       |

| 4.2.3. High Frequency Modulation Boards                              |          |

| 4.2.4. Coupling/Decoupling Circuitry                                 |          |

| 4.3. Software Design                                                 |          |

| 4.3.1. FPGA-Based Transceiver Program Structure                      |          |

| 4.3.1.1. Theoretical Introduction                                    |          |

| 4.3.1.2. Data Source                                                 |          |

| 4.3.1.3. Cyclic Redundancy Check                                     | 37       |

| 4.3.1.4. Convolutional Encoding                                      |          |

| 4.3.1.5. Interleaver                                                 |          |

| 4.3.1.6. Modulation                                                  |          |

| 4.3.1.7. Zero Padding                                                |          |

| 4.3.1.8. Fast Fourier Transform                                      |          |

| 4.3.1.9. Preamble and Prefix                                         |          |

| 4.3.1.10. Receiver Synchronisation                                   |          |

| 4.4. Ethernet POWERLINK and B&R System                               |          |

| 4.4.1. Ethernet                                                      |          |

| 4.4.2. Protocol Description                                          |          |

| 4.4.2.1. POWERLINK v1 vs. POWERLINK v2                               |          |

| 4.4.3. B&R System Description                                        |          |

| 4.4.3.1. Hardware topology                                           |          |

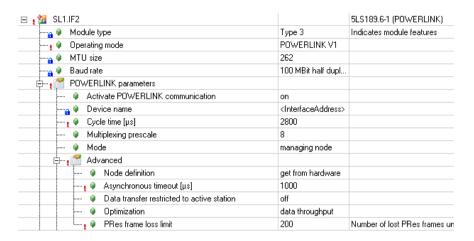

| 4.4.4. Real-Time System Configuration                                |          |

| 4.4.4.1. Network Configuration                                       |          |

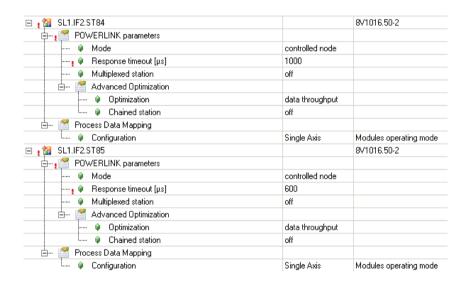

| 4.4.4.2. Ethernet POWERLINK Parameters                               |          |

|                                                                      |          |

| 5. Ethernet POWERLINK over Powerline                                 |          |

| 5.1. Ethernet and Media Independent Interface                        |          |

| 5.2. Coupling Principle                                              |          |

| 5.3. Software Designs                                                |          |

| 5.3.1. Ethernet Coupling Design                                      |          |

| 5.3.1.1. Receiver_ethernet block                                     |          |

| 5.3.1.2. Transmitter_ethernet block                                  |          |

| 5.3.2. Additional Designs                                            |          |

| 5.3.2.1. Latency Measurement                                         |          |

| 5.3.2.2. Data Rate Measurement                                       |          |

| 5.4. System Implementation                                           | 56<br>56 |

| 1/1   30HW/HP                                                        | าก       |

| 5.4.1.1. Migrating and Merging          | 56 |

|-----------------------------------------|----|

| 5.4.1.2. Ethernet Coupling              |    |

| 5.4.2. Hardware                         | 62 |

| 5.4.2.1. Channel Response               | 62 |

| 5.4.2.2. Baseband Analysis              | 62 |

| 5.4.2.3. Channel Access Management      | 64 |

| 5.4.2.4. Fine Tuning                    | 71 |

| 6. Results and Discussions              | 75 |

| 6.1. Signal-to-Noise Ratio Measurements |    |

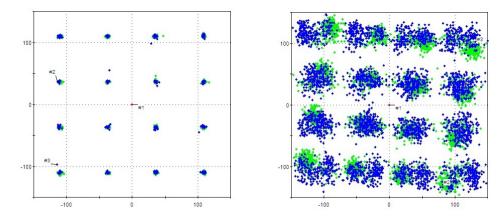

| 6.2. Constellations                     | 76 |

| 6.3. Latency Measurements               |    |

| 6.4. Ethernet Connection Analysis       |    |

| 6.4.1. Ethernet POWERLINK Runtime       |    |

| 7. Conclusions and Further Development  | 83 |

| 8. Bibliography and References          | 85 |

# **Table of Figures**

| Figure 1: Industrial Communication levels             |    |

|-------------------------------------------------------|----|

| Figure 2: Commercial Powerline Systems                | 15 |

| Figure 3: dSpace Communication over Industrial PLC    | 16 |

| Figure 4: FDM vs. OFDM                                | 18 |

| Figure 5: OFDM Transmitter                            | 19 |

| Figure 6: OFDM Receiver                               | 19 |

| Figure 7: Transceiver Stages                          | 20 |

| Figure 8: Terasic DE2-115 Development Board           | 21 |

| Figure 9: DE2-115 Features                            | 21 |

| Figure 10: Altera Cyclone IV Features                 | 22 |

| Figure 11: Marvell 88E1111 Ethernet Controller        | 22 |

| Figure 12: HSMC                                       | 23 |

| Figure 13: Transceiver Board                          | 24 |

| Figure 14: High Frequency Board                       | 26 |

| Figure 15: Transceiver Stages                         | 28 |

| Figure 16: Non-Inverter and Inverter Configurations   | 28 |

| Figure 17: Coupling Board Design                      |    |

| Figure 18: Coupling Stages                            |    |

| Figure 19: LC Resonator                               |    |

| Figure 20: Schottky Diodes Circuit                    |    |

| Figure 21: Transmitter and Receiver Blocks            |    |

| Figure 22: Transceiver Software Stages                |    |

| Figure 23: BPSK vs. 16QAM Bits                        |    |

| Figure 24: BPSK vs. 16QAM Effective Data              |    |

| Figure 25: BPSK vs. 16QAM Sampling Rate               |    |

| Figure 26: BPSK vs. 16QAM Data Frequency              |    |

| Figure 27: Without Interleaving vs. with Interleaving |    |

| Figure 28: BPSK vs. 16QAM constellation               |    |

| Figure 29: Binary vs. Gray                            |    |

| Figure 30: Ideal filtering                            |    |

| Figure 31: Real filtering                             |    |

| Figure 32: Periodic signal representation             |    |

| Figure 33: Zero Padding "in the Middle"               | 42 |

| Figure 34: 8-Point FFT.                               |    |

| Figure 35: Ethernet frame                             |    |

| Figure 36: Network topologies                         | 45 |

| Figure 37: POWERLINK v1 cycle                         |    |

| Figure 38: POWERLINK v2 cycle                         |    |

| Figure 39: B&R system                                 |    |

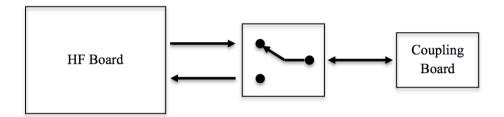

| Figure 40: POWERLINK over Powerline implementation    |    |

| Figure 41: MII Board configuration                    |    |

| Figure 42: Transmitter Ethernet signals               |    |

| Figure 43: Receiver Ethernet signals                  |    |

| Figure 44: Receiver ethernet block                    |    |

| Figure 45: Transmitter ethernet block                 |    |

| Figure 46: Ethernet Data storage stage                |    |

| Figure 47: Ethernet Data Treatment Stage              |    |

| Figure 48: Ethernet Data                              |    |

| Figure 49: OFDM Transmission packet.                  |    |

| Figure 50: Word Stuffing                              |    |

| Figure 51: Channel Response                           |    |

| Figure 52: Evaluation board                           |    |

| 4.7                                                   |    |

| Figure 53: Receiver amplification stage                         | 63 |

|-----------------------------------------------------------------|----|

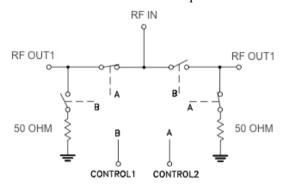

| Figure 54: ADP-2-1 electrical schematic                         |    |

| Figure 55: Coupling board with ADP-2-1                          | 66 |

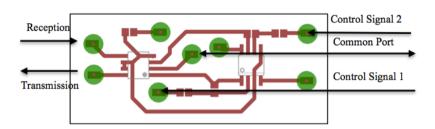

| Figure 56: Direction switching block                            | 66 |

| Figure 57: MSWA-2-20 electrical schematic                       | 67 |

| Figure 58: Output selection logic                               | 67 |

| Figure 59: LM258 Pulse Response                                 | 68 |

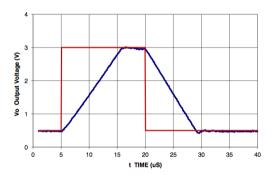

| Figure 60: TLC072A Pulse Response                               | 69 |

| Figure 61: Switching board                                      | 69 |

| Figure 62: Coupling Board one port                              | 70 |

| Figure 63: New coupling schematic                               | 70 |

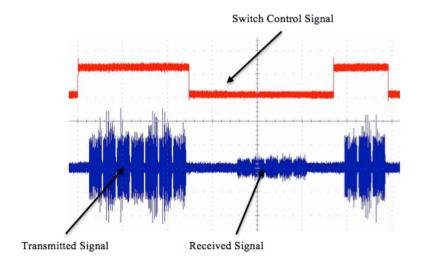

| Figure 64: Switch Control signal vs. Data signal                | 70 |

| Figure 65: Transmitter stages                                   | 71 |

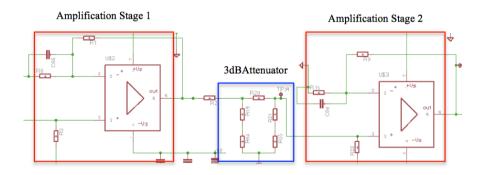

| Figure 66: Transmitter Amplification stages configuration       | 71 |

| Figure 67: Transmission gains                                   |    |

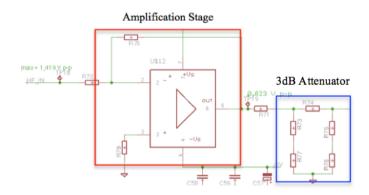

| Figure 68: Receiver stages                                      | 72 |

| Figure 69: Receiver Amplification stage configuration           | 72 |

| Figure 70: Reception gains                                      | 73 |

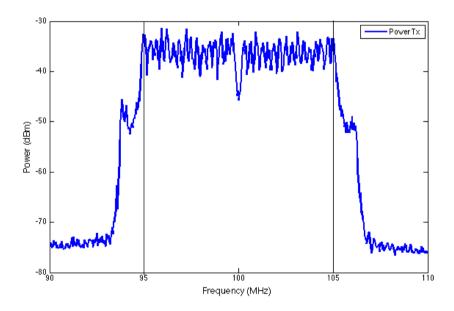

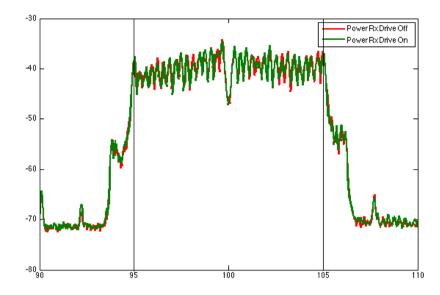

| Figure 71: Signal-To-Noise Ratio at transmission                | 75 |

| Figure 72: Signal-to-Noise Ratio at reception                   |    |

| Figure 73: Transmitted Constellation vs. Received Constellation | 77 |

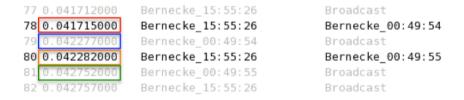

| Figure 74: Wireshark Capture - POWERLINK cycle                  | 78 |

| Figure 75: Wireshark Capture - POWERLINK flow graph             | 79 |

| Figure 76: Ethernet POWERLINK analysis                          |    |

| Figure 77: Managing Node Ethernet information                   |    |

| Figure 78: Controlled Node Ethernet information                 |    |

| Figure 79: PReq Frame Data                                      |    |

| Figure 80: PRes Frame Data                                      |    |

| Figure 81: Managing Node configuration                          |    |

| Figure 82: Controlled Node configuration                        |    |

|                                                                 |    |

## 1. Motivation

In a broad and heterogeneous industrial communications environment, the need of having flexibility as well as maintaining the reliability and low cost has pushed the researchers to look for new possibilities and market opportunities to cover all the needs. Actual industrial systems are needed of at least two ways of inputs: power input, for the system operation, and data input for controlling, testing and administrating the system. The main restrictions, that actual systems and networks have, are low flexibility and, sometimes, considerable expenses in terms on maintenance. But also they have advantages, e.g. low response time, high reliability, wide and highly known architecture etc. In this background, grows the thought of increasing the flexibility without impacting such important aspects as response time or reliability.

On the industrial communication protocols, Ethernet POWERLINK standard is one of the existing protocols in the market. Ethernet POWERLINK is a real-time industrial communication protocol based on Ethernet standard, which is used for controlling and commanding several sensors and actuators with high speed, time-synchronization and reliability, minimizing the global system latency.

The main aim of this project is to reach a balanced solution by joining both power and data inputs in just one cable that allows an increase in the flexibility, as well as decrease in the maintenance costs, restraining the response time and achieving compatibility with a wide spread standard as is Ethernet.

# 2. Industrial Communication Levels and Requirements

In the industrial environment, there are different communication levels to cover all the needs at different hierarchy levels.

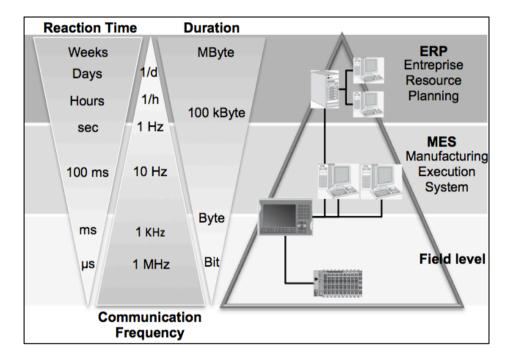

Figure 1: Industrial Communication levels

On top level, the Enterprise Resource Planning (ERP) concerns with the production planning, material management and quality management, having high reaction times and requiring high loads of data to be managed.

The next level is the Manufacturing Execution System (MES), which deals with the control and coordination of the industrial functions.

The low-end level is the Field Level, where industrial fieldbus communication takes place. Here is included the connection between sensors, actuators and Programmable Logic Controllers (PLC), which exchange lower amount of information but presenting a lower reaction time and thus, higher work frequencies.

The levels ate characterized with varying reaction time, jitter and data rates. From the general perspective, the reaction time, jitter and the size of the data decreases as the levels are descended. In the lowest level -the field level- the unwanted jitter leads to a varying cycle time. This is crucial in determining the real time capability parameter of the communication system.

The main parameters for industrial field level are defined following the next requirements:

Data Rate > 10Mbit/sLower Cycle Time: 10 ms

- Jitter: 10 μs

## 3. State of the art

#### 3.1. Commercial Powerline Communication

There are commercially extended Powerline Communication systems, which are applicable to domestic uses (LAN topologies for non-critical data transmission) and achieve enough data transmission rates for common tasks (Fast-Ethernet). The most widely deployed Powerline networking standard is from the HomePlug Powerline Alliance, whose specifications were adopted by the IEEE 1901 group as baseline for their standard [1].

Figure 2: Commercial Powerline Systems

#### 3.1.1. Main issues with Powerline

- 1. The power line is an analog channel, which means that the information must be modulated in order to achieve high data bit rates.

- 2. The power line is a noisy channel with high level of external disturbances coming from all the devices surrounding it. It is not prepared to protect the signal away from the electromagnetic interferences. Hence, the data cannot be transmitted easily with an acceptable Bit Error Rate. This problem is even more pronounced when the data is modulated.

These two issues force to protect the transmission channel by introducing data codification, interleaving and other error detection and correction techniques.

# 3.1.2. Commercial Ethernet Powerline in the industrial communication

As described before, in the field level communication, de reaction times are between the millisecond and the microsecond levels, keeping the jitter lower than 10  $\mu$ s. Moreover, the needed data rate must be at least 10Mbit/s.

Although the commercial Powerline Communication systems achieve higher data transfer rates (higher than Fast-Ethernet in some cases), the achieved latency, jitter and cycle times are not enough small to be applicable for most industrial communications, where the real-time data transmission is essential.

#### 3.1.3. Benefits of Powerline Communication?

The main benefit is the flexibility. With Powerline Communication the communication network can be established between two far away points (e.g. in large assembly lines) without need of extra cables, only the power supply cables. The robustness of the power line cables is also higher than conventional communication cables, which, on industrial environment, is a factor to take into account.

# 3.2. Developed Industrial Powerline Communication

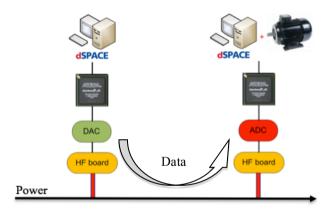

The basis of this project was the implementation of a Powerline Communication system to command a drive through a dSpace Controller board, the DS1103 and two developed Powerline modems.

Figure 3: dSpace Communication over Industrial PLC

These Powerline modems were based on a DBF3C120 board with a FPGA Altera Cyclone III integrated, a transceiver board with analog-to-digital and digital-to-analog (DAC and ADC) converters and a high frequency board (HF board). This communication was unidirectional, i.e. the communication was only to command the drive but not to read any information from it. This implementation presents a limitation; it can only be used with a dSpace system, which is not an industrial communication standard [2].

# 4. Design concept

In this chapter the concept of the existing Industrial Powerline Communications modem as well as the target system will be explained. Here are included, the hardware, the software, the Ethernet POWERLINK protocol and the B&R System descriptions.

#### 4.1. FPGA-based OFDM Modem

Transmitting digital data through a conventional DC cable, where different signals at different frequencies and voltages are being also transmitted, is more difficult than transmitting through an Ethernet cable. The data must be processed in order to avoid mixing it with unwanted signals.

To process the digital information on an analog carrier signal, an Orthogonal Frequency Division Multiplexing (OFDM) with modulation in amplitude modem is designed. The result signal can be further transmitted easily through different communication channels, e.g. cable, air, fiber, or in the project case, a DC cable.

### 4.1.1. Orthogonal Frequency Division Multiplexing

Orthogonal Frequency Division Multiplexing is a technique for multiplexing several signals into one channel, which means, sending several signals at the same time each one in a different frequency. Its main principle is grounded in the Frequency Division Multiplexing techniques (FDM) but with the objective of the efficient use of the available spectrum for transmitting multiple subcarrier frequencies.

With FDM several signals (or subcarriers) with a determined bandwidth and in a determined central frequency are transmitted. Both bandwidth and central frequency are chosen specifically for the transmission channel. FDM techniques are designed to divide the available spectrum in smaller frequency signals instead of transmitting a unique wide bandwidth signal. With this technique it is possible to adapt the signal to the transmission channel, compared with a single carrier method, by equalizing the different signals to the channel response. That means transmitting each subcarrier with slightly different characteristics to adapt it to the frequency that is going to be transmitted through. To this purpose, it is needed a previous channel estimation.

The OFDM is a concrete case of FDM, with better usage of the available bandwidth. This better usage will allow more subcarriers in the same bandwidth to be transmitted, and thus, higher data rate. The main difference with the FDM is that the frequencies that are used for multiplexing the different signals are closer, achieving a higher spectral efficiency of the available bandwidth. This is achieved thanks to the orthogonality of the transmitted subcarriers. As a result the crosstalk between subcarriers is theoretically eliminated and the inter-carrier guard band is in not required.

The orthogonality requires a minimum spacing between two consecutive subcarriers of

$$\Delta f = \frac{1}{T} Hz \tag{1}$$

Where T is the symbol duration. Therefore, with N subcarriers, the total bandwidth will be

$$BW = N \times \Delta f \tag{2}$$

In the case of FDM technique, is needed a spacing of

$$\Delta f = \frac{2}{T} Hz \tag{3}$$

Therefore the subcarriers are not orthogonal to each other and a guard band is needed to avoid channel crosstalk. The total bandwidth needed to transmit the same amount of subcarriers is then twice as with the OFDM. The total bandwidth for the project is set to 10 MHz and the number of OFDM subcarriers is set to 32. This means that each subcarrier must have a bandwidth of

$$\Delta f = \frac{B}{N} = \frac{10 \, MHz}{32} = 312.5 \, KHz \tag{4}$$

$$T_{symbol} = \frac{1}{\Delta f} = 3.2 \,\mu s \tag{5}$$

In band base, the total bandwidth of 10MHz signal is generated in two 5 MHz channels. These are In-Phase channel and In-Quadrature channel. After generating these two signals, a signal modulator modulates both signals in Quadrature at the defined carrier frequency of 100 MHz.

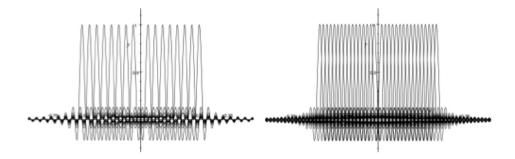

In the next pictures both FDM and OFDM in band base are depicted. It is clear the difference in terms of subcarriers for a given bandwidth.

Figure 4: FDM vs. OFDM

In left picture, a FDM multiplexing scheme is used, and for a given bandwidth of 10 MHz (from -5 to +5 MHz), 16 subcarriers are transmitted. In the right picture, an OFDM multiplexing scheme is used and for the same bandwidth, 32 subcarriers are transmitted because the separation between them is reduced to the half.

In terms of digital signal codification, first the Binary Phase Shift Keying (BPSK) modulation was implemented. To achieve more efficient data transmission, and thus a higher data rate, a 16-Quadrature Amplitude Modulation (16-QAM) was finally implemented.

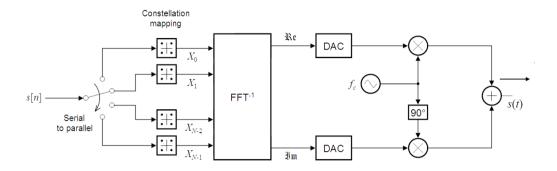

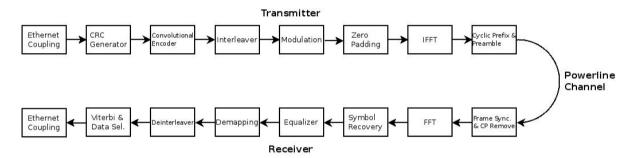

The following schematics offer an overview of the system:

Figure 5: OFDM Transmitter

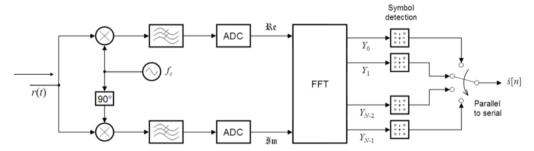

Figure 6: OFDM Receiver

Where the constellation mapping generates the BPSK or 16QAM symbols, the  $FFT^{-1}$  and FFT blocks indicate the Inverse Fast Fourier Transform and Fast Fourier Transform, essential blocks for the OFDM,  $f_c$  indicates the carrier center frequency of 100MHz, and s(t) and r(t) represent sent signal and received signal respectively [3].

#### 4.1.2. FPGA-based Powerline Modem

To implement the described characteristics, a device that has the capabilities of digital signal processing is needed. For this purpose a Field Programmable Gate Arrays (FPGA) system was chosen.

An FPGA is an integrated circuit built with logic blocks that can be programmed by a designer for a desired functionality. This kind of devices is called Programmable Logic Devices (PLD), and unlike the Relay Logic Devices, which once that is implemented cannot be changed, PLDs allow that changes can be easily made. These devices are perfect for implementation of new features and make the tasks of developing, debugging and updating easier. Furthermore, the provided development boards included several ports which are needed for the implementation, e.g. Ethernet port, HSMC port as well as switches, LEDs,

LCD display etc. Everything together makes the FPGA development board the perfect choice for the purpose [4].

For the implementation of the hardware, a Hardware Description Language (HDL), and a development environment must be used. In the project the VHDL language and the Altera Quartus II environment are used. Altera offers a complete solution to design, program and optimize the desired system.

In the design process, an Altera's offered solution plays an important role, the Altera MegaCore IP Library. The IP (Intellectual Property) Cores are blocks previously designed to implement complex functions in an easier way, e.g. Cyclic Redundancy Check (generator and checker), Triple-Speed Ethernet with MAC support, Viterbi decoder etc. This device and its capabilities as well as the used software will be described during the two sections of this chapter, the hardware design and software design sections.

## 4.2. Hardware Design

The hardware is one of the two essential parts of the system. A proper implementation of the specification into hardware as well as the maximum optimization thereof, will play an important role in the global performance of the system, i.e. minimum Bit Error Rate, maximum Signal to Noise Ratio etc.

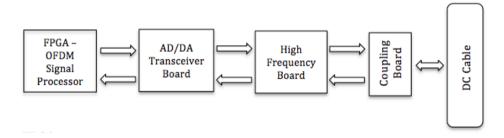

Figure 7: Transceiver Stages

On the hardware side the following parts are described:

- FPGA OFDM Signal Processor.

- AD/DA Transceiver Board.

- High Frequency Modulation Board.

- Coupling/Decoupling Circuitry.

All these parts together make the whole Powerline system.

#### 4.2.1. FPGA

The FPGA is the core of the OFDM modem. Its task is to generate the proper OFDM digital signals and send it further to the Digital-to-Analog converter, as well as receive the digital signals from the Analog-to-Digital converter and processing it.

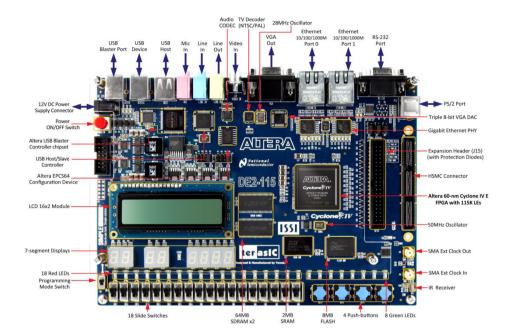

The development board used is the Terasic DE2-115 with the Altera Cyclone IV chip. This board provides different solutions for multiple needs.

Figure 8: Terasic DE2-115 Development Board

Some of the features that are included are here illustrated:

- Altera Cyclone IV 4CE115 FPGA device

- Altera Serial Configuration device

- USB Blaster (on board)

- 2MB SRAM

- Two 64MB SDRAM

- 8MB Flash memory

- SD Card socket

- 4 Push-buttons

- 18 Slide switches

- 18 Red user LED and 9 Green user LEDs

- 50 MHz external oscillator

- 24-bit CD-quality audio CODEC

- VGA DAC

- 2 Gigabit Ethernet PHY with RJ45 connectors

- USB Host/Slave

- RS-232 transceiver and 9-pin connector

- PS/2 mouse/keyboard connector

- IR Receiver

- 2 SMA connectors for external clock input/output

- One 40-pin Expansion Header with diode protection (GPIO)

- One High Speed Mezzanine Card (HSMC) connector

- Eight 7 segments displays

- 16x2 LCD module

- TV Decoder

Figure 9: DE2-115 Features

For the project, the most important characteristics of this development board are the Cyclone IV 4CE115 FPGA device, the Gigabit Ethernet PHY Port, the High Speed Mezzanine Card (HSMC) connector, the switches and buttons and the LCD Display [5].

#### Altera Cyclone IV 4CE115 FPGA device

The core of the board is the Altera Cyclone IV EP4CE115 C7. This device contains the programmable logic blocks inside. It has been chosen to meet the required specifications for the purpose [6].

| EP4CE115                     |        |  |  |

|------------------------------|--------|--|--|

| Logic elements (LEs)         | 114,48 |  |  |

| Embedded memory (Kbits)      | 3,888  |  |  |

| Embedded 18 × 18 multipliers | 266    |  |  |

| General-purpose PLLs         | 4      |  |  |

| User I/O Banks               | 8      |  |  |

| Maximum user I/O             | 528    |  |  |

Figure 10: Altera Cyclone IV Features

#### **Gigabit Ethernet PHY Port**

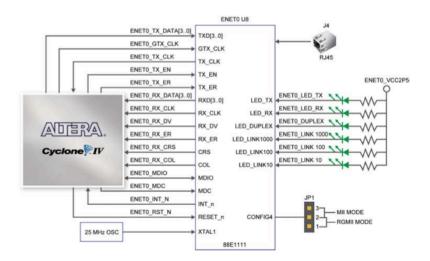

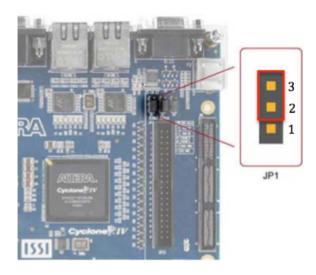

The Terasic DE2\_115 board provides Ethernet support via two Marvell 88E1111 Ethernet PHY controllers. These controllers are connected each one to a different Ethernet port installed on the board. Both controllers include 10/100/1000 Mbps Gigabit Ethernet transceiver and support GMII/MII/RGMII/TBI MAC interfaces. Nevertheless for the given board only MII and RGMII modes are supported. The selection of the operation mode is easily accessible through two jumpers provided on the board, JP1 and JP2, which allow the selection the mode for both ports independently.

In the next figure, the connections between the FPGA and one Ethernet port, through the Marvell controller, are depicted [5].

Figure 11: Marvell 88E1111 Ethernet Controller

#### High Speed Mezzanine Card (HSMC) connector

The HSMC interface provides the Terasic DE2-115 board a mechanism for extending the peripheral-set by means of add-on cards. This can couple high speed signalling requirement as well as with low-speed device interface support. The HSMC connector connects directly to the Cyclone IV FPGA with 172 pins. The voltage level of the I/O pins on the HSMC

connector can be adjusted to 3.3V, 2.5V, 1.8V or 1.5V for matching the required digital voltages level using a provided jumper on the FPGA. Since the designed boards work with 3.3V logical levels, this option must be selected.

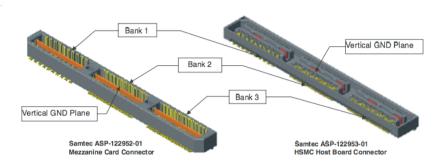

Figure 12: HSMC

The connector provides 3 independent signal banks. Each bank provides clock signals in both directions. Bank 1 has a dedicated JTAG and a system management bus (SMBus) and 8 channels CDR in both directions. Banks 2 and 3 have 12V and 3.3V power supply pins and provide 60 differential channels or 120 single-ended I/O pins.

For the project case, this connector is essential for the connection between the FPGA board and the transceiver board. This connection is possible thanks to a developed adapter board, which provides the connections between the HSMC port and the provided DBF ports on the transceiver boards [7].

# 4.2.2. Analog-to-Digital and Digital-to-Analog Transceiver Boards

Each FPGA board has to be able to send and receive digital signals. After generating the OFDM signals, in order to be modulated and transmitted to the channel, the signals have to be converted first into analog signals. Also, the received demodulated signals have to be converted to digital signals in order to be interpreted by the FPGA board.

To achieve these goals, a transceiver board was developed. This board provides two independent channels of communication, one in each direction.

The main features of the designed board are:

- Digital-to-Analog converter for transmitter side, symmetrical analogic output AD9765, up to 40 MSPS.

- Analog-to-Digital converter for receiver side, symmetrical analogic input AD9248, up to 40 MSPS.

- Connectivity with dSpace system.

- Testing jumpers and measure points.

Power Source SXLP-4.7+ AD9248 AD9765 +Q AD8138 AD8138 +Q Adapter Interface SERCOS Interface Voltage Converter իլլայի) են dSpace Interface

The layout of the board is showed and described in the next figure:

Figure 13: Transceiver Board

In the layout, the transmitter and receiver parts are distinguished and delimited by the vertical blue line, transmitter on the right side, receiver on the left side. The board needs positive and negative external power sources between 6.5 and 30V for positive and between -6.5 and -30V for negative (the needed voltage supply for the components is 3.3V and 5V and the regulators' datasheet specify a max dropout voltage of 1.5V and a absolute maximum of 30V). Connections to the FPGA board are possible thanks to the Adapter Interface and the adapter board mentioned before. The pins of the Analog-to-Digital converter and Digital-to-Analog converter are connected to these two interfaces. Connections to the High Frequency boards are possible thanks to the 8 SMA connectors, 4 on the transmitter side and 4 on the receiver side [8].

#### **SMA Connectors**

Analog connection for transmitting and receiving signals to/from the High Frequency Boards. These connectors offer  $50\Omega$  characteristic impedance and a maximum frequency of 18 GHz for the connection of a coaxial cable.

#### **Analog Devices AD9765**

12-Bit 125 MSPS Dual TxDAC+ Digital-to-Analog Converter with  $50\Omega$  characteristic impedance. This dual Digital-to-Analog converter is chosen due to the need of transmitting In-Phase and In-Quadrature signals of the OFDM. 3.3V logic voltage is supported. The main applications of this component are in Communications, Quadrature Modulation, Digital Synthesis and others [9].

#### **Analog Devices AD9248**

14-Bit Dual Analog-to-Digital Converter with  $50\Omega$  characteristic impedance. Available in 20,40 and 65 MSPS. Currently used the 40 MSPS version. This dual Analog-to-Digital converter receives the In-Phase and In-Quadrature single-ended analog signals, provided by the AD8138, and converts it into digital signals [10].

#### **Analog Devices AD8138**

Low distortion differential ADC Driver with  $50\Omega$  characteristic impedance.

The modulator needs a differential signal input centered on a 500mV DC, thus a driver and proper resistors are needed. Therefore, on the transmitter side, transmitted signal must be converted from single-ended to differential in order to be modulated. On the receiver side, received signal must be converted from differential to single-ended in order to do the sampling [11].

#### **Mini-Circuits SXLP-4.7+**

The SXLP-4.7+ is a surface mount Low-Pass Filter with stop frequency of 4.7 MHz with  $50\Omega$  characteristic impedance [12].

#### **Adapter Interface**

For the transmission of the digital signals from the FPGA to the Digital-to-Analog converters and from the Analog-to-Digital converters to the FPGA an interface is needed. For this purpose a DBF connector is used, due to the former system, which used a DBF3C120 board.

#### **DSpace Interface and Voltage Converter**

This interface provides communication between the FPGA board and the dSpace system.

#### 4.2.3. High Frequency Modulation Boards

After generating the base band In-Phase and In-Quadrature signals, the signals have to be modulated at the desired working frequency. To the project case, this frequency is 100 MHz. A modulation is the process of changing the properties of a periodic signal, which is called carrier signal, with a modulating signal, which contains the information to be transmitted. The main aims of modulating the signal to upper frequencies are adapting the signal to the channel

characteristics, avoiding possible disturbances at low frequencies, and having more available bandwidth, which is equal to having more data rate.

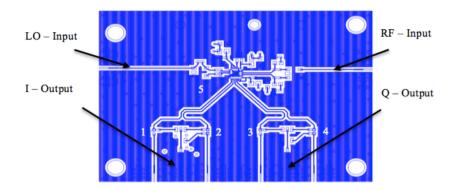

The main features of this board are the following:

- 4 Differential inputs, 2 for In-Phase signal and 2 for In-Quadrature signal (+I, -I, +Q, -Q) with SMA connectors for modulating signal.

- 4 Differential outputs, 2 for In-Phase signal and 2 for In-Quadrature signal (+I, -I, +Q, -Q) with SMA connectors for demodulated signal.

- 100 MHz carrier central frequency.

- Quadrature modulator ADL5385 and demodulator ADL5387.

- Testing jumpers and measure points.

- Input for an external oscillator (optional)

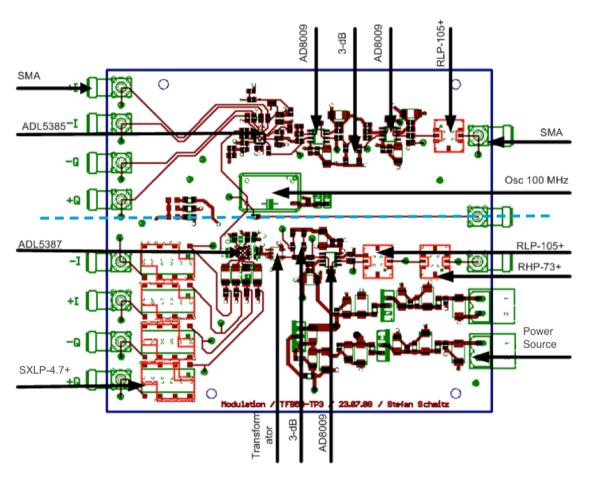

The layout of the board is shown and described in the next figure:

Figure 14: High Frequency Board

In this case, the transmitter and the receiver side are clearly defined and split by the blue striped line. It is important to notice, that both directions (transmitter and receiver) share the same transmission channel and are modulated at the same frequency, thus the communication is only possible in one direction, i.e. half duplex. The transmitter lays on the upper part and the receiver on the lower part. The board needs, as for the transceiver board, positive and negative power supplies between 6.5V and 30V for positive and between -6.5V and -30V on Power Source input [8].

#### **Analog Devices ADL5385**

The ADL5385 is a 30 MHz to 2200 MHz Quadrature Modulator with 50Ω characteristic impedance. The modulator requires differential signals in quadrature centred on a 500mV dc bias. The input carrier frequency (Local Oscillator) must be two times the desired carrier frequency i.e. 200 MHz This modulator is normally used for communication applications like Radio-link infrastructure, Cable modem termination system, UHF/VHF radio, Wireless infrastructure systems etc. hence is adequate for the purpose [13].

#### **Analog Devices ADL5387**

The ADL5387 is a 30 MHz to 2 GHz Quadrature Demodulator with  $50\Omega$  input impedance. The demodulator needs a differential RF input and offers a baseband I/Q driving a  $2V_{p-p}$  signal into  $200\Omega$ . The voltage conversion gain of the demodulator is >4dB. The input carrier frequency (Local Oscillator) must be two times the desired carrier frequency i.e. 200 MHz The main applications of this demodulator are QAM/QPSK RF/IF demodulators, W CDMA/CDMA/CDMA200/GSM, Broadband wireless and WiMAX etc [14].

#### Mini-Circuits RHP-73+

The RHP-73+ is a surface mount High-Pass filter with start frequency at 73 MHz with  $50\Omega$  characteristic impedance [15].

#### Mini-Circuits RLP-105+

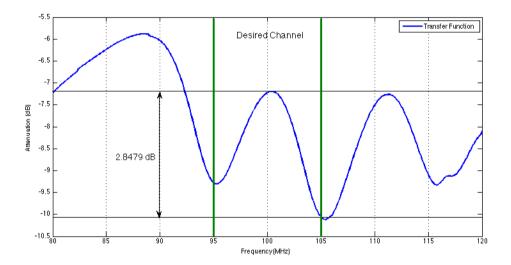

The RLP-105+ is a surface mount Low-Pass filter with stop frequency at 105 MHz with  $50\Omega$  characteristic impedance.

In receiver side, RLP-105+ in serial with RHP-73+, a band pass filter with lower cut-off frequency of 73 MHz and upper cut-off frequency of 105 MHz is built [16].

#### **Analog Devices AD8009**

1GHz Low Distortion Amplifier. Presented in different configurations to achieve desired gains for each stage. The main applications of this AD8009 are in IF/RF Gain Stage [17].

#### 3dB Attenuator

3dB attenuator made with a resistor network in PI design, designed to adequate the input signal to the next stage.

#### 1:1 BALUN

Converts the signal from single-ended to differential to adequate it to the input of the demodulator. It is 1:1 so it will not affect to the impedance that remains  $50\Omega$ .

#### Crystek CC0-085

The CC0-85 is a true sine wave clock oscillator to generate the carrier signal in a 200 MHz frequency [18].

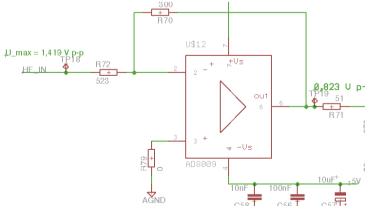

#### **Board schematic:**

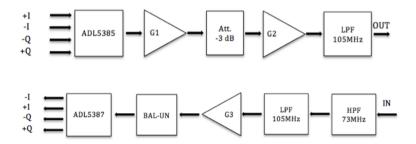

A simplified scheme of the configuration is presented in the next picture:

Figure 15: Transceiver Stages

To calculate gain values G1, G2 and G3, it is important to know the characteristics of the channel, losses in passive elements, conversion gain of the demodulator and minimum amplitude needed for demodulation in the reception part of the High Frequency Board. Also is important to specify the configuration of the amplifier used. In the case of stages G1 and G2, non-inverter amplifiers are configured. But in G3 stage an inverter amplifier is used. It is important to notice, that the equations that govern the behaviour and the gain of each configuration are different. The difference is relevant to obtain the gain. Just changing the relation between two resistors can easily change the gain of the stages as follows:

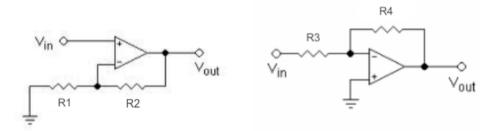

Figure 16: Non-Inverter and Inverter Configurations

Thus, for non-inverter configuration:

$$V_{out} = V_{in}(1 + \frac{R_2}{R_1}) \tag{6}$$

For inverter configuration:

$$V_{out} = -V_{in}(\frac{R_2}{R_1}) \tag{7}$$

The voltage gain is given by the equations:

$$G = \frac{V_{out}}{V_{in}} \tag{8}$$

$$G(dB) = 20\log\left(\frac{V_{out}}{V_{in}}\right) \tag{9}$$

# 4.2.4. Coupling/Decoupling Circuitry

The main characteristic of a Powerline Communication system is transmitting information through a Powerline cable. That means, in industrial fields, that the cable where the signal is coupled carries also a voltage difference of about 700V DC. To allow the transmitted signal to travel through the DC channel and protect the High Frequency Modulation Board from the DC signal, a Coupling/Decoupling circuitry is needed. Hence the main characteristics of this circuitry are the following:

- Main protection against high voltage DC input signal.

- Protection against high frequency and high power peaks.

- Coupling and decoupling the transmitted and received signal into/from the same channel.

- $75\Omega$  to  $50\Omega$  Impedance conversion.

- Converting the transmitted single-ended signal to a differential signal and the differential received signal to single-ended signal.

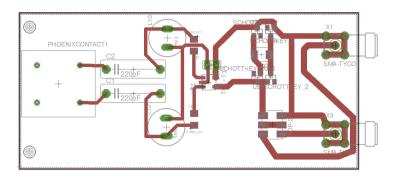

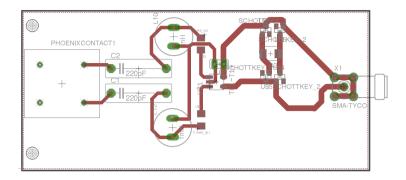

The layout of the circuitry is showed in the next figure:

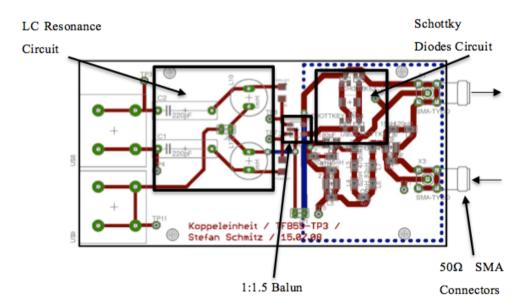

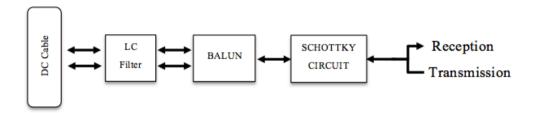

Figure 17: Coupling Board Design

In the design several stages are defined:

Figure 18: Coupling Stages

#### LC Resonance Circuit

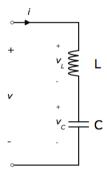

To block the unwanted frequencies (mainly high-voltage DC) signals, a resonance circuit designed to be resonant at 100 MHz is designed. At this frequency the inductive reactance is equal to the capacitive reactance, thus the impedance is at its minimum. That means, the transmitted signal at 100 MHz pass through the filter with almost no attenuation, while other frequencies are blocked. Because the signal is differential, a LC filter circuit must be implemented on each line.

Figure 19: LC Resonator

The values of L and C were calculated following the formula:

$$f_{res} = \frac{1}{2 \cdot \pi \cdot \sqrt{L \cdot C}} = 100 \, MHz \tag{10}$$

Taking a L value of 10nH, then:

$$C = \frac{1}{4 \cdot \pi^2 \cdot 10nH \cdot (100MHz)^2} = 253.3 \, pF \tag{11}$$

Thus a capacitor of 220 pF is chosen. Also important is the maximum voltage that the capacitor can support. In this case, a WIMA FKP1 capacitor, which supports up to 2000VDC [19].

#### 1:1.5 BALUN

After the filter, a 1:1.5 balun is used. This component will convert the received differential signal into a single-ended signal. Also, a relation 1:1.5 is chosen in order to convert the input  $50\Omega$  impedance of the connectors into  $75\Omega$  impedance to maximize the transmitted power.

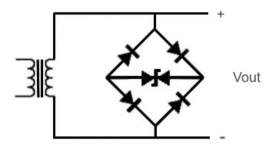

#### **Schottky Diodes Bridge Circuit**

To protect the High Frequency Board against possible high frequency and voltage peaks that could be produced, a Schottky diode bridge circuit is implemented.

Figure 20: Schottky Diodes Circuit

Usually, the Schottky diode bridge is used for rectifying AC into DC signals, but in this case a SMBJ Transient Voltage Suppressor is placed in the middle of the diode bridge.

# 4.3. Software Design

The second main part of the system is the software part. Since the core of the system is a Programmable Logic Device, this can be programmed and optimized easily to achieve the desired behaviour.

To test the proper functioning of the system, as well as to do quality measurements of the channel, initial software that transmits a known sequence was developed. This software will be the basis of the further implementation of the Ethernet coupling as will be described in the Ethernet Coupling Principle section of this chapter.

# 4.3.1. FPGA-Based Transceiver Program Structure

Initially, the existing programs implemented transmitter and receiver in separated and independent boards. This implementation was needed for concept and validation. Nevertheless, for a transceiver program, both receiver and transmitter have to be located in the same board. To achieve this goal, a merging of the two working programs of transmitter and receiver parts was performed.

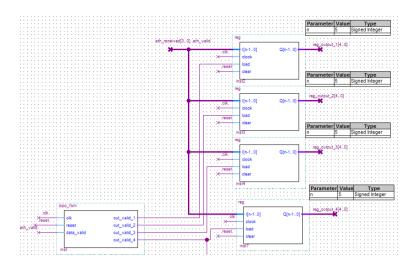

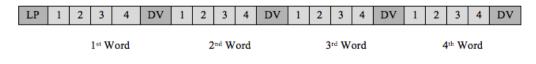

After merging both projects, a single project with two blocks at the top level of the hierarchy results. These two blocks are transmitter and receiver blocks, containing several stages that modify the data to be transmitted, in the case of the transmitter program, and properly recognized, in the case of the receiver program.

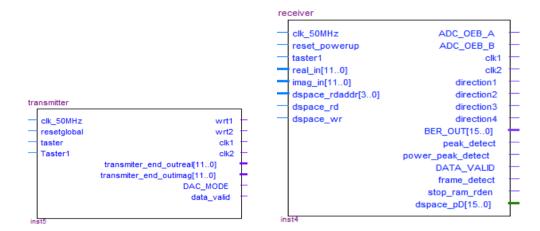

Figure 21: Transmitter and Receiver Blocks

The blocks showed before work with the 50 MHz signal clock provided by the FPGA circuitry. Furthermore, taster (to power up and to start the transmission) and reset signals are assigned to switches and buttons placed in the Terasic development board.

Figure 22: Transceiver Software Stages

During this section, the different blocks of the system will be explained through the ground theory of the transmission. There are two signal treatments along the system.

First, a treatment of the raw data, including data packaging, error prevention and modulation, where data still has a digital meaning.

Secondly, after the modulation block, modifications of the signal with the aim of constructing the analog subcarriers and the OFDM symbols to be transmitted.

#### 4.3.1.1. Theoretical Introduction

The initial communication protocol of this Powerline Communication system was developed for dSPACE. DSPACE is a company that offers different hardware and software solutions to accelerate the development of complex control systems with ease in a vast amount of industries.

In the former system design, a dSPACE DS1103 Controller board was available in one computer. This Controller board was used to command a drive with a second dSPACE system. Both dSpace systems were connected to each FPGA through the dSPACE Interface of the Transceiver board. The process consisted in writing the desired information in real-time to

the FPGA to command the drive that is placed at the other side of the Powerline channel. The dSPACE also had the function of controlling the quality of the reception. Hence the communication between the dSPACE system and the FPGA was bidirectional. This system had a working frequency of 32 kHz, and the OFDM system should be designed according to this working frequency. That means that the cycle time of the communications should be according,

$$T_{cycle} = \frac{1}{f} = \frac{1}{32 \text{ kHz}} = 31.25 \,\mu s$$

(12)

This cycle time value will define the number of data OFDM symbols and also the maximum data rate for a given modulation. In this case, as described at the OFDM description section in equation 5, the symbol duration is 3.2µs.

For the proper symbol detection and to avoid Intersymbol Interference (ISI), a guard time between symbols is inserted. This guard time is established as

$$T_{guard} = \frac{1}{4} \times T_{symbol} = 0.8 \,\mu s. \tag{13}$$

Then the total OFDM symbol duration is

$$T_{ofdm} = T_{symbol} + T_{guard} = 4 \,\mu s. \tag{14}$$

Then, the maximum OFDM symbols are

$$N_{symbols} = \frac{31.25 \,\mu s}{4 \,\mu s} = 7.8125 \rightarrow 7 \,OFDM \,\, symbols. \tag{15}$$

Apart from data symbols, training symbols for the channel estimation and equalization are needed. These symbols have the same duration as the data symbols. In this case, 5 symbols are transmitted. Data symbols will transmit data, training symbols have two purposes, one symbol is for frame synchronization, and the other is for the channel estimation. Data symbols are generated by gathering and packing codified streams of transmitted bits. The need of transmitting training symbols has as side effect a reduced net data rate [2].

To codify the transmitted bits into analog signals in order to increase the data rate, a digital modulation scheme is used. A digital modulation allows the transmission of several bits into one analog signal by modifying an analog carrier signal. Several types of digital modulations are available:

- Phase Shift Keying (PSK): Symbols are represented by changes in the phase of the signal.

- Frequency Shift Keying (FSK): Symbols are represented by changes in the frequency of the signal.

- Amplitude Shift Keying (ASK): Symbols are represented by changes in the amplitude of the signal.

- Quadrature Amplitude Modulation (QAM): Symbols are represented by changes in the amplitude of two quadrature signals.

In the design, two codification schemes are available: Binary Phase Shift Keying (BPSK) and 16 Quadrature Amplitude Modulation (16-QAM) [20]:

- Binary Phase Shift Keying (BPSK): BPSK is the simplest form of Phase Shift Keying modulation. In this modulation, only two different codified symbols can be transmitted, "0" and "1", represented with a phase of 0° and 180° respectively. BPSK is the digital modulation with highest Signal to Noise Ratio (SNR) and lowest Bit Error Rate (BER) because the symbols are far away from each other. The BPSK is also the less efficient because only transmits 1 bit per symbol.

- 16 Quadrature Amplitude Modulation (16QAM): QAM is a form of Amplitude Shift Keying, but instead of transmitting one signal, two signals are transmitted at the same time: In-Phase and In-Quadrature signals. In 16-QAM, two amplitude signals with 4 different amplitude levels each one are transmitted. Each level of each signal represents two bits "00", "01", "10" and "11". Combining both signals, a maximum number of 16 possible codified symbols are achieved. Thus the efficiency increases compared to BPSK up to 4 bits per symbol.

The modulation used is essential for the system design, and must be adapted to meet the required data rate for the application. In this case, as specified in the OFDM modem description, 32 subcarriers along the 10 MHz bandwidth are available and 5 OFDM data symbols are transmitted. The maximum number of transmitted codified symbols on each cycle time is defined by these two parameters:

$$32 \text{ subcarriers} \times 5 \text{ OFDM symbols} = 160 \text{ codified symbols}$$

(16)

The advantage of the 16QAM modulation over the BPSK modulation is clear, because 16QAM transmits 4 bits each symbol whereas BPSK transmits only 1 bit.

Therefore, in BPSK the amount of bits transmitted each cycle time is:

$$N_{bits-BPSK} = Symbols \times Bits/Symbol = 160 bits$$

(17)

Meanwhile in 16QAM is:

$$N_{bits-160AM} = Symbols \times Bits/Symbol = 640 bits$$

(18)

In each cycle time more data, apart from the desired data, is transmitted. A 16 Cyclic Redundancy Check (16CRC) block for frame checking as well as a Convolutional Encoder block for adding redundancy are added. That means that the effective number of bits is lower than the calculated above. The 16CRC block adds a 16-bit word to the data, and the Convolutional Encoder has a coding rate of  $\frac{1}{2}$ , meaning that for one bit of raw data, two bits

are transmitted. Both blocks are described in later lines. Therefore, for each modulation the following number of brute and effective bits are transmitted each cycle time:

| Modulation | Number of<br>Brute Bits | Effective<br>Bits | Data Rate        |

|------------|-------------------------|-------------------|------------------|

| BPSK       | 160                     | 80                | 2.56 Mbits/s     |

| 16QAM      | 640                     | 320               | 10.24<br>Mbits/s |

Figure 23: BPSK vs. 16QAM Bits

The data is processed in words of 16 bits, then,

$$N_{words-BPSK} = \frac{80}{16} = 5 \ words$$

,  $N_{words-16QAM} = \frac{320}{16} = 20 \ words$  (19)

In both cases, one word is reserved to transmit the 16CRC, so the effective parameters are:

| Modulation | Effective<br>Bits | Total<br>Words | Data Words | Effective<br>Data Rate |

|------------|-------------------|----------------|------------|------------------------|

| BPSK       | 80                | 5              | 4          | 2.048                  |

|            |                   | -              | •          | Mbits/s                |

| 16QAM      | 320               | 20             | 19         | 9.728                  |

| TOQAM      | 320               | 20             | 19         | Mbits/s                |

Figure 24: BPSK vs. 16QAM Effective Data

After modulating the signal, the modem must build the different subcarriers that will conform the final OFDM signal.

The core of the OFDM is the Discrete Fourier Transform (DFT) and Inverse Discrete Fourier Transform (IDFT) performed by the high efficient algorithms Fast Fourier Transform (FFT) and its inverse (IFFT). These are two computational algorithms used in signal theory to change between time-domain and frequency-domain signals. The signal from modulation block is time-domain, but to construct the OFDM signal, different subcarriers have to be differentiated by the IFFT. Therefore, the modulated signals are mapped in frequency domain and later converted to time-domain signals with the IFFT algorithm.

Since the FFT algorithms work on streams with lengths of power of two, some zeros should be added to each data symbol. The length of the FFT  $(N_{FFT})$  is a key value to the system. The following relationship must be always kept:

$$\frac{Sample\ Rate\ (Hz)}{N_{FFT}} = \frac{Bandwidth\ (Hz)}{Subcarriers} = \frac{1}{T_{symbol}} \tag{20}$$

Since 32 subcarriers and a bandwidth of 10 MHz are specified, both sample rate and FFT points are variables to be chosen. For the purpose, as described in hardware design part of this

chapter, a 40 MSPS Analog-to-Digital converter is used, which limits the maximum sample rate to use. For each modulation, the chosen sampling rate and the points of the FFT are in the next table specified:

| Modulation | $N_{\mathrm{FFT}}$ | Sampling<br>Rate |

|------------|--------------------|------------------|

| BPSK       | 64                 | 20 MSPS          |

| 16QAM      | 128                | 40 MSPS          |

Figure 25: BPSK vs. 16OAM Sampling Rate

Hence, the working frequency of each BPSK and 16QAM program will be 20 MHz and 40 MHz respectively.

To generate the required frequency, an Altera's PLL MegaCore block is used. This block can be configured to take the 50 MHz signal from the circuitry and modify it to obtain a clock signal with a different frequency. This PLL block also allows implementing more than one output independent clocks for a given input.

As defined before, the main characteristic of an OFDM modem is the transmission of several orthogonal subcarriers to increase the spectral efficiency. Sometimes can occur, that the orthogonality between both signals is lost, due to the non-ideal channel characteristics. Losing the orthogonality will cause Inter Symbol Interference (ISI). To avoid this effect, a cyclic prefix is added at the beginning of each OFDM symbol as guard interval.

Furthermore, as described at the OFDM symbols definition, there are the two training symbols introduced after adding the cyclic prefix. The first training symbol is a preamble symbol, and it is necessary to the proper synchronisation of the receiver. This symbol just transmits a complete OFDM symbol with zeros in order to detect the peak of power when the data is received.

To avoid Inter Symbol Interference (ISI) caused by time-shift between symbols, cyclic prefixes before each data symbol are added. These prefixes are added in the reserved guard interval time. If the time shift between symbols is shorter than the guard time, the ISI is completely removed.

#### **4.3.1.2. Data Source**

The first designed block is the data source of the program. In this case, a known sequence stored in a local file is transmitted. This sequence contains data with values from 0x0000 to 0xFFFF. This block will send 16-bit words from the local file to the next block at a fixed frequency. This sending frequency is determined by the modulation scheme and the cycle time used.

$$T_{send} = \frac{T_{cycle}}{Data\ Words}\ s$$

,  $f_{send} = \frac{1}{T_{send}} = \frac{Data\ Words}{T_{cycle}}\ Hz$  (21)

| Modulation | Data Words | Sending<br>Frequency |

|------------|------------|----------------------|

| BPSK       | 4          | 0.128 MHz            |

| 16QAM      | 19         | 0.608 MHz            |

Figure 26: BPSK vs. 16QAM Data Frequency

To generate this frequency, another output clock of the implemented PLL block with the convenient ratio is activated.

After generating the symbols at the sending frequency, these are stored in a RAM module to be read afterwards at working frequency of the system, defined before in FFT description.

At the receiver side, the received data is compared with the data stored in a RAM module, which is identical to the transmitted data. A counter will be incremented by one every time a received bit does not match with the stored bit.

### 4.3.1.3. Cyclic Redundancy Check

Next to the Data Source block, a Cyclic Redundancy Check (CRC) generator block is implemented. The CRC is a commonly used method to help the receiver to check if there is some data corrupted. The block generates a code, based on the previous Data Words of the same cycle and then adds this code as the last 16-bit word of the transmission. The receiver, once it has received all the data words in one cycle, calculates the CRC and compares the result with the given CRC value from the transmitter in the last word. The block has inside an error counter, which is incremented by one every time the CRC calculated is not the same as the value received in the last block and CRC valid and CRC bad output signals, which are asserted to indicate if the CRC is valid or not.

To generate the value, successive modulo 2 divisions on the data stream are performed, storing the remainder. In these divisions, the received data is divided by a 17-bit word "1100000000000101" defined by the polynomial  $x^{16} + x^{15} + x^2 + 1$ .

To perform this calculation in both directions the Altera CRC Compiler MegaCore is available. The IP Core permits different configurations, e.g. configure it as CRC generator or CRC checker, the number of channels, the data width or the CRC code. In this block, a parallel to serial conversion is also performed. This is done because the next block needs serial data in order to do the convolutional encoding [21].

### 4.3.1.4. Convolutional Encoding

Since the transmission channel is not ideal, distortions over the signal can be produced. For bit error detection and correction, a convolutional encoding method is used.

In the transmitter part, the incoming bit stream of length L is transformed into another of length M, where M is greater than L. The output stream depends on the input at the current cycle and also on the input of the previous cycle.

In the receiver part, for error correction, a Viterbi error correction algorithm is used. It is based on maximum likelihood principle, which is a statistical model that can estimate the most probable message given a received sequence. For implementing this feature, the Altera Viterbi IP MegaCore is available.

#### 4.3.1.5. Interleaver

As a complement of the convolutional encoding, an interleaver is also implemented. Its main goal is to prevent burst errors in detection due to long duration noise. Interleaving a message is a way of organizing the transmitted digital information, changing the order, and spreading several parts of the message along a defined stream of bits, making the detection easier. The difference between a non-interleaved transmission and an interleaved transmission that is affected by noise is shown in the next tables:

| Without interleaving |                              |  |

|----------------------|------------------------------|--|

| Message:             | aaaabbbbccccddddeeeeffffgggg |  |

| Message sent:        | aaaabbbbccccddddeeeeffffgggg |  |

| Message received:    | aaaabbbbcccdeeeeffffgggg     |  |

| With interleaving  |                              |  |  |

|--------------------|------------------------------|--|--|

| Message:           | aaaabbbbccccddddeeeeffffgggg |  |  |

| Message sent:      | abcdefgabcdefgabcdefg        |  |  |

| Message received:  | aaaabbbbcccdeeeeffffgggg     |  |  |

| Message reordered: | aa_abbbbccccdddde_eef_ffg_gg |  |  |

Figure 27: Without Interleaving vs. with Interleaving

In the first case, the most part of the message "dddd" is not properly detected due to the noise. However in the interleaved case, only one bit is missing in each part of the message, so it can be rebuilt with the error correction techniques.

To implement the technique at the transmitter side, a RAM stores the desired data and afterwards a state machine will interleave it following a pseudo-random sequence stored in a file. The opposite process is made at reception to undo the process.

Interleaving introduces some latency to the system because the transmitter has to read the defined stream length in order to reorganize the data, and the receiver must wait until the entire message is received to properly deinterleave the message.

### **4.3.1.6.** Modulation

The modulation is the process of modifying a specific characteristic of an analog signal to transmit the information. In the design, as mentioned before, two modulations are implemented; Binary Phase Shift Keying (BPSK) and 16 Quadrature Amplitude Modulation (16QAM). The block that implements the modulation is the mapping block. This block generates a two-dimensional signal in the complex plane a + jb, to map it later in a constellation map. Both signals will be transmitted further at the same frequency but with a phase shift of 90°, representing real plane (cosine), and imaginary plane (sine).

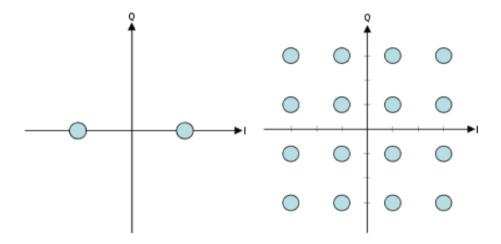

In next figure, both real (I) and imaginary (Q) planes are represented:

Figure 28: BPSK vs. 16QAM constellation

The constellations are mapped with a Gray codification. That means that between two consecutive values, only one bit is different for an easier detection. Following an example of a 2-bit Binary/Gray codification:

| Decimal | Binary | Gray |

|---------|--------|------|

| 0       | 00     | 00   |

| 1       | 01     | 01   |

| 2       | 10     | 11   |

| 3       | 11     | 10   |

Figure 29: Binary vs. Gray

As the output signal of the block contains amplitude information, represents an analog signal and thus must have the width of the analog-to-digital converter, which in this case is 12-bit wide.

- In case of BPSK modulation, only two values are available, "000010100000" (160) to represent "1", and "111101100000" (-160) to represent "0". These values are in real plane only; the imaginary plane is always zero. Therefore, every input bit will have a 12-bit output.

In case of 16QAM modulation, four values on each plane are available, "000000110010" (50) to represent "01", "000010010110" (150) to represent "00", "111111001110" (-50) to represent "11" and "111101101010" (-150) to represent "10". Therefore, every 4-bit input will correspond to two 12-bit outputs.

At the receiver part, a symbol recovery block will detect the symbols and will convert them back to digital data.

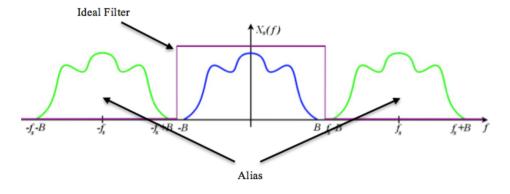

### 4.3.1.7. Zero Padding

The zero padding is a process of filling a sampled signal before performing any other process over it. The FFT and IFFT algorithms are more efficient with input data streams of a power of two lengths. To adapt the digital signal to this length, a zero padding block is used. In addition, zero padding is a good solution to prevent aliasing after generating the OFDM signal due to the oversampling.

By adding zeros to the signal the desired signal will be oversampled with a factor of:

$$v = \frac{N_{FFT}}{N} , N_{FFT} > N \tag{22}$$

Where N<sub>FFT</sub> is the length of the FFT and N is the length of the data symbol.

The aliasing appears for a sampling frequency (fs) lower than the Nyquist frequency

$$F_N = 2 \times B \tag{23}$$

Where F<sub>N</sub> is the Nyquist frequency and B is the bandwidth of the sampled signal.

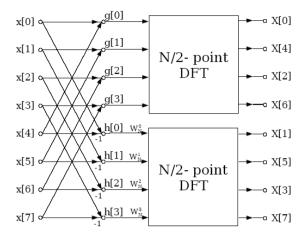

When sampling, the spectrum of the sampled signal is  $2\pi$  periodic, i.e. is repeated each fs, appearing alias of the original signal .In an ideal situation, with a perfect filter response and meeting the previous condition the alias are outside of the filter and aliasing does not appears.

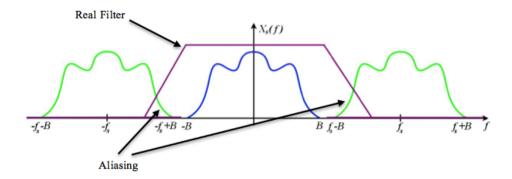

Figure 30: Ideal filtering

In a real situation, where the filters are not ideal, it might occur that part of the alias goes inside of the pass band of the filter, mixing with the desired signal and interfering with it.

Figure 31: Real filtering

The oversampling of the signal prevents the aliasing by moving away the alias in frequency domain due to the new higher sample frequency.

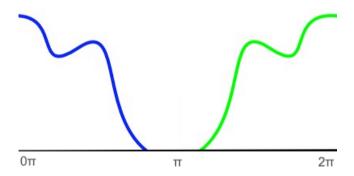

Because the spectrum will be  $2\pi$  periodic and it is impossible to transmit negative frequencies in base-band, the IFFT vector represents the frequencies between 0 and  $2\pi$ , i.e. between 0 and fs. The start of the vector represents the lower frequencies meanwhile the middle of the vector  $(\pi)$  represents the high frequencies. The end of the vector represents the negative frequency components of the spectrum, which contains the half of the transmitted subcarriers. After the generation, the transmitted signal is  $2\pi$  periodic and disposed as shown before.

Figure 32: Periodic signal representation

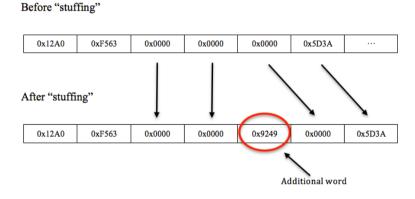

To preserve the negative frequency components of the signal, which contain modulated information, and to preserve the conjugate symmetry of the vector, the zero padding must be done by adding the zeros in the middle of the stream, instead of just adding at the end. If this is not done, the negative spectrum part will be in higher frequencies that the positive part and then, will be filtered afterwards.

Figure 33: Zero Padding "in the Middle"

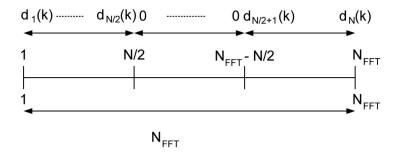

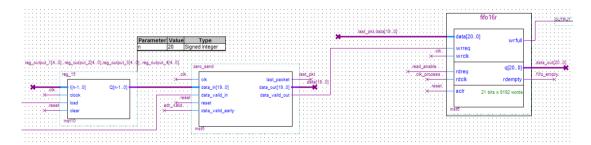

### 4.3.1.8. Fast Fourier Transform

As commented before, the Fast Fourier Transform (FFT) algorithm is the core of the OFDM modem and it is based on the Discrete Fourier Transform (DFT). Thanks to this algorithm the transition between time-domain and frequency-domain signals is possible. The FFT transforms a time-domain signal into a frequency-domain signal and the IFFT transforms a frequency-domain signal into a time-domain signal. An Altera's FFT MegaCore included in each transceiver performs both processes. It allows different configurations, including number of points and data precision [21].

The DFT defines the frequency-domain signals  $(X_k)$  as transformation of the time-domain signals  $(x_n)$  and vice-versa with N points.

$$X_k = \sum_{n=0}^{N-1} x_n \cdot e^{\frac{-i2\pi kn}{N}}, k \in \mathbb{Z}$$

(24)

$$x_n = \frac{1}{N} \sum_{k=0}^{N-1} X_k \cdot e^{\frac{i2\pi kn}{N}}, n \in \mathbb{Z}$$

(25)

Each  $X_k$  is a complex number that encodes amplitude and phase of a sinusoidal component of function  $x_n$ .

The Altera's FFT MegaCore function performs a radix-n decimation-in-frequency FFT. This FFT algorithm redisposes the DFT calculation in two parts: computation of even-numbered discrete-frequency indices ( $X_k$  for k=[0,2,4,...,N-2]) and computation of the odd-numbered indices ( $X_k$  for k=[0,1,3,...,N-1]). Each DFT calculation part can be independently performed for an N/2-point DFT, multiplying the odd-indexed frequencies by the twiddle factor term  $W_N^k = e^{-(\frac{i2\pi k}{N})}$

Figure 34: 8-Point FFT

After the computation, only a reordering of the resulted  $X_k$  components is needed [23].

Since DFT and IDFT are equals except for the 1/N factor, the IFFT computation is performed the same way.

To transmit the different subcarriers, generated data amplitude signals are disposed in the  $X_k$  vector. This vector will contain the signal with the data represented in the frequency domain as defined previously, i.e. 32 subcarriers with 312.5 KHz bandwidth each one. Then the IFFT is applied, transforming the signal to time domain generating the OFDM symbols and sending them forward.

At reception, the opposite sequence is applied. The OFDM symbols are split as they are received, and then the FFT is applied to each OFDM symbol to recover the original signal that contains the modulated data symbols.

### 4.3.1.9. Preamble and Prefix

After the IFFT block, the previously described functionalities of Cyclic Prefix and Preamble are implemented.

#### 4.3.1.10. Receiver Synchronisation

For the synchronisation at the receiver part, the algorithm of Timothy M. Schmidl and Donald C. Cox is implemented, with a modification in the method; the autocorrelation of both real and imaginary received signals is continuously calculated.

The original method describes the use of a two-symbol training sequence for achieving the detection in two steps. The first step includes the frequency-offset correction by searching for a symbol, whose first and second halves are identical. Afterwards the second step performs a correlation with the second symbol to find the carrier frequency offset.

For the modified method, the detection of the data frame is only performed with the correlation of the guard interval instead of the whole training symbol.

Real and imaginary signals have the same preamble, so the value should be the same at the start of the reception. After this, the integration of both values will provide the power of the signal. To detect the start of the signal a predefined value is provided as threshold, avoiding the detection due to noise. This value should be adapted to the characteristics of the channel, in order to detect properly the start of the signal.

# 4.4. Ethernet POWERLINK and B&R System

Instead of using a dSpace system to command the drive, now an industrial communication protocol, Ethernet POWERLINK is available. It is a complete software solution to be implemented over IEEE 802.3 Ethernet standard. That means that Ethernet POWERLINK can be implemented on every standard 802.3 Ethernet device, just by programming it. The absence of proprietary hardware makes easy the implementation and takes the benefits of Ethernet flexibility and extra hardware such as Hubs, Switches etc [24].

Some of the advantages of implementing the Ethernet POWERLINK Protocol are:

- Support IP based protocols as TCP or UDP.

- Synchronize networked nodes with high precision.

- Possibility of implementing the protocol over a standard 802.3 Ethernet device.

- Avoid of collisions by the time division access. Only one node transmits at once.

### 4.4.1. Ethernet

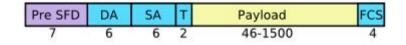

POWERLINK uses standard Ethernet frames for data transfer. An Ethernet frame contains several sections to transmit and address the data. It begins with a 7-byte preamble (Pre) and 1 byte Start-of-Frame delimiter (SFD) followed by a 6-byte destination address (DA) and a 6-byte source address (SA). The next 2 bytes represent the EtherType (T). Then come the payload (minimum 46 bytes) and a 4-byte CRC-32 checksum to check the integrity of the data.

Figure 35: Ethernet frame

Then, the maximum frame length is defined as 1518 bytes of which maximum 1500 can be of payload. Both source address and destination address are unique MAC addresses.

# 4.4.2. Protocol Description

In order to achieve real-time capabilities, Ethernet POWERLINK mixes polling with time-slot methods allowing only one node to transmit data, in contrast to basic Ethernet protocols, where an arbitration system is needed in order to avoid collisions.

In Ethernet POWERLINK two different nodes can be described:

- Managing Node (MN): Moderates and decides which node can transmit (usually an Industrial PC).

- Controlled Node (CN): All other devices controlled by the Managing Node (sensors, servo drives and others).

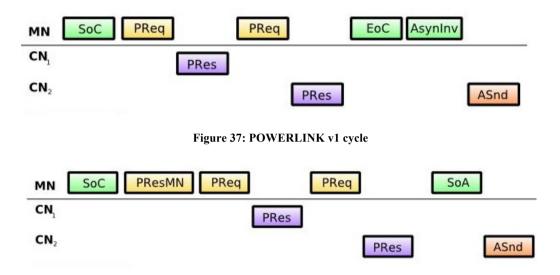

To communicate with the Controlled Nodes, the Managing Node establishes a cycle time and defines the clock pulse to synchronize all the nodes. During this cycle time two different phases are defined, Isochronous Phase and Asynchronous Phase.

First, before Isochronous Phase, the Managing Node sends a "Start of Cycle" (SoC) frame to tell all the nodes the start of the cycle and synchronize them. Afterwards, the Managing Node starts polling each Controlled Node one by one with the "PollRequest" (PReq) frame. After each poll, only the asked node has a defined maximum response time to answer with a "PollResponse" (Pres) frame. In this phase, time-critical information is exchanged between nodes.

After Isochronous Phase, Asynchronous Phase starts with the transmission of the "End of Cycle" (EoC) and "Asynchronous Invitation" (AsynInv) frames, allowing one Controlled Node to transmit non-critical data. The Managing Node can poll each cycle a different Controlled Node. During this phase, information such as TCP/IP data or parameter configuration is exchanged. This phase is not mandatory and, although it must be considered in the cycle time, asynchronous data is not transmitted on every cycle.

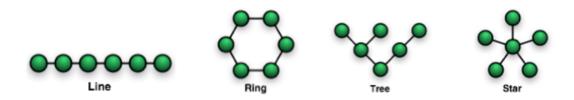

Ethernet POWERLINK allows different network topologies, star, tree, line, ring or any combination of the structures are available. Furthermore, no extra configuration is needed [24].

Figure 36: Network topologies

### 4.4.2.1. POWERLINK v1 vs. POWERLINK v2

There are two versions of POWERLINK available POWERLINK v1 and POWERLINK V2. The POWERLINK v2 meets the previous characteristics and adds additional features.

The main characteristic of POWERLINK v2 is the standardized application layer to the open IEC standard as an extension of POWERLINK v1, which is B&R proprietary. Furthermore POWERLINK v2 introduces other features:

- Introduces a unique "Start of Asynchronous" (SoA) frame instead of "End of Cycle" (SoC) and "Asynchronous Invitation" (AsynInv) frames.

- Support for safety products.

- Integration of OEM devices by introducing XML files.

- Intelligent Controlled Node (iCN).

- Configurable size of the asynchronous channel.

- PollResponse MN frame possibility.

- PollResponse chaining mode.

- DNA support.

- Continual performance optimization.

There is a slight change between the POWERLINK v1 and POWERLINK v2 cycles.

Figure 38: POWERLINK v2 cycle

In POWERLINK v2 a PresMN frame after the SoC frame can be transmitted. This is included for the "poll response chaining" feature, implemented on POWERLINK v2. With this feature, the controlled nodes are queried all at once by the PresMN frame, which is sent as multicast. All the nodes receive all the information and they answer sequentially.

## 4.4.3. B&R System Description

In the industrial automation environment, B&R Company develops different solutions for automation systems such as industrial PCs, control systems, networks and fieldbus modules, having presence in several industries.

For this purpose, B&R handles the development of hardware as well as software solutions.

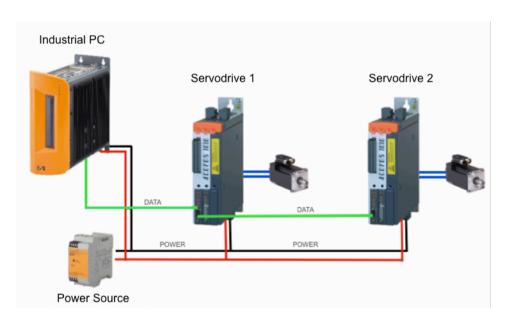

### 4.4.3.1. Hardware topology

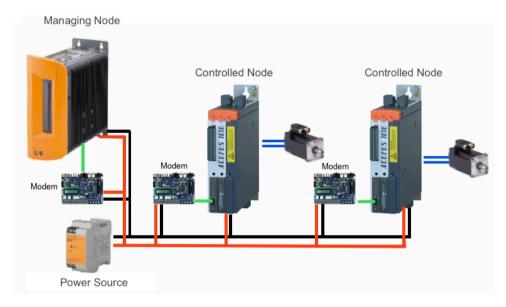

The available target system is a B&R Automation system that consists of an Industrial PC (IPC), which controls two Servo Drives; each one drives an electric motor. Furthermore, an HMI touch display and a keyboard are also integrated in a single solution.

The specific devices available are:

- A B&R 5PC810.SX01 Industrial PC.

- Two ACOPOS 1016 Servo Drives.

- Two Servo Motors.

- Two POWERLINK Bus Couplers.

To program and command the Industrial PC, an external computer is connected with it through an Ethernet cable.

The whole system works with either 24V DC power supply or with 230V AC supply. The way to supply each servo drive depends on the connectors placed on each servo drive (one supplies 24V DC and the other supplies 230V AC) and on a specific parameter on the software present in an external computer.

The servo drives include three expansion ports that allow expanding the capabilities. In the supplied system, one Ethernet POWERLINK module (with two Ethernet connectors) and one RS232 interfaces are included on each servo drive.

The POWERLINK bus couplers are connected to the drives in order to manage the information from/to the sensors and actuators of the drives.

Figure 39: B&R system

The connection between the IPC and the nodes is possible thanks to the Ethernet POWERLINK ports. Each port has a half-duplex connection with either previous node or next node. One connector receives and sends from/to the previous node; the other receives and sends from/to the next node. The network topology is hence a line topology.

When a frame is transmitted from the IPC, the first node receives the frame through one connector. If the node is the destination of the frame, it will respond back through the same connector. If it is not, it will forward the frame through the second Ethernet port to the next node with a minimum delay.

### 4.4.3.2. Software

#### **B&R Automation Studio**

B&R Automation Studio is an integrated software development environment, which includes tools for all parts of an automation project, making in the foundation for applications of any size and scope.

For every project, several stages are defined: planning, implementation, testing, production, commissioning and service. For every stage, Automation Studio always provides an interface to the machine. Therefore the Automation Studio offers solutions for:

- Creating programs

- Creating visualizations

- Creating motion applications

- Running diagnostics

- Configure communication parameters

For the described system there is a project already implemented, which operates the two described drives. For each drive a specific is created with variables and operation commands.

#### **B&R Automation Runtime**

The target system runs a Windows XP embedded version to manage the devices. This Windows XP version offers Real-Time capabilities. Installed on the IPC the B&R Automation Runtime (ARwin) software is fully embedded in the target system. It allows application programs to access I/O systems and other devices. There are different types of target systems defined by the processor type and architecture used in the system. B&R uses several platforms defined by the generation of the system.

- System Generation 3 (SG3)

- System Generation Compact (SGC)

- System Generation 4 (SG4)

The used system is a SG4 and thus, the applied configurations will be determined by this platform.

# 4.4.4. Real-Time System Configuration