# UNIVERSITAT POLITÈCNICA DE VALÈNCIA De de Informática de Sistemas y Computadores

## Design of Efficient TLB-based Data Classification Mechanisms in Chip Multiprocessors

A DISSERTATION SUBMITTED IN FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY (COMPUTER SCIENCE)

Author:

ALBERT ESTEVE GARCIA

Advisors:

Prof. ANTONIO ROBLES MARTÍNEZ Prof. MARIA ENGRACIA GÓMEZ REQUENA Prof. ALBERTO ROS BARDISA

Valencia, July 2017

### Acknowledgment

Cuatro años de esfuerzo dan para mucho. Echándo la vista atrás, muchas son las personas que me han apoyado, muchos los que me han escuchado. Gracias a todos.

A Ramón y Lola. Sin ellos, sin su apoyo y su amor, no habría llegado hasta aquí. Sin su inspiración no habría siquiera empezado el camino. Ellos plantaron la semilla de la curiosidad, tan necesaria para superar la frustración y las dificultades a las que todo investigador tiene que enfrentar en su camino.

A Víctor. Hermano y amigo. El espejo en el que me miro. Me has dado fuerza en cada etapa de mi vida. Gracias por todo. Habrá que pensar una buena ruta en bici para celebrarlo.

A Carla. Por su paciencia, por su ayuda, por respaldarme cuando lo he necesitado. Siempre me has animado a seguir adelante y has permanecido a mi lado en cada etapa del doctorado. Más que eso, eres uno de los pilares principales de mi vida.

A Salomé, Eloy y Sergio. Por quererme y aceptarme como uno más de la familia. Realmente yo lo siento del mismo modo. Gracias.

A mis amigos. Samuel, Eduardo, Manolo. Ya sea jugando a algún juego, organizándo viajes juntos, o saliendo de fiesta o a tomar algo, siempre habéis estado ahí, siendo partícipes de mis logros y mis frustraciones. Tanto como yo de las vuestras. Y espero que siga siendo así por muchos, muchos años.

Allá por 2007 empezaba mi andadura por la universidad, hace ya diez años. Ésta ha sido mi segunda casa, y le debo mucho. Y tengo muchos que agradecer también a toda la gente que he conocido en este etapa. Incluyendo ésta última fase en el Grupo de Arquitecturas Paralelas.

Por supuesto y ante todo a mis directores, Alberto, Antonio y Maria Engracia. Me habéis guiado e inspirado, desafiado y ayudado en cada etapa de mi doctorado. Vuestra paciencia y esfuerzo han sido claves para la consecución de este trabajo. He aprendido mucho durante estos años. No sólo en materia de arquitectura de computadores, sino también en investigación científica; a amarla, a observar los pequeños detalles, a analizar los datos y entender qué esta ocurriendo para así poder seguir avanzando. Ellos han cambiado mi vida, profesional y personal, para siempre.

A Núria, Salva y Eduardo. No nos vemos tanto como antes, nuestras vidas, sus obligaciones, nos alejan. Pero aún nos quedarán esas tardes de cervezas para ponernos al día. Siempre.

A mis compañeros de laboratorio. José Vicente, José María, Migue, Vicent, Joan, Fran, Javi, Roberto, Carlos, Santi, y un largo etcétera. A los que se fueron, Knut, Mario, Crispín. Tantos y tantos. A todos os debo algo. Lo que ha unido el BoardGameArena que no lo separen nuestras exitosas carreras en el extranjero, como un tren de mercancías desbocado y sin frenos. Y por supuesto a Ricardo. El verdadero pilar del laboratorio, en lo técnico y en lo personal. Tu increible paciencia y dedicación te hacen pieza central del trabajo de todos nosotros en el grupo.

A Stefanos Kaxiras y a toda la gente que conocí en Uppsala. Trevor, David, Alexandra, Andra, etc. As tough as it was, it has been one of the most enriching experiences of my life. I cannot thank you enough. Observing first hand how another research group works really changed my

perspective towards investigation. Specially Kaxiras, your wisdom was inspirational. Thank you all. Already missing the snow.

A.E.

## Contents

|   | Acknowledgment                         | i    |

|---|----------------------------------------|------|

|   | Preface                                | vii  |

|   | List of Acronyms                       | viii |

|   | List of Figures                        | xii  |

|   | List of Tables                         | xvi  |

|   | Abstract                               | xix  |

|   | Resum                                  | XX   |

|   | Resumen                                | xxi  |

|   |                                        |      |

| 1 | Introduction                           | 1    |

|   | 1.1 Context and Motivation             | 1    |

|   | 1.2 Objectives                         | 3    |

|   | 1.3 Thesis Contributions               | 3    |

|   | 1.4 Thesis Outline                     | 6    |

| 2 | Concepts and Background                | 7    |

|   | 2.1 Introduction                       | 7    |

|   | 2.2 Classification-based Optimizations |      |

|   | 2.3 Data Classification Mechanisms     |      |

|   | 2.4 Architecting and Managing TLBs     |      |

|   | 2.4 Architecting and Managing TLDs     | 11   |

| 3 | Simulation Environment                 | 23   |

|   | 3.1 Introduction                       | 23   |

|   | 3.2 Simulation Tools                   | 24   |

|   | 3.3 Simulated System                   | 26   |

|   | 3.4 Metrics                            | 27   |

|     | 3.5 Benchmarks                                            | . 28  |

|-----|-----------------------------------------------------------|-------|

| 4 7 | TLB-based Classification Mechanisms                       | 37    |

|     | 4.1 Introduction                                          | . 37  |

|     | 4.2 TLB Miss Resolution through TLB-to-TLB Transfers      | . 38  |

|     | 4.3 Snooping TLB-based Private-Shared Classification      | . 38  |

|     | 4.4 TLB-based Classification with Distributed Shared TLBs | . 42  |

|     | 4.5 Experimental Results                                  | . 46  |

|     | 4.6 Discussion                                            | . 54  |

|     | 4.7 Conclusions                                           | . 55  |

| 5 [ | Token-counting TLB-based Classification Mechanism         | 57    |

|     | 5.1 Introduction                                          | . 57  |

|     | 5.2 TokenTLB                                              | . 58  |

|     | 5.3 Read-only Data Optimizations and Full-adaptivity      | . 63  |

|     | 5.4 Experimental Results                                  | . 64  |

|     | 5.5 Conclusions                                           | . 71  |

| 6 ] | Prediction-based Classification Mechanisms                | 73    |

|     | 6.1 Introduction                                          | . 73  |

|     | 6.2 Usage Predictor (UP)                                  | . 74  |

|     | 6.3 Shared Usage Predictor (SUP)                          | . 78  |

|     | 6.4 Approaching to the Ideal Scheme                       | . 81  |

|     | 6.5 Experimental Results                                  | . 83  |

|     | 6.6 Conclusions                                           | . 91  |

| 7 ( | Cooperative TLB Page-Usage Prediction Mechanism           | 93    |

|     | 7.1 Introduction                                          | . 93  |

|     | 7.2 Cooperative Usage Predictor (CUP)                     | . 95  |

|     | 7.3 Experimental Results                                  | . 100 |

|     | 7.4 Discussion                                            | . 105 |

|     | 7.5 Conclusions                                           | . 105 |

| 8 ( | Conclusions                                               | 107   |

|     | 8.1 Contributions and Conclusions                         | . 107 |

|     | 8.2 Scientific Publications                               | . 111 |

|     | 8.3 Future Work                                           | 112   |

Bibliography 113

### Preface

The current document has been elaborated with the aim to obtain a PhD degree in Computer Science. This work has been done under the advising and guidance of professors Antonio Robles, Alberto Ros, and Maria Engracia Gómez.

This document can be divided in three parts. The first part introduced the state-of-art in classification approaches and private-based data optimizations.

The second part present all the research work and its evaluation. This research activity has been developed within the Parallel Architectures Group (GAP) in the Department of Computer Engineering (DISCA) at the Universitat Politècnica de València.

In the last part, the contributions and conclusions are summarized.

## List of Acronyms

TLB Translation Lookaside Buffer.

**CS-TLB** Complete Subblock TLB.

PS-TLB Partial Subblock TLB.

**CMP** Chip Multiprocessor.

**NUCA** Non-Uniform Cache Architecture.

**LLC** Last-Level Cache.

**SC** Sequential Consistency.

**ROB** Reorder Buffers.

**TSO** Total Store Ordering.

**RAWR** Read-After-Write Races.

**NSRT** Not Shared Region Table.

**CRH** Cached Region Hash.

${f TC}$  Temporal Coherence.

**DRF** Data Race Free.

$\mathbf{HRF}$  Heterogeneous Race Free.

nDRF Non Data Race Free.

**xDRF** Extended Data Race Free.

**ROB** Reorder Buffers.

**hLRC** Heterogeneous Lazy Release Consistency.

**PR** Private Read-only.

**PW** Private Written.

**SR** Shared Read-only.

**SW** Shared Written.

**OS** Operating System.

**VIPS** Valid/Invalid Private/Shared (set of cache coherence states).

**MOESI** Modified Owned Exclusive Shared Invalid (set of cache coherence states).

MESI Modified Exclusive Shared Invalid (set of cache coherence states).

**SWEL** Shared Written Exclusivity-Level (set of cache coherence states).

**UNITD** Unified Instruction/Translation/Data Coherence.

**DiDi** Dictionary Directory.

**FAC** First Accessing Core.

**TI** Thread Identifying.

VM Virtual Memory.

MMU Memory Management Unit.

**PTE** Page Table Entry.

**PPN** Physical Page Number.

**IPI** Inter-Processor Interrupts.

**PI/VI** Physically/Virtually Indexed.

PT/VT Physically/Virtually Tagged.

**ASID** Address Space Identifier.

**NoC** Network On Chip.

**SLL** Shared Last-Level.

MSHR Miss Status Holding Register.

**GEMS** General Execution-driven Multiprocessor Simulator.

**SLICC** Specification Language for Implementing Cache Coherence.

**CACTI** Cache Access and Cycle Time Information.

**IPC** Instructions Per Cycle.

**PID** Process Identifier.

# List of Figures

| 2.1 | State transition diagram for OS-based classification status                                                                                                                                              | 14 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | State transition diagram for the SWEL protocol                                                                                                                                                           | 15 |

| 2.3 | Example of a translation process (page table walk) in the x86 64                                                                                                                                         | 17 |

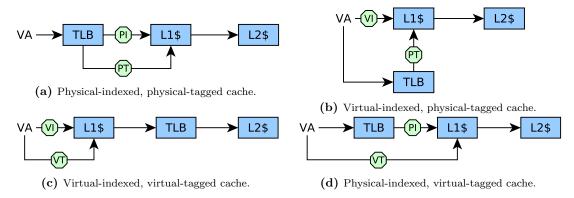

| 2.4 | Diagrams for different cache addressing options                                                                                                                                                          | 18 |

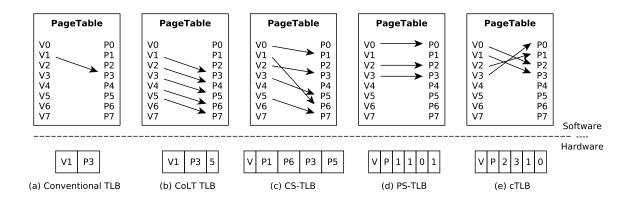

| 2.5 | An illustration of (a) conventional TLB (b) CoLT (c) CS-TLB (d) PS-TLB and (e) cTLB. For each approach, the structure of a single entry and a page table with the PTEs that can be exploited is shown.   | 20 |

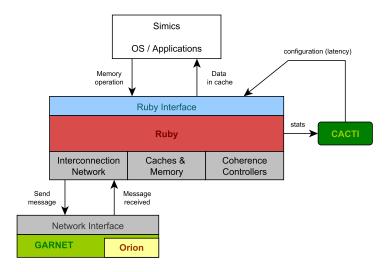

| 3.1 | Relationship between the simulation tools employed                                                                                                                                                       | 24 |

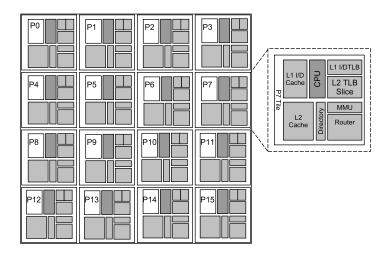

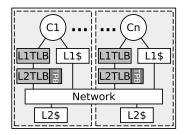

| 3.2 | Baseline tiled CMP architecture with a two-level TLB structure                                                                                                                                           | 26 |

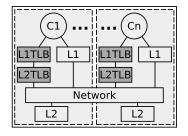

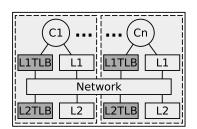

| 3.3 | Private and shared L2 TLB organizations                                                                                                                                                                  | 26 |

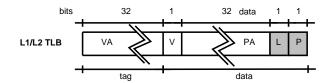

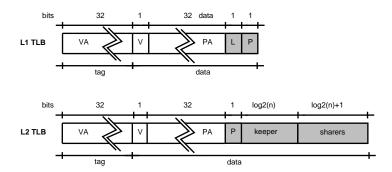

| 4.1 | L1/L2 TLB entry with the extra fields in gray                                                                                                                                                            | 38 |

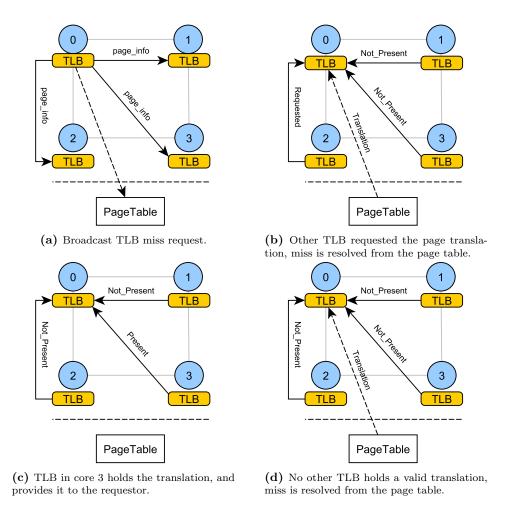

| 4.2 | Different outcomes for TLB-to-TLB requests from C0                                                                                                                                                       | 40 |

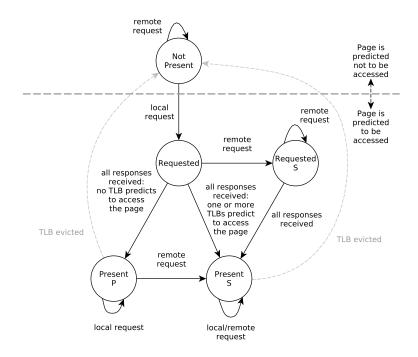

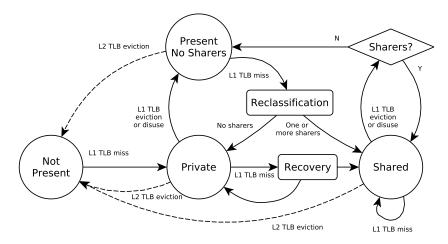

| 4.3 | TLB state transition diagram                                                                                                                                                                             | 41 |

| 4.4 | Shared L2 TLB basic working scheme                                                                                                                                                                       | 43 |

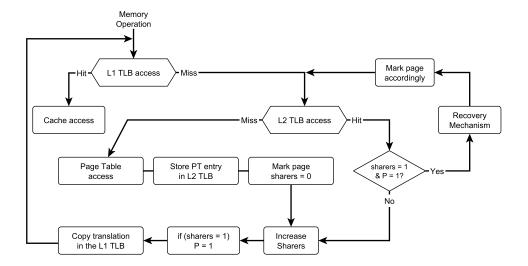

| 4.5 | Block diagram of the general working scheme under a memory operation with DirectoryTLB                                                                                                                   | 44 |

| 4.6 | Directory<br>TLB entries, with the extra field required for classification in gray.<br>$\ .$                                                                                                             | 44 |

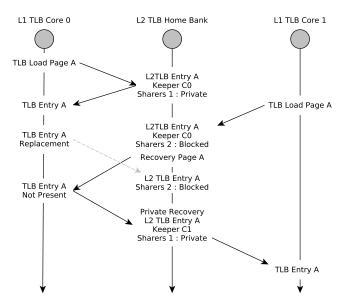

| 4.7 | Coherence recovery mechanism resolved to Private. Page A in the keeper $(C0)$ is evicted prior to receiving the Recovery message and thus, the Recovery is resolved to Private and the keeper is updated | 45 |

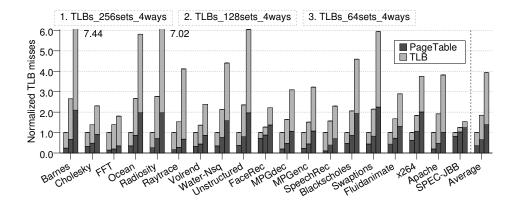

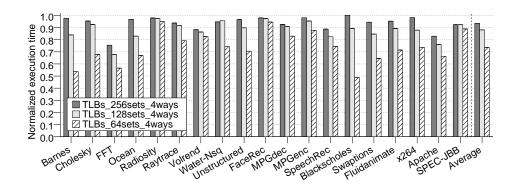

| 4.8  | Distribution of TLB misses resolved by either other TLBs or the page table                          | 46 |

|------|-----------------------------------------------------------------------------------------------------|----|

| 4.9  | Improvements in execution time when using TLB-to-TLB transfers                                      | 47 |

| 4.10 | Variations in network traffic when using TLB-to-TLB transfers                                       | 47 |

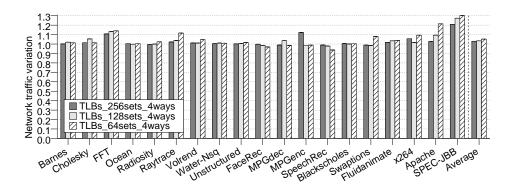

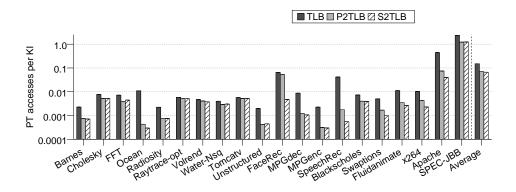

| 4.11 | TLB misses ending up as page table accesses per 1000 instructions. No classification                | 48 |

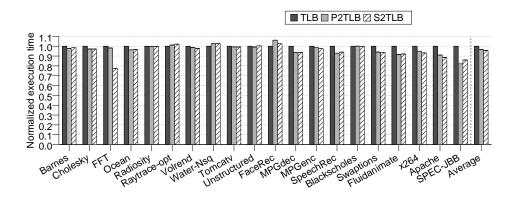

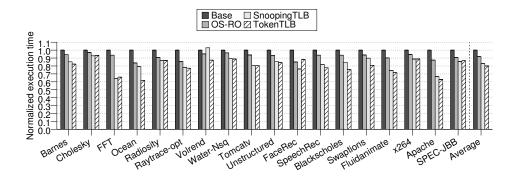

| 4.12 | Execution time normalized to baseline without classification support                                | 48 |

| 4.13 | Normalized traffic attributable to the TLB communication                                            | 49 |

| 4.14 | Private/Shared page classification with private TLBs                                                | 50 |

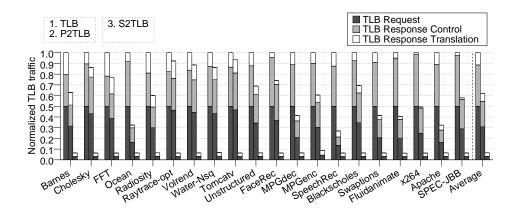

| 4.15 | Average directory entries required per cycle normalized to baseline                                 | 51 |

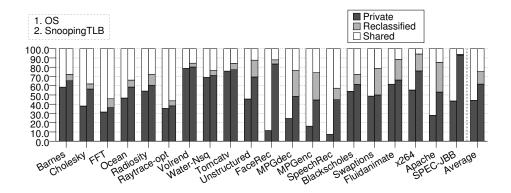

| 4.16 | Normalized data L1 misses classified by its cause                                                   | 51 |

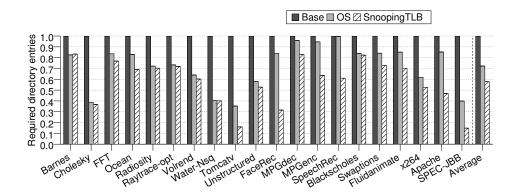

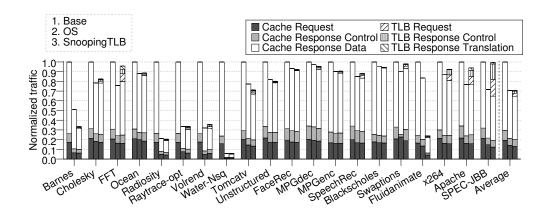

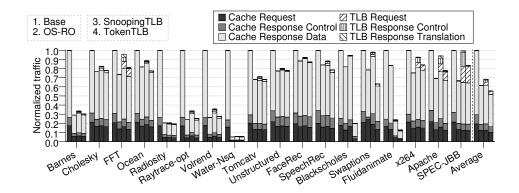

| 4.17 | Network flits injected, classified into cache or TLB-traffic                                        | 52 |

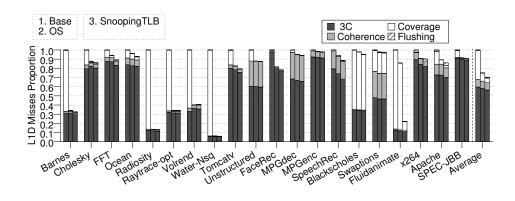

| 4.18 | Execution time normalized to baseline when applied to coherence deactivation.                       | 52 |

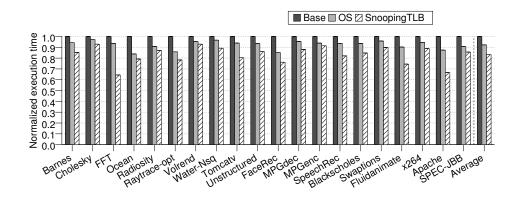

| 4.19 | Average normalized execution time depending on the directory size                                   | 53 |

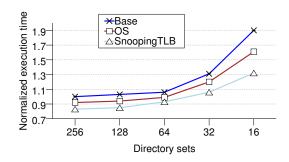

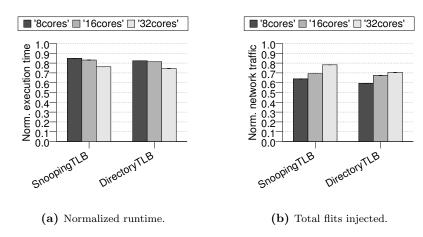

| 4.20 | Scalability analysis of TLB-based classification approaches                                         | 53 |

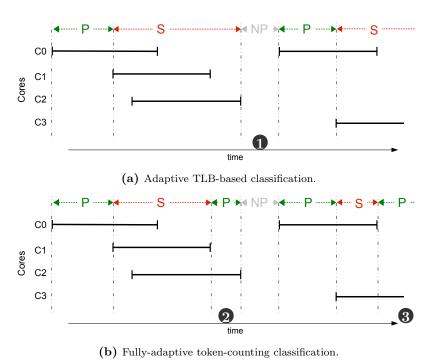

| 5.1  | Adaptivity versus Full-adaptivity in TLB-based classification                                       | 58 |

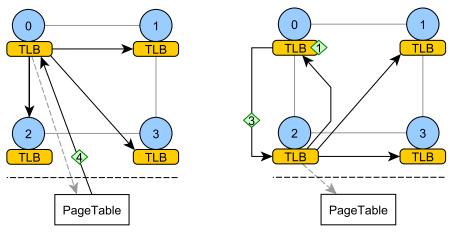

| 5.2  | Token Request example in a 4-core CMP                                                               | 60 |

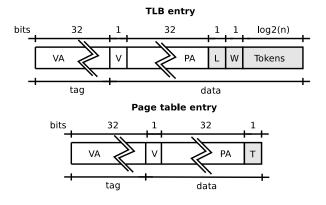

| 5.3  | TLB and page table entry format. Shaded fields represent additional the fields required by TokenTLB | 60 |

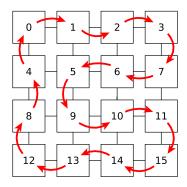

| 5.4  | Path that token messages follow after TLB evictions for a 16-cores (4x4) mesh interconnect          | 61 |

| 5.5  | Logical TPB placement with a private two-level TLB organization                                     | 62 |

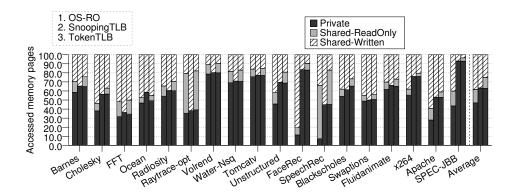

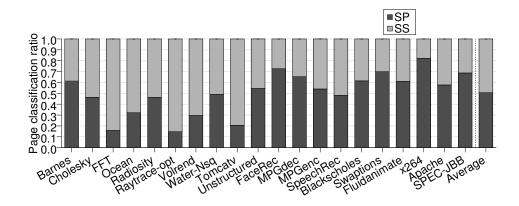

| 5.6  | Private, Shared, and Written page proportion                                                        | 64 |

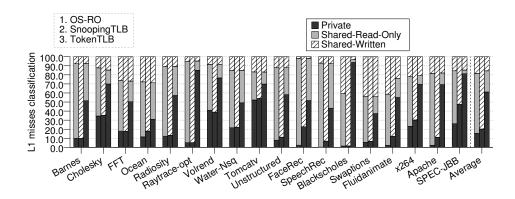

| 5.7  | Data L1 Misses proportion classified as Private, Shared-Read-Only and Shared-Written                | 65 |

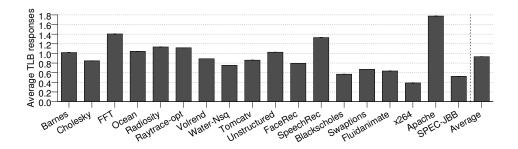

| 5.8  | Proportion of TLB Responses issued after an L2 TLB miss                                             | 66 |

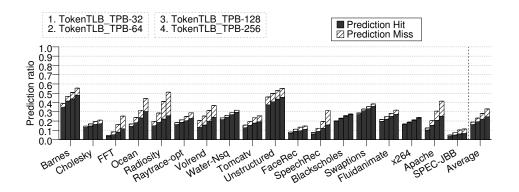

| 5.9  | Success rate for TPB predictions                                                                    | 66 |

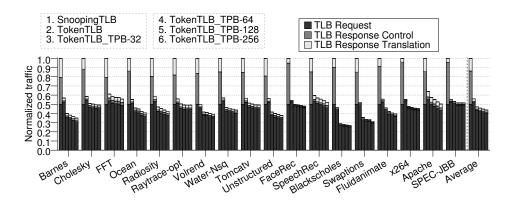

| 5.10 | Relative TLB network traffic issued                                                                 | 67 |

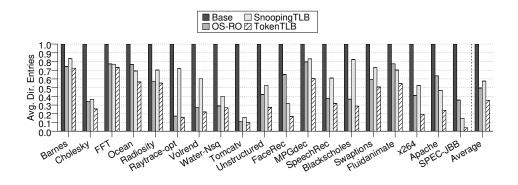

| 5.11 | Average directory entries allocated per cycle                                                       | 68 |

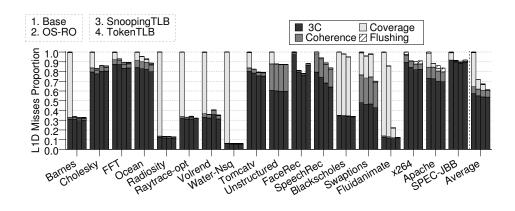

| 5.12 | Data L1 Misses classified by its cause                                                   | 68 |

|------|------------------------------------------------------------------------------------------|----|

| 5.13 | Network flits injected, classified into cache- or TLB-traffic                            | 69 |

| 5.14 | Execution time normalized to baseline                                                    | 69 |

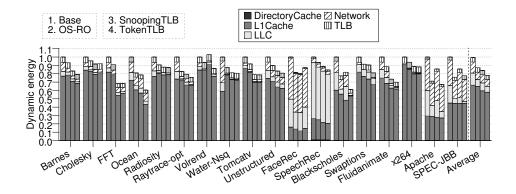

| 5.15 | Dynamic energy consumption normalized to the base system                                 | 70 |

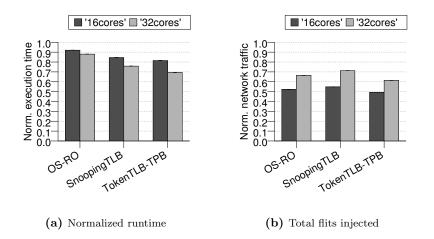

| 5.16 | Scalability analysis of classification approaches when applied to coherence deactivation | 70 |

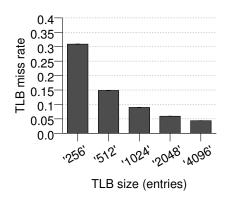

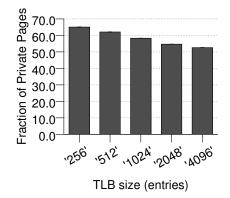

| 6.1  | TLB size analysis overview                                                               | 73 |

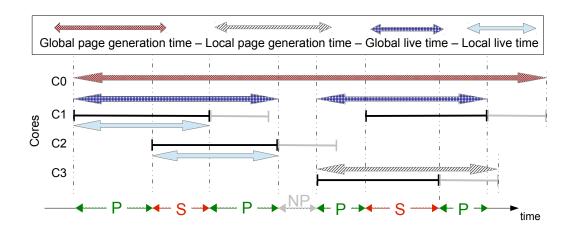

| 6.2  | Page idealization: generation and live times                                             | 75 |

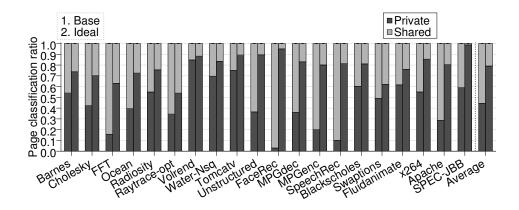

| 6.3  | Idealized page classification comparison                                                 | 76 |

| 6.4  | Page lives classification of shared pages                                                | 77 |

| 6.5  | TLB state transition diagram with forced-sharing UP                                      | 78 |

| 6.6  | L1 and L2 TLB entries, with the SUP fields in gray                                       | 78 |

| 6.7  | Block diagram of the general working scheme with SUP under a memory operation.           | 79 |

| 6.8  | L2 TLB classification state diagram with SUP                                             | 80 |

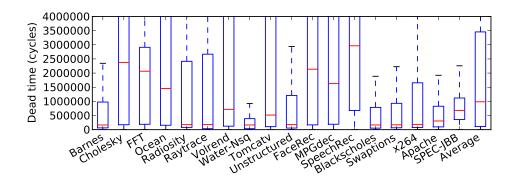

| 6.9  | Average time (cycles) from last access to a page in a core to its eviction in the TLB    | 81 |

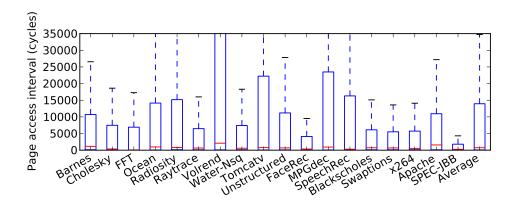

| 6.10 | Average time (cycles) between TLB accesses                                               | 82 |

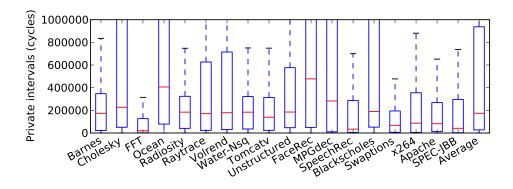

| 6.11 | Cycles spent as private on a global live                                                 | 82 |

| 6.12 | Comparative analysis: UP on top of SnoopingTLB or TokenTLB                               | 83 |

| 6.13 | Normalized execution time when increasing core count                                     | 84 |

| 6.14 | Network flits issued when increasing core count                                          | 84 |

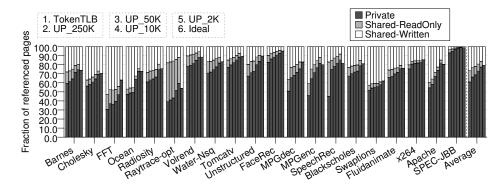

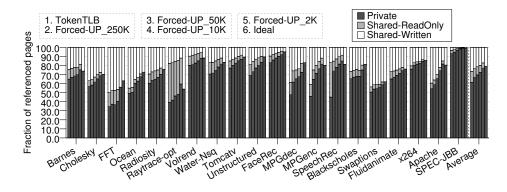

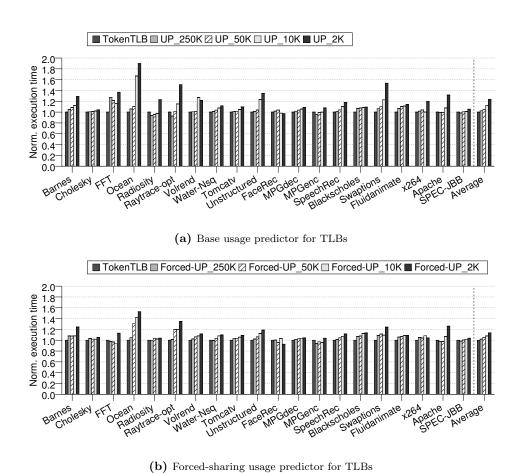

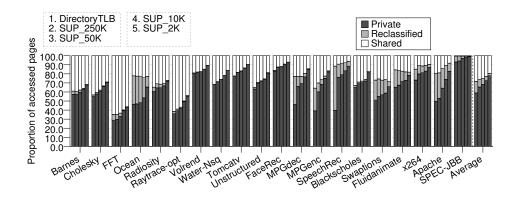

| 6.15 | Private-shared and read-only page classification                                         | 85 |

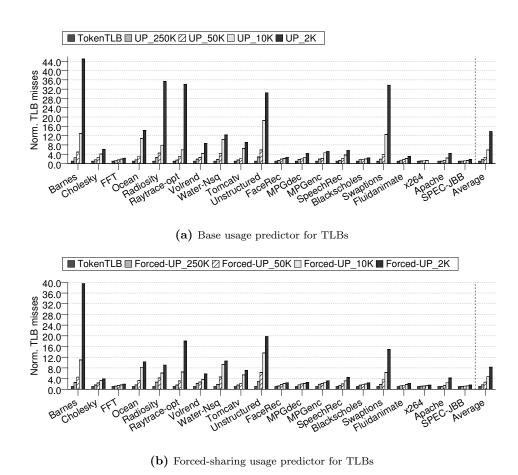

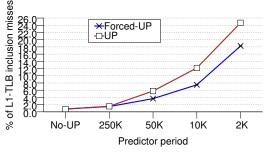

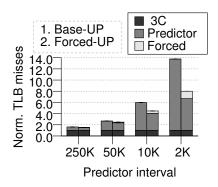

| 6.16 | Proportion of prediction-induced TLB misses                                              | 86 |

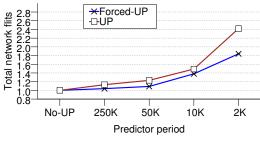

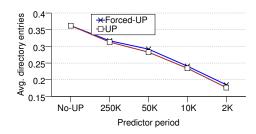

| 6.17 | Base UP versus Forced-sharing UP                                                         | 87 |

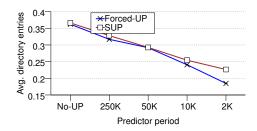

| 6.18 | Average directory entries per cycle for Base- and Forced-UP                              | 87 |

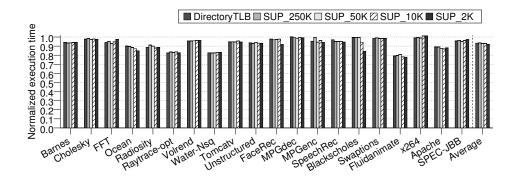

| 6.19 | Execution time normalized to baseline                                                    | 88 |

| 6.20 | Private/shared page classification with distributed shared last-level TLB                | 89 |

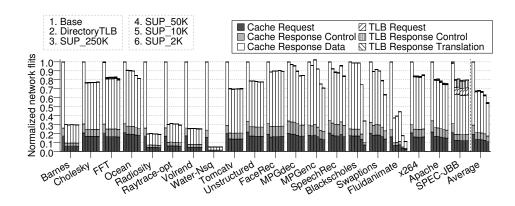

| 6.21 | Total flits injected with SUP applied to coherence deactivation                                                                                                                  | 89  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.22 | Average directory entries stored per cycle with SUP                                                                                                                              | 90  |

| 6.23 | Execution time under coherence deactivation normalized to a shared TLB baseline with SUP                                                                                         | 91  |

| 7.1  | TLB misses considering its cause                                                                                                                                                 | 94  |

| 7.2  | Prediction-based classification examples                                                                                                                                         | 95  |

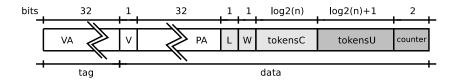

| 7.3  | TLB entry format for the cooperative usage predictor (extra fields in grey)                                                                                                      | 96  |

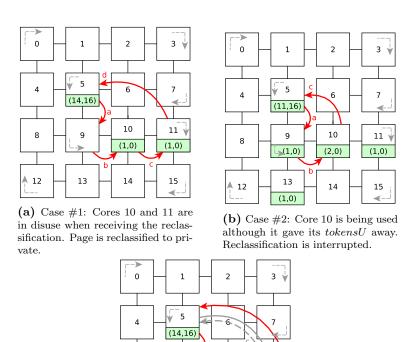

| 7.4  | Different outcomes for cruise-missile reclassifications initiated by the TLB in core 5. The grey dashed arrows depict the route followed by CMR messages across the virtual ring | 98  |

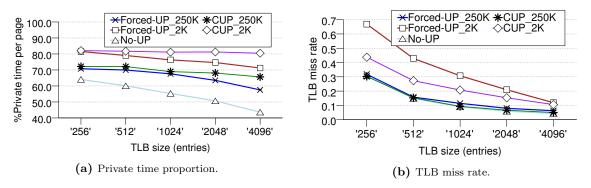

| 7.5  | TLB size and usage prediction analysis                                                                                                                                           | 100 |

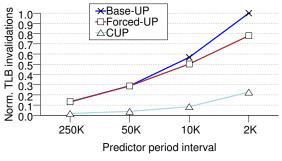

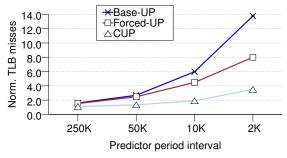

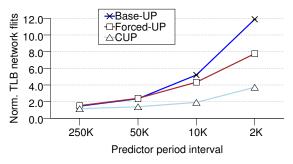

| 7.6  | Miss-prediction overhead analysis: UP against CUP                                                                                                                                | 101 |

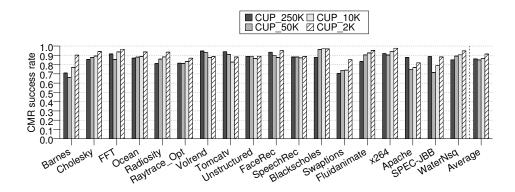

| 7.7  | CMR tryouts that successfully transition the page to private                                                                                                                     | 102 |

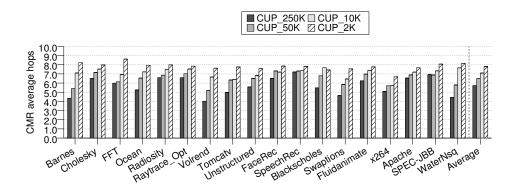

| 7.8  | Average number of steps for CMR messages                                                                                                                                         | 102 |

| 7.9  | CMR messages issued per TLB miss                                                                                                                                                 | 103 |

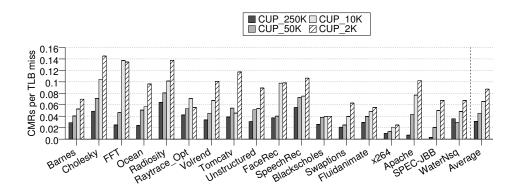

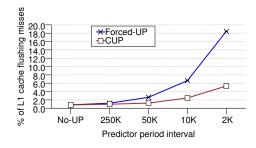

| 7.10 | Proportion of L1 cache flushing misses                                                                                                                                           | 103 |

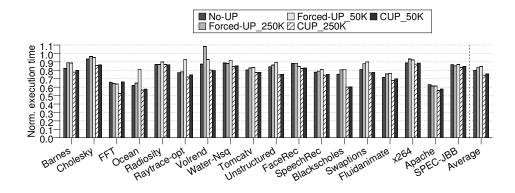

| 7.11 | Execution time normalized to baseline without coherence deactivation                                                                                                             | 104 |

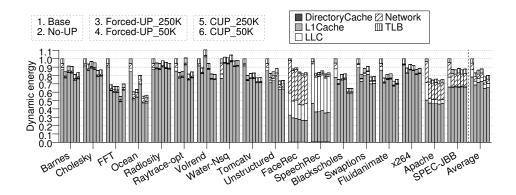

| 7.12 | Normalized dynamic energy consumption in the cache hierarchy                                                                                                                     | 104 |

## List of Tables

| 2.1 | Properties of classification schemes                     | 16 |

|-----|----------------------------------------------------------|----|

| 3.1 | System parameters for the baseline system                | 25 |

| 3.2 | Benchmarks and input sizes                               | 29 |

| 4.1 | Response messages and state transitions for TLB requests | 39 |

| 4.2 | Actions due to TLB-cache inclusion and recovery          | 41 |

#### Abstract

Most of the data referenced by sequential and parallel applications running in current chip multiprocessors are referenced by a single thread, i.e., private. Recent proposals leverage this observation to improve many aspects of chip multiprocessors, such as reducing coherence overhead or the access latency to distributed caches. The effectiveness of those proposals depends to a large extent on the amount of detected private data. However, the mechanisms proposed so far either do not consider either thread migration or the private use of data within different application phases, or do entail high overhead. As a result, a considerable amount of private data is not detected. In order to increase the detection of private data, this thesis proposes a TLB-based mechanism that is able to account for both thread migration and private application phases with low overhead. Classification status in the proposed TLB-based classification mechanisms is determined by the presence of the page translation stored in other core's TLBs. The classification schemes are analyzed in multilevel TLB hierarchies, for systems with both private and distributed shared last-level TLBs.

This thesis introduces a page classification approach based on inspecting other core's TLBs upon every TLB miss. In particular, the proposed classification approach is based on exchange and count of tokens. Token counting on TLBs is a natural and efficient way for classifying memory pages. It does not require the use of complex and undesirable persistent requests or arbitration, since when two or more TLBs race for accessing a page, tokens are appropriately distributed classifying the page as shared.

However, TLB-based ability to classify private pages is strongly dependent on TLB size, as it relies on the presence of a page translation in the system TLBs. To overcome that, different TLB usage predictors (UP) have been proposed, which allow a page classification unaffected by TLB size. Specifically, this thesis introduces a predictor that obtains system-wide page usage information by either employing a shared last-level TLB structure (SUP) or cooperative TLBs working together (CUP).

#### Resum

La major part de les dades referenciades per aplicacions paral·leles i seqüencials que s'executen en CMPs actuals són referenciades per un sol fil, és a dir, són privades. Recentment, algunes propostes aprofiten aquesta observació per a millorar molts aspectes dels CMPs, com és reduir el sobrecost de la coherència o la latència d'accés a memòries cau distribuïdes. L'efectivitat d'aquestes propostes depen en gran mesura de la quantitat de dades detectades com a privades. No obstant això, els mecanismes proposats fins a la data no consideren la migració de fils d'execució ni les fases d'una aplicació. Per tant, una quantitat considerable de dades privades no es detecta apropiadament. A fi d'augmentar la detecció de dades privades, aquesta tesi proposa un mecanisme basat en les TLBs, capaç de reclassificar les dades com a privades, i que detecta la migració dels fils d'execució sense afegir complexitat al sistema. Els mecanismes de classificació en les TLBs s'han analitzat en estructures de diversos nivells, incloent-hi sistemes amb TLBs d'últim nivell compartides i distribuïdes.

Aquesta tesi presenta un mecanisme de classificació de pàgines basat en inspeccionar les TLBs d'altres nuclis després de cada fallada de TLB. Concretament, el mecanisme proposat es basa en l'intercanvi i el compte de tokens. Comptar tokens en les TLBs suposa una forma natural i eficient per a la classificació de pàgines de memòria. A més, evita l'ús de sol·licituds persistents o arbitratge, ja que si dues o més TLBs competeixen per a accedir a una pàgina, els tokens es distribueixen apropiadament i la classifiquen com a compartida.

No obstant això, l'habilitat dels mecanismes basats en TLB per a classificar pàgines privades depenen de la grandària de les TLBs. La classificació basada en les TLBs resta en la presència d'una traducció en les TLBs del sistema. Per a evitar-ho, s'han proposat diversos predictors d'ús en les TLBs (UP), els quals permeten una classificació independent de la grandària de les TLBs. Específicament, aquesta tesi introdueix un predictor que obté informació d'ús de la pàgina a escala de sistema mitjançant un nivell de TLB compartida (SUP) or mitjançant TLBs cooperant juntes (CUP).

#### Resumen

La mayor parte de los datos referenciados por aplicaciones paralelas y secuenciales que se ejecutan en CMPs actuales son referenciadas por un único hilo, es decir, son privados. Recientemente, algunas propuestas aprovechan esta observación para mejorar muchos aspectos de los CMPs, como por ejemplo reducir el sobrecoste de la coherencia o la latencia de los accesos a cachés distribuidas. La efectividad de estas propuestas depende en gran medida de la cantidad de datos que son considerados privados. Sin embargo, los mecanismos propuestos hasta la fecha no consideran la migración de hilos de ejecución ni las fases de una aplicación. Por tanto, una cantidad considerable de datos privados no se detecta apropiadamente. Con el fin de aumentar la detección de datos privados, proponemos un mecanismo basado en las TLBs, capaz de reclasificar los datos a privado, y que detecta la migración de los hilos de ejecución sin añadir complejidad al sistema. Los mecanismos de clasificación en las TLBs se han analizado en estructuras de varios niveles, incluyendo TLBs privadas y con un último nivel de TLB compartido y distribuido.

Esta tesis también presenta un mecanismo de clasificación de páginas basado en la inspección de las TLBs de otros núcleos tras cada fallo de TLB. De forma particular, el mecanismo propuesto se basa en el intercambio y el cuenteo de tokens (testigos). Contar tokens en las TLBs supone una forma natural y eficiente para la clasificación de páginas de memoria. Además, evita el uso de solicitudes persistentes o arbitraje alguno, ya que si dos o más TLBs compiten para acceder a una página, los tokens se distribuyen apropiadamente y la clasifican como compartida.

Sin embargo, la habilidad de los mecanismos basados en TLB para clasificar páginas privadas depende del tamaño de las TLBs. La clasificación basada en las TLBs se basa en la presencia de una traducción en las TLBs del sistema. Para evitarlo, se han propuesto diversos predictores de uso en las TLBs (UP), los cuales permiten una clasificación independiente del tamaño de las TLBs. En concreto, esta tesis presenta un sistema mediante el que se obtiene información de uso de página a nivel de sistema con la ayuda de un nivel de TLB compartida (SUP) o mediante TLBs cooperando juntas (CUP).

### Chapter 1

### Introduction

This chapter briefly describes the context in which this dissertation is set and the reasons that have motivated it (Section 1.1). Then, we define the objectives aimed by this dissertation (Section 1.2). Following, we show the contributions that such objectives have originated (Section 1.3). Finally, we outline the structure of the remaining chapters in this dissertation (Section 1.4).

#### 1.1 Context and Motivation

Gordon E. Moore stated in 1965 that the number of transistors in a dense integrated circuit doubles every two years, since transistors get smaller every successive technology. This prediction, referred to as Moore's Law, proved accurate for many decades, where computers have rapidly evolved.

Currently, most high-performance processors are compound by billions of transistors, commonly organized by integrating multi- and many-core systems into a single chip (i.e., chip multiprocessors or CMPs). Core count on these CMPs is rapidly growing to cope with Moore's Law. Most architectures already offer quad-core processors, reaching up to dozens of processors. For instance, Intel has recently presented a 72-core CMP [34], or the Kalray's MPPA2 with up to a 256-core processor [38]. These large-scale CMPs are organized as tiled architectures, designed as arrays of identical or nearly-identical blocks, namely tiles. CMP tiles are compound of one or several cores, one or several levels of caches, and a network interface (router) connecting all tiles in a point-to-point interconnect. The cores of a tiled CMP usually share one or more memory modules, constituted into shared-memory multiprocessors. In this context, a cache coherence protocol is required so the memory is accessed consistently from different processors. Hence, as long as the number of cores rapidly grows, implementing low-latency and scalable coherence protocols in shared-memory CMPs leads to new challenges for future CMP architectures.

On the one hand, *snooping-based* protocols send broadcast requests to all other system' processors through a bus, or bus-like interconnect. Thus, even though snooping-based protocols provide low-latency cache-to-cache misses, the bandwidth requirements for protocols grow ex-

ponentially with the core count. Consequently, snooping protocols are only suitable on small core-count CMPs. Nonetheless, there are many approaches which try to reduce the traffic generated [19, 9, 43, 44], but scaling to larger systems is still troublesome.

On the other hand, directory-based protocols send requests to the home directory memory, which track the sharers of each memory block. Then, the directory responds with data or forwards the request to the appropriate processor(s). Therefore, directory-based approaches require less network bandwidth, representing a more scalable solution. However, consulting the directory implies an indirection that is placed in the critical path. Furthermore, the directory structure employed increases on-chip area and leakage power as the core count grows. Many proposals try to address the directory scalability problem [89, 27, 74, 22, 88, 11, 26] in order to scale to large-scale CMPs.

Another important design aspect of CMPs is the organization of the last-level cache (LLC). The wire delay latency of accessing each particular cache bank of a multi-banked shared memory prevails over the access latency to the bank itself. This design choice is referred to as *NUCA* (Non-Uniform Cache Architecture) structure. NUCA caches are designed to reduce the number of off-chip accesses [41]. However, NUCA access latency is strongly dependent on the cache bank where a particular block is mapped. Consequently, the average access latency to NUCA caches increases with the number of cores, jeopardizing their scalability. Some works have addressed this inefficiency [21, 49, 31, 32].

Among the approaches tackling the scalability problem for future CMPs, some increasingly appealing solutions try to discern the private (i.e., accessed by only one thread) or shared (i.e., accessed by two or more threads) nature of accessed data, since they provide a wide range of data optimizations to improve coherence protocols and the organization of the LLC. For instance, Cuesta et al. propose Coherence Deactivation, which identifies private [22] and read-only [23] (non-coherent) blocks, and avoids storing those blocks in the directory cache, since they do not require coherence maintenance. Therefore, directories exploit their limited storage capacity more efficiently and their access latency is reduced. Alternatively, Hardavellas et al. [31] and Li et al. [46, 48] keep private blocks in the NUCA bank of the requesting processor to reduce the access latency to NUCA caches. Ros and Kaxiras [71] propose an efficient and simple cache coherence protocol by implementing a write-back policy for private blocks and a write-through policy for shared blocks. Finally, End-to-End SC [79] allows instruction reordering and out-of-order commits of private accesses from the write-buffers, since they do not affect the consistency model enforced by the system.

The observation behind these proposals is that most referenced data both for sequential and parallel workloads are private. Therefore, data optimizations are commonly applied to private blocks (i.e., private-based optimizations). As a consequence, the effectiveness of most classification-based data optimizations relies on the amount of private data detected. However, although being a decisive factor, some previous proposed classification mechanisms do not provide runtime classification (e.g., classification status is obtained at compile time), which limits the precision of the mechanism. Moreover, some classification approaches do not detect shared-to-private transitions (i.e., non-adaptive classification) [22, 31, 43]. Non-adaptive approaches may miss-classify most accessed data as shared at some point in applications running for a long time, ultimately neglecting the advantages of the classification. Discern store memory operations allows determine read-only data, which represents a 82 percent (on average) of the memory blocks accessed [23]. Therefore, detecting read-only data significantly improves the potential of a classification mechanism. Finally, some classification approaches store the data sharing status in the cache or the directory structures [11, 25, 33, 62, 88], limiting the applicability of the classification, since the private-shared information is obtained after the cache miss.

In order to cope with these drawbacks, this thesis introduces a novel family of page classification mechanisms relying on the presence of the page translation in the system translation lookaside buffers (TLBs), namely *TLB-based* classification. TLB-based classification exploits proximity of cores in a CMP, scrutinizing other system' TLBs through fast core-to-core communication upon every TLB miss, retrieving the page sharing information alongside the page translation entry. This way, TLB-based classification mechanisms accelerate the page table walk process while performing a page-level data classification.

#### 1.2 Objectives

This section presents the objectives of this dissertation. Classification approaches improve system performance and scalability mainly through private-based data optimizations. Thus, the higher the amount of private data detected, the more the benefits obtained from the optimization applied. The main goal is to avoid all classification overheads, while pursuing all desirable properties for classification approaches. In order to achieve this goal, some specific objectives need to be accomplished:

- Design new classification alternatives in order to efficiently perform a runtime classification based on the presence of translation entries in the system' TLBs, while accelerating page translation process through TLB-to-TLB transfers.

- Detect shared-to-private transitions in order to improve private detection according to the current page access pattern, resulting in what we call a temporality-aware classification scheme.

- Thoroughly analyze page lifetimes on TLBs in order to determine an ideal classification, settled by the concurrence of accesses to a page.

- Design a prediction mechanism in order to bring TLB-based classification accuracy closer to the ideal.

- Test the benefits of our classification mechanisms through different data optimization techniques, providing evidences that affirm TLB-based classification as the best suited approach for data classification.

#### 1.3 Thesis Contributions

The aforementioned objectives have originated several contributions, which are briefly summarized in this section.

#### 1.3.1 TLB-based Classification Mechanisms

The TLB-based classification mechanisms proposed in this thesis are a new family of protocols designed to dynamically discern the sharing status of the data based on the presence of page translations in the system TLBs. Therefore, the classification is at page granularity. TLBs are employed to store the classification information. Different TLB-based classification approaches have been proposed:

#### Snooping TLB-based classification

This thesis rests on a Snooping TLB-based classification, or SnoopingTLB, as a starting point. The goal of SnoopingTLB is to achieve an adaptive classification that accounts for temporarily-private pages and tolerates thread migration. The TLB-based classification mechanism is based on inquiring the other cores' TLBs in the system (through TLB-to-TLB requests) on every TLB miss. TLBs reply to the requester indicating whether or not they are caching the page translation, which is included in the response if they do, thus accelerating the table page walking process. This way, the TLB suffering the miss naturally discovers whether blocks belonging to a page may be currently stored on a remote cache and therefore the page is shared, or, on the contrary, no TLB is currently storing the translation and the page is private. TLB-to-TLB transfers are based upon the observation that core-to-core communication in CMPs is much faster compared to traditional processors. Other works also benefit from this observation with different aims [63, 81]. Snooping TLB-based classification targets purely-private, single or multilevel TLB structures.

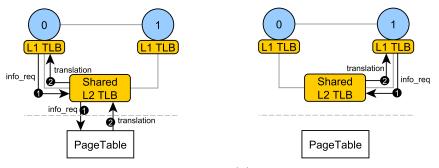

#### TLB-based classification with a shared last-level TLB

We exploit the use of a distributed shared last-level TLB structure (DirectoryTLB) similar to the NUCA cache organization [42], performing a page-level classification while avoiding most TLB traffic overheads of the snooping TLB-based classification approach. Such a distributed TLB organization has been previously suggested [47], however it has not been extensively explored. The shared TLB structure is accessed after every TLB miss and eviction, offering up-to-date sharing information. Note that this scheme has some similarities to a cache directory in the context of cache coherence, and thus its name.

#### Token-counting TLB-based classification

Token-counting classification, namely *TokenTLB*, is a novel classification mechanism implemented directly in the TLB structure and inspired by Token coherence [51, 53, 55] protocols. TokenTLB is based on the observation that, unlike Token coherence, applying tokens for classification does not require issuing persistent requests nor complex arbitration mechanisms. Persistent requests are a special type of request meant to solve races occasionally caused when several cores want to write data at the same time. These requests are a source of complexity for the coherence protocol, possibly being one of the main causes why Token coherence has not been implemented in commodity systems. However, TokenTLB avoids these races by only aiming at classifying data. When two or more TLBs race for accessing the same page, tokens are naturally distributed among the TLBs, and the page will be consequently classified as shared.

TokenTLB reduces network consumption compared to snooping TLB-based proposals. Only TLBs holding extra tokens provide them along with the page translation, which leads to about one response per TLB miss. Furthermore, token-based classification makes it possible to naturally and immediately identify a shared TLB page entry transitioning to private, improving private detection over any other TLB-based classification approach in this dissertation.

#### 1.3.2 Prediction-based Classification Mechanisms

TLB-based classification is determined by the presence of page entries in TLBs, despite the fact that they may have ceased to be accessed. This makes classification accuracy sensitive to the TLB size. Ideally, the sharing condition of a page should be settled by the concurrence of accesses to that page. Therefore, decoupling classification from TLB size in TLB-based classification mechanisms requires a mechanism able to predict whether a page is going to be accessed or not in the near future. To this aim, different prediction approaches have been proposed.

#### Usage predictor for TLBs (UP)

This prediction strategy represents another starting point in this thesis, resembling the one employed in the Cache Decay approach [40]. UP determines whether or not a page is going to be accessed in the near future. In particular, the predictor uses one saturated counter per TLB entry that is periodically increased according to an internal period (i.e., predictor period) and reset on every memory access to the page. When a TLB entry is predicted not to be used (its counter is saturated) and it is probed with a TLB-to-TLB request, the entry is invalidated. When a TLB entry is invalidated, the core is disqualified as a potential sharer of the page. This way, the usage predictor effectively increases the amount of private data detected for large or multilevel TLBs.

#### Forced-sharing usage predictor

Employing shorter periods for usage predictions may prematurely invalidate more translations, which in turn causes the TLB miss rate to rocket, producing more network inquiries, and ultimately, invalidating even more TLB entries. It can be seen as a positive feedback situation, or ping-pong invalidations when only two nodes are involved.

In order to avoid ping-pong invalidations, which could make the TLB usage predictor unattractive, a slight modification of the prediction strategy is introduced, namely *Forced Sharing*. The forced-sharing strategy avoids prediction-induced invalidations after the first prematurely invalidated entry is detected. A translation entry is considered prematurely invalidated when the page is reaccessed soon after being invalidated (i.e., the invalidated entry is still in the TLB). In order to avoid further miss-predicted page invalidations in other cores' TLBs, a special *forced-sharing* TLB miss request is sent. This request overrides the prediction, and grants a classification based solely on the presence of page translation entries in other TLBs.

Shared usage predictor (SUP)

As part of our proposed DirectoryTLB classification scheme for shared last-level TLBs, we attune UP to the new environment, namely Shared Usage Predictor (SUP). The key observation in this work is that invalidations caused by the previous predictors do not necessarily lead to higher detection of private pages. In fact, many TLB entry invalidations just reduce the number of sharers, indiscriminately increasing TLB miss rate, without the certainty of improving the amount of private data. Hence, UP is applied blindly, without considering how the classification status will evolve, despite being supposedly at its service.

SUP relies on the shared second-level TLB in order to track the sharers count, and announces a page sharer falling into disuse to the home TLB tile as soon as is predicted as so. This way, translation invalidations are only performed when the shared second-level TLB discerns a reclassification opportunity, improving prediction accuracy, acting as a natural filter to blind TLB invalidations, and avoiding most prediction overheads.

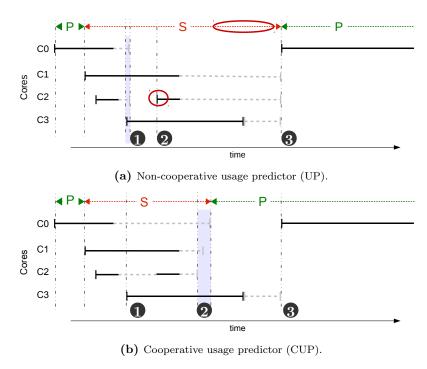

Cooperative usage predictor (CUP)

SUP averts invalidating translations based only on their local usage prediction, based on the information stored in the classification directory (i.e., a shared last-level NUCA-like TLB level). Similarly, in order to improve the prediction accuracy for purely-private TLB structures, Cooperative Usage Predictor (CUP) has been proposed. CUP exploits TLB cooperation (i.e., TLBs willingly working together for a common purpose or benefit) in order to: (i) perform a system-wide page usage prediction instead of a per-core prediction, naturally discovering reclassification opportunities without relying either on other TLBs requesting the page or the presence of a shared last-level TLB; (ii) neglect most aimlessly invalidated TLB entries, as invalidation is postponed until it may expressly serve a better data classification, avoiding performance degradation.

#### 1.4 Thesis Outline

This dissertation starts with the introductory chapter (Chapter 1). Following, Chapter 2 describes the background of data classification, presenting the main classification alternatives constituting the current state of the art. The simulation environment is described in Chapter 3. Chapter 4 presents and evaluates snooping TLB-based classification approaches for different single and multilevel TLB structures. Then, Chapter 5 introduces the token-counting TLB-based classification approach. Usage prediction is first introduced in Chapter 6, and extended with our Cooperative Usage Predictor in Chapter 7. This dissertation ends with Chapter 8, summarizing the conclusions and displaying the main contributions to the research field.

### Chapter 2

## Concepts and Background

This chapter presents the basics and terminology for private-shared data classification and private-based optimizations. For the sake of brevity we cover the main concepts, giving insight on the classification approaches assumed in this thesis.

#### 2.1 Introduction

First, this chapter describes some private-based data optimizations to show the interest of performing a private-shared classification in Section 2.2. Next, we discuss the state-of-the-art classification alternatives (Section 2.3) and how they fit into the desirable features for classification mechanisms (Section 2.3.1). Finally, some virtual address space concepts are introduced, along with some techniques to improve TLB performance, in Section 2.4.

### 2.2 Classification-based Optimizations

Data classification mechanisms are gaining interest as they allow many optimizations regarding hardware management of CMP components such as caches, interconnect or coherence protocols, based on their sharing status. For instance, while all cache protocols assume that all the accessed data may be shared at any time, data will not require coherence maintenance while being private. There are many other recent examples in the literature showing the large variety of optimization for a classification scheme that discerns the private (or read-only) nature of data. This section describes some of key classification-based data optimizations.

#### 2.2.1 Interconnect Optimizations

In bus snooping protocols there is no tracking information about block sharing, and thus every cache coherence request needs to be broadcast to all nodes. Therefore, snooping-based protocols are commonly faster than directory solutions for cache coherence, since they avoid indirections. However, their main disadvantage is their limited scalability. On the one hand, frequent snooping causes message racing, which increases cache access time and consumption. On the other hand, network bandwidth for broadcasts grows rapidly with the number of cores.

#### RegionScout

In snooping-based protocols broadcast on private memory is unnecessary, as it will result in a global miss. Moshovos [57] proposed RegionScout, a family of filters for *snooping* coherence protocols that avoid requesting, receiving or forwarding non-coherent data through broadcast messages when accessing private blocks, ultimately constraining network bandwidth, latency and consumption.

RegionScout filters comprise two structures local to each node: (i) a not shared region table (NSRT), a very small, cache-like structure storing regions (contiguous memory space that is power of two size) that are known to be not shared; and (ii) a cached region hash (CRH), a filter that records superset of all regions locally cached.

Whenever a node issues a memory request for a block for the first time, other nodes respond as corresponds to the coherence protocol, but including information regarding any other cached blocks for the same region as the block that has been requested. The node that caused the miss records the region in its NSRT, which resolves the block status as not shared. Following misses within the same region by the same node will result in private accesses, avoiding the coherence broadcast. Then, if a different node requests a block within the same region (which would miss in its own NSRT), the existing NSRT entry must be invalidated in order to ensure correctness.

The CRH structure represents an up-to-date imprecise record of regions that are locally cached. Basically, CRH is a counter for each hashed region, that is increased after every L2 cache miss within a given region and decreased after every L2 cache eviction. This way, after receiving a coherence request, a given node consults its CRH to know if the access results in a region miss or if it may have blocks stored.

#### Subspace Snooping

Kim et al. [43] propose Subspace Snooping, which extends RegionScout by tracking the sharers of a page, and snoop requests are sent only to those nodes in the subspace through a multi-cast message. Subspace Snooping maintains the page status by combining updates of page table entries and TLB entries. Therefore, it allows fast accessing the sharing information without requiring extra hardware support. Furthermore, sharing information is extended with a bitmap (i.e., sharing vector), tracking the sharers of each page. After every TLB miss the fine-grain sharing information is updated both in the page table and the TLBs.

If pages cease being accessed from a given core (e.g., all its stored blocks are evicted), the information kept in the sharing vector may be outdated, as it still accounts for the obsolete sharers. This information is considered as subspace pollution, and need to be dynamically addressed. To do so, a TLB may remove itself from the sharing vector after evicting from

the local cache the last cacheline of a given page. The corresponding TLB entry must also be invalidated. To check whether a page is cached or not, a counting bloom filter-based technique [18] is employed.

#### 2.2.2 Cache Optimizations

This section presents some cache optimizations which aim is to improve cache access latency and avoid address translation latency by discerning the sharing nature of the accessed data.

#### Reactive NUCA

While a NUCA cache is a common design for last-level caches (LLC), increasingly on-chip wire latency might as much as halve the potential performance on server workloads. Hardavellas *et al.* [31] and Kim *et al.* [46, 48] propose a mechanism where private blocks are kept on the local (or close to local –neighboring) NUCA bank, and replicates distant shared blocks in order to reduce access latency and balance capacity constraints. Consequently, block mapping in R-NUCA is guided by its classification:

- Logically divides the LLC into overlapping clusters of neighboring slices, replicating instructions at cluster granularity. The cluster size allows trading off access latency to instruction blocks for cache capacity. Small clusters provide low latency access at the cost of higher data replication and thus, lower capacity per cluster. Conversely, large clusters result in higher access latency, but less replication degree. Instead of standard address interleaving, instruction clustering technique for R-NUCA indexes blocks into a size-4 fixed-center cluster employing a rotational interleaving, where each is core is assigned with a rotational ID (RID).

- Maps private data into the local LLC slice of the requesting core. Logically, it can be seen as a size-1 cluster (i.e., loosely or tightly connected computers) mapping.

- Shared read-write data is placed at fixed address-interleaved locations in a size-N cluster (where N is the size of the system).

#### PS-TLB

Y. Li et al. [47] avoid pipeline stalls when obtaining the virtual to physical address translation by introducing a small buffer structure close to the TLB, namely partial sharing buffer (PSB). Private translations are stored locally for low-latency access. Then, when a page becomes shared the translation is distributed as in NUCA memories among all cores' PSBs. Therefore, a shared translation is obtained with lower latency and lesser storage resources than a second-level TLB scheme.

The PS-TLB architecture works as follows. After a request for a virtual address request, the L1 and L2 TLBs are sequentially checked in order to retrieve the physical address, which is obtained after hitting on either TLB level. Conversely, if a miss occurs in the L2 TLB, it may be present either in the PSB home tile or the page table (or both), and thus both are searched in parallel. If the PSB home hits on a valid entry, it replies to the requester with the corresponding translation. In that case, the translation from the page table is simply discarded when received on the requesting core. If the request misses on the PSB home, the translation is resolved on the page table and the translation is stored in the local private TLB hierarchy if

the page is private, or in both the TLB structure and the PSB home if the PSB is shared. This way, cores without the specific translation are not stalled upon TLB shootdowns, avoiding some of the shootdown process overhead. Furthermore, PSBs are not flushed on shootdowns, and their entries may be employed when reaccessing a page after a context switch or a migrating thread.

#### 2.2.3 Coherence Protocol Optimizations

Core count rapid growth in current CMPs, alongside the implementation of a shared-memory programming model, leads to the requirement of efficient coherence maintenance among data in private caches. These circumstances bring new challenges to make coherence protocols scalable and provide increasing performance. This section reviews some proposals based on the characterization of the accessed data.

#### Coherence Deactivation

Directory-based coherence is one of the best suited protocols in terms of scalability and is present on most commodity processors nowadays. The directory is in charge of tracking data sharers in order to invalidate outdated copies on writes, and obtain the most recent copy on reads. This way, sequential consistency is granted for directory-based protocols. However, on larger CMPs, the directory cache may suffer from scalability problems. Directory area and latency overheads increase in order to avoid evictions, as the eviction of a directory entry usually entails the invalidation of blocks on the lower memory hierarchy levels. Due to the limited size or associativity of directory caches or the lack of a backup directory, a system may produce frequent invalidations of directory entries, which dramatically increases the number of *Coverage* misses [67] (i.e., cache misses caused by invalidations on the directory cache due to its limited capacity) and, therefore, results in performance degradation.

However, the coherence problem arises only for shared resources (present in multiple local caches). Thus, if a block is known to be present only in a single private cache (i.e., private), coherence maintenance may be bypassed. In this regard, *Coherence Deactivation* identifies private [22] and read-only [23] (non-coherent) blocks, and avoids storing those blocks in the directory cache. Therefore, directories exploit their limited storage capacity more efficiently as long as classification mechanism becomes more accurate, while the availability of the directory is improved for blocks that really need coherence (i.e., shared blocks).

Since coherence deactivation overrides the coherence protocol for non-coherent accesses, a recovery operation is required when a page becomes coherent again, in order to avoid inconsistencies. Recovery is a costly system-wide operation in charge of atomically updating TLBs' sharing status and return to a coherent state. To this end, the blocks of a non-coherent page that becomes coherent must be either evicted from the cache (flushing-based recovery) or updated in the directory cache (update-based recovery). Once the recovery mechanism has finished, the directory cache is in a coherent state according to the new page classification.

#### VIPS

Ros and Kaxiras [71] propose an efficient and simple directory-less and broadcast-less cache coherence protocol which requires only three stable states, namely VIPS (i.e., Valid/Invalid Private/Shared). Although sequential consistency is not supported with VIPS for all applications, its definition is still satisfied for Data-Race-Free (DRF) applications.

VIPS implements a dynamic write policy: a simple write-through policy (i.e., store operations traverse the underlying storage before confirming completion to host) for shared blocks and an efficient write-back policy (i.e., store operations are directed to cache and completion is immediately confirmed) for private blocks, which represents the great majority of write misses on commercial workloads. Then, on a second step, VIPS-M waits for a synchronization point with acquire semantics (e.g., lock, barrier, wait) on DRF applications to be exposed to the hardware in order to selectively flush (i.e., self-invalidate) shared data (employing a private-shared classification scheme). This way, the requirement for tracking block readers is avoided. When a node writes into a shared data, the sharers will self-invalidate on the next synchronization point. Then, with the addition of self-downgrade (i.e., write-back) upon a release synchronization (e.g., unlock, barrier, signal), the need for a directory cache or snooping broadcast messages is completely averted.

This coherence scheme simplifies the coherence protocol, resulting in less static and dynamic energy consumption compared to conventional MESI directory protocols. Nonetheless, any synchronization that relies on races (e.g., spin-waiting races, which are employed for signaling, locking, and barrier primitives) comprises the effectiveness of the protocol due to the lack of explicit invalidations, as it repeatedly self-invalidate and re-fetch in order to obtain the spin flag value updated by writes. To solve this, a new, simple, and transparent *callback* mechanism has been proposed [72], which are set by reads involved in a spin waiting and satisfied by writes. A callback signal blocks any read to a variable that is waiting for a write, while it has not occurred since its last invocation. This way, the benefits of explicit invalidation are obtained, while the cost of an invalidation protocol is avoided (e.g., employing a directory to track all data).

#### Timestamps-based coherence

Dealing with the scalability issues of directory protocols, timestamp-based hardware coherence protocols present an appealing alternative.

TC-Strong. This is a time-based coherence protocol for GPUs, namely Temporal Coherence (TC) [80], based on globally synchronized counters. With TC-Strong, these synchronized counters are maintained in the GPU cores and L2 controllers, allowing to self-invalidate cache blocks and maintain coherence, thus eliminating coherence traffic, and reducing are overhead and protocol complexity. Small timestamps fields are added to the L1 and L2 cache entry format. The L1 timestamps indicates when a specific L1 entry is invalidated, while L2 timestamp indicates when all L1 cachelines have been self-invalidated (L2 entries are never evicted while their timestamp has not expired). TC-Strong implements an optimization to eliminate write-stalling for private data. An L2 line reads are permitted only while data are private. Writes to private L2 lines are only effective if they are from the core that originally performed the read. Then, store requests from the L1 include their local timestamps, which are matched against the global timestamp in the L2 to check when a core is performing a private write.

**TC-Release++.** TC-Release [87] is a port from TC to maintain coherence in general purpose CMPs. Private cache lines with TC-Release in write-back caches do not need to maintain

timestamps and self-invalidate upon expiration, leading to higher L1 cache hit rate. This observation is further extended to shared read-only lines, as they do not require coherence maintenance. Therefore, all private or read-only L1 cache lines are kept in the cache as long as possible.

#### 2.2.4 Memory Consistency Models

The memory consistency model of a shared-memory multiprocessor provides a formal specification of how the memory system will appear to the programmer, eliminating the gap between the behavior expected by the programmer and the actual behavior supported by the system.

#### End-To-End sequential consistency

Sequential consistency (SC) is arguably the most intuitive behavior for a shared-memory multithreaded program. A multiprocessor is sequentially consistent if the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and behaves as an interleaving of the memory accesses from its threads. Furthermore, languagelevel SC improves programmability on a CMP. Modern programming languages as C++ or Java provide SC only for DRF programs, while for racy programs only weak consistency models are provided.

End-to-End SC [79] allows instruction reordering and out-of-order commits from the reorder buffers (ROB) of private accesses from the store buffers, since they do not affect the consistency model enforced by the system. It also allows a load to a shared-read-only location to commit from the ROB without waiting for the store buffer to drain.

Racer: TSO Consistency

TSO (Total Store Ordering) is the memory model currently employed in one of the most common family of processors (TSO-x86). With TSO there is always a single, global order of writes to shared memory from all cores.

Racer [73] is a coherence approach based on self-invalidate and self-downgrade that provides TSO consistency. This is guaranteed by detecting read-after-write races (RAWR) at run time and treating them as synchronization. Since private data do not affect consistency, Racer causes self-invalidations of only shared data in the local cache of a racing reader. On the other hand, while private stores are free to coalesce in the local cache, Racer employs a store buffer to coalesce shared stores, while keeping the order seen by other cores. Therefore, when a racy read occurs, all stores previous (in program order) to the conflicting one are seen by the reader. Finally, private accesses are not tracked for race detection, thus incurring small hardware requirements and avoiding false positives at the RAWR bloom filters. Overall, Racer provides TSO consistency outperforming even state-of-the-art SC-for-DRF models.

## 2.3 Data Classification Mechanisms

All the approaches seen in the previous section require a classification mechanism to perform their data management optimization. This section first discusses some desirable features of classification schemes which are key for their effectiveness. Then, we describe the main state-of-the-art classification mechanisms and how they cope with those features.

## 2.3.1 Desirable Features of Classification

Firstly, the classification should be performed with low-overhead in terms of traffic, performance, and area. Although this is key for every classification approach, there are some other main properties for classification approaches which are decisive in order to make classification attractive:

- Knowing the classification before the memory access reaches the cache structure is critical to the applicability of the classification mechanism. This *a-priori* knowledge of data sharing status is a requirement for many data optimizations (e.g., *Coherence Deactivation* [22] or *Reactive NUCA* [31]).

- A block is commonly accessed concurrently from two or more cores (i.e., shared) only during a particular period, becoming private again after some time, since the cache lines are evicted after inactivity periods. A classification approach should be able to detect data transitioning back to private, or else most data would end up as shared on applications running for a long time, miss-classified due to temporal data patterns. This property, namely classification adaptivity, permits invoking the same schedulable entity (e.g., application's thread) from different system components (i.e., thread migration) without incurring in miss-classified shared accesses.

- Besides private and shared characterization, detecting non-written regions of data (i.e., read-only classification) provides more insight to classification, which ultimately allows better performance for classification applications that support read-only data optimizations. Therefore, when a store memory operation occurs, the sharing status evolves into a written state. The classification private-shared dichotomy is extended to four states: Private Read-only (PR), Private read-Write (PW), Shared Read-only (SR), and Shared read-Write (SW).

- Runtime classification information is decisive, as privacy cannot be always guaranteed at compile time. Commonly, complex compiler analyses (e.g., data reuse analysis or data disambiguation, among others) are usually employed to guarantee the privacy of the accessed data. Conversely, runtime classification performs an *accurate*, efficient data classification.

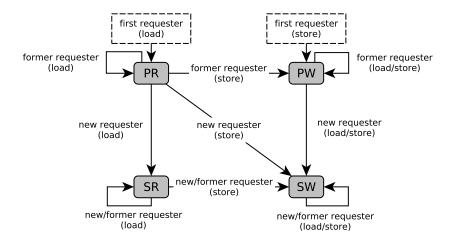

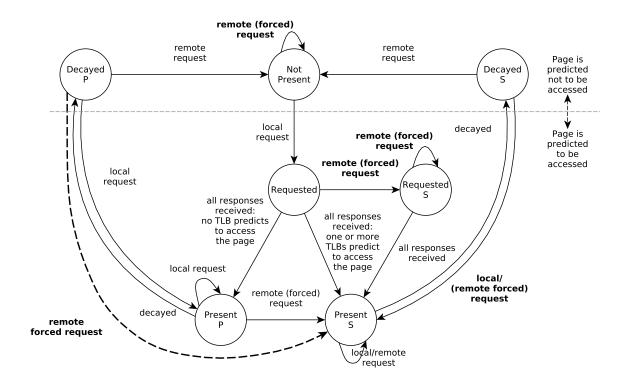

Figure 2.1: State transition diagram for OS-based classification status.

#### 2.3.2 OS-based Classification

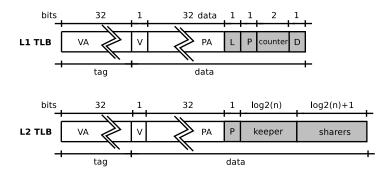

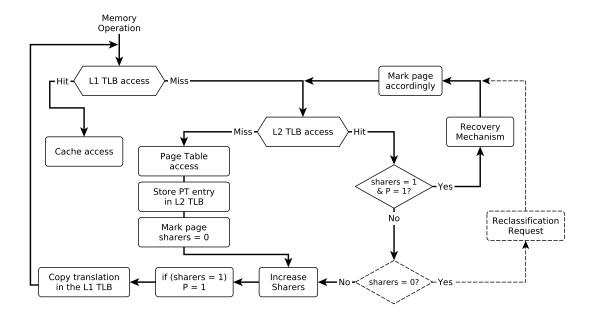

Some mechanisms classify at page-level aided by the operating system (OS) [22, 23, 31, 43, 47]. OS-based mechanisms do not require additional hardware support because they take advantage of existing OS structures (i.e., page table and TLBs). An OS-based classification considers a page as private on a page table fault. Then, the first time the virtual-to-physical address translation is requested after a TLB miss, the requesting core is annotated in the page table (keeper [22] or FAC -first accessing core- [47] field). On subsequent accesses to the page table entry, the keeper field is compared with the current requester. If the keeper field matches, it means that the keeper's TLB suffered an eviction and the page may continue as private. Conversely, if the keeper field does not match on a private page table entry, then the page is reclassified as shared. To this end, each page table entry adds a P bit that indicates the page state (private or shared). The P bit is also included in the TLB entries to allow a fast access to the page state for those cores that have the page entry in the TLB. When a page changes from private to shared, the core having the page as private must be notified in order to update the sharing status of its TLB accordingly. Moreover, OS-based classification has been also extended to support shared read-only data [23].

Figure 2.1 shows the state transition of the sharing status for a page in an OS-based classification approach. The left side of the diagram corresponds to the basic private and shared states, and the right side introduce the written states when read-only data is accounted for. Note how when a page falls either as shared or written, it remains as so for the rest of the execution time (until the page is evicted from memory), since OS-based classification is mostly non-adaptive.

#### 2.3.3 Directory-based Classification

Directory-based mechanisms [62, 33, 11, 88, 24] store the sharing status in either the directory or the last level cache structure (LLC-based mechanism), by adding some additional states in the corresponding memory. Figure 2.2 represents the state digram for SWEL [62], a cache coherence protocol that discerns five combinations of the states Shared, Writen, and Exclusivity Level. SWEL employs a LLC-based classification mechanism to discern the sharing status. Private data is stored in the L1 cache, while shared data reside at the shared L2 cache. Sharing status is determined at block level after the cache structure is accessed. The first time that a block transitions to Shared, the L1 cache copies of the block are invalidated through a broadcast message. Once the blocks classification transitions to either Shared or Written it remains as so

Figure 2.2: State transition diagram for the SWEL protocol.

until its eviction (i.e., until the block generation time ends). Then, the classification becomes private again if reaccessed.

These proposals allow performing a runtime, software-transparent classification at page or cache-line granularity. Cache-line granularity avoids spatial aliasing problems, on what data may be considered shared on broader granularity schemes, whereas blocks are never concurrently accessed. However, directory-based approaches might add prohibitive storage requirements or deal with dual-granularity complexities.

Directory-based classification mechanisms commonly require explicit notification to the directory upon L1 cache misses and replacements in order to accurately determine the generation of every cache line and classify accordingly [24]. In this scheme, shared directory lines in the directory may be evicted without invalidating cache lines (i.e., self-contained directory). This allows smaller, yet efficient directories. However, this approach requires DRF semantics and self-invalidate cache lines on the next synchronization point. Moreover, an additional logarithmic sharer count field is required per directory entry in order to revert classification from shared to private. Even though the storage requirement increase may be excessive for directory-based approaches to support classification adaptivity, it is required in order to provide sequential consistency (SC).

Finally, LLC-based classification can employ a Cache Decay [40] or any similar technique in order to shorten cache line generation time according to its access pattern, which ultimately favors a more accurate private data detection.

## 2.3.4 Compiler-assisted Classification

Compiler-assisted approaches [46, 48] exploit representative patterns existing in a huge variety of data-parallel applications to perform a classification into private or shared. In these benchmarks, each thread derives its own set of local variables with thread-dependent values to specify which regions of each array to access. These local variables are called Thread Identifying (TI) variables [46]. The compiler needs to identify these TI variables to determine how each thread accesses different portions of memory. One of the commonly used methods for specifying TI variables is to pass different values to parallel threads as function arguments. Another common way to specify TI variables in multi-threaded applications is through *mutex* lock directives to protect global variables. This type of code is much more difficult for a compiler to analyze.

Table 2.1: Properties of classification schemes

|                   | A-priori | Read-Only | Adaptive | Accurate |

|-------------------|----------|-----------|----------|----------|

| Directory-based   | X        | ✓         | ✓        | ✓        |

| OS-based          | ✓        | ✓         | X        | ✓        |

| Compiler-assisted | ✓        | ✓         | ✓        | ×        |

| TLB-based         | ✓        | ✓         | ✓        | ✓        |

Moreover, there are particular programming structures, such as loops and conditionals, that determine the memory access pattern of the threads (i.e., Thread Identifying Structures).

However, compiler-assisted data classification must remain conservative, as they deal with the difficulty of knowing at compile time (i) whether a variable is going to be accessed or not, and (ii) in which cores the data will be scheduled and rescheduled [35]. Furthermore, compiler assisted-approaches are not transparent to software, as they require recoding and/or recompilation for legacy software.

#### 2.3.5 Classification Based on Programming Languages

Finally, some approaches based on the properties of programming languages [69, 70] can precisely identify extended data-race-free (xDRF) regions (i.e., a set of DRF regions acting as one unique region) at compile-time. DRF regions may be interleaved with non-DRF (nDRF) regions, but they do no break data-race-free semantics. OpenMP programming model is employed to discern sharing status, since it is controlled by dedicated synchronization constructs (e.g., atomic, critical), which are easily identified statically.

Then, finer granularity compile-time classification is complemented by an OS-based classification to increase the accuracy with runtime page-level information, alleviating the conservative actions of a static classification. The benefit of the combined classification approaches works both ways, since the static approach resets the classification to private at the boundaries of xDRF regions, allowing the OS-based classification to become adaptive These static-dynamic classification approaches, despite being very accurate, are not applicable to most existing codes, since the compiler must unequivocally identify xDRF regions.

## 2.3.6 Summary

Table 2.1 summarizes the main properties of the previously introduced state-of-the-art classification approaches. In the first place, Directory-based classification needs to access the LLC or the directory cache (i.e., traversing the L1 cache) in order to obtain the sharing status of the block. This mechanisms are not applicable to some private-based optimizations, since they need the classification to be known before missing in the L1 cache.

OS-based mechanism is based on accesses to the page table in order to hint for concurrent accesses from multiple cores, which transitions the page classification status to shared. However, when a page ceased to be used in a core, the page table is not updated. Consequently, OS-based classification is not temporality-aware, which implies that: i) shared-to-private transitions are not detected, a page must be evicted from main memory in order to be reclassified to private, and ii) a page is possibly miss-classified as shared since it might not be currently accessed from two or more cores (e.g., due to a migrating thread). Since data access patterns change throughout different phases of the application lifetime [39, 78], adaptivity is fundamental to achieve a good classification accuracy.

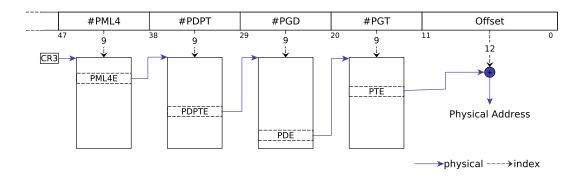

Figure 2.3: Example of a translation process (page table walk) in the x86 64.

Read-only classification (i.e., detecting non-written regions of data) is also a far-reaching property, as merely accounting for shared-read-only blocks they can reach in some cases up to 48.7% of all accessed blocks [23]. Most data classification mechanisms can detect read-only data at the cost of raising the hardware complexity, increasing the network consumption or adding storage requirements.

Finally, compiler-assisted approaches need to be conservative, because private condition for memory accesses in these approaches cannot be proved in most cases, which compromises the *accuracy* of the mechanism. Mechanisms based on the programming languages (i.e., static-dynamic approaches) rely on OpenMP directives to discern block-level, adaptive sharing information at compile time, and an OS-based classification mechanism to obtain runtime, page-level, sharing information. Nonetheless, these mechanisms are only suited for applications that identify xDRF regions, which limits its applicability.

This thesis introduces a new family of TLB-based protocols that aim to reach all desirable properties for a classification mechanism.

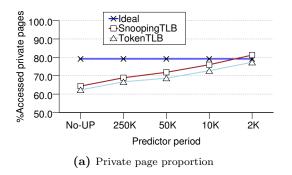

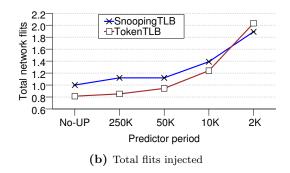

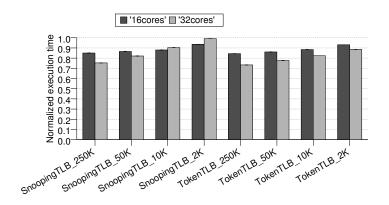

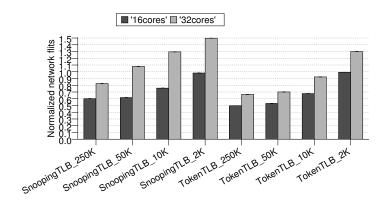

# 2.4 Architecting and Managing TLBs