#### Doctorat en Enginyeria Electrònica

PADRE pixel read-out architecture for Monolithic Active Pixel Sensor for the new ALICE Inner Tracking System in TowerJazz 180 nm technology

César Augusto Marín Tobón

supervised by

**Dr. Raúl Esteve Bosch** Universitat Politècnica de València Departament d'enginyeria electrònica

> **Dr. Walter Snoeys** CERN EP-ESE-ME

> > July 19, 2017

A dissertation submitted to the University Polytechnic of València for the degree of Doctor of Philosophy.

iii

#### Declaration

This dissertation is made of my own work, except where explicit reference is make to the work of others. It has not been submitted for another qualification to this or any other university.

Signature

v

# Acronyms

| ACORDE               | ALICE COsmic Ray DEtector.                                         |

|----------------------|--------------------------------------------------------------------|

| ADC                  | Analog to Digital Conversion.                                      |

| ALICE                | A Large Ion Collider Experiment.                                   |

| ALPIDE               | A Large fon Conder Experiment.<br>ALice PIxel DEtector.            |

| ASICs                | Application Specific Integrated Circuits.                          |

| ATLAS                | A Toroidal LHC AparatuS.                                           |

| CERN                 | European Organization for Nuclear Research.                        |

| CIS                  | CMOS Imaging Sensor process.                                       |

| CDS                  | Correlated double sampling.                                        |

| CMOS                 |                                                                    |

| CMOS                 | Complementary metal-oxide-semiconductor.<br>Compact Muon Solenoid. |

| DAC                  | *                                                                  |

| -                    | Digital-to-Analogue Converter.                                     |

| DAQ                  | Data Acquisition.                                                  |

| DPRAM                | Dual Port RAM.                                                     |

| ECAL                 | Crystal Electromagnetic Calorimeter.                               |

| ECC                  | Error Correction Coding.                                           |

| ELT                  | Enclosed Layout Transistors.                                       |

| EMCAL                | ElectroMagnetic CALorimeter.                                       |

| FE                   | FrontEnd.                                                          |

| FET                  | Field Effect Transistor.                                           |

| FF's                 | Flip Flops.                                                        |

| $\operatorname{FMD}$ | Forward Multiplicity Detector.                                     |

| FPC                  | Flexible Printed Circuit.                                          |

| FPGA                 | Field Programmable Gate Array.                                     |

| FSM                  | Finite State Machine.                                              |

| GDSII                | Graphic Database System II.                                        |

| HCAL                 | Brass/Scintillator Hadron Calorimeter.                             |

| HDL                  | Hardware Description LAnguage.                                     |

| HEP                  | High Energy Physics.                                               |

| $\operatorname{HFT}$ | Heavy Flavor Tracker.                                              |

| HMPID                | High Momentum Particle Identification.                             |

| HPD                  | Hybrid pixels detectors.                                           |

| IB                   | Inner Barrel.                                                      |

| IP                   | Interaction Point.                                                 |

| IPHC                 | Institut Pluridisciplinaire Hubert CURIEN                          |

| ITS                  | Inner Tracking System.                                             |

| LHC                  | Large Hadron Collider.                                             |

| LS2                  | Long Shutdown 2.                                                   |

|                      |                                                                    |

vii

| MADO    |                                                    |

|---------|----------------------------------------------------|

| MAPS    | Monolithic Active Pixel Sensors.                   |

| MOSFET  | Metal-Oxide-Semiconductor Field Effect Transistor. |

| MPW     | Multi-Project Wafer.                               |

| NIEL    | Non-Ionising Energy Loss.                          |

| NMOS    | n-channel MOSFET.                                  |

| OB      | Outer Barrel.                                      |

| р       | Proton.                                            |

| Pb      | Lead.                                              |

| PCB     | Printed Circuit Board.                             |

| PHOS    | PHOton Spectrometer.                               |

| PMD     | Photon Multiplicity Detector.                      |

| PMOS    | p-channel MOSFET.                                  |

| QGP     | Quark-Gluon Plasma.                                |

| RAM     | Random-Access Memory.                              |

| RHIC    | Relativistic Heavy Ion Collider.                   |

| RMS     | Root Mean Square.                                  |

| RTL     | Resistor Transistor Logic.                         |

| SCT     | SemiConductor Tracker.                             |

| SDD     | Silicon Drift Detector.                            |

| SEE     | Single Event Effects.                              |

| SET     | Single Event Transient.                            |

| SEU     | Single Event Upset.                                |

| $SiO_2$ | Silicon Dioxide.                                   |

| SPD     | Silicon Pixel Detector.                            |

| SPS     | Super Proton Synchrotron.                          |

| SRAM    | Static RAM.                                        |

| SSD     | Silicon Strip Detector.                            |

| STI     | Shallow Trench Isolation.                          |

| TID     | Total Ionising Dose.                               |

| TMR     | Triple Modular Redundancy.                         |

| TOF     | Time Of Flight.                                    |

| TPC     | Time Projection Chamber.                           |

| TRD     | Transition Radiation Detector.                     |

| TRT     | Transition Radiation Tracker.                      |

| ZDC     | Zero Degree Calorimeter.                           |

|         | Leto Degree Calorimeter.                           |

#### Resum

El subdetector ITS (Inner Tracking System) del detector ALICE (A Large Ion Collider Experiment) és un detector de vèrtex i és el detector mes proper al punt d'interacció. Es troba conformat per 3 tipus de subdetectors, dues capes de píxel de silici (Silicon Pixel Detectors), 2 capes d'acumulació de silici (Silicon Drift Detectors) i 2 capes de banda de Silici (Silicon Strip Detectors). La funció primària del ITS és identificar i rastrejar les partícules de baix moment transversal.

El detector ITS en les seues dues capes més internes estan equipades amb sensors de silici basats en píxels híbrids. Per a reemplaçar aquesta tecnologia de Píxels, el detector ITS actual serà reemplaçat per un nou detector d'una sola tecnologia, ampliant la seua resolució espacial i millorant el rastreig de traces. Aquest nou detector constarà de set capes de sensors de píxels actius monolítics (MAPS), les quals hauran de satisfer els requeriments de pressupost de materials i ser tolerants a majors nivells de radiació per als nous escenaris d'increments de lluminositat i majors taxes de col·lisions. Els sensors MAPS que integren el sensor d'imatge i els circuits de lectura es troben en la mateixa hòstia de silici, tenen grans avantatges en una bona resolució de posició i un baix pressupost material en termes de baix cost de producció.

TowerJazz ofereix la possibilitat d'una quàdruple-WELL aïllant els transistors pMOS que es troben en la mateixa nWELL evitant la competència amb l'elèctrode de recol·lecció, permetent circuits mes complexos i compactes per a ser implementats dins de la zona activa i a més posseeix una capa epitaxial d'alta resistivitat. Aquesta tecnologia proporciona una porta d'òxid molt prim limitant el dany superficial per la radiació fent-ho adequat per al seu ús dins de l'experiment ALICE. En els últims quatre anys s'ha dut a terme una intensiva R+D en MAPS en el marc de l'actualització del ITS d'A-LICE. Diversos prototips a petita escala s'han desenvolupat i provat reeixidament amb rajos X, fonts radioactives i feixos de partícules. La tolerància a la radiació d'ALICE ITS és moderada amb una tolerància d'irradiació TID de 700 krad i NIEL d' $1 \times 10^{13}$  1MeV n<sub>eq</sub> cm<sup>-2</sup>, MAPS és una opció viable per a l'actualització del ITS.

La contribució original d'aquesta tesi és la implementació d'una nova arquitectura digital de lectura de píxels per a MAPS. Aquesta tesi presenta un codificador asíncron d'adreces (arquitectura basada en la supressió de zeros transmetent l'adreça dels píxels excitats denominada PADRE) per a l'arquitectura ALPIDE, l'autor també va fer una contribució significativa en l'assemblatge i verificació de circuits. PA-DRE és la principal recerca de l'autor, basada en un codificador de prioritat jeràrquica de quatre entrades i és una alternativa a l'arquitectura de lectura rolling-shutter.

A més dels prototips a petita escala, també s'han desenvolupat prototips a escala completa a les necessitats del detector ITS (15 mm i 30 mm) emprant un nou circuit de lectura basat en la versió personalitzada del circuit PADRE. El pALPIDEfs va ser el primer prototip a escala completa i es va caracteritzar obtenint un temps de lectura de la matriu per sota de 4  $\mu$ s i un consum d'energia en l'ordre de 80 mWcm<sup>-2</sup>. En general, els resultats obtinguts representen un avanç significatiu de la tecnologia MAPS quant al consum d'energia, velocitat de lectura, temps de recol·lecció de càrrega i tolerància a la radiació. El sensor pALPIDE2 ha demostrat ser una opció molt atractiva per al nou detector ITS, satisfent els requeriments en termes d'eficiència de detecció, fake-hit rate i resolució de posició, ja que el seu rendiment no pot aconseguir-se mitjançant prototips basats en l'arquitectura de lectura tradicionals com és el rolling-shutter dissenyat en la mateixa tecnologia. Per aquesta raó, la R+D en els prototips ALPIDE ha continuat amb l'objectiu d'optimitzar encara més el rendiment del sensor especialment en termes del temps mort i estudiar solucions en altres aspectes de sistemes d'integració.

L'últim circuit de ALPIDE, el pALPDIE3B, consumeix menys de 50 mW cm-2 amb una màxima taxa de transmissió d'1,2 Gbps i té una eficiència a la reconstrucció de traces superior al 99,95%. Amb un marge operatiu satisfactori després d'irradiació amb una fluència equivalent d'× 10<sup>13</sup> 1 MeV n<sub>eq</sub>cm<sup>-2</sup>. A més, validant un consum d'energia per

sota de 50 mW cm<sup>-2</sup>. I una resolució de posició d'uns 5  $\mu$ m i una velocitat de lectura aproximada de 2 mus, complint amb les especificacions ALICE ITS per a la seua actualització. Els resultats obtinguts de la caracterització del pALPIDE3B, la fase optimització dels circuits i de prototips es finalitza i dóna motiu a l'inici de la producció en massa del xip ALPIDE per a l'any 2017. El nou detector ITS s'instal·larà durant el segon gran aturada del LHC l'any 2020 en la caverna d'ALICE.

xi

#### Resúmen

El sub detector ITS (Inner Tracking System) del detector ALICE (A Large Ion Collider Experiment) es un detector de vértice y es el detector mas cercano al punto de interacción. Se encuentra conformado por 3 tipos de subdetectores, dos capas de pixel de silicio (Silicon Pixel Detectors), 2 capas de acumulación de silicio (Silicon Drift Detectors) y 2 capas de banda de Silicio (Silicon Strip Detectors). La función primaria del ITS es identificar y rastrear las partículas de bajo momentum transversal.

El detector ITS en sus dos capas más internas están equipadas con sensores de silicio basados en píxeles híbridos. Para reemplazar esta tecnología de Píxeles, el detector ITS actual será reemplazado por un nuevo detector de una sola tecnología, ampliando su resolución espacial y mejorando el rastreo de trazas. Este nuevo detector constará de siete capas de sensores de píxeles activos monolíticos (MAPS), las cuales deberán satisfacer los requerimientos de presupuesto de materiales y ser tolerantes a mayores niveles de radiación para los nuevos escenarios de incrementos de luminosidad y mayores tasas de colisiones.

Los sensores MAPS que integran el sensor de imagen y los circuitos de lectura se encuentran en la misma oblea de silicio, tienen grandes ventajas en una buena resolución de posición y un bajo presupuesto material en términos de bajo coste de producción.

TowerJazz ofrece la posibilidad de una cuádruple-WELL aislando los transistores pMOS que se encuentran en la misma nWELL evitando la competencia con el electrodo de recolección, permitiendo circuitos mas complejos y compactos para ser implementados dentro de la zona activa y además posee una capa epitaxial de alta resistividad. Esta tecnología proporciona una puerta de óxido muy delgado limitando el daño superficial por la radiación haciéndolo adecuado para su uso dentro del experimento ALICE. En los últimos cuatro años se ha llevado a cabo una intensiva I+D en MAPS en el marco de la actualización del ITS de ALICE. Varios prototipos a pequeña escala se han desarrollado y probado exitosamente con rayos X, fuentes radioactivas y haces de partículas. La tolerancia a la radiación de ALICE ITS es moderada con una tolerancia de irradiación TID de 700 krad y NIEL de  $1 \times 10^{13}$  1 MeV n<sub>eq</sub>cm<sup>-2</sup>, MAPS es una opción viable para la actualización del ITS.

La contribución original de esta tesis es la implementación de una nueva arquitectura digital de lectura de píxeles para MAPS. Esta tesis presenta un codificador asíncrono de direcciones (arquitectura basada en la supresión de ceros transmitiendo la dirección de los píxeles excitados denominada PADRE) para la arquitectura ALPIDE, el autor también hizo una contribución significativa en el ensamblaje y verificación de circuitos. PADRE es la principal investigación del autor, basada en un codificador de prioridad jerárquica de cuatro entradas y es una alternativa a la arquitectura de lectura rolling-shutter.

Además de los prototipos a pequeña escala, también se han desarrollado prototipos a escala completa a las necesidades del detector ITS (15 mm y 30 mm) empleando un nuevo circuito de lectura basado en la versión personalizada del circuito PADRE. El pALPIDEfs fue el primer prototipo a escala completa y se caracterizó obteniendo un tiempo de lectura de la matriz por debajo de 4  $\mu$ s y un consumo de energía en el orden de 80 mWcm<sup>-2</sup>. En general, los resultados obtenidos representan un avance significativo de la tecnología MAPS en cuanto al consumo de energía, velocidad de lectura, tiempo de recolección de carga y tolerancia a la radiación.

El sensor pALPIDE2 ha demostrado ser una opción muy atractiva para el nuevo detector ITS, satisfaciendo los requerimientos en términos de eficiencia de detección, fake-hit rate y resolución de posición, ya que su rendimiento no puede alcanzarse mediante prototipos basados en la arquitectura de lectura tradicionales como es el rolling-shutter diseñado en la misma tecnología. Por esta razón, la I+D en los prototipos ALPIDE ha continuado con el objetivo de optimizar aún más el rendimiento del sensor especialmente en términos del tiempo muerto y estudiar soluciones en otros aspectos de sistemas de integración. El último circuito de ALPIDE, el pALPDIE3B, consume menos de 50 mW cm<sup>-2</sup> con una máxima tasa de transmisión de 1,2 Gbps y tiene una eficiencia a la reconstrucción de trazas superior al 99,95 %. Con un margen operativo satisfactorio después de irradiación con una fluencia equivalente de 1 × 10<sup>13</sup> 1 MeV n<sub>eq</sub>cm<sup>-2</sup>. Además, validando un consumo de energía por debajo de 50 mW cm<sup>-2</sup> y una resolución de posición de unos 5  $\mu$ m y una velocidad de lectura aproximada de 2  $\mu$ s, cumpliendo con las especificaciones ALICE ITS para su actualización.

Los resultados obtenidos de la caracterización del pALPIDE3B, la fase optimización de los circuitos y de prototipos se finaliza y da pie al inicio de la producción en masa del chip ALPIDE para el año 2017. El nuevo detector ITS se instalará durante el segundo gran parón del LHC en el año 2020 en la caverna de ALICE.

xv

#### Abstract

ALICE (A Large Ion Collider Experiment) is the heavy-ion experiment at the Large Hadron Collider (LHC) at CERN. As an important part of its upgrade plans, the ALICE experiment will schedule the installation of a new Inner Tracking System (ITS) during the Long Shutdown 2 (LS2) of the LHC. The new ITS layout will consist of seven concentric layers,  $\approx 12.5$  Gigapixel camera covering about  $10m^2$ with Monolithic Active Pixel Sensors (MAPS). This choice of technology has been guided by the tight requirements on the material budget of 0.3% X/X<sub>0</sub> per layer for the three innermost layers and backed by the significant progress in the field of MAPS in recent years. The technology initially chosen for the ITS upgrade is the TowerJazz 180 nm CMOS Technology. It offers a standard epitaxial layer of 15 - 18  $\mu$ m with a resistivity between 1 and 5 k $\Omega$  cm<sup>-1</sup> and a gate oxide thickness below 4 nm, thus being more robust to Total Ionizing Dose (TID).

The main subject of this thesis is to implement a novel digital pixel readout architecture for MAPS. This thesis aims to study this novel readout architecture as an alternative to the rolling-shutter readout. However, this must be investigated through the study of several chip readout architectures during the R&D phase. Another objective of this thesis is the study and characterization of TowerJazz, if it meets the Non-Ionizing Energy Loss (NIEL) and Single Event Effects (SEE) of the ALICE ITS upgrade program.

Other goals of this thesis are:

• Implementation of the top-down flow for this CMOS process and the design of multiple readouts for different prototypes up to the assembly of a full-scale prototype.

xvii

- Characterization of the radiation hardness and SEE of the chips submitted to fabrication.

- Characterization of full custom designs using analog simulations and the generation of digital models for the simulation chain needed for the verification process.

- Implementation and study of different digital readouts to meet the ITS upgrade program in integration time, pixel size and power consumption, from the conceptual idea, production and fabrication phase.

Chapter 1 is a brief overview of CERN, the LHC and the detectors complex. The ALICE ITS will be explained, focusing on the ITS upgrade in terms of detector needs and design constraints. Chapter 2 explains the properties of silicon detectors and the detector material and the principles of operation for MAPS. Chapters 3 and 4 describe the ALPIDE prototypes and their readout based on MAPS; this forms the central part of this work, including the multiple families of pixel detectors fabricated in order to reach the final design for the ITS. The ALPIDE3/pALPIDE3B chip, the latest MAPS chip designed, will be explained in detail, as well focusing in the matrix digital readout. In chapter 5 the noise measurements and its characterization are presented including a brief summary of detector response to irradiation with soft X-rays, sources and particle beams.

#### Acknowledgements

First and foremost, I would like to thank Dr. Carlos Solans and Dr. Alberto Valero Biot who have supported me during these years and always given me advice when needed and gratefully acknowledged for reviewing this thesis, also to Dr. Bruce Mellado for his support and pressure for finishing this research. To my supervisors Walter Snoeys for giving me this opportunity to pursue my PhD. I am grateful to Raúl Esteve Bosch for supervising me at the Polytechnic University of Valéncia during my thesis work. Special thanks also go to Dr. Luciano Musa for trusting my skills and giving me the chance to work in Switzerland at CERN, and Finally, my warmest thanks go to Dr. Richard Teuscher for reviewing this thesis, and for taking the time to be my opponent in the defense of this thesis.

I would like to thank my colleagues in the CERN EP-ESE-ME group for many discussions on microelectronics and tools. Thanks to Wojciech, Xavi, Sandro, Szymon, Pedro, Isaac and Rui.

The work described in this thesis is the result of a big collaboration with many people involved in the ALICE ITS upgrade project. Also special thanks to all the people in the WP5 team: Magnus, Felix, Markus, Jacobus, Hartmut, Petra, Monica and Krzysztof, Hyeonjoong and the rest. I want to thank Thanu, for sharing the office, and always having an open ear for all the ideas that came into my mind throughout the last five years. Also, including the WP3 team: Constanza, Gianluca, Alessandra, Daehyoek, Seingjoo, Ping, Chaosong, Jerome and Herve.

Major thanks go to my family. I know they did not appreciate my absence, but I received a lot of support from you nevertheless. To Karlita my niece, who show me that the life is different and, who has brought so much joy into my life, thank you.

xix

## Contents

| Acronyms                                                                                                      | vii            |

|---------------------------------------------------------------------------------------------------------------|----------------|

| Resum                                                                                                         | ix             |

| Resúmen                                                                                                       | xiii           |

| Abstract                                                                                                      | xvii           |

| List of Figures                                                                                               | XXV            |

| List of Tables                                                                                                |                |

| 1 CERN, the LHC and the ALICE ITS upgrade program                                                             | 1              |

| 1.1 The LHC       1.1.1 The ATLAS Experiment         1.1.2 The CMS Experiment       1.1.3 The LHCb experiment | 8              |

| 1.2 ALICE                                                                                                     | 11<br>13<br>15 |

| 1.3 ITS design and chip assembly constraints                                                                  | 21<br>23       |

xxi

| 2 Silicon Pixel Detectors in High Energy Physics                            | 25 |

|-----------------------------------------------------------------------------|----|

| 2.1 Interaction of particles with matter                                    | 26 |

| 2.1.1 Interaction with charged particles                                    | 26 |

| 2.1.2 Multiple scattering                                                   | 30 |

| 2.2 Silicon PN junction as a sensor                                         | 30 |

| 2.2.1 Silicon particle detector                                             | 34 |

| 2.2.2 Silicon tracker detector                                              | 36 |

| 2.3 CMOS technology and circuits                                            | 38 |

| 2.3.1 MOSFET                                                                | 39 |

| 2.3.2 Simple circuits                                                       | 42 |

| 2.3.3 The CMOS process                                                      | 43 |

| 2.4 Radiation Effects                                                       | 45 |

| 2.4.1 Total Ionizing Dose in transistors                                    | 46 |

| 2.4.2 Non Ionizing Energy Loss in sensors                                   | 47 |

| 2.4.3 Single Event Effects                                                  | 48 |

| 2.4.3.1 Single Event Upset mitigation implementing Triple Mode Redundancy . | 49 |

| 2.5 Technology Options for Pixel Detectors                                  | 50 |

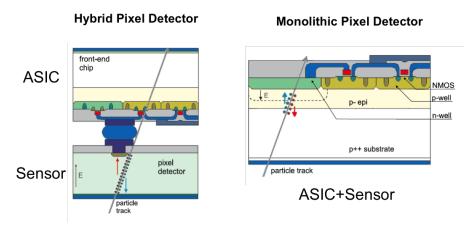

| 2.5.1 Hybrid pixels detectors                                               | 51 |

| 2.5.2 Monolithic active pixel sensors                                       | 52 |

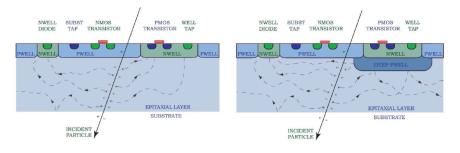

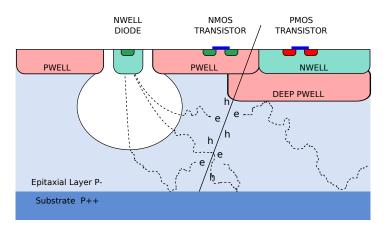

| 2.5.2.1 MAPS process                                                        | 52 |

| 2.5.2.2 MAPS Principle Operation                                            | 53 |

| 2.5.2.3 Detector Technology selection                                       | 55 |

| 2.6 Read-out architectures                                                  | 57 |

| 2.6.1 State of the art for MAPS : Rolling shutter                           | 58 |

| 2.6.1.1 The ULTIMATE ASIC                                                   | 59 |

| 2.6.2 Improved rolling shutter                                              | 60 |

| 2.6.2.1 MISTRAL                                                             | 60 |

| 2.6.2.2 ASTRAL                                                              | 62 |

| 2.6.3 New architecture ALPIDE                                               | 62 |

| 2.7 Conclusions and overview                                                | 63 |

|                                                                             |    |

| 3 Monolithic Active Pixel Sensor development for the ALICE                  |    |

| ITS Upgrade                                                                 | 65 |

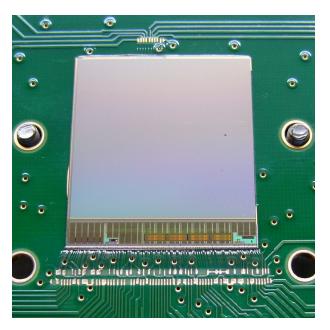

| 3.1 The Explorer Family                                                     | 67 |

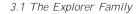

| 3.1.1 Read-out implementation                                               | 69 |

| 3.1.2 Read-out control                                   | 70  |

|----------------------------------------------------------|-----|

| 3.1.3 Experimental results                               | 72  |

| 3.2 The PADRE circuit in the pALPIDEss                   | 75  |

| 3.2.1 Encoding process                                   | 78  |

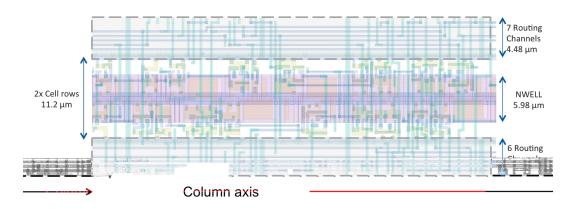

| 3.2.2 Physical Implementation                            | 81  |

| 3.2.3 PADRE implementation                               | 83  |

| 3.2.3.1 Considerations about power consumption           | 84  |

| 3.2.4 Experimental results                               | 85  |

| 3.2.4.1 Lab measurement                                  | 87  |

| 3.2.4.2 Test beam measurement                            | 88  |

| 3.3 ORTHOPIX                                             | 89  |

| 3.3.1 Implementation                                     | 93  |

| 3.3.2 Priority Address Encoder                           | 94  |

| 3.3.3 Shift Register                                     | 95  |

| 3.3.4 Experimental results                               | 96  |

| 3.4 Investigator                                         | 98  |

| 3.4.1 Experimental results                               | 101 |

| 3.5 SEU_TJ180 1                                          | .04 |

| 3.5.1 Single Event Upset measurements                    | 107 |

| 3.5.1.1 Single Event Latch-up measurements               | 110 |

| 3.6 Conclusions and overview                             | 12  |

|                                                          |     |

| 4 New full scale developments for the ALICE PIXEL DETEC- |     |

| -                                                        | 15  |

| 4.1 The ALPIDE family                                    | .16 |

| 4.2 pALPIDE3 1                                           | 22  |

|                                                          | 127 |

|                                                          | 130 |

|                                                          | 132 |

|                                                          | 133 |

|                                                          | 134 |

| 4.2.3.1 Analog Voltage drop 1                            | 135 |

| 4.2.3.2 Digital Voltage drop 1                           | 136 |

| 4.2.3.3 Power estimation                                 | 137 |

xxiii

| 4.3 Conclusions                                                                                                                   | 41 |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 5 Full scale experimental results 14                                                                                              | 43 |

| 5.1 Read-out System $\ldots \ldots 14$ | 43 |

| 5.2 ALPIDE family experimental results                                                                                            | 44 |

| 5.2.1 Charge Threshold Setting                                                                                                    | 46 |

| 5.2.2 Noise occupancy as a function of bias 1                                                                                     | 46 |

| 5.3 pALPIDEfs                                                                                                                     | 47 |

| 5.3.1 Source scan                                                                                                                 | 50 |

| 5.3.2 Test beam measurement. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                                            | 51 |

| 5.4 The pALPIDE2 18                                                                                                               | 52 |

| 5.4.1 Source scan                                                                                                                 | 52 |

| 5.4.2 Test beam measurement. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                                   | 55 |

| 5.5 The pALPIDE3 and pALPIDE3B1                                                                                                   | 56 |

| 5.5.1 Test beam measurement. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                                            | 58 |

| 5.6 Conclusion $\ldots$ 10                                                                                                        | 60 |

| 6 Conclusions and future work 10                                                                                                  | 63 |

| 6.1 Future work                                                                                                                   | 66 |

| Bibliography 1'                                                                                                                   | 71 |

# List of Figures

| 1.1  | Plate in recognition of the invention of the World Wide Web.                                                   | 2  |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Candidate Higgs boson events at $\sqrt{s} = 13$ TeV in the CMS (top) and ATLAS(bottom) experiments the LHC[4]. |    |

|      |                                                                                                                | 3  |

| 1.3  | An official guide during the CERN open days in 2014.                                                           | 3  |

| 1.4  | Picture of the LHC tunnel [5].                                                                                 | 4  |

| 1.5  | CERN's accelerators complex [6]                                                                                | 5  |

| 1.6  | Time line of the LHC Long Shutdown periods [8]. $\therefore$                                                   | 6  |

| 1.7  | Artistic view of the ATLAS experiment [10]                                                                     | 7  |

| 1.8  | Artistic view of The CMS experiment [11]                                                                       | 8  |

| 1.9  | Artistic view of the LHCb Detector characteristics [13].                                                       | 9  |

| 1.10 | VELO detector layout of LHCb [15]                                                                              | 10 |

| 1.11 | Layout of ALICE detector set-up, showing its division into subdetectors.                                       | 11 |

| 1.12 | ALICE event display of a PbPb collision at 2.76A TeV         [28].                                             | 14 |

| 1.13 | The ALICE ITS made out of six concentric barrels 2 layers of SPD, 2 layers of SDD, and 2 layers of SSD [30].   | 15 |

| 1.14 | Relation between impact parameter resolution and spa-<br>tial resolution for a pixel detector [35]             | 19 |

XXV

| 1.15 | New ITS conceptual layout with 3 Inner layers and 4<br>Outer layers [33]                                                                                                             | 20 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

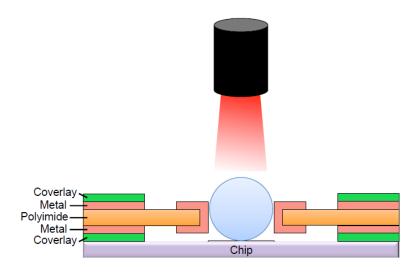

| 1.16 | Schematic view of new ITS staves [31]                                                                                                                                                | 22 |

| 1.17 | Schematic view of the laser soldering [31]. $\ldots$ $\ldots$                                                                                                                        | 23 |

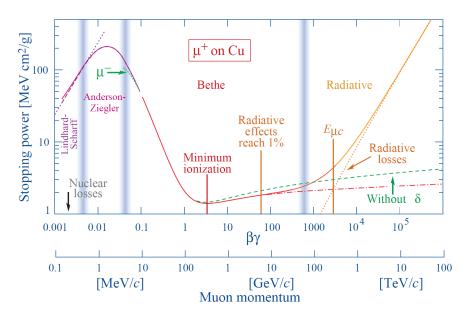

| 2.1  | Stopping power in matter of muons in copper [39]                                                                                                                                     | 28 |

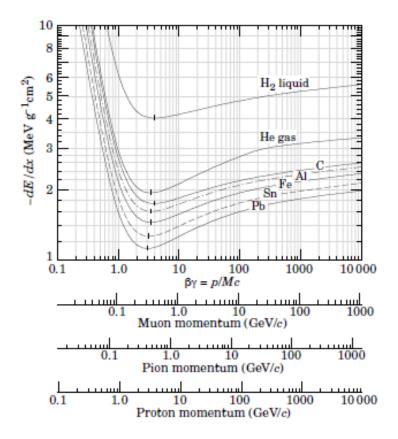

| 2.2  | Simulated stopping power for muon, pion and electrons momentum [39].                                                                                                                 | 29 |

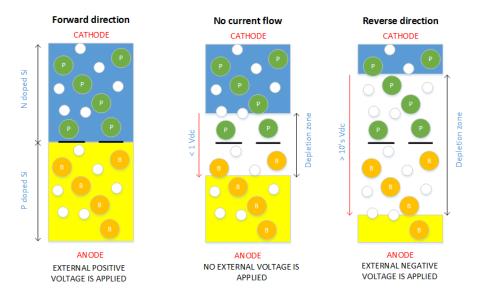

| 2.3  | PN junction current flow scenarios                                                                                                                                                   | 32 |

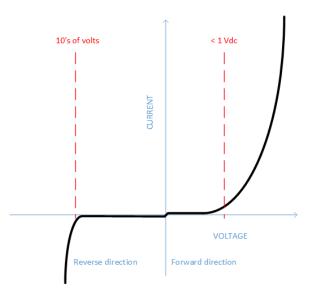

| 2.4  | Current - voltage characteristic curve of a PN junction.                                                                                                                             | 34 |

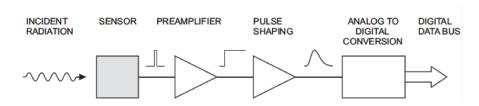

| 2.5  | Basic detector functions. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                             | 37 |

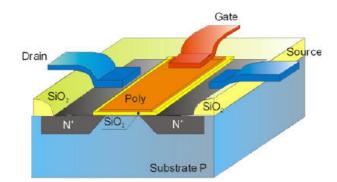

| 2.6  | Simple N-channel type transistor MOS with the sub-<br>strate (bulk), drain, gate and source electrodes and thin<br>insulating $SiO_2$ barrier [49]                                   | 39 |

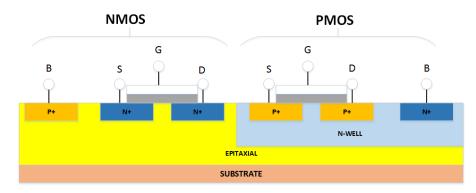

| 2.7  | Typical MOS transistors cross section[50], Usually the MAPS process includes an epitaxial layer.                                                                                     | 40 |

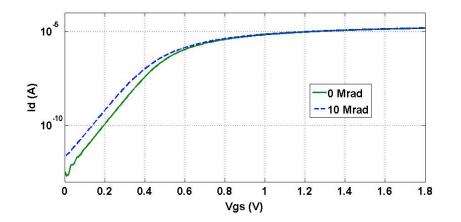

| 2.8  | TowerJazz 180 nm transistor, drain current Id versus<br>gate voltage Vgs for a minimum size NMOS transistor<br>before and after irradiation with 10 Mrad of 10keV X-<br>ray photons. | 41 |

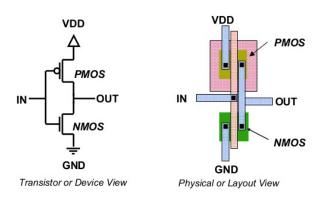

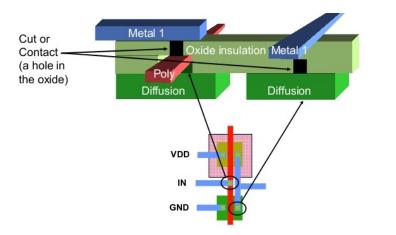

| 2.9  | Physical layout and schematic of an inverter gate. The device and its interconnections are made of polygons that represent different layers of material.                             | 42 |

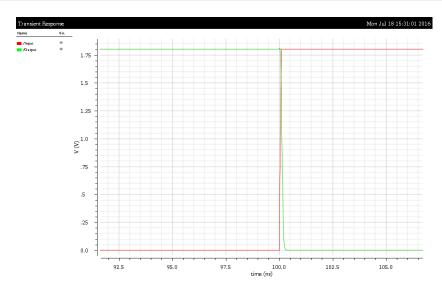

| 2.10 | Transient simulation of the inverter. $\ldots$                                                                                                                                       | 43 |

| 2.11 | Example of an inverter interconnected in a CMOS technology [49].                                                                                                                     | 44 |

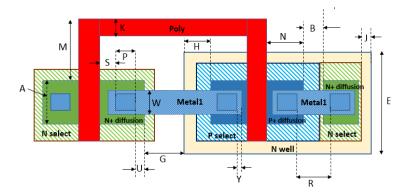

| 2.12 | Layout design rules.                                                                                                                                                                 | 44 |

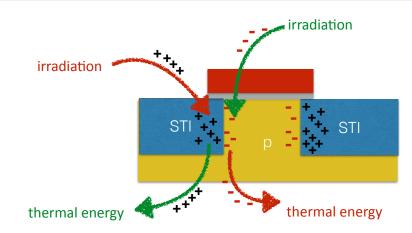

| 2.13 | The leakage current on nMOS under ionizing radiation.                                                                                                                                | 47 |

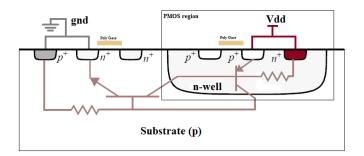

| 2.14 | Parasitic thyristor in a CMOS technology cross section [58].                                                                                                                         | 48 |

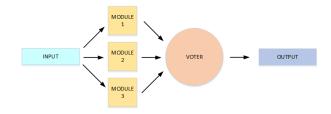

| 2.15 | TMR interconection diagram.                                                                                                                                                          | 49 |

xxvi

| 2.16 | TMR full interconection driagram.                                                                                                                                                                                                                                          | 50  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.17 | Charge collection in hybrid pixels and MAPS [62]                                                                                                                                                                                                                           | 51  |

| 2.18 | MAPS cross section [31]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                      | 54  |

| 2.19 | TowerJazz 180 nm MAPS cross section [31]                                                                                                                                                                                                                                   | 54  |

| 2.20 | ULTIMATE sensor designed on AMS 0.35 $\mu$ m technology [74]                                                                                                                                                                                                               | 60  |

| 3.1  | Comparison of the collection diode geometries of the nine sectors of the Explorer0 sensor and Explorer1 sensor. The geometries are equivalent for the two pixel pitches [88]                                                                                               | 68  |

| 3.2  | Conceptual schematic of the Explorer<br>1 ASIC. $\ . \ . \ .$                                                                                                                                                                                                              | 69  |

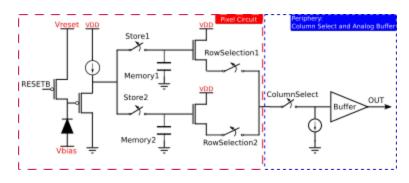

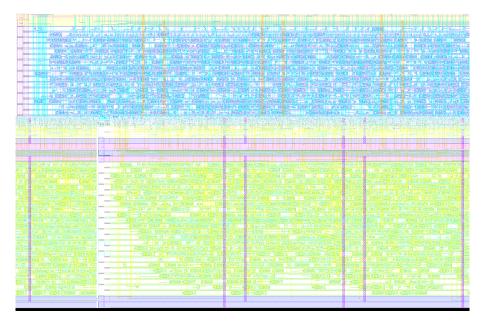

| 3.3  | Part of the Explorer sensor read-out layout implemented<br>by the author. Metal M1, M3 are for horizontal routing<br>in blue and magenta and M2 vertical is shown in green                                                                                                 | 70  |

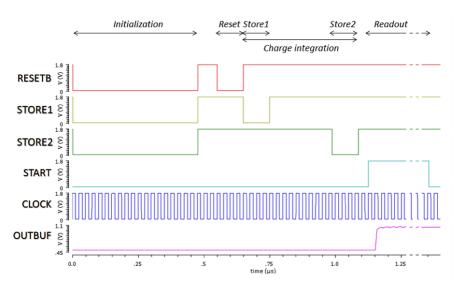

| 3.4  | Read-out control signals designed by the author. The<br>Pixel reset signal RESETB, the selection of the first<br>memory STORE1, selection of the second memory STORE<br>read-out start signal START, the general clock signal<br>CLOCK and the serial output signal OUTBUF | 22, |

| 3.5  | Detail of the OUTBUF signal                                                                                                                                                                                                                                                | 72  |

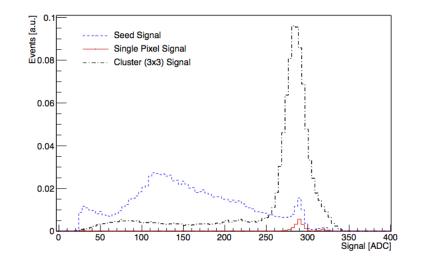

| 3.6  | Seed signal, single pixel cluster signal and $3 \times 3$ -cluster signal distribution for an Explorer1 sensor                                                                                                                                                             | 73  |

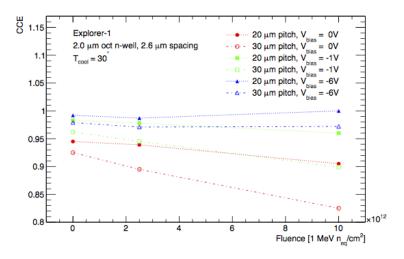

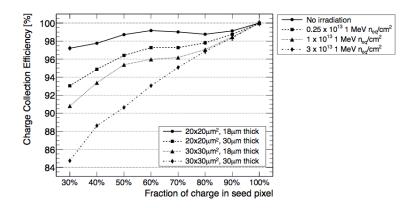

| 3.7  | Effect of NIEL and Cluster CCE measured with Explorer1 sensor for various collection diode designs and different $V_{BB}$ .                                                                                                                                                | 73  |

| 3.8  | Cluster CCE measured for Explorer1 sensor for different<br>sensor volumes and a back bias voltage of -6 Vdc before<br>and after irradiation.                                                                                                                               | 74  |

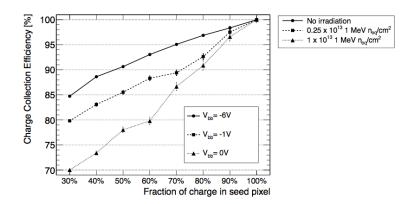

| 3.9  | Cluster CCE measured for a Explorer1 sensor with a $30 \times 30 \ \mu m^2$ pitch before and after irradiation for different back bias voltage.                                                                                                                            | 75  |

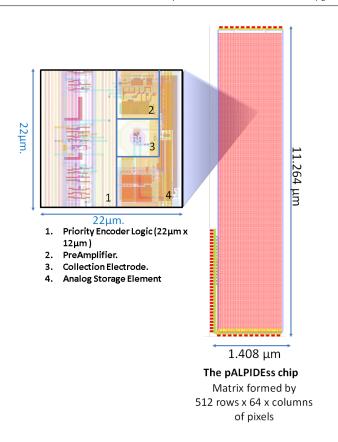

| 3.10 | pALPIDEss chip layout and pixel layout. The pixel is $22 \times 22 \ \mu m^2$ .                                                                                                                                                                                            | 76  |

xxvii

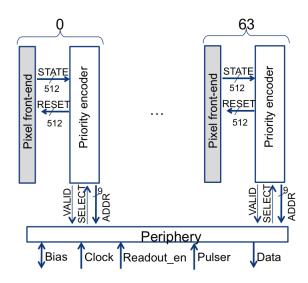

| 3.11 | pALPIDEss chip block diagram                                                                                                                                                                   | 77 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.12 | PADRE basic cell implemented by the author                                                                                                                                                     | 78 |

| 3.13 | Read-out of 2 fired pixels                                                                                                                                                                     | 79 |

| 3.14 | Simplified ALPIDEss PADRE tree interconection dia-<br>gram with 2 levels of hierarchy.                                                                                                         | 80 |

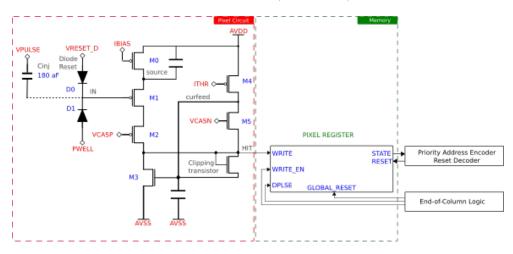

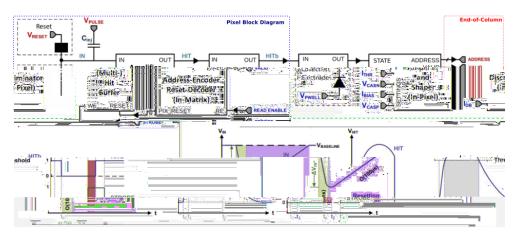

| 3.15 | pALPIDE front-end block diagram                                                                                                                                                                | 81 |

| 3.16 | Schematic drawing of the pALPIDEss sensor circuitry.                                                                                                                                           | 82 |

| 3.17 | pALPIDEss priority encoder implementation based on<br>customized standard cells, modified by the author; this<br>circuit is placed and routed using the Encounter CAE<br>tool                  | 84 |

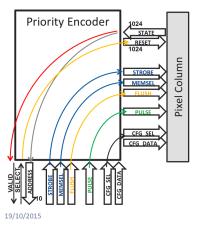

| 3.18 | Priority encoder circuit interfaced with a column of<br>front-end electronics merged with the Virtuoso CAE<br>tool                                                                             | 85 |

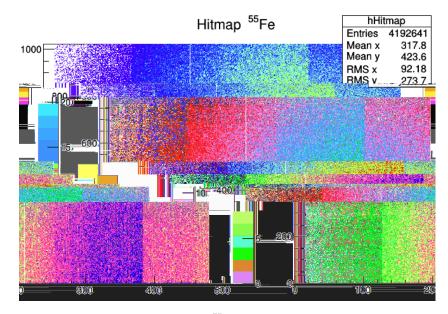

| 3.19 | pALPIDEss sensor hit-map under $^{55}{\rm Fe}$ irradiation source exposure with an epitaxial layer thickness of 18 $\mu{\rm m.}$ .                                                             | 87 |

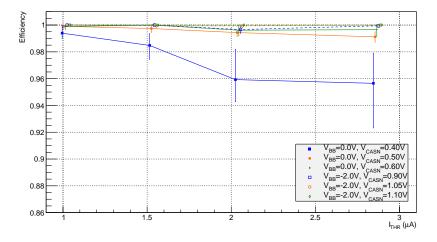

| 3.20 | pALPIDEss sensor test beam at CERN. The plot show the Charge Collection efficiency (CCE) vs different settings of $I_{THR}$ with different $V_{CASN}$ and $V_{BB}$ settings.                   | 88 |

| 3.21 | pALPIDEss sensor test beam at CERN. The plot shows<br>the hit fake rate vs different settings of $I_{THR}$ with dif-<br>ferent $V_{CASN}$ and $V_{BB}$ settings                                | 89 |

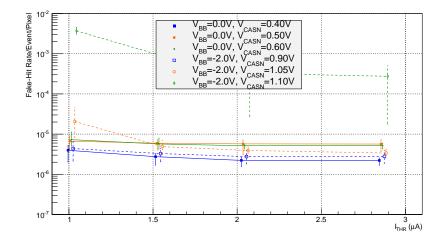

| 3.22 | Detection efficiency as function of $V_{CASN}$ and $I_{THR}$ settings for different pALPIDEss prototypes. Top: without reverse substrate bias $V_{BB} = 0$ Vdc. Bottom: for $V_{BB} = -2$ Vdc. | 90 |

| 3.23 | Orthopix chip layout and pixel floorplan                                                                                                                                                       | 91 |

| 3.24 | OrthoPix architecture projections scheme                                                                                                                                                       | 92 |

| 3.25 | Part of the read-out layout implemented by the author;<br>on top we can see the shift register and on bottom the<br>Priority Address Encoder.                                                  | 94 |

xxviii

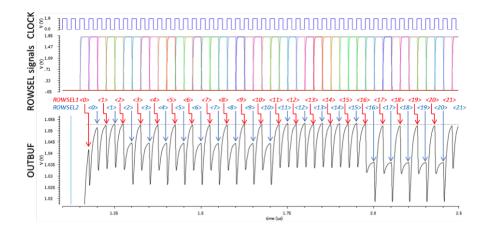

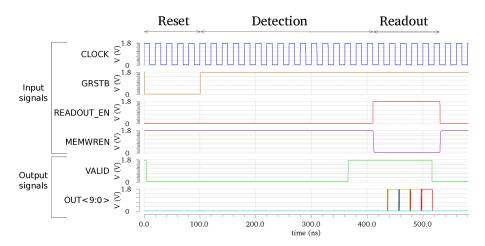

| 3.26 | ORTHOPIX chip read-out by a Priority Address En-<br>coder read-out control and output signals designed by<br>the author. The global clock signal CLK, the active low<br>global reset signal GSTB, the read-out enable signal<br>READOUT_EN the active low memory write enable<br>signal MEMWREN, the propagated or signal named<br>VALID and the column address bus OUT are shown. | 95  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

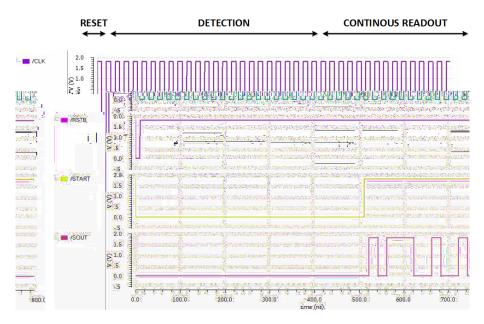

| 3.27 | ORTHOPIX chip read-out by a Priority Address En-<br>coder read-out control and output signals designed by<br>the author. The clock signal CLK, the active low reset<br>signal RSTB, the start enable signal START and the<br>shift register serial output SOUT are shown                                                                                                           | 96  |

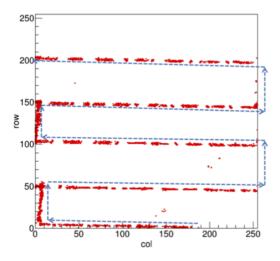

| 3.28 | Laser spot pattern through the ORTHOPIX sensor matrix and reconstructed pattern trace.                                                                                                                                                                                                                                                                                             | 97  |

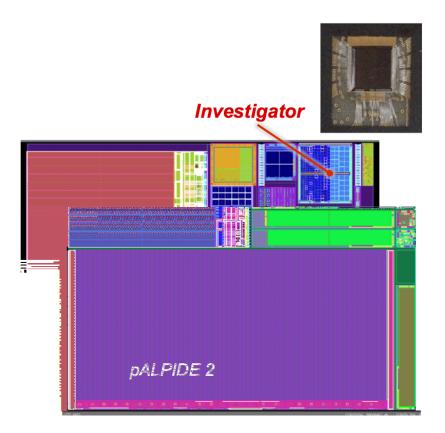

| 3.29 | Mask set Screen-shot of Engineering Run named ITS3.<br>The Investigator is located at the top, and one picture of<br>one wire-bonded Investigator chip to the carrier board<br>is shown in the top                                                                                                                                                                                 | 98  |

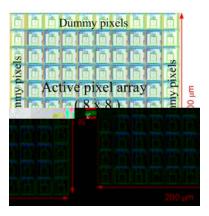

| 3.30 | $8 \times 8$ small prototype pixel matrix surrounded by dummy pixels                                                                                                                                                                                                                                                                                                               | 99  |

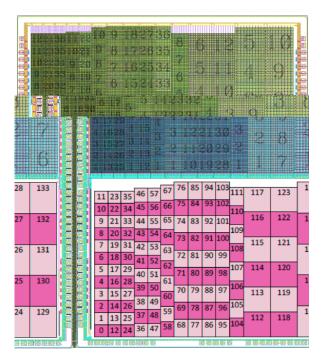

| 3.31 | Investigator Chip Mini-matrices location                                                                                                                                                                                                                                                                                                                                           | 100 |

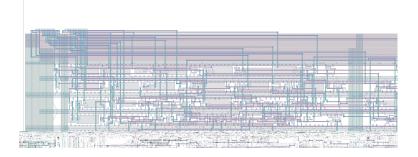

| 3.32 | Part of the layout of the Investigator sensor read-out implemented by the author.                                                                                                                                                                                                                                                                                                  | 101 |

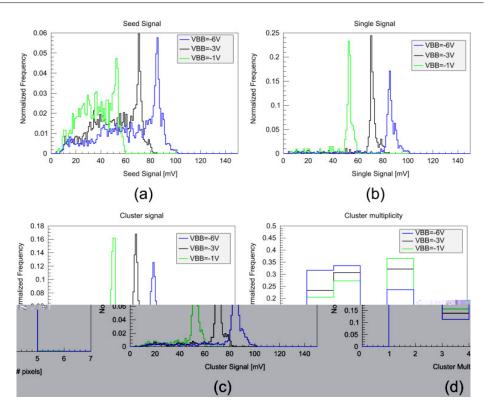

| 3.33 | Source follower signals vary with the substrate back bias voltage $V_{BB}$ =-6, $V_{BB}$ =-3 and $V_{BB}$ =-1: (a) seed signal, (b) single signal, (c) cluster signal and (d) cluster multiplicity.                                                                                                                                                                                | 102 |

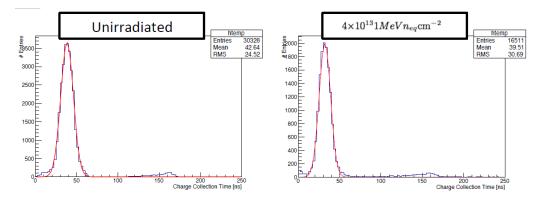

| 3.34 | Before and after neutron irradiation at the TRIGA MarkII<br>Reactor at JSI in Ljubljana using <sup>90</sup> Sr source using a<br>fluence of $4 \times 10^{13} 1 MeV n_{eq} \text{cm}^{-2}$ for 18 µm epitaxial,<br>$50 \times 50  \mu\text{m}^2$ pixel, with V <sub>BB</sub> -6 Vdc                                                                                                | 103 |

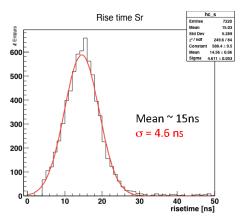

| 3.35 | Signal rise time after neutron irradiation at the TRIGA MarkII Reactor at JSI in Ljubljana using a neutrons $^{90}\text{Sr}$ source with a fluence of $1\times10^{14}1MeVn_{eq}\text{cm}^{-2}$ for 25 $\mu\text{m}$ epitaxial, $50\times50~\mu\text{m}^2$ pixel, with V_{BB} -6 Vdc.                                                                                               | 103 |

xxix

| 3.36 | SEU_TJ180 chip layout and floorplan implemented by<br>the author, at the top left a single port sram, at the<br>top right a dual port ram and bottom sea of flip-flips<br>connected in s-shape creating a shift register                                                                             | 104 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

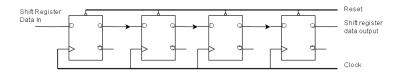

| 3.37 | Basic diagram of the Shift register interconnection                                                                                                                                                                                                                                                  | 106 |

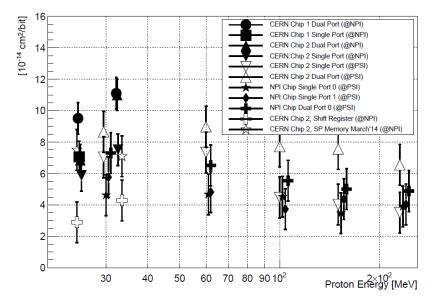

| 3.38 | SEU cross sections as a function of proton beam en-<br>ergy measured for two SEU ASICs in single and dual<br>port mode. For better readability, the values have been<br>slightly displaced horizontally.                                                                                             | 108 |

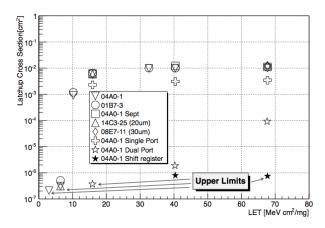

| 3.39 | Latchup cross section as a function of the LET mea-<br>sured for various SEU_TJ180 chips and various mem-<br>ory types. Some markers are upper limit values as no<br>latchup occurred over the measurement period                                                                                    | 111 |

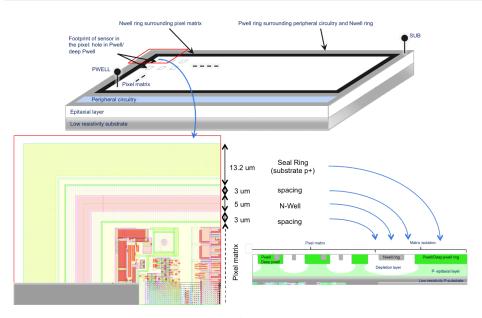

| 4.1  | Schematic illustration of the $p^+$ seal ring isolation around<br>the matrix active area and the application of the reverse<br>substrate bias in the ALPIDE design                                                                                                                                   | 117 |

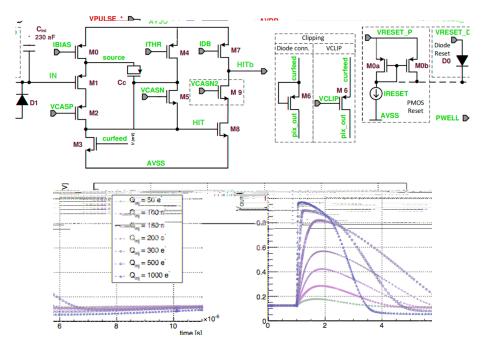

| 4.2  | pALPIDE3 sensor front-end principle of operation                                                                                                                                                                                                                                                     | 118 |

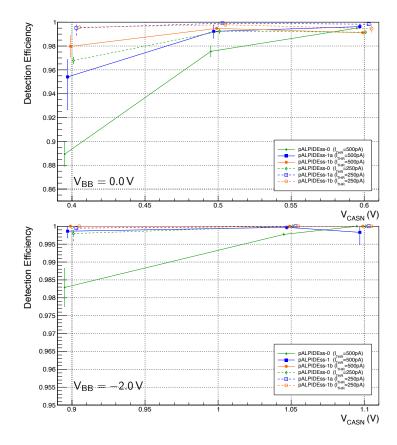

| 4.3  | pALPIDEfs sensor and pALPIDE2 sensor with four<br>front-end and one full custom front-end read-out lay-<br>out. The pixel layout components are: 1. collection<br>electrode, 2. preAmplifier & discriminator, 3. digital<br>custom storage element, 4. AERD full custom logic<br>Front-end read-out. | 119 |

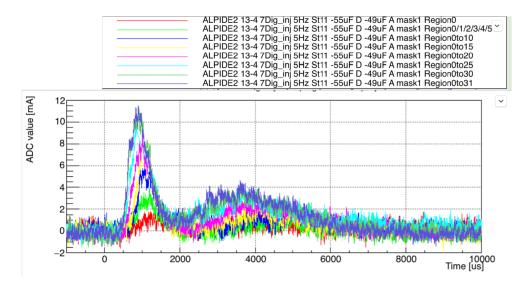

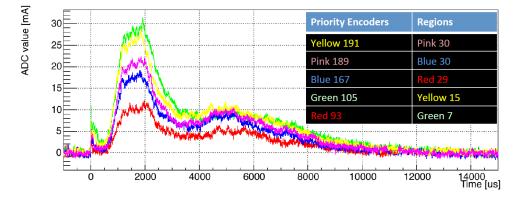

| 4.4  | pALPIDE2 chip dynamic power analysis                                                                                                                                                                                                                                                                 | 121 |

| 4.5  | pALPIDE2 chip dynamic power analysis pulsing differ-<br>ent regions.                                                                                                                                                                                                                                 | 122 |

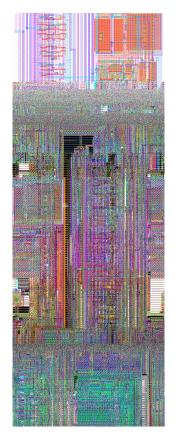

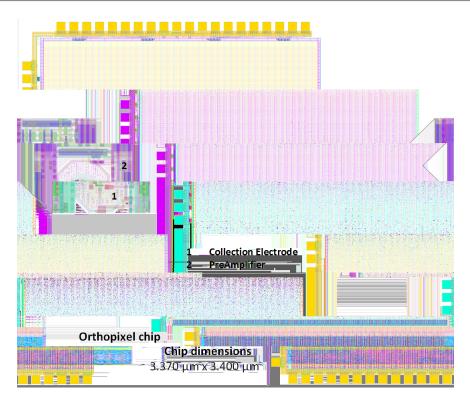

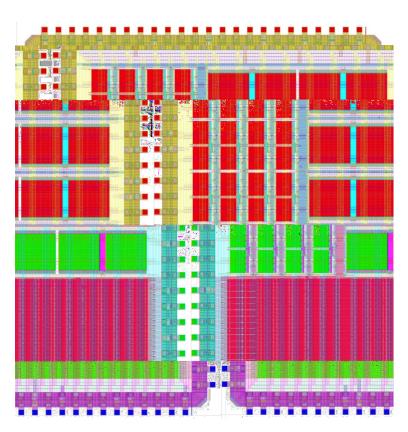

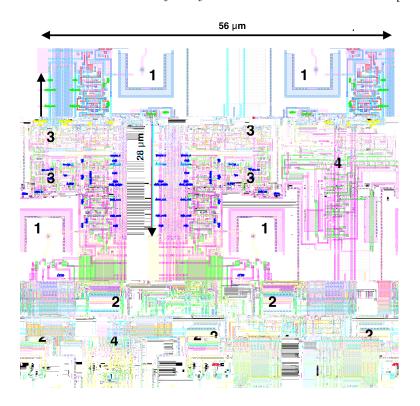

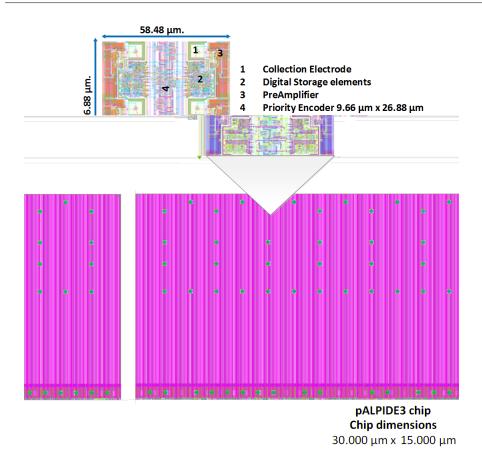

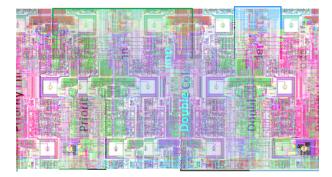

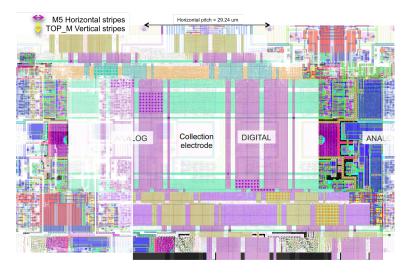

| 4.6  | ALPIDE3 chip layout assembled by the author using<br>Encounter CAE tool. The shows the pALPIDE3 pixel<br>layout components: 1. the collection electrode, 2. the<br>digital storage element, 3. the preAmplifier & discrim-<br>inator, 4. the Priority Encoder.                                       | 123 |

| 4.7  | At top pALPIDE3 pixel schematic and at bottom the front-end simulation of response to different input charges.                                                                                                                                                                                       | 124 |

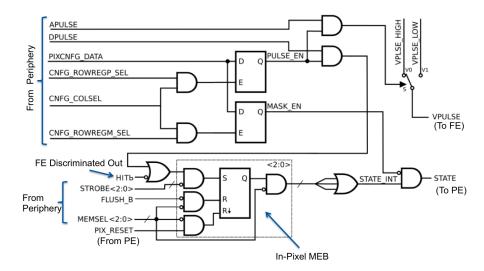

| 4.8  | pALPIDE3 IN pixel register.                                                                                                                                                                                                                                                                          | 125 |

|      |                                                                                                                                                                                                                                                                                                      |     |

List of Figures

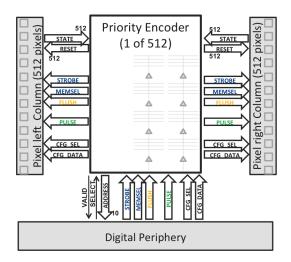

| 4.9  | The pALPIDE3 priority encoder is interfaced to 2 columns of 512 pixels and one End-Of-Column.                                                                                                                                                                                 | 3127 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.10 | The pALPIDE3 priority encoder implementation by the author using the Encounder CAE tool                                                                                                                                                                                       | 128  |

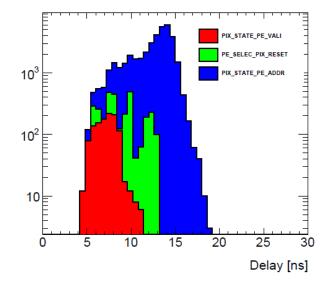

| 4.11 | Propagation of representative timing arcs in the Prior-<br>ity Encoder.                                                                                                                                                                                                       | 128  |

| 4.12 | Propagation delays of representative timing arcs ex-<br>tracted by the author.                                                                                                                                                                                                | 129  |

| 4.13 | Matrix block implemented by the author with digital flow.                                                                                                                                                                                                                     | 130  |

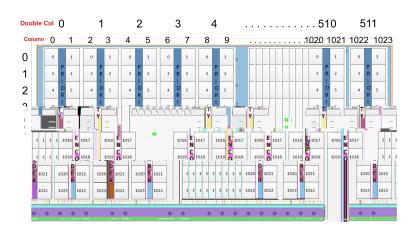

| 4.14 | Priority encoder and Matrix mapping pixel and matrix position.                                                                                                                                                                                                                | 131  |

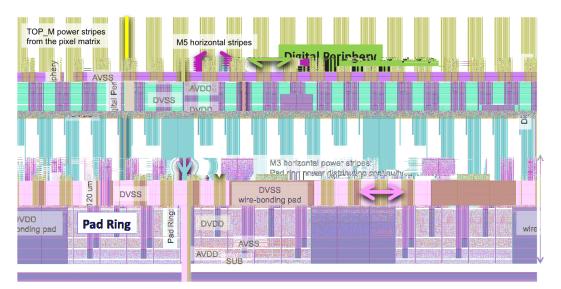

| 4.15 | Power routing mesh and integration of some digital<br>power pads layout; the power routing and pads place-<br>ment are implemented by the author. The metal top<br>layer consists of TOP_M vertical stripes, metal M5 hor-<br>izontal stripes and metal M3 horizontal stripes | 131  |

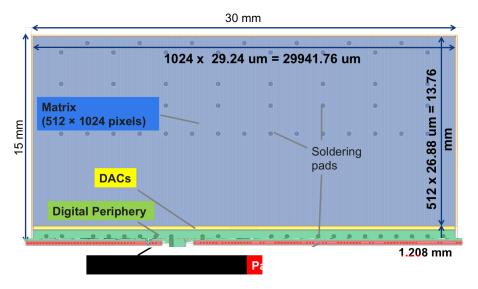

| 4.16 | pALPIDE3 chip floorplan, placement and routing by<br>the author with identification of some structures' spa-<br>tial position                                                                                                                                                 | 132  |

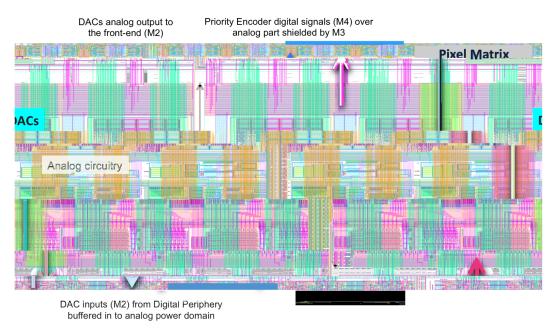

| 4.17 | Routing control signal and data though DAC block im-<br>plemented by the author                                                                                                                                                                                               | 133  |

| 4.18 | Matrix power mesh routed by the author                                                                                                                                                                                                                                        | 135  |

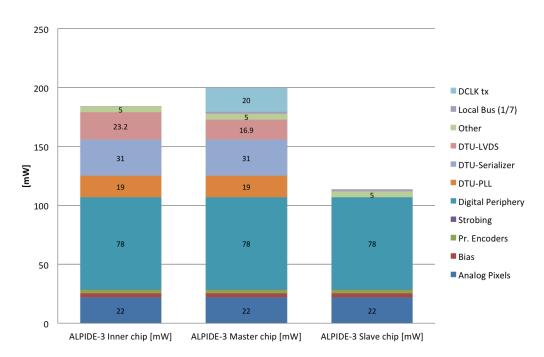

| 4.19 | pALPIDE3 chip power estimates by Encounter                                                                                                                                                                                                                                    | 137  |

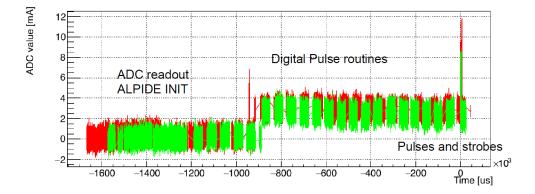

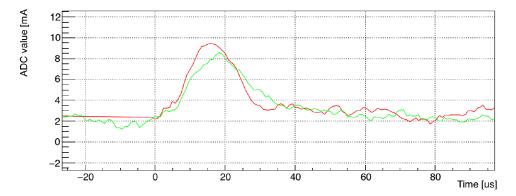

| 4.20 | The pALPIDE3, pulsing 1 pix_PE per column and 6 PE_region per region having in total = 192 fired Pixels on 32 regions; in Red no decoupling capacitor and Green: RO v3 nominal board(no modifications)                                                                        | 140  |

| 4.21 | The pALPIDE3, pulsing 1 pix_PE per column and 6 PE_region per region having in total = 192 fired Pixels on 32 regions; in Red no decoupling capacitor and Green: RO v3 nominal board(no modifications)                                                                        | 140  |

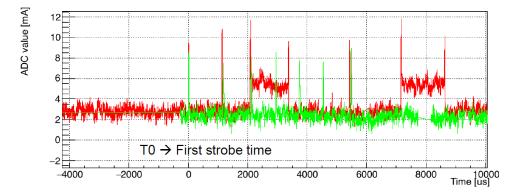

xxxi

| 4.22 | The pALPIDE3, pulsing 1 pix_PE per column and 6 PE_region per region having in total = 192 fired Pixels on 32 regions; in Red no decoupling capacitor and Green: RO v3 nominal board(no modifications) | 141  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

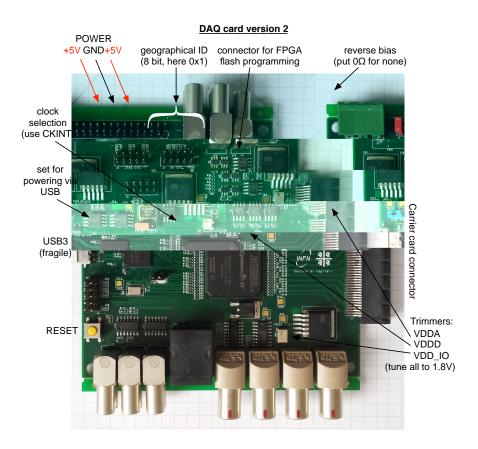

| 5.1  | Read-out DAQ board                                                                                                                                                                                     | 144  |

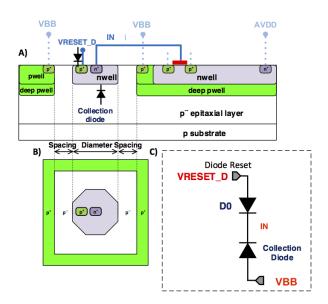

| 5.2  | Collection electrode and pixel circuit including diode<br>reset mechanism. a) Cross section, b) top projections,<br>c) circuit schematic                                                               | 148  |

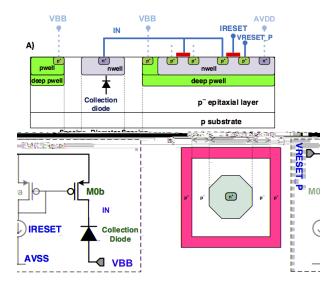

| 5.3  | Collection electrode and pixel circuit including pMOS<br>reset mechanism. a) Cross section.b) top projections,<br>c) circuit schematic                                                                 | 148  |

| 5.4  | pALPIDEfs hit-map under <sup>55</sup> Fe exposure. The source was placed over the colummn 0 and row 350, and easily are identify the different sensing elements throug all rows                        | .149 |

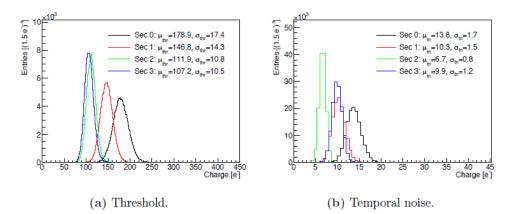

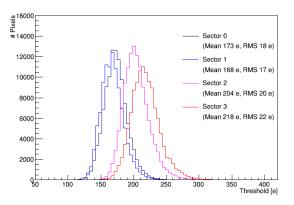

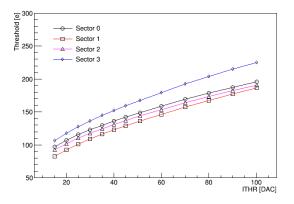

| 5.5  | Threshold and temperoal noise distribuctions (includ-<br>ing all pixels) for pALPIDEfs chipat $V_{BB} = -3$ Vdc,<br>$I_{THR} = 20$ DAC counts, and nominal $V_{CASN}$ .                                | 150  |

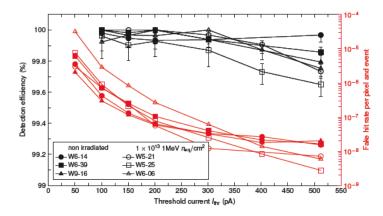

| 5.6  | pALPIDEfs efficiency and fake hit rate.                                                                                                                                                                | 151  |

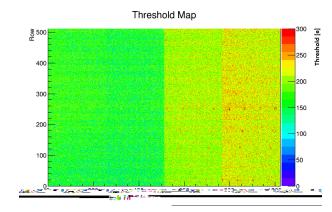

| 5.7  | pALPIDE2 Threshold Map nominal settings                                                                                                                                                                | 153  |

| 5.8  | pALPIDE2 Threshold Map $V_{BB}$ = -3 Vdc                                                                                                                                                               | 153  |

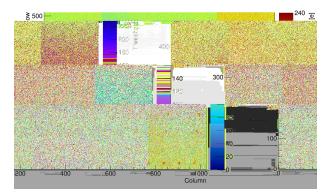

| 5.9  | pALPIDE2 Threshold Full chip nominal settings                                                                                                                                                          | 154  |

| 5.10 | pALPIDE2 Threshold Map on full chip, $V_{BB}$ = -3 Vdc.                                                                                                                                                | 154  |

| 5.11 | pALPIDE2 4 $\mu$ m spacing, 25 $\mu$ m epi, -6V back-bias pMOS reset                                                                                                                                   | 155  |

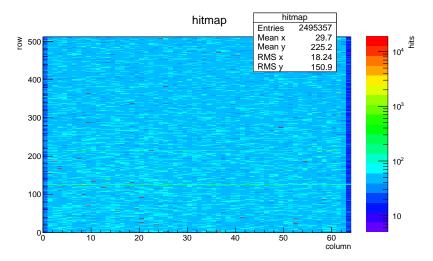

| 5.12 | pALPIDE3 hit-map with a $^{90}\mathrm{Sr}$ radiation source. $~$                                                                                                                                       | 157  |

| 5.13 | The pALPIDE3B with $3\mu$ m spacing, 25 $\mu$ m epi, -3 Vdc back-bias Diode reset, VCLIP and V <sub>CASN2</sub> in nominal settings.                                                                   | 158  |

| 5.14 | The pALPIDE3B with $3\mu$ m spacing, 25 $\mu$ m epi, -6 Vdc back-bias Diode reset, VCLIP and V <sub>CASN2</sub> in nominal settings.                                                                   | 158  |

| 5.15 | pALPIDE3B $3\mu$ m spacing, 25 $\mu$ m epi, -3 Vdc back-bias Diode reset, VCLIP and in nominal settings                                                                                                | 159  |

xxxii

### List of Tables

| 1.1 | LHC nominal beam parameters [7]                                                          | 6   |

|-----|------------------------------------------------------------------------------------------|-----|

| 1.2 | Summary of the ALICE detector subsystems [16]                                            | 13  |

| 1.3 | Properties of the current ITS layers [30]                                                | 15  |

| 1.4 | Nominal z-coverage of the ITS layers and z length of modules [31]                        | 20  |

| 1.5 | General specifications of the ITS pixel chip [31]. $\ldots$                              | 21  |

| 3.1 | Mini-matrix pixel size                                                                   | 100 |

| 3.2 | Blocks data selection output of the SEU_TJ180 chip $% \mathcal{S}_{\mathrm{T}}$ .        | 106 |

| 3.3 | TowerJazz SEU cross section measured at NPI and PSI.                                     | 107 |

| 3.4 | SEU Cross Sections and Flux                                                              | 107 |

| 3.5 | Available particles inside the cocktail at CyClotron of LOuvain la NEuve (CYCLONE2) [99] | 110 |

| 4.1 | Matrix metal layer widths                                                                | 135 |

| 4.2 | Read-out Scenario Summary                                                                | 138 |

| 4.3 | Read-out scenario summary(cont).                                                         | 139 |

| 4.4 | Overview of the read-out chips in the development of the ITS upgrade                     | 142 |

xxxiii

| 5.1 | Geometrical parameters and reset mechanisms of pALPI-<br>DEfs sensing elements in the four chip sectors 149 |

|-----|-------------------------------------------------------------------------------------------------------------|

| 5.2 | Geometrical parameters and reset mechanisms of pALPIDE2 sensing elements in the four chip sectors           |

| 5.3 | Geometrical parameters and reset mechanisms of pALPIDE3 sensing elements in the eight chip sectors          |

| 6.1 | Overview all pALPIDE chips deployed for the ITS up-<br>grade                                                |

xxxiv

Chapter 1

# CERN, the LHC and the ALICE ITS upgrade program

Over the last 60 years, CERN has been a model of international scientific collaboration and one of the most important research centers in the world of particle physics. The name of CERN is derived from the acronym in French Conseil Européen pour la Recherche Nucléaire and it is located across the French-Swiss border in the Geneva canton, founded on the  $29^{th}$  of September 1954 [1, 2].

CERN's success is not only based on its ability to produce scientific results of great interest, or the study of the particles of which matter is made of, but also because of the development of new technologies. Among them, early in the 1990's the World Wide Web (WWW) began as a CERN project. It was based on the concept of hypertext which was intended to facilitate sharing of information among researchers around the world. A plate is dedicated in one of corridors of the organization to the team who conceived the WWW (see Figure 1.1).

CERN's research infrastructure is primarily an interconnected set of particle accelerators and detectors of which the biggest one is the Large Hadron Collider (LHC), which became operational in 2008. Accelerators boost bunches of particles to high energies before the beams collide with each other or with stationary targets in the centre of the detectors that observe and record the results of these collisions [3].

1

Figure 1.1: Plate in recognition of the invention of the World Wide Web.

CERN celebrated the discovery of the Higgs boson on the 4<sup>th</sup> of July of 2012 by the ATLAS and CMS experiments. A new Higgs-like particle had been observed with mass of  $m_H = 125.09 \pm 0.24$  (0.21 statistical  $\pm$  0.11 systematic) GeV, which was the last missing piece of the Standard Model (SM). Nowadays researchers study the properties of the new boson and search for new physics beyond the SM (supersymmetry and dark matter).

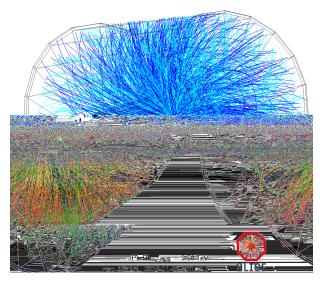

Figure 1.2 shows the candidate Higgs boson events from collisions in the center of the experiments. The top figure in the CMS experiment shows a decay into two photons (dashed yellow lines and green towers). The lower figure in the ATLAS experiment shows a decay into four muons (red tracks).

Between the 28<sup>th</sup> and 29<sup>th</sup> of September of 2013, CERN held two major events for the general public: the CERN Open Days, in which the laboratory was open to the general public and the experiments could be visited, guided by many physicist and engineering collaborators. Figure 1.3 shows a member of the open days crew during a visit to the ALICE experiment cavern.

In 2014 CERN celebrated its  $60^{th}$  anniversary with the good performance of the LHC. The United Nations Economic and Social Council (ECOSOC) and CERN celebrated science for peace and development highlighting the values of science and its ability to build bridges between nations. The event was the last in a series of celebrations organized by CERN.

Figure 1.2: Candidate Higgs boson events at  $\sqrt{s} = 13$  TeV in the CMS (top) and ATLAS(bottom) experiments the LHC[4].

Figure 1.3: An offical guide during the CERN open days in 2014.

Figure 1.4: Picture of the LHC tunnel [5].

The LHC is the world's largest and most powerful particle accelerator. Figure 1.4 shows a section of the LHC tunnel. The LHC machine was built inside the Large Electron Positron (LEP) tunnel, which was a circular collider with a circumference of 27 km straddling the border of Switzerland and France, which operated between 1989 until the end of 2000 and led to the world's most precise measurements of the  $Z^0$  boson.

The LHC accelerates and collides protons (p) at a centre-of-mass energy of  $\sqrt{s} = 13$  TeV as well as lead (Pb) ions at centre-of-mass energy per nucleon of  $\sqrt{s_{NN}} = 2.76$  TeV, and plans are to increase these energies to their design values of 14 TeV and 5.5 TeV, respectively [1] with an instantaneous luminosity exceeding  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>.

The LHC beam parameters are detailed in Table 1.1.

Protons are produced by a duoplasmatron source that ionizes hydrogen gas with an electric field. The protons have a kinetic energy of 100 keV after leaving the source. They enter a linear accelerator Linac that uses Radio-frequency (RF) cavities to increase the proton energy

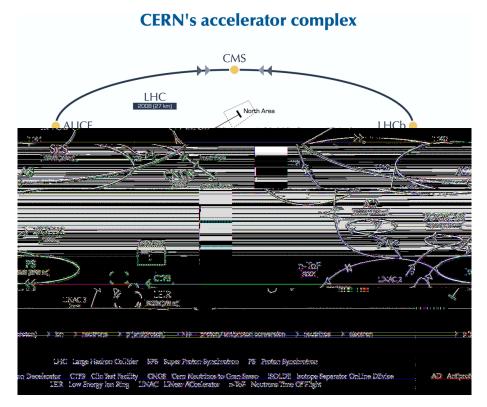

Figure 1.5: CERN's accelerators complex [6].

up to 50 MeV. The Proton Synchrotron Booster (PSB) then accelerates the protons up to 1.4 GeV, from where they are injected into the Proton Synchrotron (PS). The PS accelerates the protons to 25 GeV and splits the beam into smaller bunches of 4 ns length with a spacing of 25 or 50 ns as required by the LHC operation. The Super Proton Synchrotron (SPS) increases the proton beam energy to 450 GeV before the beams are finally injected into the LHC for further acceleration, from 450 GeV to 6.5 TeV per beam. Finally, beams cross at the center of the experiments and produce inelastic collisions interesting for the physics program of the LHC. Figure 1.5 summarizes the the accelerators complex and the experiments at CERN.

Chapter 1. CERN, the LHC and the ALICE ITS upgrade program

| Injection energy per beam             | 450 GeV                                  |

|---------------------------------------|------------------------------------------|

| Collision energy per beam             | 7000 GeV                                 |

| Nominal number of particles per bunch | $1.15 \times 10^{11}$                    |

| Nominal number of bunches per fill    | 2808                                     |

| Nominal luminosity                    | $10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ |

| Inelastic pp cross section            | 60  mb                                   |

| Total pp cross section                | $100 \mathrm{~mb}$                       |

| Bunch revolution frequency            | 11.245  kHz                              |

| Bunch frequency                       | $40.08 \mathrm{~MHz}$                    |

| Circumference length                  | $26.66~\mathrm{km}$                      |

| Radius                                | $4.24 \mathrm{~km}$                      |

| Number of dipole magnets              | 1232                                     |

| Number of quadrupole magnets          | 392                                      |

| Nominal magnetic field strength       | 8.33 T                                   |

Table 1.1: LHC nominal beam parameters [7].

The LHC physics program involves upgrades for high luminosity running starting after the Long Shutdown 2 (LS2) scheduled for 2019 and beyond (see Figure 1.6).

Figure 1.6: Time line of the LHC Long Shutdown periods [8].

The four main experiments of the LHC are ATLAS, CMS, LHCb and ALICE.

# 1.1.1 The ATLAS Experiment

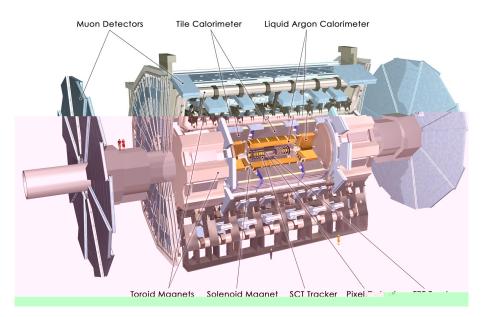

The ATLAS experiment [9] is a multi-purpose detector about 45 meters long, more than 25 meters high and an overall weight of approximately 7000 tonnes. The detector is divided into sub-detectors as shown in Figure 1.7. ATLAS is designed to work at high luminosity  $(10^{34} \text{ cm}^{-2} \text{ s}^{-1})$  with a bunch crossing every 25 ns. Therefore, the detector is built with highly sophisticated technologies and specialized materials. After the successful operation in Run 1 and the electronics consolidation campaign during the LS1, ATLAS is taking data again at  $\sqrt{s} = 13$  TeV.

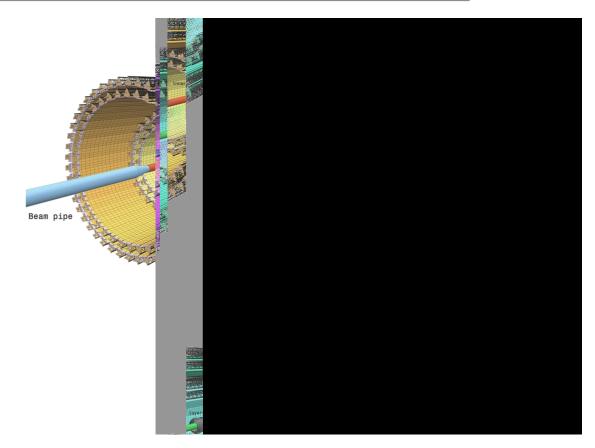

Figure 1.7: Artistic view of the ATLAS experiment [10].

The ATLAS inner detector is built around the beam pipe and is designed especially for tracking and vertexing. It is formed by the Pixel, the SCT (SemiConductor Tracker) and the TRT (Transition Radiation Tracker) detectors, that measure the trajectories of charged particles. The inner detector is embedded in a solenoidal magnet which generates a magnetic field of 2 T. The curvature of the trajectories which result from the the magnetic field bending power, is used to calculate the momentum of the particles. Additionally, the TRT provides electron identification measuring transition radiation photons generated in its radiator material. The electromagnetic and hadronic calorimeters surround the solenoid magnet and are designed to measure the energy of the different kinds of particles. The last layer of the detector is a huge muon spectrometer embedded in a toroidal magnet. The muon tracking system measures the trajectories of charged particles leaving the calorimeters. The trajectories are bent by the magnetic deflection provided by three superconducting air-core toroid magnets, which generate a field of 4 T.

## 1.1.2 The CMS Experiment

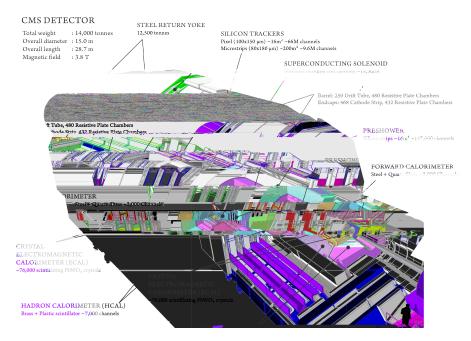

Figure 1.8: Artistic view of The CMS experiment [11].

The CMS (Compact Muon Solenoid) experiment [12] was built as a multi-purpose particle detector to study proton-proton, proton-lead, or lead-lead collisions at the TeV scale. It has large dimensions, being 22 m in length and 15 m in diameter, and a weight of 14.000 tonnes (see Figure 1.8). In the CMS detector each layer is specialized in detecting different types of particles. It covers nearly the full solid

angle of  $4\pi$  around the nominal interaction point. The distinctive characteristic feature of the CMS apparatus is the superconducting solenoid. Contained within the field volume are a silicon pixel and strip tracker, a crystal Electromagnetic Calorimeter (ECAL) and a brass/scintillator Hadron Calorimeter (HCAL). Muons are measured in gas-ionization detectors embedded in the steel return yoke.

### 1.1.3 The LHCb experiment

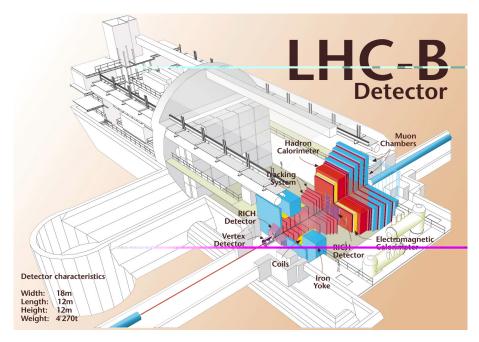

Figure 1.9: Artistic view of the LHCb Detector characteristics [13].

The LHCb experiment [14] specializes in investigating the slight differences between matter and antimatter by studying beauty quarks. hence the Large Hadron Collider beauty detector at the LHC. Figure 1.9 shows the LHCb experiment layout.

Instead of surrounding the entire collision point with an enclosed detector as ATLAS and CMS do, the LHCb experiment uses a series of subdetectors to detect mainly particle showers produced forward in the collision. The first subdetector is mounted close to the interaction

point, with the others following one behind the other over a length of 20 meters.

An abundance of different types of quarks are created in the interaction before they decay quickly into other particles. To record the b quarks, LHCb has developed sophisticated movable tracking detectors close to the path of the beams circling in the LHC. Figure 1.9 shows the layout of the LHCb experiment.

Figure 1.10: VELO detector layout of LHCb [15].

The VErtex LOcator "VELO" is the part of the LHCb detector closest to the collisions at the LHC. Its sensitive elements are Si detectors and during operation these are only 8 mm away from the beam. Its proximity to the interactions allows physicists to observe the decays of short lived particles, called B-mesons. The Bs have the property of decaying rapidly, in about one millionth of a millionth of a second. The VELO has been designed to perform an accurate measurement of their decay positions [15]. Figure 1.10 shows the VELO detector layout.

1.2 ALICE

# 1.2 ALICE

ALICE (A Large Ion Collider Experiment) [16] is a general-purpose, heavy-ion detector located at point 2 of the LHC ring [3]. It is designed to study the physics of strongly interacting matter, and in particular the properties of the Quark-Gluon Plasma (QGP), using pp, pPb and PbPb collisions at the LHC. The QGP is the state of matter in which quarks and gluons are deconfined, i.e. where they are not bound into hadrons but may move around freely. It is assumed that this was the state of our universe shortly after it was born with the Big Bang (at the age of 1 ps to 10  $\mu$ s) and it is the state that is created in collisions of high-energy heavy ions as they currently happen at the LHC [16].

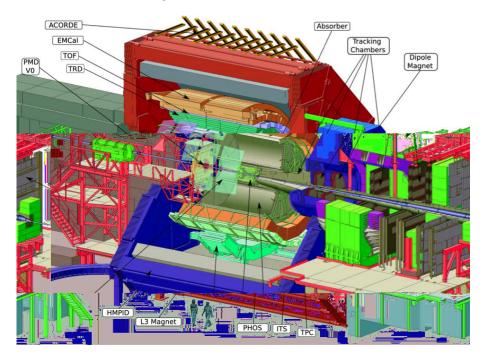

The ALICE apparatus as seen in Figure 1.11, consists of a central barrel, which measures hadrons, electrons, and photons, and a forward muon spectrometer along with some smaller detectors for trigger and event characterisation. It has dimensions of 26 m in length and 16 m in diameter, and a weight of 10 000 tonnes.

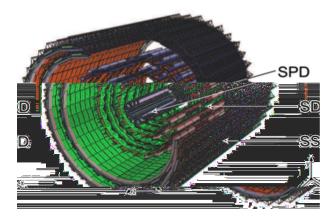

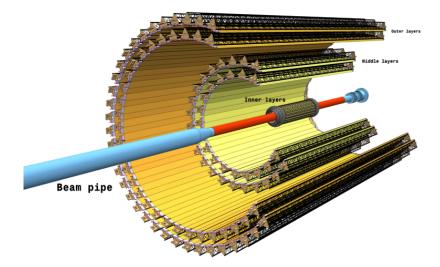

Figure 1.11: Layout of ALICE detector set-up, showing its division into subdetectors.

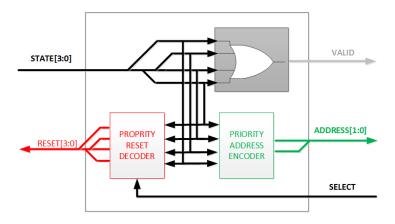

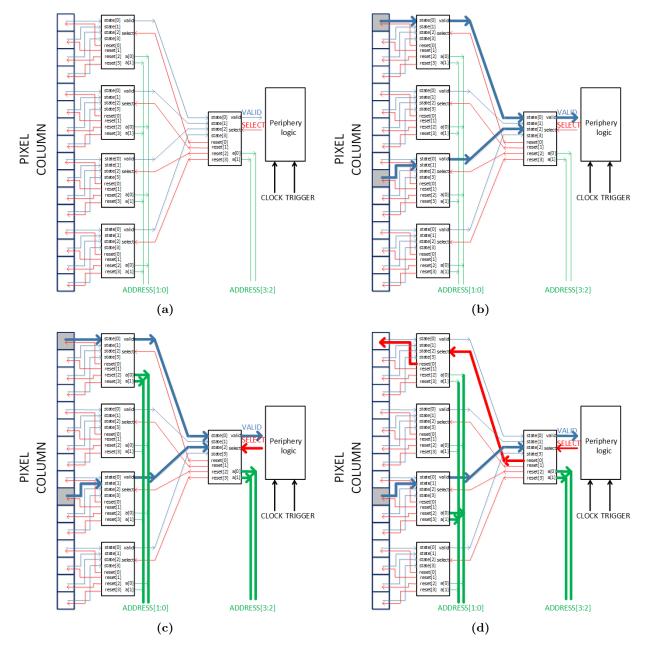

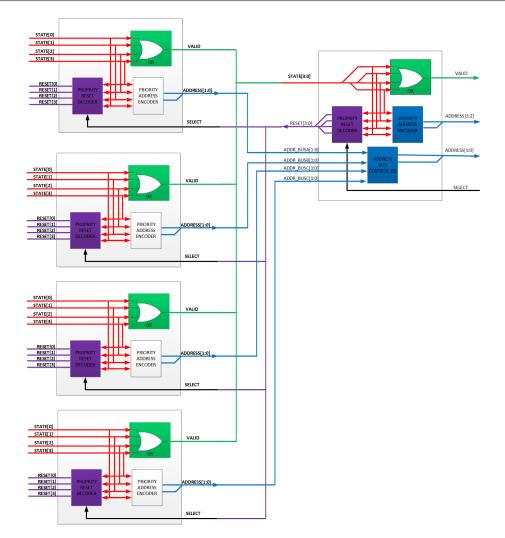

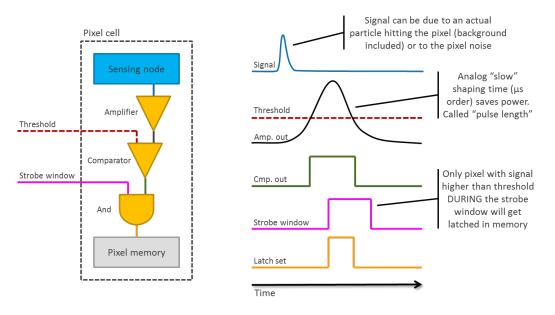

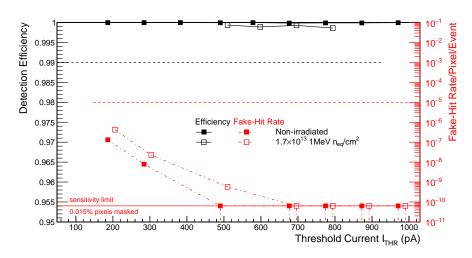

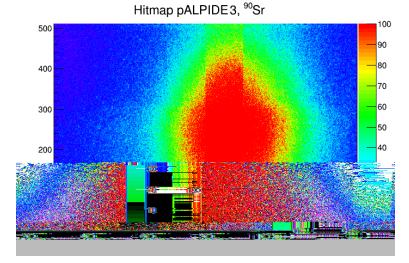

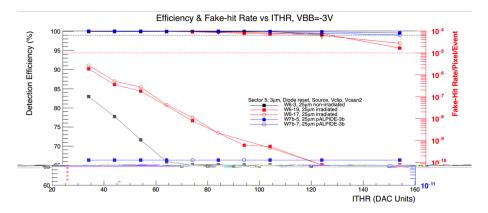

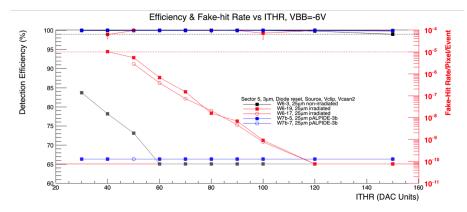

The central barrel is mounted inside a solenoidal magnet which provides a magnetic field of 0.5 T parallel to the beam axis. The detectors in the central barrel are mainly dedicated to vertex reconstruction, tracking, particle identification and momentum measurement. The main tracking detectors in the central barrel are the Time Projection Chamber (TPC) [17] and the Inner Tracking System (ITS)[18]. The ITS performs vertexing and is composed of six layers of silicon detectors: two layers each of Silicon Pixel Detector (SPD), Silicon Drift Detector (SDD) and Silicon Strip Detector (SSD) [19]. The other detectors in the central barrel are the Time Of Flight (TOF) detector [20] for particle identification, High Momentum Particle Identification (HMPID) [21], the Transition Radiation Detector (TRD) [22] counters for electron identification and two electromagnetic calorimeters, the Photon Spectrometer (PHOS) [23] and electromagnetic calorimeter (EMCAL) [24]. There are other smaller detectors for trigger and multiplicity measurement: the Photon Multiplicity Detector (PMD) [25], Forward Multiplicity Detector (FMD), V0 and T0 [26]. There are two sets of hadronic calorimeters which provide the centrality measurements: the Zero Degree Calorimeters (ZDC) [27] located on both sides of ALICE along the beam line at 115 m from the interaction point. In addition, there is an array of scintillators named ACORDE installed on top of the solenoid to trigger on cosmic rays for calibration purposes.