#### Universidad Politécnica de Valencia Departamento de Informática de Sistemas y Computadores

# Low-Memory Techniques for Routing and Fault-Tolerance on the Fat-Tree Topology

A dissertation submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY (COMPUTER SCIENCES)

Author

Crispín Gómez Requena

Advisors

María Engracia Gómez Requena Pedro Juan López Rodríguez

Valencia, Julio de 2010

## Acknowledgments

There have been a lot of people that have supported and helped me in several ways during all these years at the university. Most of them have greatly influenced my research and changed me as a person. I could not thank all of them, but I want to remark the support of several people.

First and foremost, I thank my parents and brothers for being always there. There are so many reasons to thank them that I should write an encyclopedia to enumerate them. Just to sum up, I would like thank my mother and father for being the strongest people I have ever met, I hope one day I could be half strong as them. I would like to thank my brother for introducing me in the world of the computers, I have spent most of my childhood watching him playing in the computer, and also thanks for all the great moments that we have had playing together. I would like to thank my sister for directing me during all my PhD, since she is indeed one of my advisors, and for all the great moments we have enjoyed working together. Also, I want to note that her children (Belén and Juan) are the joy of my live.

In second place, I would like to thank my friends, they all could make me laugh during the hard moments, so I could continue working to finish the PhD. Mainly, I would like to thank Paco, Merlyx, Blas and Diego. Paco is almost like a member of my family, I spend most of my free time playing or watching movies with him. Also, we have traveled around the world together, and we have several moments that I will remember forever. I would like to thank Merlyx (Paco's wife) for overfeeding me during our weekly D&D game, and for being such a kind person. I would like to thank Blas for introducing me to the "Futbol Xtreme", a sport that is only meant to we played by real men who can risk their lives in every single football match. Finally, I would

thank Diego for being such a freak, and traveling with me every year to the "Salò del Manga de Barcelona".

Of course, I would like to thank to my advisors, my sister (María Engracia) and Pedro López, for their guidance during all these years. This dissertation would not have been possible without all the time that we have spent discussing, and without their valuable knowledge. I hope that someday I could know the interconnection networks as well as you do. Like a friend told me once: "I have learned a great deal by simply observing their excellent example and behavior. I do not have any doubt that my research and non-research life has forever been changed by their advice". Also, I would like to thank Prof. José Duato for allowing me to be a part of the big family composed by all the members of the Parallel Architecture Group. Many of the other faculty members in the Parallel Architecture Group have helped me too, thanks to you all.

I have met many interesting students while in the lab. Although I cannot possibly mention everyone who has enriched my experience or provided moral support, I wish to specifically thank a few individuals: Gaspar, Andrés (both are lost in the mists of Intel), Blas, Paco, Samuel, Héctor, Carles, Rafa, and David. They all have unselfishly helped me in different aspects of my research and I would like to highlight their support. Finally, I have to highlight the amazing work of Ricardo, he is the one responsible of keeping our clusters up and running, and the one that help us when our computers start to act crazy.

# Contents

| A            | ckno     | wieagr | nents                                     | 11 |  |

|--------------|----------|--------|-------------------------------------------|----|--|

| A            | Abstract |        |                                           |    |  |

| $\mathbf{R}$ | esum     | nen    | xi                                        | x  |  |

| $\mathbf{R}$ | esum     | ı      | xxi                                       | ii |  |

| 1            | Inti     | roduct | ion                                       | 1  |  |

|              | 1.1      | Motiv  | ation                                     | 1  |  |

|              | 1.2      | Objec  | tives                                     | 6  |  |

|              | 1.3      | Disser | tation Outline                            | 8  |  |

| <b>2</b>     | Bac      | kgrou  | nd and State of the Art                   | 9  |  |

|              | 2.1      | Interc | onnection Networks                        | 0  |  |

|              |          | 2.1.1  | Interconnection Network Basics            | 1  |  |

|              |          | 2.1.2  | Interconnection Network Design Parameters | 4  |  |

|              |          | 2.1.3  | Topology                                  | 5  |  |

|              |          | 2.1.4  | Switching Techniques                      | 5  |  |

|              |          | 2.1.5  | Virtual Channels                          | 8  |  |

|              |          | 2.1.6  | Routing Technique                         | 1  |  |

|              |          | 2.1.7  | Fault-Tolerance                           | 2  |  |

|              |          | 2.1.8  | Network Metrics                           | 6  |  |

|              | 2.2      | State  | of the Art                                | 9  |  |

|              |          | 2.2.1  | Fault-Tolerance in MINs                   | 9  |  |

|              |          | 2.2.2  | Routing in Commodity Fat-Trees            | 3  |  |

vi

| L T | EI: F                                                      | ault-lolerant fat-free with Exclusion Intervals                                                                                                                                                                            | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-----|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3.1 | Introd                                                     | luction                                                                                                                                                                                                                    | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 3.2 | Static                                                     | Fault-tolerant Routing with Exclusion Intervals                                                                                                                                                                            | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 3.2.1                                                      | Computing the Exclusion Intervals                                                                                                                                                                                          | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 3.2.2                                                      | Extension to more than one fault                                                                                                                                                                                           | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 3.3 | Dynai                                                      | mic Fault-tolerance Routing with Exclusion intervals                                                                                                                                                                       | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 3.3.1                                                      | Informal Description                                                                                                                                                                                                       | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 3.3.2                                                      | Formal Description                                                                                                                                                                                                         | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 3.3.3                                                      | Multiple Faults Considerations                                                                                                                                                                                             | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 3.3.4                                                      | Avoiding Losing Packets during Reconfiguration                                                                                                                                                                             | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 3.4 | Evalu                                                      | ation                                                                                                                                                                                                                      | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 3.4.1                                                      | Simulation Environment                                                                                                                                                                                                     | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 3.4.2                                                      | Fault-Tolerance Results                                                                                                                                                                                                    | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 3.4.3                                                      | Dynamic Issues                                                                                                                                                                                                             | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|     | 3.4.4                                                      | Impact on Network Performance                                                                                                                                                                                              | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

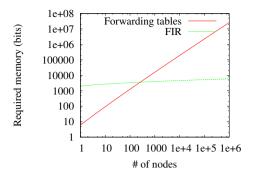

|     | 3.4.5                                                      | $FT^2EI$ Memory Requirements                                                                                                                                                                                               | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 3.5 | Concl                                                      | usions                                                                                                                                                                                                                     | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| DE  | STRO                                                       | : Effective Deterministic Routing in Fat-Trees                                                                                                                                                                             | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 4.1 | Introd                                                     | luction                                                                                                                                                                                                                    | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

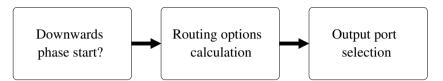

| 4.2 | Description of the Deterministic Routing algorithm         |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

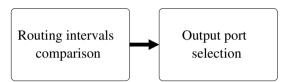

|     | 4.2.1                                                      | Implementation of <i>DESTRO</i> by using Flexible Interval                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|     |                                                            | Routing                                                                                                                                                                                                                    | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 4.3 | Evalu                                                      | ation                                                                                                                                                                                                                      | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|     | 4.3.1                                                      | Adaptive Routing Issues                                                                                                                                                                                                    | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|     | 4.3.2                                                      | Traffic Patterns                                                                                                                                                                                                           | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|     | 4.3.3                                                      | Simulation Environment                                                                                                                                                                                                     | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

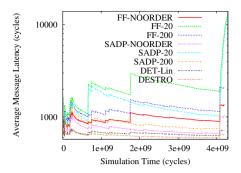

|     | 4.3.4                                                      | Performance Results                                                                                                                                                                                                        | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|     | 4.3.5                                                      | DESTRO Memory Requirements                                                                                                                                                                                                 | 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 4.4 | Concl                                                      | usions                                                                                                                                                                                                                     | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RU  | <i>FT</i> : Si                                             | mplifying the Fat-tree Topology                                                                                                                                                                                            | 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5.1 | Introd                                                     | luction                                                                                                                                                                                                                    | 168                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5.2 | Descri                                                     | iption of the RUFT Topology                                                                                                                                                                                                | 169                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| ·-  |                                                            |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|     | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>DE<br>4.1<br>4.2<br>4.3 | 3.1 Introd 3.2 Static 3.2.1 3.2.2 3.3 Dynas 3.3.1 3.3.2 3.3.3 3.3.4 3.4 Evalu 3.4.1 3.4.2 3.4.3 3.4.5 3.5 Concl  DESTRO 4.1 Introd 4.2 Descr 4.2.1  4.3 Evalu 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.4 Concl  RUFT: Si 5.1 Introd | 3.2.1       Computing the Exclusion Intervals         3.2.2       Extension to more than one fault         3.3       Dynamic Fault-tolerance Routing with Exclusion intervals         3.3.1       Informal Description         3.3.2       Formal Description         3.3.3       Multiple Faults Considerations         3.3.4       Avoiding Losing Packets during Reconfiguration         3.4       Evaluation         3.4.1       Simulation Environment         3.4.2       Fault-Tolerance Results         3.4.3       Dynamic Issues         3.4.4       Impact on Network Performance         3.4.5       FT <sup>2</sup> EI Memory Requirements         3.5       Conclusions     DESTRO: Effective Deterministic Routing in Fat-Trees  4.1  Introduction  4.2.1 Implementation of DESTRO by using Flexible Interval Routing  4.3.1 Adaptive Routing Issues 4.3.2 Traffic Patterns 4.3.3 Simulation Environment 4.3.4 Performance Results 4.3.5 DESTRO Memory Requirements  4.4  Conclusions  RUFT: Simplifying the Fat-tree Topology  5.1 Introduction  Introduction  Introduction  Intervals  Introduction  Intervals  Introduction  Intervals  Introduction  Intervals  Introduction  Intervals  Intervals  Intervals  Introduction  Intervals  Intervals |  |

| Contents | vii |

|----------|-----|

|          |     |

|    | 5.4    | Evaluation                                | 7                |  |  |

|----|--------|-------------------------------------------|------------------|--|--|

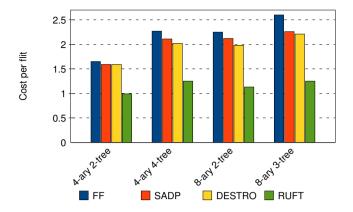

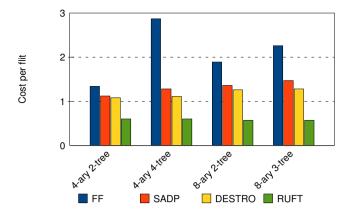

|    |        | 5.4.1 Cost Comparison                     | 3                |  |  |

|    |        | 5.4.2 Simulation Environment              | 1                |  |  |

|    |        | 5.4.3 Performance Results                 | 3                |  |  |

|    |        | 5.4.4 Cost and Performance Comparison 194 | 1                |  |  |

|    | 5.5    | Conclusions                               | 1                |  |  |

| c  |        |                                           | •                |  |  |

| 6  |        | aclusions 203                             | _                |  |  |

|    | 6.1    | Conclusions                               | 3                |  |  |

|    | 6.2    | Future Work                               | 5                |  |  |

|    | 6.3    | Contributions                             | ĉ                |  |  |

| R  | ihliod | graphy 209                                | a                |  |  |

| ப. | DITO   | graphy 208                                | Bibliography 209 |  |  |

viii Contents

# List of Figures

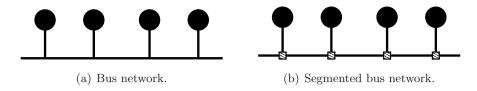

| 2.1  | An example of shared-medium network (a), and a switch-based       |    |

|------|-------------------------------------------------------------------|----|

|      | network (b)                                                       | 12 |

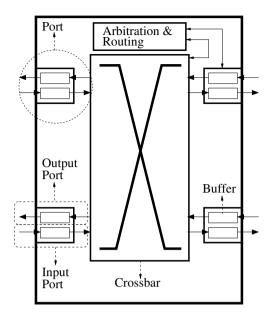

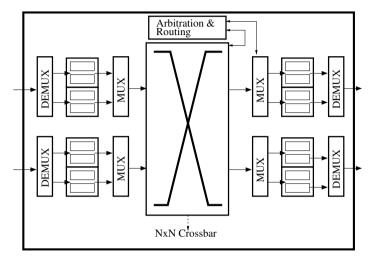

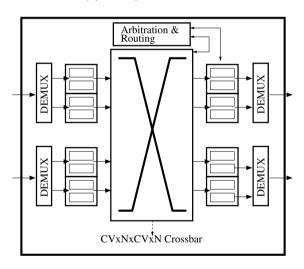

| 2.2  | Simplified view of a 4x4 switch                                   | 13 |

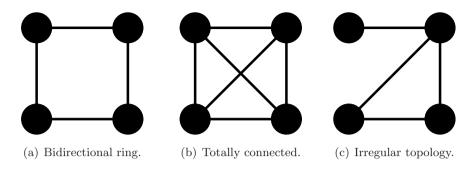

| 2.3  | Example of different topologies to interconnect four nodes        | 16 |

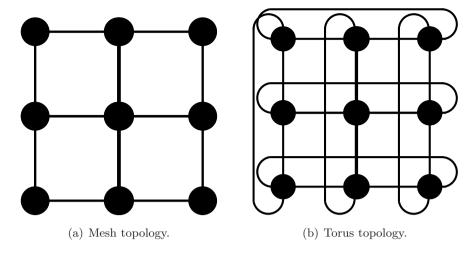

| 2.4  | Two examples of direct networks                                   | 19 |

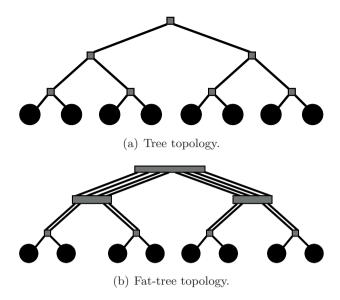

| 2.5  | Two examples of indirect networks                                 | 20 |

| 2.6  | Two examples of multistage interconnection networks               | 21 |

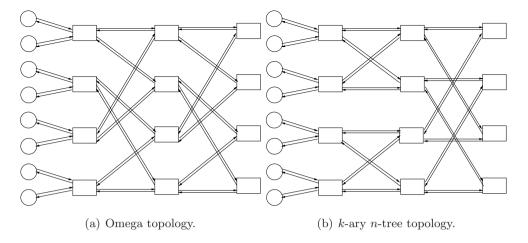

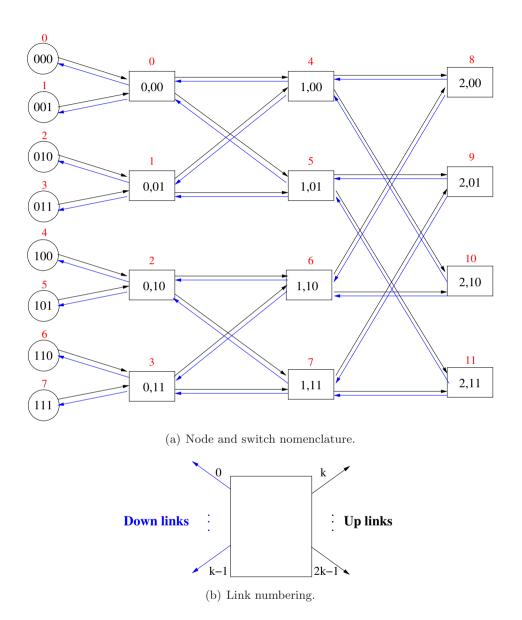

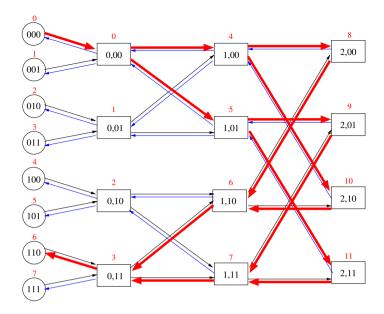

| 2.7  | Used nomenclature and numbering for nodes, switches and links.    | 24 |

| 2.8  | Two types of virtual channels switches                            | 30 |

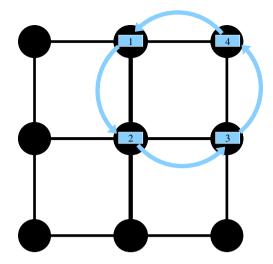

| 2.9  | Example of a deadlock of 4 packets in a mesh network              | 33 |

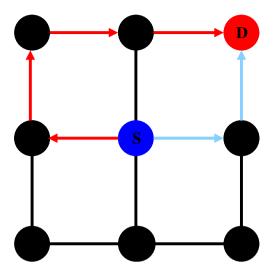

| 2.10 | Difference between non-minimal path (in red) and minimal path     |    |

|      | (in light blue) between two nodes in a mesh                       | 34 |

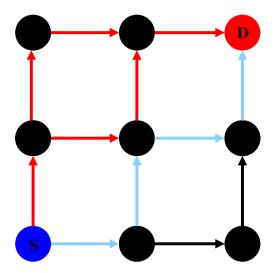

| 2.11 | Difference between deterministic routing (in light blue), par-    |    |

|      | tially adaptive routing (in red), and fully adaptive              | 36 |

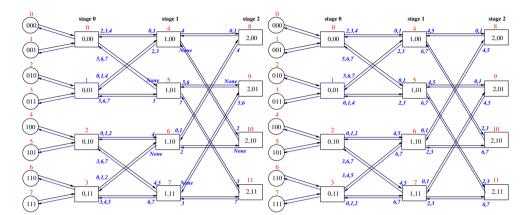

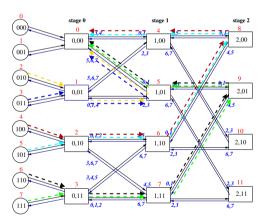

| 2.12 | All the possible routes for a packet from node 1 to node 6 in a   |    |

|      | 2-ary 3-tree                                                      | 39 |

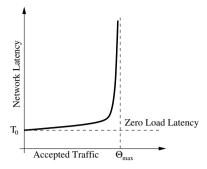

| 2.13 | Ideal performance graphics of a network                           | 48 |

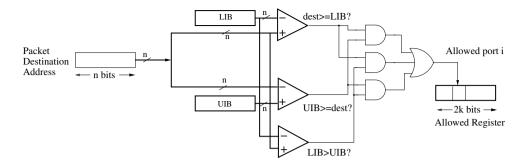

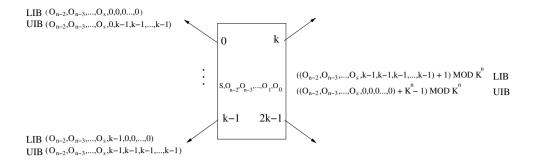

| 3.1  | IR hardware associated to each output port                        | 60 |

| 3.2  | A 8-node 2-ary 3-tree. Paths coming from node 0 to node 2 are     |    |

|      | highlighted                                                       | 62 |

| 3.3  | Prototyped IR register configuration for adaptive routing in fat- |    |

|      | trees                                                             | 63 |

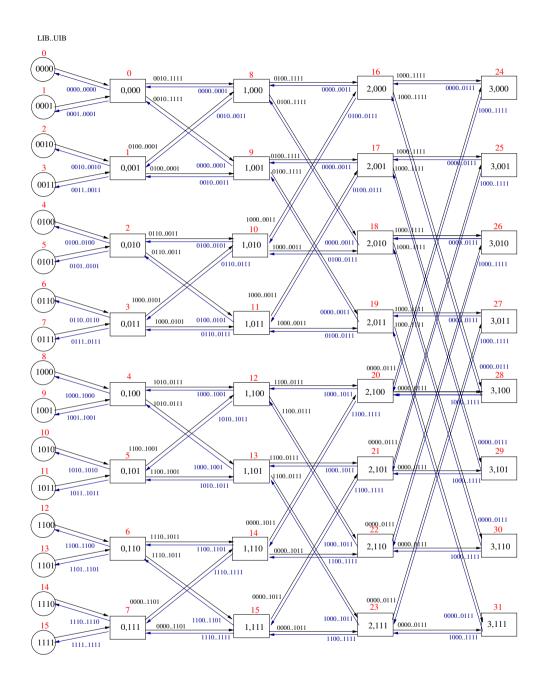

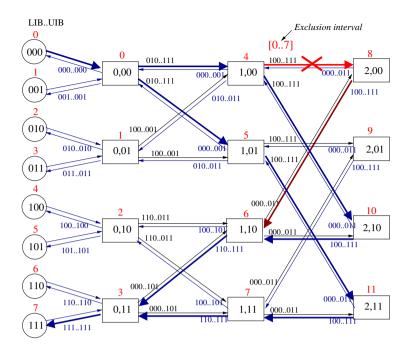

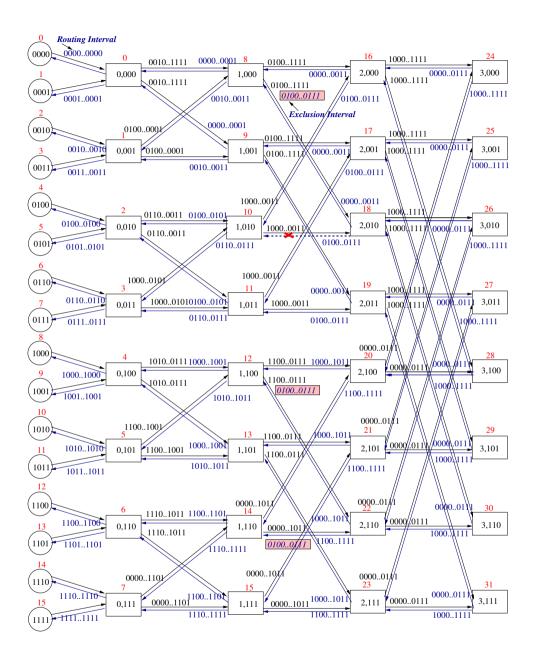

| 3.4  | Adaptive routing with IR in a 2-ary 4-tree                        | 65 |

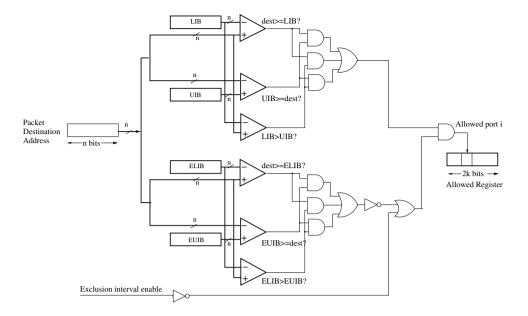

| 3.5  | $FT^2EI$ hardware associated to each output port                  | 68 |

x List of Figures

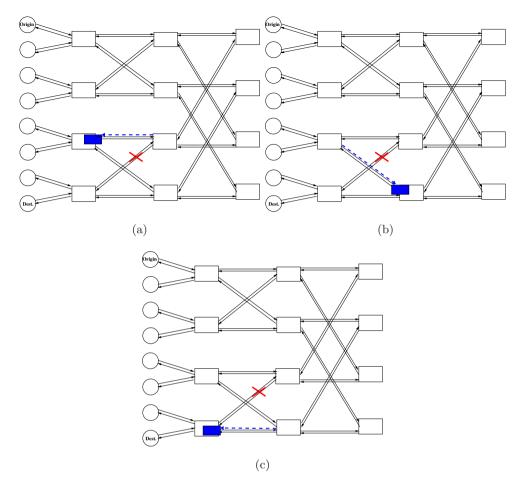

| 3.6  | Example of ascending fault handling 69                                 | 9 |

|------|------------------------------------------------------------------------|---|

| 3.7  | A 2-ary 4-tree with a faulty link at switch 18                         | 0 |

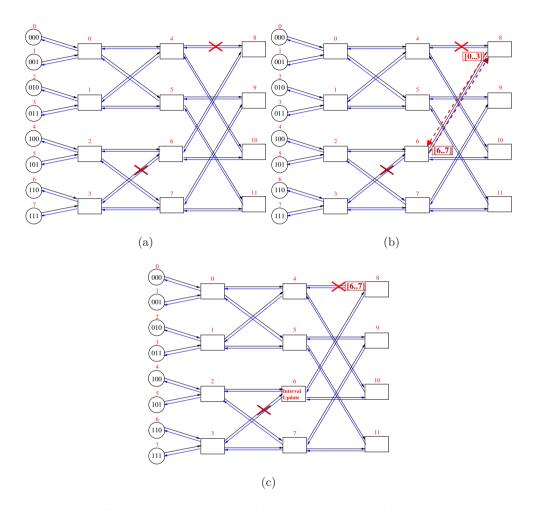

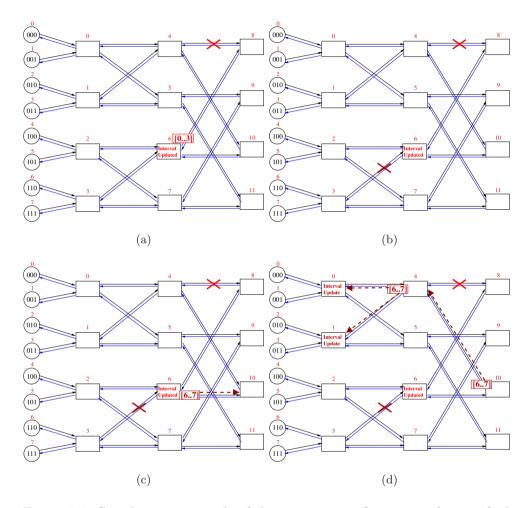

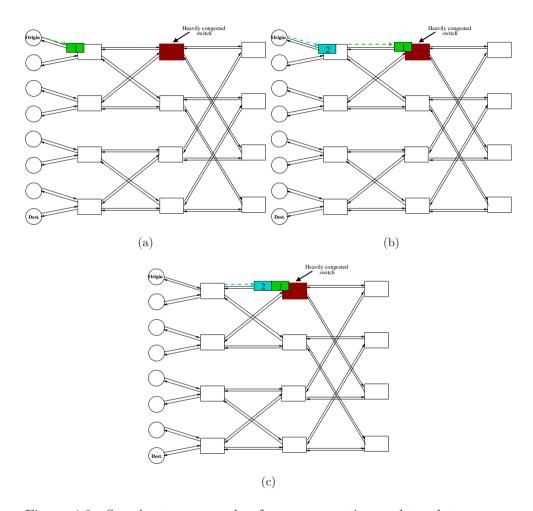

| 3.8  | Step-by-step example of an incorrect reconfiguration due to two        |   |

|      | simultaneous faults                                                    | 6 |

| 3.9  | Step-by-step example of the correct reconfiguration of a new           |   |

|      | fault despite the presence of previous faults                          | 8 |

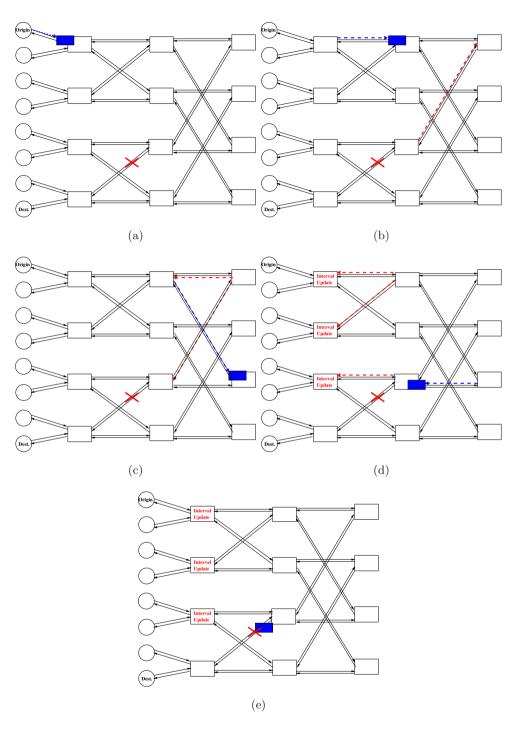

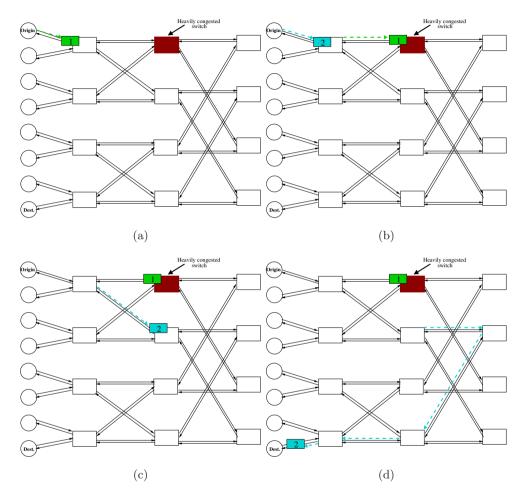

| 3.10 | Step-by-step example of packet lost during reconfiguration 9           | 1 |

| 3.11 | Step-by-step example of a deviated packet through an emer-             |   |

|      | gency path                                                             | 2 |

| 3.12 | 2-ary 3-tree with two faults that break the network connectivity. 9    | 6 |

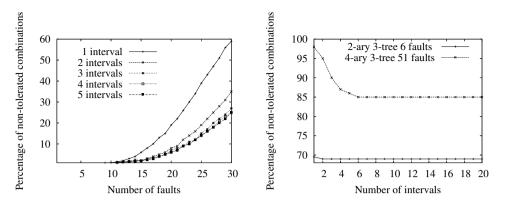

| 3.13 | Percentage of non-tolerated combinations versus number of faults. $99$ | 9 |

| 3.14 | Percentage of non-tolerated combinations                               | 1 |

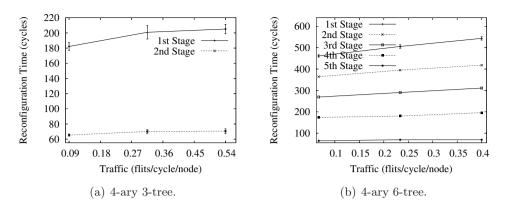

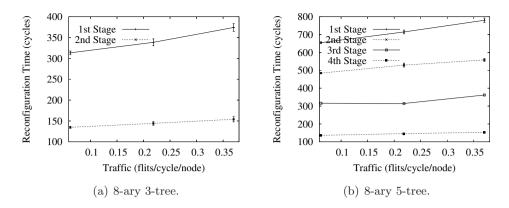

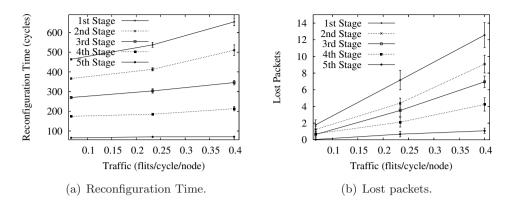

| 3.15 | Reconfiguration time classifying the faults by the stage at which      |   |

|      | they are located for different traffic loads                           | 3 |

| 3.16 | Reconfiguration time classifying the faults by the stage at which      |   |

|      | they are located for different traffic loads                           | 4 |

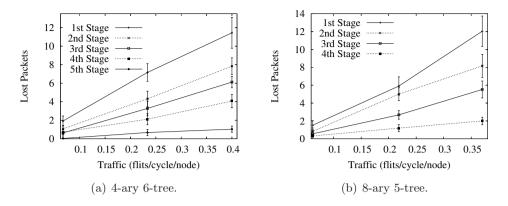

| 3.17 | Number of lost packets classifying the faults by the the stage         |   |

|      | at which the fault is located for different traffic loads $100$        | 6 |

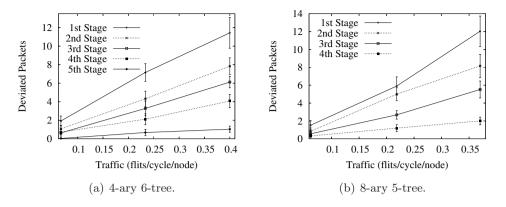

| 3.18 | Number of deviated packets depending on which stage the fault          |   |

|      | is located at for a 4-ary 6-tree with emergency path $10^{\circ}$      | 7 |

| 3.19 | Results for a 4-ary 6-tree without giving priority to the fault-       |   |

|      | tolerance control packets                                              | 8 |

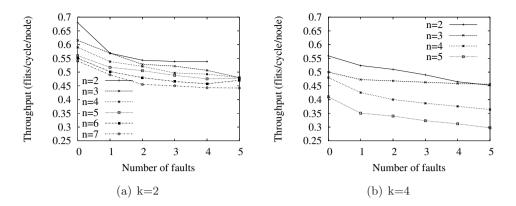

| 3.20 | Network throughput degradation for one exclusion interval $10^{\circ}$ | 9 |

| 3.21 | Network throughput degradation depending on the which stage            |   |

|      | the fault is located at for several networks                           | 9 |

| 3.22 | Network throughput degradation for 4 faults and multiple ex-           |   |

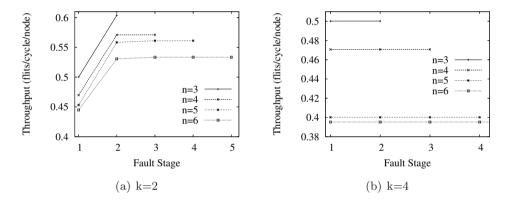

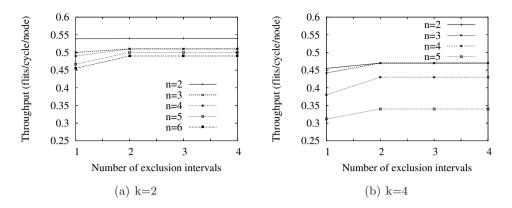

|      | clusion intervals                                                      | 1 |

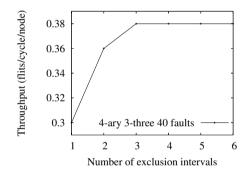

| 3.23 | Network throughput degradation for multiple exclusion inter-           |   |

|      | vals. 4-ary 3-tree with 40 faults                                      | 1 |

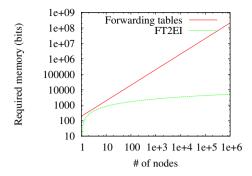

| 3.24 | Memory requirements per switch for a routing scheme based on           |   |

|      | forwarding tables and one based on $FT^2EI$ with 2 exclusion           |   |

|      | intervals in a network with $k = 32. \dots 113$                        | 3 |

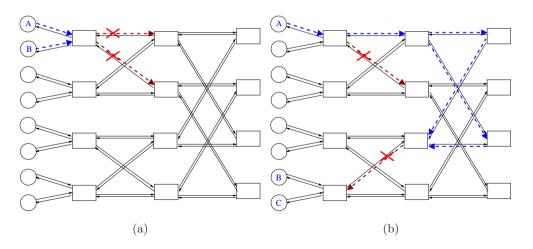

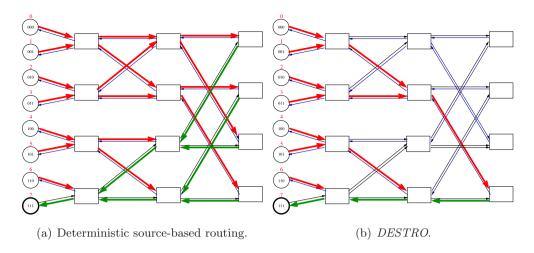

| 4.1  | Step-by-step example of two consecutive packets that follow different paths in a fat-tree with adaptive routing |

|------|-----------------------------------------------------------------------------------------------------------------|

| 4.2  | Step-by-step example of two consecutive packets that preserve                                                   |

| 7.2  | their order despite the network conditions with deterministic                                                   |

|      | routing                                                                                                         |

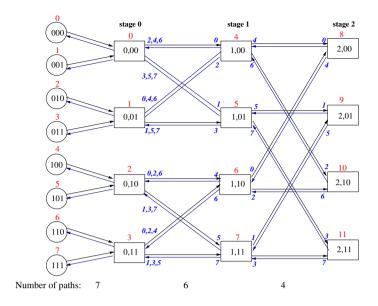

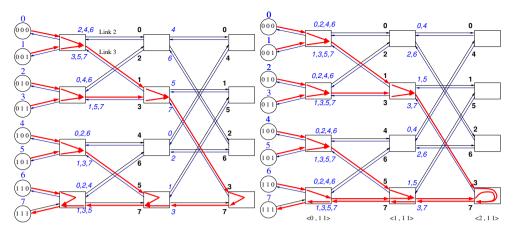

| 4.3  | The different adaptive routes from node 0 to node 7 in a 2-ary                                                  |

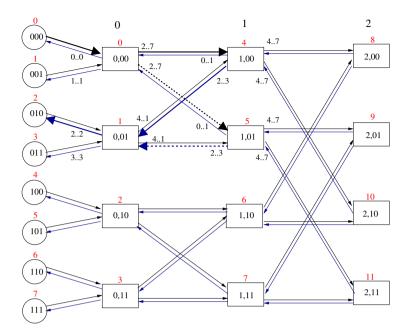

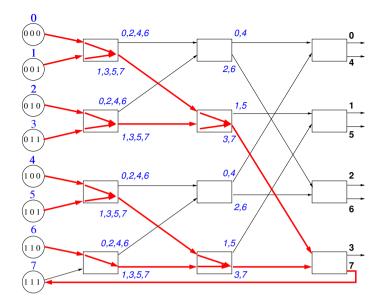

| 4.0  | 3-tree highlighted in different colors                                                                          |

| 4.4  | Two possible groupings of destinations for deterministic routing. 125                                           |

| 4.5  | Reachable destinations through each output port in a 2-ary 3-                                                   |

| 1.0  | tree with our proposal                                                                                          |

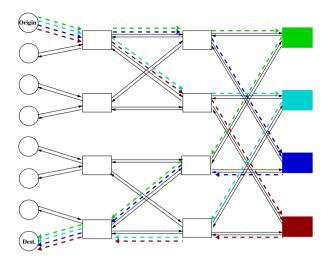

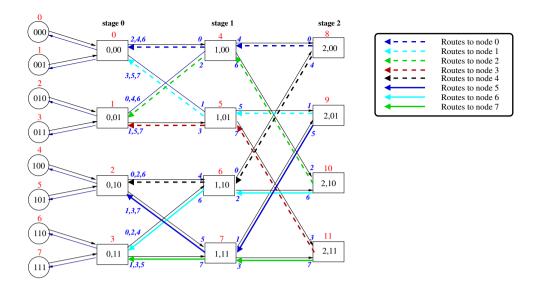

| 4.6  | DESTRO downwards routing paths for each destination are                                                         |

| 1.0  | highlighted in different colors in a 2-ary 3-tree                                                               |

| 4.7  | Routes from all the source nodes to destination node 7 in source-                                               |

| 1.1  | based routing and DESTRO                                                                                        |

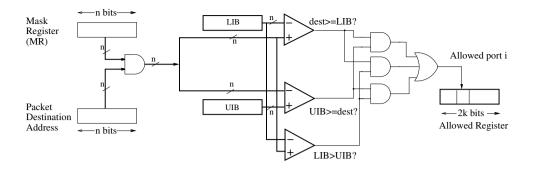

| 4.8  | FIR hardware associated to each output port for masking the                                                     |

| 1.0  | direction address of the packet and comparing it with the rout-                                                 |

|      | ing interval                                                                                                    |

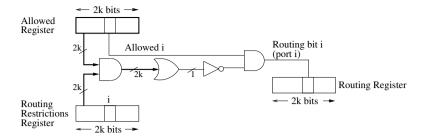

| 4.9  | FIR hardware associated to each output port to prioritize out-                                                  |

|      | put ports                                                                                                       |

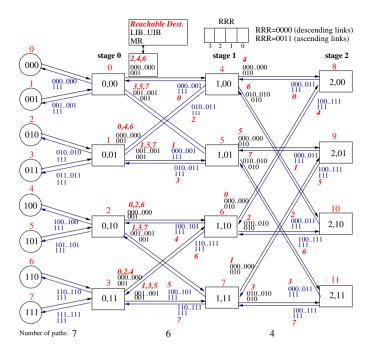

| 4.10 | DESTRO routing in a 2-ary 3-tree with FIR registers 134                                                         |

|      | Register configuration in the ascending links with deterministic                                                |

| 1,11 | routing                                                                                                         |

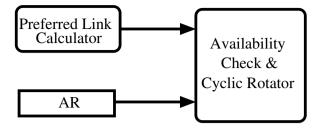

| 4.12 | Basic implementation of a selection function with prioritization. 138                                           |

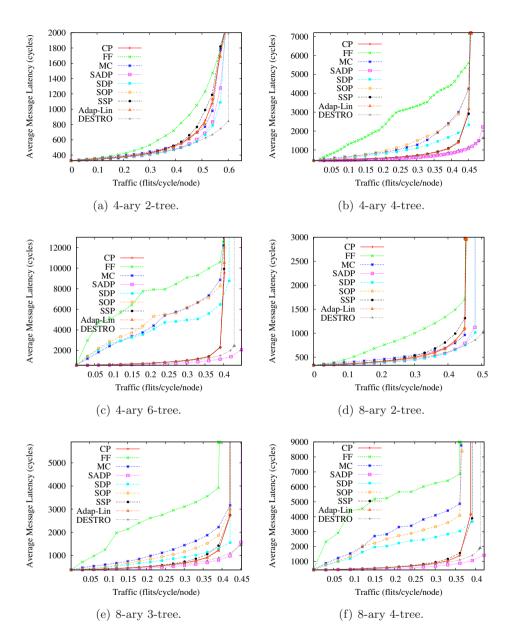

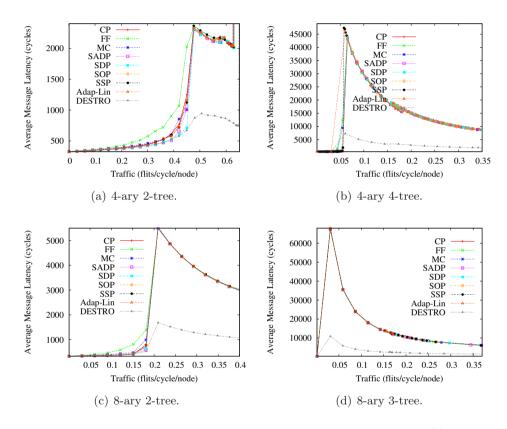

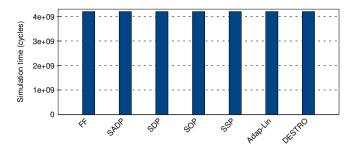

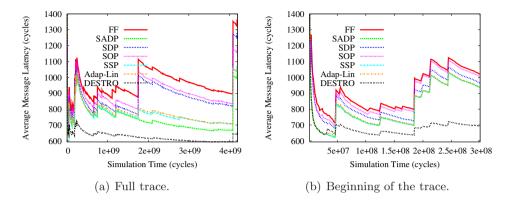

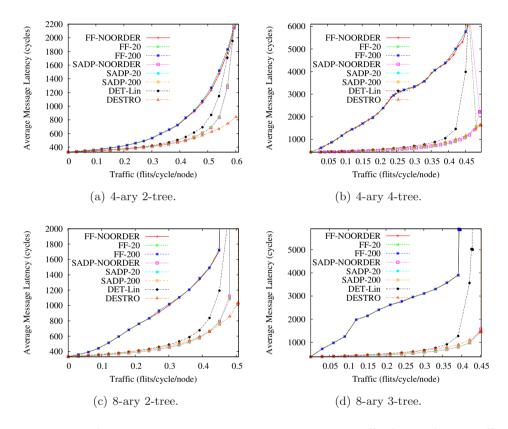

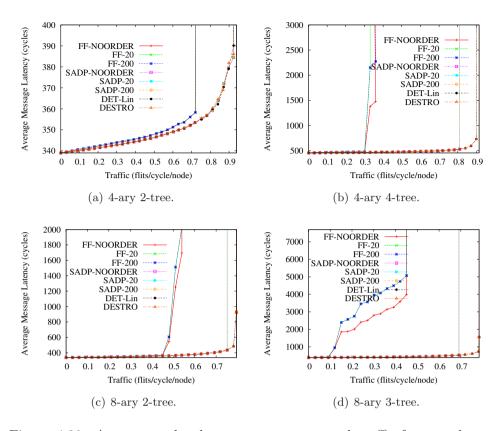

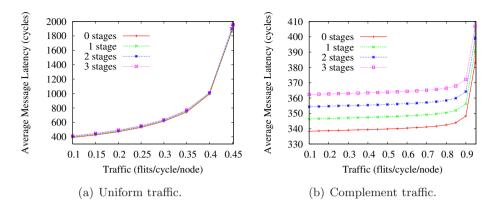

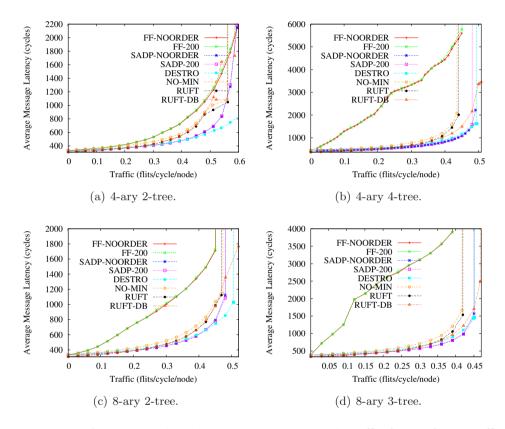

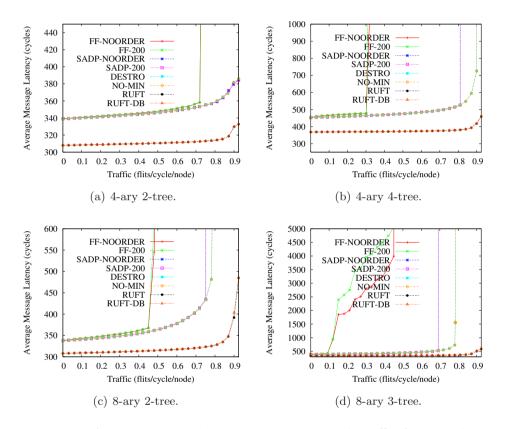

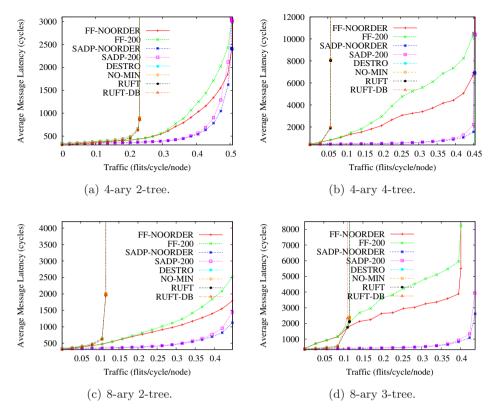

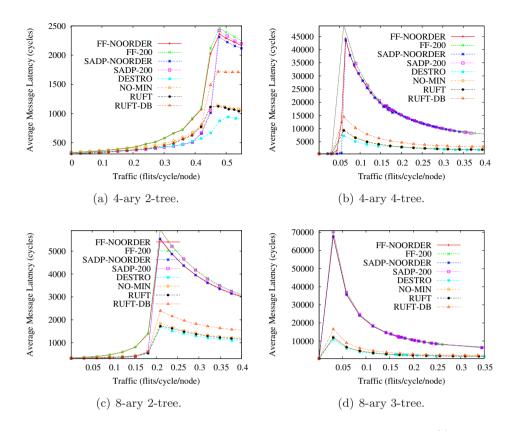

|      | Average packet latency versus accepted traffic for uniform traffic.145                                          |

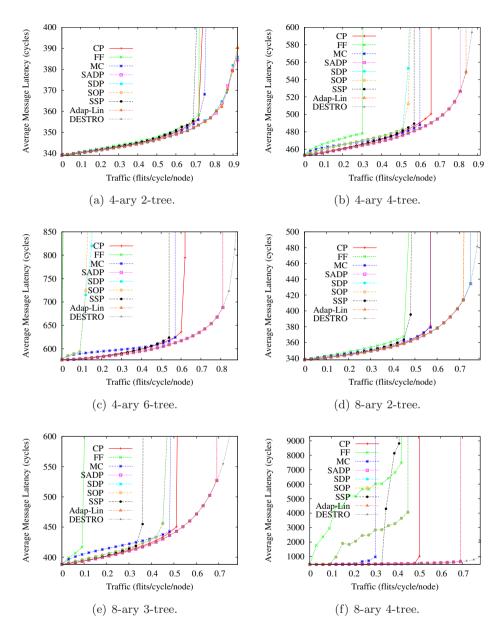

|      | Average packet latency versus accepted traffic for complement                                                   |

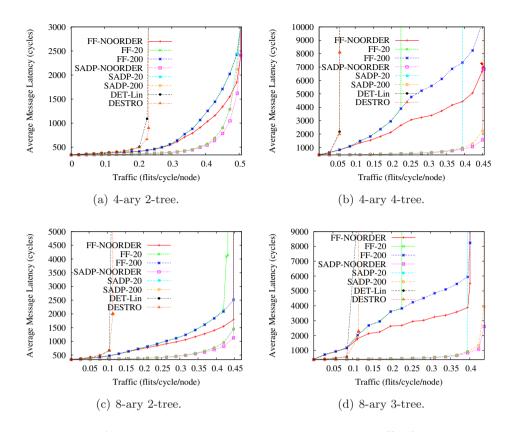

| 1.11 | traffic                                                                                                         |

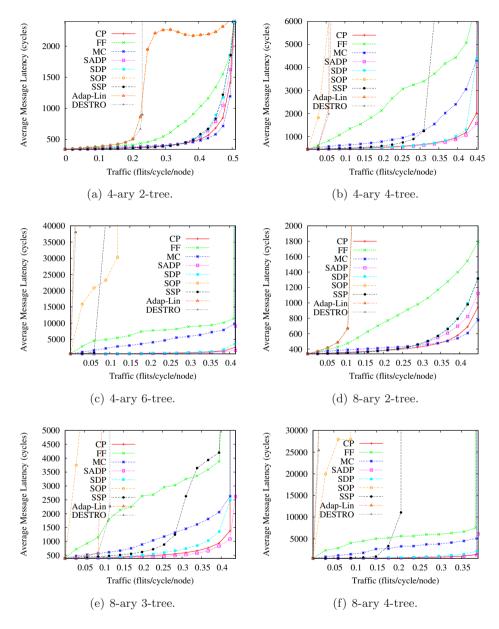

| 4 15 | Average packet latency versus accepted traffic for bit reversal                                                 |

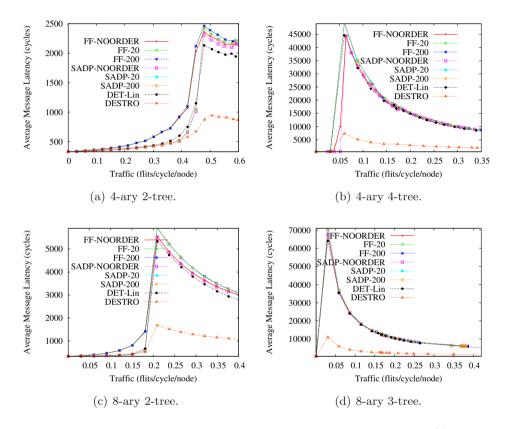

| 1.10 | traffic                                                                                                         |