Document downloaded from:

http://hdl.handle.net/10251/102096

This paper must be cited as:

The final publication is available at http://doi.org/10.1049/el.2017.1240

Copyright Institution of Electrical Engineers

Additional Information

## A New Decoupled Empty Substrate Integrated Waveguide Realization

Juan R. Sánchez, Carmen Bachiller, Héctor Esteban, Ángel Belenguer, Vicente Nova and Vicente Boria

This work presents a novel Decoupled Empty Substrate Integrated Waveguide (DESIW), which enables AC/DC decoupling in any device that is integrated in it. The decoupling strategy is performed throughout a micro-milling square pattern of easy implementation that increases the insertion losses compared to the standard ESIW. However, the DESIW related losses are still tolerable, allowing the employment of the new periodic structure in many practical applications. In particular, it can be used for the design and manufacturing of reconfigurable devices which need a bias voltage on the whole device, or just on some of its particular areas. A broadband transition from DESIW to microstrip planar lines has been also successfully designed. The new line has been manufactured and measured.

*Introduction:* The use of Substrate Integrated Waveguides (SIWs) has become common in many high frequency applications [1]. The main reasons are their high performance in terms of quality factor, and the ease of integration and manufacturing of devices made in that technology. The SIW technology has appeared in response to the emerging problem of integration of planar and non-planar circuits for high-frequency applications, since it allows the integration of waveguides on the same dielectric substrate used for the synthesis of planar transmission lines and circuits. The advantage of this scheme is clear: the whole circuit (planar circuits, transitions and waveguides) can be implemented by standard PCB techniques, as well as by any other standard planar manufacturing process.

Although performance is better in terms of quality factor than other planar circuits, SIW is not yet comparable with waveguide technology. In order to approach to the quality factor of the waveguide, different lines of work are being established in order to remove the dielectric substrate, that provides significant losses. One of these strategies is based on the new Empty SIW (ESIW) transmission line [2], consisting in emptying, metallizing, and covering a planar substrate with a top and bottom metal cover. The structure is completed with a specific broadband transition from a microstrip line.

The need for reconfigurable devices has also led to different strategies. Many of them include the possibility of introducing a DC bias voltage in the device, acting on an additional element that is capable of modifying its response.

Obviously, this involves that the structure must be composed of more than one single conductor. This is not the case of a waveguide structure, which is completely closed on itself with a single conductor. The decoupling of waveguides has been tried in several ways. For example the Corrugated SIW (CSIW) [3] is a simple structure which provides similar results to the standard SIW case. Nevertheless both are supported on a dielectric substrate, thus having similar levels of insertion losses. In this letter, we propose DESIW as a potential alternative to all previous solutions.

Decoupled Empty Substrate Integrated Waveguide: The Empty Substrate Integrated Waveguide is a transmission line integrated in a planar substrate. The basic idea is to develop the line into three different layers, two of them are the top and bottom covers of the line, and the other is the body of the transmission line. The top and bottom covers are just two metallic layers with some holes for fastening screws, moreover the covers are welded to the body of the line in order to ensure electric continuity. The body of the line contains the microstrip line that can integrate the ESIW to any substrate based circuit, the Empty SIW itself and the transition between microstrip and ESIW. The body of the ESIW is performed by milling a PCB substrate and metallizing the side walls galvanically. The resultant structure is a waveguide of very low height, perfectly integrated in a substrate circuit and having better performance in terms of dispersion and losses than microstrip, coplanar lines and traditional SIWs.

The ESIW is a single conductor structure, i.e. a closed non dispersive transmission line, which has obvious advantages but also one disadvantage: this structure is not AC/DC decoupled, thus it can not be used to integrate elements that need a bias voltage to be operated. These

elements are of great practical interest, since they can provide a certain reconfiguration range to the devices that are built using them.

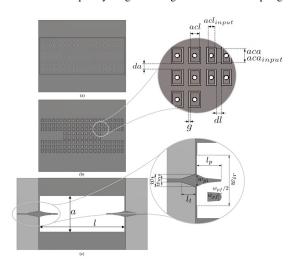

This work proposes a modification of ESIW transmission line in order to make it decoupled. The basic idea is to maintain the three layers line, but milling a pattern on the surface of the top cover to separate the electric conductor.

For the fundamental mode of the waveguide, the RF electric field currents flow inside the structure. If DC decoupling is pursued, the continuity of these high frequency surface currents should be granted.

To avoid cutting the currents and inducing radiation, a new structure with the top cover divided in several isolated metal squares is designed. Thus, RF currents can flow through the grid created between the squares, preventing interruption by the discontinuity as shown in Fig. 1. This structure, also called frequency selective surface [4], enables the transmission in a frequency range assuring the AC/DC decoupling.

**Fig. 1** *Layout of an ESIW with the top cover cut in small squares. (a) Top view of the top cover. (b) Bottom view of the top cover with detail of the squares. (c) Top view of the central body with detail of the transition.*

The voltage difference can be applied between each small inner square and the rest of the structure. It is expected that this solution, even considering some low radiation losses, has a proper performance. In order to have access to the decoupled conductors from outside the structure, it is needed to drill a set of conducting vias in the center of each square, between the lower and upper sides of the top cover of the DESIW. In this way the bias voltage can be applied to the surface of the waveguide. Moreover different bias voltages could be applied to different sections of the waveguide, since the squares are accessible separately.

| <b>Table 1:</b> Dimensions of the DESIW transmission line. |

|------------------------------------------------------------|

|------------------------------------------------------------|

| Line Paramaters | Dimmension (mm) | Transition Paramaters | Dimmension (mm) |

|-----------------|-----------------|-----------------------|-----------------|

| a               | 19.050          | w <sub>ms</sub>       | 3.300           |

| l               | 58.475          | $w_t$                 | 5.000           |

| g               | 0.150           | $l_t$                 | 4.702           |

| aca             | 1.335           | wir                   | 9.320           |

| acainput        | 1.335           | wpi                   | 7.056           |

| acl             | 1.068           | $l_p$                 | 9.080           |

| aclinput        | 1.260           | w <sub>pf</sub>       | 0.500           |

| da              | 0.950           |                       |                 |

| dl              | 0.700           |                       |                 |

*Results of the transmission line:* An X-band DESIW transmission line has been designed and manufactured. The dimensions of squares patches were optimized to maximize return losses and are specified in Table 1. A two step microstrip to ESIW transition, as the one described in [5], has been used. The geometrical dimensions have been optimized for maximizing return losses. The optimum values are shown in Table 1.

The body of the line has been manufactured using Rogers RO4003C substrate with height h = 1.524 mm,  $\epsilon_r = 3.55$  and copper cladding of 17.5  $\mu$ m.

In order to consider the possible influence of the top cover substrate in the structure behaviour, the electromagnetic response of the line was simulated using CST Studio Suite for different substrates: FR4, RO4003C, RO4360G2 and TMM10. These simulations showed that the substrate of the top cover barely influences on the performance of the line. So that, for both (top and bottom) covers of the line, a Rogers RO4003C substrate with height h =0.813 mm,  $\epsilon_r$  =3.55 and copper cladding of 17.5  $\mu$ m has been finally chosen.

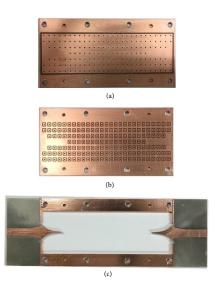

The first stage of the manufacturing procedure is related to the DESIW body: the substrate is partially emptied to conform the line and its sides are covered with copper by electrodeposition, then the transition is milled. Next, the top cover is manufactured: the vias that connect the inner squares to the outside of the cover are drilled and electrodeposited with copper. Then the inner squares are milled, as well as the decoupling big square of the upper side. The bottom cover acts just as a whole copper foil. The structure is welded to ensure electric continuity and it is fastened by screws. Fig. 2 shows the structure separately.

A TRL calibration kit (thru, line and short) for this line was developed and manufactured for the measurement of DESIW parameters, thus removing the additional losses introduced by the microstrip lines and involved transitions.

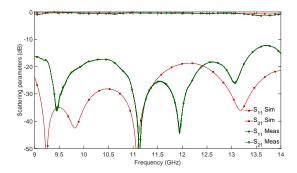

The response of the new DESIW is compared in Fig. 3 with the simulated data obtained with CST Studio Suite. As it can be observed, simulation and measurement are in good agreement. A comparison between DESIW results and previous works in the field is provided in Table 2.

Moreover the transmission parameters are presented in Fig. 4, which shows the good agreement between the simulation and the measurement, furthermore the low attenuation of the line ensures a good performance of this structure for different applications.

Table 2: Comparison of scattering parameters between DESIW and other SIWs.

|               | AC/DC decoupled | Return Losses | Insertion Losses |

|---------------|-----------------|---------------|------------------|

| DESIW         | Yes             | 15 dB         | 0.5 dB           |

| ESIW [5]      | No              | 20 dB         | 0.3 dB           |

| CSIW [3]      | Yes             | 10 dB         | 3.5 dB           |

| SBFSS-SIW [6] | Yes             | 12 dB         | 1 dB             |

**Fig. 2** *Manufactured DESIW line. (a) Top view of the top cover. (b) Bottom view of the top cover. (c) Top view of the body of the line.*

*Conclusion:* A novel DESIW has been designed and manufactured. Its good performance in the monomode range assures its usage for the design of several devices that require to apply a bias voltage to the whole line or to some parts of it.

The scattering and the transmission parameters have been studied, concluding that the line is highly competitive when compared to recently published alternative solutions.

*Acknowledgment:* This work was partially founded by the Generalitat Valenciana research project PROMETEOII/2015/005, by the Ministerio de Educación, Cultura y Deporte (Spain) under the Fellowship Program for Training University Professors FPU14/00150 and by Ministerio de Economía y Competitividad (Spain) under R&D project TEC2016-75934-C4-R.

Fig. 3 Comparison between simulation (CST Studio Suite) and measurement results for the DESIW line.

(b) Attenuation of the line (Np/m)

Fig. 4 Comparison between simulation (CST Studio Suite) and measurement results for transmission parameters of the DESIW line.

Juan R. Sánchez, Carmen Bachiller, Héctor Esteban, Ángel Belenguer, Vicente Nova and Vicente Boria (*Instituto de Telecomunicaciones y Aplicaciones Multimedia*. Universitat Politècnica de València. Spain) E-mail: mabacmar@dcom.upv.es

Ángel Belenguer (Ingeniería Eléctrica, Electrónica, Automática y Comunicaciones, Universidad de Castilla-La Mancha, Spain)

## References

- Deslandes, D. and Wu, K.: 'Integrated microstrip and rectangular waveguide in planar form', *IEEE Microw. Wireless Comp. Letters*, 2001, 11, (2), pp. 68-70

- 2 Belenguer, A., Esteban, H. and Boria, V.: 'Novel Empty Substrate Integrated Waveguide for High Performance Microwave Integrated Circuits', *IEEE Trans. Microw. Theory Techn.*, 2014, **62**, (4), pp. 832-839

- 3 Chen, D. and Eccleston, K.: 'Substrate Integrated Waveguide with Corrugated Wall', Asia Pacific Microwave Conference, 2008, pp. 1-4

- 4 Munk, B.: 'Frequency Selective Surfaces. Theory and Design', John Wiley and Sons, 2000

- 5 Peng, H., Xia, X. Dong, J. and Yang, T.: 'An Improved Broadband Transition between Microstrip and Empty Substrate Integrated Waveguide', *Microwave and Optical Technology Letters*, 2016

- 6 Esparza, N., Alcón, P.,Herrán, L., Las-Heras, F.: 'Substrate Integrated Waveguide Structures using Frequency Selective Surfaces operating in Stop-band', *IEEE Microw. Wireless Comp. Letters*, 2016, 26, (2), pp. 113-115