#### Universitat Politècnica de València Departamento de Informática de Sistemas y Computadores

# Design Space Exploration for Networks On-chip

A DISSERTATION SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY (COMPUTER SCIENCES)

Author

Francisco Gilabert Villamón

Advisors

María Engracia Gómez Requena Davide Bertozzi

Valencia, 2011

## Acknowledgments

It is a pleasure to thank the many people who made this thesis possible.

First and foremost, I thank my family for their unending support. I would like to thank Merlyx (my wife) for giving the most important step of my entire life with me: starting our own family. Also, I would like to thank her for her patience during the months I spent out of home in stays and conferences. I would like to thank my parents and my sister for all the help they have provided to me.

In second place, I would like to thank my friends, for their support and company. Mainly, I would like to thank Cris, Blas, Ricardo and Simone. Cris is the closest friend I ever had, and we spent most of our free time together playing computer games, watching movies or just talking. Also, we have traveled around the world together, and we shared several moments that I will never forget. I would like to thank Blas for the great moments spend playing football, as well as for the great meals we shared together with Ricardo in our preferred restaurant. Finally, I would like to thank Simone for his help during my stays on Italy.

I am indebted to my advisors, Davide Bertozzi and María Engracia, for their enthusiasm, their inspiration, and their sound advices, as well as for the encouragement they provided to me. I would have been lost without them. I would like to thank Davide Bertozzi for being such an amazing host during my stays in Italy. Also, I would like to thank Prof. José Duato for including me in his Parallel Architecture Group: a big family composed by good professionals and excellent persons. I would like to thanks Pedro López, I will always remember his help and understanding during my first steps into the research world. Many of the other faculty members in the Parallel Architecture

Group did help me too, either professionally or personally, thanks to you all. Finally, I would like to thanks Sören Sonntag for showing their advices and their guidance during my stay at Lantiq.

I have met many students and professionals from around the world along the years, either in the lab, or during my trips and stays. Although I cannot possibly mention everyone who has enriched my experience or provided moral support, I wish to specifically thank a few individuals: Cris, Simone, Ricardo, Daniele, Gaspar, Carles, Blas, Héctor and Knut. All of them have helped me at any point on my research and on my personal life, and I would like to thanks them for it.

## Contents

| A            | cknov    | wledgn     | nents                                                | iii  |

|--------------|----------|------------|------------------------------------------------------|------|

| A            | Abstract |            |                                                      |      |

| $\mathbf{R}$ | esum     | en         |                                                      | xix  |

| $\mathbf{R}$ | esum     | L          | X                                                    | xiii |

| 1            | Intr     | troduction |                                                      |      |

|              | 1.1      | Motiva     | ation                                                | 1    |

|              | 1.2      | Object     | tives                                                | 4    |

|              | 1.3      | Disser     | tation outline                                       | 7    |

| 2            | Bac      | kgrour     | nd and State of the art                              | 9    |

|              | 2.1      | Netwo      | rks on-Chip                                          | 10   |

|              |          | 2.1.1      | Systems on-Chip                                      | 11   |

|              |          | 2.1.2      | Shared bus                                           | 14   |

|              |          | 2.1.3      | A new design paradigm                                | 16   |

|              |          | 2.1.4      | Networks on-Chip components                          | 17   |

|              |          | 2.1.5      | Topology                                             | 31   |

|              |          | 2.1.6      | Virtual Channels                                     | 33   |

|              |          | 2.1.7      | Networks on-Chip performance evaluation              | 35   |

|              |          | 2.1.8      | Networks on-Chip physical synthesis evaluation       | 35   |

|              |          | 2.1.9      | Reference architecture                               | 36   |

|              |          | 2.1.10     | Design challenges for Networks on-Chip architectures | 41   |

|              | 2.2      | State      | of the Art                                           | 44   |

vi

| 3 | Top | ology  | exploration for Networks On-Chip                              | 51  |

|---|-----|--------|---------------------------------------------------------------|-----|

|   | 3.1 | Introd | luction                                                       | 51  |

|   | 3.2 | The h  | igh level view                                                | 53  |

|   |     | 3.2.1  | High level topology properties                                | 53  |

|   |     | 3.2.2  | Topologies for Networks on-Chip                               | 57  |

|   |     | 3.2.3  | High level topology exploration                               | 70  |

|   | 3.3 | Netwo  | orks on-Chip modelling                                        | 74  |

|   |     | 3.3.1  | Networks on-Chip behavior abstraction                         | 75  |

|   |     | 3.3.2  | Network traffic generation                                    | 76  |

|   |     | 3.3.3  | Validation of Transaction-Level simulator accuracy            | 77  |

|   |     | 3.3.4  | Case study: Parametrical exploration                          | 81  |

|   | 3.4 | Physic | cal design pitfalls                                           | 92  |

|   | 3.5 | Case s | study: 16-tiles systems                                       | 96  |

|   |     | 3.5.1  | Total wire length                                             | 97  |

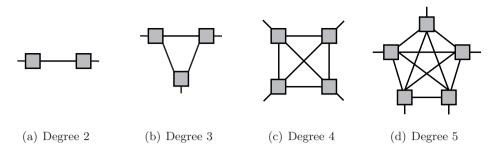

|   |     | 3.5.2  | Switch degree                                                 | 100 |

|   |     | 3.5.3  | Link length                                                   | 101 |

|   |     | 3.5.4  | Link performance boosting                                     | 102 |

|   | 3.6 | Case s | study: 64-tiles topologies                                    | 110 |

|   |     | 3.6.1  | Characterization methodology                                  | 111 |

|   |     | 3.6.2  | Physical implementation                                       | 113 |

|   |     | 3.6.3  | Pipeline stage insertion for 64-tiles systems                 | 115 |

|   |     | 3.6.4  | The performance prediction gap                                | 117 |

|   | 3.7 | Case s | study: assessing Multi-stage Interconnection Networks $\ .$ . | 121 |

|   |     | 3.7.1  | Topologies under test                                         | 121 |

|   |     | 3.7.2  | Floorplanning                                                 | 126 |

|   |     | 3.7.3  | Physical evaluation                                           | 129 |

|   |     | 3.7.4  | Performance evaluation                                        | 132 |

|   | 3.8 | Concl  | usions                                                        | 134 |

| 4 | Vir | tual C | hannels for Networks On-Chip                                  | 137 |

|   | 4.1 | Introd | luction                                                       | 138 |

|   | 4.2 | Classi | cal virtual channel design                                    | 140 |

|   |     | 4.2.1  | Classical virtual channel switch architecture                 | 140 |

|   |     | 4.2.2  | Conventional multi-stage virtual channel switch               | 142 |

Contents

|   | 4.3    | Bringing virtual channels to Networks On-Chip |

|---|--------|-----------------------------------------------|

|   |        | 4.3.1 Motivation                              |

|   |        | 4.3.2 Proposed multi-switch implementation    |

|   |        | 4.3.3 Full network replication                |

|   | 4.4    | Architecture comparison                       |

|   |        | 4.4.1 Physical synthesis                      |

|   |        | 4.4.2 Performance comparison                  |

|   | 4.5    | Conclusions                                   |

| 5 | Des    | gn Space Exploration for Networks On-Chip 16  |

|   | 5.1    | Introduction                                  |

|   | 5.2    | The industry point of view                    |

|   |        | 5.2.1 Network architecture                    |

|   |        | 5.2.2 Target domain                           |

|   |        | 5.2.3 Traffic characterization                |

|   |        | 5.2.4 Core placement strategies               |

|   |        | 5.2.5 Full custom design                      |

|   |        | 5.2.6 Simulation framework                    |

|   |        | 5.2.7 NaNoC compatibility                     |

|   | 5.3    | LDSET                                         |

|   |        | 5.3.1 LDSET NoC simulator framework 17        |

|   |        | 5.3.2 Design space definition                 |

|   |        | 5.3.3 Design space initialization             |

|   |        | 5.3.4 Design space exploration                |

|   |        | 5.3.5 Output generation                       |

|   |        | 5.3.6 Example                                 |

|   | 5.4    | Place & Route                                 |

|   | 5.5    | Conlucions                                    |

| 6 | Cor    | clusions 19                                   |

|   | 6.1    | Conclusions                                   |

|   | 6.2    | Future Work                                   |

|   | 6.3    | Contributions                                 |

| B | iblioc | ranhy 20                                      |

viii Contents

# List of Figures

| 2.1  | Example of a System on-Chip: CW4512                            | 12 |

|------|----------------------------------------------------------------|----|

| 2.2  | Schema of a shared bus                                         | 14 |

| 2.3  | Schema of a Network on-Chip                                    | 16 |

| 2.4  | Schema of a Network Interface                                  | 18 |

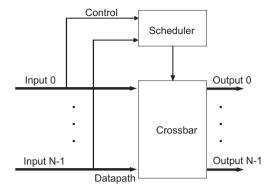

| 2.5  | Schema of a Network on-Chip switch                             | 20 |

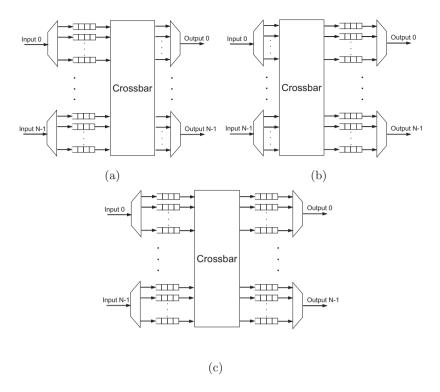

| 2.6  | Switch architecture by buffer allocation: (a) Input queued (b) |    |

|      | Output queued (c) Input/Output queued                          | 22 |

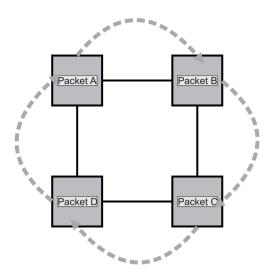

| 2.7  | Example of a deadlock of 4 packets in a mesh topology          | 25 |

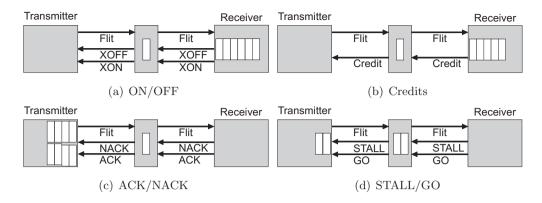

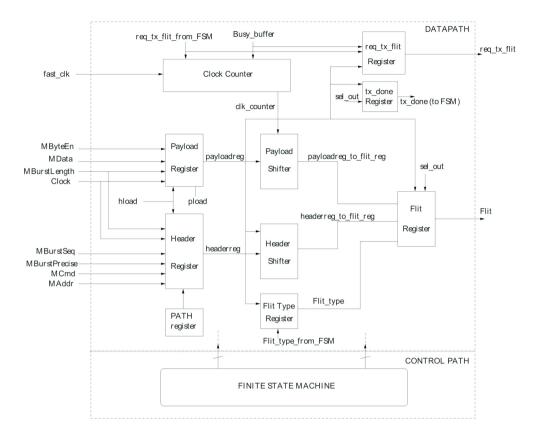

| 2.8  | Flow control mechanisms for a link with 2 cycles of latency    | 30 |

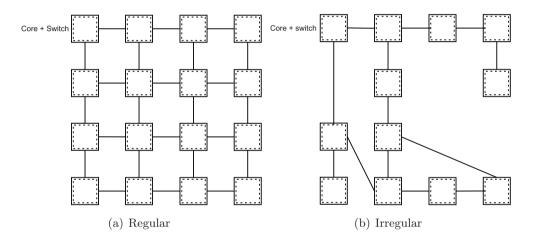

| 2.9  | Example of direct topologies                                   | 30 |

| 2.10 | Example of indirect topologies                                 | 31 |

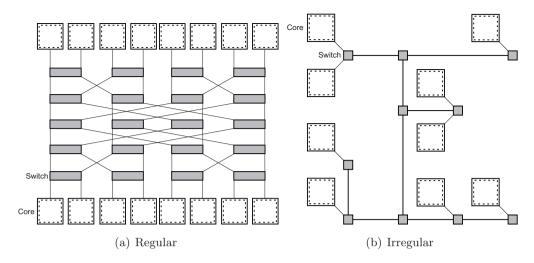

| 2.11 | Head-of-Line blocking                                          | 33 |

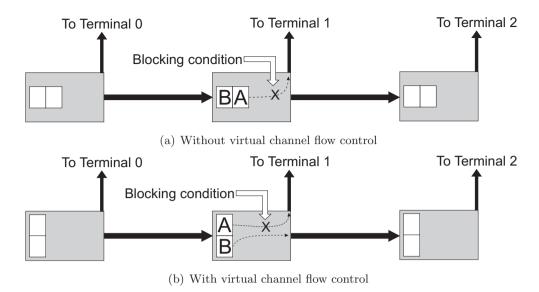

| 2.12 | Xpipes Lite network interface initiator architecture           | 37 |

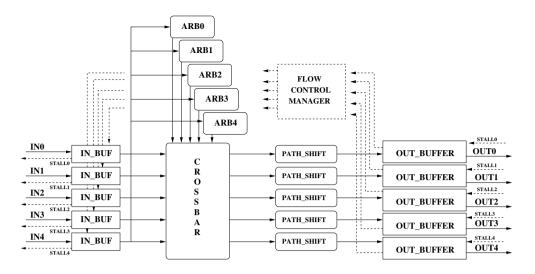

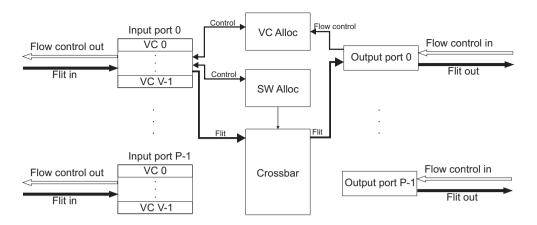

| 2.13 | Xpipes Lite switch architecture                                | 39 |

| 2.14 | Area and power breakdown                                       | 40 |

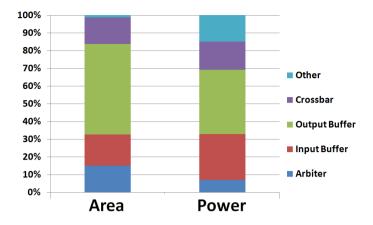

| 3.1  | Example of symmetric and non-symmetric topologies              | 53 |

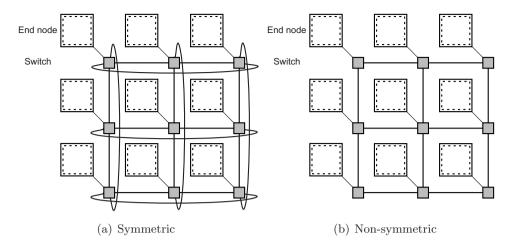

| 3.2  | Examples of topology bisection bandwidth                       | 55 |

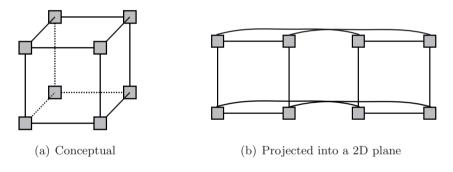

| 3.3  | Representations of a 3-hypercube                               | 55 |

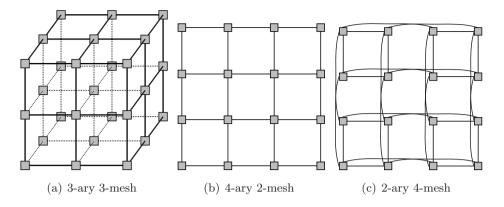

| 3.4  | Switch distribution of several mesh configurations             | 59 |

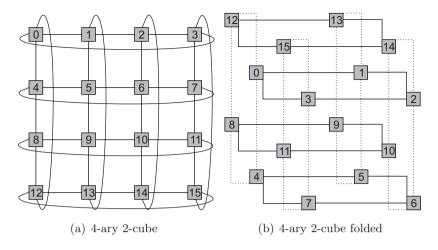

| 3.5  | Switch distribution of several torus configurations            | 60 |

| 3.6  | Switch distribution in WK-Recursive first level virtual nodes  | 62 |

| 3.7  | Switch distribution of several WK-Recursive configurations     | 63 |

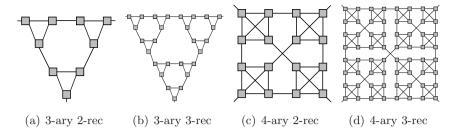

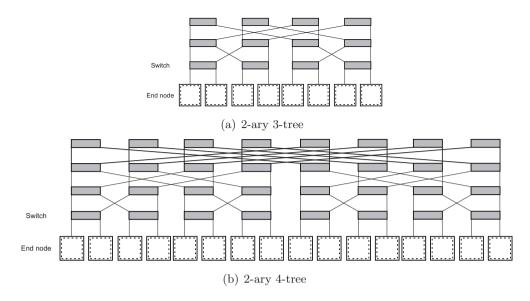

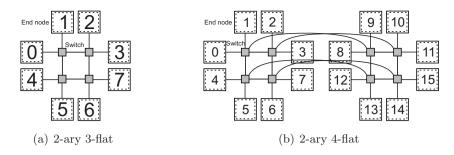

| 3.8  | Examples of fat-tree configurations                            | 64 |

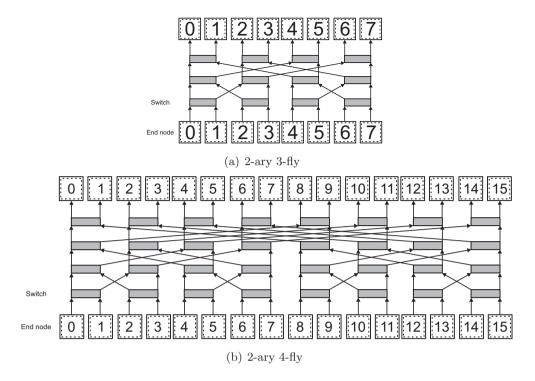

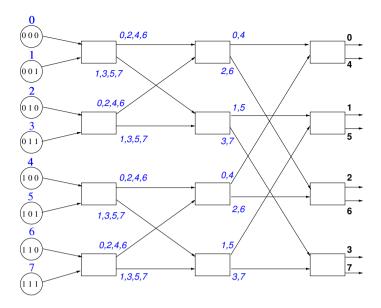

| 3.9  | Examples of butterfly configurations                           | 65 |

x List of Figures

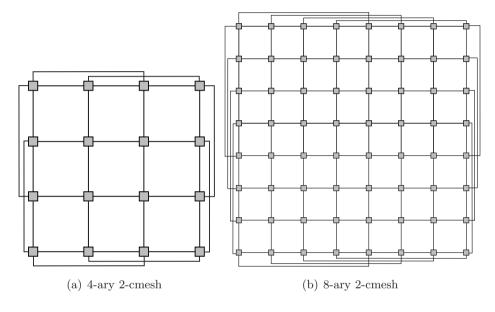

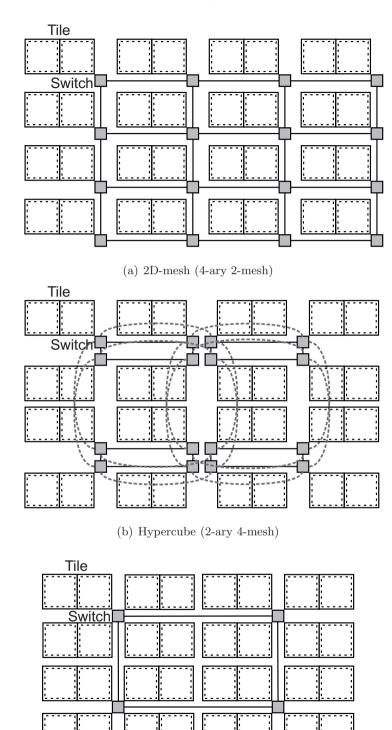

| 3.10 | Switch distribution of several C-Mesh configurations 67                   |

|------|---------------------------------------------------------------------------|

| 3.11 | Examples of flattened butterfly configurations 69                         |

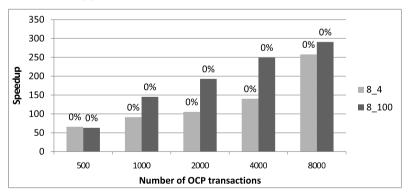

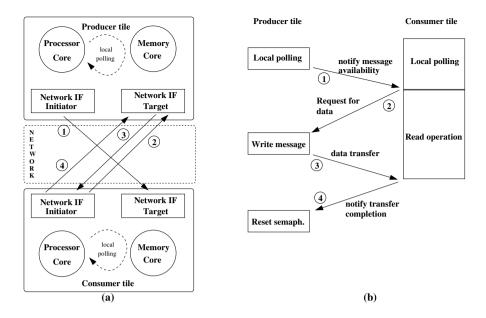

| 3.12 | Experimental setup                                                        |

| 3.13 | Experimental setup results                                                |

| 3.14 | Tile abstraction and mapping of producer-consumer communi-                |

|      | cation handshake on network transactions                                  |

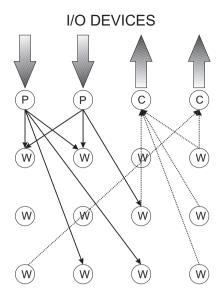

| 3.15 | System organization and workload distribution                             |

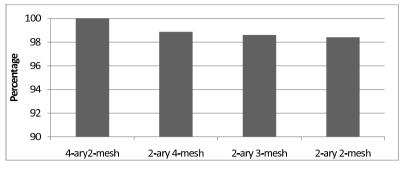

| 3.16 | Performance comparison (in execution cycles) of topologies $87$           |

| 3.17 | Implementation space: 4-ary 2-mesh vs 2-ary 4-mesh 89                     |

| 3.18 | Floorplanning directives for a 2-ary 2-mesh with 4 tiles per switch. $90$ |

| 3.19 | Implementation space: 4-ary 2-mesh vs concentrated 2-ary 2-               |

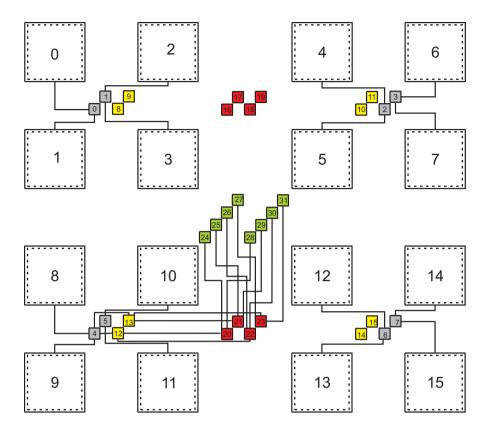

| 2.00 | mesh                                                                      |

|      | High-level sketch of a 2-ary 4-tree                                       |

| 3.21 | Floorplan of a 2-ary 4-tree. Only the main wiring patterns are reported   |

| 2 22 | 1                                                                         |

|      | Floorplan directives                                                      |

|      | 0                                                                         |

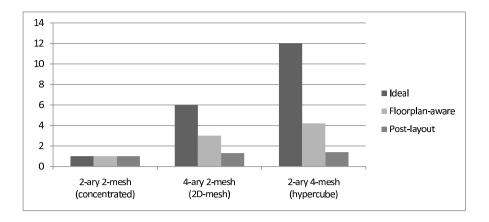

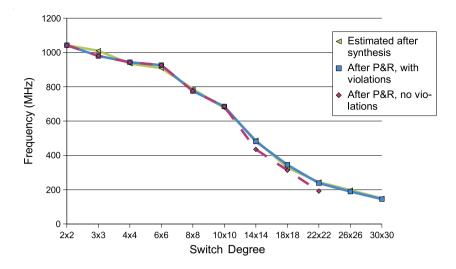

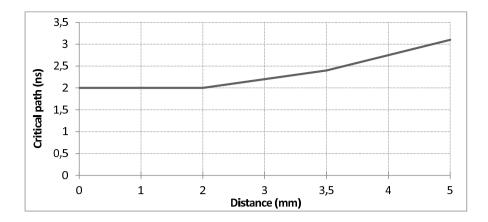

|      | Switch frequency scaling (courtesy of [123])                              |

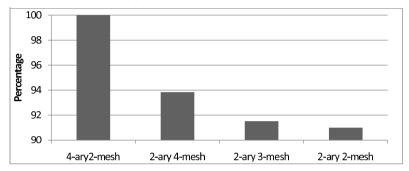

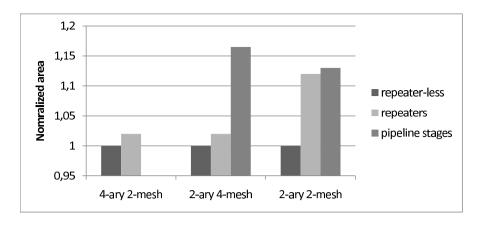

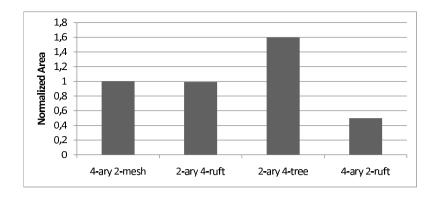

|      | Normalized area                                                           |

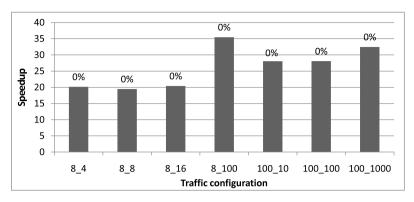

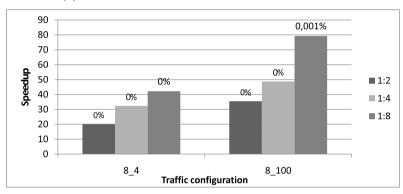

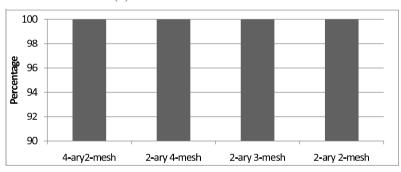

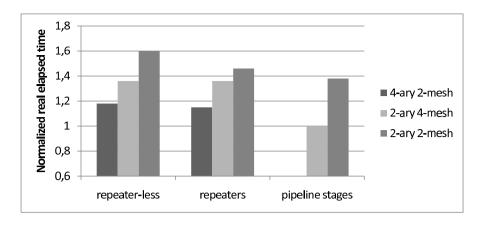

|      | Real elapsed time of topologies under test                                |

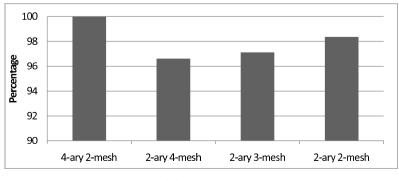

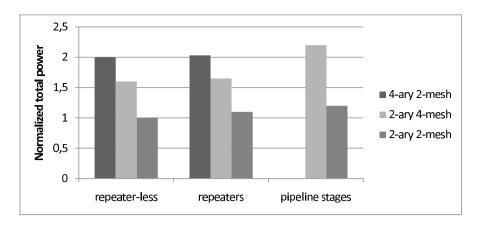

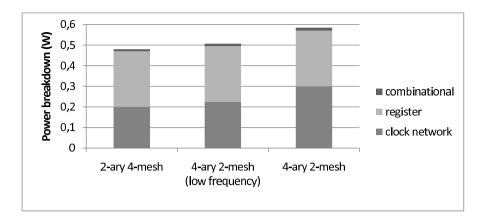

|      | Total power                                                               |

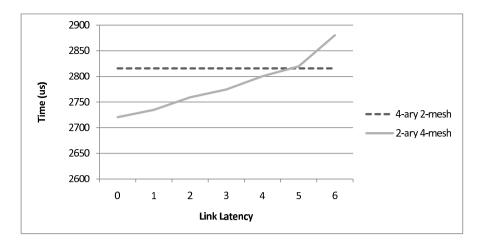

|      | Clock tree power impact                                                   |

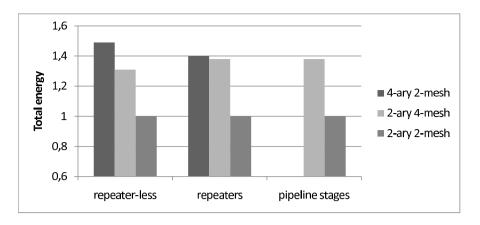

|      | Normalized time, power and energy with link synthesis techniques. 110     |

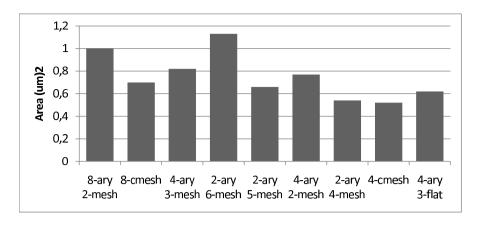

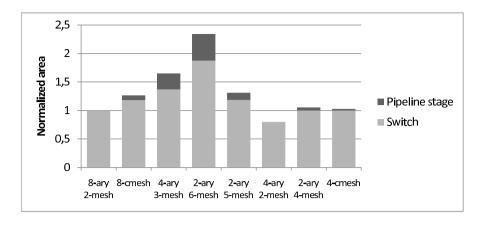

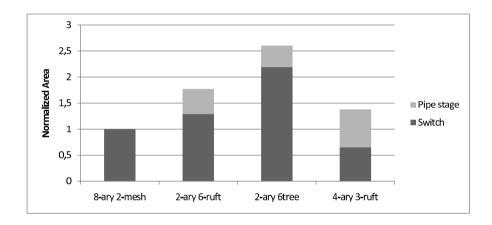

|      | Normalized area for 64-tiles topologies                                   |

|      | Normalized area for 64-cores topologies with pipeline stages              |

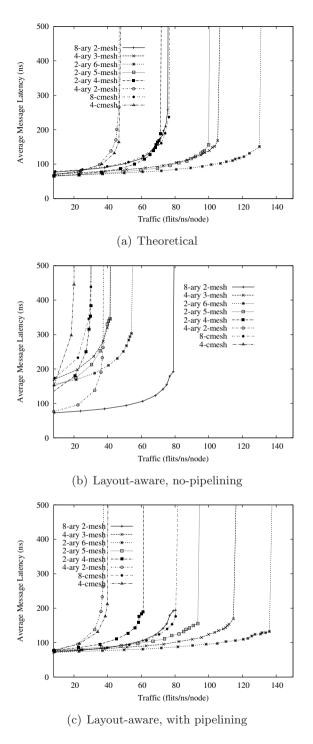

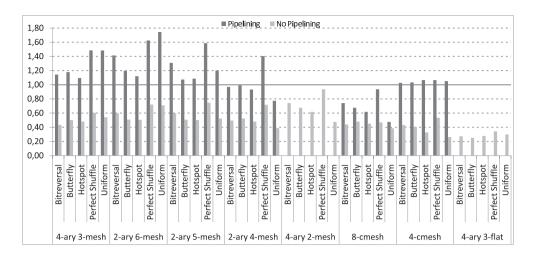

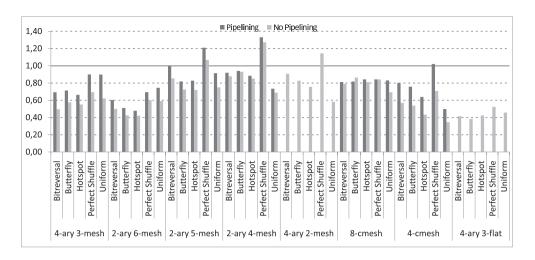

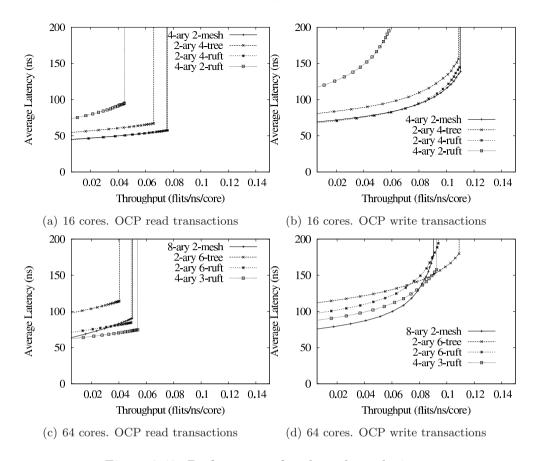

|      | Performance of 64-tiles systems with uniform traffic                      |

|      |                                                                           |

|      | -                                                                         |

|      |                                                                           |

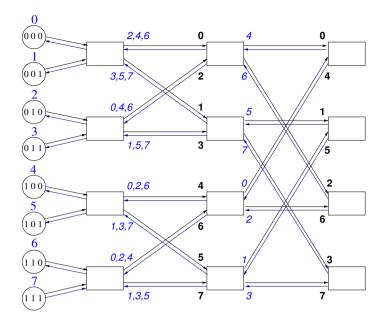

|      | A 2-ary 3-tree topology                                                   |

|      | RUFT derived from a 2-ary 3-tree                                          |

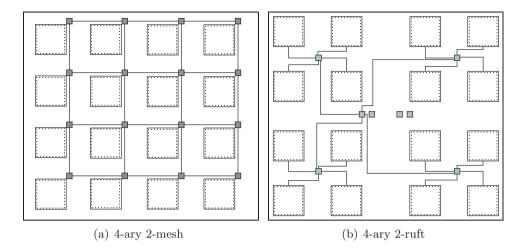

| 5.58 | Floorplans of topologies of 4-ary 2-mesh and 4-ary 2-ruft. Only           |

|      | the main wiring patterns are reported                                     |

List of Figures xi

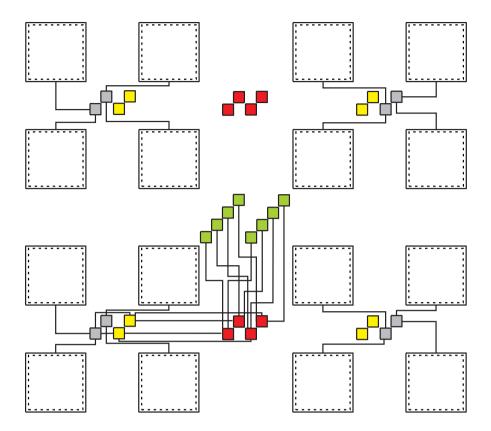

| 3.39 | Floorplan of a 2-ary 4-tree. Only the main wiring patterns are        |

|------|-----------------------------------------------------------------------|

|      | reported                                                              |

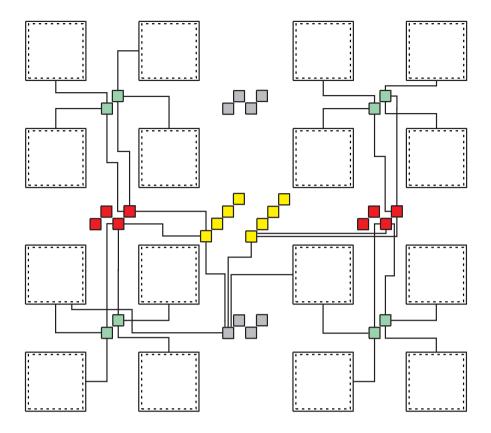

| 3.40 | Floorplan of a 2-ary 4-ruft. Only the main wiring patterns are        |

|      | reported                                                              |

| 3.41 | Normalized area of 16-cores systems                                   |

| 3.42 | Normalized area of 64-cores systems                                   |

| 3.43 | Performance of evaluated topologies                                   |

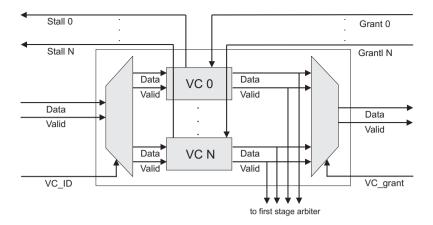

| 4.1  | Schema of a conventional wormhole virtual channel switch ar-          |

|      | chitecture                                                            |

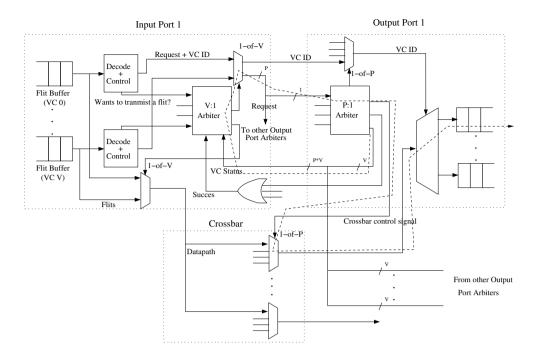

| 4.2  | Input port schematic of the multi-stage virtual channel switch. 142   |

| 4.3  | Detailed control path of the multi-stage virtual channel switch. 143  |

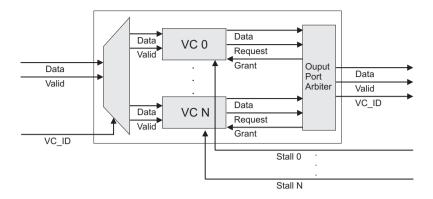

| 4.4  | Output port schematic of the multi-stage virtual channel switch. 144  |

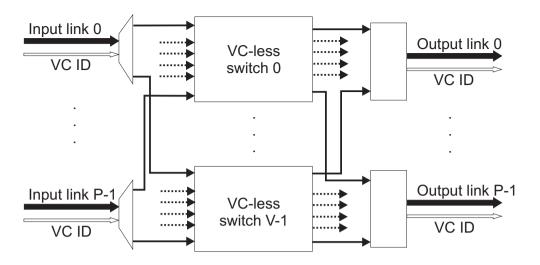

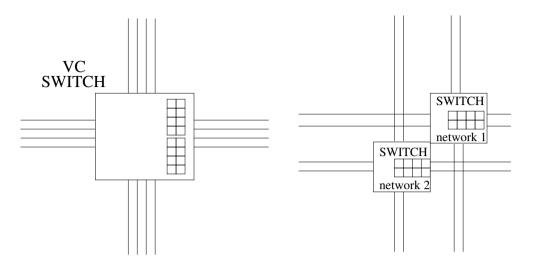

| 4.5  | Multi-switch implementation of a virtual channel switch $147$         |

| 4.6  | Multi-stage virtual channel switch vs multi-network compound          |

|      | switch: aggregate link width and switch buffering are kept con-       |

|      | stant                                                                 |

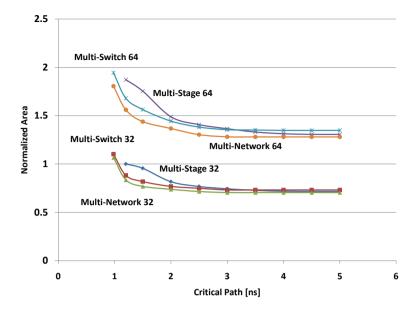

| 4.7  | Area scalability as a function of the target delay constraint. 2      |

|      | virtual channels                                                      |

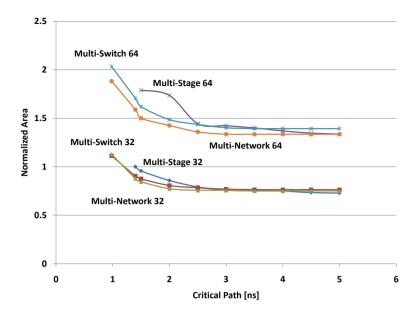

| 4.8  | Area scalability as a function of the target delay constraint. 4      |

|      | virtual channels                                                      |

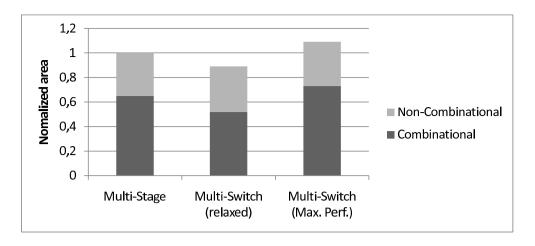

| 4.9  | Area breakdown of 32-bit multi-switch (maximum and relaxed            |

|      | performance) and multi-stage implementations 155                      |

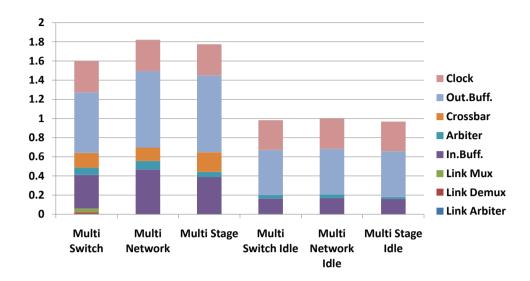

| 4.10 | Power analysis with $50\%$ switching activity and with idleness $156$ |

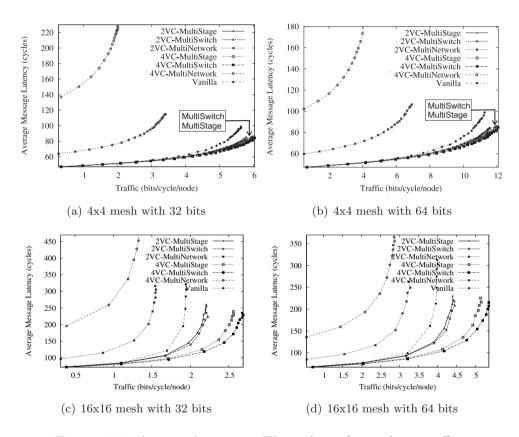

| 4.11 | Average latency vs Throughput for uniform traffic 160                 |

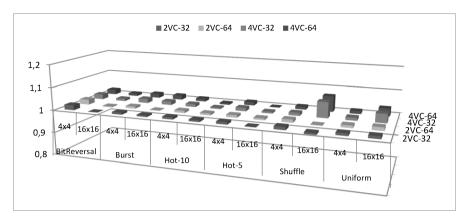

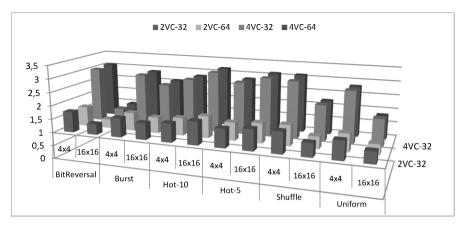

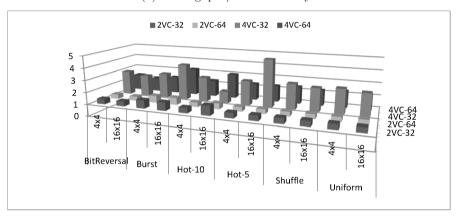

| 4.12 | Multi-switch performance normalized to multi-stage 161                |

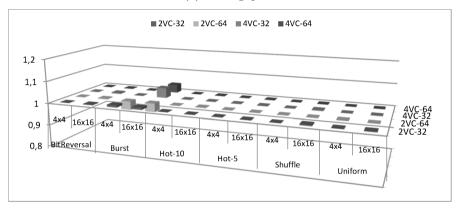

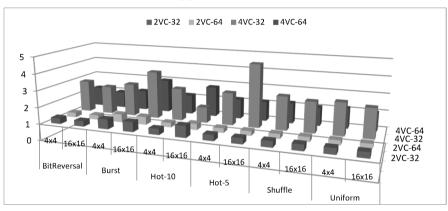

| 4.13 | Multi-switch performance normalized to multi-network 162              |

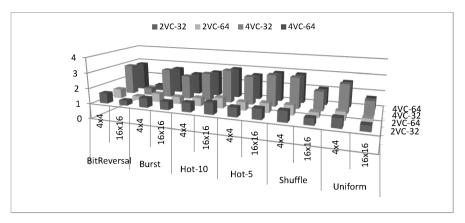

| 4.14 | Multi-switch area efficiency normalized to multi-network 164          |

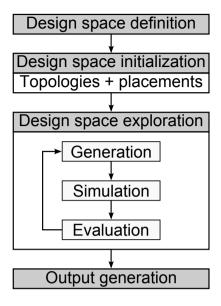

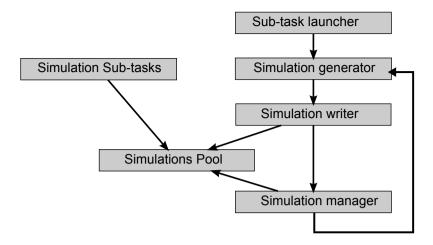

| 5.1  | LDSET execution flow                                                  |

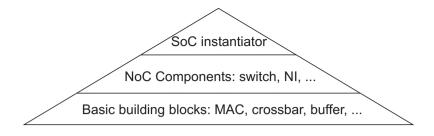

| 5.2  | NoC simulator hierarchy                                               |

| 5.3  | Example of CEF input file DSE definition                              |

| 5.4  | Example range of values                                               |

| 5.5  | Example numerical comparison in evaluation rules 179                  |

| 5.6  | Example of traffic flow description in CEF                            |

xii List of Figures

| 5.7  | Example of library with a switch and a NI                           | 183 |

|------|---------------------------------------------------------------------|-----|

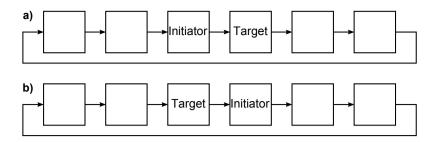

| 5.8  | Optimal placement of target and initiator a) for a write trans-     |     |

|      | action and b) for a read transaction                                | 184 |

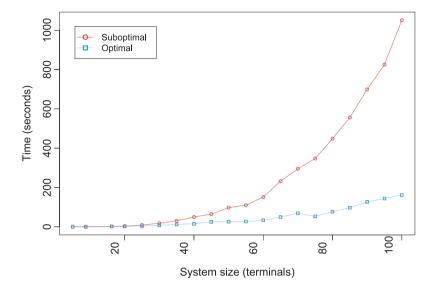

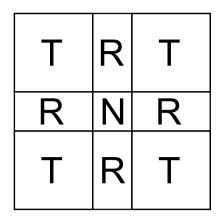

| 5.9  | Core placement algorithm                                            | 185 |

| 5.10 | Candidate calculation for optimal and suboptimal sets of can-       |     |

|      | did<br>ate templates for different system sizes                     | 187 |

| 5.11 | Flow diagram of the simulation engine                               | 188 |

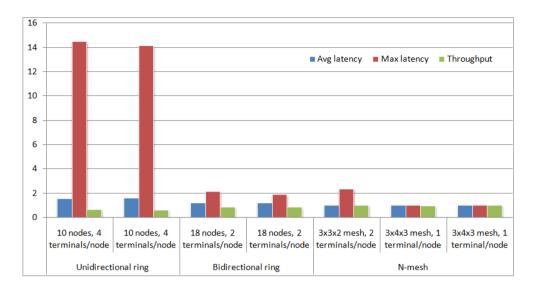

| 5.12 | Performance results of a DSE for an SoC with 36 cores               | 190 |

| 5.13 | Example of core definition in CEF format                            | 192 |

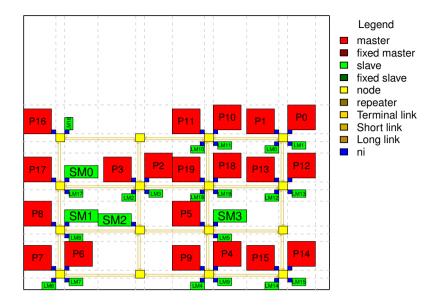

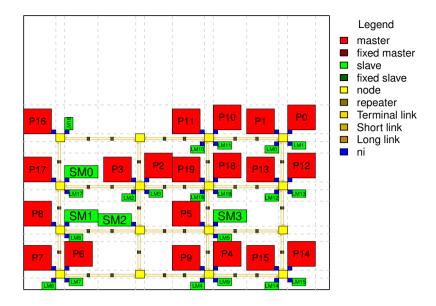

| 5.14 | Place and route at 1 mm inter-switch spacing at a target speed      |     |

|      | of 1 GHz (IP Core size not drawn to scale)                          | 193 |

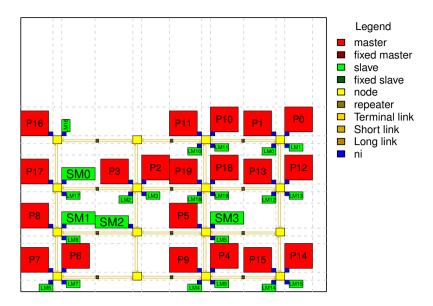

| 5.15 | Place and route at 1.5 mm inter-switch spacing at a target speed $$ |     |

|      | of 1 GHz (IP Core size not drawn to scale)                          | 194 |

| 5.16 | Place and route at 3 mm inter-switch spacing at a target speed      |     |

|      | of 1 GHz (IP Core size not drawn to scale)                          | 195 |

| 5.17 | Cell distribution of a core                                         | 196 |

## List of Tables

| 2.1  | Minimum buffer requirements of flow control mechanisms by                          |

|------|------------------------------------------------------------------------------------|

|      | link latency                                                                       |

| 3.1  | High level properties of analyzed topologies                                       |

| 3.2  | High level parameters of solutions for 16 cores                                    |

| 3.3  | High level parameters of solutions for 64 cores                                    |

| 3.4  | Simulation accuracy for a 4-ary 2-mesh 80                                          |

| 3.5  | Topologies under test                                                              |

| 3.6  | Topologies under test                                                              |

| 3.7  | Timing results                                                                     |

| 3.8  | Topologies under test                                                              |

| 3.9  | Post-place&route results of 64-tiles topologies with pipeline stage                |

|      | insertion                                                                          |

| 3.10 | Network topologies under test                                                      |

| 3.11 | Critical delay for 16-cores systems                                                |

| 4.1  | Overhead for VC support                                                            |

| 4.2  | Configurations for the compound switch architectures for $32 \ \mathrm{bits.} 151$ |

| 4.3  | Configurations for the compound switch architectures under                         |

|      | test for 64 bits                                                                   |

| 4.4  | Packet length for a burst of 10 32-bit words. Aggregate link                       |

|      | width in the NoC: 32 bits                                                          |

xiv List of Tables

### Abstract

Multi-core designs are becoming a more and more popular solution to most of the single-core designs limitations. A multi-core design follows the System on-Chip (SoC) paradigm, in which several cores are integrated into a single chip. The performance of SoC designs is heavily influenced by the interconnection infrastructure implemented: while small SoCs designs can employ buses as their interconnection, more complex interconnections are required as the number of cores of the design increases.

In this context, the Network on-Chip (NoC) paradigm arises as a solution to the interconnection challenges of new SoC designs. In a NoC, transactions between cores are encapsulated into packets, and delivered through a shared interconnection network. This concept is adopted from the off-chip interconnection networks field, and thus it can inherit most of the techniques of this mature field. Anyway, the on-chip environment presents different constraints than the off-chip one. For example, buffer size is a critical design parameter for any on-chip design, while it is a more relaxed constraint in off-chip ones. For this reason, techniques from the off-chip domain should not be taken for granted when implementing a NoC, but revised and adapted by taking into account the special characteristics of the on-chip domain.

In particular, in the on-chip domain the relentless pace of technology scaling to the nanoscale regime is bringing physical effects into the forefront. For this reason, visibility of the lower layers of the design hierarchy is required to accurately assess the capabilities of any given NoC design. In SoCs, the on-chip interconnect will be implicated in every communication stream. Therefore, the NoC physical characteristics are critical for overall SoC performance. In this context, SoC designs will be viable only when taking silicon aware decision at

xvi Abstract

each layer of the design hierarchy. However, this does not affect to need for fast design space exploration frameworks by means of abstract tools, hence making the accuracy-exploration speed trade-off increasingly difficult to cope with. For a given design space, the high heterogeneity (architectural and technological) of NoC solutions increases the complexity of selecting the optimal NoC configuration. A common approach is to use high level tools to provide performance estimations that the designer will use to select the most promising candidates at the earlier stages of the design flow. But there is a gap between the performance predictions of high-level tools and the real performance achieved after the system is implemented. In fact, this gap is growing, as the number of libraries available for a given technology node increases, forcing to increase the number of design re-spins due to inaccurate high level predictions, which results in increased design cost. The ultimate implication is that back-annotations from the lower layers of the design hierarchy need to be exposed to design tools operating at the upper layers, finding a new trade-off between simulation and/or exploration speed and layout awareness. Current front-end tools for use in the early design stages suffer from performance mispredictions, since they often ignore the technology platform. The challenge in finding the new trade-off point is that when considering both front-end and back-end issues (e.g., multiple technology libraries, core size), the design space becomes even wider than it is now.

This dissertation focuses on the development of a new set of front-end design, modeling and simulation tools for layout-aware pruning of the design space toward the most promising candidates. As an outcome of this dissertation, NoC designers will be able to take advantage of a new set of design space exploration tools reducing time-to-market and bridging the accuracy gap with the lower layers of the design process. In a first step, we focused on the design and development of an experimental setting for use in the analysis of alternative architecture design techniques. Since the objective is the analysis of a large range of implementation alternatives, it was decided to pursue transaction-level simulations. Hence, the dissertation reports on an extensive abstraction and modeling effort of NoC architecture building blocks while retaining accuracy of functionally equivalent Register Transfer Level (RTL) models. As a result, dramatic improvements in simulation speed were

Abstract xvii

achieved. At the same time, all abstract models were parameterized with some key parameters from the physical synthesis (e.g., target frequency, link latency), thus being able to evaluate points in the design space quickly and with high accuracy.

In the second step, by using the developed abstract simulation framework layout awareness was brought to the upper layers of NoC design, by reviewing architectural design techniques mutated from the off-chip domain in light of layout constraints, selecting the most promising candidates and in some cases even exploiting the distinctive features of the on-chip setting to come up with radically new (and even counterintuitive) solutions. This activity, which was preliminary to the design of the Design Space Exploration (DSE) tool, was aimed at gaining that layout awareness that the tool itself should have. The activity was split into two stages.

On one hand, starting from a theoretical description of the most popular topologies proposed for NoCs in the open literature, the developed simulation framework was employed in order to demonstrate and address the above mentioned gap. Concrete examples of the abstraction and accuracy gap will be provided for industry-relevant NoC configurations and the methodology will be put at work to close this gap, hence coming up with trustworthy cross-benchmarking indications. To demonstrate the potentials of the new NoC investigation framework, the topology analysis process will be extended to a number of architecture variants, featuring different size, floorplanning constraints, technologies and even HW/SW interaction patterns. Additionally, the most common pitfalls of topology physical design will be highlighted, and most common techniques to address them will be analyzed both in terms of achieved performance and cost overhead.

On the other hand, during the research on the topology exploration topic, several topologies were considered that require the use of the virtual channels flow control mechanism in order to reach their maximum potential. This very popular technique has been used for several years in off-chip networks for a broad number of reasons, and thus, its use has been widely advocated for NoCs. The most common VC architecture for NoCs proposed in the open literature is mutated from off-chip networks. Although fully functional in the NoC context, this architecture is aimed to a different environment and results

xviii Abstract

in an overly large area and delay overhead. For this reason, we propose and evaluate an implementation of VC better suited for the constraints of NoCs and therefore able to provide a considerable improvement both in performance and in area/power over the commonly proposed implementation, with the aim of demonstrating the mismatch between smart architecture design techniques conceived for off-chip interconnection networks and an on-chip setting.

Finally, we focused on the development of the Design Space Exploration (DSE) tool. Our approach to this challenge is two-folded. On one hand, we capitalize the knowledge gained in previous steps on silicon-aware architecture design choices and simulation tools, to build a CAD tool to aid in the design of NoC-based systems. On the other hand, we introduce some techniques to reduce the time-to-market of new designs via DSE acceleration and fast re-spin techniques.

### Resumen

Los diseños multi-núcleo se están convirtiendo en la solución más popular a la mayoría de las limitaciones de los diseños mono-núcleo. Un diseño multi-núcleo sigue el paradigma de diseño conocido como Sistema dentro del Chip (o SoC , del inglés System on-Chip), en el cuál varios núcleos se integran en un mismo chip. Las prestaciones de un diseño SoC dependen en gran medida de la infraestructura de interconexión que implemente: mientras que un SoC pequeño puede utilizar una interconexión de tipo bus, interconexiones más complejas serán necesarias conforme el número de núcleos del diseño aumente.

En este contexto, el paradigma de diseño conocido como red dentro del chip (o NoC, del inglés Network on-Chip) surge como una solución a los desafíos de interconexión presentes en los nuevos diseños de tipo SoC. En una NoC, las transacciones entre núcleos se encapsulan en paquetes, lo cuales serán entregados a su destinatario a través de la red de interconexión. Este concepto está adoptado del campo de las redes de interconexión de altas prestaciones, y como tal, puede heredar la mayoría de las técnicas diseñadas para un campo de investigación tan maduro como este. Pero a pesar de las similitudes existentes, ambos campos presentan diferentes limitaciones. Por ejemplo, el tamaño de los buffers es un factor crítico para el coste de diseños NoC, mientras que es un factor mucho menos relevante en el coste de las redes fuera del chip. Por ello, las técnicas diseñadas en el dominio de las redes fuera del chip no deberían suponerse directamente disponibles en NoCs, sino que deberán ser revisadas y adaptadas a sus particularidades.

En concreto, la reducción continua de las escalas de integración de las nuevas tecnologías hace que los efectos físicos afecten cada vez más a las prestaciones de una NoC. Dado que en la NoC está involucrada en todos los flujos de

xx Resumen

comunicaciones de cualquier SoC, es necesario que todas las etapas del flujo de diseño de una NoC tengan en cuenta de las consecuencias a nivel físico de todas las decisiones tomadas. Sin embargo, para un diseño concreto, el alto número de posibles soluciones basadas en NoCs (tanto a nivel de arquitecturas como a nivel de tecnologías) incrementa la complejidad de analizar el espacio de diseño y de elegir la NoC óptima. La solución más común a este problema pasa por la utilización de herramientas de alto nivel para la obtención de estimaciones sobre las prestaciones de cada posible solución NoC, que posteriormente serán utilizadas por el diseñador para cribar el espacio de diseño en las primeras etapas del proceso de diseño. Pero hay una gran diferencia entre las prestaciones estimadas por herramientas de alto nivel y las prestaciones reales obtenidas una vez el sistema se implementa. De hecho, esta diferencia aumenta conforme la cantidad de librerías disponibles para cada nodo tecnológico aumenta, generando un mayor número de errores en el proceso de diseño, lo que se traduce en un mayor coste de diseño. Para evitar estos problemas, es necesario extraer las características físicas de las NoCs de las capas de nivel más bajo del proceso de diseño y anotarlas en las herramientas que operan en los niveles más altos, encontrando nuevos puntos de compromiso entre velocidad de exploración del espacio de diseño y su precisión. Las herramientas actuales para la exploración temprana del espacio de diseño sufren de una pobre precisión, dado que es una práctica habitual el ignorar los efectos de la implementación física en ellas. El principal desafío es que al añadir las implicaciones de la implementación física al espacio de diseño, el tamaño de éste es incluso mayor de lo que era en un principio.

Este trabajo se centra en el desarrollo de nuevas herramientas de alto nivel de diseño, modelado y simulación de NoCs, con el fin de cribar el espacio de diseño de los candidatos menos atractivos mediante simulaciones de alta precisión basadas en la anotación de las características físicas de los candidatos. Como resultado de este trabajo, los diseñadores de NoCs serán capaces de aprovechar un nuevo conjunto de herramientas para la exploración del espacio de diseño que reducen el tiempo de desarrollo y minimizan los problemas de precisión mencionados anteriormente. En un primer paso, nos centraremos en el diseño y desarrollo de una plataforma experimental para analizar arquitecturas alternativas para el diseño de NoCs. Por ello, este trabajo presenta

Resumen xxi

los esfuerzos realizados en el desarrollo de modelos abstractos de los bloques básicos de arquitecturas NoC con una funcionalidad y precisión similares a las de modelos equivalentes con precisión a nivel de registro (o modelos RTL, del inglés Register Transfer Level). Como resultado de dichos esfuerzos, se obtuvieron dramáticas mejoras en los tiempos de simulación sobre modelos RTL funcionalmente equivalentes. Al mismo tiempo, todos los modelos desarrollados permiten anotar algunos parámetros claves del proceso de síntesis física (como la frecuencia de operación o la latencia de los enlaces), de forma que permiten evaluar cualquier punto del espacio de diseño de forma rápida y precisa.

En el segundo paso, mediante el uso de la plataforma de simulación desarrollada en el primer paso, las capas superiores del proceso de desarrollo de una NoC fueron aumentadas con la capacidad de considerar efectos físicos derivados de la implementación de una NoC sobre sus prestaciones. Mediante esta metodología, se revisaron arquitecturas y técnicas de diseño adoptadas del dominio de las redes de interconexión fuera del chip, seleccionando las más prometedoras y, en algunos casos, explotando las características propias de las redes dentro de chip para obtener nuevas soluciones. Este paso, preliminar al desarrollo de la herramienta para la realización de exploraciones del espacio de diseño (o herramientas DSE, del inglés Design Space Exploration), tiene como objetivo depurar las técnicas para la abstracción de los efectos de la implementación física de las NoCs sobre sus prestaciones. Este paso se dividió en dos etapas.

Por un lado, partiendo de un punto de vista puramente teórico, se analizaron las topologías más populares presentes en la literatura. Posteriormente, la plataforma de simulación desarrollada se utilizó para demostrar y corregir los fallos de precisión anteriormente mencionados. Ejemplo concretos relacionados con dichos problemas de precisión fueron analizados para configuraciones de NoCs relevantes para la industria, utilizando la metodología desarrollada para corregirlos. Para demostrar el potencial de la nueva plataforma para la investigación de NoCs, el análisis de topologías se extendió a un variado número de arquitecturas, con diferentes tamaños, restricciones de mapeado, tecnologías en incluso patrones de interacción entre hardware y software. Adicionalmente, los problemas más comunes que se pueden encontrar a la hora

xxii Resumen

de analizar el diseño físico de topologías, así como las técnicas para corregirlos, fueron analizados en términos tanto de prestaciones como de coste de implementación.

Por otra parte, varias de las topologías consideradas durante la investigación sobre topologías para NoCs requieren del uso de un mecanismo de control de flujo basado en canales virtuales para poder rendir a su máximo potencial. Esta popular técnica de control de flujo ha sido utilizada en el dominio de las redes de interconexión durante varios años por una gran variedad de razones, y por ello, se ha propuesto en numerosas ocasiones su uso en NoCs. La arquitectura con canales virtuales para NoCs más común en la literatura es importada del dominio de redes off-chip. Aunque es completamente funcional en el contexto de las NoCs, esta arquitectura está diseñada para un entorno diferente, lo que se traduce en penalizaciones en términos de frecuencia de operación y área. Por este motivo, proponemos y evaluamos una implementación de canales virtuales adaptada a las características de las NoCs, y consecuentemente capaz de mejorar considerablemente las prestaciones, el área y el consumo de potencia comparado con la implementación comúnmente aceptada.

Finalmente, nos centramos en el desarrollo de la propia herramienta para la realización de DSE. Nuestra solución a este desafío es doble. Por un lado, aprovechamos las técnicas desarrolladas en los pasos previos relativas al impacto de la implementación física sobre las prestaciones de las NoCs para construir una herramienta CAD para el apoyo al diseño de sistemas basados en NoCs. Por otro lado, introducimos algunas técnicas para reducir el coste de desarrollo de nuevos diseños mediante la aceleración de la exploración y técnicas para la corrección rápida de errores en el proceso de diseño.

#### Resum

Els dissenys multi-nucli s'estàn convertint en la solució més popular a la majoria de les limitacions dels dissenys mono-nucli. Un disseny multi-nucli segueix el paradigma de disseny conegut com a Sistema dins del Xip (o SoC, de l'anglés System on-Chip), en el qual diversos nuclis s'integren en un mateix xip. Les prestacions d'un disseny SoC depenen en gran mesura de la infraestructura d'interconnexió que implemente: mentres que un SoC petit pot utilitizar una interconnexión de tipus bus, interconnexions més complexes seràn necessàries conforme el nombre del disseny augmente.

En aquest context, el paradigma de disseny conegut com a red dins del xip (o NoC, de l'anglés Network on-Chip) sorgeix com una solución als desafiaments d'interconnexión presents en els nous dissenys de tipus SoC. En una NoC, les transaccions entre els nuclis s'encapsulen en paquets, els quals seràn entregats al seu detsinatari a través de la xarxa d'interconnexió. Aquest concepte està adoptat del camp de les xarxes d'interconnexió d'altes prestacions, i com a tal, pot heretar la majoria de les tècniques dissenyades per a un camp d'investigació tan madur com aquest. Però a pesar de les similituds existents, ambdós camps presenten diferents limitacions. Per exemple, el tamany dels buffers és un factor crític per al cost de dissenys NoC, mentre que és un factor molt menys relevant en el cost de les xarxes fora del xip. Per això, les tècniques dissenyades en el domini de les xarxes fora del xip no haurien de suposar-se directament disponibles en NoCs, més bé haurien de ser revisades i adaptades a les seues particularitats.

Concretament, la reducció contínua de les escales d'integració de les noves tecnologies fa que els efectes físics afecten cada vegada més a les prestacions de una NoC.

xxiv Resum

Atès que en la NoC està involucrada en tots els fluxs de comunicacions de qualsevol SoC, és necessari que totes les etapes del flux de disseny d'una NoC tinguen en compte les consegències, a nivell físic, de totes les decisions preses. No obstant això, per a un disseny concret, l'elevat númeo de possibles solucions basades en NoCs (tant d'arquitectures com de tecnologies) incrementa la complexitat d'analitzar l'espai de disseny i d'escollir la NoC òptima. La solució més comú a aquets problema pasa per la utilització d'eines d'alt nivell per a l'obtenció d'estimacions sobre les prestacions de cada possible solució NoC, que posteriorment seran utilitzades pel dissenyador per tal de garbellar l'espai de disseny en les primeres etapes del procés de disseny. Però hi ha una gran diferència entre les prestacions estimades per eines d'alt nivell i les prestacions reals obtingudes una vegada el sistema s'implementa. De fet, aquesta diferència augmenta segons la quantitat de llibreries disponibles per a cada nòdul tecnològic augmenta, generant un major nombre d'errors en el procès de disseny, la qual cosa es tradueix en un major cost de disseny. Per tal d'evitar aquests problemes, és necessari extraure les característiques físiques de les NoCs de les capes del nivell més baix del procés i anotar-les en les eines que operen en els nivells més alts, encontrant nous punts de compromís entre velocitat d'exploración de l'espai de disseny i la seua precisió. Les eines actuals per a l'exploració temprana de l'espai de disseny pateixen una pobre precisió, ja que és una pràctica habitual ignorar els efectes de la implementació física en aquestes. El principal desafiament és que en afegir les implicacions de la implementació física a l'espai de disseny, el tamany d'aquest és fins i tot major del que era al principi.

Aquest treball es centra en el desenvolupament de les noves eines d'alt nivell de disseny, modelat i simulació de NoCs, amb l'objectiu de garbellar l'espai de disseny dels candidats menys atractius mitjanant simulacions d'alta precisió basades en l'anotació de les característiques físiques dels candidats. Com a resultat d'aquest treball, els dissenyadors NoCs seran capaos d'aprofitar un nou conjunt d'eines per a l'exploració de l'espai de disseny que redueixen el temps de desenvolupament i minimitzen els problemes de precisió mencionats anteriorment. En un primer pas, ens centrarem en el disseny i desenvolupament d'una plataforma experimental per tal d'analitzar arquitectures alternatives per al disseny de NoCs. Per això, aquest treball presenta els esforos realitzats

Resum

en el desenvolupament de models abstractes dels blocs bàsics d'arquitectures NoC amb una funcionalitat i precisió similars a les dels models equivalents amb precisió de registre (o models RTL, de l'anglès Register Transfer Level). Com a resultat dels esforos mecionats, es van obtindre dramàtiques millores en els temps de simulació sobre models RTL funcionalment equivalents. Al mateix temps, tots els models desenvolupats permeten anotar alguns paràmetres claus del procés de síntesi física (com la freqència d'operació o la latència dels enl-laos), de forma que permeten evaluar qualsevol punt de l'espai de disseny de forma ràpida i precisa.

En el segon pas, mitjanant l'ús de la plataforma de simulació desenvolupada en el primer pas, les capes superiors del procés de desenvolupament de una NoC foren augmentades amb la capacitat de considerar efectes físics derivats de la implementació de una NoC sobre les seues prestacions. Mitjanant aquesta metodologia, es revisaren arquitectures i tècniques de disseny adaptades del domini de les xarxes d'interconnexió fora del xip, seleccionant les més prometedores i, en alguns casos, explotant les característiques pròpies de les xarxes dins del xip per tal d'obtindre noves solucions. Aquest pas, preliminar al desenvolupament de l'eina per a la realització d'exploracions de l'espai de disseny (o eines DSE, de l'anglès Design Space Exploration), té com a objectiu depurar les tècniques per a l'abstracció dels efectes de la implementació física de les NoCs sobre les seues prestacions. Aquest pas es va dividir en dues etapes.

D'una banda, partint d'un punt de vista purament teòric, es van analitzar les topologies més populars presents en la literatura. Posteriorment, la plataforma de simulació desenvolupada es va utilitzar per tal de demostrar i corregir les fallades de precisió anteriorment mencionades. Exemples concrets relacionats amb els problemes de precisió foren analitzats per a configuracions de NoCs relevants per a la indústria, utilitzant la metolodologia desenvolupada per a corregir-los. Per tal de demostrar el potencial de la nova plataforma per a la investigació de NoCs, l'anàlisi de topologies es va extendre a un variat nombre d'arquitectures, amb diferents tamanys, restriccions de mapatge, tecnologies en fins i tot patrons d'interacció entre hardware i software. Adicionalment, els problemes més comuns que es poden encontrar a l'hora d'analitzar el disseny físic de topologies, així com les tècniques per a corregir-los, foren

xxvi

analitzatz en termes tant de prestacions com de cost d'implementació.

D'altra banda, diverses de les topologies considerades durant la investigació sobre topologies per a NoCs requereixen l'ús d'un mecanisme de control de flux basat en canals virtuals per tal de poder rendir al seu màxim potencial. Aquesta popular tècnica de control de flux ha estat utilitzada en el domini de les xarxes d'interconnexió durant diversos anys per una gran varietat de raons, i per això, s'ha proposat en nombroses ocasions el seu ús en NoCs. L'arquitectura amb canals virtuals per NoCs més comú en la literatura és importada del domini de xarxes off-xip.

Encara que és completament funcional en el context de les NoCs, aquesta arquitectura està dissenyada per a un entorn diferent, la qual cosa es tradueix en penalitzacions en termes de freqència d'operació i àrea. Per aquest motiu, proposem i avaluem una implementació de canals virtuals adaptada a les característiques de les NoCs, i consequentment capa de millorar considerablement les prestacions, l'àrea i el consum de potència comparat amb la implementació comunament acceptada

Finalment, ens centrem en el desenvolupament de la pròpia eina per a la realització de DSE. La nostra solució a aquest desafiament és doble. D'una banda, aprofitem les tècniques desenvolupades en els passos previs relatives a l'impacte de la implementació física sobre les prestacions de les NoCs per construir una eina CAD per al suport al disseny de sistemes basats en NoCs. D'altra banda, introduïm algunes tècniques per reduir el cost de desenvolupament de nous dissenys mitjanant l'acceleració de l'exploració i tècniques per a la correcció ràpida d'errors en el procés de disseny

## Chapter 1

## Introduction

"Motivation is a fire from within. If someone else tries to light that fire under you, chances are it will burn very briefly."

Stephen R. Covey

In this chapter, we describe the reasons that have motivated this dissertation (Section 1.1). Then, we briefly define the objectives aimed by the dissertation (Section 1.2). Finally, we conclude this chapter by presenting the structure of this thesis (Section 1.3).

#### 1.1 Motivation

The increment on the integration densities will have to be exploited to meet the computational requirements of applications from different domains. Traditionally, scalable performance was requested for high-performance microprocessors, but nowadays this request is also common to embedded computing systems. In the recent past, microprocessors designers followed two main trends in order to address this challenge. First, mono-core architectures with advanced techniques to improve their performance were employed. Second, the operating frequency of new generation designs was significantly increased with respect to previous generations. But those design trends have run out of steam. The resulting architectures present power consumption and heat dissipation levels too high to be attractive for commercial products. Also, their complexity is increasing up to the point in which the designs are too complex and error prone, which increases the number and cost of design re-spins.

As mono-core architectures are ill-suited to solve the above exposed challenges, multi-core architectures have risen as the most elegant solution to address them. Multi-core architectures are composed by several cores that communicate with each other by means of some on-chip interconnection infrastructure, and are usually referred as Systems-on-Chip (SoC). In order to exploit the computation scalability provided by multi-core architectures, the communication bottleneck will have to be addressed. In this context, performance of gigascale SoCs will be communication dominated. Current on-chip interconnects consist mostly of shared arbitrated buses, based on the serialization of bus access requests. The main drawback of this solution is its poor scalability, which will result in unacceptable performance degradation for SoCs of medium or higher complexity (more than a dozen of integrated cores). Moreover, the connection of new blocks to a shared bus increases its associated load capacitance, increasing the energy consumption of bus transactions associated with the broadcast communication paradigm. Thus, Networks-on-Chip (NoCs) emerged as an scalable communication infrastructure that better supports the trend of the SoC paradigm [29,49,154]. The basic idea behind NoCs is borrowed from the interconnection networks domain, and envisions the onchip interconnection as a network on which packet-switched communication takes place. NoCs are able to inherit design techniques from interconnection networks, which is a nice quality as interconnection networks are a very mature field. A good example of this quality that can be analyzed in the open literature is the virtual channels flow control mechanism. Virtual channels are very popular in interconnection networks. First proposed by [47] as an effective workaround for head-of-line blocking, this design technique was then proposed for a wide range of aims, like implementing fault tolerance mechanisms [38] or guaranteeing deadlock freedom in adaptive routing algorithms [52]. The original virtual channel switch architecture of off-chip networks was further analyzed in [118], and then became the de facto solution for NoCs, with minimal changes to adapt it to this new environment. But this practice is not free of risks. NoCs and interconnection networks impose different constraints. As an example, in NoCs links are a cheaper resource than in interconnection 1.1. Motivation 3

networks, while buffers are much more expensive. This implies that NoC designers should adapt the techniques developed for interconnection networks, not just adopt them. Following the example of the virtual channel flow control mechanism, it is possible that either feasible implementations for off-chip networks become unfeasible in NoCs or unfeasible implementations for interconnection networks become feasible, and even competitive, in NoCs.

The design process of a SoC consists of a chain of design decisions. Among those decisions, a choice of utmost importance for global system performance is topology selection. A topology describes the connectivity pattern of networked cores, defining hard boundaries to the maximum performance achievable by the NoC as well as influencing other critical parameters like area requirements and power consumption. In particular, those boundaries stem from the combination of the theoretical properties of a NoC topology (e.g., average latency, bisection bandwidth) with the quality of its physical synthesis (e.g., link latencies, maximum operating frequency). For this reason it is very important to choose the most suitable topology for the requirements of each design.

The most popular NoC topology proposed in the open literature is the 2D-mesh, in which network cores are distributed in a grid-like structure. This topology provides great modularity and a predictable physical layout, but it is known it presents serious scalability issues as the number of network cores connected to it increases. This fact has motivated several works proposing alternative topologies for NoCs [23, 81], as well as techniques to improve the scalability of 2D-meshes by adapting them to the needs of a given design [110], or methodologies to build ad-hoc topologies for application specific designs [27, 109]. Some works based on abstract level analysis and simulation of topologies [23,81] lack of accurate performance predictions to support their conclusions. For this reason, other works employ synthesizable Register Transfer Level (RTL) tools, instead of abstract level ones, as the backbone of their performance predictions [27]. This approach solves the accuracy issue, being able to provide signal accurate results that will consider the quality of the physical synthesis of the design. But it presents a serious drawback: although RTL models are usually very accurate, they tend to be slow and/or memory-intensive, at least when compared with more abstract models. This limitation becomes very noticeable when exploring the candidates that compose the design space of any given SoC. When the possible topologies valid for a design are combined with several routing algorithms, network architectures and core placements, the number of combinations starts to be overwhelming. And this number of combinations will grow even higher when considering several technology libraries, with different aims (e.g., low power or high performance libraries). This fact points to the need of using more accurate abstract models able to provide cycle accurate performance estimations while at the same time being able to reflect the impact of the physical synthesis over performance predictions. Also, CAD tools will be needed to guide the designers towards the configurations that are more suitable to the peculiarities of each design.

Just to sum up, this dissertation will make a set of proposals intended for:

- Close the gap between performance predictions based on abstract models and real system performance by enhancing abstract modeling frameworks with layout awareness.

- Evaluate the viability and feasibility of regular NoC topologies other than a 2D-mesh, under different design constraints.

- Demonstrate the benefits of adapting design techniques to the NoC environment, as opposed to simply borrowing them from off-chip networks.

- Implement a CAD tool to assist designers in the process of selecting the most suitable network candidates out of a large design space with layout awareness.

#### 1.2 Objectives

This section presents the objectives of this dissertation. As commented in the previous section, we expect to provide an evaluation framework for a wide range of SoC configurations, as well as demonstrating the benefits of adapting off-chip design techniques to the NoC environment. In order to do this, we pursue the following goals:

To evaluate the viability and feasibility of several topologies for NoCs under different design constraints and architectural conditions by devel-

5

oping a methodology to perform fast and accurate topology explorations. Our proposal should consider several key points:

- The proposed methodology should use a simulation framework faster than existing RTL models while achieving similar performance estimations. Our proposed simulation framework should be able to run several simulations in the same time than existing RTL models take to run a single simulation.

- Physical synthesis impact over topology performance should be reflected with as much accuracy as possible, helping in this way to close the aforementioned gap in performance estimations.

- The methodology should be able to support different design techniques unique to NoCs, (e.g., cross-domain clocking mechanisms or link pipelining techniques). In this way it would be possible to analyze the impact of different implementation techniques over the selection of the best candidate topology for a given design.

In other words, we want to develop a topology exploration framework that will allow us to evaluate a wide range of topologies under different design constraints and with layout awareness.

- To show the benefits that can be achieved when off-chip design techniques are adapted to the NoC environment, even when those techniques can be directly adopted. As virtual channel flow control is a popular design choice that can be used for a wide variety of purposes, we aim to demonstrate how it can be adapted to NoCs, while achieving the following improvements over the adopted solution in interconnection networks.

- Reduced power consumption and area cost. As the number of virtual channels of a design is increased, the power consumption and area cost of the design typically tends to skyrocket.

- Improved scalability. The operating frequency of a classical virtual channel switch for NoCs quickly deteriorates as the number of virtual channels grows up. Our solution should have a better

- scalability, helping to alleviate one of the main issues of complex switch architectures in NoCs: their maximum operating frequency.

- Lower design cost. A common drawback of most proposals of new switch architectures is the cost of implementation, validation and verification. Although this cost is usually neglected in the open literature, it is one of the main reasons that prevents new proposal to be used in real system implementations. Our aim is to provide a new virtual channel switch architecture with a low design cost, which means to use simpler blocks as the foundation of the architecture, even reusing previously designed blocks when possible.

- To design and implement a tool to automatically explore the whole design space. Starting from the system specification, it should be able to provide a detailed description of the most suitable candidates inside the design space. For this reason it is required that it implements:

- A layout-aware topology exploration, using the methodology presented in this dissertation.

- The capability to consider a design space as large as possible. That is, it should be able to support different SoC designs with different applications, architectures, requirements, etc.

- A highly modular implementation, which should allow to easily change any part of the tool without affecting the rest of the modules.

For example, expanding the number of supported topologies should not affect other parts of the tool.

- A versatile simulation framework, which should be able to explore the design space as fast as possible.

- Support to fast design re-spins, in such a way that it should be possible for the designer to switch candidates later on the design flow without having to repeat the design space exploration process.

For example, this can be achieved by providing a classified list of candidates instead of a single one.

#### 1.3 Dissertation outline

The rest of the dissertation is organized as follows. Chapter 2 describes the fundamentals of NoCs and several works related to the contributions of this dissertation. Chapter 3 presents an analysis of a set of topologies proposed as NoC topologies in the open literature, as well as a topology exploration methodology. Chapter 4 describes a new virtual channel implementation for NoCs as a way of demonstrating the advantages of the *adapt not adopt* philosophy. Chapter 5 presents the Design Space Exploration (DSE) tool developed in collaboration with the company Lantiq Deutschland GmbH. The dissertation ends with Chapter 6, which summarizes our contributions and their advantages.

f

## Chapter 2

# Background and State of the art

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year... Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000. I believe that such a large circuit can be built on a single wafer."

#### Gordon Earle Moore

This chapter describes the basics and terminology for understanding the main aspects of Networks on-Chip. An in-depth view of the whole Networks on-Chip topic is not provided, since it is very complex with a multitude of aspects of no relevance for this dissertation. For this reason, we provide an overview of Networks on-Chip. We refer the reader to the established text-books on this topic, as well as textbooks for classical off-chip interconnection networks, for further background and introductory material [31, 45, 52, 60].

This chapter is composed by two sections. Section 2.1 is devoted to the aforementioned background on Networks on-Chip, while Section 2.2 provides

the state of the art in topology exploration and design space exploration, as well as for virtual channels architectures, for Networks on-Chip.

#### 2.1 Networks on-Chip

Moore's law states that the number of transistors that can be placed inexpensively on an integrated circuit will double approximately every two years [104]. This increment on the integration densities will have to be exploited to meet the computational requirements of applications from different domains such as multimedia processing, high-end gaming, biomedical signal processing, advanced networking services, automotive or ambient intelligence. Traditionally, scalable performance was requested for high-performance microprocessors, but nowadays this request is also common to embedded computing systems. As an example, systems designed for ambient intelligence use high-speed digital signal processing with computational loads ranging from 10 MOPS for lightweight audio processing, 3 GOPS for video processing, 20 GOPS for multilingual conversation interfaces and up to 1 TOPS for synthetic video generation. Those requirements define a computational challenge that must be addressed at manageable power levels and affordable costs [35].

In the recent past, microprocessors designers followed two main trends in order to address those challenges. First, mono-core architectures were preferred and advanced techniques were employed in order to improve their performance (e.g., executing of instructions out-of-order [135] and/or in an speculative way [111]) together with improvements to some components externals to microprocessors (e.g., placing parts of the cache inside the microprocessor chip, increasing the cache hierarchy or increasing its size and speed [147]). Second, the operating frequency of new generation designs was increased with respect to previous generations. Although it is still possible to design monocore microprocessors based on the above exposed trends, this design model is exhausted, as it produces designs with a power consumption and heat dissipation too high for attractive commercial products. Also, the techniques required to keep the competitiveness of mono-core architectures are becoming too complex, increasing the design and implementation cost of mono-core architectures. On the other hand, new generation applications require an

increasing amount of parallel capabilities, both in high-performance micro-processors and in embedded systems, like domestic systems (e.g., multi-task systems, game consoles, mobile phones, etc.), scientific applications (e.g., genetic sequentiation, numerical calculus, etc.) and in specialized servers (e.g., digital video encoder/decoder, Internet servers, etc.). Thus, consumers of next generation microprocessors are becoming more demanding, expecting products that achieve performance levels difficult to support in mono-core architectures

In the case of domestic and high-performance systems, the power consumption has been a limiting factor for some time now, as it has a direct impact over the operating cost of any system. But with the increment of popularity of mobile devices (smartphones, PDA, even laptops, etc.) the need for providing designs with a high energy efficiency has increased the pressure of power-wise designs [76], with the aim of maximizing battery life. In addition, the power consumption effect over system cost is two-folded, as the heat dissipation cost of a system is directly related to its power consumption. As new designs become more compact, it becomes more expensive to remove the excess of heat dissipation, an effect that is aggravated by the growing cost of heat dissipation systems.

The most accepted solution to address the above exposed issues consists of simplifying the architecture of microprocessors. But in order to do this and to keep up with the ever increasing demand of performance, the design should be composed of several simple processors integrated into a single chip, in what is commonly referred as *Systems-on-Chip* (SoCs). In this way, a SoC would be composed of several cores with a manageable operating frequency, for instance by implementing simple processors for generic use and specialized ones for the heaviest tasks, instead of a big complex processor able to carry out all the task by itself. The resulting architecture will be capable of achieving similar or better raw performance than an equivalent mono-core microprocessor, with less heat dissipation and power consumption issues.

# 2.1.1 Systems on-Chip

A typical SoC is composed by one or more processors, several memory blocks (possibly heterogeneous) and several devices and interfaces to provide connections with the external world (e.g., USB, FireWire, Ethernet, etc.), all of them

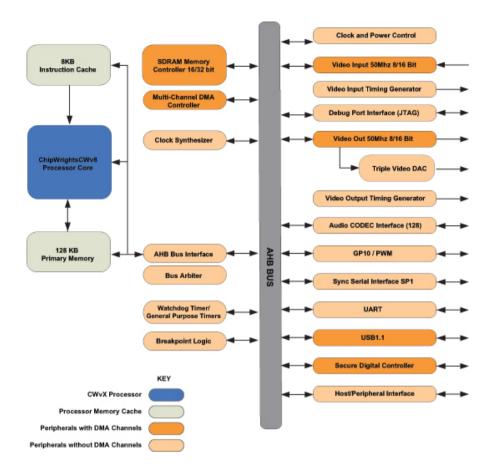

Figure 2.1: Example of a System on-Chip: CW4512

interconnected through a shared infrastructure, like a bus. As an example of a SoC architecture, Figure 2.1 shows the diagram of the CW4512 System on-Chip [1], which is composed by a ChipWrightsCWv8 [1] processor attached to a shared bus that interconnects the different components: processor, memories and other peripherals.

By following this paradigm designers are able to tackle the above exposed challenges. First, SoC designs are by definition better suited than classical mono-core designs to work with multi-thread applications and multi-task systems, as they are able to execute several threads and/or applications at the same time in different cores. Second, they offer a great potential to reduce the development cost of new designs due to their modular nature, either by up-

grading old designs by just re-designing a sub-set of the cores or by developing new design that reuse cores developed for previous designs. Third, SoC design are highly scalable as a wide range of characteristics can be adjusted just by altering the number and type of cores of a design, which allows designers to easily derive a whole product family from a single SoC design. Finally, the SoC design paradigm presents high power saving capabilities, as they favor designs with lower operating frequency than an equivalent classical mono-core design. Additionally, it exists the possibility to drastically reduce the power consumption of the system by shutting down idle cores transparently to applications.

Based on the type of cores that compose a SoC, this latter can be grouped into two main classes. On one hand, a SoC is homogeneous when composed by cores of the same type. Commonly used in general purpose systems (e.g., multi-core processors for cluster of computers for scientific computation), several examples of commercial homogeneous SoCs exists, like the Intel Core2 Quad [2] and the AMD Phenom X4 Quad-Core [3] processors, which are composed by four identical processing cores. On the other hand, a SoC is heteroqeneous if it is composed by cores with a variety of types, like programmable processors of generic use, different kinds of memories, processors optimized for specific applications and/or hardware accelerators. The high degree of heterogeneity of those SoCs makes it possible to use the optimal core for each task. For example, a real-time MPEG4 encoder will use several specialized cores to code the video frames, while another core will code the audio track. A commercial example of heterogeneous SoC is the Nokia N770 Internet Tablet, which implements an OMAP 1710 processor [4] composed by an ARM926TEJ [5] generic processor and by a TMS320C55x digital signal processor [4].

SoCs can also be named after their target market. On one hand, *Multi-Procesor Systems-on-Chip* (MPSoCs) are SoCs aimed to the embedded system market, and therefore are heavily constrained in their power and area cost. Additionally, the extreme commercial competitiveness of this market push designers to reduce the *Time To Market* (TTM) of the new designs to the limit, favoring the use of standard cell libraries and synthesis-based design flows. On the other hand, *Chip Multi-Processors* (CMPs) aim at the high-performance market. Favoring high performance over area and power efficiency over other

Figure 2.2: Schema of a shared bus.

considerations, full custom designs techniques are largely adopted, rendering TTM as a second rate design constraint.

In this context SoC performance is mainly defined by the cores that compose it, but the impact of the interconnection over SoC performance should not be underestimated; an inadequate interconnection infrastructure may become the system bottleneck, increasing the power consumption of the system and decreasing its performance. For this reason, the choice of the adequate communication infrastructure is a critical step in any SoC design process.

#### 2.1.2 Shared bus

Traditionally, on-chip interconnects consist of low-cost shared arbitrated buses [21,43]. Those networks employ one of the most simple interconnection infrastructures, in which there is a unique communication medium that is shared by all the devices (see Figure 2.2). In a shared medium, transactions are serialized, as usually it is no possible to carry out more than a single simultaneous transaction, thus at any given time only a single device, called master, can send data through the bus, while all the other devices can only read data from the bus, acting as slaves. In some bus implementations simultaneous transactions are supported, but usually with serious limitations, like a low number of concurrent transactions. This serialization makes the arbitration mechanism a key design factor for any bus based system. The arbitration decides which master device will write in the bus when the number of simultaneous transactions. The information sent through the bus is divided into three kinds: data,

address and control. It is possible to send it through a single multiplexed channel or to send each kind through an independent one. Also, bus networks are usually passive, meaning that the network does not generate messages on its own. Besides, a shared bus is naturally well-suited to work with broadcast communications, in which a single device sends the same data set to a group of devices.

Modern bus-based designs usually implement backplane buses, that are designed as a low-overhead communication infrastructure aimed for systems composed by a low number master devices and a variable number of slave devices. While master devices can initiate transactions slave devices are not, being limited to respond to the transactions initiated by the masters. In modern buses the most common arbitration solution is a centralized mechanism, implemented as a bus arbiter module. In this mechanism a master device must obtain permission from the arbiter module before starting any transaction. Centralized arbitration has a negative impact over the system performance due to the overhead introduced by the requests to the arbiter module, so the arbitration should be as fast and infrequent as possible.

An example of a commercial shared bus is the AMBA (Advanced Microcontroller Bus Architecture) 2.0 standard, designed for the ARM [5] processor family. This simple bus, which has been widely used in SoC designs, uses the AHB protocol (Advanced High-performance Bus) to interconnect on-chip integrated devices, like ARM processors and RAM memories. It supports differentiated transmission of data and address, both in normal and burst modes<sup>1</sup>. This latter is also utilized to alleviate the overhead introduced by the implemented centralized arbiter. However, the 3.0 version of this same standard supports several simultaneous transactions as well as out-of-order transaction resolution.

To summarize, shared buses are the most well-known and the most widely used communications architecture for SoCs, as they are very simple and cost effective. But their scalability is quire limited: it is a viable solution for SoCs with up to five processors and up to ten master devices [31]. For bigger systems it presents unaffordable congestion rates, becoming a bottleneck with a severe

<sup>&</sup>lt;sup>1</sup>In burst mode, the master device schedules several consecutive data transfers to the same destination with a single round of arbitration

Figure 2.3: Schema of a Network on-Chip.

negative impact over system performance and increasing the system waiting time, therefore wasting a considerable amount of power. For these reasons, the performance achievable by bus-based high-scale SoCs is very limited. As an example, a possible commercial design in which a bus would be ill-suited to satisfy the system communication demands would be the MPSoC TILE64 [6], an MPSoC composed by 64 processors.

Thus, more powerful communication infrastructures are needed in order to fulfill the needs of SoCs with a growing number of components. Although it may seems that this requires to develop new solutions, the truth is that we can adapt solutions developed for similar issues in other research fields. In particular, interconnection networks are the most common high performance communication infrastructures used in other environments, like in supercomputers. The Network on-Chip (NoC) concept is born from the application of interconnection networks to SoC designs [29, 49].

# 2.1.3 A new design paradigm

Networks-on-Chip (NoCs) were proposed as the solution to shared bus scalability issues, emerging as the new parading for designing scalable communication infrastructures in SoCs. The main advantage of a NoC over a shared bus is its capability to reduce design costs while providing high-performance communications.

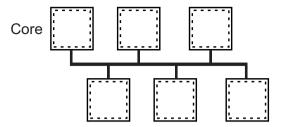

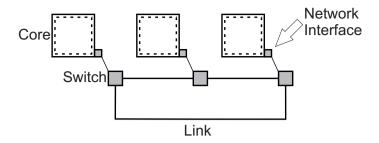

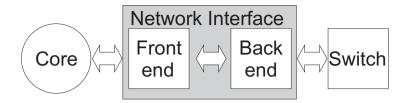

In a NoC, each core is connected by a Network Interface (NI) to a network link. Those links are point-to-point data lines connected with other links via switches. A link can connect a switch with another switch or with a NI, in such a way that it exists direct or indirect connection between any two cores.

Due to the similarities between interconnection networks and NoCs, it is possible to borrow concepts and techniques from the former and apply them to NoCs. Even so, most of the techniques developed for interconnection networks cannot be directly applied in NoCs, while other ones would be completely unaffordable using current technologies. The reason for this lies in the restrictions imposed by each environment. For example, while in interconnection networks buffers are a relatively abundant and affordable resource, in NoCs they are scarce and expensive, with high area requirements and power consumption, which hinders even more their use in NoCs. On the contrary, links are an expensive resource in interconnection networks, that must be used with austerity, while in NoCs links are more abundant. Additionally, the total area available and the tolerable power consumption bugdet of a SoC are very limited. An ideal NoC must meet the communications needs of the design while minimizing power and area consumption. This latter fact implies that the switches should be as fast, small and power-efficient as possible, which hinders even more the application of interconnection solutions in NoC designs. The architecture of each NoC component directly or indirectly affects all kinds of design parameters, like maximum operating frequency, buffering requirements, etc. The compilation of architectures of the components that compose the network is referred as network architecture.

# 2.1.4 Networks on-Chip components

Most of the terminology used in NoCs is inherited from the interconnection network domains. Transactions between cores are compacted and divided in packets, which are divided into parts of the size of a flow control unit, known as flits. Flits can be classified based on their position inside the packets as header, tail or payload. Header flits are located at the beginning of the packet, and contain all the information required to route the packet towards its destination. The tail flit is the last flit of the packet, and its main role is to act as an end-of-packet marker. Flits located between the header and the payload qualify as payload, and their function is to carry data. On the other hand, a phit is the minimal data that can be transmitted through a link in a single cycle. In other words, flits represent logical data units while phits represent physical data units. In the case that the phit size of a link is lower than flit size it will

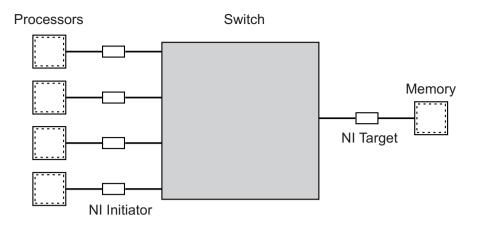

Figure 2.4: Schema of a Network Interface.

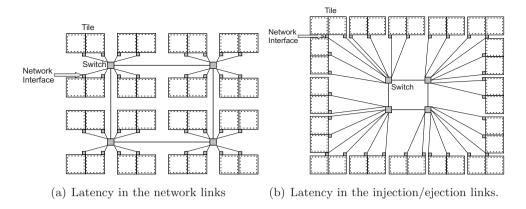

take several cycles to transmit a single flit through this link. For this reason, it is a common design technique to build architecures in such a way that flit size and phit size are similar.