# Efficient L2 Cache Management to Boost GPGPU Performance

July 2019

Author: Francisco Candel Margaix

Advisors: Salvador Petit Martí

Julio Sahuquillo Borrás

# Abstract

In recent years, the growing need for computing capacity has become a challenge that has led the industry to look for alternative architectures to conventional out-of-order superscalar processors, with the goal of enabling an increase of computing power while achieving higher energy efficiency.

GPU architectures, which just a decade ago were applied to accelerate computer graphics exclusively, have been one of the most employed alternatives for several years to reach the mentioned goal. A particular characteristic of GPUs is their high main memory bandwidth, which allows executing a large number of threads in a very efficient way. This feature, as well as their high computational power regarding floating-point operations, have caused the emergence of the *GPGPU computing* paradigm, where GPU architectures perform general purpose computations. The aforementioned characteristics make GPU devices very appropriate for the execution of massively parallel applications that have been traditionally executed in conventional high-performance processors.

The work performed in this thesis aims to help improve the performance of GPUs in the execution of GPGPU applications. To this end, as a first step, a characterization study is carried out. In this study, the most important features of GPGPU applications, with respect to the memory hierarchy and its impact on performance, are identified. For this purpose, a detailed cycle-accurate simulator is used to model the architecture of a recent GPU. The study reveals that it is necessary to model with more detail some critical components of the GPU memory hierarchy in order to obtain accurate results. In addition, it shows that the achieved benefits can vary up to a factor of  $3 \times$  depending on how these critical components are modeled.

Due to this reason, as a second step before realizing a novel proposal, the work in this thesis focuses on determining which components of the GPU memory hierarchy must be modeled with more detail to increase the accuracy of simulator results and improving the existing simulator models of these components. Moreover, a validation study is performed comparing the results obtained with the improved GPU models against those from a real commercial GPU. The implemented simulator improvements reduce the deviation of the results obtained with the simulator from results obtained with the real GPU by about 96%.

Finally, once simulation accuracy is increased, this thesis proposes a novel approach, called FRC (Fetch and Replacement Cache), which highly improves the GPU computational power by enhancing main memory-level parallelism. The proposal increases the number of parallel accesses to main memory by accelerating the management of fetch and replacement actions corresponding to those cache accesses that miss in the cache. The FRC approach is based on a small auxiliary cache structure that efficiently uncloss the memory subsystem, enhancing the GPU performance up to 118% on average compared to the studied baseline. In addition, the FRC approach reduces the energy consumption of the memory hierarchy by a 57%.

# Resumen

En los últimos años, la creciente necesidad de la capacidad de cómputo ha supuesto un reto que ha llevado a la industria a buscar arquitecturas alternativas a los procesadores superescalares con ejecución fuera de orden convencionales, con el objetivo de incrementar la potencia de cómputo con una mayor eficiencia energética.

Las GPU, que hasta hace apenas una década se dedicaban exclusivamente a la aceleración de los gráficos en los computadores, han sido una de las arquitecturas alternativas más utilizadas durante varios años para alcanzar el mencionado objetivo. Una de las características particulares de las GPU es su gran ancho de banda para acceder a memoria principal, lo que les permite ejecutar un gran número de hilos de forma muy eficiente. Esta característica, así como su elevada potencia computacional ejecutando operaciones de coma flotante, ha originado la aparición del paradigma de computación denominado *GPGPU computing*, paradigma en el que las GPU realizan cómputo de propósito general. Las citadas características convierten a las GPU en dispositivos especialmente apropiados para la ejecución de aplicaciones masivamente paralelas que tradicionalmente se habían ejecutado en procesadores convencionales de altas prestaciones.

El trabajo desarrollado en esta tesis persigue ayudar a mejorar las prestaciones de las GPU en la ejecución de aplicaciones GPGPU. Con este fin, como primer paso, se realiza un estudio de caracterización donde se identifican las características más importantes de estas aplicaciones desde el punto de vista de la jerarquía de memoria y su impacto en las prestaciones. Para ello, se utiliza un simulador detallado ciclo a ciclo donde se modela la arquitectura de una GPU reciente. El estudio revela que es necesario modelar de forma más detallada algunos componentes críticos de la jerarquía de memoria de las GPU para obtener resultados precisos.

Los resultados obtenidos muestran que las prestaciones alcanzadas pueden variar hasta en un factor de  $3\times$  dependiendo de cómo se modelen estos componentes críticos.

Por este motivo, como segundo paso antes de elaborar la propuesta de mejora, el trabajo se centra en determinar qué componentes de la jerarquía de memoria de la GPU necesitan modelarse con mayor detalle para mejorar la precisión de los resultados del simulador, y en mejorar los modelos existentes de estos componentes. Además, se realiza un estudio de validación que compara los resultados obtenidos con los modelos mejorados contra los de una GPU comercial real. Las mejoras implementadas reducen la desviación de los resultados del simulador sobre los resultados reales alrededor de un 96%.

Finalmente, una vez mejorada la precisión del simulador, en esta tesis se presenta una propuesta innovadora, denominada FRC (siglas en inglés de Fetch and Replacement Cache), que mejora en gran medida la potencia computacional de la GPU, gracias a que aumenta el paralelismo en el acceso a memoria principal. La propuesta incrementa el número de accesos en paralelo a memoria principal mediante la aceleración de la gestión de las acciones de búsqueda y reemplazo relacionadas con los accesos que fallan en la cache. La propuesta FRC se basa en una pequeña estructura cache auxiliar que descongestiona el subsistema de memoria eficientemente, aumentando las prestaciones de la GPU hasta un 118% de media respecto al sistema base. Además, también reduce en 57% el consumo energético de la jerarquía de memoria.

# Resum

En els últims anys, la creixent necessitat de capacitat de còmput ha suposat un repte que ha portat a la indústria a buscar arquitectures alternatives als processadors superescalars amb execució fora d'ordre convencionals, amb l'objectiu d'incrementar la potència de còmput alhora que s'aconsegueix una major eficiència energètica.

Les arquitectures GPU, les quals fins fa només una dècada es dedicaven exclusivament a l'acceleració dels gràfics en els computadors, han sigut una de les alternatives més utilitzades durant alguns anys per a aconseguir l'esmentat objectiu. Una de les característiques particulars de les GPU és el seu elevat ample de banda per a accedir a memòria principal, la qual cosa permet executar un gran nombre de fils de forma molt eficient. Aquesta característica, així com la seua elevada potència computacional executant operacions de coma flotant, ha originat l'aparició del paradigma de computació anomenat *GPGPU computing*, paradigma on les GPU realitzen còmput de propòsit general. Les citades característiques converteixen a les GPU en dispositius especialment apropiats per a l'execució d'aplicacions massivament paral·leles que tradicionalment s'havien executat en processadors convencionals d'altes prestacions.

El treball desenvolupat en aquesta tesi persegueix ajudar a millorar les prestacions de les GPU en l'execució de les aplicacions GPGPU. A aquest efecte, com a primer pas, es realitza un estudi de caracterització on s'identifiquen les característiques més importants d'aquestes aplicacions des del punt de vista de la jerarquia de memòria i el seu impacte en les prestacions. Per a això s'utilitza un simulador detallat cicle a cicle on es modela l'arquitectura d'una GPU recent. L'estudi revela que és necessari modelar de forma més detallada alguns components crítics de la jerarquia de memòria de les GPU per a obtindre resultats precisos. Els resultats obtinguts

mostren que les prestacions aconseguides poden variar fins i tot en un factor de  $3\times$  depenent de com es modelen aquests components crítics.

Per aquest motiu, com a segon pas abans d'elaborar la proposta de millora, el treball se centra en determinar quins components de la jerarquia de memòria de la GPU necessiten modelar-se amb major detall per a millorar la precisió dels resultats del simulador i en millorar els models existents d'aquests components. A més, es realitza un estudi de validació que compara els resultats obtinguts amb els models millorats contra els d'una GPU comercial real. Les millores implementades redueixen la desviació dels resultats del simulador sobre els resultats reals al voltant d'un 96%.

Finalment, una vegada millorada la precisió del simulador, en aquesta tesi es presenta una proposta innovadora, denominada FRC (sigles en anglés de Fetch and Replacement Cache), que millora en gran manera la potència computacional de la GPU, gràcies a que augmenta el paral·lelisme en l'accés a memòria principal. La proposta incrementa el nombre d'accessos en paral·lel a memòria principal mitjançant l'acceleració de la gestió de les accions de recerca i reemplaçament relacionades amb els accessos que fallen en la cache. La proposta FRC es basa en una xicoteta estructura cache auxiliar que descongestiona el subsistema de memòria eficientment, augmentant les prestacions de la GPU fins a un 118% de mitjana respecte al sistema base. A més, també redueix, al voltant d'un 57%, el consum energètic de la jerarquia de memòria.

# Contents

| Abstract                                                                      | iii |

|-------------------------------------------------------------------------------|-----|

| Contents                                                                      | ix  |

| 1 Introduction                                                                | 1   |

| 1.1 Motivation                                                                | 1   |

| 1.2 Background                                                                | 3   |

| 1.3 Thesis Objectives                                                         | 10  |

| 1.4 Contributions                                                             | 11  |

| 1.5 Outline                                                                   | 11  |

| 2 Impact of Memory-Level Parallelism on the Performance of GPU Coherence Pro- |     |

| tocols                                                                        | 13  |

| 2.1 Abstract                                                                  | 14  |

| 2.2 Introduction                                                              | 14  |

| 2.3 GPU Architecture                                                          | 15  |

| 2.4 Axes of Characterization                                                  | 15  |

| 2.5 Experimental Evaluation                                                   | 17  |

| 2.6. Rolated Work                                                             | วา  |

|   | 2.7 Conclusions                                                        | . 23 |

|---|------------------------------------------------------------------------|------|

| 3 | Accurately Modeling the GPU Memory Subsystem                           | 25   |

|   | 3.1 Abstract                                                           | . 26 |

|   | 3.2 Introduction                                                       | . 26 |

|   | 3.3 Related Work                                                       | . 28 |

|   | 3.4 Southern Islands GPU Architecture and Programming Model            | . 29 |

|   | 3.5 Proposed Multi2Sim GPU Extensions                                  | . 32 |

|   | 3.6 Experimental Results                                               | . 37 |

|   | 3.7 Conclusions                                                        | . 41 |

| 4 | Accurately Modeling the On-chip and Off-chip GPU Memory Subsystem      | 43   |

|   | 4.1 Abstract                                                           | . 44 |

|   | 4.2 Introduction                                                       | . 44 |

|   | 4.3 Related Work                                                       | . 46 |

|   | 4.4 Southern Islands GPU Programming Model and Architecture            | . 47 |

|   | 4.5 Modeled Memory Subsystem Components                                | . 50 |

|   | 4.6 Experimental Results                                               | . 56 |

|   | 4.7 Putting it All Together and Validation                             | . 63 |

|   | 4.8 Conclusions                                                        | . 64 |

|   | Improving GPU Cache Hierarchy Performance with a Fetch and Replacement | c.5  |

| U | ache                                                                   | 67   |

|   | 5.1 Abstract                                                           | . 68 |

|   | 5.2 Introduction                                                       | . 68 |

|   | 5.3 Background                                                         | . 70 |

|   | 5.4 Motivation                                                         | . 71 |

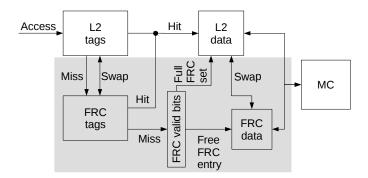

|   | 5.5 FRC Approach                                                       | . 72 |

|   | 5.6 Experimental Evaluation                                            | . 74 |

|   | 5.7 Related Work                                                       | . 77 |

| 5.8 Conclusions                                                          | 78  |

|--------------------------------------------------------------------------|-----|

| 6 Efficient Management of Cache Accesses to Boost GPGPU Memory Subsystem |     |

| Performance                                                              | 85  |

| 6.1 Abstract                                                             | 86  |

| 6.2 Introduction                                                         | 86  |

| 6.3 Background                                                           | 89  |

| 6.4 Motivation                                                           | 90  |

| 6.5 FRC Implementation                                                   | 94  |

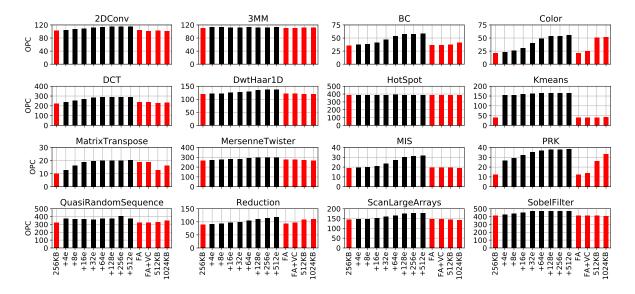

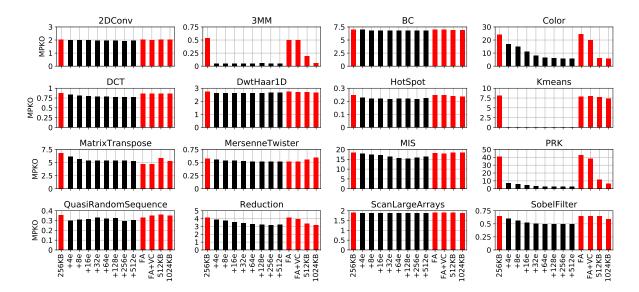

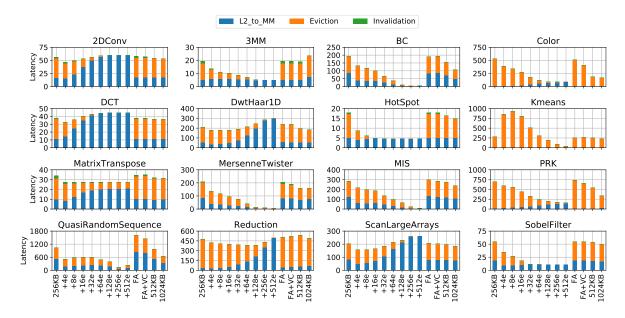

| 6.6 Experimental Evaluation                                              | 96  |

| 6.7 Related Work                                                         | 10  |

| 6.8 Conclusions                                                          | 12  |

| 7 Results Discussion 1                                                   | 15  |

| 7.1 Characterization of GPGPU Applications                               | 16  |

| 7.2 Simulator Framework Improvements and Validation                      | 17  |

| 7.3 Proposed LLC Miss Management Approach                                | 18  |

| 8 Conclusions                                                            | 21  |

| 8.1 Characterization of GPGPU Applications                               | 22  |

| 8.2 Simulator Framework Improvements and Validation                      | 22  |

| 8.3 Proposed LLC Miss Management Approach                                | .24 |

| 8.4 Other Indirectly Related Work                                        | 25  |

| 8.5 Future Work                                                          | 26  |

| Bibliography 1                                                           | 27  |

# Chapter 1

# Introduction

This chapter introduces both basic and fundamental concepts to help understand this dissertation and presents the motivation for the work developed in this thesis.

# 1.1 Motivation

In the last decade, GPU (Graphics Processing Unit) architectures have acquired a great relevance in both high-performance computing and heterogeneous computing. The main reason of this increasing relevance is that GPUs are much more energy efficient than CPUs [27, 29], since they provide a much higher thread-level parallelism and a better performance to power ratio. As a consequence, many of the most powerful and energy-efficient supercomputers in the world, ranked in both Top500 and Green500 lists [71], rely on GPUs.

The huge computational power that GPUs can provide mainly comes from their ultra-parallel architecture. They are composed of around one hundred of Single Instruction Multiple Data (SIMD) units that work in parallel, while a single SIMD unit can execute the same instruction for tens of different threads in the same clock cycle. This architecture allows GPU applications to be characterized by their massive parallelism, and they are composed of thousands of logical threads.

However, to feed all the SIMD units with enough data, memory accesses need to be handled in a fast manner; otherwise these units would suffer starvation, preventing the GPU from achieving its peak performance. This means that the memory hierarchy plays a key role in GPU performance and it must be designed to provide much higher bandwidth than conventional multi-core CPU memory subsystems. Based on these requirements, the memory hierarchy of a GPU is not designed to reduce the latency of individual accesses but to support a huge number of concurrent accesses. In this way, the high thread-level parallelism allows to hide the major part of the main memory latency.

GPUs were originally built in the 70s as specialized hardware to accelerate graphic processing. The first designs could not be programmed and their functionality was implemented directly in the hardware. With the evolution of GPU designs this constraint was removed and, in the 2000s, the first cards with programmable shaders were presented, that is, small programs that run for every pixel that is rendered on the screen. Not much later, manufacturers introduced support that enabled the use of these programmable GPUs not only for graphics but for accelerating the processing of matrices or vectors, giving birth to the General Purpose computing on Graphics Processing Units (GPGPU) programming paradigm.

Nowadays, GPGPU is a major computing paradigm, whose requirements drive the development of current and future GPU devices. Nevertheless, programming high-performance GPGPU applications widely differs from programming CPU applications because the application work must be distributed among the highest possible number of threads. Unfortunately, the high level of parallelism increases programming complexity and requires from efficient architectures to support it. To deal with this fact, and to help programmers to accelerate the development of fast GPGPU applications, the industry is both facilitating GPU programmability and raising the computational power of GPU devices by adapting different architectural mechanisms, like cache memories or prefetchers, which have worked successfully in CPUs. Even including these system components, GPU memory subsystems present serious performance bottlenecks caused by the huge level of parallelism. To palliate this problem, as GPU architectures evolve they include larger on-chip memory subsystems that allow improving the Memory-Level Parallelism (MLP) and so the system performance. For instance, Nvidia has systematically enlarged the Last-Level Cache (LLC) size in 2MB on consecutive recent architectures (e.g., LLC sizes of Maxwell [53], Pascal [54], and Volta [55] GPUs are 2MB, 4MB, and 6MB, respectively).

The importance of facilitating the programmability of GPUs and increasing their memory subsystem performance is currently driving the research on the memory hierarchy of GPUs. In order to design and evaluate new memory subsystem approaches for GPUs, researchers often use complex simulation environments because they are more affordable and easier to

implement than real hardware. In addition, this software allows researchers to focus only on those components having a significant impact on the system performance, while paying less or no attention to the implementation details of other, less significant, components. However, the continuous evolution of real GPU architectures makes simulators to quickly loose accuracy and becoming less representative with respect to the real hardware of last GPU generations. Therefore, simulation software needs to be revised and updated from time to time to ensure that the simulation results remain valid. In particular, the modeling of components of new architectures critical for performance needs to be accurately covered.

This thesis pursues to improve the GPU performance by acting on the GPU memory hierarchy. To this end, several steps have been carried out progressively. First, characterization study has been performed to provide a sound understanding on the main memory subsystem bottlenecks that impact on the performance of GPU applications. The main aim of this characterization study is to help improving the memory subsystem of modern GPUs. This study reveals identifies some critical memory subsystem components that need to be accurately modeled in recent simulators in order to provide solid and representative proposals. These components have been modeled in a state-of-the-art simulator and its validated by comparing them with those of a recent commercial GPU. This validation is required because, to the best of our knowledge, there is not any official published information about the GPU memory subsystem from major GPU manufacturers, such as AMD or Nvidia, that deals with GPU memory hierarchy microarchitectural details (e.g. miss management). Finally, a new approach that efficiently improves the performance of the GPU memory subsystem, and thus the overall GPU throughput, has been proposed. The proposal improves the management of the LLC cache misses, increasing both the MLP and the hit ratio. Moreover, it scales well both in terms of performance and energy consumption with larger GPUs. Note that although this thesis is focused on memory hierarchies from AMD GPUs, some of its contents are also useful for GPU caches and coherence protocols based on academic proposals like NMOESI.

# 1.2 Background

This section provides some background on the GPGPU programming model, the GPU architecture and memory subsystem, and the simulation framework used in this thesis.

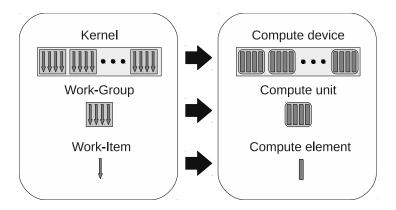

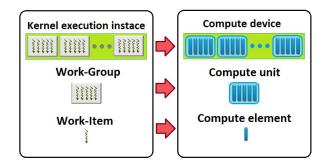

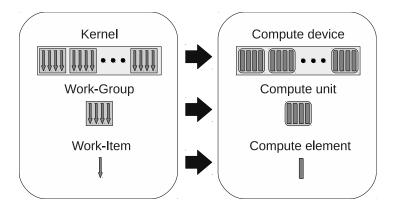

Figure 1.1: OpenCL platform and execution models.

# 1.2.1 OpenCL GPGPU programming model

There are two main GPGPU programming platforms and models, CUDA [52] from Nvidia and OpenCL [36] from the Khronos group. While CUDA is only supported by GPUs designed by Nvidia, OpenCL is, *de facto*, an industry standard programming model [66] and it is supported on devices from different brands such as Intel, AMD, ARM, or even Nvidia itself.

OpenCL defines a platform model, which is an abstraction of a real system where kernels are executed. The model comprises a hierarchy of Compute Devices (CDs), Compute Units (CUs), and Processing Elements (PEs), which refer to the GPU devices in the system, multicore units inside GPU devices, and cores that execute scalar operations, respectively. The platform model maps the execution model, where the executing threads are also organized in a hierarchical manner. Each individual thread, which is executed in a single PE, is defined as a work-item. Work-items are grouped in work-groups, which are mapped to CUs. Finally, a kernel executing in a GPU is composed of several work-groups. Figure 1.1 depicts a block diagram of both models and how they map each other.

### 1.2.2 Graphics Core Next microarchitecture

The experimental work developed on this dissertation has considered several GPU architectures from AMD: Southern Islands [68], Arctic-Islands [6, 5], and the most recent Vega [9, 7]. These GPU architectures implement different versions of the same Graphics Core Next (GCN) CU microarchitecture, introduced in 2012 by AMD. The microarchitecture has evolved in the last few years across these versions; for instance, the working frequency has steadily increased from 1GHz in Southern Islands up to 1.5GHz in Vega, but the basic GCN design have remained almost stable.

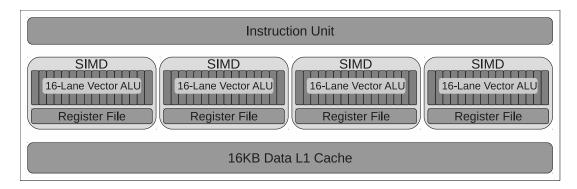

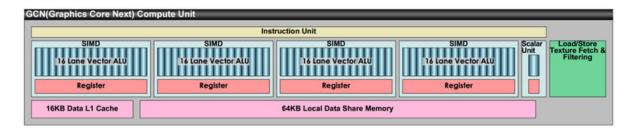

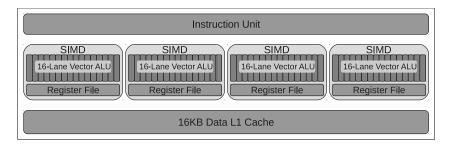

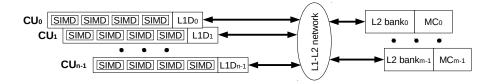

Figure 1.2: Graphics Core Next compute unit.

Figure 1.2 presents a block diagram of the GCN CU microarchitecture. A GCN CU consists of four 16-lane SIMD units; thus, it is capable of executing 64 work-items at the same time. In addition, a GCN CU includes several load/store units and a scalar unit to process scalar data.

Each kernel work-group is assigned to a specific SIMD unit, where it is executed. To be executed, the work-group is divided in 64-thread bundles, named *wavefronts*, consisting of 64 work-items. In turn, these wavefronts are subdivided in 4 sets composed of 16 work-items (also known as *subwavefronts*).

The instructions from the 64 work-items of a wavefront are executed in a lockstep manner. To do that, the SIMD unit executes sequentially the same instruction for the corresponding 4 subwavefronts. Therefore, the instruction (i.e. the entire wavefront) takes 4 cycles (i.e. one cycle per subwavefront) to execute.

To increase resource utilization and improve throughput, the GPU scheduler ensures that each SIMD unit is assigned tens of wavefronts, during most of the execution time of a kernel. SIMD units switch among wavefronts in a fine-grained multithreading manner, which helps hide the memory latencies.

### 1.2.3 Memory subsystem

Memory reference instructions are also executed following the SIMD paradigm; that is, a wavefront can generate up to 64 memory requests per memory reference. To reduce the overall amount of cache accesses, those requests addressing the same 64-byte cache block are *coalesced* into a single cache access, which is issued to the memory subsystem.

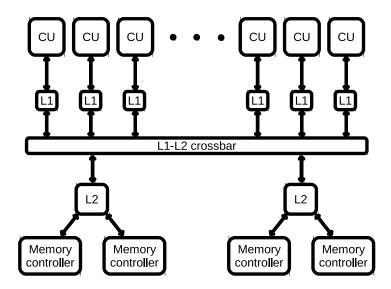

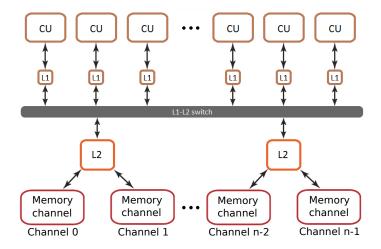

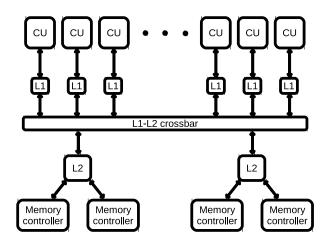

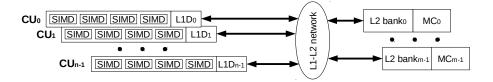

Figure 1.3: Memory hierarchy.

As in a conventional processor, the memory subsystem is organized hierarchically (see Figure 1.3). Those requests that miss the L1 cache are forwarded through an all-to-all crossbar switch to a multi-banked L2 cache, which acts as the LLC. Cache block addresses are interleaved among among L2 banks at a granularity of 256 bytes.

In the Southern Islands and Arctic Islands architectures, each bank is connected to a dual-channel memory controller that manages the corresponding off-chip GDDR5 main memory, while in the Vega architecture, the GDDR5 main memory modules are replaced with two stacks of the second version of the High Bandwidth Memory (HBM2) [31]. HBM2 is a a high-performance RAM interface for 3D-stacked DRAM from Samsung, AMD, and Hynix. This standard allows stacking up to 8 DRAM dies, each one with its own independent memory channel. In other words, each L2 bank in Vega architecture is directly connected to a single memory channel. This design reduces the number of channel conflicts and increases the memory bandwidth utilization.

# 1.2.4 Critical memory subsystem components

As mentioned above, in this thesis we identified critical memory subsystem components that have a significant impact on the system performance and whose accuracy is not properly modeled in state-of-the-art simulators. This section briefly discusses these components as background to help understanding the contribution.

# Vector memory instruction buffer

The GCN microarchitecture implements the Vector Memory-instruction Buffer (VMB) in the CU. This buffer keeps track of the memory instructions issued to the cache until all their associated memory operations finish. Using the VMB and other structures, GPU architectures implement mechanisms that group memory requests of the same type (load or store) targeting the same cache line in a single memory access, so reducing the effective number of memory accesses. This way greatly reduces the pressure on the memory hierarchy.

### Memory request coalescing and merging mechanisms

Two main approaches, namely coalescing and merging, can be found in modern GPUs to reduce the number of memory accesses. The coalescing approach combines all the requests of the same instruction targeting the same cache block into a single cache access in the CU just before issuing the instruction to the memory subsystem. For instance, the AMD Evergreen [2, 49] implements coalescing of both load and store instructions.

In contrast, the merging approach is implemented in the memory subsystem, decoupled from the CU. Merging is more flexible since it can applied to multiple memory requests regardless of whether they have been generated by the same memory instruction or not. Nevertheless, its use must be restricted to deal with memory coherence and memory consistency issues.

# MSHR file

GPUs generate a huge quantity of memory accesses, but only a limited number of pending cache requests can be supported simultaneously. For this purpose, current non-blocking caches implement Miss Status Holding Registers (MSHR) files. Upon a cache miss, the MSHR file is looked up to check if the target block is already being fetched. On such a case, the missing memory access is queued into the MSHR entry associated to the target block.

A single MSHR entry is in charge of tracking all the memory accesses associated to a given cache block (i.e., all the requests whose target address falls within the same block). Therefore, the maximum number of outstanding memory accesses is limited to the number of MSHR entries. Consequently, if all MSHR entries are busy and the missing cache block is not being fetched, the memory access is stalled until an MSHR entry is released.

### GPU cache coherence protocols

Cache coherence protocols were originally designed to support data coherence among caches in CPU multiprocessors. These protocols tolerate a moderate traffic of coherence requests, however, they are rather complex and would strangle the performance if they were directly applied to GPUs, mainly due to GPUs are designed to support a massive amount of memory requests generated by typical GPU applications. In short, neither GPUs nor heterogeneous CPU-GPU systems work properly with typical CPU protocols. To deal with this fact, alternative protocols have been devised both by the academia and the industry.

NMOESI coherence protocol. To support GPU cache coherence, Multi2Sim implements NMOESI, that extends the well-known MOESI protocol [67] implemented in a wide range of CPU multicores. NMOESI extends this protocol to support memory coherence in both CPU and GPU applications, and it is especially suited for heterogeneous CPU-GPU systems with a cache hierarchy shared among CUs and CPU cores. Under MOESI, a given cache block can be in one of five main states (M, O, E, S and I). NMOESI extends this protocol by adding a new non-coherent state (N) to be used in GPUs. This state avoids that non-coherent write requests, which are common in GPU applications, generate coherence traffic.

SI protocol. The protocol deployed in the Southern Islands (SI) GPU family, hereafter SI protocol, supports a relaxed memory consistency model based on Release Consistency [26]. This consistency model allows the compiler to specify when data modifications performed by a given CU must be visible to other CUs, which enables the implementation of simpler coherence protocols. To support the consistency model, the opcode of a SI memory instruction includes 2 bits called GLC (Global Coherent) and SLC (System Level Coherent), which indicate the coherency scope.

### Memory controller

As conventional DDR SDRAM memories, Graphics DDR (GDDR) memory contain multiple independent DRAM banks. A bank is implemented as a matrix of DRAM cells. When a bank is accessed, the entire row also referred to as memory page, is accessed. The accessed memory page is stored in the DRAM sense amplifiers associated to the bank, also referred to as row buffer.

The memory controller uses three commands that are issued sequentially to a bank in order to access the target data [38]. First, the *precharge* command writes back the row content to the bank, and then precharges the row bitlines for accessing the target row. Second, the *activate* command reads the target row and stores its information into the row buffer. Finally, the *read/write* command reads or write the requested data in the row buffer. After issuing the last command, the memory controller can either keep the accessed memory page in the row buffer (open page policy) or close the row buffer by issuing a precharge command (closed page policy). Depending on the implemented page policy, the latency of the next access varies. For example, with an open page policy, if the requested block is already present in the row buffer (i.e., a row buffer hit), only a read/write command needs to be issued by the memory controller, thus the latency can be significantly reduced. However, a row buffer miss would require to serialize the issuing of the three mentioned commands, roughly trebling the latency of a row buffer hit.

# Off-chip GDDR memory

The memory bus is used to read from or write to the memory device. In conventional DDR memories, the memory bus 64-bit width, while in GDDR memories this width is typically 32 bits. Since the typical cache block size is 64 bytes, transferring a cache block through the data bus doubles the number of transfers over DDR memories.

An option to reduce the total transfer time would be the use of a wider memory bus. Since GDDR devices are standardized to a 32-bit bus, working with a wider memory bus would require multiple memory devices to operate in lockstep. For example, the Intel i875P memory controller connects through a 128-bit memory data bus to matching pairs of 64-bit wide DIMMs (Dual In-Line Memory Modules). This paired DIMM configuration is often referred to as dual channel configuration [30].

# 1.2.5 GPU simulators

In comparison with CPU research simulators, the number of available GPU simulators is much lower. Moreover, existing GPU simulators are relatively recent and still maturing. The main causes of this situation are the lack of documentation provided by GPU manufacturers and the fast evolution of GPU architectures, which complicates the development of GPU simulators, since it requires stable and well-known architecture models.

Nevertheless, due to the growing use of GPUs, some GPU simulation frameworks have become recently available. Among them, it is worth mentioning GPGPU-Sim [23, 11] and Barra [22]. GPGPU-Sim is currently one of the most referenced GPU simulators and models a GPU microarchitecture that resembles the Nvidia GeForce 8x, 9x, and Fermi series. However, due to its dependence on Nvidia drivers, which only support OpenCL 1.1, GPGPU-Sim does not provide support for the execution of GPGPU benchmark suites like those provided by AMD [3] with modern OpenCL code. On the other hand, Barra is a parallel GPU simulator that implements both a CUDA driver emulator and an Nvidia Tesla GPU simulator. Unfortunately, Barra does not model the GPU microarchitecture, thus it cannot be used for the purposes of this thesis, which requires the evaluation of possible enhancements in the memory subsystem.

In this thesis, the Multi2Sim [73, 72] simulation framework has been selected as the main experimental platform. Multi2Sim is an accurate cycle-by-cycle execution-driven simulator for CPU-GPU heterogeneous computing. Release and development versions of Multi2Sim are available. It provides a fully configurable memory subsystem with several cache levels and interconnection network. Multi2Sim implements several GPU architectures from both AMD (e.g., Evergreen and Southern Islands) and Nvidia (e.g., Fermi) as well as CPU architectures like x86, MIPS-32 and ARM. The Multi2Sim developer team is currently modeling the HSA heterogeneous architecture [1], where CPU and GPU share the same memory subsystem. Finally, Multi2Sim includes its own implementation of OpenCL and CUDA libraries. In this way, it can provide dynamic information about CPU-GPU interaction by instrumenting OpenCL and CUDA calls.

# 1.3 Thesis Objectives

The general objective of this dissertation is improving current GPU memory subsystems in order to increase the overall system performance when executing GPGPU applications.

For this purpose, we need first to characterize the behavior and demands of GPGPU applications from the memory hierarchy point of view, as well as the impact of this hierarchy on performance. This study will provide insights on the main performance bottlenecks on the memory hierarchy. Based on this study new approaches will be devised to remove or mitigate the identified bottlenecks. After that, we need to implement the devised approaches in a state of the art simulator modeling recent GPU architectures. To this end, we need to update existing simulators to accurately modeling the GPU memory subsystem of current GPU architectures.

In short, this thesis pursues as a key objective the design of an efficient memory hierarchy management approach to boost the performance of GPGPU applications, which needs from the previous achievement of two sub-objectives: i) a detailed characterization study relating the impact of the memory hierarchy on the performance, ii) extending state-of-the-art simulators to accurately modeling current GPUs.

# 1.4 Contributions

This thesis makes three main contributions, each one addressing a specific sub-objective, discussed below:

- A characterization is performed in order to better understand the behaviour of GPGPU applications. The study modifies the underlying coherence protocols and the size of the MSHR file, which directly affects the available Memory Level Parallelism (MLP).

- The accuracy of a state-of-the-art GPU simulator is improved and validated by modeling several critical memory subsystem components and extending the models of existing ones.

The results have been validated against those obtained with a real commercial GPU.

- A new proposal that improves the performance of GPU memory subsystems is presented.

The proposed approach raises the GPU computational power by unclogging the LLC miss management and improving the hit ratio. It can scale to the largest GPUs from AMD while reducing the energy consumption of the memory hierarchy.

# 1.5 Outline

Following the UPV rules, this thesis has been written as a compendium of articles. Therefore, the rest of this thesis is organized as follows:

Chapters 2 to 6 present the scientific publications derived from the work performed in this thesis. They have been adapted to the required formatting style.

In Chapter 7, a general discussion of the results of the main contributions of this thesis is given.

Finally, in Chapter 8, some conclusions and ideas for future work are presented.

# Chapter 2

# Impact of Memory-Level Parallelism on the Performance of GPU Coherence Protocols

- Authors: Francisco Candel, Salvador Petit, Julio Sahuquillo, José Duato

- Type: Conference

- Conference: 24th Euromicro International Conference on Parallel, Distributed, and Network-Based Processing (PDP)

- Location: Heraklion, Greece

- Year: 2016

- **DOI:** 10.1109/PDP.2016.67

# 2.1 Abstract

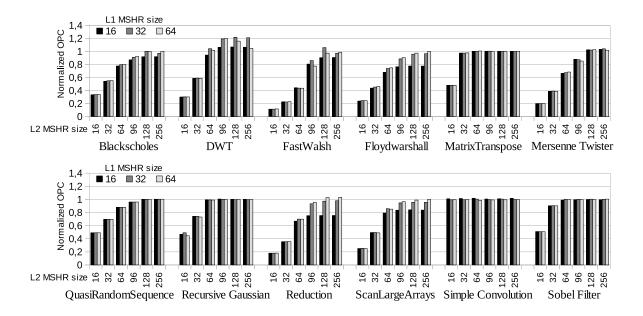

Graphics Processing Units (GPUs) are being implemented in heterogeneous CPU/GPU systems due their high efficiency when executing massively parallel applications. New challenges appear to deal with heterogenous coherence in these systems due to the huge amount (hundreds or thousands) of on-going memory requests of GPUs, which is limited by the Miss Status Holding Register (MSHR) file size associated to the L1 cache. This paper analyzes how the number of MSHRs i) affects to typical memory performance metrics and ii) impacts on the system performance under two recent GPU coherence protocols, called NMOESI and SI (Southern Islands), which introduce distinct coherence traffic. We find two key findings that can help improve the performance of coherence protocols. First, there is a strong correlation between system performance and memory subsystem latency regardless of the used protocol. Second, system performance varies with the number of supported cache misses; however, counterintuitively, supporting more cache misses does not always bring enhanced performance but it can turn into performance drops.

# 2.2 Introduction

Nowadays, heterogeneous CPU/GPU processors are being introduced in the market. These systems combine CPU with GPU computing capabilities [21]. The CPU is used to accelerate the execution of the sequential part of the applications, while the GPU allow the execution of a massive number of threads in parallel.

This paper studies the impact on performance of the supported MLP (Memory level paralelism) by GPU considering both GPU and CPU coherence protocols. For this purpose, we first characterize the behavior of GPGPU (General Purpose GPU) applications increasing the supported MLP up to 256 memory requests. This study is done in two state-of-the-art GPU coherence protocols: NMOESI from the academia and Southern Islands (SI) from AMD.

Two important findings are presented that can help improve existing GPU protocol designs. First, unlike CPU memory systems, we find that a higher number of MSHRs can rise cache and memory contention, which can turn into performance drops in some applications. Consequently, in this paper we claim that GPU systems must support a configurable MSHR file size for better performance. Second, huge memory latencies (by 2K processor cycles) cannot be hidden even by the massive thread parallelism of current GPUs. Thus, latency values higher than

Figure 2.1: Southern Islands memory hierarchy.

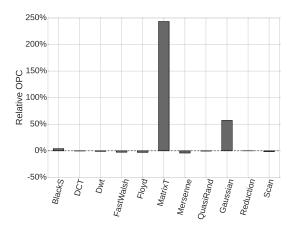

this threshold present an inverse correlation with performance. Finally, we also show that specific GPU protocols are required since both NMOESI and SI protocols provide performance improvements up to  $4\times$  over MOESI.

# 2.3 GPU Architecture

Southern Islands family [8] was the first GPU implementing the AMD's Graphics Core Next (GCN) architecture [68]. Its memory subsystem consists of 3 memory levels as depicted in Figure 2.1: first-level caches, second-level caches, and main memory. All these levels work with a 64-byte block size. The first level cache is composed of data caches (read-write), instruction caches (read-only), and constant caches (read-only). L1-instruction and L1-data caches are private to each Compute Unit (CU), while each constant cache is shared by a group of 4 CUs. L2 is composed of a single cache partitioned into modules, each of them connected to a different dual-channel main memory controller. L1 caches and L2 modules are connected through a crossbar. Finally, depending on the specific card model, main memory is divided into 4, 8, or 12 GDDR5 memory modules.

# 2.4 Axes of Characterization

This section summarizes the main features of the memory protocols studied in this paper and describes the MSHR file. Both elements of the system are used in the next section to characterize the memory behavior of GPU kernels, since as experimental results will show, the overall system performance strongly depends on them.

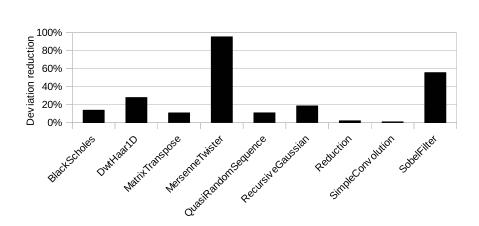

Figure 2.2: Speedup of SI and NMOESI with respect to MOESI varying the MSHR file size.

### A. Coherence protocols

**MOESI:** Currently, MOESI is the protocol commonly implemented to guarantee cache coherence in conventional CPU processors. Under this protocol, a given cache block can be in one of five different states (M,O,E,S and I).

**NMOESI:** This protocol is an extension of MOESI proposed by Multi2Sim team to improve the performance of MOESI in GPU memory systems. A new state N is added to save unnecessary coherence traffic caused by *non-coherent* blocks. When a GPU write access is issued, the requested block is brought to L1 and its state is set to N without invalidating other copies of the block. Thus, multiple non-coherent copies of the same block are allowed in different L1 caches. Then, when a block in state N is replaced, –the part of the block that has been locally modified— is updated in L2, which properly combines the modifications of individual CUs.

SI: This protocol refers to our implementation of the coherence protocol deployed in the Southern Islands GPUs family, which has been implemented based on the oficial SI instruction set architecture [8].

# B. Miss status holding registers

Miss Status Holding Registers (MSHRs) are used in non-blocking caches to handle multiple memory accesses at the same time. Each MSHR records all inflight accesses to a specific block. Therefore, the maximum number of inflight requests is limited by the number of available MSHRs. In this work we vary the MSHR file size of L1 caches to control the available number of blocks being fetched (i.e. MLP) [15].

# 2.5 Experimental Evaluation

Experimental results have been obtained with the Multi2Sim simulation tool[72]. Multi2Sim is a detailed simulator for heterogeneous CPU/GPU systems. It provides cycle-accurate simulation of the processor pipeline and memory subsystem. Multi2Sim supports the MOESI (baseline in our experiments) and NMOESI protocols, and we extended it to support the SI protocol implemented in recent GPUs. The experiments have been carried out with the OpenCL SDK 2.5 benchmarks [3].

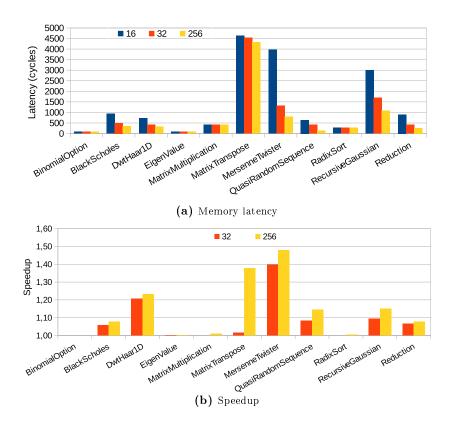

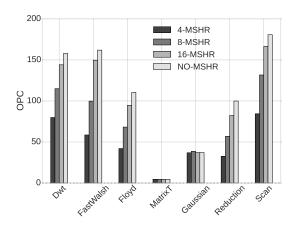

The GPU configuration is shown in Table 2.1, which represents the AMD HD 7770 GPU.

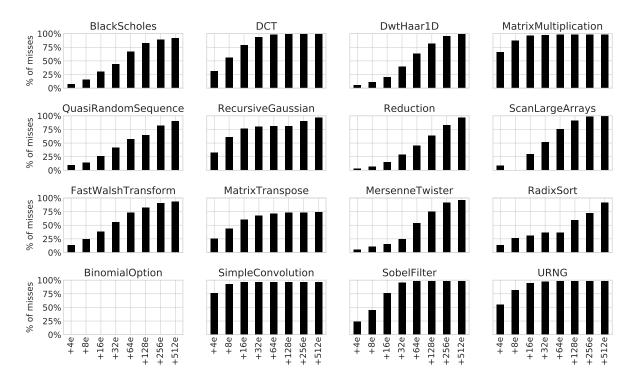

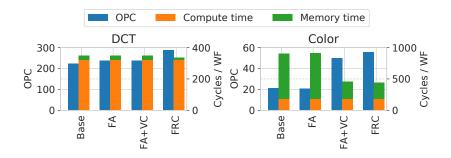

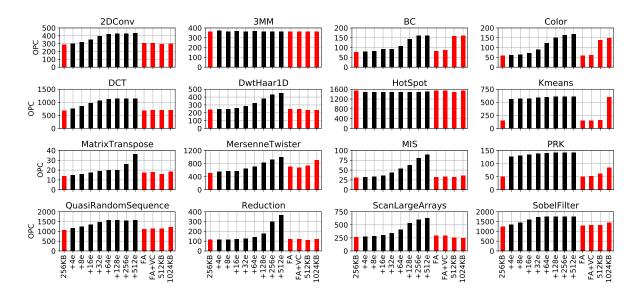

### A. Performance of SI and NMOESI with respect to MOESI

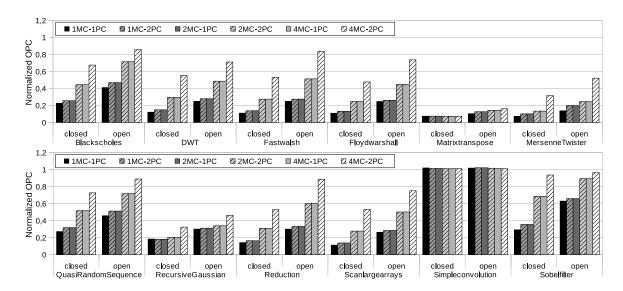

This section studies the effect of limiting the MLP on the system performance under the SI and NMOESI protocols. For this experiment, we increase the L1 MSHR file size from 32 to 64 and up to 256 entries. Figure 2.2 presents the speedup of the studied benchmarks for each protocol and MSHR configuration with respect to MOESI with 256 MSHRs. As observed, both NMOESI and SI obtain significant performance enhancements in 6 of 10 benchmarks. In general, compared to MOESI, both NMOESI and SI achieve better performance.

The MSHR file size does not equally affect to NMOESI and SI protocols; but depending on the protocol and the application, a high number of MSHRs (e.g. MatrixTranspose with SI) or a low number achieves the best performance. In general, SI (see Figure 2.2a) achieves higher performance benefits as the number of MSHR entries increases. That is, this protocol should be deployed with a high number of MSHRs. In contrast, Figure 2.2b shows that the optimal MSHR file size for NMOESI varies with the application. NMOESI, however, achieves in general its poorest performance with a 256 MSHR file size, and improves as the number of supported misses is constrained. To remark that when the number of MSHRs is significantly reduced, NMOESI's performance can be also affected due to the constrained MLP (e.g., DwtHaar1D). In

GCN & Memory subsystem configuration Compute Units 10 10 Work-groups per CU Wavefronts per wrok-group 4 Work-items per wavefront 64 SIMD units per CU 4 LRU, 64B-lines, 2 ports All caches L1 caches 16KB, 4 ways, 1 cicle L1 texture cache 1 cache per CU

2 modules, 128KB per module,

16 ways, 10 cycles

2 channels per L2 module,

100 cycles

Table 2.1: GCN configuration and memory subsystem.

contrast, SI shows a scalable behavior, improving its performance as the number of MSHRs is increased.

L2 caches

Main memory

Overall, NMOESI offers the best performance for standard MSHR file sizes (e.g., 16 entries) in half of the studied applications. However, in some applications like BlackScholes, this protocol presents worse performance than SI regardless of the MSHR file size.

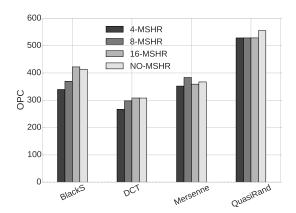

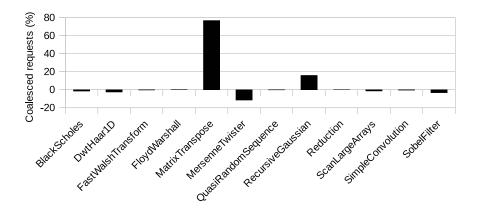

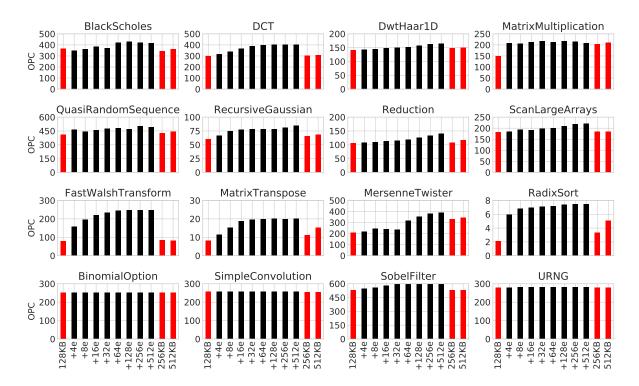

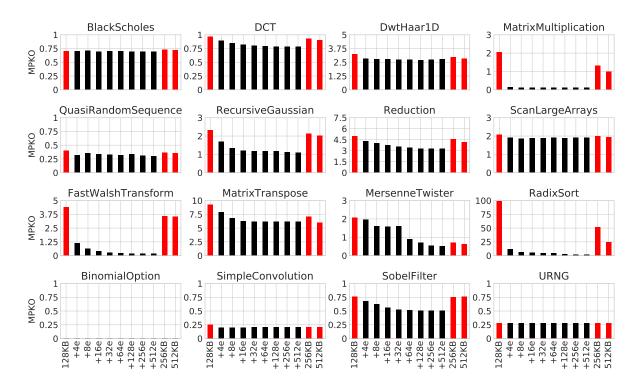

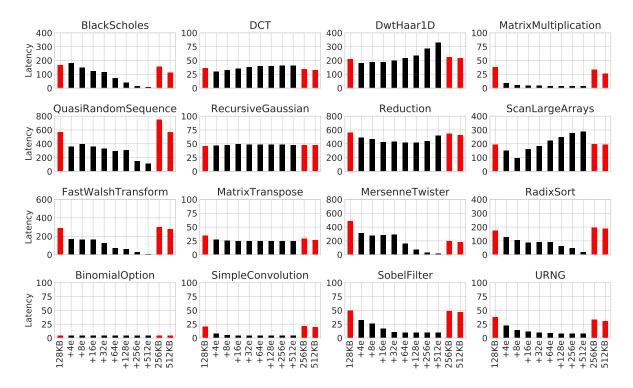

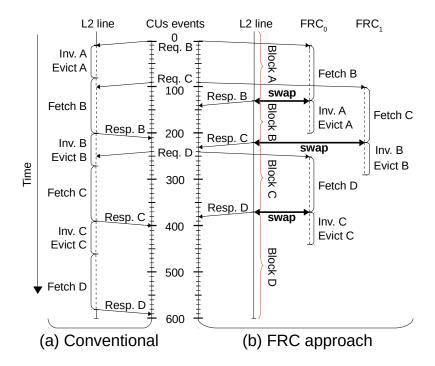

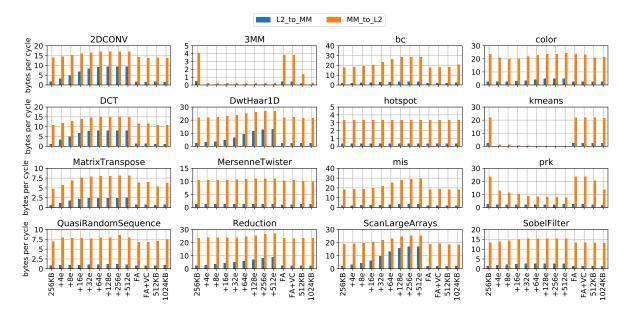

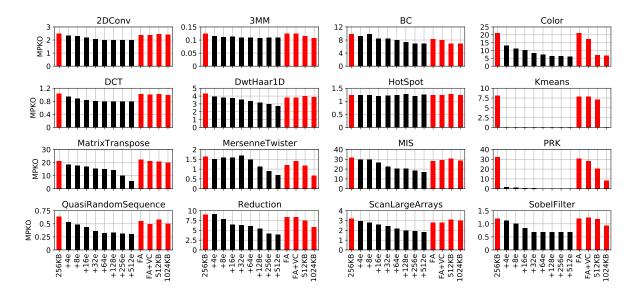

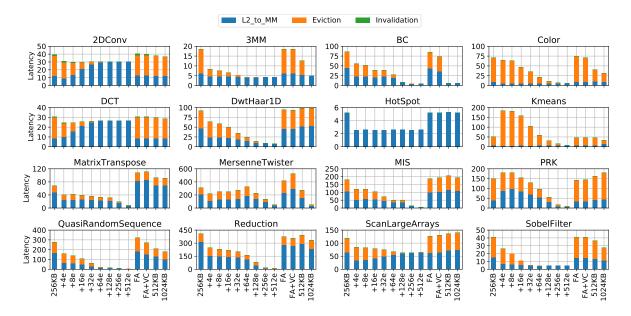

# B. Benchmark characterization

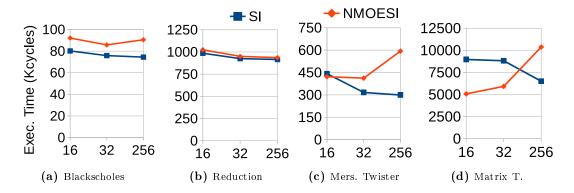

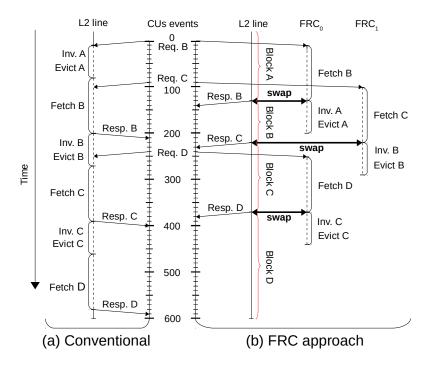

The supported MLP affects in a different way the applications performance depending on the deployed protocol. In this section, we analyze the execution time of the studied benchmarks and classify them into four categories. As example, Figure 2.3 presents the execution time for a benchmark in each category. Next, we present these categories.

SI always better: This category includes those benchmarks where SI achieves better performance than NMOESI regardless of the MSHR file size. This is the case of BlackScholes (see Figure 2.3a).

**Similar behavior:** This category includes those benchmarks where both protocols present similar performance when varying the MSHR file size. Figure 2.3b shows **Reduction** as example.

SI better for large MSHR file sizes: In some benchmarks, both protocols present similar performance for a small number of MSHRs, but differences appear as the MSHR file size in-

Figure 2.3: Execution time of NMOESI and SI for each benchmark category.

Figure 2.4: Memory latency of NMOESI and SI for each benchmark category.

creases (see Figure 2.3c).

NMOESI better for small MSHR file sizes: This caterogy includes benchmarks, like MatrixTranspose (see Figure 2.3d), where NMOESI with small number of MSHRs achieves better performance, but when the number of MSHRs is increased the SI protocol becomes the best protocol.

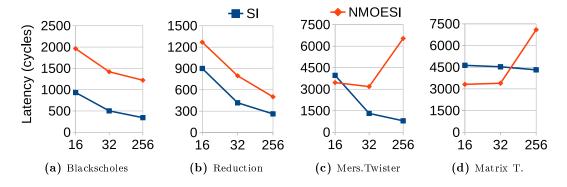

To provide a sound understanding of the relationship between execution time and MLP we analyzed multiple memory related metrics such as hit ratio, Misses Per Kilo Instructions (MPKI), and memory access latency. We found that memory latency is the metric that better explains changes in performance due to the low temporal locality and high parallelism of some benchmarks.

Regarding memory latency, remark that GPU memory instructions affect a whole vector of data items, thus potentially generating multiple memory accesses. In addition, current GPU architectures execute instructions belonging to the same wavefront in order. In other words, a GPU must wait for all the accesses generated by a given GPU memory instruction to complete before issuing subsequent instructions. Taken into account this behavior, the latency presented

Figure 2.5: SI performance varying the MSHR file size over 16 MSHRs.

by a given memory instruction has been quantified as the maximum latency among all its generated memory accesses; i.e. the maximum latency per vector instruction. We feel that these values accurately reflect what happens in this scenario so we used them to focus the analysis.

Figure 2.4 presents, for the applications representing the four categories, the average of this maximum latency per vector instruction for the NMOESI and SI protocols varying the MSHR file size. Compared to the previous execution time plots, it can be observed that a significant latency reduction does not necessarily reduce the execution time. This is due to the latency-hiding capabilities of GPUs, which come from the fact that application's work-groups are executed following a time-multiplexing manner. In short, in order to latency savings affect the performance, the original memory latency must be higher than a given threshold. For instance, in Reduction (Figure 2.4b) a 256-MSHR file reduces latency more than half over 16 MSHRs in both protocols but the execution time is barely affected. Moreover, SI allows by 40% more latency savings than MOESI and, again, this latency improvement does not significantly reduce the execution time. A similar effect can be observed in BlackScholes (Figure 2.4a). In contrast, latency plots of MersenneTwister (Figure 2.4c) and MatrixTranspose (Figure 2.4d) show a similar shape as their corresponding plot in Figure 2.3.

Figure 2.6: NMOESI performance varying the MSHR file size over 16 MSHRs.

In summary, we can conclude that the average maximum latency per GPU memory instruction is a good indicator of the expected performance behavior in these applications. The main cause is that their memory latencies are, in general, much higher (by 8 thousand cycles) and cannot be hidden by the GPU microarchitecture.

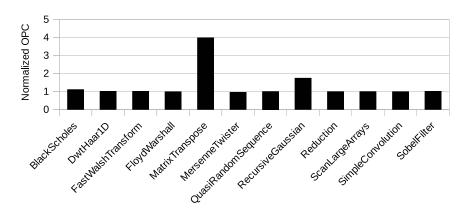

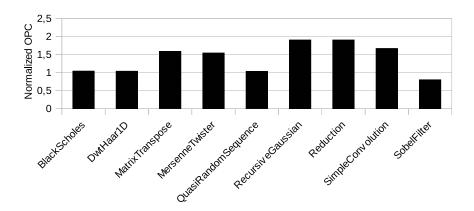

## C. Analyzing the relationship between memory latency and performance in SI and NMOESI

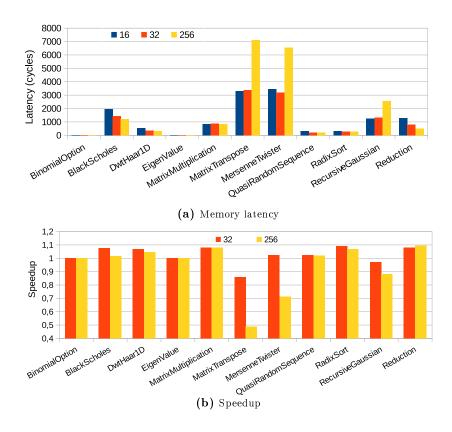

Figures 2.5 and 2.6 present the memory latency (upper plots) and performance (lower plots) under the SI and NMOESI protocols, respectively, varying the MSHR file size. In all the plots it has been used the same protocol with a 16-entry MSHR as baseline. This way allows study how performance is affected by memory latency.

It can be appreciated a high correlation between memory latency variations and performance in both protocols. This correlation is much stronger for high memory latencies (by above 1000 cycles). For instance, BinomialOption performance does not vary when changing the protocol. This is because all the studied configurations successfully hide the memory latency, which is very low. This is also the case of EigenValue, which presents a very low latency in both NMOESI and SI, thanks to its high L1 hit ratio (by 99%). On the other hand, the performance of Matrixtranspose, MersenneTwister, and RecursiveGaussian clearly depends

on the huge memory latencies. In SI, these latencies decrease with the number of MSHRs, which turn into performance improvements. However, the results for the same applications with NMOESI present a noticeable latency increase as the MSHR file size grows, being 16 or 32 MSHRs—depending on the application—, the best configurations for this protocol.

In summary, NMOESI works in general better in configurations with few MSHRs, whereas SI improves its performance with large MSHR files (e.g. 256 entries). On the other hand, SI allows obtaining better memory latencies due to its lack of coherence messages, which enables fast invalidations of blocks.

# 2.6 Related Work

This section relates important work focusing on caches and protocols for GPUs. Regarding caches, an interesting study analyzing the benefits of cache memories versus scratchpad memories is presented in [33]. This study concludes that some applications improve their performance with cache memories, while the performance may significantly drop in others applications. One possible solution would be to design adaptive memory structures that behave differently depending on the workload characteristics. Regarding coherence protocols, it is known that they should deal with the massively parallel computing capabilities of GPUs. Protocols were originally designed for typical processors having a relatively few number of cache misses at any point in time. Therefore, when they work on GPUs with thousands of requests in flight, they are easily saturated, with the consequent performance loss. In [58], it is presented a coherence protocol that avoids that a massive number of memory accesses saturate the protocol directory. In [65], authors propose a directoryless protocol, which is one of the major performance bottlenecks. The order in which the large amount of memory transactions are processed in the GPU also can significantly affect the performance. In [32], a technique to reorder memory accesses is presented. In [48], reordering requests is also investigated, but focusing on L2 and main memory.

# 2.7 Conclusions

This paper has shown that coherence protocols especially designed for GPU memory subsystems can accelerate up to 4 times the performance of some applications compared to conventional coherence protocols. Nevertheless, unlike CPU memory subsystems, allowing a higher level of memory level parallelism (i.e. increasing the MSHR file size) can reduce the system performance. This behavior is due to the memory protocol induced contention and can widely vary with the application. In addition, this paper demostrates that: i) the potential negative effect of the protocol on performance can be detected by measuring the maximum latency per vector instruction, and ii) the best MSHR file size depends on the running GPU kernel and the underlying memory protocol.

### Chapter 3

# Accurately Modeling the GPU Memory Subsystem

- Authors: Francisco Candel, Salvador Petit, Julio Sahuquillo, José Duato

- Type: Conference

- Conference: The 2015 International Conference on High Performance Computing & Simulation (HPCS)

- Location: Amsterdam, Holland

- Year: 2015

- **DOI:** 10.1109/HPCSim.2015.7237038

#### 3.1 Abstract

Nowadays, research on GPU processor architecture is extraordinarily active since these architectures offer much more performance per watt than CPU architectures. This is the main reason why massive deployment of GPU multiprocessors is considered one of the most feasible solutions to attain exascale computing capabilities. In this context, ongoing GPU architecture research is required to improve GPU programmability as well as to integrate CPU and GPU cores in the same die.

One of the most important research topics in current GPUs, is the GPU memory hierarchy, since its design goals are very different from those of conventional CPU memory hierarchies. To explore novel designs to better support General Purpose computing in GPUs (GPGPU computing) as well as to improve the performance of GPU and CPU/GPU systems, researchers often require advanced microarchitectural simulators with detailed models of the memory subsystem.

Nevertheless, due to fast speed at which current GPU architectures evolve, simulation accuracy of existing state-of-the-art simulators suffers. This paper focuses on accurately modeling the GPU memory subsystem. We identified three main aspects that should be modeled with more accuracy: i) miss status holding registers, ii) coalescing vector memory requests, and iii) non-blocking GPU stores. In this sense, we extend the Multi2Sim heterogeneous CPU/GPU processor simulator to model these aspects with enough accuracy. Experimental results show that if these aspects are not considered in the simulation framework, performance deviations can rise in some applications up to 70%, 75%, and 60%, respectively.

#### 3.2 Introduction

In the recent years there have been an steady increase in the use of GPUs (Graphics Processing Units) for general purpose computing. The main cause is due to General Purpose computing in GPUs or simply GPGPU computing is much more energy-efficient than conventional computing. That is, for the same energy budget, it can provide higher computational power, especially in the execution of massively parallel workloads. Because of this fact, most supercomputers in the top 10 of the top 500 list [71] implement GPUs. For instance, the Titan supercomputer, ranged in second place of the top 500 list in november 2014, was built with Nvidia K20x devices; and the top one, Titanhe-2 was deployed with the Intel Xeon Phi, which incorporates a large graphic unit that occupies a significant part of its layout. However, GPU programmability is

still harder than that of conventional computing. To deal with this fact, computer architects are trying to adapt different techniques (e.g. caches and prefetching) that have successfully worked on CPUs to ease programmability and also increase their computational power.

The huge computational power of GPUs comes from implementing hundreds of processing elements that work in parallel. To keep busy all these processing elements with data, memory accesses must be properly handled. This means that the memory hierarchy must provide much more bandwidth than the memory hierarchy of conventional CPU multicores. On the other hand, GPU applications are characterized by their massive parallelism applications (they are usually composed of thousands of logical threads). Based on this fact, the memory hierarchy in the GPU is not designed to reduce latencies as in the CPU but to tolerate a high number of concurrent accesses. This way allows to hide most of the main memory latencies.

The importance of easing the programmability of GPUs for GPGPU computing, as well as the integration in the same chip of CPU and GPU cores (i.e., heterogeneous multicores), which present very different memory hierarchy designs, is driving GPU memory hierarchy research at this moment. To explore and evaluate new proposals and enhancements on the memory subsystem, researchers use complex and detailed simulation frameworks. These software packages are abstractions of the real hardware and model its functionality, concentrating on those hardware components that have a significant impact on the system performance.

However, due to the fast speed at which current systems evolve, as well as their high complexity, simulation accuracy is not always as good as it should. For this purpose, and in order to get representative results, simulators should be continuously updated to reflect the behavior of the real hardware and capture its impact on performance. On the other hand, research on heterogeneous multicores requires from powerful simulation environments that usually model a generic system that often miss significant specific details of GPU architectures.

This paper focuses on enhancing the model of the GPU memory subsystem in the Multi2Sim simulation framework, which is widely used across the scientific community and the academia. Multi2Sim simulates the newest AMD GPU architectures in detail and allows users to configure internal architectural parameters, the characteristics of the modules of the cache hierarchy, as well as the interconnection network. Unfortunately, some parts of the memory subsystem that, as experimental results will show, have a high impact on GPU performance are not accurately modeled, leading sometimes to important performance deviations.

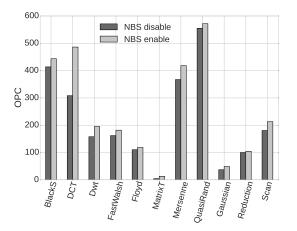

In particular, this paper enhances the Multi2Sim accuracy by modeling three key aspects of current GPU memory subsystems: i) the Miss Status Holding Register (MSHR) file, ii) a coalescing unit at the processor pipeline of the memory requests generated by vector memory instructions, and iii) non-blocking GPU store instructions. The first mechanism allows estimating the effect of the MSHR file on performance. The second Multi2Sim extension coalesces the memory requests issued by the same vector memory instruction at the processor pipeline level, which provides a more realistic model of the memory access patterns affecting the memory subsystem. Finally, the third enhancement avoids the GPU processor pipeline to be blocked when a vector store instruction is located at the head of the vector memory buffer.

Experimental results show that: i) modeling the MSHR file can reduce the performance up to 3 times with respect to assuming an unbounded MSHR file; ii) coalescing at the processor pipeline can speedup the execution time higher than 30% in some applications; iii) non-blocking stores improve the performance across all the studied benchmarks and up to 60% in some cases. In summary, not modeling these realistic hardware mechanisms can result in important performance deviations.

The remainder of this work is organized as follows. Section 3.3 presents a relevant subset of current GPU simulators. Section 3.4 describes the Southern Islands architecture and its programming model. In Section 3.5, the proposed Multi2Sim extensions are described in detail. Section 3.6 presents the experimental results. Finally, in Section 3.7 some concluding remarks are drawn.

#### 3.3 Related Work

GPU research simulators are relatively young and still maturating. In fact, the number of available GPU simulation frameworks is nowadays much lower than that of CPU simulators. The main reasons of this lack of tools is the few information given by GPU manufacturers as well as the fact that the architecture of modern GPUs has been and is quickly evolving, hampering the design of GPU simulators which require an established and well-known architecture model. In spite of this fact, due to the growing use of GPUs, some GPU simulation frameworks have become recently available. Below, we describe a representative set of them.

GPGPU-Sim [23, 11] is currently one of the most referenced GPU simulators. It is a detailed cycle by cycle simulator that supports CUDA version 3.1. It models a GPU microarchitecture similar as the Nvidia GeForce 8x, 9x, and Fermi series. GPGPU-Sim also simulates the

interconnection network between SIMT cores and memory modules. Recently, the Gem5 [12] discrete event driven computer system simulator platform was combined with GPGPU-Sim to implement a full heterogenous system simulator. Moreover, GPGPU-Sim version 3.2.0 and later integrate GPUWattch [39] as well, an energy model based upon McPAT [42]. However, due to its dependence on Nvidia drivers, which only support OpenCL 1.1, GPGPU-Sim is not appropriate to evaluate GPGPU benchmark suites like that provided by AMD [3] with modern OpenCL code.

Barra [22] is a parallel GPU functional simulator. It is based in the UNISIM framework [10] and implements both a CUDA driver emulator and a Nvidia Tesla GPU simulator. In this way, Barra can execute directly unmodified CUDA programs and generate statistics at the instruction level. However, presents two main shortcomings. It only supports CUDA 2.2 while nowadays Nvidia has already launched CUDA 7. In addition, Barra does not simulate the GPU microarchitecture, thus it does not provide support to evaluate possible enhancements in the memory subsystem.

Multi2Sim [73, 72] is an accurate cycle by cycle execution driven simulation framework for CPU-GPU heterogeneous computing. Release and development versions of multi2sim are available. It provides a fully configurable memory subsystem with several cache levels and interconnection network. Multi2Sim implements several GPU architectures from both AMD (Evergreen, Southern Islands) and Nvidia (Fermi) as well as CPU architectures like x86, MIPS-32 and ARM. The Multi2Sim developer team is currently modeling the HSA heterogeneous architecture [1], where CPU and GPU share the same memory subsystem. Finally, Multi2Sim includes its own implementation of OpenCL and CUDA libraries. In this way, it can provide dynamic information about CPU-GPU interaction by instrumenting OpenCL and CUDA calls.

In summary, we chose Multi2Sim since it i) simulates a full system cycle by cycle, ii) implements the recent AMD GPU core architectures called GCN [68], iii) includes its own OpenCL and CUDA libraries, and iv) support for HSA architecture is being developed.

# 3.4 Southern Islands GPU Architecture and Programming Model

This section describes the architecture and programming model of a recent GPU to illustrate how GPUs work. For this purpose, we selected the Southern Islands GPU from AMD, presented

Figure 3.1: OpenCL relation between platform and execution models

Figure 3.2: Graphics Core Next microarchitecture. Source: Hiroshige Goto (PC Watch)

in 2012, and modeled by Multi2Sim. This GPU is internally implemented with distinct cores that share the memory subsystem. The architecture of the cores and the memory subsystem are described below. In addition, the OpenCL framework, which is used to program the Southern Islands GPU, is also introduced.

#### 3.4.1 OpenCL Framework

There are two main frameworks for GPGPU programming: CUDA from Nvidia and OpenCL from the Khronos group. While CUDA only is supported by GPUs manufactured by Nvidia, there are OpenCL implementations that work on devices from different brands such as Intel, AMD, ARM, or even Nvidia.

The platform model defines the concepts of *Compute Device*, *Compute Unit* (CU), and *Processing Element* (PE) to refer to whole GPU chip, an individual GPU core, and the computing node within the core where the thread is allocated to, respectively, as illustrated in Figure 3.1.

The OpenCL execution model defines several levels of thread organizations. An individual thread is defined as a *Work-Item*, which are clustered in *Work-Groups*. A given GPU application (also known as a *Kernel*) is composed of several work-groups. Figure 3.1 depicts the relationship between the platform and execution models.

#### 3.4.2 Graphics Core Next Microarchitecture

A Southern Islands GPU can include up to 32 CUs implementing the AMD's Graphics Core Next (GCN) microarchitecture. A GCN compute unit is capable of executing 64 work-items in parallel. Together, these 64 work-items are named a wavefront and execute instructions in lockstep. Thus, at a given point in time, the 64 work-items composing a wavefront are executing the same instruction on multiple data (SIMD).

The SIMD hardware in a CU is divided in 4 16-lane vector ALUs (see Figure 3.2). Each vector ALU is in charge of executing 16 work-items or a *subwavefront*. In addition, a GCN compute unit also includes a scalar unit and several load/store units.

#### 3.4.3 Memory Subsystem

In Southern Islands GPUs, the 64 memory requests generated by a vector load instruction are coalesced before accessing the memory subsystem. The coalescing mechanism combines in the same memory access those load requests that reference the same cache line. In this way, the number of potential memory accesses is highly reduced. Regarding store instructions, they are not coalesced in the same way that load instructions, but merged once they arrive to the memory queues accessing the different memory and cache modules. Remark that the above management distinction between load and store instructions is specific to the Southern Islands architecture. Other GPU architectures (e.g., AMD's Evergreen family [49]) do not present this management.

Once the memory requests have been coalesced, they are issued to a 16KB L1 data cache (see Figure 3.2), which represents the first level of the memory hierarchy. Only those accesses that miss in the L1 cache access the multi-banked L2 cache through an all-to-all crossbar switch. In addition, the CU has a 64KB Local Data Share (LDS) memory.

L2 banks are address interleaved and connected to main memory modules with private (one per L2 bank) 64-bit wide dual channel memory controllers. Southern Islands GPUs may include up to 6 of these memory controllers. Thus, up to 12 DRAM modules can be installed in the system.

#### 3.5 Proposed Multi2Sim GPU Extensions

Multi2Sim GPU memory subsystem model shares the same source code as its CPU counterpart. This way, which eases the modeling of heterogeneous CPU-GPU processors and allows a more generic implementation, is one of the main reasons due to some particular aspects of GPUs are not modeled with enough detail or in a more accurate way (e.g., coalescing vector load requests in the CU pipelines versus merging them in the memory queues). As we show in Section 3.6, these variations incur significant (positive or negative) impact on performance.

In order to improve the accuracy of the Multi2Sim GPU model, we have implemented three main extensions, detailed below: i) Miss Status Holding Registers (MSHR) file, ii) coalescing vector memory requests, and iii) non-blocking GPU store instructions.

#### 3.5.1 MSHR File Modeling

GPUs generate a huge quantity of memory accesses, but only a limited number of pending cache requests are allowed at a given point in time. For this purpose, current non-blocking caches implement MSHR files. Upon a cache miss, the MSHR file is looked up to check if the target block is already being fetched. On such a case, the missing memory access is queued into the MSHR entry associated to the target block.

Note that a given MSHR entry is in charge of tracking all the memory accesses to a given cache block (i.e., all the requests whose data address falls within the block). Therefore, the maximum number of outstanding memory accesses is limited by the number of MSHR entries. Consequently, if all MSHR entries are busy and the missing cache block is not being fetched, the memory access is stalled until a MSHR entry is released.

#### Multi2Sim MSHR Model

In Multi2Sim, two main parts can be distinguished in a CPU or a GPU model, the processor pipeline and the memory subsystem. The processor pipeline models the hardware more closely related to the processor pipe stages excluding first-level caches. First-level caches are modeled in the memory subsystem, which considers all the parts of the cache hierarchy and the main memory. In this context, a memory access enters into the memory subsystem as soon as it is issued by the pipeline logic to access the first level of the memory hierarchy.

Multi2Sim only models the MSHR file in the CPU pipeline but no MSHR file is modeled for the GPU pipeline. Moreover, the model only considers first-level cache misses. Thus, in a Multi2Sim GPU model, the number of outstanding cache blocks handled by any L2 cache is virtually unbounded. As Section 3.6 will show, this implementation provides important performance deviations.

#### Modeled MSHR Extension

We propose to decouple the MSHR from the pipeline model, and to associate a MSHR file to each cache structure in the memory subsystem. This implementation provides a more accurate simulation in both CPU and GPU architectures, since they share the same source code for modeling the memory subsystem. Our implementation allows the MSHR files of distinct cache structures to present a different number of entries, closely mimicking the real implementation of commercial machines.

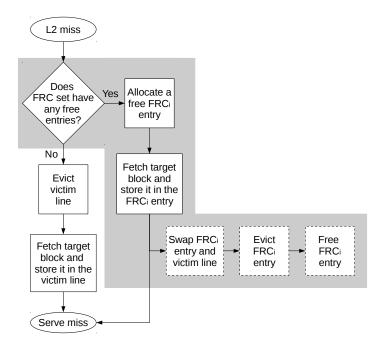

Our implementation works as follows. When a cache access misses in a given L1 cache, the associated MSHR file is accessed. If the comparison matches, the access is queued in the corresponding MSHR entry. If the comparison fails, a free MSHR entry is allocated. Then, the block is looked up in the corresponding L2 cache. If the L2 copy of the requested block is being involved in other operations (e.g., it is being replaced), then a nack signal is returned to the L1 cache, which will retry the operation later. When this situation occurs, to make an efficient use of the MSHR file, the associated MSHR entry is released and the associated queued accesses are moved to a special retry queue. When finally the missing block is transferred to the L1 cache, its associated MSHR entry is released and the memory accesses queued to that entry are satisfied, letting the processor pipeline follow with its normal operation. On a L2 cache miss, the described mechanism is applied recursively to a lower level of the memory hierarchy (e.g. L3 or main memory). Finally, if there are not any free MSHR entry available when it is required, the access waits for a free entry in the MSHR waiting queue, from where they are accessed in FIFO order as soon as an MSHR file entry is freed.

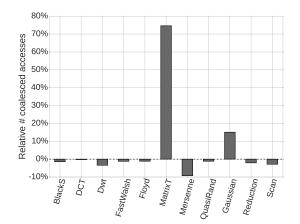

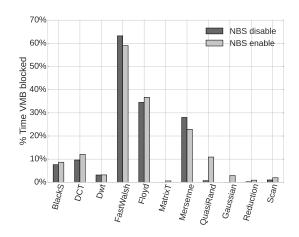

#### 3.5.2 Coalescing Vector Memory Requests

Grouping threads in wavefronts helps improve the memory system performance. For example, in the GCN microarchitecture, one of the main factors limiting the amount of in-flight accesses is the size of the vector memory instruction buffer (VMB) within the vector memory unit (VMU) in the CU since each instruction stored in this buffer can generate up to 64 memory requests. A given instruction is stored in the VMB until all its associated memory requests finish. Assuming a 32-entry VMB (a default value used in our experiments in absence of publicly free available information from AMD), there can be up to 2048 (32×64) memory requests in flight at a given point in time. Note that this is the number of memory requests that can be issued by only 1 CU. This situation clearly makes the memory subsystem to become an important performance bottleneck.

To alleviate this situation, GPU architects group memory requests of the same type (load or store) to the same cache line into a single memory access, so reducing the effective number of memory accesses. This way reduces the pressure on the memory hierarchy.

#### Coalescing and Merging Approaches

Two main approaches, or a combination of them, are being followed in current GPU designs to reduce the number of memory accesses: coalescing and merging. The coalescing approach implements a coalesce logic that combines multiple requests belonging to the same vector memory instruction into a single cache access. This logic acts in the VMU just before the access is issued to the memory subsystem, thus it is synchronized with the instruction issue stage.

In contrast, the merging approach is implemented within the memory subsystem, decoupled from the VMU; in loads and store queues. Unlike the previous approach, memory requests from the same vector instruction may arrive at the memory subsystem at different points in time. For example, in the GCN microarchitecture each subwavefront issues the memory accesses from the same vector memory instruction in a different clock cycle. Thus, distinct cache accesses can potentially rise from requests from the same instruction, even if finally those cache accesses target the same cache line.

Different commercial GPUs implement one of both approaches or a specific combination. AMD Evergreen [2][49] support coalescing for both loads and stores. In contrast, in the Southern Islands architecture, load requests are coalesced while store requests are merged.

#### Multi2Sim Coalescing Model

Multi2Sim implements a generic merging model to access the L1 caches that is applied both in GPU and CPU architectures. This model can merge multiple memory accesses regardless of their amount and if they are produced by the same or different vector memory instructions, although some restrictions are applied to attend memory coherence and consistency issues.

However, coalescing is not implemented in Multi2Sim even for the GPU architectures, which highly benefit from this approach. As shown in Section 3.6, the Multi2Sim model is incomplete since coalescing instead of merging can sometimes lead to significant performance differences.

#### Modeled Coalescing Extension

We have extended Multi2Sim with a flexible coalescing and merging implementation that allows any approach or combination to be accurately simulated. In addition to the merging capabilities of the original implementation, the proposed extension can coalesce memory requests from the same instruction in a single memory access to be issued later to the memory subsystem.

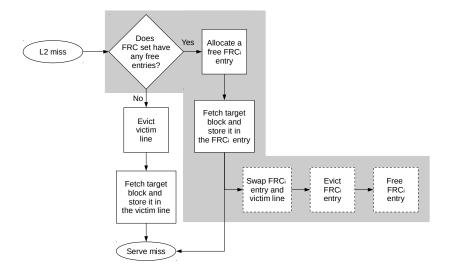

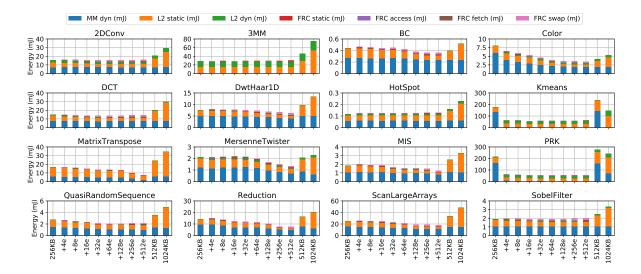

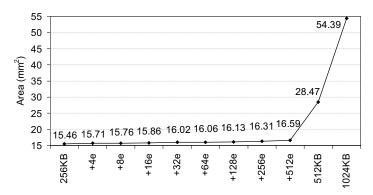

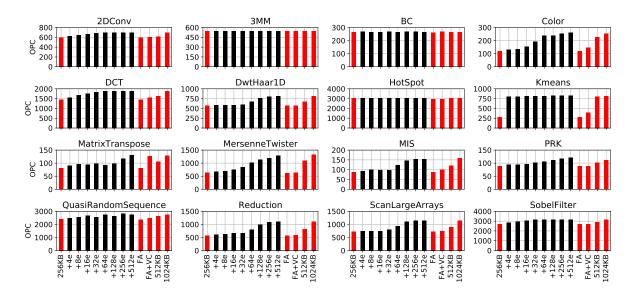

#### 3.5.3 Non-Blocking Stores