# "Techniques for adaptive bias compensation and adaptive biasing in LDOs for SoC applications"

Guillermo Darder Calabuig

**Tutor: Vicente Herrero Bosch**

**Cotutor: Jose Luis Gonzalez**

Trabajo Fin de Máster presentado en la Escuela Técnica Superior de Ingenieros de Telecomunicación de la Universitat Politècnica de València, para la obtención del Título de Máster en Ingeniería Sistemas Electrónicos

Curso 2017-18

Valencia, 24 de julio de 2018

### Resumen

Para resolver el trade-off entre respuesta transitoria vs Iq diversas técnicas se han presentado en el pasado para tratar de mantener la estabilidad de los LDO para diferentes corrientes de carga. Estas técnicas pueden ser clasificadas a groso modo en 3 categorias: bias adaptativo, pole-zero tracking y una combinación de ambas. Estas técnicas presentan una gran desventaja y es que tienen una respuesta bastante lenta empeorando el slew-rate del LDO. Para resolver este problema se estudiará otro método conocido como bias dinámico. La técnica de bias dinámico trata de dar un impulso de corriente al bias del LDO para compensar cambios rápidos en el voltaje de salida.

El objetivo final de este trabajo es el de lograr realizar un diseño de LDO adaptativo adecuado para ser usado en aplicaciones de SoC. Gracias a su eficiencia incluso para muy bajas corrientes de carga y su habilidad para mantenerse estable para un amplio rango de corrientes.

#### Resum

Per a resoldre el trade-off entre resposta transitòria vs Iq diverses tècniques s'han presentat en el passat per a tractar de mantindre l'estabilitat dels LDO per a diferents corrents de càrrega. Aquestes tècniques poden ser classificades en termes generals en 3 categories: bias adaptatiu, pole-zero tracking i una combinació de les dos. Aquestes tècniques presenten un gran desavantatge i és que tenen una resposta bastant lenta empitjorant el slew-rate del LDO. Per a resoldre aquest problema s'estudiarà un altre mètode conegut com bias dinàmic. La tècnica de bias dinàmic tracta de donar un impuls de corrent al bias del LDO per a compensar canvis ràpids en el voltatge d'eixida.

L'objectiu final d'aquest treball és el d'aconseguir realitzar un disseny de LDO adaptatiu adequat per a ser usat en aplicacions de SoC. Gràcies a la seua eficiència fins i tot per a molt baixos corrents de càrrega i la seua habilitat per a mantindre's estable per a un ampli rang de corrents.

# **Abstract**

For solving the transient response vs Iq trade-off various current schemes have been presented in the past to maintain stability of the LDO for different current loads. These techniques can be broadly categorized in 3 categories: adaptive bias, pole-zero tracking and a combination of both. These techniques present a big disadvantage when it comes to slew-rate. To solve this problem another technique will be studied: dynamic bias. Dynamic bias scheme tries to boost the bias of the LDO to compensate for fast changes in output voltage.

The final goal of this project is to achieve an adaptive LDO design suitable to be used for SoC supply domains. Thanks to its good efficiency even with very low loads and its ability to remain stable for great load ranges.

# Índice

| Capítulo 1. |            | Objetivo                                 | 2  |

|-------------|------------|------------------------------------------|----|

| Capítulo 2. |            | LDO                                      | 3  |

| 2.1         | Buc        | cles de control                          | 5  |

| 2.1.1       |            | Transformada de Laplace                  | 5  |

| 2.1.2       |            | Teoría de control                        | 6  |

| 2.2         | Mo         | delos de alto nivel                      | 10 |

| 2.3         | Tip        | os de LDO                                | 12 |

| 2.4         | Téc        | enicas de compensación                   | 15 |

| 2.4         | .1         | Compensación Miller                      | 15 |

| 2.4.2       |            | Compensación paralela                    | 16 |

| 2.4         | .3         | Compensación Ahuja                       | 17 |

| 2.4         | .4         | Compensación Feedforward                 | 18 |

| 2.5         | Pov        | wer Supply Rejection Ratio               | 19 |

| Capítulo    | 3.         | Bias adaptativo y bias dinámico          | 22 |

| 3.1         | Bia        | s adaptativos                            | 22 |

| 3.2         | Pol        | e-Zero tracking                          | 23 |

| 3.3         | Bia        | s dinámico                               | 25 |

| Capítulo    | <b>4</b> . | Aplicación de bias dinámico y adaptativo | 28 |

| 4.1         | Tra        | nsistor de paso                          | 28 |

| 4.2         | Rec        | de feedback                              | 29 |

| 4.3         | Am         | mplificador de error                     |    |

| 4.4         | Coı        | mpensación                               | 30 |

| 4.4.1       |            | Análisis de alto nivel                   | 30 |

| 4.4         | .2         | Implementación en el circuito            | 32 |

| 4.5         | Bia        | s adaptativos                            | 33 |

| 4.6         | Bia        | s dinámico                               | 34 |

| Capítulo    | 5.         | Simulaciones                             | 36 |

| 5.1         | Mo         | delo ideal                               | 36 |

| 5.2         | LD         | O base                                   | 40 |

| 5.3         | Bia        | s adaptativo                             | 42 |

| 5.4         | Bia        | s dinámico                               | 46 |

| Capítulo 6. |            | Conclusiones y trabajo futuro            | 50 |

| Capítulo 7. |            | Bibliografía                             | 51 |

# Capítulo 1. Objetivo

En la actualidad, abundan los dispositivos electrónicos portátiles tales como smartphones, smartgears o tablets así como nuevos dispositivos en la tendencia IoT. Todos estos dispositivos portátiles y aquellos que constituyen las redes IoT requieren una buena optimización en términos de consumo para poder reducir los tamaños de las baterías. Para poder reducir el consumo, estos circuitos suelen emplear sistemas de apagado/encendido que permiten consumir corriente solo cuando sea necesario. Para alimentar dichos circuitos suelen emplearse LDOs puesto que son capaces de mantener voltaje de salida estables incluso para variaciones en la alimentación principal. El problema es que los LDOs se diseñan generalmente para ser estables y funcionar bajo cierta corriente de carga lo que supone el empleo de diferentes LDOs para diferentes consumos de corriente o el uso de corriente fija para mantener la polarización, implicando un mayor consumo. Además, cambios drásticos en la carga pueden suponer cambios grandes en el voltaje de salida. Con todo esto, el objetivo de este trabajo es el de analizar diferentes métodos para mejorar la estabilidad de los LDOs bajo diferentes cargas y su respuesta a los transitorios rápidos de corriente de carga.

En primer lugar, se hará un estudio previo sobre el funcionamiento de los LDO centrándose en las características principales, funcionamiento y estabilidad. Para analizar la estabilidad del LDO se va a emplear un método basado en la teoría de bucles de control que permitirá ajustar la estabilidad a nivel teórico del LDO de manera mucho más sencilla. También se realizará una comparativa entre los dos tipos más usados comúnmente de LDO en circuitos integrados valorando las ventajas y desventajas de cada uno.

Este trabajo en principio no se enfoca tanto en el diseño de un LDO sino más bien en la búsqueda y análisis de un sistema que permita a estos reguladores adaptarse fácilmente a cambios de corriente de carga. Por ello este trabajo se centrará principalmente en analizar las ventajas y desventajas, así como el funcionamiento de los métodos escogidos para análisis, realizando un posterior diseño de un LDO sencillo para poner en práctica dicho método sin hacer demasiado hincapié en la metodología de diseño del mismo.

Finalmente, el objetivo último de este proyecto será el de proporcionar un método de bias adaptativo y bias dinámico, recopilando sus ventajas y desventajas y analizando la viabilidad de uso práctico en circuitos reales.

# Capítulo 2. LDO

Como se ha comentado en el apartado anterior, con la tendencia actual en tecnologías portables y sistemas IoT se requiere que los dispositivos consuman cada vez menos energía. Debido a ello surge una técnica ampliamente usada que consiste en mantener el dispositivo apagado y reactivar el funcionamiento solo cuando se requiera cada cierto tiempo o atendiendo a una señal de evento. Esto hace que los reguladores LDO (Low Dropout Voltage) sean mejor opción frente a los "switching regulators" puesto que presentan mejor respuesta frente a señales transitorias y además requieren un menor consumo estático [2] [4] [5].

Los reguladores LDO utilizan una realimentación negativa para mantener el voltaje de salida estable al voltaje deseado. Un LDO consta de tres componentes principales:

- Transistor de paso

- Amplificador de error

- Red de realimentación

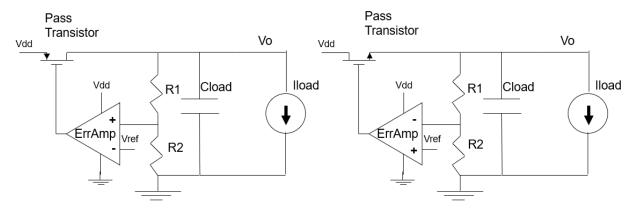

El funcionamiento básico del LDO es muy simple, se pretende obtener un voltaje concreto a la salida, para ello se debe comparar con voltaje de referencia y en función de la diferencia entre estos se ajusta la corriente a la salida regulando así el voltaje de salida. En primer lugar, se reduce el voltaje de salida mediante la red de feedback y, tras pasar por la red de realimentación se compara dicho voltaje con el de referencia mediante un amplificador de error (Amplificador operacional). La salida se utiliza como voltaje de puerta del transistor de paso que tendrá la función de regular la corriente de salida para poder ajustar el voltaje final. Si se ha diseñado bien con suficiente ganancia este bucle de realimentación se encargará de lograr que el voltaje en los terminales Vp y Vn del operacional sean iguales. Para escoger el voltaje final dado el voltaje de referencia basta con realizar el siguiente cálculo en base a la Ilustración 1:

$$Vp = Vn = Vref = Vout * \frac{R_2}{R_1 + R_2}$$

(1)

$$Vout = Vref * \left(1 + \frac{R_1}{R_2}\right) \tag{2}$$

Dado que los LDO utilizan realimentación negativa pueden volverse inestables, esto es, pueden darse el caso que a cierta frecuencia el voltaje quede desfasado 180° con amplitud superior a 0dB dando lugar a una realimentación positiva que haría oscilar el sistema. Para poder analizar de forma más sencilla la estabilidad en los LDO se utilizará una metodología basada en la teoría de bucles de control y en modelos de alto nivel que permiten simplificar el análisis.

La principal característica de los LDO es que permiten tener un voltaje de dropout muy bajo. Se entiende por voltaje de dropout el voltaje mínimo que debe haber entre entrada y salida de un regulador para que este siga funcionando correctamente. Dentro de los LDO se pueden encontrar diferentes tipos según el tipo de transistor de paso que se utilice:

Ilustración 1. Tipos LDO según transistor de paso (tipo p izquierda, tipo n derecha)

En principio, los LDO con transistor de paso MOSFET suelen ser más comunes por presentar una menor Iq (corriente de bias) y por lo tanto son más eficientes.

Los reguladores LDO se pueden caracterizar a través de los siguientes parámetros:

- Voltaje de dropout

- Eficiencia

- Corriente de bias

- Regulación de carga

- Regulación de línea

- Estabilidad

- PSRR

Empezando por el voltaje de dropout, este es un parámetro muy importante puesto que se debe diseñar correctamente el transistor de paso para la alimentación que se utilice y el voltaje de salida que se requiera. En los transistores tipo P el voltaje de dropout vendrá marcado por el voltaje Vds que permita que el transistor de paso se mantenga en saturación, por lo tanto, será Vdsat. En el caso del transistor tipo N, en caso de que el amplificador trabaje con el mismo voltaje de alimentación que el transistor de paso, resulta evidente que el voltaje en la puerta del transistor nunca podrá ser mayor que Vdd y por lo tanto Vout + Vth tendrá que ser menor que Vdd. De esta forma el voltaje de dropout de un LDO tipo N sería de Vth lo cual puede resultar demasiado grande para ciertas aplicaciones. Para poder solucionarlo se puede añadir un charge pump que aumente el voltaje en la puerta del transistor y permita tener mayor voltaje de Vdd pudiendo reducir así el voltaje de dropout.

En cuanto a la eficiencia en el LDO, esta está relacionada con la perdida de voltaje inherente debida al voltaje de dropout y con la corriente no útil utilizada para alimentar los bloques del circuito (amplificador, feedback, charge pump, ...). La fórmula quedaría de la siguiente forma:

$$\eta = \frac{V_o}{V_{dd}} * \frac{I_o}{I_o + I_q} * 100 (\%)$$

(3)

De forma que a mayor corriente utilizada para polarizar los transistores implicará una perdida en la eficiencia del LDO. Es por eso que resulta importante escoger las corrientes de polarización adecuadas, así como evitar corrientes innecesarias para mantener un alto valor de eficiencia.

Aunque el LDO tiene como principal objetivo mantener fijo el voltaje a la salida, cuando se utilizan componentes reales esto no se llega cumplir completamente, por ello existen tres parámetros que definen hasta qué punto es capaz de mantener el voltaje de salida regulado el LDO: PSRR, Regulación de línea y regulación de carga.

El PSRR (Power Supply Rejection Ratio) representa la variación que se observa a la salida del LDO cuando existe un ruido o variación AC en la entrada de alimentación. Es un parámetro muy importante y que ha motivado diferentes estudios con el objetivo de reducir el PSRR. En otro apartado se comentará más en profundidad las fuentes de ruido de alimentación y el efecto que tienen ciertos bloques del circuito.

La regulación de carga y la regulación de línea muestran como los cambios en alimentación y corriente de carga pueden afectar al voltaje de salida.

Aunque no se ha añadido a la lista puesto que es un efecto que puede no ser importante según las frecuencias a las que se trabaje y los parásitos presentes en el encapsulado del circuito, el LDO puede presentar corriente negativa en el terminal de alimentación a frecuencias cercanas a la zona de ganancia unidad del bucle. Esta corriente negativa en conjunto con posibles inductancias parasitas del empaquetado puede dar a resonancias que hagan oscilar la alimentación del LDO dado lugar fallas de funcionamiento.

Finalmente, el último parámetro a tener en cuenta en un LDO es la estabilidad. Dado que el LDO es un bucle de realimentación de dos etapas puede dar lugar a inestabilidad y por lo tanto requiere un correcto análisis y posible compensación en caso de no ser estable. La estabilidad se explicará a continuación mediante una metodología que permite un análisis más sencillo. Además, se comentarán las diferencias entre tipología tipo N y tipo P.

## 2.1 Bucles de control

Como se ha comentado, los LDO hacen uso de una realimentación negativa (bucle de control) para poder regular el voltaje a la salida por ello durante este trabajo se utilizará una metodología basada en la teoría de los bucles de control para simplificar el análisis de estabilidad de los LDO, así como de su funcionamiento de las técnicas propuestas en este trabajo.

#### 2.1.1 Transformada de Laplace

Cuando se trata con circuitos que requieren cálculos diferenciales sobre señales variantes en el tiempo se suele emplear la transformada de Laplace. Esta transforma una función dependiente de una variable real (t) a una función dependiente de una variable compleja (s) que en este caso representaría una frecuencia compleja.

$$F(s) = \int_0^\infty f(t)e^{-st}dt \tag{4}$$

De esta forma, cuando se está tratando con ecuaciones diferenciales se pueden comprobar las siguientes igualdades:

$$\frac{dX}{ds} = sX \tag{5}$$

$$\int X \, ds = \frac{X}{s} \tag{6}$$

Gracias a la transformada de Laplace se puede convertir sencillamente una ecuación diferencial en una ecuación polinómica en la que la "s" representaría la frecuencia compleja. Una vez resuelta la ecuación diferencial se puede volver al dominio del tiempo haciendo la transformada inversa de Laplace, logrando de esta forma resolver de forma mucha mas sencillas las complejas ecuaciones diferencial.

#### 2.1.2 Teoría de control

La teoría de control es una rama de la matemática que se encarga de estudiar el control de sistemas dinámicos y desarrollar un modelo de control para dichos sistemas que sea capaz de mantenerlos estables y optimizar el retraso o el overshoot del mismo [8].

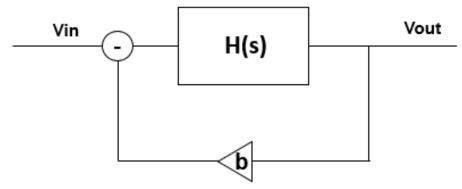

Para ello se utiliza un controlador que comprueba la variable dinámica que se pretende controlar y la compara con una referencia estática. La diferencia entre ambos se utiliza hace pasar a través de una red de feedback y se utiliza como variable de control para ajustar la variable monitorizada.

Debido a la realimentación negativa que se forma y a posibles retrasos en la señal a lo largo del bucle a causa de los elementos capacitivos, es posible que a ciertas frecuencias la realimentación pase de ser negativa a positiva dando lugar a inestabilidades en el circuito.

Ilustración 2. Esquema básico de un bucle de control.

En la imagen se pueden ver tres componentes básicos en el bucle de control, una señal de referencia que servirá para ajustar la señal de salida, un comparador para comprobar el error actual de la señal de salida respecto a la referencia, un bloque de feedback que ayuda equiparar la señal

de salida a la de referencia y el bloque H(s) que se encargará de ajustar la señal de salida en función del error.

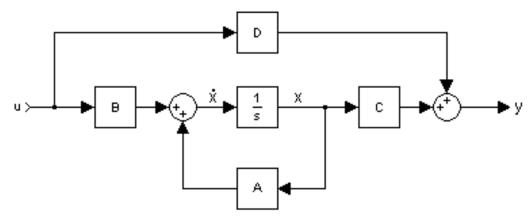

En general la respuesta de un sistema linear e invariante en el tiempo puede representarse de la siguiente forma:

Ilustración 3. Sistema linear invariante general.

$$\begin{cases} \frac{dx(t)}{dt} = Ax(t) + Bu(t) \\ y(t) = Cx(t) + Du(t) \end{cases}$$

(7)

Y si se observa desde el punto de vista frecuencial mediante la transformada de Laplace:

$$\begin{cases} sX = AX + BU \\ Y = CX + DU \end{cases} \tag{8}$$

Para analizar la estabilidad se debe analizar la respuesta natural del sistema usando U=0 y por lo tanto esta solo dependerá de A. Siguiendo el criterio de Routh-Hurwith [7] [8], el sistema será estable si la ecuación característica dada por "det(sI - A)=0" presenta todos sus coeficientes mayores a 0 siendo I la matriz identidad. Es decir, si alguno de los coeficientes es 0 o menor de 0 el sistema será intrínsecamente inestable. De forma simplificada para este caso concreto, la ecuación característica resulta ser el denominador de la función de transferencia del circuito realimentado.

Para el caso concreto de la Ilustración 2, si se calcula el valor del voltaje de salida con los parámetros mostrados se obtiene lo siguiente:

$$V_{out} = (V_i - b * V_{out}) * H(s)$$

(9)

$$V_{out} = \frac{H(s)V_{in}}{1 + H(s) * b} \tag{10}$$

Si se toma el caso H(s) = 1/D(s) con D(s)=(1+p1s)(1+p2s) finalmente se llega a la siguiente ecuación simplificada:

$$V_{out} = \frac{V_{in}}{D(s) + b} \tag{11}$$

$$V_{out} = \frac{\frac{V_{in}}{b}}{1 + \frac{(p1+p2)}{b}s + \frac{p1p2}{b}s^2}$$

(12)

$$V_{out} = \frac{N(s)V_i}{1 + A s + B s^2}$$

(13)

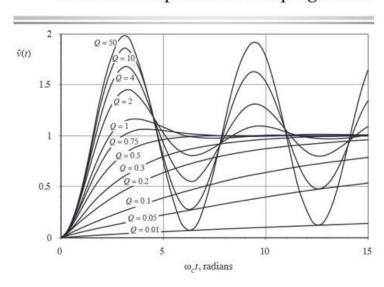

En este caso el determinante de la ecuación anterior sería el polinomio característico mediante el cual se puede analizar la estabilidad. Además, se puede ver que los componentes que acompañan a los términos cuadrático y lineal del denominador nos proporcionan información de la frecuencia de corte y amortiguamiento del sistema en bucle cerrado.

$$V_{out} = \frac{N(s)V_i}{1 + \frac{1}{w_0 * Q} s + \frac{1}{w_0^2} s^2}$$

(14)

$$w_0 = \sqrt{\frac{1}{B}} = Frecuencia de corte$$

(15)

$$Q = \sqrt{\frac{B}{A^2}} = Factor \ de \ amortiguamiento$$

(16)

# Transient response vs. damping factor

Ilustración 4. Respuesta transitoria en función del factor de calidad.

De esto se pueden extraer dos conclusiones principales:

- 1- Si dos sistemas en bucle cerrado tienen el mismo denominador tendrán misma respuesta transitoria.

- 2- A mayor factor de calidad más tardará en estabilizarse el sistema y por lo tanto, si el factor de amortiguamiento es infinito el sistema será inestable.

La primera conclusión nos permite diseñar bucles de control de forma más sencilla simplemente ajustando los componentes para obtener los parámetros de frecuencia y factor de calidad que previamente se habrán calculado. La segunda conclusión nos permitirá averiguar de forma rápida si un sistema es estable o no, si el factor de amortiguamiento fuese infinito se reflejaría en la falta de alguno de los términos del denominador característico.

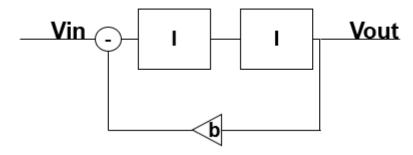

Con todo esto en mente, pasemos a analizar dos posibles bucles de control con los que nos encontraremos cuando tratemos de analizar en profundidad las características de los LDO:

Ilustración 5. Bucle de control de dos integraciones.

Ilustración 6. Bucle de control con integrador y producto-integral en serie.

En el primer caso tenemos un bucle de control que utiliza un  $H(s) = 1/s^2$ , es decir dos integradores en serie. Como se ha comentado antes solo resulta interesante analizar el denominador del sistema, lo que implica que el voltaje de referencia no será necesario en este caso para analizar la estabilidad del circuito. De esta forma, si se suprime el voltaje de entrada y se analiza únicamente la realimentación queda la siguiente fórmula a través de la cual se puede obtener el denominador del sistema y por lo tanto su estabilidad.

$$V_{out} = -V_{out} * H(s) * b = -V_{out} * \frac{b}{s^2}$$

(17)

$$V_{out} = \frac{1}{1 + []s + \frac{1}{h}s^2}$$

(18)

Se puede ver que no existe el término lineal en el denominador característico del bucle de control, así pues, tal como se ha comentado anteriormente se puede concluir sin lugar a duda que este sistema será inestable.

Si analizamos el segundo caso, vemos que se trata de sistema que utiliza un  $H(s) = 1/s^2 + 1/s$ , es decir un integrador con parte proporcional seguido por otro integrador. De igual forma que en el caso anterior el análisis quedaría de la siguiente forma:

$$V_{out} = -V_{out} * H(s) * b = -V_{out} * \frac{b}{s^2} - V_{out} * \frac{b}{s}$$

(19)

$$V_{out} = \frac{1}{1 + s + \frac{1}{h}s^2} \tag{20}$$

En este caso sí que aparece un término lineal con lo que el sistema será estable. Con esto se puede concluir que tras añadir una parte proporcional se logra estabilizar el sistema.

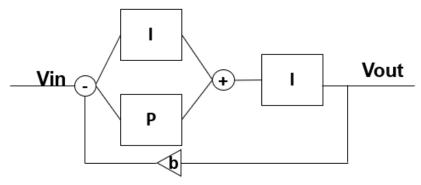

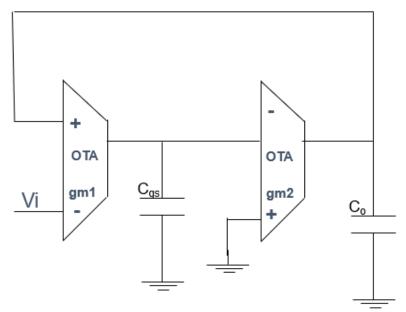

#### 2.2 Modelos de alto nivel

Para simplificar el análisis de los LDO se hará un primer análisis en alto nivel modelizando el transistor de paso y el amplificador de la siguiente forma:

Ilustración 7. Modelos de amplificador operacional y transistor con operacionales de transadmitancia.

Si se tiene en cuenta que un transistor en zona de saturación no es más que una fuente de corriente controlada por tensión, se puede modelizar como un OTA. De igual forma, funcionalmente, un amplificador operacional no es más que un OTA con una impedancia de carga generalmente grande que le permite tener una alta ganancia.

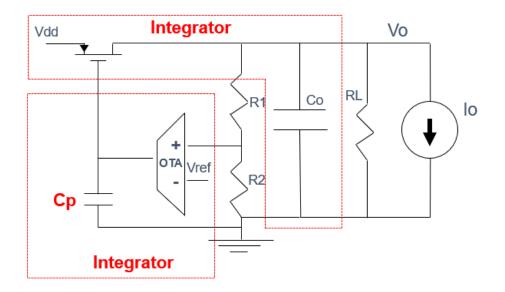

Tomando en cuenta estos modelos de alto nivel y aplicándolos a la estructura ya comentada de un LDO básico con transistor de paso tipo P quedaría de esta manera:

Ilustración 8. Simplificación de LDO mediante modelos con OTAs pt.1.

Ilustración 9. . Simplificación de LDO mediante modelos con OTAs pt.2.

Con esto ahora ya se puede realizar un análisis mucho más sencillo del funcionamiento de este tipo de reguladores.

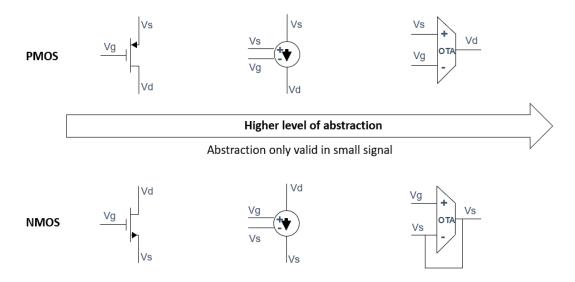

# 2.3 Tipos de LDO

Existen dos grandes grupos de LDO en función del tipo de transistor de paso que se utilice. Para analizar las diferentes características de estos tipos se utilizará la simplificación comentada en el apartado anterior y se supondrá un amplificador de una única etapa, aunque esta metodología de análisis también sería válida para amplificadores multietapa.

El transistor de paso que funciona como una fuente de corriente controlada por voltaje para ajustar la tensión de salida puede ser de tipo P o de tipo N según los requerimientos del regulador.

En primer lugar, se va a plantear un modelo de alto nivel para cada tipo comparando sus diferencias.

Ilustración 10. Abstracción en alto nivel de los transistores tipo P y N

Vout

Vin

Ilustración 11. Modelo simplificado LDO con transistor de paso tipo P.

Ilustración 12. Modelo simplificado mediante OTAs para LDO tipo N.

Se puede ver en la imagen que en el caso del transistor tipo N habría una realimentación negativa extra. Si se extraen las fórmulas simplificadas quedarían de la siguiente manera:

Tipo P:

$$V_o = \frac{V_o g m 1}{C_{p_1} s} * \frac{-g m 2}{C_{p_2} s} \tag{21}$$

$$V_o = \frac{1}{gm1gm2\left(1 + [] + \frac{c_{p_1}c_{p_2}}{gm1gm2}s^2\right)}$$

(22)

Tipo N:

$$V_o = \frac{-V_o gm1}{C_{p1}s} * \frac{gm2}{C_{p2}s} - \frac{V_o gm2}{C_{p2}s}$$

(23)

$$V_o = \frac{1}{gm1gm2\left(1 + \frac{c_{p1}s}{gm1} + \frac{c_{p1}c_{p2}}{gm1gm2}s^2\right)}$$

(24)

Como se puede comprobar en el caso del tipo P estaríamos ante un caso de  $H(s)=1/s^2$  (como el primer ejemplo de bucle de control analizado en el apartado anterior) y en el caso del tipo N habría un  $H(s)=1/s^2+1$  (como en el segundo ejemplo del apartado anterior). Como ya se ha visto, el regulador tipo N sería por sí mismo estable mientras que el tipo P sería, en principio,

inestable. Cabe destacar que haciendo un análisis sin tener en cuenta las resistencias en paralelo a las capacidades se está suponiendo el peor caso posible, es decir, que podría darse el caso de que a pesar de parecer inestable un circuito en alto nivel posteriormente resulte ser estable. No obstante, no es aconsejable valerse de esto para estabilizar el circuito dado que resulta peligroso.

Si se analiza ahora el voltaje de dropout en ambos tipos se obtendrían las siguientes fórmulas:

Tipo P:

$$V_{do} = V_{sat} = VSG - |Vth| \tag{25}$$

Tipo N:

$$V_{do} = \begin{cases} V_{sat} = VGS - Vth & Si \quad V_{th} < V_{sat} \\ Vth & Si \quad V_{th} > V_{sat} \end{cases}$$

(26)

Dado que el voltaje VGS del transistor tipo N depende directamente del voltaje de salida, en caso de que se utilice misma alimentación en el amplificador y en el transistor de paso, da como resultado un voltaje de dropout igual al voltaje de threshold. Esto es debido a que VGS debe ser como mínimo mayor a Vth y en consecuencia Vdd-Vo, dando lugar a un mayor voltaje de dropout. Una forma de solucionar esto es mediante un charge pump para aumentar el voltaje máximo a la salida del amplificador. No obstante, utilizar un charge pump implica un mayor consumo que puede suponer un problema. Por ello, generalmente, se suelen utilizar transistores tipo P con una compensación adecuada para mantener la estabilidad.

# 2.4 Técnicas de compensación

Para analizar las técnicas de compensación más comunes que se suelen utilizar, se realizará el mismo procedimiento de análisis en alto nivel que ya se ha explicado.

Las técnicas de compensación se basan principalmente en añadir una parte proporcional al primer integrador (amplificador de error) de diferentes formas. Algunas técnicas se basan en cancelar los elementos que ralentizan la señal generando desfase (condensadores) mientras que otras proporcionan caminos rápidos de menor ganancia.

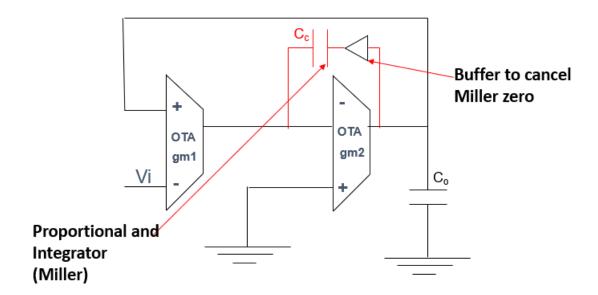

#### 2.4.1 Compensación Miller

El primer método que se va a realizar es la compensación Miller la cual añade un bucle de realimentación negativa extra mediante un condensador entre los terminales de puerta y drenador del transistor de paso permitiendo añadir una parte proporcional. El esquema básico sería el siguiente:

Ilustración 13. Modelo simplificado mediante OTAs de compensación Miller.

Realizando los cálculos oportunos, se obtienen las siguientes fórmulas:

$$V_o = \frac{-V_o g m 1 g m 2}{C_c C_o s^2} + \frac{-V_o g m 2}{C_o s}$$

(27)

$$V_o = \frac{1}{gm1gm2\left(1 + \frac{C_c}{gm1}s + \frac{C_cC_o}{gm1gm2}s^2\right)}$$

(28)

Este tipo de compensación permite un ajuste sencillo del margen de fase sin necesidad de añadir un consumo de corriente extra. La gran desventaja que supone utilizar la compensación de Miller es que puede llegar a empeorar mucho el PSRR como se verá en posteriores apartados.

El otro inconveniente que puede presentar la compensación Miller es que añade un zero parásito que aumenta todavía más el desfase y por tanto puede deteriorar la estabilidad. Este zero parásito se puede atenuar mediante el uso de una resistencia serie que ajuste la frecuencia del mismo o mediante un buffer que prácticamente elimine dicho zero.

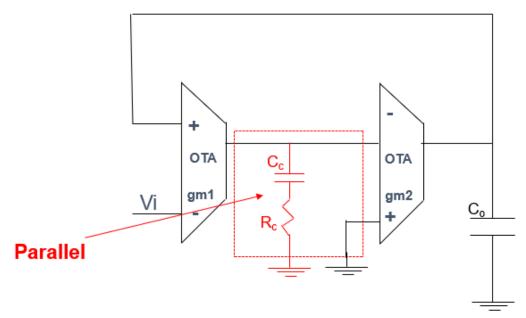

#### 2.4.2 Compensación paralela

Esta compensación consigue añadir la parte proporcional que se busca mediante la inclusión de una resistencia en serie con cualquiera de los condensadores que formen parte de los integradores. De esta forma, la resistencia estaría añadiendo un zero para cancelar el polo del condensador al que acompaña. Una técnica bastante común consiste en aprovechar la ESR (resistencia serie parasita) del condensador de salida externo para añadir dicho zero; no obstante, en circuitos SoC suele ser más común incluir la compensación de forma interna en el chip y, por lo tanto, añadir una capacidad y una resistencia en la puerta del transistor de paso.

Ilustración 14. Modelo simplificado mediante OTAs de compensación paralela.

Analizando el circuito se pueden obtener las siguientes fórmulas:

$$V_{o} = \frac{-V_{o}gm1gm2}{C_{c}C_{o}s^{2}} + \frac{-V_{o}gm2gm1R_{c}}{C_{o}s}$$

(29)

$$V_o = \frac{1}{gm1gm2\left(1 + R_cC_cs + \frac{C_cC_o}{gm1gm2}s^2\right)}$$

(30)

Este método, al igual que el método Miller, no añade consumo extra de polarización al circuito y, además, como se verá más adelante, ayuda a mejorar el PSRR. No obstante, requiere una capacidad extra grande que puede llegar a empeorar la respuesta del LDO frente a transitorios de corriente de carga.

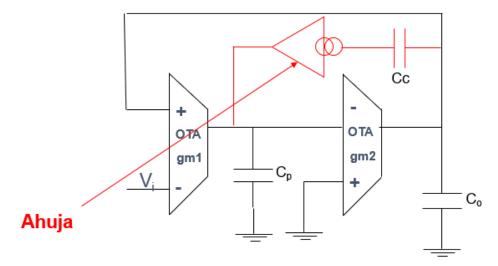

#### 2.4.3 Compensación Ahuja

La compensación Ahuja, también conocida como compensación cascodo o compensación de Miller indirecta, tiene un funcionamiento similar a la compensación Miller, pero logra solventar el problema del polo parásito mediante la inclusión de un buffer de corriente. Se le llama compensación cascodo porque generalmente se suele conectar a un cascodo para que haga la función de buffer de corriente. El esquema típico del Ahuja sería el siguiente:

Ilustración 15. Modelo simplificado mediante OTAs de compensación Ahuja.

Y obteniendo las fórmulas:

$$V_o = \frac{-V_o gm1gm2}{C_p C_o s^2} + \frac{-V_o gm2gmaC_c}{C_o s}$$

(31)

$$V_o = \frac{1}{gm1gm2\left(1 + \frac{C_c}{gma}s + \frac{C_cC_o}{gm1gm2}s^2\right)}$$

(32)

En este caso, la capacidad junto con el buffer de corriente forma un derivador que logra compensar el efecto del primer integrador y, por lo tanto, añadir la parte proporcional. Viéndolo desde otro punto de vista, dicha combinación proporciona un camino rápido que compensa el primer integrador.

Aunque en principio esta compensación requiera mayor consumo de corriente para polarizar el buffer, se puede reaprovechar la fuente de corriente utilizada para polarizar el amplificador de error.

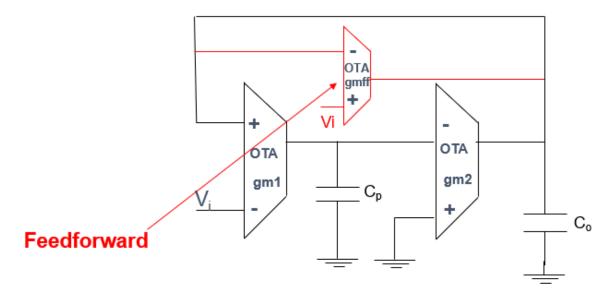

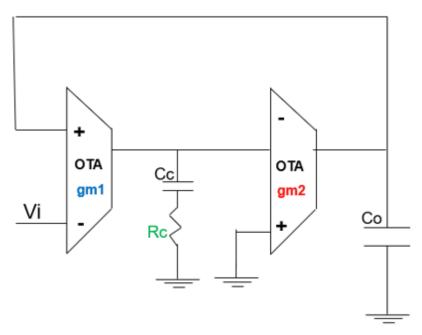

# 2.4.4 Compensación Feedforward

Esta compensación sólo tiene sentido su uso con amplificadores de más de dos etapas dado que se basa en añadir un camino que evite alguna de las etapas del bucle principal, o, dicho de otra forma, que añada un camino rápido para compensar alguna de las etapas. Este sería su esquema:

Ilustración 16. Modelo simplificado mediante OTAs de compensación feedforward.

Y las ecuaciones resultantes serían las siguientes:

$$V_o = \frac{-V_o gm1gm2}{C_n C_o s^2} + \frac{-V_o gmff}{C_o s}$$

(33)

$$V_{o} = \frac{1}{gm1gm2\left(1 + \frac{c_{o}gmff}{gm1gm2}s + \frac{c_{c}c_{o}}{gm1gm2}s^{2}\right)}$$

(34)

Este último caso de compensación sí que requiere de un consumo de corriente mayor, pero no necesita capacidades extra y, por lo tanto, ofrecerá una mejor respuesta a los transitorios de corriente de carga.

# 2.5 Power Supply Rejection Ratio

Como ya se ha comentado, el principal objetivo de un LDO es mantener el voltaje de salida estable y poder rechazar las variaciones de la alimentación de entrada. No obstante, los LDO no son ideales y, por lo tanto, no son capaces de rechazar completamente estas variaciones ni de mantener el rechazo para todas las frecuencias. Por ello, una forma de caracterizar un LDO sería mediante el PSRR que no es más que el voltaje en AC a la salida en función de la frecuencia cuando se inyecta una señal en la alimentación de entrada.

El primer paso para analizar el PSRR en un LDO es comprender el origen del mismo, por ello, en la imagen siguiente se muestran los distintos caminos a través de los cuales se cuela el ruido de alimentación en el circuito.

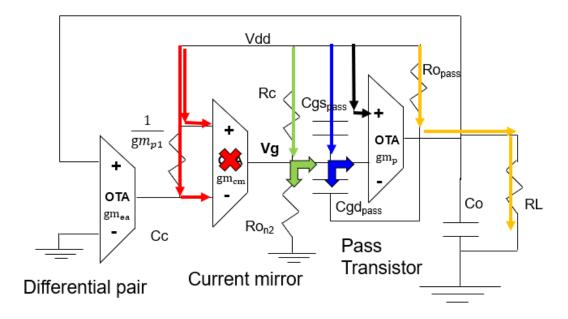

Ilustración 17. Fuentes de ruido de alimentación.

En principio, si los bloques que componen el LDO fueran ideales, no habría caída de tensión entre los nodos Vdd y Vg y, por lo tanto, al ser el voltaje Vgs nulo el ruido de alimentación no pasaría a la salida. No obstante, dado que los componentes son reales, aparecen estos tres caminos a través de los cuales se cuela el ruido a la salida.

Los caminos amarillo y verde se forman a baja frecuencia debido a los divisores de tensión que se forman a causa de las impedancias de salida del transistor de paso y de las ramas P y N del amplificador de error. Si el bucle completo tiene suficiente ganancia en DC este ruido es compensado por el propio bucle quedando la fórmula de la siguiente manera:

$$V_{o} = -V_{o}gm_{ea}gm_{p}Ro_{ea}R_{o} + \left(V_{dd} - \frac{V_{dd}Ro_{2}gm_{p}R_{o}}{Ro_{2} + Ro_{1}}\right) + \frac{V_{dd}R_{L}}{Ro_{pass} + R_{L}}$$

(35)

$$V_{o} = \frac{\left(V_{dd} - \frac{V_{dd}Ro_{2}gm_{p}R_{o}}{Ro_{2} + Ro_{1}}\right) + \frac{V_{dd}R_{L}}{Ro_{pass} + R_{L}}}{1 + A_{o}}$$

(36)

El segundo camino aparece en frecuencia media cuando la impedancia de la capacidad entre la alimentación y puerta es menor que las resistencias que forman el camino verde. Cuando esto ocurre, en principio el ruido pasa a través del condensador Cgs y el PSRR puede volver a mejorar. Por ello, la compensación paralela al añadir capacidad extra entre alimentación y puerta mejora el PSRR. No obstante, debido a la existencia de una capacidad entre puerta y drenador, se puede llegar a formar un divisor capacitivo volviendo otra vez a la situación anterior. Es por esto por lo que se comentaba en apartados anteriores que la compensación de Miller empeora el PSRR puesto que favorece este último efecto. Cabe destacar, además, que el zero que introduce la compensación paralela también supone un obstáculo a la hora de mejorar el PSRR.

El último camino se da en alta frecuencia cuando la corriente a través de las capacidades Cgs y Cgd supera la corriente proporcionada por el transistor de paso de forma que se acaba teniendo un divisor capacitivo entre la alimentación y el nodo de salida.

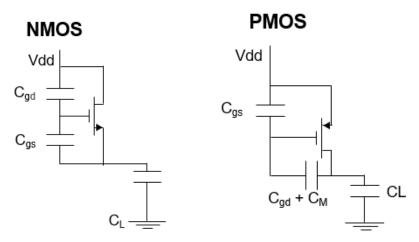

Teniendo todo esto en cuenta se puede realizar una comparación entre el tipo N y el tipo P. Si se analizan ambos tipos se puede comprobar que los caminos por los que se cuela el ruido de alimentación son exactamente los mismos y por lo tanto se infiere que, en principio, en términos de PSRR no existe diferencia entre ambos. Esto se puede ver también tras obtener las fórmulas para ambos casos:

Fórmula y esquema de tipo P y tipo N cuando el bucle ya ha caído:

Ilustración 18. Esquema de transistor de paso tipo N y tipo P fuera del bucle.

$$Vout = \frac{Vin\left(1 + \frac{c_{gs}}{gm}s\right)}{1 + \left(\frac{c_L c_{gs}}{c_{gd}gm} + \frac{c_L}{gm} + \frac{c_{gs}}{gm}\right)s}$$

(37)

La única diferencia entre P y N residiría pues, en el efecto que pueda tener la inclusión de la compensación necesaria en los tipo P.

# Capítulo 3. Bias adaptativo y bias dinámico

Una vez comprendido el funcionamiento básico de un LDO se puede ver claramente que la corriente de carga tiene un papel muy importante en la estabilización y, por lo tanto, variaciones de la corriente en DC pueden dar lugar a la inestabilidad del sistema. Por ello, para poder tener un LDO que pueda ser utilizado en diferentes condiciones de carga, se han analizado distintos métodos de entre los cuales se ha escogido el método del bias adaptativo por ser el más versátil junto con la utilización de un bias dinámico por temas de mejora de slew-rate como se comentará más adelante [1] [3].

Antes de hablar del funcionamiento básico del bias adaptativo cabe destacar que la forma más común actualmente de mantener la estabilidad en estos reguladores para diferentes cargas consiste en añadir una corriente fija de leakage que permite mantener una mínima corriente de bias e, incluso, añadir configurabilidad al tamaño del transistor de paso que permita mantener el mismo punto de operación. No obstante, esto supone un aumento tanto del área como del consumo estático y, por tanto, una pérdida de eficiencia en el regulador.

# 3.1 Bias adaptativo

Como ya se ha visto al analizar la estabilidad de un LDO, se puede observar que el margen de fase del bucle de realimentación depende de la transconductancia del transistor de paso. Como ya se conoce, la transconductancia de un transistor depende directamente de la raíz de la corriente de bias a través de él. Si se toma como ejemplo un modelo de LDO en alto nivel compensado con técnica paralela se puede ver los siguiente:

$$Q = \sqrt{\frac{C_o}{C_c} * \frac{1}{gm2'gm1R_c^2}}$$

(38)

$$gm2' = \sqrt{\frac{I'_{load}}{I_{load}}} gm2$$

(39)

Como se puede ver, en caso de reducirse la corriente a través del transistor de paso (corriente de carga), la gm se ve reducida y, por lo tanto, el factor de calidad aumenta dando lugar a una reducción del margen de fase. Es por esto por lo que, de forma sencilla, se puede ver que para mantener el mismo margen de fase es necesario que el resto de factores que afectan al factor de calidad cambien de forma proporcional para compensar la pérdida de transconductancia.

El método más sencillo para conseguir compensar las variaciones de transconductancia que se ha encontrado en la bibliografía es el del bias adaptativo. Este método consiste en lograr que la transconductancia del amplificador de error siga los cambio en la transconductancia del transistor de paso. La forma de conseguir esto es copiando la corriente a través del transistor de paso y usándola como bias del amplificador de error.

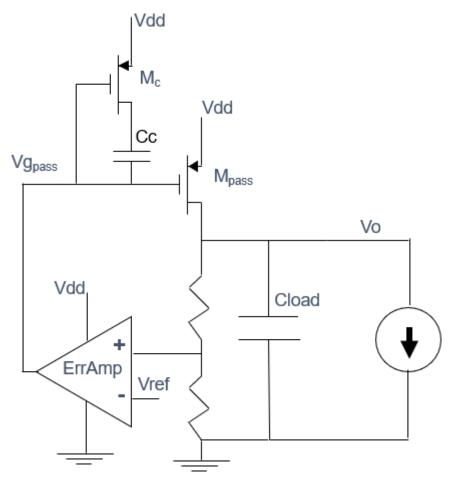

Ilustración 19. Esquema del sistema bias adaptativo.

En esta imagen se puede observar un esquema simplificado del funcionamiento del bias adaptativo. La copia de corriente se obtiene a través del voltaje de puerta del transistor de paso y se escala para obtener la corriente nominal diseñada en el amplificador de error, de forma que, en caso de haber menor corriente de la nominal, se seguiría teniendo la misma relación de corrientes y, por lo tanto, la misma relación de gm y factor de calidad.

El hecho de usar el voltaje de puerta supone uno de los principales defectos que tiene el bias adaptativo. Esto se debe a que el voltaje de puerta del transistor de paso está sujeto a la velocidad máxima del bucle de realimentación y, por lo tanto, los cambios rápidos en la carga tardan en hacerse notar en la corriente de bias del amplificador. Además, debido a este problema, cuando el voltaje de puerta del transistor de paso es muy alto (por ejemplo, debido a picotazo de corriente o a inicio rápido de alimentación), no hay casi corriente de bias a través del amplificador de error y, por lo tanto, tardará mucho más en alcanzar el punto de estabilidad.

La ventaja que tiene este método además de poder compensar corrientes menores a las nominales es que puede ser aplicado sin mayor dificultad en cualquier LDO, siendo así una herramienta muy versátil.

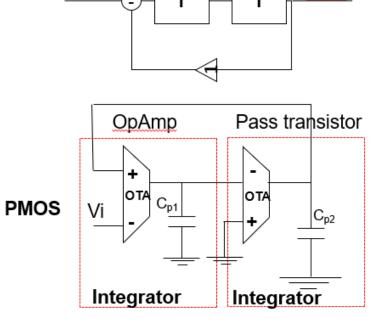

# 3.2 Pole-Zero tracking

La técnica del bias adaptativo, si se mira desde otro punto de vista, se puede entender como un seguimiento de polos, es decir, a la vez que el polo de salida se reduce en frecuencia el polo interno (salida del amplificador de error) se reduce en frecuencia de igual forma. No obstante, cuando nos encontramos con una compensación tipo paralela como la que se utilizará en el ejemplo del capítulo siguiente, para mantener la misma Q será necesario que el zero (la

combinación de condensador y resistencia) a la salida del amplificador también siga el mismo desplazamiento frecuencial al cambiar la corriente de carga. Si se analiza en alto nivel se puede comprobar el efecto deseado de la siguiente forma:

Ilustración 20. Esquema simplificado mediante OTAs de compensación paralela.

$$Q' = \sqrt{\frac{Co}{Cc} * \frac{1}{gm1'gm2'Rc'^2}} \tag{40}$$

$$g_{m2}' = \frac{g_{m2}}{\sqrt{n}} \tag{41}$$

$$\begin{cases} g'_{m1} = \frac{g_{m1}}{\sqrt{n}} & (Bias \ adaptativo) \\ R'_{c} = \sqrt{n}R_{c} & (Seguimiento \ de \ polos \ y \ ceros) \end{cases}$$

(42)

$$Q' = \sqrt{\frac{Co}{Cc} * \frac{1}{\frac{\sqrt{n^2}}{\sqrt{n^2 + \sqrt{n}}} gm2gm1Rc^2}} = Q$$

$$\tag{43}$$

Como se puede ver, es necesario que la resistencia varíe en función de la raíz de la corriente. Para lograr esto se ha encontrado en la bibliografía un método que utiliza un transistor

como resistencia para lograr una variación cuadrática con la corriente. El esquema simplificado quedaría de la siguiente forma:

Ilustración 21. Esquema del circuito de seguimiento de polos y ceros.

El transistor se polarizará en región lineal para conseguir la relación resistencia-corriente requerida en pequeña señal como se puede ver en la fórmula:

$$gds \approx Ngmp$$

En zona lineal  $R_c = \frac{1}{gds} = \frac{1}{Ngmp}$

Donde N es la relación entre la nueva corriente y la nominal.

Además, el voltaje de bias se cogerá de la puerta del transistor de paso de la misma forma que se hacía con el bias adaptativo, de forma que se conseguirá un mejor matching entre los transistores.

#### 3.3 Bias dinámico

Debido al hecho de que el método de bias adaptativo requiere la utilización del voltaje en la puerta del transistor y por lo tanto tiene un slew rate bajo, puede llegar a ser necesario la utilización de algún método que permita solventar este problema. Cuando la corriente a la salida se reduce rápidamente, durante el tiempo que tarda el voltaje en la puerta del transistor en ajustarse, la diferencia de corriente termina cargando el condensador de salida y por lo tanto aumentado el voltaje de salida. En la bibliografía se encontró un método que aprovecha esta diferencia de voltaje a la salida debida a los cambios de corriente de carga para aumentar la transconductancia del amplificador de error y aumentar la velocidad de carga y descarga del condensador a la entrada del transistor de paso.

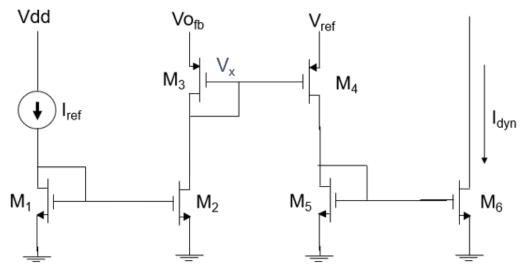

Ilustración 22. Esquema del circutio de bias dinámico.

En la imagen anterior los transistores que tienen la fuente conectada a los voltajes de referencia y feedback se diseñan para trabajar en la zona de sub-threshold, de esta forma, al existir una diferencia de tensión entre el voltaje de feedback y el voltaje de referencia habrá un cambio de corriente exponencial que se sumará al bias del amplificador de error.

El principal inconveniente de este método es que requiere también de una corriente de bias que puede afectar tanto al voltaje de salida como al rango de corrientes de carga. Dado que el voltaje de feedback está conectado a la fuente de uno de los transistores, la corriente de bias de éstos pasará a través de la red de feedback y, en caso de ser una corriente comparable a la corriente nominal a través de ésta, afectará al comportamiento del bucle. Además, si esta corriente de bias no se elimina y se inyecta junto con el bias adaptativo, siempre existirá una corriente mínima (corriente del bias dinámico) que reducirá el rango de corrientes que es capaz de soportar el LDO.

Dado que se pretende reducir al máximo posible el consumo estático para maximizar la eficiencia del regulador, conviene utilizar una red de feedback con bajo consumo de corriente. Sumado a esto, para mejorar la respuesta transitoria frente a cambios de corriente de carga, es necesario que la corriente de bias del circuito dinámico sea grande para que proporcione grandes picos de corriente. Con todo esto, es posible que este circuito de bias dinámico no sea el más adecuado en algunas ocasiones, por ello, en algunos casos es posible que se requiera sustituir el circuito de bias dinámico por un solo transistor con puerta conectada a Vout y fuente a Vref2 (0.8V). En este caso, el transistor en DC está polarizado en corte y una vez la diferencia de tensión entre los terminales de fuente y puerta supera al voltaje de threshold el transistor comienza a dejar

pasar corriente que se añadirá al bias adaptativo. En esta ocasión será el nodo Vref2 el que tenga que soportar la corriente dinámica generada por la diferencia de tensión. El principal inconveniente de este método es que para que se active deberá haber una diferencia de tensión de como mínimo el voltaje de threshold, por ello, conviene, en caso de permitirlo la tecnología utilizada, usar transistores de bajo threshold, así como aprovechar el voltaje Vout y una segunda referencia para maximizar el efecto.

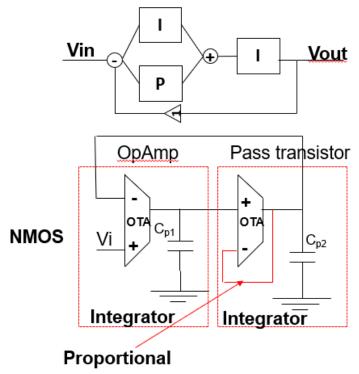

# Capítulo 4. Aplicación de bias dinámico y adaptativo

Una vez analizados y comprendidos los métodos para aumentar el rango de corrientes del LDO y mejorar la respuesta frente a cambios de corriente de carga transitorios se realizó una aplicación práctica de diseño de un LDO. Dado que éste será un LDO de ejemplo, se han escogido valores razonables de corriente de carga y frecuencia máxima de operación.

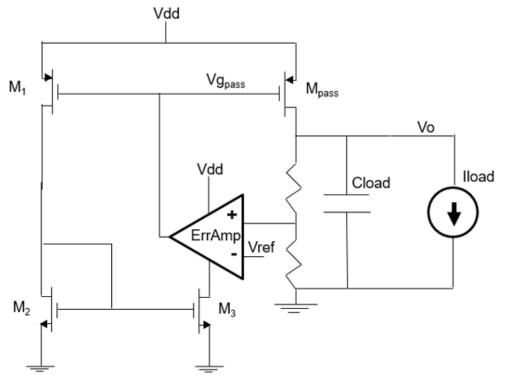

# 4.1 Transistor de paso

El primer paso para diseñar un LDO es escoger el tipo de transistor de paso que se va a utilizar. Para simplificar el diseño y evitar tener que utilizar un charge pump se escogió un transistor de paso tipo P. Una vez decidido el tipo de transistor, se montó el siguiente circuito en alto nivel:

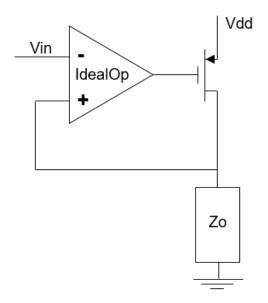

Ilustración 23. Circuito ideal para diseñar el transistor de paso.

En este circuito se utiliza un amplificador de error ideal para mantener estable el bucle de control y poder analizar la repuesta del transistor de paso de forma independiente. Una vez montado el circuito y con una corriente de carga de 10mA, se variaron los parámetros del transistor (longitud y ancho del canal) hasta ajustar los valores de voltaje overdrive (Vdsat) y transconductancia (gm). Aunque en este caso no fuera necesario al no tener restricciones en cuanto al PSRR, en caso de requerirse una mejora en el PSRR sería necesario ajustar la resistencia entre drenador y fuente del transistor (rds) para mejorar el divisor resistivo formado por rds y la resistencia de carga. Además, cabe tener en cuenta que las cargas reales constarán normalmente no sólo de corriente continua, sino que además pueden presentar una impedancia en pequeña señal a baja frecuencia. Esta impedancia en pequeña señal puede afectar al funcionamiento del LDO, así pues, cabría realizar las simulaciones con la impedancia AC estimada de la carga real lo cual se analizará en posteriores apartados.

#### 4.2 Red de feedback

El principal objetivo de la red de feedback es el de ajustar el voltaje de salida al voltaje de puerta necesario para polarizar el par diferencial. Para ello, se emplea un simple divisor resistivo y se obtiene la relación necesaria entre las resistencias operando con la fórmula del voltaje de salida.

$$V_{ofb} - V_{ref} = 0 (44)$$

$$V_{ofb} = Vref = \frac{V_o R_2}{R_1 + R_2} \tag{45}$$

$$V_o = V_{ref} \left( \frac{R_1}{R_2} + 1 \right) \tag{46}$$

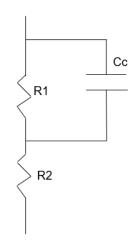

Para que haya la caida de tensión necesaria en las resistencias se requiere una corriente a través de ellas y, por lo tanto, un consumo extra. Dado que se pretende reducir el consumo en la medida de lo posible, es recomendable utilizar resistencias lo más grandes posible. No obstante, existe un límite debido a que la resistencia R2 queda en paralelo con la capacidad de puerta del transistor del par diferencial formando un polo que puede afectar a la estabilidad. Una posible forma de solucionar este problema sería mediante la inclusión de una capacidad en paralelo a R1 de forma que se genere un cero que compense el polo parásito.

Ilustración 24. Red de feedback.

# 4.3 Amplificador de error

El siguiente paso en el diseño de un LDO es escoger la estructura del amplificador de error que se va a utilizar. En este caso, para poder tener suficiente ganancia en el bucle, se utilizó una estructura folded cascode que aumenta la impedancia de salida y a la vez permite un mayor

output swing. En un principio, se diseñó el amplificador con un bias fijo para simplificar el diseño base y, además, poder comparar el funcionamiento con y sin bias adaptativo.

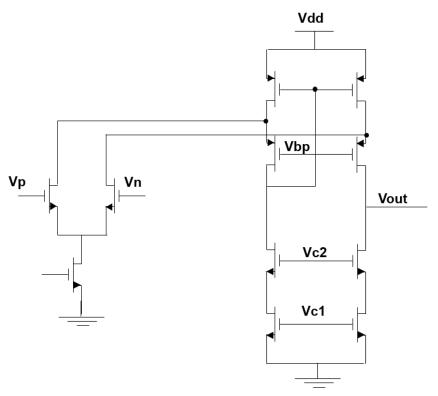

Ilustración 25. Circuito amplificador (Folded Cascode).

Se escogió en primer lugar una corriente que fuese proporcional a la corriente de bias para después ajustar los transistores del par diferencial para obtener la transconductancia necesaria. Esta misma corriente se utilizó como bias de los cascodos para reducir al mínimo el offset del amplificador. Una vez comprobado que la ganancia del amplificador se ajustaba a lo deseado, se pasó a diseñar la compensación del circuito.

# 4.4 Compensación

El diseño de la compensación se dividió en dos partes: un primer análisis en alto nivel con las simplificaciones y los modelos comentados anteriormente y un análisis posterior del circuito con la compensación ya implementada.

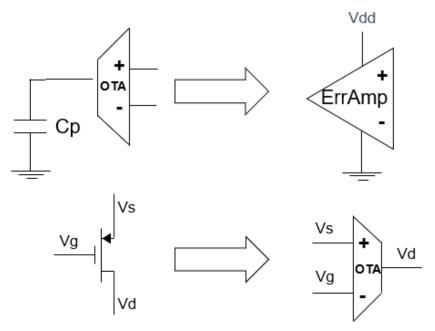

## 4.4.1 Análisis de alto nivel

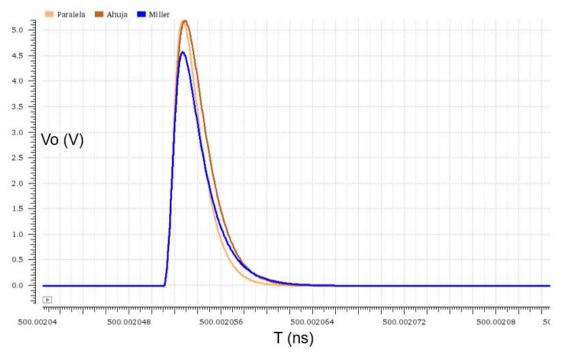

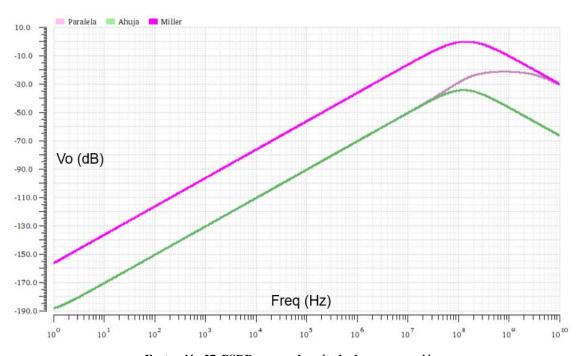

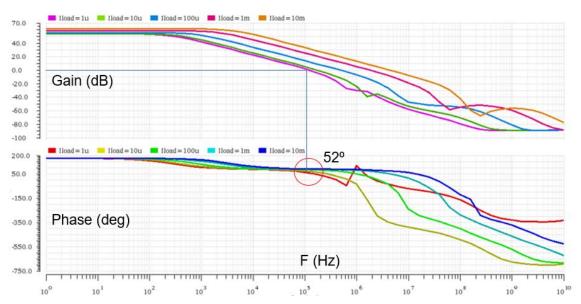

Utilizando los modelos y simplificaciones ya mencionados, se implementaron las tres técnicas más utilizadas para compensar y se verificaron los resultados de cada una.

Ilustración 26. Respuesta transitoria para cada método de compensación.

Ilustración 27. PSRR para cada método de compensación.

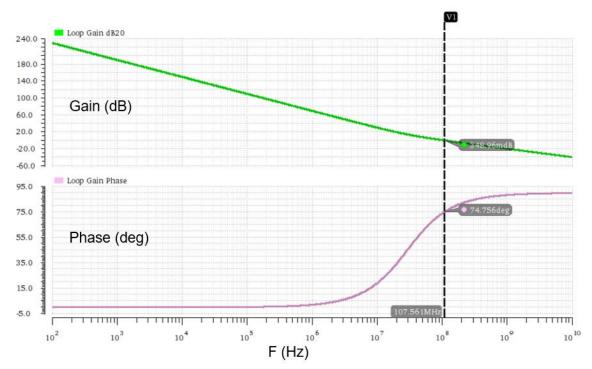

Dado que el principal objetivo es tratar de reducir el consumo de corriente y mejorar la eficiencia del LDO, se ha escogido una compensación paralela puesto que, además, resulta más sencilla de implementar y mejora el PSRR.

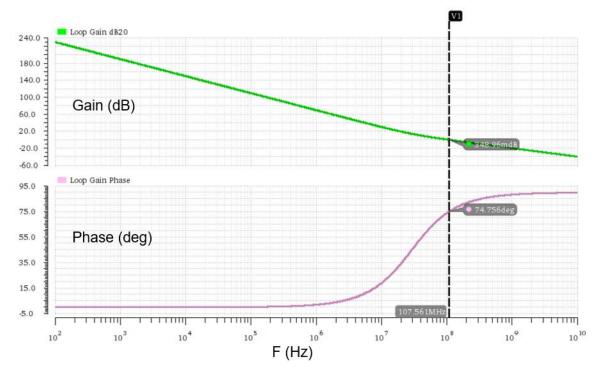

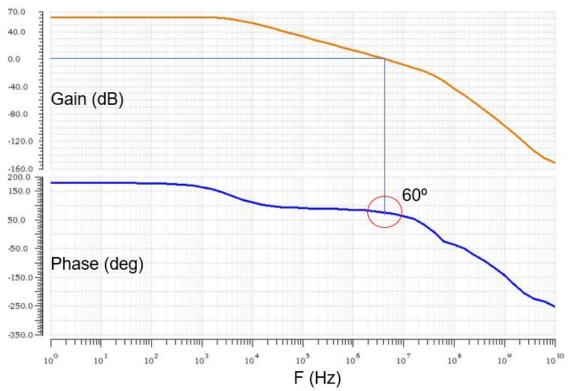

Con este modelo se ajustó la capacidad y la resistencia de la compensación hasta obtener los valores deseados de margen de fase (>60°) y ancho de banda (107.56M). Finalmente, se consiguieron los siguientes resultados:

Ilustración 28. Estabilidad del circuito ideal con cgs, cgd y cout.

# 4.4.2 Implementación en el circuito

Una vez aclarados los valores de resistencia y capacidad de compensación, se realizó la implementación en el LDO sin utilizar todavía el bias adaptativo, usando una resistencia y una capacidad ideales. A pesar de que en el modelo en alto nivel se conectó la compensación entre la puerta del transistor de paso y el gnd, al estar utilizando un transistor tipo P, se debe conectar entre la puerta y el nodo de alimentación puesto que la puerta debe seguir el voltaje de alimentación.

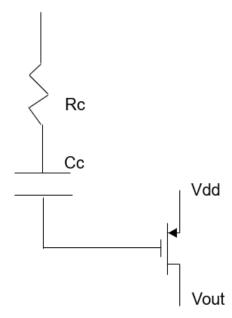

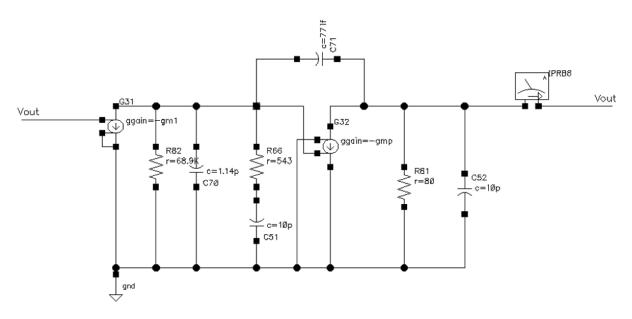

Ilustración 29. Transistor de paso y compensación paralela sin seguimiento de cero.

Una vez implementada la compensación se comprobó la estabilidad del circuito completo y se verificó que los valores de margen de fase, ganancia y ancho de banda fuesen los adecuados.

# 4.5 Bias adaptativo

Una vez comprobado el correcto funcionamiento del circuito con un bias fijo, se pasó a implementar la técnica antes explicada de bias adaptativo. En una primera versión, simplemente se utilizó el voltaje en la puerta del transistor de paso para polarizar la fuente de corriente tipo P del amplificador de error con el escalado adecuado y, además, mediante un espejo de corriente se obtuvo la corriente saliente necesaria para polarizar los cascodos y las ramas del par diferencial. Más adelante se cambiará esta configuración para facilitar la inclusión del bias dinámico.

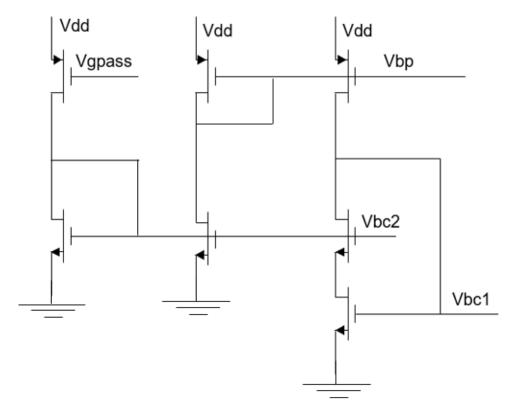

Ilustración 30. Circuito diseñado del bias adaptativo.

Además, puesto que se ha utilizado una compensación paralela, fue necesario implementar el método del seguimiento de polos y ceros. Para ello, se sustituyó la resistencia por un transistor tipo P conectado entre el condensador y el voltaje de alimentación. De esta forma, al conectar el voltaje de puerta al mismo nodo que el del transistor de paso, en DC no habrá corriente y, por lo tanto, el voltaje Vsd será cero. Al no haber caída de tensión entre los terminales de fuente y drenador, el transistor quedará polarizado en zona lineal y, por lo tanto, su resistencia Rds será proporcional a la raíz de la variación de corriente tal y como se deseaba conseguir.

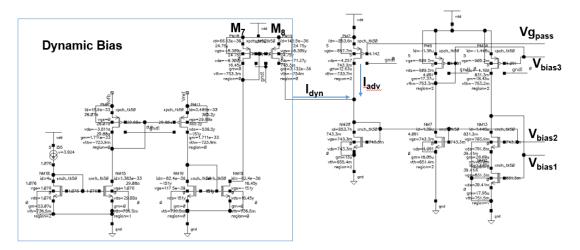

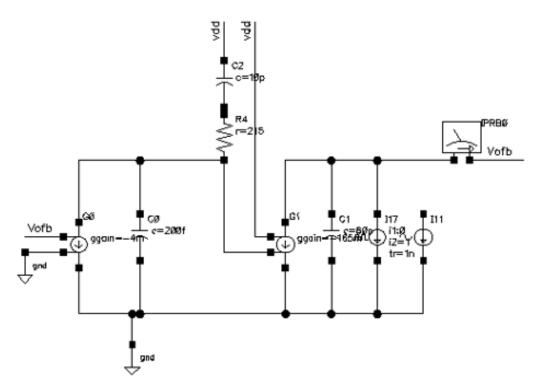

#### 4.6 Bias dinámico

Dado que en este circuito no hay especificaciones en cuanto a la respuesta transitoria para corrientes de carga, se optó por utilizar un circuito que, a pesar de no mejorar demasiado el transitorio, tiene un consumo más reducido. El circuito sería el primero de los comentados en el apartado de bias dinámico. Para implementarlo, simplemente se utilizó una corriente razonablemente pequeña y se ajustaron los transistores para que trabajen en saturación a excepción de los dos que realizan la comparación de tensiones.

# Capítulo 5. Simulaciones

Conforme se fue implementando el circuito se fueron realizando las simulaciones oportunas tanto del modelo ideal como del circuito real. Una vez implementado el LDO y las técnicas de bias adaptativo y bias dinámico se realizaron las simulaciones finales incluyendo respuesta transitoria de corriente, ruido y power-on.

### 5.1 Modelo ideal

Las primeras simulaciones que se hicieron fueron con el modelo ideal tanto con resistencias de salida del amplificador de error y del transistor de paso como sin ellas. El análisis sin resistencias se realizó previamente para hacer una estimación de la compensación dado que si no presenta inestabilidad al añadir las resistencias tampoco la presentará.

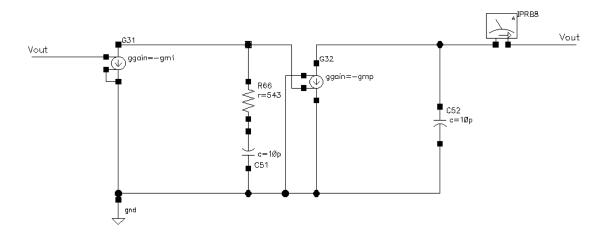

Ilustración 31. Modelo ideal del LDO mediante VCCS.

De este primer modelo se extrajo únicamente la respuesta del bucle abierto y de ella los parámetros de ganancia y margen de fase. Para ello, se utilizó el elemento iprobe y se realizó un análisis de estabilidad. Es importante a la hora de realizar un análisis en bucle abierto saber en qué punto se debe abrir el bucle dado que, para obtener resultados fiables, se deben cortar todos los bucles que haya. En este caso, dado que no existen más bucles que el principal, se optó por colocar el iprobe entre el voltaje de salida y la red de feedback. Esta fue la respuesta obtenida:

Ilustración 32. Estabilidad obtenida mediante el circuito ideal.

Tras haber realizado la primera implementación del circuito sin bias adaptativo ni bias dinámico, se amplió el modelo para incluir las resistencias y obtener los valores de margen de fase y ganancia, esta vez ya más cercanos a los que se podría esperar en el circuito real.

Ilustración 33. Modelo del LDO con resistencias de carga y de salida del amplificador.

Ilustración 34. Estabilidad modelo ideal con resistencias de carga y salida del amplificador.

Para poder realizar un análisis del PSRR del circuito, se cambió el modelo ligeramente quedando de esta forma:

Ilustración 35. Modelo modificado para simular ruido de alimentación (PSRR).

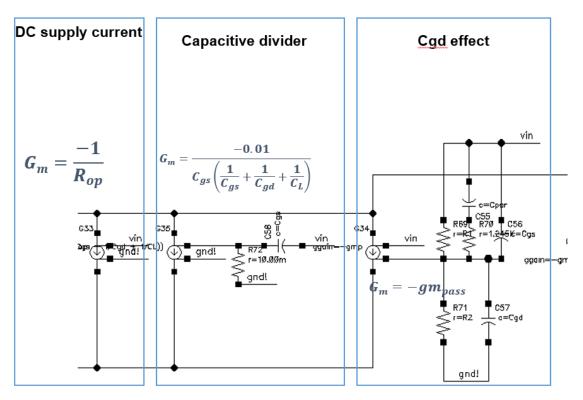

No obstante, de esta forma resulta complicado comprender el origen del ruido de alimentación y sus causas. Por ello, se calcularon en base a las fuentes que se descubrieron en apartados anteriores las fórmulas de cada una de ellas y se añadieron como fuentes ideales a la salida, pudiendo comprobar de esta forma qué fuente afecta en cada zona frecuencial.

Ilustración 36. Modelo del ruido de alimentación separado por fuentes.

Con este modelo se consiguieron los siguientes resultados:

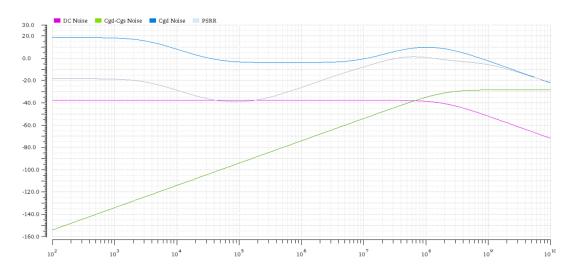

Ilustración 37. Fuentes de ruido de PSRR

Aquí se puede ver de forma mucho más sencilla el origen de cada uno de los polos y ceros del PSRR.

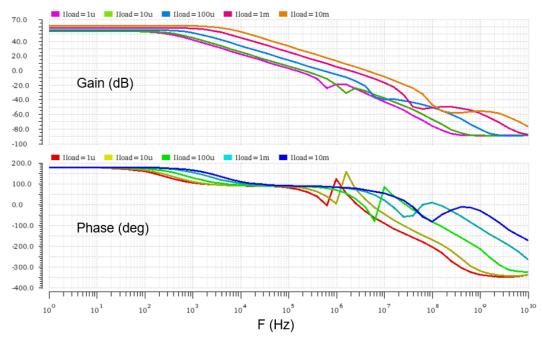

## 5.2 LDO base

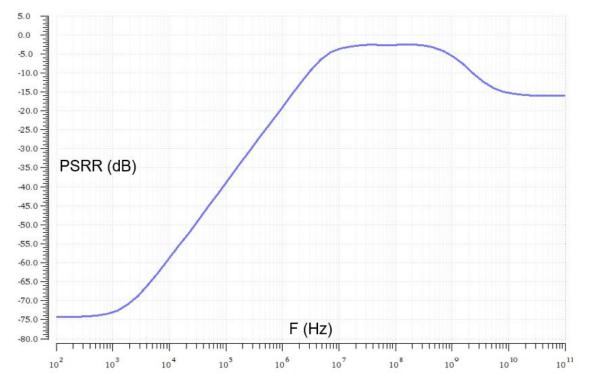

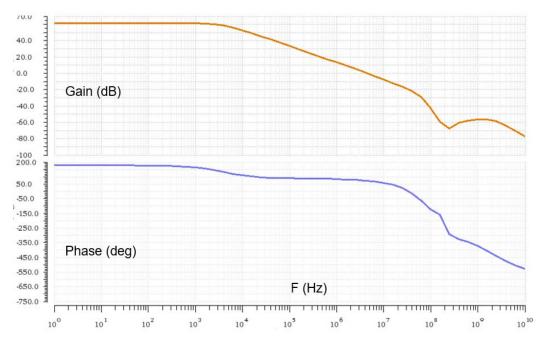

Una vez implementado el circuito y analizada la respuesta ideal que se espera, se creó un testbench donde se realizaron los análisis de margen de fase, ganancia y PSRR con el circuito base. El componente iprobe se colocó en el mismo lugar que en el circuito ideal a pesar de que en el circuito real la capacidad Cgd del transistor de paso forma un bucle interno haciendo de capacidad de Miller. No obstante, este efecto no llega a afectar al análisis de estabilidad en cuanto a elección del punto de corte del bucle. Los resultados obtenidos fueron los siguientes:

Ilustración 38. Estabilidad del circuito real.

Ilustración 39. PSRR del circuito real.

Se puede observar que, en principio, se obtienen valores de margen de fase y ganancia en DC similares a los del modelo ideal. En cuanto al PSRR, la gráfica también se aproxima a la esperada en simulaciones previas.

Tras haber realizado las simulaciones del circuito base, se concluyó que el diseño funcionaba tal y como se esperaba con un margen de fase superior a 60° y una ganancia de 60dB. El siguiente paso fue comprobar el efecto de reducir la corriente de carga sin la utilización del bias dinámico y del adaptativo.

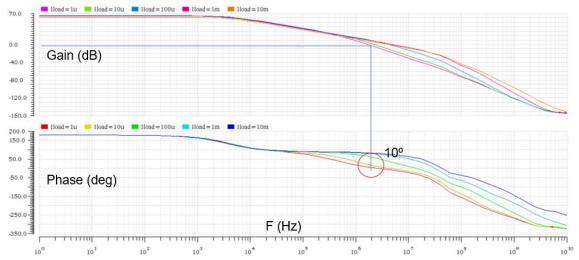

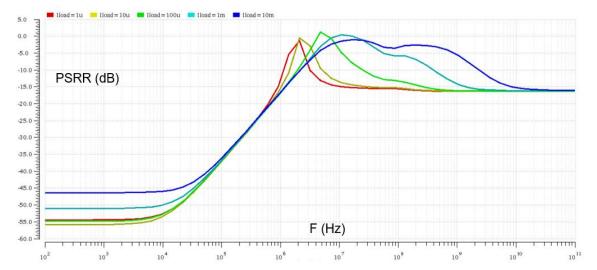

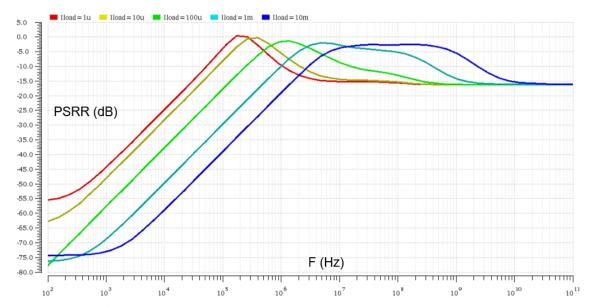

Ilustración 40. Estabilidad del circuito real con diferentes corriente de carga.

Ilustración 41. PSRR del circuito real con diferentes corrientes de carga.

Como se esperaba, el margen de fase se ve reducido debido al hecho de que el polo de salida se desplace hacia la izquierda mientras que el polo interno se mantiene en el sitio. Con esto se comprobó la necesidad de los métodos propuestos en este trabajo.

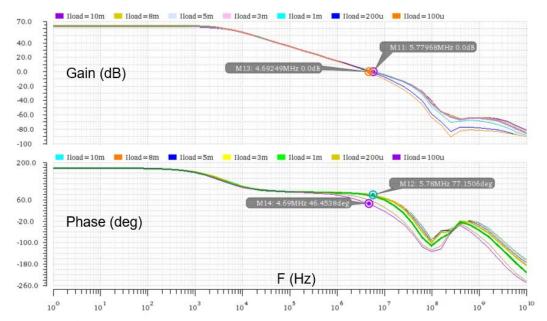

## 5.3 Bias adaptativo

Una vez comprobada la necesidad de este método, como ya se ha comentado, se realizó su implementación en el circuito y se volvieron a realizar las simulaciones tanto con la corriente nominal de carga como con las corrientes reducidas.

Ilustración 42. Estabiliad del ciruito real con bias adaptativo.

En primer lugar, cabe destacar que se obtiene aproximadamente el mismo margen de fase y la misma ganancia con corriente nominal, por lo tanto, el bias adaptativo no afectará al funcionamiento normal.

Ilustración 44. Estabilidad del circuio real con bias adaptativo para diferentes corrientes de carga.

Ilustración 45. PSRR del circuito real con bias adaptativo con diferentes corrientes de carga.

Lo siguiente que se observa es que para bajas corrientes se pierde margen de fase. Esto se debe principalmente, como se puede ver, a que a pesar de que ambos polos se muevan hacia la izquierda, el cero sigue fijo. Por ello, se comprueba que es necesario añadir la técnica de seguimiento de polos y ceros. Aunque en principio el margen de fase debería caer más al no utilizar el seguimiento de polos y ceros, dado que existe una capacidad de Miller debida a la Cgd, para bajas corrientes de carga es esta compensación la que domina, siendo sólo necesario el bias adaptativo.

Cuando se añade el seguimiento de polos y ceros, se obtiene la siguiente respuesta:

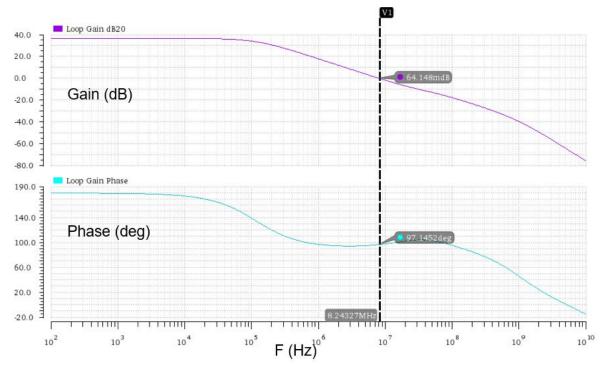

Ilustración 46. Estabilidad del circuito con bias adaptativo y seguimiento de ceros para diferentes corrientes.

Ilustración 47. PSRR del circuito con bias adaptativo y seguimiento de ceros para diferentes corrientes.

Ahora ya se consigue mantener aproximadamente el mismo margen de fase con una ligera caída. Esta caída se descubrió que se debe al hecho de haber utilizado un par diferencial tipo N. Al ser de diferente tipo que el transistor de paso, la variación de gm y Rds en función de la corriente difiere ligeramente entre ellos.

Otra cosa importante que se observa es el aumento de la ganancia en baja frecuencia. Esto se debe a que, mientras que la gm depende de la raíz de la variación de corriente, la Rds depende de la inversa de la variación y, por lo tanto, ésta última aumenta más rápidamente que la gm, dando lugar a un aumento de la ganancia.

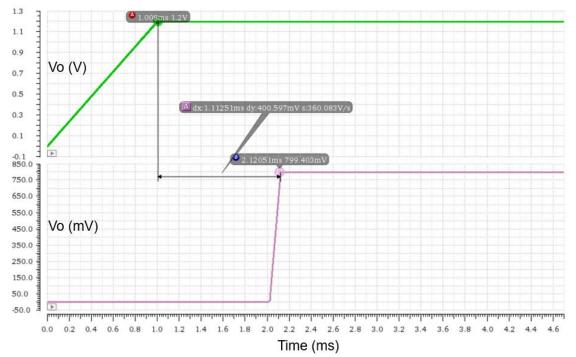

Las dos últimas simulaciones que se realizaron fueron el transitorio de corriente de carga y el power-on del circuito. Para el transitorio de corriente se utilizó una resistencia controlada por voltaje de forma que el cambio de corriente de carga fuera de No-Load (corriente casi nula) a Full-Load (corriente nominal), de forma que se pudiese comprobar el apagado y encendido de los posibles circuitos conectados a la salida. Para el power-on simplemente se añadió una rampa en alimentación entre 0V y 1.2V.

Ilustración 48. Respuesta transitoria frente a rampa de subida de voltaje de entrada.

En primer lugar, analizando el power-on se puede ver que hay un retardo bastante notorio entre que se termina de activar la alimentación y se fija el voltaje de salida del LDO. Tras analizar el circuito, se comprobó que el problema se debe al hecho de que el bias adaptativo requiere que en la puerta del transistor de paso haya un voltaje suficientemente bajo como para que los transistores del espejo de corrientes no estén en corte. Al iniciar el power-on, al ser un transitorio rápido, el voltaje en la puerta del transistor de paso trata de seguir al voltaje de alimentación y, por lo tanto, cuando termina de establecerse la alimentación, el nodo de puerta tiene la misma tensión, impidiendo que circule suficiente corriente por el amplificador. No obstante, la poca corriente que circula proporciona suficiente ganancia al amplificador como para poder descargar lentamente el nodo de puerta.

En cuanto al transitorio de corriente, se puede observar que hay una bajada en el voltaje de salida bastante notable que podría llegar a repercutir en el funcionamiento de los circuitos de carga. Esta caída de tensión se debe a la diferencia de tiempos entre la subida de la corriente de salida y la bajada del voltaje en la puerta del transistor de paso. Dado que se ha utilizado un tiempo de subida muy pequeño, el bucle principal se ve incapaz de reaccionar con la misma velocidad, de forma que la corriente a través del transistor tarda más en incrementarse. La diferencia de corrientes entre la corriente a través del transistor y la corriente de carga se obtiene como descarga del condensador de salida haciendo que el voltaje de salida disminuya.

Los dos problemas que se han comentado se pueden solventar, o como mínimo paliar, al implementar el bias dinámico, como se explicará a continuación.

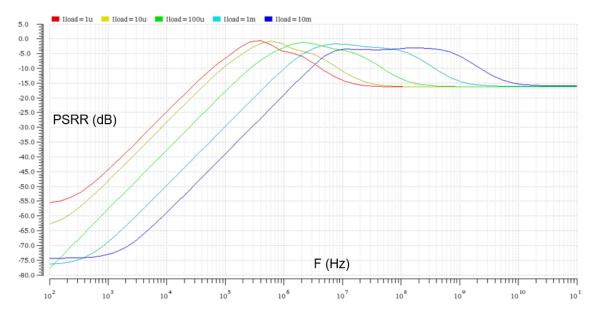

#### 5.4 Bias dinámico

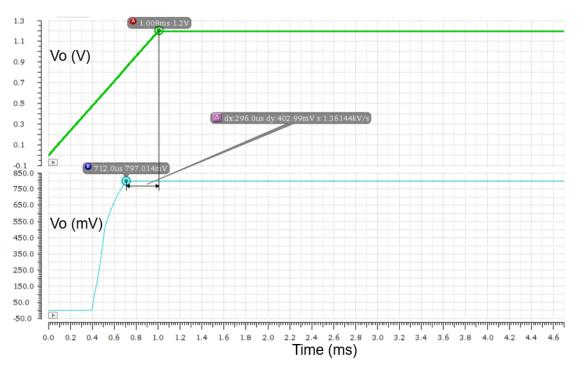

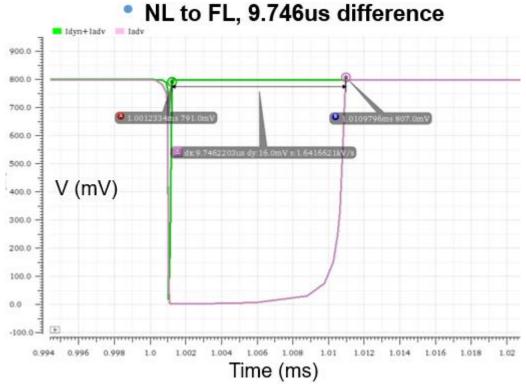

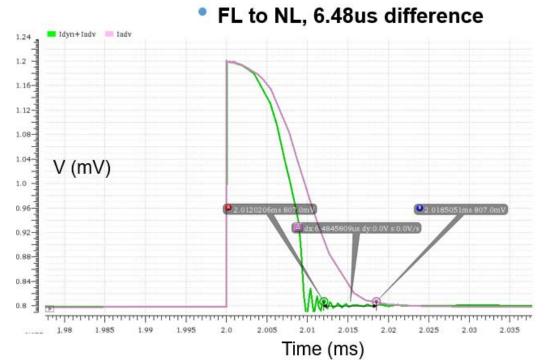

Como ya se ha comentado, tras implementar el bias dinámico, lo principal es analizar si los problemas encontrados en las respuestas transitorias se han logrado solventar. Las respuestas obtenidas son las siguientes:

Ilustración 49. Respuesta transitoria frente a rampa de subida de voltaje de entrada.

Ilustración 50. Transitorio de corriente no-load a full-load.

Ilustración 51. Transitorio de corriente full-load a no-load.

Se puede observar que, para el caso del power-on, se consigue reducir de forma sustancial el tiempo de establecimiento del voltaje de salida, dado que la corriente extra añadida al bias del amplificador de forma dinámica sirve para descargar el nodo de la puerta del transistor de paso y evitar que se enganche. En cuanto a la caída de tensión debida al pico de corriente, se consigue reducir bastante, aunque todavía tendría margen de mejora.

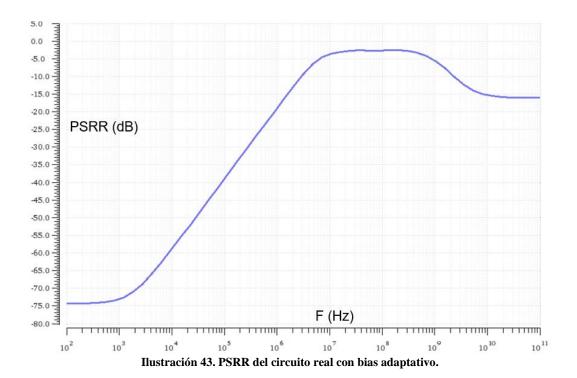

Finalmente, se comprobó que el rango de corrientes siguiese siendo el mismo, obteniendo las mismas gráficas que para el bias adaptativo. En este caso se puede ver que el rango de corrientes se ha reducido puesto que para bajas corrientes se pierde el margen de fase y, por ello, se obtuvo una gráfica para tratar de obtener el límite para 60°.

Ilustración 52. Estabilidad del circuito con bias dinamico y adaptativo para diferentes corrientes.

A pesar de que el rango sigue siendo más que aceptable, se trató de analizar el problema. Esta reducción de margen de fase se debe, principalmente, a la corriente fija que añade el bias dinámico, evitando que la corriente a través del amplificador de error siga disminuyendo.

# Capítulo 6. Conclusiones y trabajo futuro

Este trabajo se ha centrado principalmente en la búsqueda y análisis de diferentes métodos de lograr un LDO que pueda ser utilizado en diferentes circuitos con diferentes corrientes de carga. Además, se ha presentado un método basado en bucles de control y bloques en alto nivel para poder analizar tanto los LDO como cualquier amplificador multietapa de forma mucho más sencilla.

Tras haber analizado los métodos convencionales basados en la configurabilidad del tamaño del transistor de paso y en el uso de corrientes fijas que proporcionen un mínimo de corriente de polarización, se ha comprendido que estos métodos suponen un consuma extra de corriente y por lo tanto una reducción de la eficiencia considerable. La configurabilidad del transistor de paso supone un aumento de la lógica, los registros de control, el área del chip y el consumo.

Tras analizar diversos papers se ha encontrado un método basado en corriente adaptativa que permite ajustar los polos y los ceros del LDO para que sigan la variación del polo de salida debido a la variación de corriente de carga. Con esto se ha podido comprobar que se consigue mantener el margen de fase alto incluso con cargas de corriente muy bajas. Además, se ha logrado comprender perfectamente el funcionamiento de este método haciendo uso de la metodología basada en la teoría de bucles de control. No obstante, se ha descubierto que el bias adaptativo ralentiza mucho la respuesta del bucle de control y puede llegar a suponer un gran problema en el power-on del circuito y los picos de corriente de carga. Otro problema que se ha encontrado es que a pesar de que en bajas corrientes el regulador permanezca estable, debido a la baja corriente la mayoría de transistores entran en zona de sub-threshold. Aunque en principio esto no supone demasiado problema, puede hacer que falle en simulación Montecarlo. Finalmente se descubrió que se perdía ligeramente margen de fase en bajas corrientes debido al bajo emparejamiento del transistor de paso con los transistores del par diferencial. Esto se debe principalmente a que el transistor de paso en tipo P y los del par diferencial tipo N y por lo tanto no están tan parejos.

Para solventar el problema de lentitud del bias adaptativo se implementó un método de bias dinámico que logre aumentar la corriente del amplificador cuando el voltaje de salida varíe de su valor nominal. Para ello se utilizó un sistema encontrado en la bibliografía. Con este método se consigue aumentar temporalmente la corriente del amplificador y por lo tanto su ganancia, gracias a esto se mejora la respuesta del power-on y del transitorio de corriente. El principal inconveniente de este circuito es la corriente de polarización que requiere. Esta corriente se extrae tanto del nodo de feedback como del nodo de referencia y por lo tanto si esta es mayor que la del feedback afecta al voltaje de salida. Además, dicha corriente se añade a la corriente del bias adaptativo y por lo tanto limita la corriente mínima que es capaz de controlar el LDO.

Con todo esto, como trabajo futuro habría que cambiar el amplificador para que utilizase un diferencial tipo P y estuviese más emparejado con el transistor de paso. Además, habría que mejorar el bias dinámico para que no afecte al voltaje de salida, para ello se podría tratar de utilizar una corriente de bias bastante menor que la que pasa a través del feedback y añadir una corriente DC a la salida del bias dinámico de forma que solo las variaciones de corriente se sumen a la corriente del bias adaptativo. Otro método que podría ser utilizado es sustituir el circuito por un único transistor con fuente conectada a Vref y puerta conectada al voltaje de feedback.

# Capítulo 7. Bibliografía

- [1] Raveesh Magod Ramakrishna "Ultra-low Quiescent Current NMOS Low Dropout Regulator With Fast Transient response for Always-On Internet-of-Things Applications" *IEEE Journal of Solid-State Circuits*, vol. 55, no. 9, pp. 2356–2367, April 2018.

- [2] Sai Kit Lau; Philip K. T. Mok; Ka Nang Leung "A Low-Dropout Regulator for SoCWith Q-Reduction" *IEEE Journal of Solid-State Circuits*, vol. 42, no. 3, pp. 658–664, February 2007.

- [3] Yat-Hei Lam; Wing-Hung Ki "A 0.9V 0.35 µm Adaptively Biased CMOS LDO Regulator with Fast Transient Response" 2008 IEEE International Solid-State Circuits Conference Digest of Technical Papers, February 2008.

- [4] Jungsu Choi; Jungeui Park; Wooju Jeong; Junsang Lee; Seok Lee; Jayang Yoon; Jaehoon Kim; Joongho Choi "Design of LDO Linear Regulator with Ultra Low-Output Impedance Buffer" 2009 International SoC Design Conference (ISOCC), November 2009.

- [5] J. Pérez-Bailón; A. Márquez; B. Calvo; N. Medrano "A Power Efficient LDO Regulator for Portable CMOS SoC Measurement Systems" 2017 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), July 2017.

- [6] Colaboradores de Wikipedia. Wikipedia: State-space representation; Wikipedia, La enciclopedia libre, 2020 [consulta: 10 de Enero del 2019]. Disponible en <a href="https://en.wikipedia.org/wiki/State-space\_representation">https://en.wikipedia.org/wiki/State-space\_representation</a>

- [7] Colaboradores de Wikipedia. Wikipedia: Teorema de Routh-Hurwitz; Wikipedia, La enciclopedia libre, 2020 [consulta: 10 de Enero del 2019]. Disponible en <a href="https://es.wikipedia.org/wiki/Teorema\_de\_Routh-Hurwitz">https://es.wikipedia.org/wiki/Teorema\_de\_Routh-Hurwitz</a>

- [8] Norman S. Nise. *Control Systems Engineering*. USA: John Wiley & Sons, Inc. <u>ISBN</u> <u>0-471-44577-0</u>.