Document downloaded from:

http://hdl.handle.net/10251/144714

This paper must be cited as:

Pérez-López, D.; Gasulla Mestre, I.; Capmany Francoy, J. (2017). Multi-purpose programmable optical chips. Optical Society of America (OSA). 1-3. https://doi.org/10.1364/SPPCOM.2017.SpW3F.1

The final publication is available at https://doi.org/10.1364/SPPCOM.2017.SpW3F.1

Copyright Optical Society of America (OSA)

Additional Information

# Multi-purpose programmable optical chips

## Daniel Pérez,<sup>1</sup> Ivana Gasulla,<sup>1</sup> and José Capmany<sup>1\*</sup>

<sup>1</sup>ITEAM Research Institute, Universitat Politècnica de València, Camino de Vera s/n, 46022 Valencia, Spain <u>*jcapmany@iteam.upv.es*</u>

**Abstract:** We review multi-purpose optical chip architectures based on optical FPGA reconfigurable core. We provide configuration examples for the synthesis of interferometric lattice filters and universal linear interferometers on a single software-defined integrated photonic hardware.

OCIS codes: (130.3120) Integrated optics; (250.4745) Optical processing devices; (250.5300) Photonic integrated circuits

#### 1. Introduction

In line all-optical signal processing is essential [1,2] to leverage on the unique properties of photonic devices to perform flexible, broadband and reconfigurable operations over high-speed, multi-format signals, which will be the basis of emerging information and communication (ICTs) systems designed to support and convey a plethora of different services. Many successful approaches have been demonstrated so far that can perform specific operations or functionalities over specific signal formats and most of them have been implemented either on free-space optics or in optical fiber format [1]. The experimental demonstrations of these approaches have highlighted two main limitations that preclude the penetration of optical signal processing in massive takeover applications. The first limitation is connected to their bulky, unstable and power-consuming nature, while the second is the high cost incurred in the fabrication and assembly of systems that are capable of performing one or perhaps a few number of functionalities.

A solution to both limitations resides in [3, 4]: a) Designing a multiple-purpose processor that supported by a single hardware architecture may be able to perform multiple tasks by suitable programming of control signals and b) Integrating this platform in a photonic chip. The final objective is to obtain a new generation of devices that we call Multi-purpose programmable optical chips. In this paper we report on recent advances in this concept.

### 2. Multipurpose programmable optical chip architecture

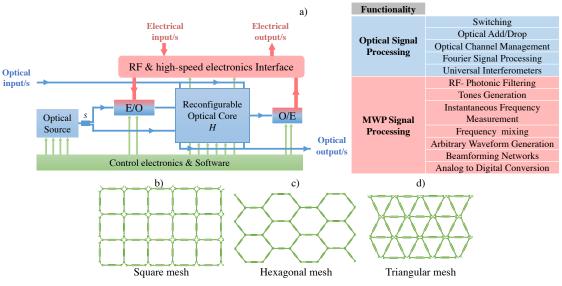

Figure 1 illustrates the processor architecture composed by subsystems that are enabled by software when required for each application. It includes an optical source, electro-optic modulators opto-electronic photodetectors and a reconfigurable optical core. The latter must be a versatile subsystem capable of implementing different photonic integrated circuit topologies and design parameters. Although several multi-purpose designs have been demonstrated recently, most of them rely on the cascaded/combination of optical ring resonators (ORRs) and Mach-Zehnder Interferometers (MZIs) lacking in flexibility, and scalability.

Fig 1. Generic architecture of a multi-purpose programmable photonic processor (left). Table covering the main signal processing functionalities for all-optical and RF-photonic applications.

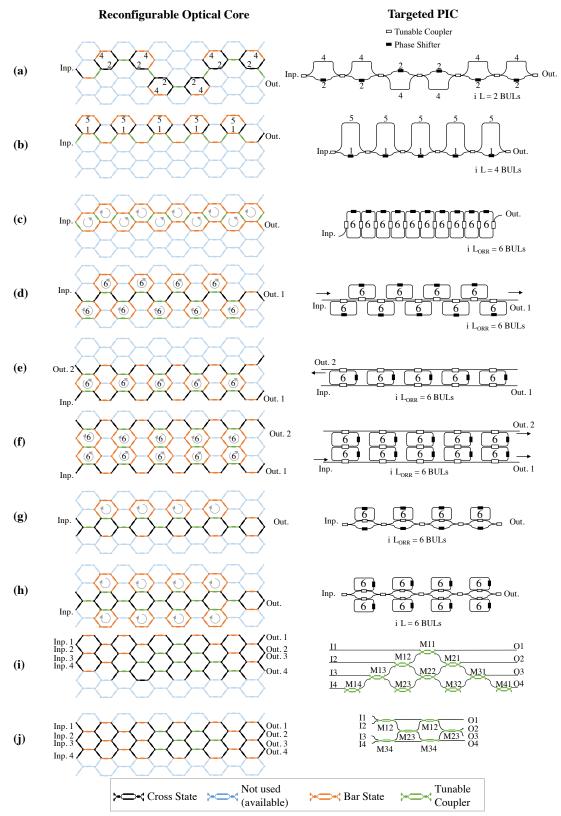

Fig 2. Hexagonal mesh configuration and targeted Photonic Integrated Circuit (a, b) 2-cascaded lattice FIR filters with arm difference ΔL equal to 2 and 4 BULs respectively. (c) SCISSOR structure of 10-coupled ring cavities, (d) Single channel CROW, (e) Double-channel CROW, (f) Twisted double-channel CROW, (g) Lattice ORR-loaded MZIs, (h) Lattice double-ORR-loaded MZIs, (i) Triangular and Rectangular (j) arrangement for universal interferometers. Note: Represented numbers indicates the light path length in BUL units.

An approach similar to that of FPGAs in electronics proposing the discretization of typical photonic integrated circuits into a square waveguide-mesh of beamsplitters (Fig.1 b) has been proposed in [5]. There, the beamsplitters can be implemented with unbalanced MZIs loaded with a phase shifter on each arm. The configuration of each beamsplitter shaping the mesh, define the light path and the relative phase at any point in the circuit and constitutes the most versatile approach for the reconfigurable optical core to date.

More recently, a hexagonal and a triangular (Fig. 1 c-d) waveguide-mesh topologies were proposed [6]. The hexagonal feature improved performance in terms of spatial tuning reconfiguration step, reconfiguration performance, switching elements per unit area and losses per spatial resolution, and enable the simplest implementation of both classic FIR and IIR photonic circuits and universal linear multiport devices, [6]. This work also defines the interferometric structure free spectral range (FSR) and its direct relationship with the Basic Unit Length (BUL) of each beamsplitter.

#### 3. Hexagonal waveguide-mesh based Core Design

The reconfigurable optical core, implemented using the hexagonal waveguide-mesh, enables synthesis of single(double)- input/ single(double)-output photonic integrated circuits alltogether with multiple-input/multiple-output designs enabling parallel processing. These photonic structures are typically at the core of fixed application specific processing systems.

Fig. 2 illustrates, as an example of versatility, 10 different photonic integrated circuits based on the same underlying hardware configuration. Fig. 2 (a,b) shows the configurations of each beamsplitter for the synthesis of finite impulse response (FIR) filters of  $6^{th}$  and  $5^{th}$  order respectively. Note that the free spectral range (FSR) can be set as well by varying the interferometric length.

Infinite impulse response filters can be designed as well and combined with FIR filters as reported by Fig.2 (c-h). Cascading this stages, more zeros/poles can be added and programmed to the filtering structure. Fig. 2(h) corresponds to the implementation of double-loaded MZIs where the independent position setting of the zeros/poles along the z-plane enable arbitrary magnitude or phase responses.

Finally, universal interferometric structures [7,8] performing multiple/input multiple/output linear operations that find applications in signal processing, quantum optics and microwave photonics can also be supported by the proposed hardware architecture. They consist of an arrangement of beamsplitter arrangements with phase shifting capabilities that propagate light in forward direction. The hexagonal waveguide mesh can perform the 2 arrangements proposed in the literature (triangular and rectangular) as shown in Fig. 2 (i, j).

### 4. Conclusions

We have proposed the generic architecture for multi-purpose optical chips. A hexagonal waveguide mesh of tunable couplers with phase shifting capabilities performs the reconfigurable optical core. We provide several examples of core configurations for the synthesis of interferometric lattice filters circuits together with the settings enabling universal linear interferometers.

#### References

[1] A.E. Willner, et al, "All-Optical Signal Processing," J. Lightwave Technol. 32, 660-680 (2014).

[2] "Birth of the programmable optical chip," Nature Photon. 10, 1 (2016).

[3] W. Liu et al., "A fully reconfigurable photonic integrated signal processor," Nature Photon. 10, 190-195 (2016).

[4] J. Capmany, I. Gasulla, and D. Pérez, "Microwave photonics: The programmable processor," Nature Photon. 10, 6-8 (2016).

[5] L. Zhuang, C.G.H. Roeloffzen, M. Hoekman, K-J. Boller, and A.J. Lowery, "Programmable photonic signal processor chip for radiofrequency applications," Optica **2**, 854-859 (2015).

[6] D. Pérez, I. Gasulla, J. Capmany y R. A. Soref, "Reconfigurable lattice mesh designs for programmable photonic processors," Optics Express , 24, 12093-12106 (2016).

[7] M. Reck, A. Zeilinger, H. J. Bernstein and P. Bertani, "Experimental realization of any discrete unitary operator," Phy. Rev. Lett., **73**, 58–61 (1994)

[8] W. Clements, P. Humphreys, B. Metcalf, W. Kolthammer y I. Walsmley, "Optimal design for universal multiport interferometers," Optica, **3**, 1460–1465 (2016).