# Escola Tècnica Superior d'Enginyeria Informàtica Universitat Politècnica de València

# Adaptation of High Performance and High Capacity Reconfigurable Systems to OpenCL Programming Environments MASTER DEGREE FINAL WORK

Master Degree in Computer Engineering

Author:Davide RussoTutor:Flich Cardo, JoséFirst External Tutor:Cilardo, AlessandroDirector Experimental:Tornero Gavilá, Rafael

Course 2019-2020

# Resumen

En este trabajo se va a realizar la adaptación de un sistema reconfigurable de cómputo basado en tecnologías de FPGAs hacia entornos de programación en OpenCL. El sistema reconfigurable forma parte de un prototipo de cálculo del proyecto Europeo MANGO que incluye 96 FPGAs. Con el fin de optimizar el uso y de obtener sus máximas prestaciones, se hace imprescindible una adaptación a entornos de programación de sistemas heterogéneos como OpenCL, lo cual simplifica su programación y uso. En este trabajo se realizarán todas las actividades necesarias para una correcta implementación de la capa software y hardware necesaria para su uso en OpenCL así como una evaluación de las prestaciones obtenidas y de la flexibilidad ofrecida por la solución aportada.

Este trabajo se ha llevado a término durante una estancia de cinco meses en la Universitat Politécnica de Valéncia. Esta estancia está vinculada a un acuerdo entre la Universitat Politécnica de Valéncia y la Università degli Studi di Napoli Federico II.

**Palabras clave:** Sistema de cómputo heterogéneos; PCI express; OpenCL; Xilinx runtime; Custom platform FPGA

# Abstract

In this work, we adapt a reconfigurable computer system based on FPGA technologies to OpenCL programming environments. The reconfigurable system is part of a compute prototype of the MANGO European project that includes 96 FPGAs. To optimize the use and to obtain its maximum performance, it is essential to adapt it to heterogeneous systems programming environments such as OpenCL, which simplifies its programming. In this work, all the necessary activities for correct implementation of the software and hardware layer required for its use in OpenCL will be carried out, as well as an evaluation of the performance obtained and the flexibility offered by the solution provided.

This work has been performed during an internship of 5 months. The internship is linked to an agreement between UPV and UniNa (Università degli Studi di Napoli Federico II).

**Keywords:** Heterogeneous computing system; PCI express; OpenCL; Xilinx runtime; Custom platform FPGA

# Contents

| Co  | Contents v |               |                                            |     |

|-----|------------|---------------|--------------------------------------------|-----|

| Li  | st of l    | Figures       | 3                                          | vii |

| Lis | st of 7    | <b>Fables</b> |                                            | ix  |

| Ac  | crony      | ms            |                                            | xi  |

| 1   | Intro      | oductio       | n                                          | 1   |

|     | 1.1        | Hetero        | ogeneous system for HPC application        | 1   |

|     | 1.2        | Standa        | ard vs custom FPGAs platform               | 2   |

|     | 1.3        | MAN           | GO infrastructure                          | 3   |

|     | 1.4        | Goals         | and Motivations of this Work               | 4   |

|     | 1.5        | Struct        | ure of the Document                        | 4   |

| 2   | Back       | kgroun        | d                                          | 7   |

|     | 2.1        | FPGA          | introduction                               | 7   |

|     |            | 2.1.1         | Architecture                               | 7   |

|     |            | 2.1.2         | Taxonomy                                   | 7   |

|     |            | 2.1.3         | Logic Block Architecture                   | 11  |

|     |            | 2.1.4         | Routing Architecture                       | 15  |

|     |            | 2.1.5         | I/O Architecture                           | 18  |

|     |            | 2.1.6         | Programming                                | 18  |

|     |            | 2.1.7         | Xilinx vs Intel Altera FPGAs               | 21  |

|     | 2.2        | Partia        | l Reconfiguration                          | 28  |

|     |            | 2.2.1         | Vivado Partial Reconfiguration design flow | 29  |

|     | 2.3        | Open(         | CL introduction                            | 30  |

|     |            | 2.3.1         | Platform Model                             | 30  |

|     |            | 2.3.2         | Memory Model                               | 31  |

|     |            | 2.3.3         | Execution Model                            | 32  |

|     |            | 2.3.4         | Programming Model                          | 35  |

|    |                 | 2.3.5   | OpenCL Framework                                     | 36 |

|----|-----------------|---------|------------------------------------------------------|----|

|    |                 | 2.3.6   | OpenCL Devices and FPGAs                             | 36 |

|    | 2.4             | SDAce   | cel Platform                                         | 37 |

|    |                 | 2.4.1   | Hardware Platform                                    | 38 |

|    |                 | 2.4.2   | Software Platform                                    | 50 |

|    |                 | 2.4.3   | Generating Platform files                            | 52 |

|    | 2.5             | Tools   |                                                      | 54 |

|    |                 | 2.5.1   | Xilinx Vivado Design Suite                           | 54 |

|    |                 | 2.5.2   | Xilinx SDAccel Development Environment               | 55 |

|    |                 | 2.5.3   | proFPGA prototyping system                           | 58 |

| 3  | Con             | tributi | on                                                   | 61 |

|    | 3.1             | Specif  | ication                                              | 61 |

|    |                 | 3.1.1   | Reference design specification                       | 61 |

|    |                 | 3.1.2   | Our design specification                             | 61 |

|    | 3.2             | Desig   | n                                                    | 62 |

|    |                 | 3.2.1   | Hardware Platform                                    | 62 |

|    |                 | 3.2.2   | Software Platform                                    | 77 |

|    |                 | 3.2.3   | Generating Platform files                            | 80 |

|    |                 | 3.2.4   | Installing the Platform                              | 82 |

|    |                 | 3.2.5   | Programming the FPGA                                 | 83 |

|    | 3.3             | Testin  | g                                                    | 84 |

|    |                 | 3.3.1   | Testing the correctness of the Platform installation | 84 |

|    |                 | 3.3.2   | Partial Reconfiguration workaround                   | 85 |

|    |                 | 3.3.3   | Area performance evaluation                          | 85 |

|    |                 | 3.3.4   | PCIe speed performance evaluation                    | 87 |

|    |                 | 3.3.5   | A real application: nnsim                            | 89 |

| 4  | Con             | clusior | 15                                                   | 97 |

| Bi | Bibliography 99 |         |                                                      |    |

# List of Figures

| 1.1  | Results for Classic DNNs                                    | 2  |

|------|-------------------------------------------------------------|----|

| 1.2  | MANGO Prototype                                             | 3  |

| 2.1  | FPGA architecture                                           | 8  |

| 2.2  | SRAM cell                                                   | 8  |

| 2.3  | Use of static memory cells                                  | 9  |

| 2.4  | Floating gate transistor                                    | 10 |

| 2.5  | Configurable Logic Block                                    | 12 |

| 2.6  | Basic Logic Element                                         | 12 |

| 2.7  | Illustration of tile based heterogeneity                    | 14 |

| 2.8  | Hierarchical-style FPGA                                     | 16 |

| 2.9  | Island-style FPGA                                           | 17 |

| 2.10 | A typical FPGA design flow starting from RTL specifications | 20 |

| 2.11 | LUT configuration                                           | 23 |

| 2.12 | Xilinx SLICEL I/O connection                                | 23 |

| 2.13 | Xilinx SLICEL architecture                                  | 24 |

| 2.14 | LUT configuration                                           | 25 |

| 2.15 | Xilinx DSP architecture                                     | 25 |

| 2.16 | Xilinx FPGA enabled by SSI Technology                       | 26 |

| 2.17 | ALM Block Diagram                                           | 27 |

| 2.18 | Example of 4-LUT                                            | 27 |

| 2.19 | Intel Altera DSP block                                      | 28 |

| 2.20 | Intel Altera DSP configuration                              | 28 |

| 2.21 | Rounting of Intel Altera FPGAs                              | 29 |

| 2.22 | The logical view of OpenCL Platform Model                   | 31 |

| 2.23 | The logical view of OpenCL Memory Model                     | 32 |

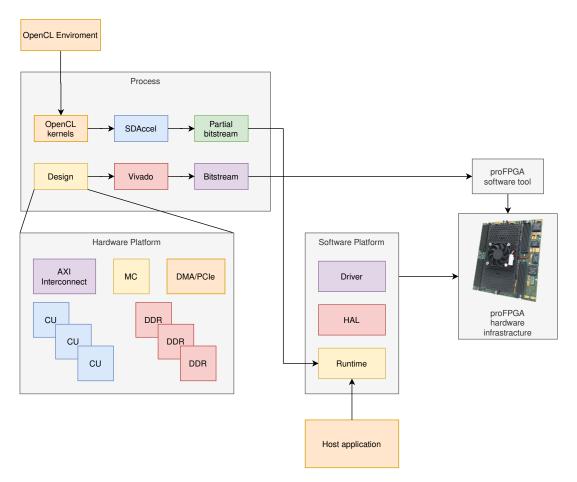

| 2.24 | Entire system                                               | 37 |

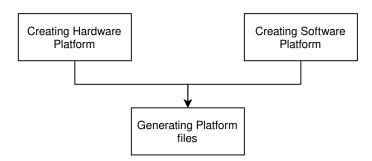

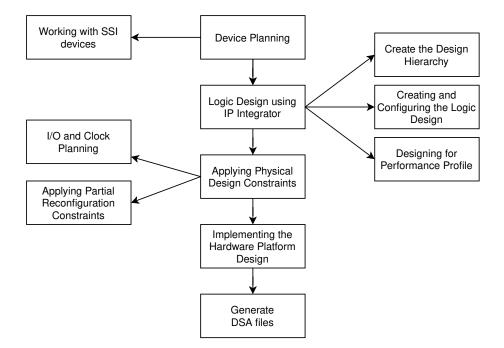

| 2.25 | Creation Platform flow                                      | 38 |

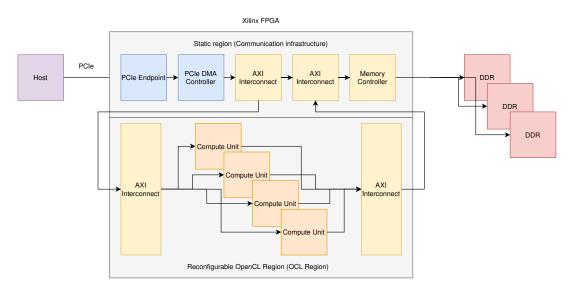

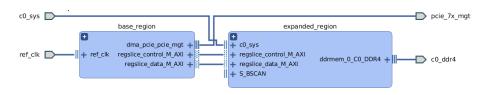

| 2.26 | Logical view of SDAccel Hardware Platform                                     | 39 |

|------|-------------------------------------------------------------------------------|----|

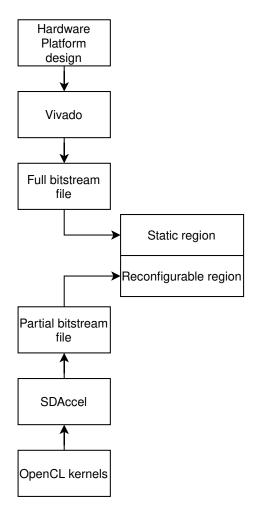

| 2.27 | Tools used to manage the SDAccel Hardware Platform                            | 39 |

| 2.28 | Hardware Platform creation and validation flow diagram                        | 41 |

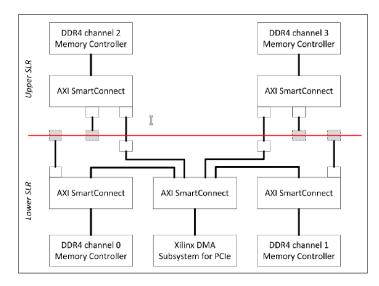

| 2.29 | Simplified representation of IP partitioning for controlled SLR cross-<br>ing | 43 |

| 2.30 | Top-Level Logic Hierarchy for Expanded Region                                 | 43 |

| 2.31 | Layers of the Software Platform                                               | 50 |

| 2.32 | Platform folder structure                                                     | 52 |

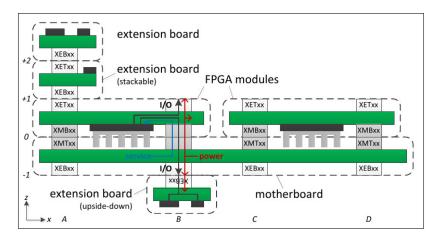

| 2.33 | The logical view of the proFPGA prototyping system hardware-side              | 58 |

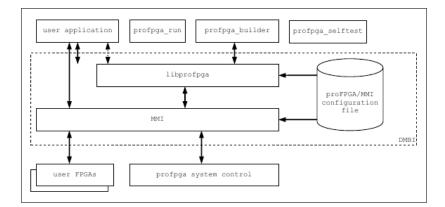

| 2.34 | The software architecture of the proFPGA prototyping system                   | 60 |

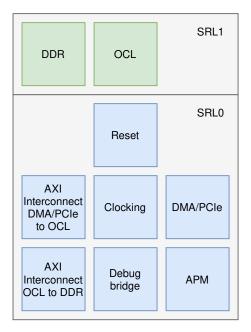

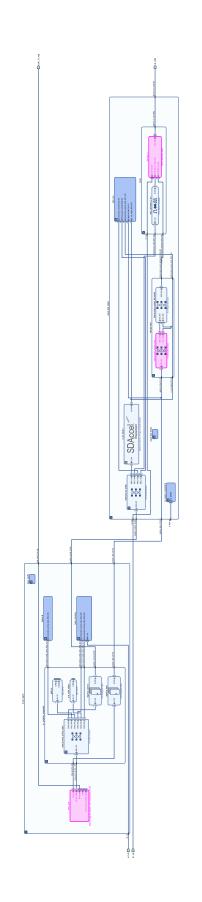

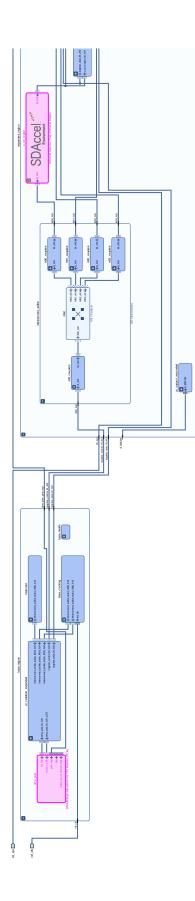

| 3.1  | Logical view of position of components in the FPGA                            | 62 |

| 3.2  | Use of SmartConnect IP                                                        | 64 |

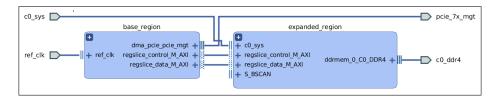

| 3.3  | Top-Level Logic Hierarchy of our design                                       | 65 |

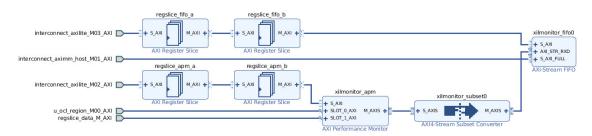

| 3.4  | AXI Interconnect DMA/PCIe to SDAccel OpenCL Programmable region IP            | 66 |

| 3.5  | AXI Interconnect SDAccel OpenCL Programmable region IP to DDR and to bypass   | 67 |

| 3.6  | Memory address in the design                                                  | 68 |

| 3.7  | Logic module for profiling                                                    | 69 |

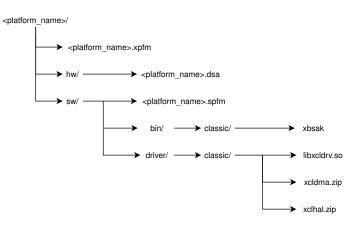

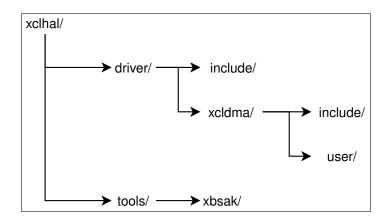

| 3.8  | XCL HAL folder structure                                                      | 80 |

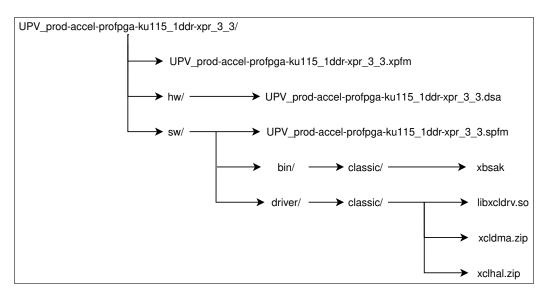

| 3.9  | Custom Platform folder structure                                              | 81 |

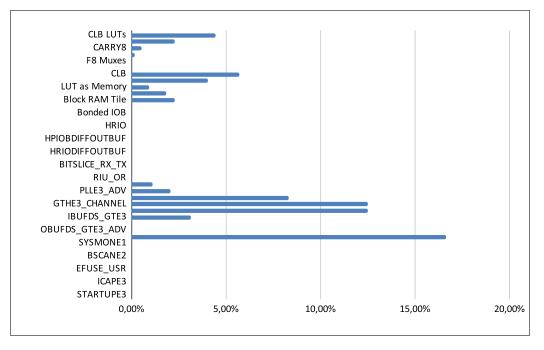

| 3.10 | Static region resource utilization chart                                      | 87 |

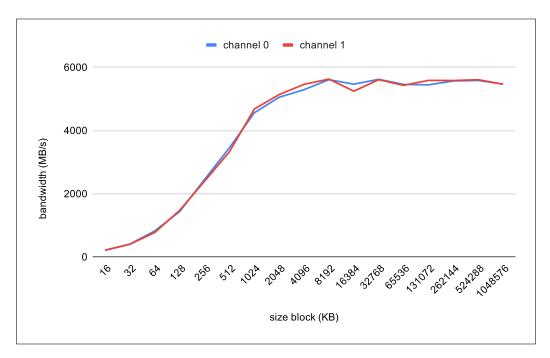

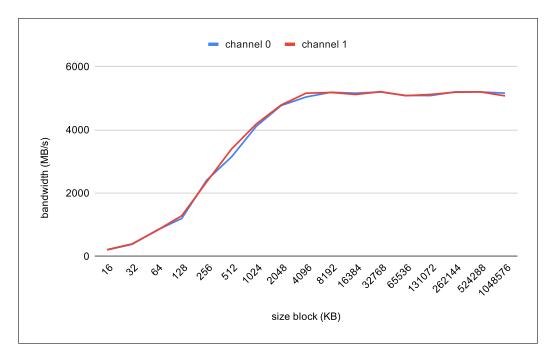

| 3.11 | Results of test of reading                                                    | 88 |

| 3.12 | Results of test of writing                                                    | 88 |

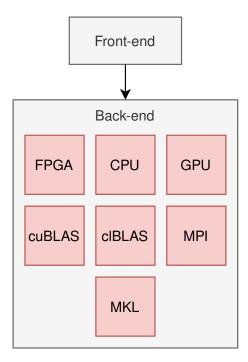

| 3.13 | Logical view of nnsim's software architecture                                 | 89 |

# List of Tables

| 2.1 | Meaning of Device ID bits                       | 52 |

|-----|-------------------------------------------------|----|

| 2.2 | Meaning of Subsystem ID bits                    | 52 |

| 3.1 | Meaning of Device ID bits of custom Platform    | 77 |

| 3.2 | Meaning of Subsystem ID bits of custom Platform | 77 |

| 3.3 | Static region resource utilization value        | 86 |

| 3.4 | nnsim's kernels performance estimate part 1     | 92 |

| 3.5 | nnsim's kernels performance estimate part 2     | 92 |

# Acronyms

AER Advanced Error Reporting.

AI Artificial Intelligence.

ALM Adaptive Logic Module.

**ALUT** Adaptive LUT.

**API** Application Programming Interface.

**APM** AXI Performance Monitor.

ASIC Application Specific Integrated Circuit.

AXI Advanced eXtensible Interface.

BAR Base Address Register.

**BD** Big Data.

**BLE** Basic Logic Element.

**BRAM** Block RAM.

C2H DMA Write Channel.

CAD Computer-Aided Design.

CIC Cascaded Integrator-Comb.

CLB Configurable Logic Block.

CLI Command-Line Interface.

CMOS Complementary Metal-Oxide Semiconductor.

**CPU** Central Processing Unit.

CU Compute Unit.

DDR Double Data Rate.

DL Deep Learning.

**DLL** Delay-Locked Loop.

**DMA** Direct Memory Access.

DMBI Device Message Box Interface.

**DNN** Deep convolutional Neural Network.

**DSA** Device Support Archive.

**DSP** Digital Signal Processing.

**EEPROM** Electrically Erasable Programmable Read-Only Memory.

**EPROM** Erasable Programmable Read-Only Memory.

FF Flip-Flop.

FFT Fast Fourier Transform.

**FIFO** First In First Out.

**FIR** Finite Impulse Response.

FPGA Field Programmable Gate Array.

FSM Finite-State Machine.

**GN** General-purpose Node.

**GPU** Graphics Processing Unit.

**GUI** Graphical User Interface.

H2C DMA Read Channel.

HAL Hardware Abstraction Layer.

HDL Hardware Description Language.

**HLS** High-Level Synthesis.

HN Heterogeneous Node.

**HPC** High-Performance Computing.

I/O Input/Output.

**IBUF** Input Buffer.

**IC** Integrated Circuit.

**IDE** Integrated Design Environment.

**IP** Intellectual Property.

LAB Logic Array Block.

LUT Look-Up Table.

MAC Multiply-Accumulate.

MIG Memory Interface Generator.

MPSoC Multiprocessor SoC.

**OBUF** Output Buffer.

OCL Region OpenCL Region.

**OpenCL** Open Computing Language.

**Pblock** Physical Block.

PCIe PCI Express.

PE Processing Element.

PLL Phase-Locked Loop.

**PR** Partial Reconfiguration.

**PROM** Programmable Read-Only Memory.

RAM Random Access Memory.

**RM** Reconfigurable Module.

**RP** Reconfigurable Partition.

**RPR** Regular Partial Reconfiguration.

RTL Register Transfer Level.

**SDC** Synopsys Design Constraints.

SDRAM Synchronous Dynamic Random Access Memory.

SIMD Single Instruction Multiple Data.

SLR Super-Logic Region.

SoC System-on-a-Chip.

SPI Serial Peripheral Interface.

SPMD Single Program Multiple Data.

SRAM Static Random Access Memory.

SRL Shift Register Logic.

SSI Stacked Silicon Interconnect.

SysMon System Monitor.

System ILA System Integrated Logic Analyzer.

Tcl Tool Command Language.

**TSV** Through-Silicon Vias.

**USB** Universal Serial Bus.

WA Write Address.

WE Write Enable.

xbinst Xilinx Board INSTallation.

xbsak Xilinx Board Swiss Army Knife.

XCL HAL Xilinx OpenCL Hardware Abstraction Layer.

xclbin Xilinx OpenCL Compute Unit Binary.

**XDC** Xilinx Design Constraints.

**XDMA** Xilinx DMA Subsystem for PCIe.

**xocc** Xilinx OpenCL Compiler.

**XPR** Expanded Partial Reconfiguration.

# CHAPTER 1 Introduction

# 1.1 Heterogeneous system for HPC application

Traditional computing systems always relied on the use of Central Processing Units (CPUs) for the computation of applications. This was a valid solution while power and energy were not a concern. However, as performance and size of these systems grew the influence of the power consumption and energy dissipation became apparent and CPUs were no longer regarded as the only one computing components in the system.

This led to the emergence of heterogeneous computing. In such a system, different types of computing devices, each with different power consumption values and performances can be used all together. They rely on different architectures and therefore they are better suited for specific and particular programming approaches and problems definitions.

The first boost we had in High-Performance Computing (HPC) systems was the adoption of Graphics Processing Units (GPUs) as computing devices, typically regarded to be used in desktop systems for graphics processing. The computing capabilities of GPUs as they have many small cores with floating point capabilities, made those devices perfect for massive parallel applications being efficiently computed on them. Although power consumption of GPUs can be on par with CPUs they exhibit one or two orders of magnitude (if not more) when compared with CPUs.

Indeed, nowadays, new applications from the recent Artificial Intelligence (AI) boost with Deep convolutional Neural Network (DNN), and the fusion of Big Data (BD) and HPC led the GPUs to be seen as commodity components and key players in such large installations.

While the CPU and GPUs are combined and they are the elected components, we can see the emergence of other heterogeneous components which can be used for more specific application domains or where power and energy are of real concern. This is the case of manycores (one clear example is the Intel Xeon Phi which later was discontinued) and the Field Programmable Gate Arrays (FPGAs). FPGAs are flexible devices where its architecture can be programmed and thus, the hardware inside the FPGA can be perfectly adapted to the algorithm used

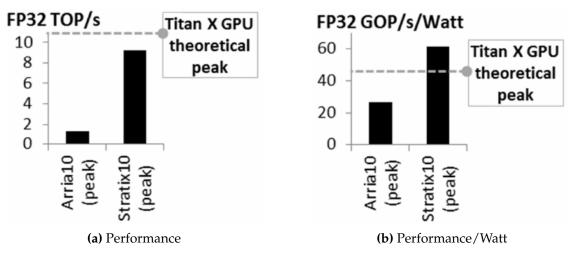

Figure 1.1: Results for Classic DNNs

to solve a problem. Indeed, FPGAs are massively used in embedded systems domains and critical application domains such space, avionics, and automotive.

For HPC systems there are new efforts and early adoptions of FPGAs-based systems for HPC computation problems. Although FPGAs are flexible, they are not so powerful as GPUs in floating point operations. However, FPGAs can be very profitable in specific application domains for HPC where floating point is not of vital need and reduced precision algorithms can be used instead. In this project we bet for the use of FPGAs as a equal partner in the set of computing devices and focus on their adoption for HPC systems.

in favour of what has been said, a study carried out by Intel is reported [5]. This study compares FPGAs and GPU, supported by several algorithms of DNN. In this thesis work, the results of what is called *Classic DNNs* in the study are reported in the following Figures 1.1.

As we can see, the threshold in the case of performance, represented by the GPU, is not reached by the two FPGAs. While in the case of Strafix 10, the power consumption is much higher.

The use of FPGAs in HPC systems is increasingly widespread due to this power consumption advantage: this advantage is multiplied by the huge number of FPGAs that can replace GPUs in a heterogeneous HPC system, drastically reducing power consumption.

# 1.2 Standard vs custom FPGAs platform

Once we adopted the use of FPGAs for HPC systems, we need to care about the flexibility offered by these systems for the average programmer. Indeed, it is well known the complexity and the difficulties that FPGA programming has imposed to the end users. This is out of question as is clear the average programmer does not have any expertise on computer architecture and any design expertise. Indeed, an FPGA can be programmed easily but the resulting performance will be quite poor as the flexibility of components connection inside the FPGA are not exploited.

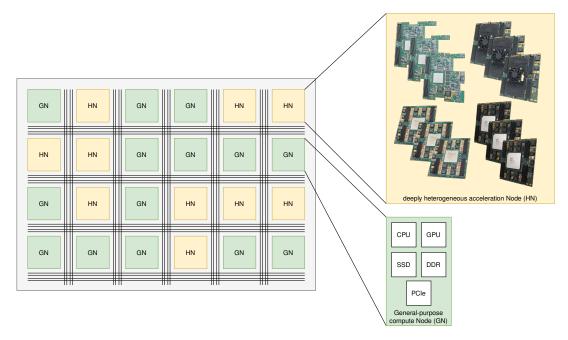

Figure 1.2: MANGO Prototype

To solve this bridge gap between FPGA programming and end user expertise, the Open Computing Language (OpenCL) programming paradigm came into play (other solutions exist also). OpenCL defines a programming approach where FPGAs can be programmed easily and with the required abstraction of its complexities and optimization opportunities. In Chapter 2.3 we fully describe the OpenCL framework.

OpenCL can be directly used by most FPGA boards available in the market. Indeed, the FPGA manufacturing companies (mostly Xilinx and Intel/Altera) offer their boards with current software and hardware support for the use of OpenCL programming frameworks. Xilinx and Intel/Altera market different FPGA-based acceleration platforms, but the flow used is very similar. The key goal of the flow lays in enabling a hardware platform and a set of software libraries to diminish programming complexities and facilitate the application of acceleration to software developers. However, and here is where our project is focused to, other FPGA systems implemented by third party companies do not have such support for OpenCL as they are focused on other fields, mostly Application Specific Integrated Circuit (ASIC) prototyping. This is the case of the products offered by the proDesign company, which offers an interesting solution where one can build a complete large FPGA solution with components as if they were part of a LEGO game. FPGA boards, Double Data Rate (DDR) memories, and Input/Output (I/O) components can be plugged in different ways based on the computing needs.

# 1.3 MANGO infrastructure

The MANGO prototype is shown in Figure 1.2. As we can see there is two types of node:

- Heterogeneous Node (HN): to instantiate different hardware architectures coded directly in Hardware Description Language (HDL) programming languages. Each HNs consist of 12 FPGAs and 22GB of DDR-3 and DDR-4 memory mounted on top of 4 proFPGA motherboards from ProDesign GmbH. This cluster is also heterogeneous, since it is composed of different types of FPGAs: Xilinx Kintex Ultrascale KU115, Xilinx Virtex 7 Series V2000T, Xilinx Zynq 7000 SoC Z100 and Intel Stratix 10 SG280.

- General-purpose Node (GN): to run a low-level runtime library and extended a runtime management system to manage both the different computational units implemented on a given architecture and the architecture itself. Each GNs consist of an high-end Intel Xeon E5 V3, a GPU, 64 GB of DDR4 of memory, 1 TB SSD hard disk and a PCI Express (PCIe) connectivity.

Every HN is connected to a GN through PCIe Gen3 x8 lanes, thus every GN can access two different HNs, for a total of 24 FPGAs and 44 GB of DDR3/4 memory.

The MANGO prototype was originally made of 16 clusters each with 12 FP-GAs and 8 DDR memories. However, after project end, the prototype was split and UPV received half of the prototype, which still has reasonable performance capabilities. In this section we briefly describe the MANGO prototype located at UPV premises and which is the target of our project.

# 1.4 Goals and Motivations of this Work

Contrary to the Intel and Xilinx approach, the FPGAs delivered within the MANGO prototype are not equipped with any kind of circuitry to provide a high-performance communication link with the host or to facilitate the programming of these devices to software developers.

The goal of this thesis work is to create a Platform, including both hardware and software, on a FPGA implemented by a third-party company. The Platform will be used by the MANGO project and will therefore use its infrastructure. In particular the FPGA target is the **Xilinx Kintex UltraScale KU115** provided by proDesign.

To reach the final goal, several sub-objectives will be achieved, including enabling the OpenCL and High-Level Synthesis (HLS) high-level programming models for the MANGO prototype.

## 1.5 Structure of the Document

The project of this thesis is to solve a purely technical problem. Therefore, in the Chapter 2 will be exposed all the knowledge useful to a reader to understand what has been addressed. The chapter is extremely substantial because, as also

said in Chapter 1, the proposed problem embraces many technologies, including FPGA, OpenCL and Platform concept.

In the Chapter 3 the whole process of development of the custom Platform and all the design choices made and the why of certain choices will be explained. In addition, it will be explained in the same Chapter, the tests carried out to evaluate the correct functioning of the Custom Platform and evaluate its performance.

In Chapter 4, the final conclusions are presented, along with some suggestions on how the results could be further improved.

# CHAPTER 2 Background

As said, several technologies are used in this thesis work. This chapter introduce the knowledge about these technologies, therefore most of reported information are taken from technical official documentation.

# 2.1 FPGA introduction

FPGAs are pre-fabricated silicon devices that can be electrically programmed to become almost any kind of digital circuit or system. Compared to ASIC technology, FPGAs provide advantages in terms of reduced reprogramming time and, consequently, cost. In fact, while for ASICs reprogramming time takes months and millions of dollars, for FPGAs it takes only a few moments. The flexible nature of an FPGA has a significant cost in terms of area, delay and power consumption.

## 2.1.1. Architecture

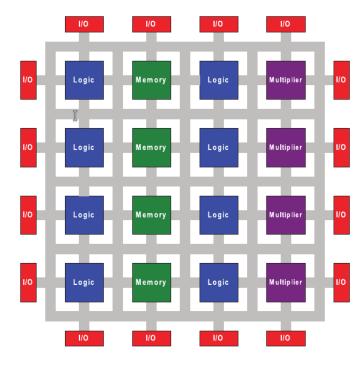

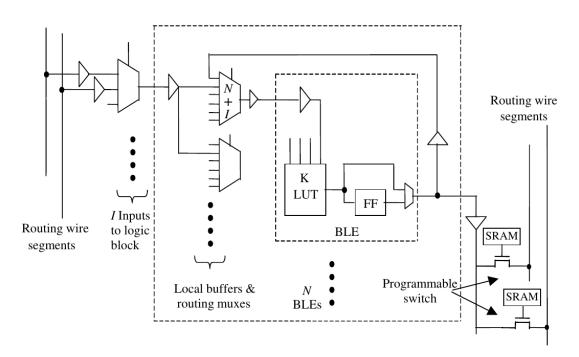

As shown in figure 2.1, FPGAs consist of a series of programmable logic blocks of different types: general logic blocks, memory blocks and multipliers. These elements are interconnected by a programmable routing fabric. The matrix is surrounded by programmable I/O blocks that connect the chip to the outside world. The term programmable indicates the ability to program a function in the chip after silicon manufacturing is completed.

## 2.1.2. Taxonomy

### 2.1.2.1. Static Memory Programming Technology

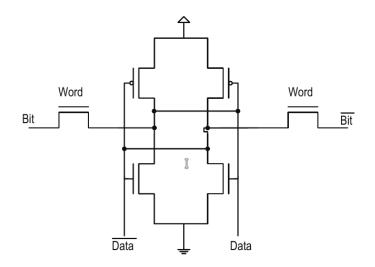

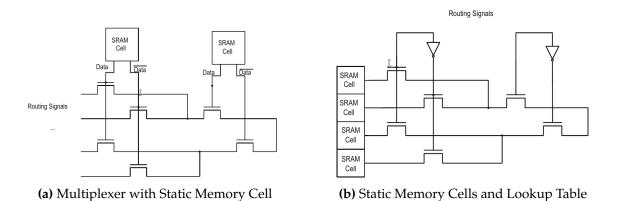

The static memory cells, represented in Figure 2.2, are the basis of the Static Random Access Memory (SRAM) programming technology. Nowadays this technology is the most used by Xilinx, Lattice and Altera. In these devices, static memory cells are distributed throughout the FPGA to provide configurability. The SRAM cells allow to

Figure 2.1: FPGA architecture

- select lines to multiplexers that steer interconnect signals, by the circuit shown in Figure 2.3a.

- store the data in the Look-Up Tables (LUTs) that are typically used in SRAMbased FPGAs to implement logic functions, by the circuit shown in Figure 2.3b.

The main advantages of SRAM programming technology are reprogrammability and the use of standard Complementary Metal-Oxide Semiconductor (CMOS) process technology. The first is guaranteed by the fact that a SRAM cell can be programmed an indefinite number of times. A dedicated circuit on the FPGA initializes all SRAM bits at power-up and configures the bits with a user-supplied configuration. The second advantage is given by the fact that the use of SRAM

Figure 2.2: SRAM cell

Figure 2.3: Use of static memory cells

cells does not require particular phases of Integrated Circuit (IC) processing beyond the standard CMOS. As a result, SRAM-based FPGAs can use the latest CMOS technology available and therefore benefit from the increased integration, higher speeds and lower dynamic power consumption of new processes with smaller minimum geometries. However, SRAM-based programming technologies has the following disadvantages:

- The SRAM cell requires 5 or 6 transistors and the programmable element used for signal interconnection requires at least a single transistor causing size problems.

- Use of external devices, such as flash or Electrically Erasable Programmable Read-Only Memory (EEPROM), to permanently store configuration data when the device is powered down.

- Because the configuration information must be loaded into the device when the power is turned on, there is a possibility that the configuration information may be intercepted and stolen for use in a competing system.

- Multiplexers are implemented on pass transistor. However, they are not ideal switches as they have significant ignition resistance and an appreciable capacitive load. The problem increases as the FPGAs switches to smaller devices.

#### 2.1.2.2. Flash/EEPROM Programming Technology

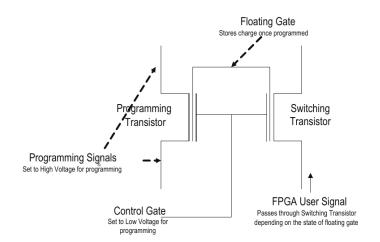

This technology is based on the use of floating gate programming technologies, shown in figure 2.4, which inject the charge onto a gate that *floats* over the transistor. This approach is used in flash or **EEPROM** memory cells.

The operation of the scheme is as follows: the smaller programming transistor is used to program the floating gate (injecting a charge that remains even when the power is switched off) while the larger switching transistor serves as a programmable switch. The switching transistor must also be used to cancel the device.

The advantages offered by this technology are: non-volatility and efficient use in terms of area. Compared to SRAM-based programming technology, non-

Figure 2.4: Floating gate transistor

volatility eliminates the need for external resources needed to store and load configuration data and therefore also eliminates the need to wait for configuration data to load when the device is powered on. The flash memory cells approach is also more area efficient than SRAM-based technology due to the reduced number of transistors to build the cell.

One of a disadvantages of flash-based devices is that they can not be reprogrammed an infinite number of times. The accumulation of charge in the oxide eventually prevents a flash-based device from being erased and programmed correctly after a certain number of reprogramming. For example the **Actel ProASIC3** is only guaranteed for 500 programming cycles. Another significant disadvantage of flash devices is the need for a non-standard **CMOS** process. Furthermore, like **SRAM**-based programming technology, this programming technology suffers from relatively high resistance and capacitance due to the use of transistor switches.

Nowadays, there are devices on the market that use flash memory in combination with SRAM programming technology. In particular, on-chip flash memory is used to provide non-volatile storage, while SRAM cells are still used to control programmable elements in the design. This solves problems associated with the volatility of pure SRAM approaches, such as the cost of additional storage devices or the ability to intercept configuration data, while maintaining the infinite reconfigurability of SRAM-based devices.

With the exception of very low capacity devices, such approaches are no longer commonly used because of the static power dissipation inherent in such schemes.

#### 2.1.2.3. Anti-fuse Programming Technology

Anti-fuse programming technology is based on anti-fuse as programmable element. This structure exhibits very high-resistance under normal circumstances but a low resistance link can be created. Unlike SRAM or floating gate programming technologies, this link is permanent. Two approaches have been used to implement anti-fuses: dielectric anti-fuses and metal-to-metal-based anti-fuses. The primary advantage of anti-fuse programming technology is its low area. With metal-to-metal anti-fuses, no silicon area is required to make connections, decreasing the area overhead of programmability. Anti-fuses have an additional advantage: they have lower on resistances and parasitic capacitances than other programming technologies. The low area, resistance, and capacitance of the fuses means it is possible to include more switches per device than in other technologies. Non-volatility also means that the device works instantly once programmed. This lowers system costs since additional memory for storing the programming information is not required and it also allows the FPGA to be used in situations that require operation immediately upon power up. Finally, since programming, and hence transmitting the bitstream to the FPGA, need only be done once, this can be done in a secure environment which improves the security of the design on the FPGA. To further enable this security, current devices offer security modes which disable accesses through the programming interface once the device is programmed.

There are also significant disadvantages to this programming technology. In particular, since anti-fuse-based FPGAs require a non-standard CMOS process, they are typically well behind in the manufacturing processes that they can adopt compared to SRAM-based FPGAs. Finally, the one-time programmability of anti-fuses makes it impossible for manufacturing tests to detect all possible faults. Some faults will only be uncovered after programming and, therefore, the yield after programming will be less than SRAM or floating-gate devices.

### 2.1.3. Logic Block Architecture

The purpose of a logic block in an FPGA is to provide the basic computing and storage elements used in digital logic systems.

In addition to a basic logic block, modern FPGAs contain a heterogeneous mix of different blocks, some of which can only be used for very specific functions, such as dedicated memory blocks or multipliers. These structures are very efficient in implementing specific functions, but are wasted if not used.

In general, published research on logic block architecture tends to model and explore relatively simple basic logic elements taking into account area, speed and power. In contrast, commercial logic blocks have undergone an evolution that typically has led to the development of more complex blocks in an attempt to gain more functionality.

The most relevant trade-off in the study of logical blocks is the area. The efficiency of the FPGA area is a key metric because the size of the FPGA dictates a significant part of its cost, especially for devices with a large logical capacity.

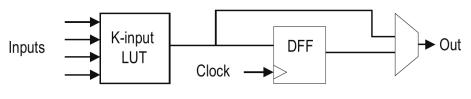

In general, logic blocks are also called Configurable Logic Blocks (CLBs). Each logic block contains a group of Basic Logic Elements (BLEs), shows in Figure 2.5, where each BLE is formed by a LUT and an Flip-Flop (FF), as shown in figure 2.6.

Figure 2.5: Configurable Logic Block

Figure 2.6: Basic Logic Element

### 2.1.3.1. Heterogeneity

As said, modern FPGA include different types of logical blocks. We give two definitions:

- **soft logic fabric**: the array of combinational logic elements, each consisting of a logic function implemented as a gate or LUT, that is connected through a programmable routing fabric.

- hard circuit structure: any other circuitry employed in the device which we define as a structure that allows the implementation of a specific logic function, such as a dedicated FF inside a logic block.

Modern commercial FPGAs contain dedicated logic within each general purpose block to support arithmetic carry and sum functions and some memory functions.

We distinguish between two kinds of heterogeneity:

- **soft logic fabric**: it refers to the heterogeneity within the soft logic fabric such as the FF and dedicated carry logic that appear alongside the combinational logic in every logic block that makes up the soft logic fabric.

- **tile-based heterogeneity**: distinct tiles containing dedicated hard circuit structures are added to the array of tiles. For example, multi-bit Block RAMs (BRAMs) or Multiply-Accumulate (MAC) blocks that appear in modern FPGAs are common hard circuit structures.

Figure 2.7 illustrates an FPGA with a mixture of different blocks with tilebased heterogeneity.

**Soft Fabric Heterogeneity** As said Soft Fabric Heterogeneity contains a set of heterogeneous elements. Examples of elements are:

- **FF**: all commercial FPGAs have included FFs in their basic logic elements. Modern FPGA FFs are typically edge-triggered and include a variety of set, reset, load, enable and clocking capabilities. Research investigated the area efficiency of FPGAs with and without dedicated FFs, and clearly established the significant benefits of including FF circuits within logic elements.

- **circuitry for arithmetic operations**: Many modern FPGAs include explicit circuitry for addition/subtraction/carry logic to make adders and subtraction units smaller and faster.

**Memory** Since different applications will need memory configured in many different ways, basic memory blocks must be flexible and configurable. All contemporary FPGAs include memory blocks and they have grown to cover a significant fraction of the FPGA die area.

| SOFT<br>LOGIC | SOFT<br>LOGIC | Memory<br>Block   | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

|---------------|---------------|-------------------|------|---------------|---------------|

| SOFT<br>LOGIC | SOFT<br>LOGIC | no ry<br>ick      | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

| SOFT<br>LOGIC | SOFT<br>LOGIC | M em ory<br>Block | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

| SOFT<br>LOGIC | SOFT<br>LOGIC |                   | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

| SOFT<br>LOGIC | SOFT<br>LOGIC | Memory<br>Block   | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

| SOFT<br>LOGIC | SOFT<br>LOGIC |                   | MULT | SOFT<br>LOGIC | SOFT<br>LOGIC |

Figure 2.7: Illustration of tile based heterogeneity

Contemporary BRAMs provide the dual port functionality, i.e. they allow simultaneous read and write operations.

Others recent FPGAs have special features such as the ability to support First In First Out (FIFO) configurations. The cost of this added flexibility requires additional memory ports and internal memory complexity. Complex memory operation can be supported with control circuits implemented in soft logic. Often, it can be costly to combine memory blocks to perform large, complicated memory functions due to logic and routing overheads.

**Computation-Oriented Tiles** A popular industrial example of this type of block is MAC, it is also called Digital Signal Processing (DSP).

If multipliers are not needed by an application, the multiplier tiles located inside a target FPGA provide little benefit. One way to deal with this issue is to create multiple sub-families within a device family that use different ratios of soft logic to hard-logic. A device family typically consists of a set of FPGAs with the same basic architecture that contain differing amounts of resources. A designer can select the device with the most appropriate ratio, minimizing wasted computational tiles.

**Microprocessors** Microprocessors are vital components in many digital systems. Since they are often used in conjunction with FPGA logic, it makes sense to consider their integration into an FPGA logic fabric.

A challenging aspect of including a hard processor on an FPGA is the development of the interfaces between the processor, memory system, and the soft fabric. Nowadays, the most used communication protocols is Advanced eXtensible Interface (AXI). The alternative to a hard processor is a soft processor, built out of the soft fabric and other hard logic. The latter is generally slower in performance and larger in terms of area. However, the soft processor can often be customized to exactly suit the needs of the application to gain back some of the lost performance and area-efficiency.

### 2.1.4. Routing Architecture

The programmable routing in an FPGA provides connections among logic blocks and I/O blocks to complete a user-designed circuit. It consists of wires and programmable switches that form the desired connections. Additionally, circuits also contain a number of signals such as clocks and resets that must be widely distributed across the FPGA. Modern FPGAs all contain dedicated interconnect networks that handle the distribution of these signals. Typically, these networks are carefully designed to be low skew for use in distributing clock signals

We distinguish between two kinds of routing:

- **global routing**: defines the relative position of routing channels in relation to the positioning of logic blocks, how each channel connects to other channels, and the number of wires in each channel.

- **detailed routing**: specifies the lengths of the wires, and the specific switching quantity and patterns between and among wires and logic block pins.

FPGA global routing architectures can be characterized as either hierarchical or island-style. Currently, most commercial SRAM-based FPGA architectures use island-style architectures.

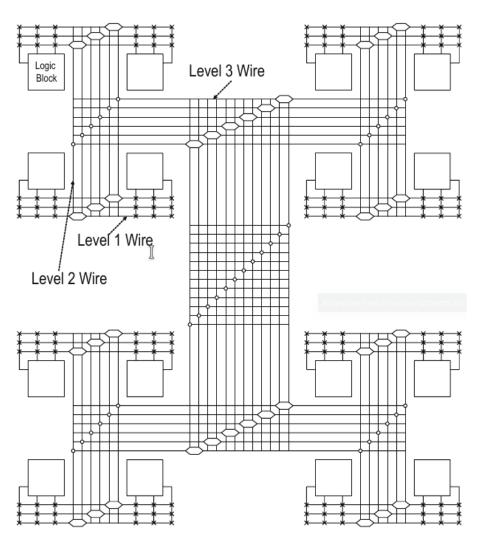

#### 2.1.4.1. Hierarchical-style

Hierarchical routing architectures, shows in Figure 2.8 separate FPGA logic blocks into distinct groups. Connections between logic blocks within a group can be made using wire segments at the lowest level of the routing hierarchy. Connections between logic blocks in distant groups require the traversal of one or more levels (of the hierarchy) of routing segments.

The advantage of this placement of logical elements is that the predictability of block delays is higher. The disadvantages, however, are present in design mapping and scalability.

For these reasons, most recent commercial FPGA routing architectures do not use this type of global routing architecture and, instead, use only one level of hierarchy to create a flat, island-style global routing architecture.

#### 2.1.4.2. Island-style

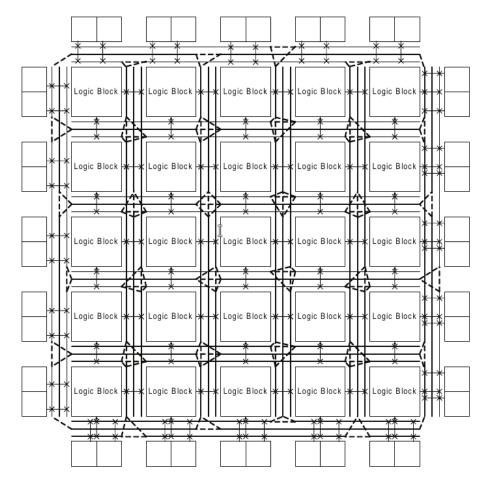

As shown in Figure 2.9, island-style FPGAs logic blocks are arranged in a two dimensional mesh with routing resources evenly distributed throughout the mesh.

Figure 2.8: Hierarchical-style FPGA

Figure 2.9: Island-style FPGA

The logic blocks have routing channels on all four side. The number of wires contained in a channel is pre-set during fabrication and generally lengths of wire segments are different in an attempt to provide the most appropriate length for each given connection.

The advantage of wires of different lengths near the logic blocks is that efficient connections can be formed. The physical layout for each logic block and surrounding routing channels can be optimized to form a single tile. This combined logic and routing tile can be replicated in two dimensions to form the FPGA array. As a result of this regularity, the minimum feasible routing delay between logic blocks can quickly be estimated.

Others component in this type of routing architecture are:

- **switch block**: connects wires in adjacent channels through programmable switches such as pass-transistors or bi-directional buffers.

- **connection block**: connects the wire segments around a logic block to its inputs and outputs, also through programmable switches.

### 2.1.5. I/O Architecture

In order to communicate with the outside world, a FPGA needs I/O cells. Given the huge number of communication protocols, these blocks are extremely heterogeneous to meet voltage and speed requirements.

The I/O pad and surrounding supporting logic and circuitry as an I/O cell. These cells, along with their supporting peripherals, consume a significant portion of an area of FPGA.

#### 2.1.5.1. Basic I/O Standards

The major challenge in I/O architecture design is the great diversity in I/O standards. For example, different standards may require different input voltage thresholds and output voltage levels. To support these differences, different I/O supply voltages are often needed for each standard. They may also require a reference voltage to compare against the input voltages. Other standards require clamping diodes which allow specific abnormally high or low voltages to be tolerated. Many standards also rely on differential signaling to improve noise immunity and enable increased data transmission speeds. Proper termination is also essential for maintaining signal integrity but different standards have different termination requirements.

#### 2.1.5.2. High-Speed I/O Support

When we talk about high-speed I/O we mean both the interfacing with the memory and the communication between two entities. In both cases, additional circuitry is required to facilitate this high-speed transfer. At a minimum, standards that make use of differential signaling require two I/O cells to be paired together with differential transmitters/receivers.

High-speed communication requires more than the high-speed signaling that these analog features enable. Therefore, contemporary FPGAs frequently include dedicated digital circuits to support higher-level protocols, such as PCIe

High-speed memory interfaces also need special-purpose hardware to accurately capture data flowing between memory chips and the FPGA. Delay-Locked Loops (DLLs) and Phase-Locked Loops (PLLs) are used to adjust the phase of a transfer clock to ensure that data from the external memory is sampled when the data is valid.

#### 2.1.6. Programming

Nowadays, most FPGA vendors provide a set of design tools that allows automatic synthesis and compilation from design specifications in hardware specification languages, such as Verilog or VHDL, all the way down to a bit-stream to program FPGA chips. Examples of tool are **Xilinx Vivado** and **Intel Quartus Prime**.

#### 2.1.6.1. Inputs

Inputs to the design flow typically are:

- HDL specification of the design: the most widely used design specification languages are Verilog and VHDL at the Register Transfer Level (RTL) which specify the operations at each clock cycle. Nowadays, there is a general trend to use a high-level languages like C or SystemC, or domain-specific languages, such as MatLab or Simulink to simplify the programming of FPGAs. Using these languages, one can specify the behavior of the design without going through a cycle-accurate detailed description of the design. A behavior synthesis tool is used to generate the RTL specification in Verilog or VHDL.

- design constraints: design constraints typically include the expected operating frequencies of different clocks, the delay bounds of the signal path delays from input pads to output pads (I/O delay), from the input pads to registers (setup time), and from registers to output pads (clock-to-output delay). In some cases, delays between some specific pairs of registers may be constrained. Design constraints may also include specifications of socalled false paths and multi-cycle paths. False paths will not be activated during normal circuit operation, and therefore can be ignored; multi-cycle paths refer to signal paths that carry a valid signal every few clock cycles, and therefore have a relaxed timing requirement. Finally, the design constraints may include physical location constraints, which specify that certain logic elements or blocks be placed at certain locations or a range of locations. These location constraints may be specified by the designer, or inherited from the previous design iteration (for making incremental changes), or generated automatically by the physical synthesis tools in the previous design iterations.

- **specification of target FPGA devices**: each FPGA vendor typically provides a wide range of FPGA devices, with different performance, cost, and power trade-offs. The selection of target device may be an iterative process. The designer may start with a low capacity device with a nominal speed-grade. if synthesis effort fails to map the design into the target device or if the synthesis result fails to meet the operating frequency, the designer has to, respectively, either upgrade to a high-capacity device or upgrade to a device with higher speed-grade. In both the cases, the cost of the FPGA device will increase. This clearly underscores the need to have better synthesis tools, since their quality directly impacts the performance and cost of FPGA designs.

#### 2.1.6.2. Fow

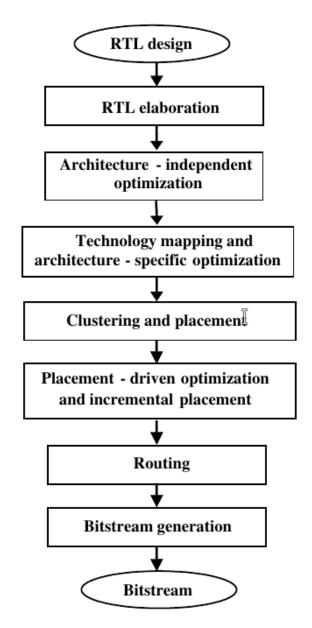

A typical FPGA design flow includes the steps and components shown in Figure 2.10.

We now briefly describe each step in the design flow shown in Figure 2.10:

Figure 2.10: A typical FPGA design flow starting from RTL specifications

- **RTL elaboration**: identifies and/or infers *datapath* operations, such as sums, multiplications, register files, and/or memory blocks, and *control logic*, which is elaborated into a set of Finite-State Machine (FSM) and/or generic Boolean networks. It is important to recognize the datapath elements due to special architectural support in modern FPGAs, such as adders with dedicated fast-carry chains and embedded multipliers.

- Architecture-independent optimization: this includes both *datapath optimization*, using techniques such as constant propagation, strength reduction, operation sharing, and expression optimization; and *control logic optimization*, which includes both sequential optimization, such as FSM encoding/minimization and retiming, and combinational logic optimization, such as constant propagation, redundancy removal, logic network restructuring and optimization, and don't-care based optimization.

- Technology mapping and architecture-specific optimization: maps: (i) the optimized datapath to on-chip dedicated circuit structures, such as on-chip multipliers, adders with dedicated carry-chains, and embedded memory blocks for datapath implementation, and (ii) the optimized control logic to BLEs. Note that datapath operations can be mapped to BLEs as well if the dedicated circuit structures are not available or not convenient to use.

- **Clustering and placement**: determines the location of each element in the mapped netlist. With hierarchical FPGAs a separate clustering step may be performed prior to placement to group BLEs into logic blocks.

- Placement-driven optimization and incremental placement: once placement is available, interconnects are defined and may become a performance bottleneck. Further optimization may be carried out in the presence of interconnect delays, including logic restructuring, duplication, rewiring. After such operations, an incremental placement step is needed to validate the placement again. The step of placement-driven optimization is optional, but may improve design performance considerably.

- **Routing**: global routing and detail routing will be performed to connect all signal paths using the available programmable interconnects on-chip.

- **Bit-stream generation**: the final step of the design flow. It takes the mapped, placed, and routed design as input and generates the necessary bit-stream to program the logic and interconnects to implement the intended logic design and layout on the target FPGA device.

## 2.1.7. Xilinx vs Intel Altera FPGAs

### 2.1.7.1. Xilinx

The huge variety of FPGAs offered by Xilinx cannot be fully explored in this Section. Therefore, since a **Kintex UltraScale** has been used in this thesis work, the main features of FPGAs based on Ultrascale architecture will be exposed.

The UltraScale architecture is one of the architecture proposed by Xilinx for its FPGAs. UltraScale architecture-based devices address a vast spectrum of highbandwidth, high-utilization system requirements by using technical innovations, including next-generation routing, ASIC-like clocking, 3D-on-3D ICs, Multiprocessor SoCs (MPSoCs) technologies, and new power reduction features. The devices share many building blocks, providing scalability across process nodes and product families to leverage system-level investment across platforms.

Kintex UltraScale is family devices for packet processing in networking and data centers applications as well as DSP-intensive processing needed in next-generation medical imaging, 8k4k video, and heterogeneous wireless infrastructure. Kintex UltraScale devices is a mid-range device that provides signal processing bandwidth, next-generation transceivers, and low-cost packaging for an optimum blend of capability and cost-effectiveness.

There are two types of slices in the UltraScale architecture, with different ratios of the two types by device: **SLICEL** and **SLICEM**.

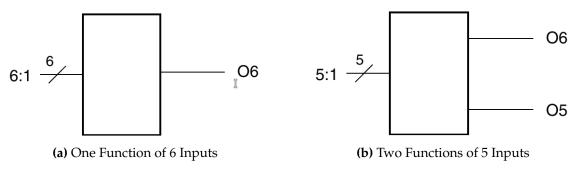

**SLICEL** The **SLICEL** has the LUT and storage element resources, along with the carry logic and wide multiplexers. One SLICEL is included in a CLB. The UltraScale architecture CLBs provide advanced, high-performance, low-power programmable logic with:

- Real 6-input LUT capability.

- Dual 5-input LUT option.

- Distributed memory and Shift Register Logic (SRL) ability.

- Dedicated high-speed carry logic for arithmetic functions.

- Wide multiplexers for efficient utilization.

- Dedicated storage elements that can be configured as FFs or latches with flexible control signals.

Each slice provides eight 6-input LUTs and sixteen FFs. The slices and their CLBs are arranged in columns throughout the device, with the size and number of columns increasing with density. The UltraScale architecture LUTs can be configured as shown in Figure 2.11.

Each LUT output can connect to slice outputs, or optionally be registered in a FF or latch. The storage elements can also be driven by direct inputs to the slice (X and I), or by the results of the internal carry logic or wide multiplexers, as shown in Figure 2.12. The storage elements have a clock enable input, along with an initialization signal that can be programmed as either synchronous or asynchronous, and as set or reset.

Carry logic consists of dedicated carry-lookahead gates, multiplexers, and routing that are independent of the general-purpose logic resources while providing both higher density and increased performance. Carry logic is often inferred for smaller arithmetic functions.

Finally, a SLICEL is represented in Figure 2.13.

Figure 2.11: LUT configuration

Figure 2.12: Xilinx SLICEL I/O connection

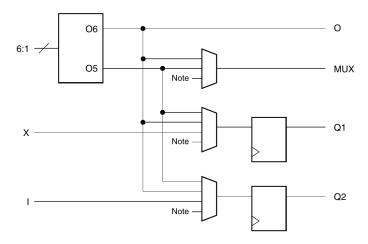

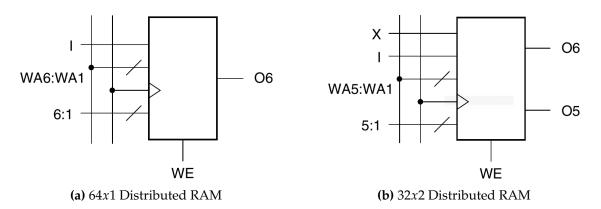

**SLICEM** A **SLICEM** use the LUTs as distributed 64-bit Random Access Memory (RAM), by adding a separate Write Address (WA), Write Enable (WE), and clock signal. The LUT can be configured as either a 64x1 or 32x2 memory, as shown in Figure 2.14. The direct inputs X and I serve as the data inputs.

The distributed RAM can be combined across the eight LUTs in the SLICEM to create memories of up to 512 bits. The SLICEM shares a common write address and write clock across all 8 LUTs. The SLICEM write enable is also shared but can be used in combination with three other slice inputs for more flexibility.

Each LUT in a SLICEM can also be used as a 32-bit shift register (SRL32). Combining the LUTs allows up to a 256-bit shift register in one SLICEM, compared to the 16 dedicated FFs per slice.

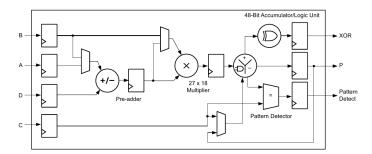

**DSP block** The UltraScale devices have many dedicated low-power DSP slices, combining high speed with small size while retaining system design flexibility. The DSP resources enhance the speed and efficiency of many applications beyond digital signal processing, such as wide dynamic bus shifters, memory address generators, wide bus multiplexers, and memory-mapped I/O registers. The DSP slice in the UltraScale architecture is defined using the **DSP48E2** primitive and the slice is referred to as either **DSP** or **DSP48E2** in the Xilinx tools. The scheme of the DSP48E2 slice is shown in Figure 2.15.

The DSP slice functionality include:

• 27*x*18 two's complement multiplier with dynamic bypass

Figure 2.13: Xilinx SLICEL architecture

Figure 2.14: LUT configuration

Figure 2.15: Xilinx DSP architecture

- Power saving 27-bit pre-adder: optimizes symmetrical filter applications and reduces DSP logic requirements

- 48-bit accumulator that can be cascaded to build 96-bit and larger accumulators, adders, and counters

- Single Instruction Multiple Data (SIMD) arithmetic unit: dual 24-bit or quad 12-bit add/subtract/accumulate

- 48-bit logic unit: bitwise AND, OR, NOT, NAND, NOR, XOR, and XNOR

- Pattern detector: terminal counts, overflow/underflow, convergent/symmetric rounding support, and 96-bit wide AND/NOR when combined with logic unit

- Optional pipeline registers and dedicated buses for cascading multiple DSP slices in a column for hierarchical/composite functions like Systolic Finite Impulse Response (FIR) filters

Applications of the DSP slice include:

- Fixed and floating point Fast Fourier Transform (FFT) functions

- Systolic FIR filters

- MultiRate FIR filters

- Cascaded Integrator-Comb (CIC) filters

- Wide real/complex multipliers/accumulators

Figure 2.16: Xilinx FPGA enabled by SSI Technology

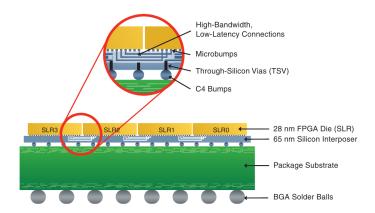

**SSI technology** Since the FPGA chosen for this thesis work uses Stacked Silicon Interconnect (SSI) technology, we introduce what this technology is.

The growing demand for FPGAs with high capacity and high bandwidth has led Xilinx to define a new technology to meet these needs with the second generation of the pioneering 3D SSI technology.

SSI technology uses passive silicon interposers with microbumps and Through-Silicon Vias (TSV) to combine multiple highly manufacturable FPGA die slices, referred to as SRLs, in a single package. The technology also allows die of different types or silicon processes to be interconnected on the interposer. This type of construction is referred to as a heterogeneous FPGA. Figure 2.16 shows the side view of the die stack-up with four FPGA SRLs, silicon interposer, and package substrate.

#### 2.1.7.2. Intel Altera

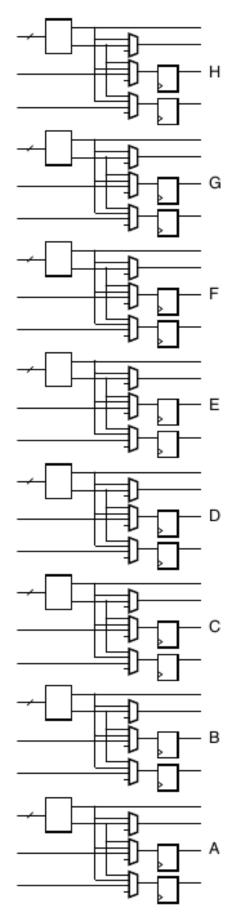

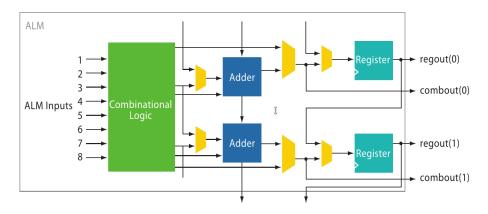

**Logic fabric** The logical fabric of Intel Altera FPGAs consists of logical blocks called Adaptive Logic Module (ALM). As we can see in Figure 2.17, it consists of combinational logic, two registers, and two adders. The combinational portion has eight inputs and includes a LUT that can be divided between two Adaptive LUTs (ALUTs) using Altera's patented LUT technology. To implement an arbitrary six-input function, ALM is needed, but because it has eight inputs to the combinational logic block, one ALM can implement various combinations of two functions.

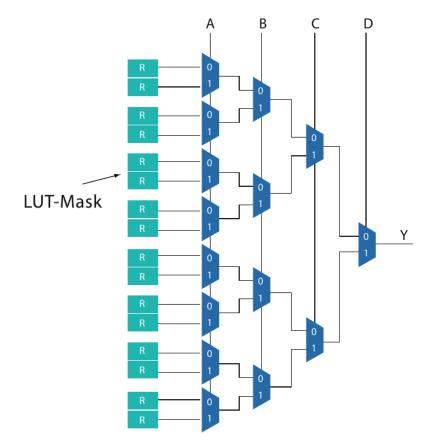

**Building LUTs** Since the type of FPGA produced by Intel Altera is SRAMbased programming technology, a LUT consists of SRAMs to hold the the configuration memory LUT-mask and a set of multiplexers to select the configuration bit to drive the output. Remember, to implement a k-input LUT, i.e. a LUT that can implement any k-input function,  $2^k$  SRAM bits and a  $2^k$  : 1 multiplexer are needed. Figure 2.18 shows an example of 4-LUT, which consists of 16 bits of SRAM and a 16 : 1 multiplexer implemented as a tree of 2 : 1 multiplexers.

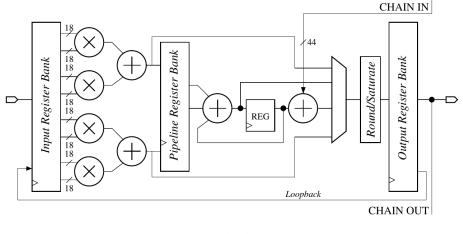

**DSP block** On Stratix II-IV devices the block DSP, shown in Figure 2.19, consists of four 18*x*18 bit multipliers (signed or unsigned) and an adder tree with

Figure 2.17: ALM Block Diagram

Figure 2.18: Example of 4-LUT

Figure 2.19: Intel Altera DSP block

Figure 2.20: Intel Altera DSP configuration

different possible configurations, represented in Figure 2.20. Stratix III-IV calls these DSPs half-DSPs, and pack two of them into a block DSP. In these devices, the limiting factor in terms of configurations is the number of I/O in the DSP block. In addition, all DSPs allow various sum-of-two/four modes for greater versatility. Here also, adjacent DSP blocks can be cascaded, internal registers allow high-frequency pipelining and a loopback path allows for accumulation. These cascading chains reduce resource consumption, but also latency: a sum-of-two 27-bit multipliers can be clocked at the nominal DSP speed in just 2 cycles.

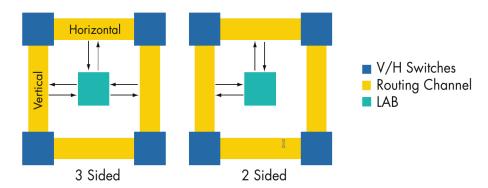

**Routing architecture** The routing architecture provides the connectivity between different clusters of logic blocks, called Logic Array Blocks (LABs), and can be measured by the number of *hops* required to get from one LAB to another. The fewer the number of hops and more predictable the pattern, the better the performance and the easier it is for Computer-Aided Design (CAD) tool optimization.

The Stratix and Stratix II families use a three-sided routing architecture as shown in Figure 2.21. This means that a LAB can drive or listen to all of the wires on one horizontal channel above it and two vertical channels to the left and right side of it. The channels contain wires of length 4, 8, 16, and 24, and signals can get off at any LAB along the length of the wire.

# 2.2 Partial Reconfiguration

Partial Reconfiguration (PR) takes the flexibility offered by FPGA one step further, allowing the modification of an operating FPGA design by loading a partial configuration file, usually a partial bitstream file. After a full bitstream file configures the FPGA, partial bitstream files can be downloaded to modify reconfig-

Figure 2.21: Rounting of Intel Altera FPGAs

urable regions in the FPGA without compromising the integrity of the applications running on those parts of the device that are not being reconfigured.

There are many reasons why the ability to time multiplex hardware dynamically on a single FPGA is advantageous. These include:

- Reducing the size of the FPGA needed to implement a given function, with consequent reductions in cost and power consumption.

- Providing flexibility in the choices of algorithms or protocols available to an application.

- Enabling new techniques in design security

- Improving FPGA fault tolerance

- Accelerating configurable computing

In addition to reducing size, weight, power and cost, PR enables new types of FPGA designs that would be otherwise impossible to implement.

We can find examples of partial reconfiguration application in networks, cryptography and HPC fields.

# 2.2.1. Vivado Partial Reconfiguration design flow

The **Vivado Partial Reconfiguration design flow** is similar to a standard design flow, with some notable differences. The implementation software automatically manages the low-level details to meet silicon requirements. It is needed to guide to define the design structure and floorplan. The following steps summarize processing a PR design:

- 1. Synthesize the static and Reconfigurable Modules (RMs) separately.

- 2. Create physical constraints (Physical Blocks (Pblocks)) to define the reconfigurable regions.

- 3. Set the *HD.RECONFIGURABLE* property on each Reconfigurable Partition (RP).

- 4. Implement a complete design (static and one RM per RP) in context.

- Save a design checkpoint for the full routed design.

- 6. Remove RMs from this design and save a static-only design checkpoint.

- 7. Lock the static placement and routing.

- 8. Add new RMs to the static design and implement this new configuration, saving a checkpoint for the full routed design.

- 9. Repeat Step 8 until all RMs are implemented.

- 10. Run a verification utility (*pr\_verify*) on all configurations.

- 11. Create bitstreams for each configuration.

# 2.3 OpenCL introduction

Most information in this Section has been extracted from [12].

OpenCL is an open royalty-free standard for general-purpose parallel programming across CPUs, GPUs and other processors, giving software developers portable and efficient access to the power of these heterogeneous processing platforms.

**OpenCL** supports a wide range of applications, ranging from embedded and consumer software to HPC solutions, through a low-level, high-performance, portable abstraction. By creating an efficient, close-to-the-metal programming interface, **OpenCL** will form the foundation layer of a parallel computing ecosystem of platform-independent tools, middleware and applications.

OpenCL is particularly suited to play an increasingly significant role in emerging interactive graphics applications that combine general parallel compute algorithms with graphics rendering pipelines. OpenCL consists of an Application Programming Interface (API) for coordinating parallel computation across heterogeneous processors; and a cross-platform programming language with a wellspecified computation environment.

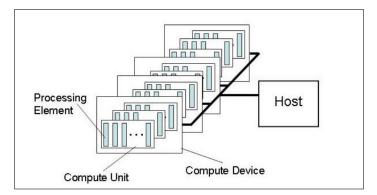

#### 2.3.1. Platform Model

The Platform Model for OpenCL is defined in Figure 2.22. The model consists of a host connected to one or more OpenCL devices. An OpenCL device is divided into one or more Compute Units (CUs) which are further divided into one or more Processing Elements (PEs). Computations on a device occur within the PEs.

An OpenCL application runs on a host according to the models native to the host platform. The OpenCL application submits commands from the host to execute computations on the processing elements within a device. The processing elements within a CU execute a single stream of instructions as SIMD units (execute in lockstep with a single stream of instructions) or as Single Program Multiple Data (SPMD) units (each PE maintains its program counter).

Figure 2.22: The logical view of OpenCL Platform Model

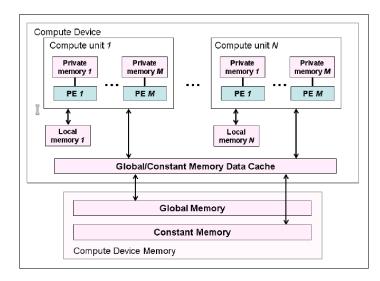

# 2.3.2. Memory Model

Work-item(s) executing a kernel, have access to four distinct memory regions:

- **Global Memory**: this memory region permits read/write access to all workitems in all work-groups. Work-items can read from or write to any element of a memory object. Reads and writes to global memory may be cached depending on the capabilities of the device.

- **Constant Memory**: a region of global memory that remains constant during the execution of a kernel. The host allocates and initializes memory objects placed into constant memory.

- Local Memory: a memory region local to a work-group. This memory region can be used to allocate variables that are shared by all work-items in that work-group. It may be implemented as dedicated regions of memory on the OpenCL device. Alternatively, the local memory region may be mapped onto sections of the global memory.

- **Private Memory**: a region of memory private to a work-item. Variables defined in one work-item's private memory are not visible to another work-item.

The memory regions and how they relate to the platform model are described in Figure 2.23.

The application running on the host uses the OpenCL API to create memory objects in global memory and to enqueue memory commands that operate on these memory objects.

The host and OpenCL device memory models are, for the most part, independent of each other. This is necessary given that the host is defined outside OpenCL. They, however, at times need to interact. This interaction occurs in one of two ways: by explicitly copying data or by mapping and unmapping regions of a memory object.

To copy data explicitly, the host enqueues commands to transfer data between the memory object and host memory. These memory transfer commands may be blocking or non-blocking. The **OpenCL** function call for a blocking memory

Figure 2.23: The logical view of OpenCL Memory Model

transfer returns once the associated memory resources on the host can be safely reused. For a non-blocking memory transfer, the OpenCL function call returns as soon as the command is enqueued regardless of whether host memory is safe to use.

The mapping/unmapping method of interaction between the host and OpenCL memory objects allows the host to map a region from the memory object into its address space. The memory map command may be blocking or non-blocking. Once a region from the memory object has been mapped, the host can read or write to this region. The host unmaps the region when accesses (reads and/or writes) to this mapped region by the host are complete.

### 2.3.2.1. Memory Consistency

**OpenCL** uses a relaxed consistency memory model. In other words, the state of memory visible to a work-item is not guaranteed to be consistent across the collection of work-items at all times.

Within a work-item memory has load/store consistency. Local memory is consistent across work-items in a single work-group at a work-group barrier.

Global memory is consistent across work-items in a single work-group at a work-group barrier, but there are no guarantees of memory consistency between different work-groups executing a kernel.

Memory consistency for memory objects shared between enqueued commands is enforced at a synchronization point.

# 2.3.3. Execution Model

Execution of an OpenCL program occurs in two parts: kernels that execute on one or more OpenCL devices and a host program that executes on the host. The host program defines the context for the kernels and manages their execution.

The core of the OpenCL execution model is defined by how the kernels execute. When a kernel is submitted for execution by the host, an index space is defined. An instance of the kernel executes for each point in this index space. This kernel instance is called a work-item and is identified by its point in the index space, which provides a global ID for the work-item. Each work-item executes the same code but the specific execution pathway through the code and the data operated upon can vary per work-item.

Work-items are organized into work-groups. The work-groups provide a more coarse-grained decomposition of the index space. Work-groups are assigned a unique work-group ID with the same dimensionality as the index space used for the work-items. Work-items are assigned a unique local ID within a workgroup so that a single work-item can be uniquely identified by its global ID or by a combination of its local ID and work-group ID. The work-items in a given work-group execute concurrently on the processing elements of a single compute unit.

The index space supported in **OpenCL** is called an **NDRange**. An NDRange is an N-dimensional index space, where N is one, two or three. An NDRange is defined by an integer array of length N specifying the extent of the index space in each dimension starting at an offset index F (zero by default). Each work-item's global ID and local ID are N-dimensional tuples. The global ID components are values in the range from F, to F plus the number of elements in that dimension minus one.

Work-groups are assigned IDs using a similar approach to that used for workitem global IDs. An array of length N defines the number of work-groups in each dimension. Work-items are assigned to a work-group and given a local ID with components in the range from zero to the size of the work-group in that dimension minus one. Hence, the combination of a work-group ID and the local-ID within a work-group uniquely defines a work-item. Each work-item is identifiable in two ways; in terms of a global index, and terms of a work-group index plus a local index within its work-group.

#### 2.3.3.1. Context and Command Queues

The host defines a context for the execution of the kernels. The context includes the following resources:

- **Devices**: the collection of **OpenCL** devices to be used by the host.

- Kernels: the OpenCL functions that run on OpenCL devices.

- **Program Objects**: the program source and executable that implement the kernels.

- **Memory Objects**: a set of memory objects visible to the host and the **OpenCL** devices. Memory objects contain values that can be operated on by instances of a kernel.

The context is created and manipulated by the host using functions from the OpenCL API. The host creates a data structure called a command-queue to co-

ordinate execution of the kernels on the devices. The host places the commands into the command-queue which are then scheduled onto the devices within the context. These include:

- **Kernel execution commands**: execute a kernel on the processing elements of a device.

- **Memory commands**: transfer data to, from, or between memory objects, or map and unmap memory objects from the host address space.

- Synchronization commands: constrain the order of execution of commands.

The command-queue schedules the commands for execution on a device. These execute asynchronously between the host and the device. Commands execute relative to each other in one of two modes:

- **In-order Execution**: commands are launched in the order they appear in the command-queue and complete in order. In other words, a prior command on the queue completes before the following command begins. This serializes the execution order of commands in a queue.

- **Out-of-order Execution**: commands are issued in order, but do not wait to complete before following commands execute. Any order can be enforced by the programmer through explicit synchronization commands.

Kernel execution and memory commands submitted to a queue generate event objects. These are used to control execution between commands and to coordinate execution between the host and the devices.

It is possible to associate multiple queues with a single context. These queues run concurrently and independently with no explicit mechanisms within OpenCL to synchronize between them.

### 2.3.3.2. Categories of Kernels

The OpenCL execution model supports two categories of kernels:

- **OpenCL kernels** are written with the OpenCL C programming language and compiled with the OpenCL compiler. All OpenCL implementations support OpenCL kernels. Implementations may provide other mechanisms for creating OpenCL kernels.

- Native kernels are accessed through a host function pointer. Native kernels are queued for execution along with OpenCL kernels on a device and share memory objects with OpenCL kernels. For example, these native kernels could be functions defined in application code or exported from a library. Note that the ability to execute native kernels is an optional functionality within OpenCL and the semantics of native kernels are implementation-specific. The OpenCL API includes functions to query capabilities of a device and determine if this capability is supported.

# 2.3.4. Programming Model

The OpenCL execution model supports data-parallel and task-parallel programming models, as well as supporting hybrids of these two models. The primary model driving the design of OpenCL is data-parallel.

### 2.3.4.1. Data-Parallel Programming Model

A data-parallel programming model defines a computation in terms of a sequence of instructions applied to multiple elements of a memory object. The index space associated with the **OpenCL** execution model defines the work-items and how the data maps onto the work-items. In a strictly data-parallel model, there is a one-to-one mapping between the work-item and the element in a memory object over which a kernel can be executed in parallel. **OpenCL** implements a relaxed version of the data-parallel programming model where a strict one-to-one mapping is not a requirement.

OpenCL provides a hierarchical data-parallel programming model. There are two ways to specify the hierarchical subdivision. In the explicit model, a programmer defines the total number of work-items to execute in parallel and also how the work-items are divided among work-groups. In the implicit model, a programmer specifies only the total number of work-items to execute in parallel, and the division into work-groups is managed by the OpenCL implementation.

## 2.3.4.2. Task Parallel Programming Model

The OpenCL task parallel programming model defines a model in which a single instance of a kernel is executed independently of any index space. It is logically equivalent to executing a kernel on a CU with a work-group containing a single work-item. Under this model, users express parallelism by:

- using vector data types implemented by the device,

- enqueuing multiple tasks, and/or

- enqueuing native kernels developed using a programming model orthogonal to OpenCL.

### 2.3.4.3. Synchronization

There are two domains of synchronization in OpenCL:

- Work-items in a single work-group

- Commands enqueued to command-queue(s) in a single context

Synchronization between work-items in a single work-group is done using a work-group barrier. All the work-items of a work-group must execute the barrier before any is allowed to continue execution beyond the barrier. Note that the

work-group barrier must be encountered by all work-items of a work-group executing the kernel or by none at all. There is no mechanism for synchronization between work-groups.

The synchronization points between commands in command-queues are:

- Command-queue barrier. The command-queue barrier ensures that all previously queued commands have finished execution and any resulting updates to memory objects are visible to subsequently enqueued commands before they begin execution. This barrier can only be used to synchronize between commands in a single command-queue.

- Waiting for an event. All OpenCL API functions that enqueue commands return an event that identifies the command and memory objects it updates. A subsequent command waiting on that event is guaranteed that updates to those memory objects are visible before the command begins execution.

# 2.3.5. OpenCL Framework

The OpenCL framework allows applications to use a host and one or more OpenCL devices as a single heterogeneous parallel computer system. The framework contains the following components:

- **OpenCL Platform layer**: the platform layer allows the host program to discover OpenCL devices and their capabilities and to create contexts.

- **OpenCL Runtime**: the runtime allows the host program to manipulate contexts once they have been created.

- **OpenCL Compiler**: the OpenCL compiler creates program executables that contain OpenCL kernels. The OpenCL C programming language implemented by the compiler supports a subset of the ISO C99 language with extensions for parallelism.

# 2.3.6. OpenCL Devices and FPGAs

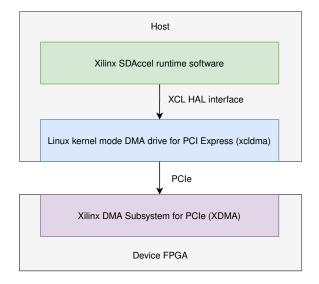

In the context of CPU and GPU devices, the attributes of a device are fixed and the programmer has very little influence on what the device looks like. On the other hand, this characteristic of CPU/GPU systems makes it relatively easy to obtain an off-the-shelf board, i.e. this devices are ready to use without any type of changes. The major limitation of this type of device is that there is no direct connection between system I/O and the OpenCL kernels. All transactions of data are through memory-based transfers.