### DEPARTAMENTO DE INFORMÁTICA DE SISTEMAS Y COMPUTADORES

# Novel Cache Hierarchies with Photonic Interconnects for Chip Multiprocessors

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Engineering)

Author

José Puche Lara

Advisors

Prof. Julio Sahuquillo Borrás Prof. Salvador V. Petit Martí

December 2020

# Doctoral Committee

- Prof. José Ángel Gregorio Monasterio Universidad de Cantabria

- Prof. Antonio Robles Martínez

Universidad Politécnica de Valencia

- Prof. Carlos Reaño González

Queen's University of Belfast

### A grade cimientos

La presentación de la tesis doctoral pone el punto final a una etapa tan importante en la vida como es la formación académica. Ha sido un camino largo y complicado y, consecuentemente, su última etapa tampoco ha sido fácil. Desde que, hace ya más de cinco años, Julio nos abordara al bueno de José Duro y a mí, y nos picara el gusanillo de la investigación (els millors congressos del món), han sido muchas las reuniones y las horas delante de la pantalla.

Sin embargo, no he estado solo. Se dice que la sección de agradecimientos de la tesis es la más importante porque al final es la única que se lee la gran mayoría de gente que, por azar o por castigo, acaba teniendo en sus manos tu tesis doctoral, exceptuando a los revisores. Personalmente, sin embargo, la considero importante por otro motivo: esta tesis doctoral también recoge toda la ayuda y el apoyo de quienes me han acompañado durante todos estos años, y para ellos es esta sección.

Me gustaría empezar agradeciendo su labor y su trato, como no puede ser de otra manera, a mis directores Julio y Salva. Gracias por depositar su confianza en mí para ser su alumno de doctorado; gracias por su paciencia y ayuda, por lo que me han enseñado tanto a nivel académico como a nivel personal; y gracias por haber conseguido, en definitiva, ayudarme a ser doctor.

Un escalón por debajo, pero igualmente de capital importancia para la elaboración de esta tesis, se encuentran mis compañeros del Grupo de Arquitecturas Paralelas. Muchos nombres han pasado por el acogedor laboratorio de la segunda planta, pero quiero hacer especial mención a algunos de ellos: gracias al ya mencionado José Duro, el buen *jebi*, por su elocuencia (qué eufemismo), generosidad y también, por qué no, por esos momentitos que nos ha regalado; gracias a José Rocher, incansable compañero de fatigas y lloros, por su sinceridad y complicidad desinteresadas; gracias a Javier Prades, por los cafés, por la pajita a Marte, por llevarme habitualmente la contraria, por las 13 Copas de Europa y por ayudarme a ver la vida de otro modo; gracias a Francisco Andújar, el doctor de Isso, eminencia albaceteña en historia borbónica y redes de computadores, por su energía contagiosa; y gracias a Leíto Chancay, cuya amistad debería contar como

Core A\*, por todo en general y mucho en particular. A todos los demás: Josué, José María, Tomás, Santi, Danilo, Willian, Jaime, Adrián, Andrés, Escamilla, Vicent, Xisco (¡alabado seas!), Carlos, Lucía, Ricardo ... gracias por haber hecho de este viaje uno que mereciera la pena vivir.

Por último, quiero agradecer a mi familia y amigos su apoyo incondicional durante este tiempo. A mis padres, que siempre se las arreglan para ayudarme hasta en los temas más insospechados. A mi pareja, a la que se le ha hecho el doctorado casi más largo que a mí. A mis abuelos, en especial a mi querido abuelo Andrés, al que también se le ha hecho largo mi doctorado y ha preferido ver la presentación desde arriba. A mi tía Dori, por preocuparse tanto por mí. Y a mis amigos, que siempre están ahí, porque sin saberlo ayudan cada día a empezar el siguiente con una sonrisa. Gracias de corazón a todos.

# Contents

| Li            | st of | Figures                                              | ciii |

|---------------|-------|------------------------------------------------------|------|

| $\mathbf{Li}$ | st of | Tables                                               | χV   |

| $\mathbf{A}$  | bbrev | viations and Acronyms x                              | vii  |

| $\mathbf{A}$  | bstra | ct                                                   | cix  |

| R             | esum  | en                                                   | xi   |

| R             | esum  | xx                                                   | ciii |

| 1             | Intr  | roduction                                            | 1    |

|               | 1.1   | Background: Shared Resources in Chip Multiprocessors | 2    |

|               |       | 1.1.1 Chip Multiprocessor                            | 3    |

|               |       | 1.1.2 Cache Hierarchy                                | 5    |

|               |       | 1.1.3 Network On-Chip                                | 7    |

|               |       | 1.1.3.1 Photonics Interconnects                      | 8    |

|               | 1.2   | Main Contributions of the Thesis                     | 9    |

|               | 1.3   | Thesis Outline                                       | 10   |

| 2             | Rela  | ated Work                                            | 13   |

|               | 2.1   | Optical Interconnects                                | 14   |

|               |       | 2.1.1 Optical Devices                                | 14   |

|               |       | 2.1.2 Optical Networks On-Chip                       | 15   |

|               | 2.2   | Adaptive Cache Organizations                         | 17   |

|               |       | 2.2.1 Cache Partitioning                             | 18   |

|               |       | 2.2.2 Cooperative Caching                            | 20   |

|               |       | 2.2.3 Other Approaches                               | 21   |

|               | 2.3   | Energy Consumption in the Cache Hierarchy            | 22   |

|               |       | 2.3.1 Reducing Energy Consumption in Caches          | 22   |

|               |       | 2.3.2 Alternative Technologies                       | 24   |

|               | 2.4   | Summary                                              | 24   |

| 3             | Exp   | perimental Framework                                 | 27   |

|               | 3.1   | Simulation Framework                                 | 28   |

|               |       | 3.1.1 Multi2Sim                                      | 28   |

|               |       | 3.1.1.1 Chip Multiprocessor                          | 29   |

Contents

|   |     |         | 3.1.1.2 Cache Hierarchy                                      |

|---|-----|---------|--------------------------------------------------------------|

|   |     |         | 3.1.1.3 NMOESI coherence protocol                            |

|   |     | 0.4.0   | 3.1.1.4 Interconnection Layer                                |

|   |     | 3.1.2   | DRAMSim2                                                     |

|   | 0.0 | 3.1.3   | CACTI 6.5                                                    |

|   | 3.2 | Bench   | mark Suites                                                  |

| 4 |     |         | y Modeling an Optical-NoC in a Detailed Simulation Envi-     |

|   |     | ment    | 37                                                           |

|   | 4.1 |         | round on Optical Interconnects                               |

|   |     | 4.1.1   | Silicon Photonics Devices                                    |

|   |     | 4.1.2   | Working Example                                              |

|   |     | 4.1.3   | Communication Schemes                                        |

|   | 4.0 | 3.5.1.1 | 4.1.3.1 Dense Wavelength Division Multiplexing               |

|   | 4.2 |         | ing the Components of an Optical Network-on-Chip             |

|   | 4.3 |         | d System: CMP with ONoC                                      |

|   |     | 4.3.1   | Optical Token-based Arbitration                              |

|   |     | 4.3.2   | Experimental Setup                                           |

|   | 4.4 | _       | imental Results                                              |

|   |     | 4.4.1   | Benchmark Characterization                                   |

|   |     | 4.4.2   | Individual Execution                                         |

|   |     | 4.4.3   | Multiprogram Workloads                                       |

|   |     | 4.4.4   | Power Consumption                                            |

|   | 4.5 | Summ    | ary                                                          |

| 5 | FOS | S: A L  | ow Power Cache Organization for Chip Multiprocessors 65      |

|   | 5.1 | Cache   | Demands and Performance Analysis                             |

|   | 5.2 | Flat C  | On-chip Storage                                              |

|   |     | 5.2.1   | Buffer Management Mechanism                                  |

|   |     | 5.2.2   | Buffer Management Mechanism Evaluation                       |

|   |     | 5.2.3   | Implementation Issues and Shared Data Support                |

|   | 5.3 | FOS N   | Network-on-Chip                                              |

|   |     | 5.3.1   | FOS ONoC                                                     |

|   |     | 5.3.2   | Energy Consumption in the FOS ONoC 81                        |

|   | 5.4 | Exper   | imental Framework and Studied Approaches 83                  |

|   |     | 5.4.1   | Simulation Setup                                             |

|   |     | 5.4.2   | Studied Approaches                                           |

|   |     | 5.4.3   | Design of Multiprogram Workloads                             |

|   | 5.5 | Exper   | imental Results                                              |

|   |     | 5.5.1   | Energy Consumption of Multiprogram Workloads                 |

|   |     | 5.5.2   | Performance Evaluation of Individual Applications 89         |

|   |     | 5.5.3   | Performance and Cache Space Management Evaluation for Multi- |

|   |     |         | program Workloads                                            |

|   |     | 5.5.4   | Energy Efficiency                                            |

|   | 5.6 | Summ    | arv 96                                                       |

*Contents* xi

| 6 | FOS   | S-Mt:   | An efficient Flat Storage Organization for Multithreaded |            |

|---|-------|---------|----------------------------------------------------------|------------|

|   | Wo    | rkloads |                                                          | 99         |

|   | 6.1   | Backgr  | ound: the FOS architecture                               | 00         |

|   | 6.2   | Flat O  | n-chip Storage for Multithreaded Applications            | 00         |

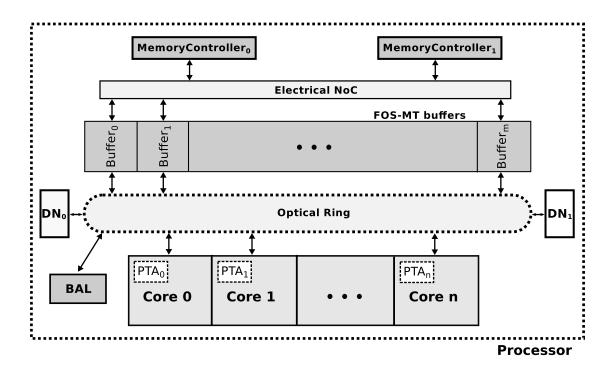

|   |       | 6.2.1   | FOS-Mt Architecture Overview                             | 00         |

|   |       | 6.2.2   | FOS-Mt Architecture: Detailed Implementation             | 02         |

|   |       | 6.2.3   | Off-Core Buffer Management                               | 08         |

|   | 6.3   | FOS-N   | It Optical Network-on-Chip                               | 14         |

|   |       | 6.3.1   | FOS ONoC                                                 | 15         |

|   |       | 6.3.2   | Energy model                                             | 17         |

|   | 6.4   | Experi  | mental Framework                                         | 18         |

|   |       | 6.4.1   | Studied Approaches                                       | 19         |

|   | 6.5   | Experi  | mental Results                                           | 22         |

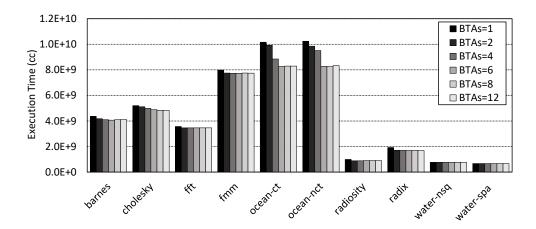

|   |       | 6.5.1   | Impact of the PTA Size on Performance                    | 22         |

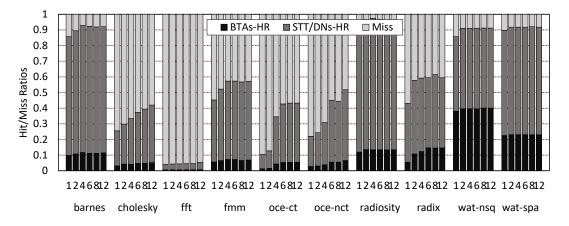

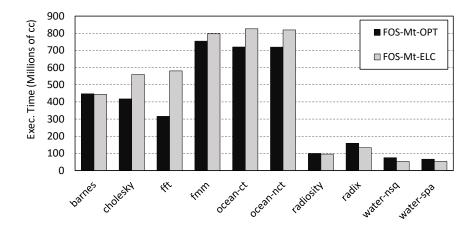

|   |       | 6.5.2   | Impact of the Optical Ring in FOS-Mt                     | 24         |

|   |       | 6.5.3   | Energy Evaluation                                        | 25         |

|   |       | 6.5.4   | Performance analysis                                     | 29         |

|   |       | 6.5.5   | Energy Efficiency                                        | 30         |

|   |       | 6.5.6   | Comparison against Cache Decay Approaches                | 31         |

|   | 6.6   | Summ    | ary                                                      | 33         |

| 7 | Con   | clusio  | us 1                                                     | <b>3</b> 5 |

|   | 7.1   | Contri  | outions                                                  | 36         |

|   | 7.2   | Future  | Directions                                               | 38         |

|   | 7.3   | Public  | ations                                                   | 38         |

| R | efere | nces    | 1.                                                       | 41         |

# List of Figures

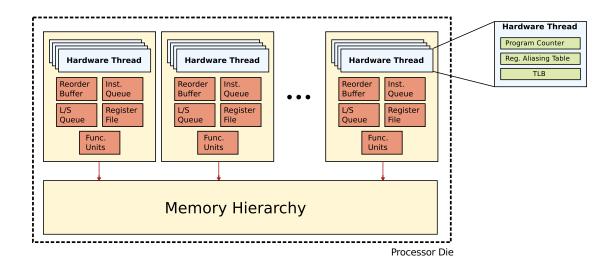

| 3.1  | Multi2Sim model of a CMP implementing N superscalar cores                                                                 | 29 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

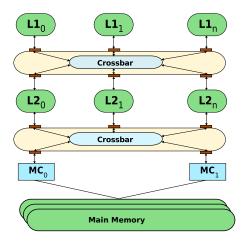

| 3.2  | Model of a 2-level memory hierarchy in Multi2Sim                                                                          | 30 |

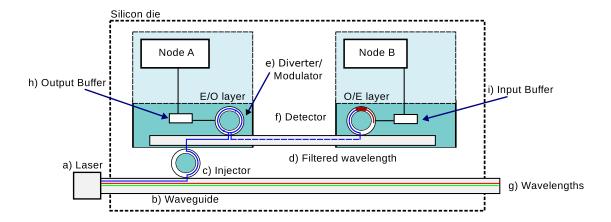

| 4.1  | End-to-end transmission between two network nodes using photonic in-                                                      | 40 |

| 4.0  | terconnects.                                                                                                              | 40 |

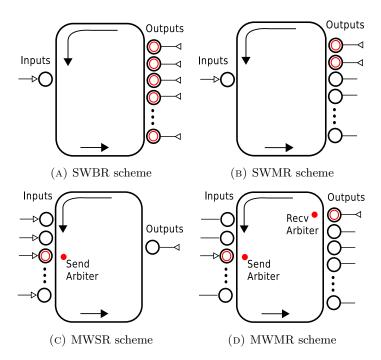

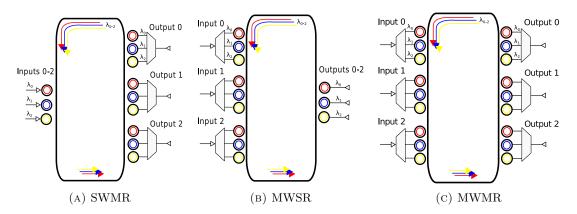

| 4.2  | Communication schemes using a single wavelength for transmissions                                                         | 42 |

| 4.3  | Communication schemes using DWDM                                                                                          | 43 |

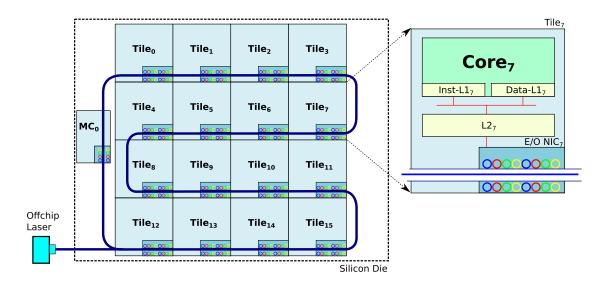

| 4.4  | Block diagram of the evaluated system                                                                                     | 48 |

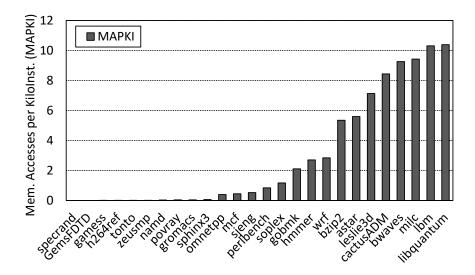

| 4.5  | Memory Accesses Per KiloInstructions (MAPKI) of SPEC2006                                                                  | 54 |

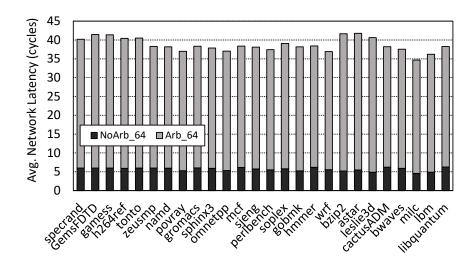

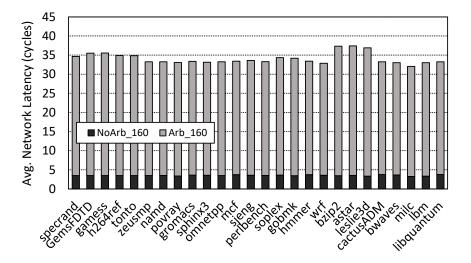

| 4.6  | Network latency of benchmarks executed with and without arbitration                                                       | == |

| 4.7  | delay and 64 wavelengths per waveguide                                                                                    | 55 |

| 4.7  | delay and 160 wavelengths per waveguide                                                                                   | 55 |

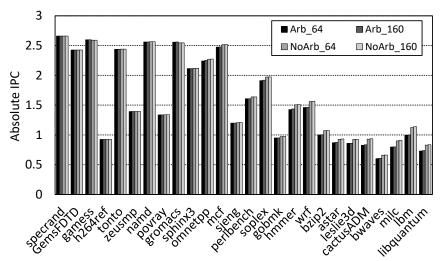

| 4.8  | Absolute IPC of executions with and without arbitration delay in 64 and                                                   | 55 |

| 1.0  | 160 wavelengths per waveguide configurations                                                                              | 57 |

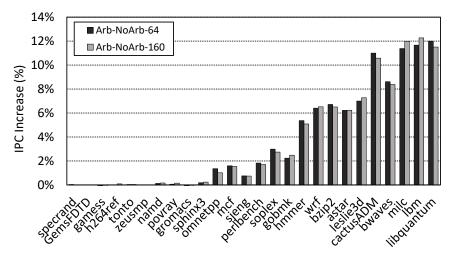

| 4.9  | IPC deviation of executions with and without arbitration delay in 64 and                                                  | ٠. |

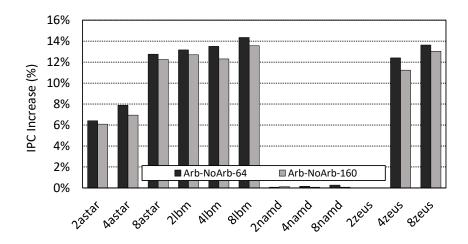

| 1.0  | 160 wavelengths per waveguide configurations                                                                              | 58 |

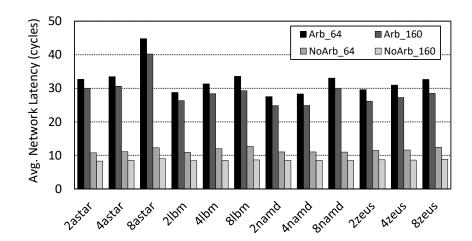

| 4.10 |                                                                                                                           |    |

|      | and 160 wavelengths per waveguide configurations                                                                          | 59 |

| 4.11 | IPC deviation of executions with and without arbitration delay in 64 and                                                  |    |

|      | 160 wavelengths per waveguide configurations                                                                              | 60 |

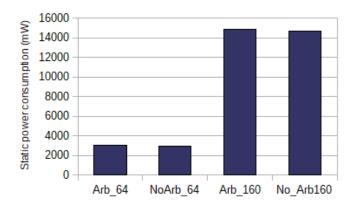

| 4.12 | Static power consumption (mW) required by the four photonic network                                                       |    |

|      | configurations studied                                                                                                    | 62 |

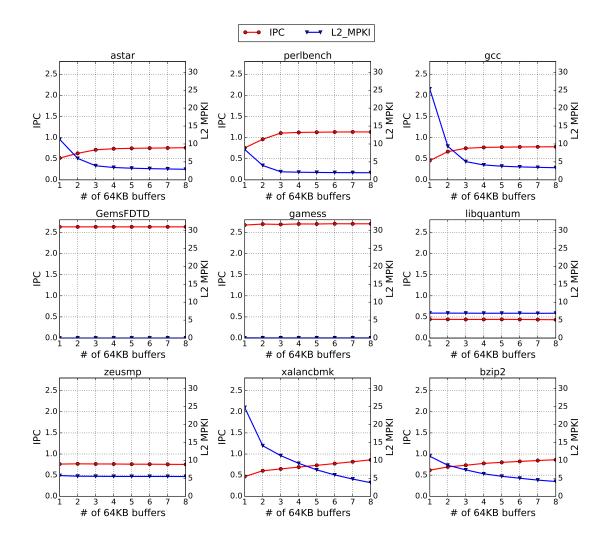

| 5.1  | IPC and L2 MPKI values varying the number of buffers (1 buffer is $64\ KB$                                                |    |

|      | - 8 buffers are 512 $KB$ )                                                                                                | 66 |

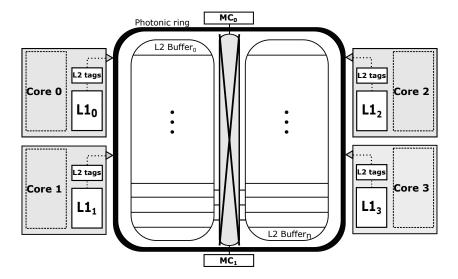

| 5.2  | Schematic of the proposed architecture                                                                                    | 68 |

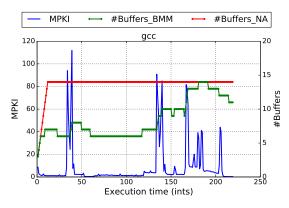

| 5.3  | MPKI and allocated buffers for xalancbmk, gcc and libquantum along                                                        |    |

|      | execution time                                                                                                            | 73 |

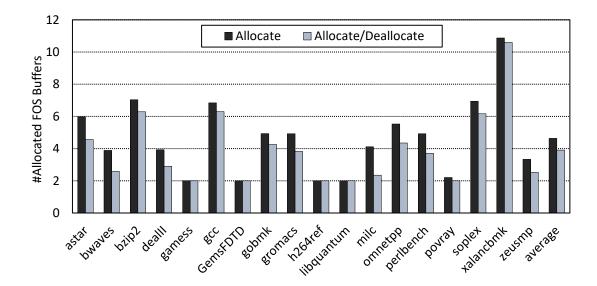

| 5.4  | Average number of buffers allocated with and without activating the deal-                                                 |    |

|      | location algorithm.                                                                                                       | 74 |

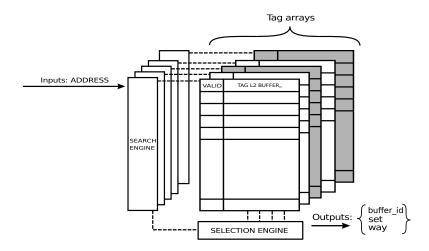

| 5.5  | High-level hardware schematic of a PTA module                                                                             | 75 |

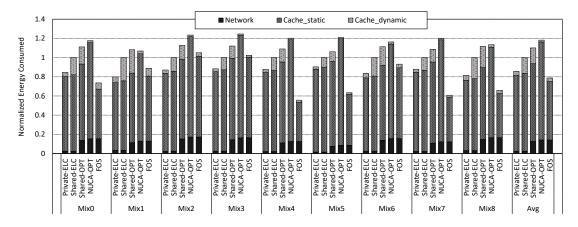

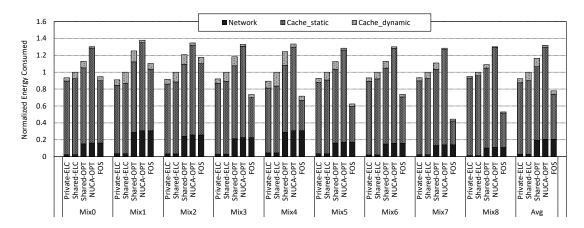

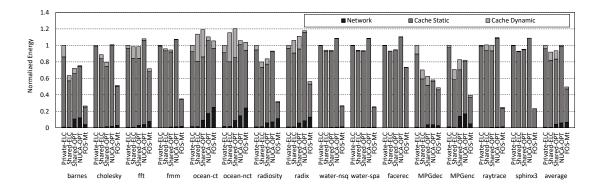

| 5.6  | Normalized energy consumption of 2-benchmark mixes                                                                        | 87 |

| 5.7  | Normalized energy consumption of 4-benchmark mixes                                                                        | 87 |

| 5.8  | Normalized performance of the individual applications                                                                     | 89 |

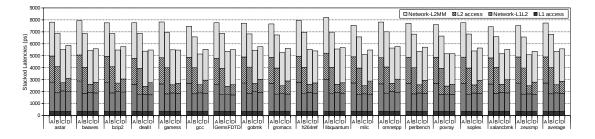

| 5.9  | Memory subsystem latencies broken down in four main categories. Legend: A: Shared-ELC, B: Shared-OPT, C: NUCA-OPT, D: FOS | 89 |

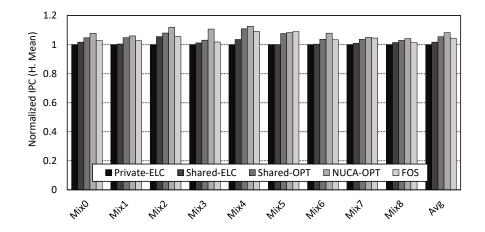

| 5.10 | Normalized Performance of 2-bench mixes                                                                                   | 91 |

List of Figures xiv

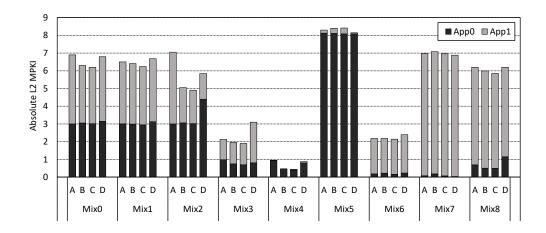

| 5.11 | MPKIs of 2-benchmark mixes for: A: Private, B: Shared, C: NUCA, D:                          |

|------|---------------------------------------------------------------------------------------------|

|      | FOS                                                                                         |

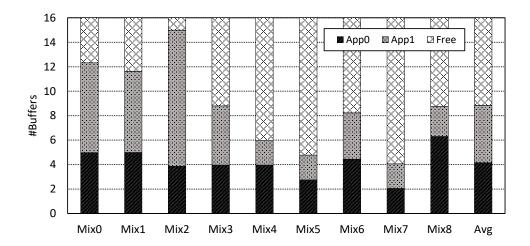

| 5.12 | Average number of buffers assigned to each application in FOS 92                            |

| 5.13 | Normalized Performance of 4-bench mixes                                                     |

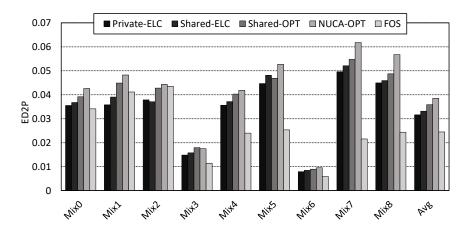

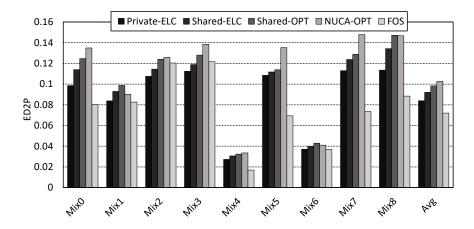

| 5.14 | Energy Delay Squared Product of 2-benchmark mixes                                           |

| 5.15 | Energy Delay Squared Product of 4-benchmark mixes 95                                        |

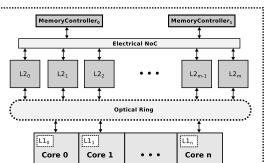

| 6.1  | Block diagram of FOS-Mt                                                                     |

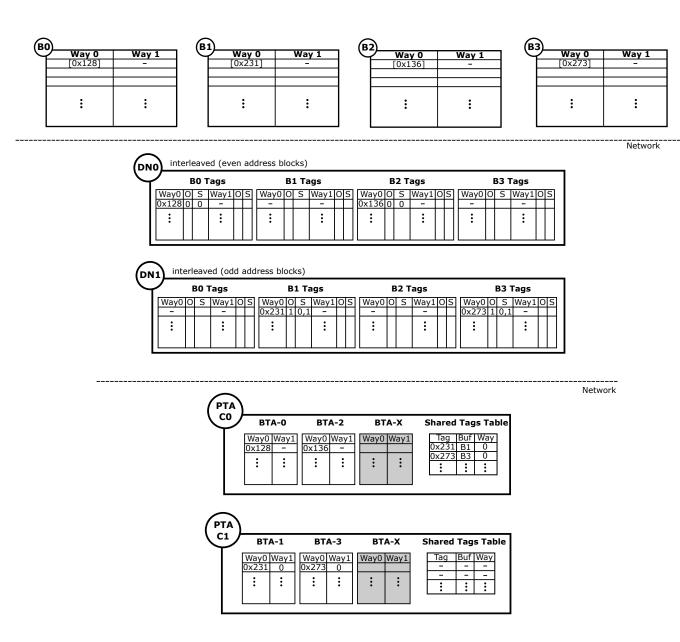

| 6.2  | Example implementation of a 2core-4buffers FOS-Mt                                           |

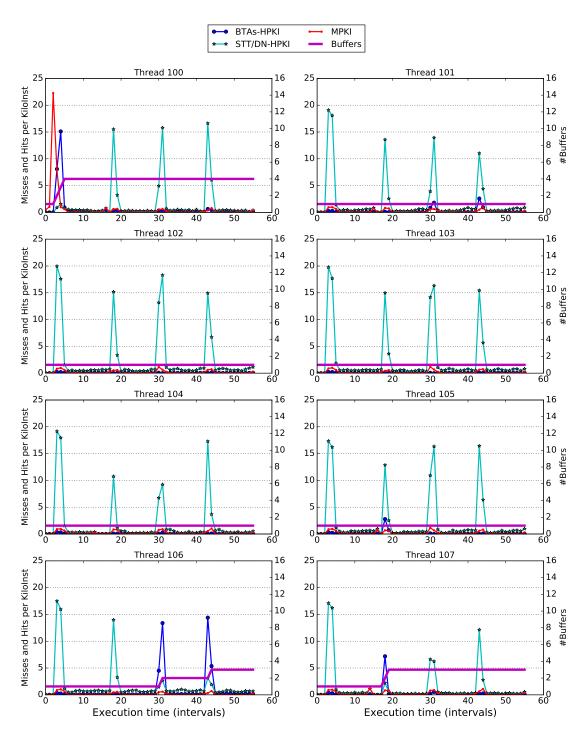

| 6.3  | Number of allocated buffers during execution time for the $8 \text{ barnes}$ threads. $111$ |

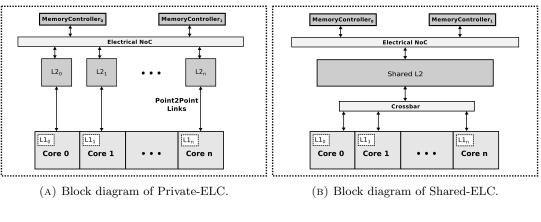

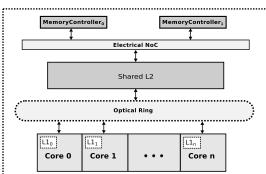

| 6.4  | Block diagrams of all the conventional baseline approaches                                  |

| 6.5  | Execution Time                                                                              |

| 6.6  | Distribution of access types. The number in the X axis below each bar                       |

|      | indicates the number of BTAs                                                                |

| 6.7  | Execution time across the studied workloads for FOS-Mt with electrical                      |

|      | crossbar and optical ring interconnects                                                     |

| 6.8  | Normalized energy consumed by conventional approaches and FOS-Mt                            |

|      | with respect to <i>Private-ELC</i>                                                          |

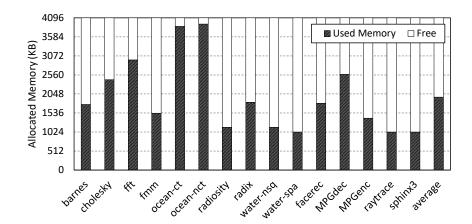

| 6.9  | Average amount of cache space (KB) allocated during execution in FOS-Mt.127                 |

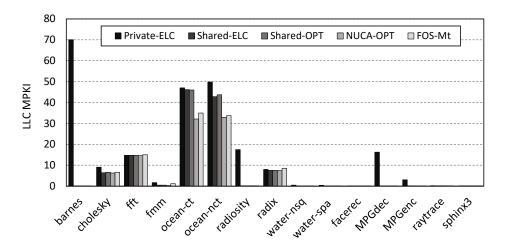

| 6.10 | L2 Misses Per Kilo-Instruction                                                              |

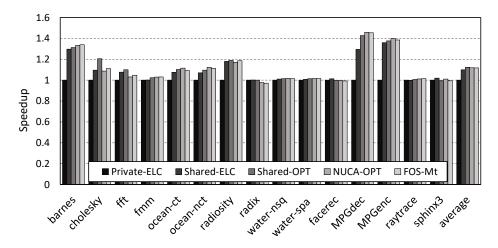

| 6.11 | Speedup with respect to <i>Private-ELC</i>                                                  |

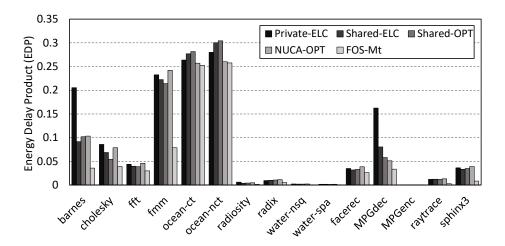

| 6.12 | Energy Delay Product (EDP) of the studied approaches                                        |

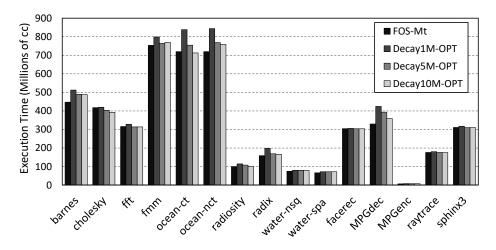

| 6.13 | Execution time of FOS-Mt and various decay approaches                                       |

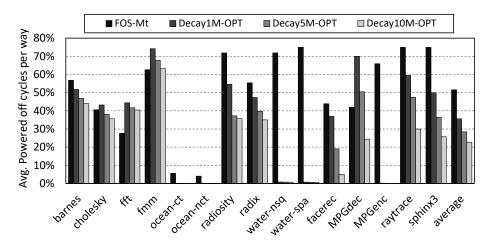

| 6.14 | Average percentage of cycles powered off per way during the execution. $\cdot$ . 132        |

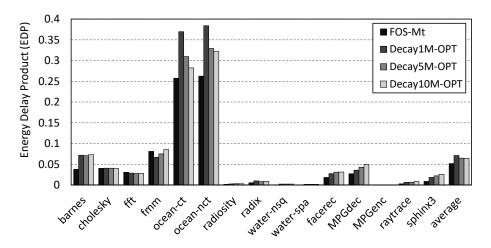

| 6.15 | Energy Delay Product of FOS-Mt and Decay configurations                                     |

# List of Tables

| 4.1 | mance and energy consumption                                             | 17 |

|-----|--------------------------------------------------------------------------|----|

| 4.2 | Baseline system setup. Network cycles account for $100~ps$ , while clock |    |

|     | cycles account for 333 $ps$                                              | 52 |

| 4.3 | Energy consumption parameters                                            | 61 |

| 5.1 | Evolution of size devoted to tag-storing structures in FOS               | 77 |

| 5.2 | Optical network-on-chip parameters and latencies                         | 79 |

| 5.3 | Loss values of the photonic components                                   | 81 |

| 5.4 | Baseline system parameters                                               | 83 |

| 5.5 | Composition of the evaluated 2- and 4-benchmark mixes. Legend: M:        |    |

|     | Minimum Slice Needs, L: Limited Slice Needs, N: Non-limited Slice Needs. | 85 |

| 5.6 | Energy efficiency, performance and energy savings achieved by each ar-   |    |

|     | chitecture normalized to the Private-ELC approach                        | 96 |

| 6.1 | FOS-Mt design considerations                                             | 03 |

| 6.2 | Optical network-on-chip parameters and latencies                         |    |

| 6.3 | Loss values of photonic components                                       | 17 |

| 6.4 | Baseline system parameters                                               | 20 |

| 6.5 | Access time and capacity of the Buffer Tag Arrays                        |    |

# Abbreviations and Acronyms

$\mathbf{ANTT} \quad \mathbf{A} \text{verage } \mathbf{N} \text{ormalized } \mathbf{T} \text{urnaround } \mathbf{T} \text{ime}$

CMP Chip Multicore Processor

CPI Cycles Per Instruction

DRAM Dynamic Random-Access Memory

IABW Ideal Average BandWidth

IPC Instructions Per Cycle

LLC Last-Level Cache

L1 First-level (cache)

L2 Second-level (cache)

L3 Third-level (cache)

MPKI Misses Per Kilo-Instruction

NUMA Non-Uniform Memory Access

SMT Simultaneous MultiThreading Memory

ST Single-Threaded

PA Process Allocation

PS Process Selection

OATR Online Average Transaction Rate

OS Operating System

QoS Quality of Service

ROB ReOrder Buffer

STP System Throughput

TLB Transaction Lookaside Buffer

UMA Uniform Memory Access

### Abstract

Current multicores face the challenge of sharing resources among the different processor cores. Two main shared resources act as major performance bottlenecks in current designs: the off-chip main memory bandwidth and the last level cache. Additionally, as the core count grows, the network on-chip is also becoming a potential performance bottleneck, since traditional designs may find scalability issues in the near future.

Memory hierarchies communicated through fast interconnects are implemented in almost every current design as they reduce the number of off-chip accesses and the overall latency, respectively. Main memory, caches, and interconnection resources, together with other widely-used techniques like prefetching, help alleviate the huge memory access latencies and limit the impact of the core-memory speed gap. However, sharing these resources brings several concerns, being one of the most challenging the management of the inter-application interference. Since almost every running application needs to access to main memory, all of them are exposed to interference from other co-runners in their way to the memory controller. For this reason, making an efficient use of the available cache space, together with achieving fast and scalable interconnects, is critical to sustain the performance in current and future designs. This dissertation analyzes and addresses the most important shortcomings of two major shared resources: the Last Level Cache (LLC) and the Network on Chip (NoC).

First, we study the scalability of both electrical and optical NoCs for future multicores and many-cores. To perform this study, we model optical interconnects in a cycle-accurate multicore simulation framework. A proper model is required; otherwise, important performance deviations may be observed otherwise in the evaluation results. The study reveals that, as the core count grows, the effect of distance on the end-to-end latency can negatively impact on the processor performance. In contrast, the study also shows that silicon nanophotonics are a viable solution to solve the mentioned latency problems.

This dissertation is also motivated by important design concerns related to current memory hierarchies, like the oversizing of private cache space, data replication overheads, and Abstract xx

lack of flexibility regarding sharing of cache structures. These issues, which can be overcome in high performance processors by virtue of huge LLCs, can compromise performance in low power processors. To address these issues we propose a more efficient cache hierarchy organization that leverages optical interconnects. The proposed architecture is conceived as an optically interconnected two-level cache hierarchy composed of multiple cache modules that can be dynamically turned on and off independently. Experimental results show that, compared to conventional designs, static energy consumption is improved by up to 60% while achieving similar performance results.

Finally, we extend the proposal to support both sequential and parallel applications. This extension is required since the proposal adapts to the dynamic cache space needs of the running applications, and multithreaded applications's behaviors widely differ from those of single threaded programs. In addition, coherence management is also addressed, which is challenging since each cache module can be assigned to any core at a given time in the proposed approach. For parallel applications, the evaluation shows that the proposal achieves up to 78% static energy savings.

In summary, this thesis tackles major challenges originated by the sharing of on-chip caches and communication resources in current multicores, and proposes new cache hierarchy organizations leveraging optical interconnects to address them. The proposed organizations reduce both static and dynamic energy consumption compared to conventional approaches while achieving similar performance; which results in better energy efficiency.

### Resumen

Los procesadores multinúcleo actuales cuentan con recursos compartidos entre los diferentes núcleos. Dos de estos recursos compartidos, la cache de último nivel y el ancho de banda de memoria principal, pueden convertirse en cuellos de botella para el rendimiento. Además, con el crecimiento del número de núcleos que implementan los diseños más recientes, la red dentro del chip también se convierte en un cuello de botella que puede afectar negativamente al rendimiento, ya que las redes tradicionales pueden encontrar limitaciones a su escalabilidad en el futuro cercano.

Prácticamente la totalidad de los diseños actuales implementan jerarquías de memoria que se comunican mediante rápidas redes de interconexión. Esta organización es eficaz dado que permite reducir el número de accesos que se realizan a memoria principal y la latencia media de acceso a memoria. Las caches, la red de interconexión y la memoria principal, conjuntamente con otras técnicas conocidas como la prebúsqueda, permiten reducir las enormes latencias de acceso a memoria principal, limitando así el impacto negativo ocasionado por la diferencia de rendimiento existente entre los núcleos de cómputo y la memoria. Sin embargo, compartir los recursos mencionados es fuente de diferentes problemas y retos, siendo uno de los principales el manejo de la interferencia entre aplicaciones. Hacer un uso eficiente de la jerarquía de memoria y las caches, así como contar con una red de interconexión apropiada, es necesario para sostener el crecimiento del rendimiento en los disenos tanto actuales como futuros. Esta tesis analiza y estudia los principales problemas e inconvenientes observados en estos dos recursos: la cache de último nivel y la red dentro del chip.

En primer lugar, se estudia la escalabilidad de las tradicionales redes dentro del chip con topología de malla, así como ésta puede verse comprometida en próximos disenõs que cuenten con mayor número de núcleos. Los resultados de este estudio muestran que, a mayor número de núcleos, el impacto negativo de la distancia entre núcleos en la latencia puede afectar seriamente al rendimiento del procesador. Como solución a este problema, en esta tesis proponemos una de red de interconexión óptica modelada en un entorno de

Resumen xxii

simulación detallado, que supone una solución viable a los problemas de escalabilidad observados en los diseños tradicionales.

A continuación, esta tesis dedica un esfuerzo importante a identificar y proponer soluciones a los principales problemas de diseño de las jerarquías de memoria actuales como son, por ejemplo, el sobredimensionado del espacio de cache privado, la existencia de réplicas de datos y rigidez e incapacidad de adaptación de las estructuras de cache. Aunque bien conocidos, estos problemas y sus efectos adversos en el rendimiento pueden ser evitados en procesadores de alto rendimiento gracias a la enorme capacidad de la cache de último nivel que este tipo de procesadores típicamente implementan. Sin embargo, en procesadores de bajo consumo, no existe la posibilidad de contar con tales capacidades y hacer un uso eficiente del espacio disponible es crítico para mantener el rendimiento. Como solución a estos problemas en procesadores de bajo consumo, proponemos una novedosa organización de jerarquía de dos niveles cache que utiliza una red de interconexión óptica. Los resultados obtenidos muestran que, comparado con diseños convencionales, el consumo de energía estática en la arquitectura propuesta es un 60 % menor, pese a que los resultados de rendimiento presentan valores similares.

Por último, hemos extendido la arquitectura propuesta para dar soporte tanto a aplicaciones paralelas como secuenciales. Esta extensión no es trivial, ya que la propuesta adapta dinámicamente el espacio de cache requerido por las aplicaciones en ejecución, y es bien conocido que aplicaciones paralelas y secuenciales presentan coomportamientos muy diferentes. Además, el manejo de la coherencia de memoria se vuelve más complejo, ya que los módulos de cache pueden ser asignados y desasignados a cualquier núcleo en cualquier momento de la ejecución. Los resultados obtenidos con la esta nueva arquitectura muestran un ahorro de hasta el 78 % de energía estática en la ejecución de aplicaciones paralelas.

En resumen, esta tesis estudia y propone soluciones a los problemas derivados de la compartición de caches y recursos de comunicación dentro del chip en los procesadores multinúcleo actuales. Las dos organizaciones de cache propuestas reducen el consumo de energía tanto estática como dinámica en comparación a otras arquitecturas convencionales, a la vez que consiguen un rendimiento similar.

### Resum

Els processadors multinucli actuals compten amb recursos compartits entre els diferents nuclis. Dos d'aquests recursos compartits, la memòria d'últim nivell i l'ample de banda de memòria principal, poden convertir-se en colls d'ampolla per al rendiment. A més, amb el creixement del nombre de nuclis que implementen els dissenys més recents, la xarxa dins del xip també es converteix en un coll d'ampolla que pot afectar negativament el rendiment, ja que les xarxes tradicionals poden trobar limitacions a la seva escalabilitat en el futur proper.

Pràcticament la totalitat dels dissenys actuals implementen jerarquies de memòria que es comuniquen mitjançant ràpides xarxes d'interconnexió. Aquesta organització és eficaç atès que permet reduir el nombre d'accessos que es realitzen a memòria principal i la latència mitjana d'accés a memòria. Les caches, la xarxa d'interconnexió i la memòria principal, conjuntament amb altres tècniques conegudes com la prebúsqueda, permeten reduir les enormes latències d'accés a memòria principal, limitant així l'impacte negatiu ocasionat per la diferència de rendiment existent entre els nuclis de còmput i la memòria. No obstant això, compartir els recursos esmentats és font de diversos problemes i reptes, sent un dels principals la gestió de la interferència entre aplicacions. Fer un ús eficient de la jerarquia de memòria i les caches, així com comptar amb una xarxa d'interconnexió apropiada, és necessari per sostenir el creixement del rendiment en els dissenys tant actuals com futurs. Aquesta tesi analitza i estudia els principals problemes i inconvenients observats en aquests dos recursos: la memòria cache d'últim nivell i la xarxa dins del xip.

En primer lloc, s'estudia l'escalabilitat de les xarxes tradicionals dins del xip amb topologia de malla, així com aquesta es pot veure compromesa en propers dissenys que

compten amb major nombre de nuclis. Els resultats d'aquest estudi mostren que, a

major nombre de nuclis, l'impacte negatiu de la distància entre nuclis en la latència pot

afectar seriosament al rendiment del processador. Com a solució a aquest problema,

en aquesta tesi proposem una xarxa d'interconnexió òptica modelada en un entorn de

Resum

simulació detallat, que suposa una solució viable als problemes d'escalabilitat observats en els dissenys tradicionals.

A continuació, aquesta tesi dedica un esforç important a identificar i proposar solucions als principals problemes de disseny de les jerarquies de memòria actuals com són, per exemple, el sobredimensionat de l'espai de memòria cache privat, l'existència de rèpliques de dades i la rigidesa i incapacitat d'adaptació de les estructures de memòria cache. Encara que ben coneguts, aquests problemes i els seus efectes adversos en el rendiment poden ser evitats en processadors d'alt rendiment gràcies a l'enorme capacitat de la memòria cache d'últim nivell que aquest tipus de processadors típicament implementen. No obstant això, en processadors de baix consum, no hi ha la possibilitat de comptar amb aquestes capacitats, i fer un ús eficient de l'espai disponible es torna crític per mantenir el rendiment. Com a solució a aquests problemes en processadors de baix consum, proposem una nova organització de jerarquia de dos nivells de memòria cache que utilitza una xarxa d'interconnexió òptica. Els resultats obtinguts mostren que, comparat amb dissenys convencionals, el consum d'energia estàtica en l'arquitectura proposada és un 60% menor, malgrat que els resultats de rendiment presenten valors similars.

Per últim, hem estès l'arquitectura proposada per donar suport tant a aplicacions paral·leles com seqüencials. Aquesta extensió no ès trivial, ja que la proposta adapta dinàmicament l'espai de memòria cache requerit per les aplicacions en execució, i ès ben conegut que aplicacions paral·leles i seqüencials presenten comportaments molt diversos. A més, la gestió de la coherència de memòria es torna més complex, ja que els mòduls de memòria cache poden ser assignats i desassignats a qualsevol nucli en qualsevol moment de l'execució. Els resultats obtinguts amb aquesta nova arquitectura mostren un estalvi de fins al 78 % d'energia estàtica en l'execució d'aplicacions paral·leles.

En resum, aquesta tesi estudia i proposa solucions als problemes derivats de la compartició de caches i recursos de comunicació dins del xip en els processadors multinucli actuals. Les dues organitzacions de memòria cache proposades redueixen el consum de energia tant estàtica com dinàmica en comparació a altres arquitectùres convencionals, alhora que aconsegueixen un rendiment similar.

## Chapter 1

# Introduction

This chapter introduces some concepts to help understand the manuscript and presents the motivation for the work developed in the proposed approaches. First, background on Chip Multiprocessors (CMP) is introduced, focusing on major components of the architecture like the cache hierarchy or the network-on-chip. Next, we discuss major challenges that arise in these research topics and how they are addressed in current processors. After that, we present insights about where performance problems arise in multicores due to shared resources, especially the network on chip (NoC) and the shared caches. Then, we summarize the way this dissertation addresses these shortcomings by proposing a novel cache organization. Finally, we present the thesis outline.

# 1.1 Background: Shared Resources in Chip Multiprocessors

Since published by Gordon Moore in 1965, the performance improvement of microprocessors has roughly followed what is known as the Moore's Law [1], which states that the amount of transistors in a microprocessor doubles every two years. Following this rule, the performance of microprocessors has steadily increased throughout the past decades, thanks to the continuous reductions in the integration scale and the design of more and more complex hardware structures and architectures. Although this technology scaling trend has resulted in the achievement of huge computing power, the bigger complexities and the large amounts of transistors bring new concerns regarding power consumption.

As the number of transistors grows, the electrical power they consume generates heat that far exceeds the cooling capacities of current processors. This fact is known as the *power wall*, which refers to the performance scaling limitations caused by power consumption constraints in terms of heat and cost. There are two possible solutions to address the power wall problem: i) designing inexpensive cooling techniques and technologies; and ii) reducing the processor complexity and, by doing so, cutting down the power consumption.

In order to keep the power consumption in acceptable levels while sustaining the performance gains brought by technology scaling, processor designers and manufacturers moved to multicore approaches following the second solution mentioned above. The multicore paradigm initially pursued to deploy multiple but less complex *cores* (i.e. computing units provided with a given amount of private memory) in a processor die as opposite to increasing the complexity of a single-core monolithic processor. This approach allows reducing the overall energy consumption while achieving higher aggregated performance than monolithic processors. Currently, multicores can be found not only in the high-performance computing market but also in almost any other segment of the market, since these processors have become ubiquitous in almost any commercial electronic device.

Multicore processors, however, are not exempt from other shortcomings and design issues. First, single-threaded applications need to be adapted to effectively exploit the parallelism provided by multicore architectures. Second, multicore architects reduce cost by implementing resources (e.g. the main memory bandwidth) which are shared among the processor cores. This fact, which represents an advantage from the cost perspective, becomes a shortcoming since inter-application interference is introduced at the shared resources, making the execution time of individual applications unpredictable.

This dissertation is aimed at achieving an efficient use of shared resources in a chip multiprocessor. Taking into account the different nature of each resource, this aim is challenging, since it has to be addressed from different directions. For this reason, we address this problem with a two-step strategy. First, we explore the use of a novel technology to address scalability issues of current and future electrical NoCs. Then, the results of this study are used to build, on the top of that, a holistic solution for the cache hierarchy. Finally, after these two steps, we refine and adapt the proposed solution to efficiently work with both single-threaded and multithreaded or parallel applications.

Below, chip multiprocessor architectures are further studied, including the specific challenges that still remain for each of these shared resources.

#### 1.1.1 Chip Multiprocessor

For the past decades, microprocessor manufacturers exploited the reductions on the integration scale to achieve more computing power. At the same time, hardware complexity increased as new components such as non blocking caches, support for out-of-order execution, or speculative loads were introduced in the new designs. Together, technology developments and refined hardware structures have sustained microprocessors performance, continuously increasing the maximum frequency (f) that the chips are able to achieve.

In conjunction with Moore's law, Dennard scaling [2] has been the other major pillar for the performance-driven computing industry. Formulated by Robert H. Dennard in 1974, the MOSFETs scaling rule states that as transistors get smaller, their power density remains constant. The method proposed by Dennard and his team allowed scaling chip dimensions, voltage, current and operating frequency while keeping a steady device power density. Following this rule, if there was a reduction in a transistor's linear size by 2, the power it used fell by 4 (with voltage and current both halving). Unfortunately, technological advances have exposed new findings that slow down the traditional scaling path predicted by these rules. On the one hand, as shrinking transistors becomes more and more challenging. Moore's law is expected to extend the duration between technology nodes far from that predicted by the initial rate. On the other hand, Dennard scaling has already been broken down. With current transistor sizes, the ability to drop the voltage and the current that they need to operate reliably has reached an end. This is because the original Dennard scaling rule accounted only for transistors size, voltage, current and frequency, that is, the dynamic power of the processor. However, as transistor dimensions shrinks, a new source of power dissipation appears in the form of leakage currents. The explanation to this fact is as follows: the Dennard scaling rule requires an equal scaling of the threshold voltage to scale down the supply voltage; threshold voltage, however, is physically limited and scaling it down dramatically increases static power; therefore, failing to scale down threshold voltage translates to failing to scale down supply voltage, which breaks Dennard scaling. In all projections, device power densities are expected to keep growing in the foreseeable future.

As a consequence of the breaking down of Dennard scaling, the operating frequencies of new devices stopped growing. Given this situation, chip manufacturers and designers adopted Chip Multiprocessors, also known as multicore processors. A CMP is typically a single processor that contains multiple cores, computing units that are provided with small private caches. The cores are connected through an interconnection network on-chip, which also links the cores to other shared resources like the last level cache (LLC) or the memory controllers. Multicore designs that implement a significant amount of cores (e.g. 32 cores) typically follow a mesh topology since it eases the layout of wires and facilitates the manufacture process.

The adoption of the multicore paradigm helped both performance and power consumption: the former, due to the exploitation of parallelism (i.e. tasks can be distributed among the available cores); and the latter, because of the lower complexity of the cores, which reduces their switched capacitance and, ultimately, the dynamic power consumption. These advantages, however, come at the expense of new challenges that need to be addressed by computer architects and software developers. For instance, in order to

exploit parallelism, applications first need to be adapted to divide their workload and therefore be benefited from the multiple cores.

Multicores also pose the challenge of sharing resources. Future multicores are expected to increase the amount of cores, hindering the management of the shared processor resources. Key shared resources in a typical multicore are the on-chip last level cache cache and the main memory bandwidth. When the cores are running different applications concurrently, these applications introduce interference at the shared resources, thrashing the cache or stressing the main memory bandwidth.

Another shared resource that is gaining importance as the core count increases is the onchip network. Technology advancements currently enable integrating hundreds of cores in a single chip, which compromises the scalability of existent NoC approaches. Additionally, CMPs need from fast communication among cores, caches, memory controllers and other resources; otherwise, the performance may be significantly compromised. Therefore, future multicore generations have to face the challenges of fast communications and low power consumption, so existent interconnection approaches and their scalability need to be revisited.

In order to sustain the performance while keeping power consumption in acceptable levels, multicore processors need to address the aforementioned issues, and make an efficient use of the available shared resources. With this objective, this dissertation analyzes and addresses specific problems derived from current NoCs and cache hierarchies. Below, these two major components of chip multiprocessors are further discussed and explained.

#### 1.1.2 Cache Hierarchy

Processors have implemented cache memories for more than four decades, becoming a key component since the design or the first pipelined processors. Cache memories exploit spatial and temporal localities of the data referenced by the running applications, which significantly boosts the system performance. Due to the increasing disparity between the speed of the cache and the main memory, new cache levels were deployed in the called cache hierarchy. The cache hierarchy includes huge last level caches with the aim of reducing the number of off-chip main memory accesses, therefore this organization helps mitigate the consumed main memory bandwidth.

Most existing multicores implement a three level cache hierarchy, where the two first levels are private to each core and the third level, referred to as the LLC, is shared by all the cores. The higher hierarchy cache levels (L1 cache and L2 cache) are small (e.g. from  $32 \ KB$  up to  $512 \ KB$ ) and fast, while the LLC size is much bigger, especially in high-performance processors. For instance, Intel Xeon Skylake processors implement an LLC of up to  $38.5 \ MB$  at its maximum configuration (28 cores), and IBM POWER8 devotes to it  $96 \ MB$  (12-chiplet processor) [3, 4].

It can be noticed that, to reduce the number of main memory accesses, current LLCs are on the order of tens of MB and this capacity keeps increasing. LLC misses are specially harmful for the processor performance, since accessing main memory is costly and can take hundreds of processor cycles. These huge latencies block the reorder buffer of the cores, and ultimately prevent them issuing new instructions. Additionally, since a key goal of LLCs is to avoid capacity misses, high associativities need to be used to reduce the number of conflict misses; for this reason, the associativity degree of the LLCs is usually higher than 16 ways.

Despite its huge capacity, the fact that the LLC is a shared resource rises important shortcomings that need to be addressed. First, requests from the co-running applications compete among them for the LLC, introducing interference in this resource. When distinct applications access the LLC, they can interfere each other and evict cache blocks that are being used by the co-runner, impairing the cache performance. Additionally, not all applications make an efficient use of the LLC, since some workloads (e.g. streaming applications) may have no locality. Other applications, like those belonging to the cloud segment, present different needs such as providing isolation or guaranteeing quality of service (QoS).

Efficiently managing the LLC is, therefore, an important concern that needs to be addressed for improving performance and fairness. Targeting this objective, many solutions have been proposed in the past to efficiently share the cache, being the most popular approach the cache partitioning policies (see Section 2.2.1). Approaches adopting this solution assign specific cache ways to the applications running in the processor cores according to different criteria. Proceeding in this way applications that make a less efficient use of the cache receive a reduced number of ways, which limits their adverse impact on

the performance. Way partitioning can be performed by software (i.e. page coloring), by extending the hardware capabilities or by modifying the replacement algorithm.

Although effective for reducing the interference, existing cache partitioning solutions do not completely solve the problem. Way partitioning solutions do not reduce the on-chip latency, since they mostly work at the LLC. Moreover, this kind of approaches are not as effective for processors that implement low-capacity caches, such as those belonging to the low-power and embedded segments of the market, as it is for high-performance processors. This means that, in order to improve the cache performance in multicores, a holistic approach on the topic needs to be taken, addressing both on-chip latencies and isolation capabilities.

#### 1.1.3 Network On-Chip

Multicores require from efficient on-chip interconnection networks to provide fast communication among cores, caches and memory controllers. Simple and effective electrical networks following a mesh topology are the mainstream design choice for many chip manufacturers, although some processors also implement ring-based topologies (e.g. Intel Skylake [3]). However, its effectiveness drops as the core count increases, and the scalability constraints of conventional electrical NoC need to be revisited.

Regarding scalability issues, the continuous reductions on the integration scale currently enable integrating hundreds of cores on a single chip [5–7]. Conventional electrical networks may suffer performance degradation when dealing with such a high number of cores. These networks often present a mesh topology where memory controllers are usually placed at the corners and edges of the processor chip. Since the NoC must interconnect all the processor tiles (e.g. core plus L2 cache), the higher the number of cores, the higher the average distance from the nodes to the memory controller, and hence to the main memory. In such a scheme, when a node requests a cache block, the incurred latencies and energy consumption could be unacceptable depending on the distance to the memory controller. Current multicore architectures incorporate several MCs to alleviate this shortcoming but, unfortunately, the number of memory controllers can not scale linearly with the number of nodes [8].

The scalability concerns are directly related with power consumption. As discussed before, in order to prevent heating problems, multicore designers are forced to keep a limited power budget. NoC designers are not exempt from this directive, since as the number of network nodes increases, so it does the number of network switches and the overall cost, in terms of power, of sending data through the network. It is expected, therefore, that high-performance CMPs exceeding a high number of cores (e.g. 100 cores) suffer from the power bottlenecks of current electrical interconnects [9].

For the last decade, the aforementioned concerns led to new and alternative designs to conventional NoCs. In this context, one of the most promising solutions to the scalability issues of existing approaches is photonics interconnects. Below, this novel technology is briefly presented and discussed.

#### 1.1.3.1 Photonics Interconnects

The need of a faster on-chip multicore communication technology has led to lay out the use of CMOS-compatible photonic interconnects as a possible solution. Nanophotonics technology has experienced a vertiginous development during the last decade and this trend is expected to continue in the next years. Because of its high bandwidth and energy consumption, which scarcely varies with the communication distance, CMOS compatible photonics interconnects is the most promising technology to satisfy future CMPs' bandwidth demands [10].

Manycore and multicore architectures can leverage the capacities provided by nanophotonics to reduce their network latency and, as a result, their average memory access time. Additionally, wavelength multiplexing eases the implementation of multicast and broadcast operations, which are widely used in CMPs (e.g. the coherence protocol performs multicast transmissions when invalidates incoherent copies in multiple nodes).

However, new technologies such as photonics interconnects bring the cost of facing also new challenges. Since this technology is still maturing, it is difficult to find up-to-date models in CMP simulation frameworks, which are mainly developed by computer architects whose focus is on computing and communication aspects. This situation leads to incomplete models whose results could present important deviations and generate an

expectancy on this technology that still does not correspond with its current development state. Therefore, the first challenge is achieving detailed and accurate simulation environments to develop reliable CMP simulators considering photonics interconnects.

Other major challenges still remain for this technology, especially for silicon photonics. On the one hand, current losses observed in silicon photonics devices can be too prohibitive from a power consumption perspective. The higher the loss introduced by these devices, the higher the output power that the laser source needs to drive all receivers at satisfaction bit error rates. On the other hand, ring heater power is yet to be improved. Ring heater power is needed since it mitigates temperature variations and post-manufacturing geometric mismatches of microring resonators. A prohibitive heating power means that only a limited amount of microrings can be equipped in the Optical-Network on Chip (ONoC) [11]; otherwise, the static power consumption would be out of budget.

However the challenges, the potential benefits that nanophotonics technology can bring to already existing and future CMP architectures are still worth it. Current efforts of computer architects shall focus on achieving accurate models and designing new interconnection approaches so, together with technology scaling, on-chip communications could overcome scalability issues in the near future.

#### 1.2 Main Contributions of the Thesis

The three main contributions of this thesis are described below:

• Accurately modeling an ONoC in a CMP simulation framework. Photonic interconnects are a promising solution for the so-called communication bottleneck in current CMP architectures. This technology presents an inherent low-latency and power consumption almost independent of communication distance, which are key features to improve the performance in future Networks on Chip generations. Nevertheless, since nanophotonics technology is still growing and therefore it is still immature, current detailed system simulators lack to provide complete and detailed models of photonic components. Consequently, in case that such optical models are assumed, the obtained results may introduce important

deviations. This dissertation summarizes all the components that conform a fully operative optical NoC and presents their current state-of-the-art. Additionally, realistic ring-based ONoCs featuring token arbitration techniques are evaluated and compared against their electrical counterparts.

- Increasing energy efficiency in low-power CMPs. Conventional cache hierarchy approaches of current multicores incur area and energy wasting due to several well-known design issues: oversizing the private cache space, replicating data through the inclusive cache levels and the increasing cache associative degree. In spite of these shortcomings, the multi-level hierarchy is the commonly adopted design approach. In this dissertation we claim that a more energy efficient organization is needed to address these design issues. To this end, this thesis proposes Flat On-Chip Storage (FOS), a novel cache organization aimed at addressing energy and area of low-power processors by facing these design issues. FOS combines L2 and L3 cache levels into a single and flattened cache level composed of a pool of private small cache buffers. These buffers are initially powered off to save energy, and buffers are powered on and assigned to cores when the system performance is expected to improve. To provide fast and uniform access from the private L1 caches to the FOS cache buffers, multiple architectural challenges are overcome, including the design of a custom optical network-on-chip.

- Increasing energy efficiency in low-power CMPs for multithreaded applications. The aforementioned drawbacks associated to conventional cache organizations are especially harmful when running parallel applications. This kind of applications typically employs multiple threads accessing to shared data, and efficiently managing these data in the cache hierarchy is key to achieve high performance. This dissertation extends the baseline FOS architecture to propose FOS-Mt, a cache organization aimed at addressing energy savings in current multicores for multithreaded applications.

#### 1.3 Thesis Outline

This dissertation consists of seven chapters. The remaining chapters are organized as follows:

- Chapter 2 discusses previous work on both photonics interconnects and cache organizations.

- Chapter 3 presents the experimental platforms and common aspects of the evaluation methodology.

- Chapter 4 introduces the accurate modeling of optical devices, and the integration of these models in a state-of-the-art CMP simulation framework.

- Chapter 5 proposes Flat On-chip Storage, an efficient cache organization that reduces energy consumption in CMPs.

- Chapter 6 extends previous Flat On-Chip Storage approach and optimizes the proposal for multithreaded applications.

- Chapter 7 summarizes this thesis, discusses future work and enumerates related publications.

# Chapter 2

# Related Work

This chapter discusses previous work related to this dissertation, summarizing important state-of-the-art works which paved the way for the approaches proposed in this thesis. First, it is introduced the related work regarding optical interconnects, covering both the latest technological advances and recent optical networks on-chip. Next, we discuss important work dealing with cache sharing and cache partitioning, focusing our efforts on energy efficient caches. Finally, we also discuss related work that addresses energy savings at the cache hierarchy.

## 2.1 Optical Interconnects

This section discusses the state-of-the-art work focusing on optical devices and optical networks on-chip. First, we summarize some representative works dealing with technological advances in Photonic Integrated Circuits, focusing on the integration of on-chip lasers and improving microrings efficiency. Next, we discuss important proposals regarding optical networks on-chip in CMPs, which have guided us towards the design of the networks proposed in this dissertation.

#### 2.1.1 Optical Devices

Current research efforts focusing on Photonic Integrated Circuits (PICs) concentrate on the realization of reliable hybrid silicon lasers, electro-optical modulators, and detectors, which are the most critical building blocks of optical circuits. The promising research results pave the way for achieving fully on-chip integrated devices, able to overcome the inherent limitations of electronic networks [12].

Laser sources are the most difficult devices to be integrated in the on-chip processor die due to power, area, and optical signal attenuation constraints. Duan et al. have developed hybrid silicon/III-V lasers [13, 14] exhibiting new features and lower power consumption than previous works [15, 16]. However, these advances do not yet achieve the ultra-low power consumption required for on-chip laser integration. Moreover, integrated lasers are only able to provide output signal powers of tens of mW, raising attenuation concerns, although it is expected to accomplish higher figures in the next few years, hence allowing the exploitation of the real potential of on-chip lasers. In fact, some works on optical NoCs assume that on-chip lasers will be integrated in future technologies since they are much more energy-efficient [17].

Also, regarding lasers, other approaches apart from those deriving from technological improvements are possible. In this regard, Joshi et al. [18] propose a multibus network architecture to dynamically distribute the laser power across multiple buses and even turn the laser sources off at run-time, hence reducing the overall energy consumption. Following a similar approach, in [19] authors propose Ecolaser, an adaptive control mechanism that turns the laser off and saves up to 77% of the laser power. In addition,

other works like [20–23] target the heating problem of current designs and propose thermal management solutions, which is a key design issue to deal with the energy efficiency requirements of existing and future approaches.

The switching capacity (i.e. data routing) of electro-optical modulators represents the key feature for establishing the operation bandwidth of any PIC. High-bandwidth modulation in silicon (achieving up to 30 to 50 Gb/s data rates and working at switching times of several GHz [24–26]) can be realized by free-carrier induced index change and using biased pn structures (carrier depletion) [27, 28].

Optical coherent receivers (i.e. detectors), which convert the amplitude, phase, and polarization of an optical field signal into the electrical domain, have already been integrated showing similar performance to those deployed in commercial devices with very high data conversion. Polarization-division-multiplexed quadrature phase-shift keying (PDM-QPSK) has been employed for 100-Gb/s networks, and even higher modulation formats such as 16-ary quadrature amplitude modulation (16-QAM) can be utilized . These modulation formats can achieve a performance in commercial devices up to  $224 \ Gb/s$  with PDM-16-QAM signals [29]. Depending on the technology node, the output signal of these devices may need to be amplified before being used in the digital circuit. Small input capacitances for transistors would allow obtaining a signal that would not require any amplifier and therefore would reduce the power consumption [30].

Regarding current research on other PIC components, critical issues are to minimize light signal attenuation in the manufacturing process of waveguides [31] and to reduce the width of the light spectrum that resonators can filter. The latter characteristic defines the number of wavelengths achievable by Dense Wavelength Division Multiplexing (DWDM), which currently ranges from 64 to 160 wavelengths per waveguide.

#### 2.1.2 Optical Networks On-Chip

Based on the aforementioned technological advances regarding the integration of fully optical components, many works have been proposed focusing on optical networks onchip [30, 32–43]. Next we discuss state-of-the-art research on hybrid photonic-electronic and pure optical NoC implementations. In this regard, Vantrease et al. explore bandwidth requirements of future manycores and propose Corona [32], which is a 3D-stacked architecture that employs silicon photonics for both on-chip and off-chip communication. Kurian et al. present ATAC [30], a 1K-core system that leverages optical interconnects to implement a global broadcast network designed together with minor modifications in the coherence protocol. LumiNOC [34] follows a more conservative approach and implements a fully-optical network which is partitioned into subnets for the sake of efficiency.

Although fully-optical solutions are theoretically possible, their static power is considered still too high and prevents them to be adopted in the near future. It could be said that most of the ONoCs that can be found in existing works are hybrid, in the sense that they put together electrical and optical components. For instance, in [39], authors propose a hybrid network composed of optical links and a circuit-switched electrical mesh, aimed at improving broadcast operations in current and future manycores. In [33], authors propose Firefly, a hybrid network that performs node clustering and communicates these clusters using optical interconnects. METEOR [42] is also a hybrid network composed of an optical ring and a conventional 2D electrical mesh network, which authors claim to improve efficiency with respect to previous works like [32, 33]. In [35], authors also target efficiency by globally sharing several optical channels across the network. The scalability issues attached to optical crossbars are further studied in [40], where authors propose PROPEL, a hybrid network that implements a scalable optical crossbar and electrical switching for a 256-core CMP.

Following a different approach, in [37] Joshi et al. explore silicon-photonics clos networks (PClos), reducing energy consumption with respect to fully-optical global crossbars. In [38], authors adopt the previous approach and propose a bufferless implementation of PClos that improves scheduling and routing for this kind of networks.

Research on photonic NoCs is closely related to research on DWDM arbitration techniques. Since most DWDM-based communication schemes require wavelength sharing, some works consider the arbitration as an important part of the communication efficiency [32, 35]. In this context, Vantrease et al. [44] also take advantage from silicon photonics to perform arbitration related tasks. They identify latency, average network utilization and fairness as the key features that a suitable arbitration mechanism must address.

Other studies also point out that the cost of photonic resources must be taken into account. In [45], García Guirado et al. analyze the overhead of photonic components employed in some NoC proposals. They note that a responsible management and distribution of these resources can result in significant performance gains while keeping optical-related costs in acceptable levels.

Notice that most of the aforementioned works like [32–35] aim to improve network performance (by increasing network bandwidth) while also reducing energy consumption. Other works do not concentrate on improving the optical networks, but they take advantage of the capabilities that these networks can bring to overcome traditional limitations of current CMPs. In this context, some works like [36, 46, 47] leverage optical interconnects to enhance particular aspects of the architecture. In [46], Bartolini and Grani enhance a traditional NoC with an optical ring to support low-latency coherence control messages, making use of the optical technology capabilities to implement multicast transmissions. In [36], Cianchetti et al. employ an optical crossbar to reduce the number of hops for distant communications when transmitting 64-byte cache lines, which translates into a shorter memory access time. Similarly, in [47], a hybrid NoC that employs optical links for long-distance block transmissions while keeping electrical links for close communications is proposed.

Finally, other works explore the use of silicon photonics in other architectures different than CMPs. For instance, in [48], authors leverage optical interconnects to improve the scalability issues inherent to future GPUs, as the number of compute units grows in each GPU generation. Authors use a hybrid photonic crossbar to improve latency and energy efficiency of communications at the memory hierarchy of an AMD Southern Islands GPU.

# 2.2 Adaptive Cache Organizations

Cache organizations have been an important research topic when dealing with performance and energy consumption in chip multiprocessors. More specifically, important works [49–52] showed in the past that static and rigid cache hierarchies are inefficient and that applications may suffer from well known issues like unfairness or starvation in such systems. On the other hand, some seminal work [53–55] pointed out that splitting

the cache organization in small and independent cache structures do not only reduce energy consumption but also, when these structures are properly managed, may also enhance the system performance.

In this context, research approaches aimed at improving the utilization and efficiency of the cache hierarchy can be classified following different criteria. This section first presents a subset of previous *cache sharing* and *cache partitioning* approaches, which are typically applied to shared caches. Next, we discuss some important works that propose *cooperative caching* approaches as a way to improve the efficiency of the cache hierarchy. Finally, other approaches are studied in Section 2.2.3.

#### 2.2.1 Cache Partitioning

This category includes works that pursue to improve the use of the shared cache space by partitioning it according to different criteria. Approaches falling in this category [49–51, 56–58] aim to improve the system performance by properly assigning specific cache ways to the different applications running in the processor cores. An example of cacheway based partitioning can be found in [49], where a CMP prototype using this technique at the last level cache is presented. Another interesting piece of research belonging to this group is UCP [50] by Qureshi and Patt. This approach distributes the cache ways of the LLC among the co-running applications based on the reduction of cache misses that each one of them is likely to obtain for a given amount of cache resources. The estimates on the reduction of misses are carried out by duplicating tags and sampling a reduced amount of sets. ASM-Cache [56] employs similar techniques to gather useful information to partition the cache. In [51], authors propose distributing the cache ways with the aim of improving system fairness rather than just focusing on performance.

Other works [59–61] that also explore cache partitioning at the cache-way granularity focus on the cache replacement algorithm. Both [59, 60] propose using eviction probabilities to manage the occupation of the LLC, for instance, increasing the probability of evicting cache lines occupied by a given core. In [61], authors also partition the cache but control the size of partitions by properly scaling the futility of their cache lines.

A different approach considered to devise cache partitioning solutions is based on *skew* associative caches [62] or zcaches [63]. These approaches [64, 65] decouple the cache

associativity from the number of cache ways by increasing the replacement candidates upon a cache miss, hence they enable to partition the cache using the replacement policy. In [64], up to 90% of the cache is partitioned this way, by soft-pinning a large portion of the cache lines. In [65], authors dynamically partition the cache based on the predicted transient behavior of latency-critical workloads, maintaining their tail latency and ensuring QoS.

The aforementioned works focus on approaches that propose hardware modifications to current designs. However, software-based approaches [66–70] have been also proposed to partition the cache. Most of these approaches are based on page coloring, which is used to control the location of the application data in the cache. In [66], authors adopt a hybrid software and hardware approach, which aims to reduce the cache misses by: i) color mapping at compile time code and data pages; and ii) adding a page remap field to the TLB. A simple and software-only approach is followed in [67], which relies on the OS to allocate the physical page that maps the desired portion of a L2 shared cache. COLORIS [68] analyzes the case of page coloring in over-committed processors (i.e. where there are more executable threads than cores) and propose several policies to reconfigure the assignment of page colors among application threads. Lastly, in [69] authors refine the approach and propose hot-page coloring, which colors only a small set of frequently accessed pages for each process. The reason behind this approach is reducing the adverse effect associated to the lack of versatility of page coloring approaches, which need to reallocate the pages when repartitioning occurs.

Finally, more recent works [71–75] leverage Intel's Cache Allocation Technology, implemented in some current processors (e.g. Intel Xeon E5 v4 family), in order to limit the amount of LLC ways that a hardware thread can occupy. Some of these works [73–75] focus on the cloud field, and employ Intel CAT to maximize the utilization of large-scale data centers and to partition the cache when renting virtual machines. In [73], authors propose Heracles, a feedback-based framework that increases the utilization in large data centers while ensuring that latency-sensitive jobs meet their latency targets. In Dirigent [74], a lightweight performance management runtime system is proposed to accurately control the QoS of latency-critical applications using existing architectural solutions like Dynamic Voltage and Frequency Scaling (DVFS) or the already mentioned

Intel's CAT. In [71], Vicent Selfa et al. propose a family of clustering-based cache partitioning policies to address fairness in systems that feature Intel's CAT. Finally, in [72], Lucía Pons et al. propose a simple and effective approach based on identifying critical and non-critical applications that considerably improve the workloads' turnaround times by featuring Intel's CAT.

## 2.2.2 Cooperative Caching

The proposals presented above mostly apply to shared caches, but some works concentrate their effort on CMPs implementing private caches, or caches that count with both private and shared levels. In this category, cooperative caching approaches [76–78] allow applications with high cache demands to borrow part of the private cache from other (i.e. neighbor) cores. In [76], Chang et al. propose a centralized directory that manages the private L2 caches in a four-core system, allowing cache-hungry applications to borrow cache ways from neighbor cores. This directory is also in charge of keeping coherence and several counters that indicate the reuse of blocks.

The scalability issues observed in the aforementioned solution are addressed in [77], where a distributed implementation of the centralized directory is proposed. This proposal introduces several improvements to the centralized version: the tag management is optimized, reducing the time needed to look up a given block; size and bottlenecks are also reduced, since distributed directories store the tags in an interleaved manner. However, these improvements require extending the underlying coherence protocol, which entails significant hardware modifications.

Finally, the cooperative-caching approach is further refined in [78]. In this proposal, aimed at working both with private and shared caches, authors propose a hardware solution that dynamically adjusts the cache space available for a given core based on the behavior of the running application. The approach overcomes the strict private/shared categories applied to the cache levels and dynamically adjusts the *private size* on each cache module, leaving the remaining cache ways to be occupied by shared blocks belonging to other executing threads.

Cooperative caching solutions are an interesting approach to address the different cache requirements that the co-running applications can present. However, the performance of

these approaches is limited by the interconnection network, which can increase latency when borrowing cache space from distant cores. Therefore, proposals falling in this category highly restrict the maximum cache space that is available for a single core. This fact limits the potential performance gains, especially in processors with a significant amount of cores.

#### 2.2.3 Other Approaches

This section discusses other approaches that have been proposed dealing with existing cache hierarchies, and some works that combine and improve previous approaches. In this regard, we first focus on approaches targeting Non Uniform Cache Access (NUCA) architectures and on schemes that redefine the complete cache hierarchy.

With the aim of reducing the latency and energy consumption of large caches, some works explored in the past solutions focused on NUCA architectures [79–86]. Conventional NUCA architectures organize the cache space as a set of interconnected banks (i.e. modules), which are typically accessed in an interleaved manner. This *statically* interleaved access to the cache banks brings well-known shortcomings associated to rigid cache hierarchies like multiple tag look-ups, excessive data movement and thrashing.

An interesting piece of research that aims to deal with these issues is NUCA-Substrate [83]. In this work, authors propose a dynamic mapping that keeps the most used blocks in banks close to the running application and the least used blocks are kept farther away, hence improving the average access latency. In NUCA-Substrate, a cache hungry application may occupy a high number of NUCA banks, which are located close to the tile executing the application, while applications that barely performs cache accesses are left with a reduced cache space.