# Desarrollo de un Sistema para la caracterización de la transmisión OOK-NRZ a través de LEDs de iluminación

Autor: Adrián Luis Arándiga Martínez

**Tutor: Javier Valls Coquillat y Vicente Torres Carot**

Trabajo Fin de Máster presentado en el Departamento de Ingeniería Electrónica de la Universitat Politècnica de València para la obtención del Título de Máster Universitario en Ingeniería de Sistemas Electrónicos

Curso 2020-21

Valencia, julio de 2021

#### Resumen

En este trabajo se realiza el diseño e implementación en FPGA de un sistema que permite evaluar una transmisión a través de LEDs de iluminación mediante el uso de la modulación OOK-NRZ. El sistema permitirá operar con diferentes frecuencias de transmisión y capturar la señal con diferentes fases. Se realizará una calibración para seleccionar la fase óptima y, capturando la señal en esa fase, se medirá la tasa de error de bit de la transmisión. Se implementará un interfaz para controlar el sistema desde un ordenador mediante instrucciones en Matlab. Finalmente, se montará un prototipo y se realizarán medidas para caracterizar el sistema.

#### Resum

En aquest treball, es realitza el disseny i l'implementació en FPGA d'un sistema que permet avaluar una transmissió a través de LED's d'il·luminació per mitjà de l'ús de la modulació OOK-NRZ. El sistema permetrà operar amb diferents freqüències de transmissió i capturar el senyal amb diferents fases. Es realitzarà una calibració per a seleccionar la fase òptima i, capturant el senyal en eixa fase, es mesurarà la taxa d'error de bit de la transmissió. S'implementarà un interfície per a controlar el sistema des d'un ordinador per mitjà d'instruccions en Matlab. Finalment, es muntarà un prototip i es realitzaran mesures per a caracteritzar el sistema.

#### **Abstract**

The main goal of this work is the design and implementation on an FPGA device of a system that evaluates a transmission through illumination LEDs using the OOK-NRZ modulation. The system will be able to operate with different transmission frequencies and capture the signal with different phases. The optimal phase will be decided with a calibration stage. That phase will be used to capture the signal to measure the bit error rate of the transmission. An interface to control the system from a computer through Matlab instructions will be implemented as well. Finally, the prototype will be mounted and tested.

# Índice

| Capítulo | o 1.    | Introducción                                        | 6  |

|----------|---------|-----------------------------------------------------|----|

| 1.1      | Intro   | oducción                                            | 6  |

| 1.2      | Mod     | lulación OOK-NRZ en la comunicación con luz visible | 6  |

| 1.3      | Obje    | etivos                                              | 8  |

| 1.4      | Hen     | ramientas y metodología                             | 8  |

| 1.4      | .1      | Placa de desarrollo                                 | 8  |

| 1.4      | 2       | Matlab                                              | 8  |

| 1.4      | 3       | Quartus Prime                                       | 9  |

| 1.4      | .4      | ModelSim                                            | 9  |

| 1.4      | 5       | Platform Designer                                   | 9  |

| 1.4      | 6       | SignalTap Logic Analyzer                            | 9  |

| 1.4      | 7       | Visual Studio                                       | 9  |

| 1.4      | .8      | Metodología de trabajo                              | 9  |

| 1.5      | Estr    | uctura de la memoria                                | 11 |

| Capítulo | 2.      | Diseño del sistema                                  | 12 |

| 2.1      | Fun     | cionamiento del sistema                             | 12 |

| 2.1      | .1      | Etapa de calibración                                | 12 |

| 2.1      | .2      | Etapa de cálculo del BER                            | 16 |

| 2.2      | Espe    | ecificaciones técnicas                              | 18 |

| 2.3      | Imp     | lementación hardware                                | 19 |

| 2.3      | .1      | Calibración                                         | 21 |

| 2        | 2.3.1.1 | Correlador                                          | 22 |

| 2        | 2.3.1.2 | Detector de picos de correlación                    | 27 |

| 2        | 2.3.1.3 | Almacenamiento en RAM                               | 29 |

| 2        | 2.3.1.4 | Selección de fase                                   | 32 |

| 2        | 2.3.1.5 | Control                                             | 35 |

| 2        | 2.3.1.6 | Verificación del bloque de calibración              | 38 |

| 2.3      | .2      | Cálculo del BER                                     | 42 |

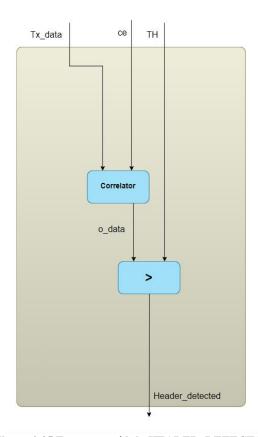

| 2        | 2.3.2.1 | Detección de preámbulo                              | 43 |

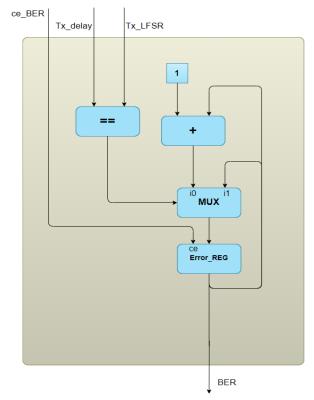

| 2        | 2.3.2.2 | Contador de errores                                 | 45 |

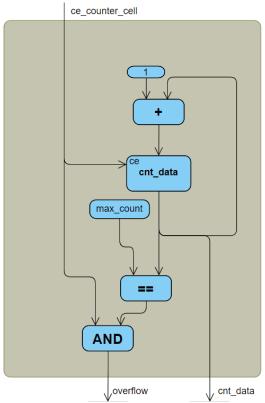

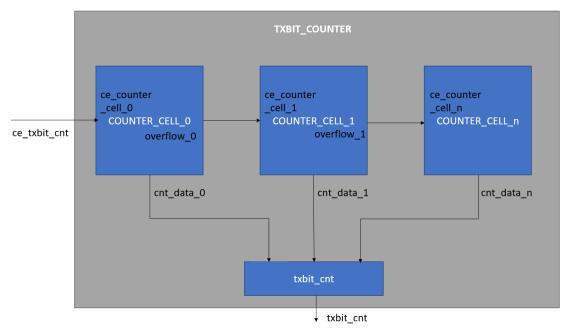

| 2        | 2.3.2.3 | Contador de muestras                                | 47 |

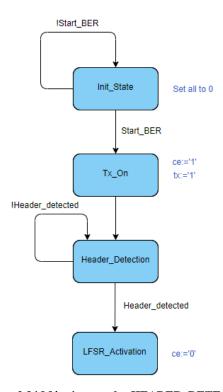

| 2        | 2.3.2.4 | Control                                             | 49 |

| 2        | 2.3.2.5 | Generación de transmisión de referencia             | 51 |

| 2        | 2.3.2.6 | Verificación del bloque del BER                     | 53 |

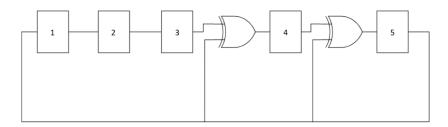

| 2.3      | .3      | Transmisor                                          | 55 |

| 2        | 2.3.3.1 | Modo Calibración                                    | 56 |

| 2.3        | 3.3.2 Modo cálculo del BER5                                                                                                      | 58 |

|------------|----------------------------------------------------------------------------------------------------------------------------------|----|

| 2.3.4      | Incremento de fase                                                                                                               | 50 |

| 2.3        | .4.1 PLL6                                                                                                                        | 52 |

| 2.3        | .4.2 Control de incremento de pasos del PLL                                                                                      | 53 |

| 2.3.5      | Captura y procesado de la señal de entrada                                                                                       | 55 |

| 2.3.6      | Control del sistema6                                                                                                             | 56 |

| 2.3.7      | Test RTL sistema completo6                                                                                                       | 58 |

| Capítulo 3 | . Interfaz con Matlab6                                                                                                           | 59 |

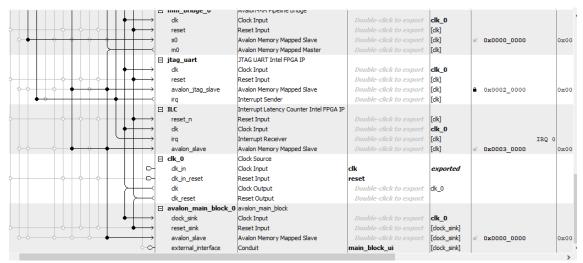

| 3.1        | Creación del componente avalon_main_block6                                                                                       | 59 |

| 3.2        | Sistema en Platform Designer                                                                                                     | 71 |

| 3.3        | Comunicación entre Matlab y el Microprocesador                                                                                   | 12 |

| Capítulo 4 | . Testeo del prototipo                                                                                                           | 74 |

| 4.1        | Pruebas con SignalTap                                                                                                            | 74 |

| 4.2        | Pruebas en laboratorio                                                                                                           | 79 |

| Capítulo 5 | . Conclusiones                                                                                                                   | 37 |

| Capítulo 6 | . Actividades a desarrollar en el futuro                                                                                         | 38 |

| Capítulo 7 | . Referencias                                                                                                                    | 39 |

|            | le figuras  VLC en un entorno de oficina. Fuente [3]                                                                             | 6  |

|            |                                                                                                                                  |    |

|            | Estructura de sistema VLC basado en (IM/DD).                                                                                     |    |

|            | Señal recibida a 2.5 Mb/s.                                                                                                       |    |

| -          | Periféricos DE10-Standard. Fuente [5].                                                                                           |    |

| _          | Estructura modular del sistema.                                                                                                  |    |

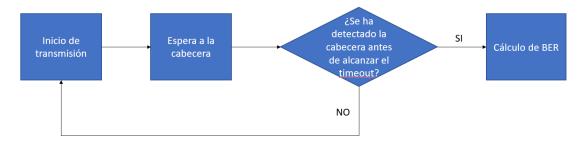

| •          | Diagrama de flujo del sistema.                                                                                                   |    |

| U          | Diagrama de bloques fase de calibración                                                                                          |    |

| -          | Señal de calibración. Arriba directa del LFSR. Medio Filtrada. Abajo añadiendo                                                   |    |

| _          | Curvas de correlación obtenidas en Matlab para 8 fases y secuencia de 15 bits (n en cada fase. (b) Media de correlación por fase |    |

| •          | Correlación en función del ruido. (a) SNR_dB=4. (b) SNR_dB=8. (c) SNR_dB=1 B=16 1                                                |    |

| Figura 2.6 | Curvas de correlación en función del filtro. Derecha wn = $1/2$ . Izquierda wn = $1/8$ . 1                                       | 15 |

| Figura 2.7 | Correlación para 6 fases (Izqda.) y 32 (Dcha.) coeff 50, wn 1/2, snr 10                                                          | 15 |

| Figura 2.8 | Curva correlación con un retardo de 10 muestras                                                                                  | 16 |

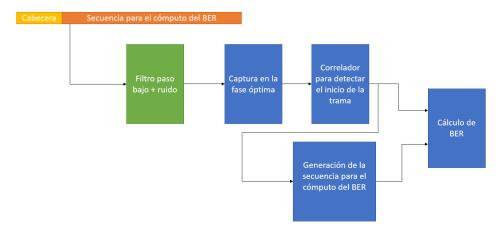

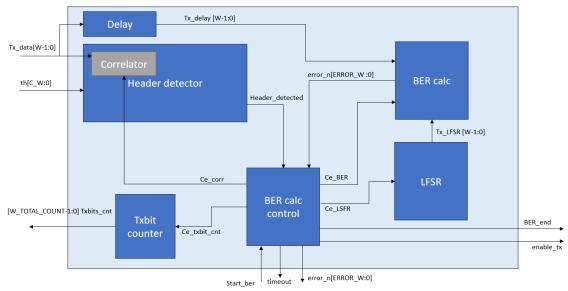

| Figura 2.9 | Diagrama de bloques cálculo del BER.                                                                                             | 16 |

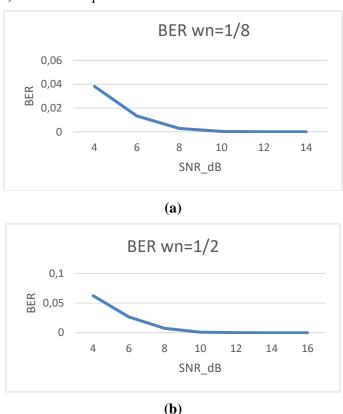

| Figura 2.10 BER en función del ruido. (a) wn=1/8. (b) wn=1/2                                                                                                                     | 17             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

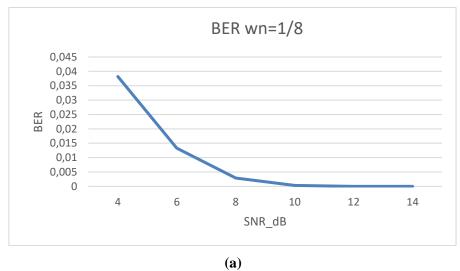

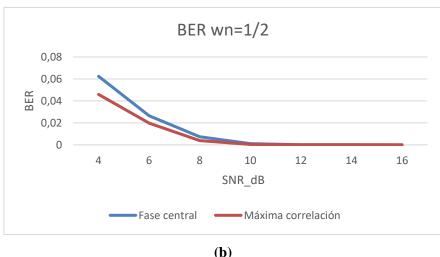

| Figura 2.11 Cálculo del BER comparando la fase central con la de máxima con distintos filtros. (a) $wn=1/8$ . (b) $wn=1/2$ .                                                     |                |

| Figura 2.12 Conexiones entre los bloques que componen el sistema. Naranja: reloj Azul: Reloj estático. Verde: Reloj dinámico                                                     |                |

| Figura 2.13 Interfaz del sistema.                                                                                                                                                | 20             |

| Figura 2.14 Diagrama de flujo proceso de calibración.                                                                                                                            | 21             |

| Figura 2.15 Esquema conexiones bloque CALIBRATION_BLOCK                                                                                                                          | 21             |

| Figura 2.16 Visualización de la operación de convolución [8]                                                                                                                     | 23             |

| Figura 2.17 Arquitectura correlador.                                                                                                                                             | 23             |

| Figura 2.18 Izqda. celda coeficiente 1, Dcha. celda coeficiente -1                                                                                                               | 24             |

| Figura 2.19 Correlador con secuencia de calibración 1, -1, 1, -1                                                                                                                 | 24             |

| Figura 2.20 Correlador segmentado.                                                                                                                                               | 24             |

| Figura 2.21 Celdas del correlador. (a) Coeficiente -1. (b) Coeficiente 1                                                                                                         | 26             |

| Figura 2.22 Síntesis de ambos tipos de celda del correlador                                                                                                                      | 26             |

| Figura 2.23 Máquina estados PEAK_DETECTOR.                                                                                                                                       | 28             |

| Figura 2.24 Esquema módulo PEAK_DETECTOR.                                                                                                                                        | 28             |

| Figura 2.25 Curvas de correlación con 8 fases. Superior: curva de correlación, infecorrelación desfasada.                                                                        |                |

| Figura 2.26 Máquina de estados PHASE_RAM.                                                                                                                                        | 30             |

| Figura 2.27 Esquema PHASE_RAM.                                                                                                                                                   | 31             |

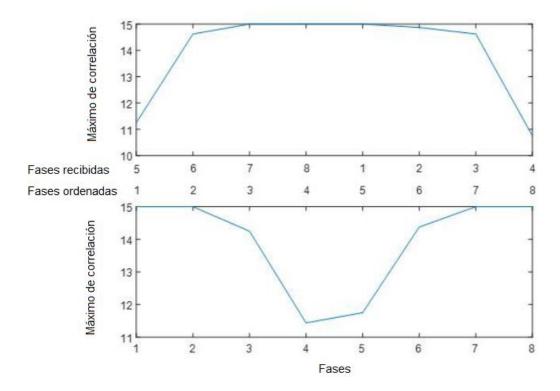

| Figura 2.28 superior: curva de correlación ordenada. (fases recibidas: numeradas seguente del transmisor, fases ordenadas, según el módulo PHASE_RAM); inferior: curva orecibida | de correlación |

| Figura 2.29 Máquina de estados PHASE_SELECTOR                                                                                                                                    |                |

| Figura 2.30 Esquema PHASE_SELECTOR.                                                                                                                                              |                |

| Figura 2.31 Diagrama de flujo del control.                                                                                                                                       | 36             |

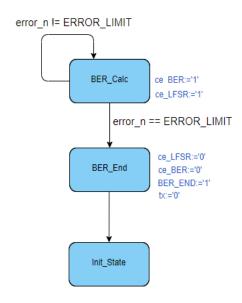

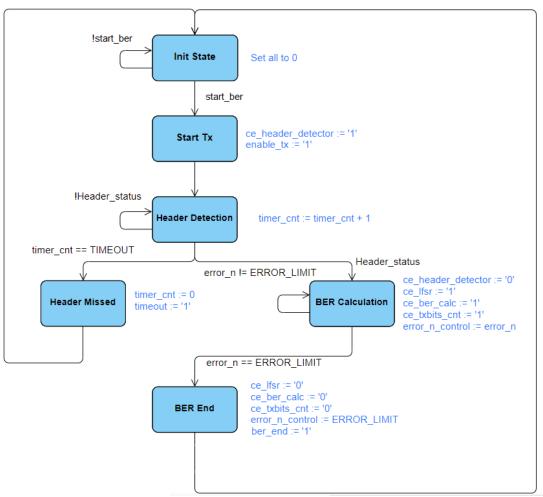

| Figura 2.32 Diagrama de flujo proceso cálculo del BER                                                                                                                            | 42             |

| Figura 2.33 Esquema conexiones bloque BER_BLOCK                                                                                                                                  |                |

| Figura 2.34 Máquina estados HEADER_DETECTOR.                                                                                                                                     | 44             |

| Figura 2.35 Esquema módulo HEADER_DETECTOR                                                                                                                                       |                |

| Figura 2.36 Máquina estados BER_CALC.                                                                                                                                            |                |

| Figura 2.37 Esquema módulo BER_CALC.                                                                                                                                             | 46             |

| Figura 2.38 Esquema módulo COUNTER_CELL.                                                                                                                                         | 47             |

| Figura 2.39 Esquema TXBIT_COUNTER para n contadores                                                                                                                              | 48             |

| Figura 2.40 Etapas del BER_CONTROL.                                                                                                                                              |                |

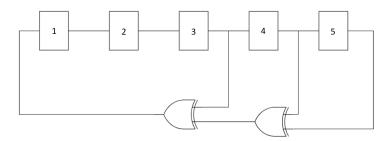

| Figura 2.41 Ejemplo LFSR [5,4,3] Fibonacci                                                                                                                                       |                |

| Figura 2.42 Ejemplo LFSR [5,4,3] Galois.                                                                                                                                         |                |

| Figura 2.43 Esquema del transmisor.                                                                                                                                              |                |

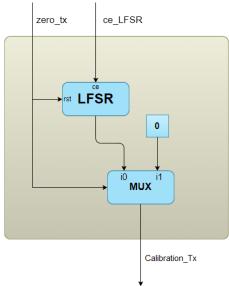

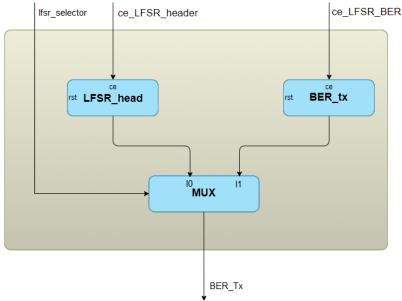

| Figura 2.44 Esquema módulo TRANSMISSION_CALIBRATION.                                                                                                                                                    | 57   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figura 2.45 Diagrama FSM TRANSMISSION_CALIBRATION_CONTROL.                                                                                                                                              | 57   |

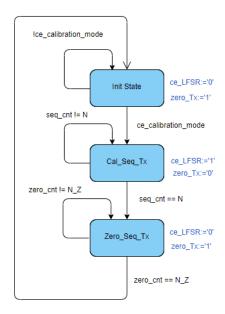

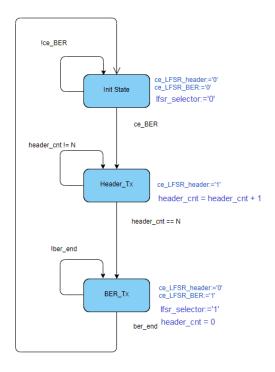

| Figura 2.46 Esquema módulo TX_BER                                                                                                                                                                       | . 59 |

| Figura 2.47 Máquina de estados TX_BER_CONTROL.                                                                                                                                                          | 60   |

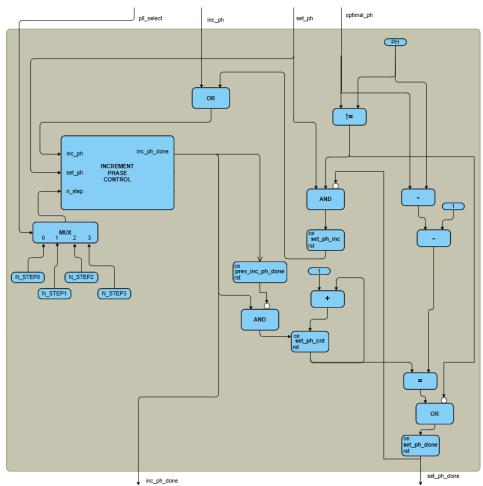

| Figura 2.48 Esquema bloque INCREMENT_PHASE.                                                                                                                                                             | 61   |

| Figura 2.49 Esquema de PLL.                                                                                                                                                                             | 63   |

| Figura 2.50 configuración señales PLL fase dinámica. Fuente [11].                                                                                                                                       | 63   |

| Figura 2.51 Máquina de estados INCREMENT_PHASE_CONTROL.                                                                                                                                                 | 64   |

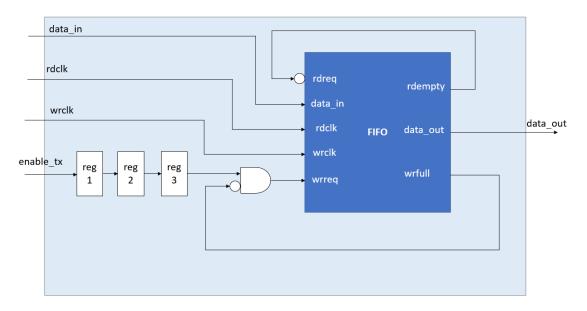

| Figura 2.52 Esquema DATA_FIFO.                                                                                                                                                                          | 65   |

| Figura 2.53 Etapas de MAIN_CONTROL.                                                                                                                                                                     | 67   |

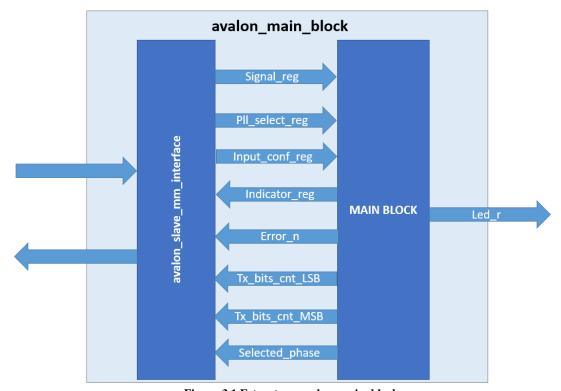

| Figura 3.1 Estructura avalon_main_block                                                                                                                                                                 | 70   |

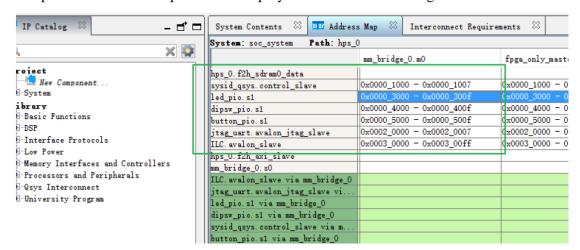

| Figura 3.2 Mapa de memoria de los periféricos del proyecto DE10_Standard_GHRD. Fuente [1                                                                                                                |      |

| Figura 3.3 Integración de avalon_main_block en el platform designer                                                                                                                                     | 72   |

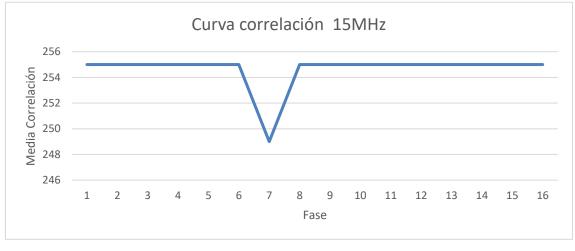

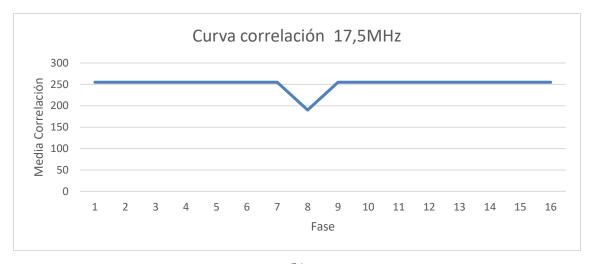

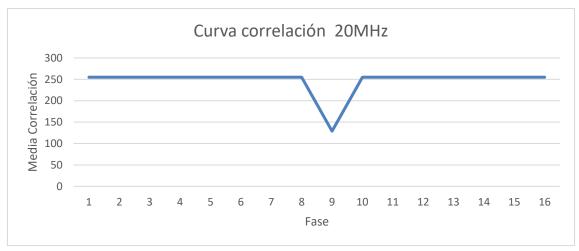

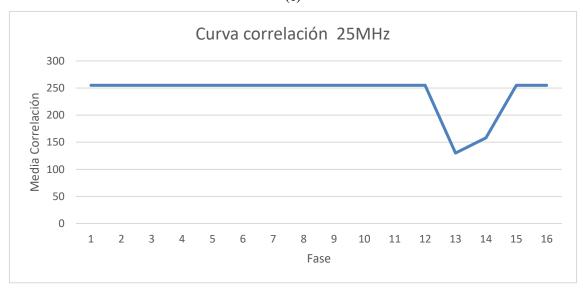

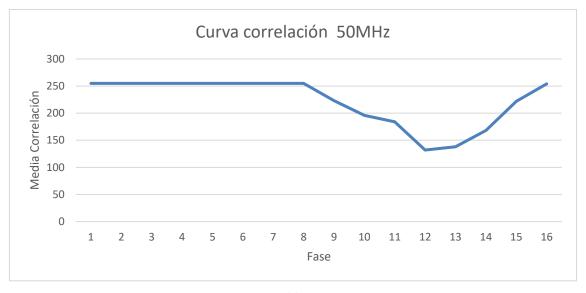

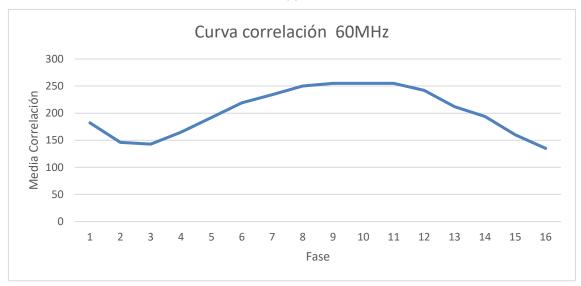

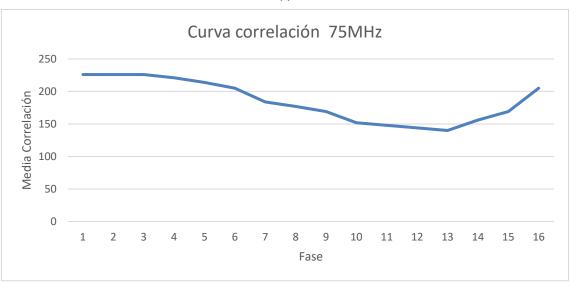

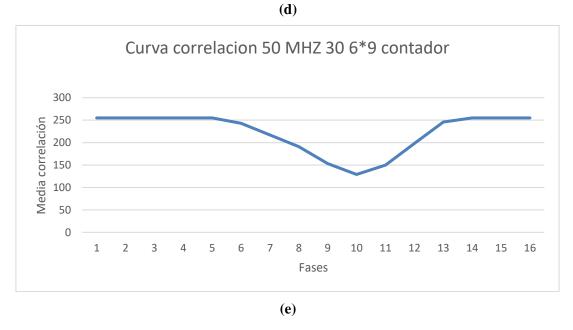

| Figura 4.1 Gráficas de correlación a distintas frecuencias. a 15 MB/s. b 17,5 MB/s. c 20 MB/s 25 MB/s. e 50 MB/s. f 60 MB/s. g 70 Mb/s.                                                                 |      |

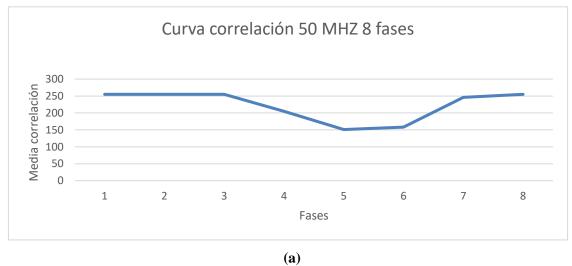

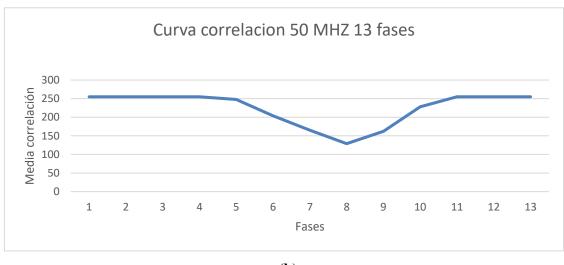

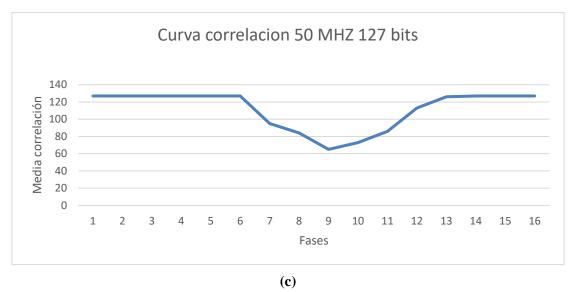

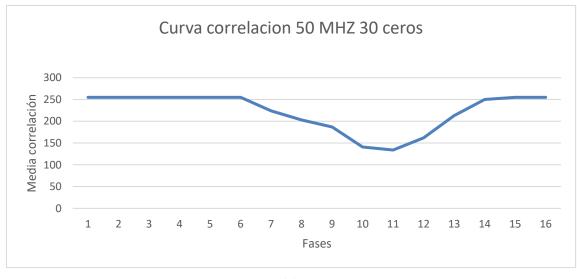

| Figura 4.2 Pruebas de calibración con distintos parámetros. a 8 fases. b 13 fases. c secuencia 127 bits. d 30 ceros tras la secuencia. e contador de muestras de 6*9                                    |      |

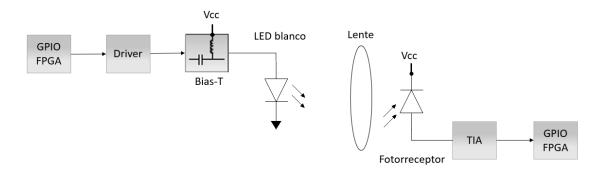

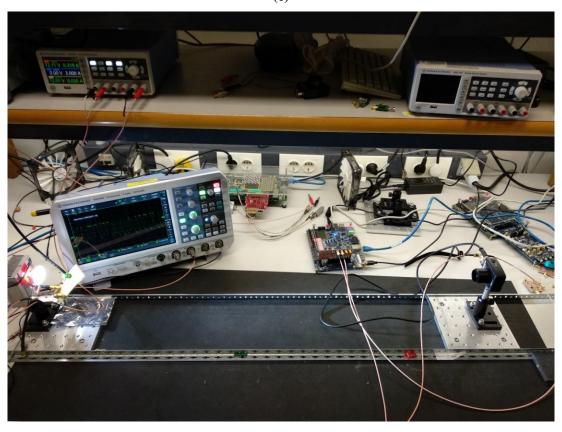

| Figura 4.3 Esquema de sistema de transmisión y recepción en el laboratorio.                                                                                                                             | .79  |

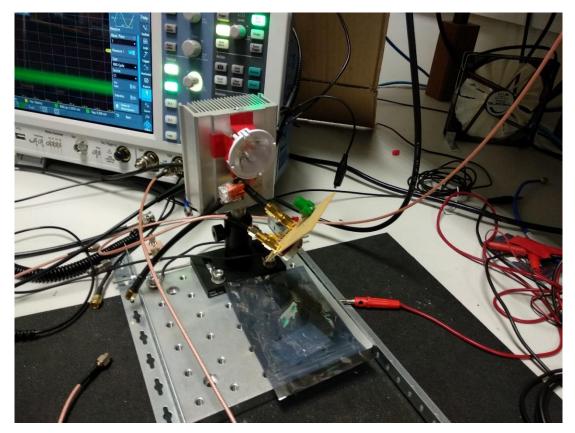

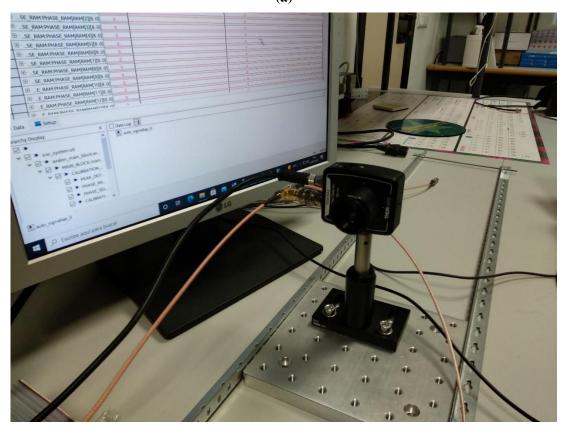

| Figura 4.4 Sistema de modulación de intensidad y detección directa montado en el laborato (a) LED. (b) Fotoreceptor. (c) Proptotipo montado en la placa de desarrollo DE-10 Standard. Sistema completo. | (d)  |

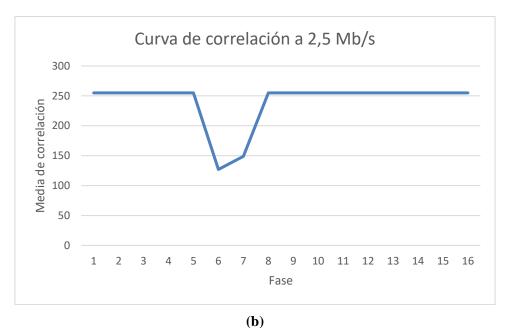

| Figura 4.5 Calibración a 2.5 Mb/s. (a) secuencia de calibración capturada en el osciloscopio. curva de correlación.                                                                                     |      |

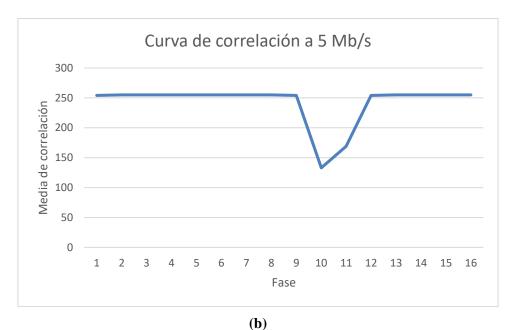

| Figura 4.6 Calibración a 5 Mb/s. (a) secuencia de calibración capturada en el osciloscopio. curva de correlación.                                                                                       |      |

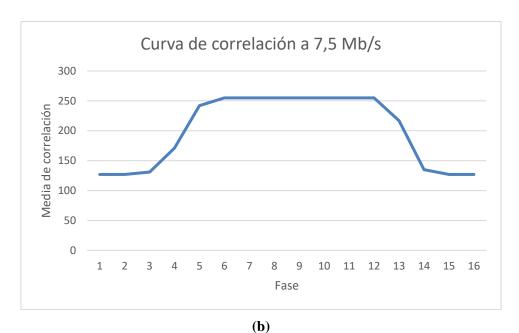

| Figura 4.7 Calibración a 7.5 Mb/s. (a) secuencia de calibración capturada en el osciloscopio. curva de correlación.                                                                                     |      |

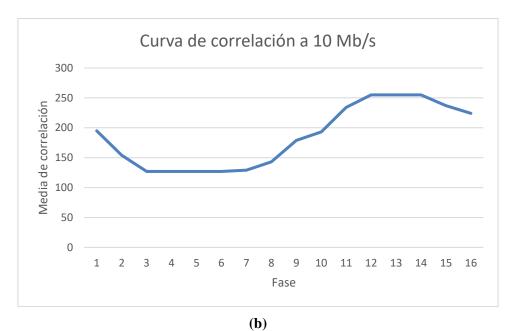

| Figura 4.8 Calibración a 10 Mb/s. (a) secuencia de calibración capturada en el osciloscopio. curva de correlación.                                                                                      |      |

|                                                                                                                                                                                                         |      |

| Índice de tablas                                                                                                                                                                                        |      |

| Tabla 2.1 Activación de señales en cada etapa de CALIBRATION_CONTROL                                                                                                                                    | 38   |

| Tabla 2.2 Test variando el retardo por transmisión.                                                                                                                                                     | 38   |

| Tabla 2.3 Test variando el número de fases.                                                                                                                                                             | 39   |

| Tabla 2.4 Test variando la secuencia de calibración.                                                                                                                                                    | 39   |

| Tabla 2.5 Test variando el número de secuencias transmitidas por fase.                                                                                                                                  | 40   |

| Tabla 2.6 Test variando el ruido                                                                                                                                                                        | 40   |

| Tabla 2.7 Test variando el número de muestras por secuencia de calibración                  | 41 |

|---------------------------------------------------------------------------------------------|----|

| Tabla 2.8 Diferentes casos de test.                                                         | 42 |

| Tabla 2.9 Frecuencia máxima del contador para diferentes configuraciones                    | 49 |

| Tabla 2.10 Activación de señales en cada etapa del BER_CONTROL                              | 51 |

| Tabla 2.11 Test variando el número de errores hasta detener el sistema y el orden del LFSR. | 53 |

| Tabla 2.12 Test variando la configuración de los contadores en cascada                      | 54 |

| Tabla 2.13 Test variando la cabecera.                                                       | 54 |

| Tabla 2.14 Test variando el ruido                                                           | 55 |

| Tabla 2.15 Activación de señales en cada etapa MAIN_CONTROL.                                | 68 |

| Tabla 3.1 Configuración registro signal_reg.                                                | 69 |

| Tabla 3.2 Configuración registro input_config_reg.                                          | 69 |

| Tabla 3.3 Configuración registro pll_select_reg.                                            | 70 |

| Tabla 3.4 Configuración registro indicator_reg.                                             | 70 |

| Tabla 3.5 Formato del mensaje para la comunicación entre Matlab y el periférico             | 72 |

# Listado de acrónimos

BER: Bit Error Rate. Tasa de error de bit.

**FIFO:** First In, First Out. Primero en entrar, primero en salir.

**FPGA:** Field-Programmable Gate Array. Matriz de puertas lógicas programables en campo.

HDL: Hardware Description Language. Lenguaje de descripción hardware.

**HPS:** Hard Processor System.

**IM/DD:** Intensity Modulation and Direct Detection. Modulación de intensidad y detección directa.

IP: Intellectual Property. Propiedad intellectual.

**IP:** Internet Protocol. Protocolo de internet.

**LED:** Light-Emitting Diode. Diodo emisor de luz.

LFSR: Linear Feedback Shift Register. Registro de desplazamiento con retroalimentación lineal.

**OOK-NRZ:** On-Off Keying Non-Return to Zero. Manipulación Encendido-Apagado sin retorno a cero.

**PC:** Personal Computer. Ordenado personal.

**PLL:** Phase-Locked Loop. Lazo de seguimiento de fase.

RAM: Random Access Memory. Memoria de acceso aleatorio.

RTL: Register Transfer Level. Transferencia a nivel de registro.

**SNR:** Signal-to-Noise Ratio. Relación señal ruido.

TCP: Transmission Control Protocol. Protocolo de control de transmisión.

**TFM:** Trabajo Fin de Master.

VLC: Visible Light Communication. Comunicación con luz visible.

# Capítulo 1. Introducción

#### 1.1 Introducción

En este proyecto, se pretende proporcionar una herramienta que permita testear comunicaciones con luz visible.

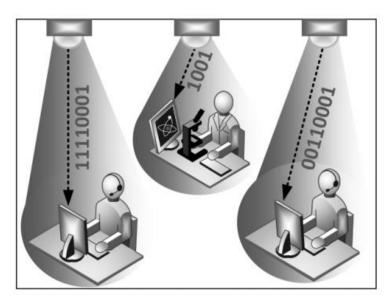

La comunicación con luz visible (VLC) utiliza LEDs como fuente de iluminación, y como transmisor de señal modulando los LEDs. Por lo que con VLC se combinan las funcionalidades de iluminación y comunicación [1].

La comunicación con luz visible ofrece ciertas ventajas sobre la comunicación por radio frecuencia. No tienen interferencia electromagnética al tratarse de comunicaciones con luz. Tienen bajo coste ya que reutilizan la infraestructura de iluminación, añadiéndole ciertos módulos. Son energéticamente eficientes ya que utilizan los LEDs como fuente de transmisión. Y proporcionan seguridad en la transmisión ya que la luz no penetra objetos opacos [2].

No obstante, también pueden mencionarse diversas desventajas. VLC únicamente funciona cuando la iluminación está activada. Sin una fuente de iluminación directa, la transferencia de datos se detiene. La luz natural puede afectar negativamente a la comunicación, pero reducir el aprovechamiento de la luz natural entra en conflicto con el aspecto del ahorro energético de la VLC. La aplicación en dispositivos portátiles o en exteriores todavía está en vías de investigación. Y el ancho de banda está limitado por los LEDs comerciales.

Algunas de las desventajas de la comunicación con luz visible podrían mitigarse combinando VLC con Wi-Fi. Las aplicaciones de la VLC donde se aprovechan sus puntos fuertes, son redes en el hogar, oficinas, clases y hoteles entre otras, donde el receptor podría estar en un punto fijo bajo la fuente de iluminación. En ambientes industriales pueden ser particularmente convenientes debido a su inmunidad electromagnética. De forma parecida, es posible utilizar VLC en zonas sensibles a interferencia electromagnética, como hospitales y cabinas de avión [3].

Figura 1.1 VLC en un entorno de oficina. Fuente [3].

#### 1.2 Modulación OOK-NRZ en la comunicación con luz visible

El sistema diseñado en este proyecto se utiliza para evaluar la transmisión a través de LEDs de iluminación mediante el uso de la modulación on-off keying non return to zero (OOK-NRZ). Consiste en una modulación de amplitud, donde se conmuta entre dos niveles de tensión la fuente de iluminación para transmitir un uno o un cero, y después de enviar un bit de información se envía inmediatamente el siguiente.

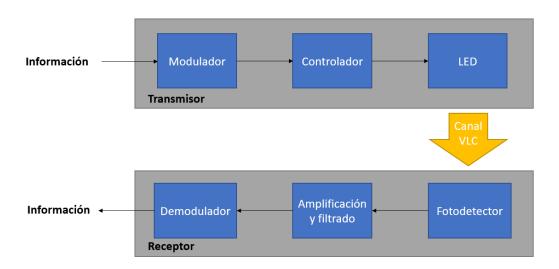

La transmisión y recepción de información se realiza por modulación de intensidad y detección directa (IM/DD). Para ello, un modulador transforma el flujo de bits a transmitir en una señal analógica. Al modulador le sigue un driver que amplifica la señal y alimenta la fuente de iluminación. Esta emite pulsos de luz que se transmiten a través del aire y son capturados por un fotodetector, que vuelve a transformar los pulsos de luz en señal eléctrica. Esta señal pasa por una etapa de amplificación y filtrado que se conecta a un demodulador para recuperar la señal transmitida. La señal por encima de una tensión determinada se considera un uno lógico, y por debajo un cero. En la Figura 1.2 se muestra la estructura de un sistema de VLC basado en modulación de intensidad y detección directa [4].

Figura 1.2 Estructura de sistema VLC basado en (IM/DD).

El medio de transmisión y el procesado de la señal introducen un retardo entre la señal transmitida y la recibida. Además, los pulsos recibidos se verán deformados en función de la frecuencia de transmisión. La recepción de los pulsos se puede observar en la Figura 1.3. Para asegurar una lectura de la señal correcta, cada pulso se captura en distintas fases. En una etapa de calibración se encuentra cual de esas fases es la que captura mejor la señal y se realiza la recepción de la señal en esa fase.

Figura 1.3 Señal recibida a 2.5 Mb/s.

# 1.3 Objetivos

El objetivo de este TFM es el de desarrollar con un dispositivo FPGA un sistema que permita transmitir una trama de datos modulados en OOK-NRZ, a través de un LED de iluminación, y que, al recibirlos mediante un fotodiodo, recupere la fase de transmisión, sincronice el inicio de la trama y realice una medida del bit error rate (BER). Se monta un prototipo y se realizan medidas para caracterizar la transmisión.

La lista de objetivos a cumplir es la siguiente:

- Desarrollo de un modelo del sistema en Matlab. Incluye el modelo del canal, la etapa de calibración para obtener la fase óptima y la etapa de medida del BER.

- Implementación del sistema en SystemVerilog. Este objetivo incluye el diseño de los módulos, su codificación en lenguaje de descripción hardware (HDL) y verificación.

- Desarrollar la etapa de comunicación del sistema con el PC.

- Montaje del prototipo y realización de pruebas.

# 1.4 Herramientas y metodología

#### 1.4.1 Placa de desarrollo

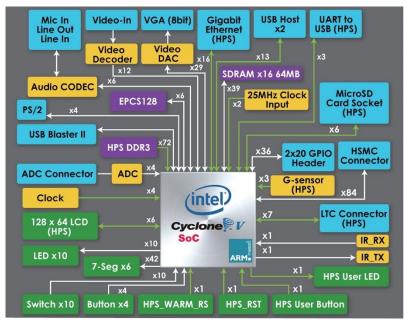

El prototipo se implementa en la placa de desarrollo DE10-Standard de Terasic [5] que integra una FPGA Cyclone V SX SoC – 5CSXFC6D6F3F31C6N. En la Figura 1.4 se muestran los periféricos que incluye la placa.

Figura 1.4 Periféricos DE10-Standard. Fuente [5].

Los que se utilizan en el prototipo son:

- Conexión Ethernet para la comunicación con el PC.

- LEDs como indicadores.

- Interruptores como señales de control.

- Pulsadores como señales de reset.

- GPIO Para la transmisión y recepción de señal.

#### 1.4.2 Matlab

Es una software de programación y cálculo numérico. Matlab permite realizar manipulación de matrices, representación gráfica de datos y la implementación de algoritmos entre otras funciones.

Se ha utilizado para modelar el sistema y estudiar el comportamiento del mismo para diferentes parámetros y niveles de ruido. Además, a partir de los modelos, se han generado los ficheros utilizados en la verificación de los módulos hardware y se ha creado el paquete con los parámetros de configuración del hardware. Finalmente, se ha utilizado como interfaz de usuario entre el PC y el sistema para el control y lectura de registros.

# 1.4.3 Quartus Prime

Software de diseño de dispositivos de lógica programable producido por Intel. Permite realizar el análisis y síntesis de diseños HDL. Se ha utilizado para la implementación del hardware en SystemVerilog.

#### 1.4.4 ModelSim

Software de simulación de HDL que permite realizar simulaciones a nivel de transferencia de registros (RTL) y a nivel de puertas lógicas. Se ha empleado para la verificación de todos los módulos hardware diseñados, tanto individualmente, como en conjunto al integrarlos en bloques.

# 1.4.5 Platform Designer

Herramienta de integración de sistemas que permite generar automáticamente lógica para conectar funciones de propiedad intelectual (IP) con subsistemas. Se ha utilizado para integrar el sistema en un componente que permite la comunicación de manera sencilla con el microprocesador de la placa de desarrollo.

# 1.4.6 SignalTap Logic Analyzer

Es una herramienta de depuración a nivel de sistema que permite monitorizar distintas señales y registros internos del diseño sintetizado en la FPGA. Se sintetiza junto al sistema a depurar y consume recursos lógicos de la FPGA. Se ha utilizado para la depuración del sistema completo implementado en la FPGA, visualizando la evolución de las señales y el valor de los registros.

#### 1.4.7 Visual Studio

Es un entorno de desarrollo integrado compatible con múltiples lenguajes de programación. Se ha utilizado para establecer la comunicación entre la placa de desarrollo y el PC.

#### 1.4.8 Metodología de trabajo

Primero se modela utilizando Matlab la calibración y el cálculo del BER. Este modelo permite que se entienda el funcionamiento del sistema y la realización de pruebas para ver como la modificación de diferentes parámetros de configuración afectan al mismo. Con la información obtenida, se decide el criterio para considerar una fase válida y cómo elegir la fase óptima de entre las válidas.

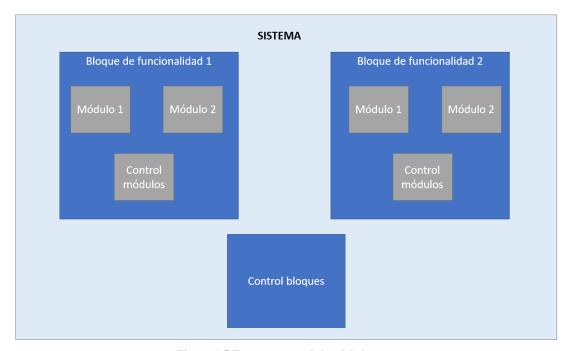

Para el diseño del hardware, se separan las funciones que debe cumplir el sistema en distintos bloques que se coordinan con un control general. Cada uno de estos bloques, se separa en los módulos necesarios para que el conjunto de estos realice una función concreta. Estos bloques cuentan con su propio control. En la Figura 1.5 se muestra la compartimentalización del sistema. Se diseña siguiendo la filosofía de usar máquinas de estado de alto nivel descritas en el capítulo 5 del libro de diseño digital de Frank Vahid [6]. Con el comportamiento del módulo definido, se diseña la ruta de datos necesaria para llevar a cabo las operaciones necesarias, y se conecta esta ruta de datos al control.

Figura 1.5 Estructura modular del sistema.

La mayoría de los módulos que componen el sistema se modelan en Matlab primero. De estos modelos se extraen ficheros utilizados en la verificación del módulo. A partir de este modelo se implementa el hardware en SystemVerilog. Los módulos que no siguen este flujo son los que utilizan una IP del catálogo de IP de Quartus Prime.

Una vez completado el hardware de un módulo, se realiza la verificación del sistema en ModelSim. Para la verificación se comparan los resultados del hardware con los obtenidos en Matlab y se observa que la evolución de las señales en el visor de formas de onda es coherente. En los módulos donde no haya datos que contrastar, se realiza la verificación analizando la evolución de las señales en la simulación. Para módulos donde la temporización pueda ser crítica, se realiza una simulación a nivel de puerta.

Una vez se han implementado y testeado todos los módulos que componen un bloque, se realiza la integración de los módulos en el bloque y se testea el bloque completo. Para estos bloques, se realizan pruebas más exhaustivas, modificando todos los parámetros de configuración del bloque para garantizar un funcionamiento robusto. Como en la verificación de los módulos, se contrastan los resultados del bloque hardware con el modelo en Matlab y se analiza la evolución de las señales.

Una vez implementados y testeados todos los bloques de funcionalidad, se integran en el sistema. Se verifica comparando los resultados del sistema con los del modelo Matlab para distintas configuraciones.

Con el testeo en ModelSim finalizado, se programa el prototipo en la placa de desarrollo y se utiliza el SignalTap para depurar el sistema y comprobar que la evolución de las señales y los datos almacenados en los registros son los esperados.

Finalmente se integra el sistema al equipo del laboratorio que realiza la transmisión de señales a través de un LED de iluminación y las recibe con un fotodetector. Se realizan pruebas de calibración y medida del BER a distintas frecuencias para comprobar el funcionamiento del sistema en una transmisión real.

#### 1.5 Estructura de la memoria

La memoria se estructura como se explica a continuación:

- En el punto 2 se explica el sistema y su implementación hardware. Primero se muestra el sistema completo. A continuación, se subdivide en los distintos bloques que realizan las funciones y se detalla su implementación. Estos se descomponen en diversos módulos que se utilizan para realizar la función del bloque y también son explicados.

- En el punto 3 se detalla cómo se ha realizado la interfaz que permite al usuario comunicarse con el sistema desde un PC a través de Matlab.

- En el punto 4 se muestran los resultados de test del prototipo programado en la placa de desarrollo. Primero se muestran los resultados obtenidos realizando pruebas con el SignalTap. Luego se explica el sistema de transmisión con LED del laboratorio, y se muestran los resultados de las pruebas del sistema dentro del entorno del laboratorio.

- En el punto 5 se exponen las conclusiones.

- En el punto 6 se describen ampliaciones y posibles mejoras del sistema.

# Capítulo 2. Diseño del sistema

#### 2.1 Funcionamiento del sistema

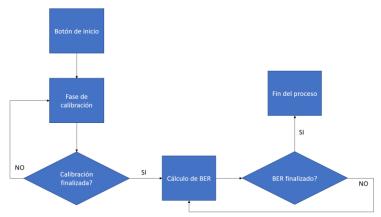

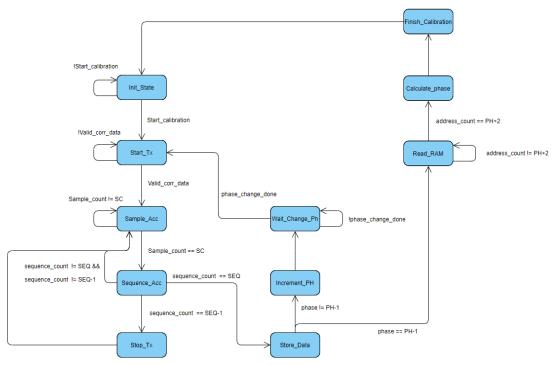

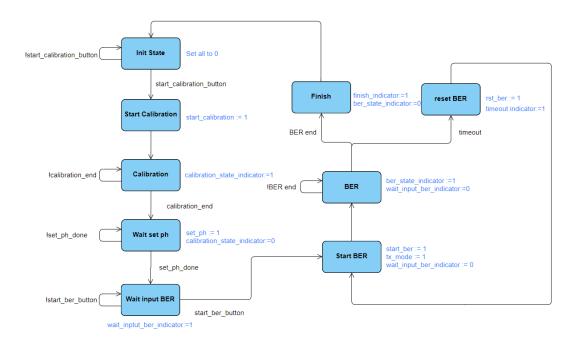

El sistema realiza dos funciones principales, la calibración y el cálculo del BER. A través de un interfaz se inicia la etapa de calibración, cuando finaliza esta etapa, se pasa a la etapa del cálculo del BER. Cuando acaba con el cálculo, se almacenan los resultados en registros y finaliza el proceso. El diagrama de flujo del sistema, teniendo en cuenta únicamente estas dos etapas, se muestra en la Figura 2.1. Además de esto, el sistema genera la señal a transmitir.

Figura 2.1 Diagrama de flujo del sistema.

#### 2.1.1 Etapa de calibración

En el modo de calibración, se configura el sistema para que se capture la señal en la parte óptima del pulso con el bit recibido para minimizar las pérdidas de datos por el deterioro de la señal en la transmisión.

Para conseguir esto, el sistema emite una secuencia de calibración. Cada bit de esta secuencia se captura en varias fases del reloj de recepción de señal. En todas las fases, se realiza una operación de correlación de la secuencia recibida con la secuencia de calibración. La secuencia de calibración se envía un número elevado de veces para cada una de las fases y se realiza el promediado de los máximos de correlación de cada fase. Finalmente se realiza la decisión de fase óptima, seleccionando la fase intermedia entre todas las que superan cierto nivel de correlación. En la Figura 2.2 se muestra el diagrama de bloques de la fase de calibración.

Figura 2.2 Diagrama de bloques fase de calibración.

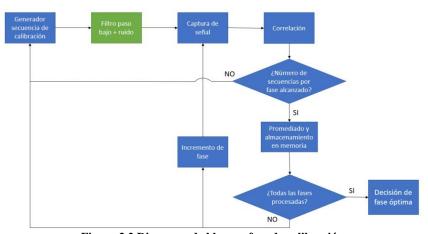

El bloque de calibración se implementa primero en Matlab para tener un modelo con el que comprobar y estudiar el comportamiento de esta etapa y que, posteriormente, se utiliza para la verificación de la implementación hardware.

En esta etapa primero se generan múltiples secuencias de calibración, utilizando un registro de desplazamiento con retroalimentación lineal, también conocido como linear feedback shift register (LFSR). En Matlab la secuencia se genera utilizando el objeto PNSequence de la caja de herramientas de comunicaciones. [7]. Para modelar el efecto del canal de transmisión, esta secuencia se filtra con un filtro paso bajo y se le introduce un ruido, el resultado de este proceso puede observarse en Figura 2.3. Se captura la secuencia recibida en distintas fases del reloj de recepción y se realiza la operación de correlación de cada fase de la señal filtrada con la secuencia de calibración. Esta operación se realiza múltiples veces para poder calcular el valor medio de correlación en cada fase. Con estos valores medios, se realiza la decisión de fase óptima.

Figura 2.3 Señal de calibración. Arriba directa del LFSR. Medio Filtrada. Abajo añadiendo el ruido.

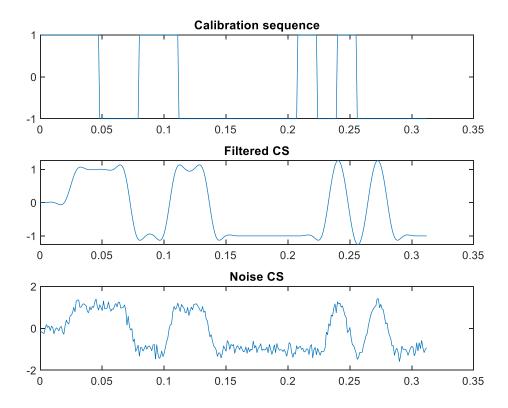

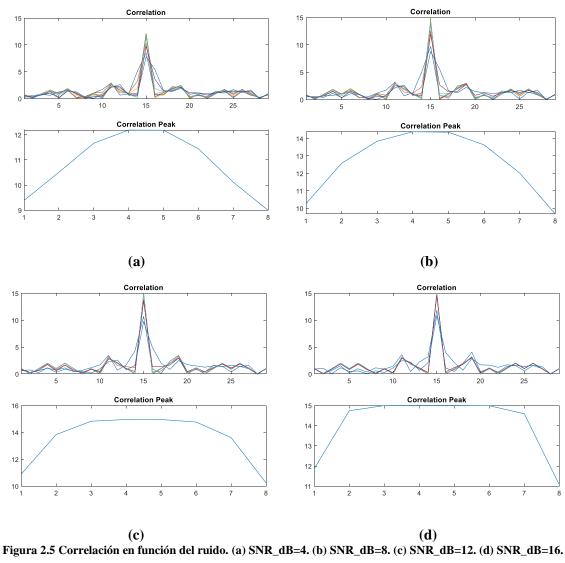

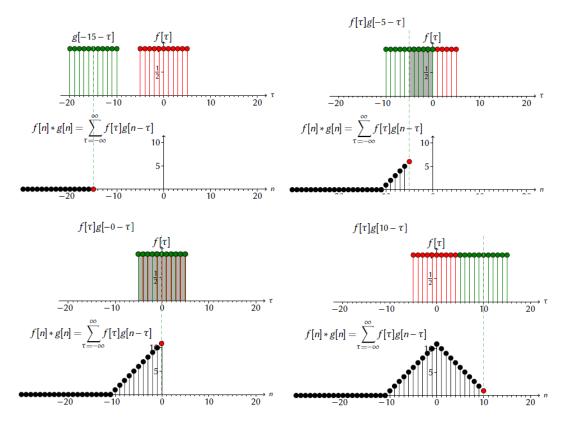

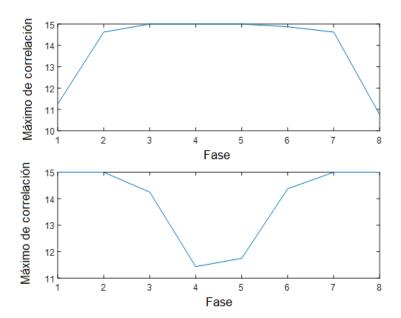

En la gráfica (a) de la Figura 2.4, se representa la media de la correlación cruzada entre las secuencias de calibración recibidas capturadas en ocho fases y la secuencia de calibración generada sin pasar por el medio de transmisión. La secuencia de calibración en esta gráfica es de quince bits. En el quinceavo desplazamiento de la operación de correlación, se compara la secuencia recibida completa con la generada y se puede observar cómo se alcanza el máximo de correlación.

La gráfica (b) de la Figura 2.4, recoge el valor medio de los máximos de correlación obtenidos en cada fase en un número elevado de secuencias de calibración. Con esta gráfica es posible determinar con qué fases del reloj de recepción se captura mejor la señal.

Figura 2.4 Curvas de correlación obtenidas en Matlab para 8 fases y secuencia de 15 bits (a) Correlación en cada fase. (b) Media de correlación por fase.

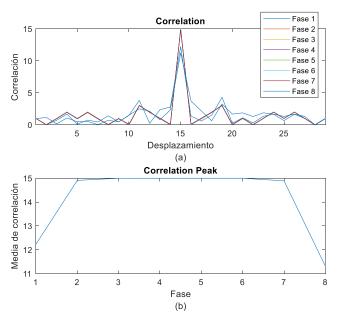

Utilizando el modelo de simulación de esta etapa, se estudia como el ruido afecta a estas curvas de correlación. En la Figura 2.5 se representa el resultado de la correlación para diferentes relaciones de señal y ruido (SNR). Puede observarse como para malas relaciones señal ruido, los máximos de correlación obtenidos están por debajo del máximo de correlación posible, y pocas fases alcanzan niveles altos de correlación. A medida que va mejorando la relación señal ruido, el máximo valor de correlación obtenido se va aproximando al máximo valor de correlación posible, hasta finalmente alcanzarlo. A su vez el número de fases con buena correlación va aumentando.

Como se puede ver, las peores fases se encuentran en los extremos y las mejores en el centro, por eso se selecciona la fase central de entre las que superan cierto nivel de correlación como fase óptima sobre la que capturar la señal recibida. De esta forma se sabe que se está capturando en una de las fases con mejor correlación, y se tiene cierto margen de maniobra.

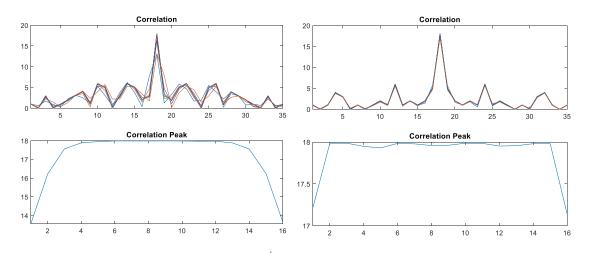

Se han realizado distintas pruebas para comprobar como diferentes parámetros afectan a la calibración. En la Figura 2.6 se muestra como un filtro más estrecho reduce el número de fases válidas.

Figura 2.6 Curvas de correlación en función del filtro. Derecha wn = 1/2. Izquierda wn = 1/8.

Se estudia también como el número de fases con las que se captura la señal afecta al sistema, y se concluye que, a mayor número de fases, más amplio es el intervalo de fases válidas, como se observa en la Figura 2.7.

Figura 2.7 Correlación para 6 fases (Izqda.) y 32 (Dcha.) coeff 50, wn 1/2, snr 10.

15

El retardo introducido por el canal hace que la curva de correlación obtenida se desplace y se vea como se muestra en la Figura 2.8. Esto complica la decisión de la fase óptima ya que no es posible conocer antes de la transmisión en qué momento comienza a capturarse la señal ni qué forma tendrá la curva de correlación. Para solucionarlo, se almacena la curva de correlación de las secuencias recibidas en una memoria. A continuación, se ordena la curva comenzando por la fase de menor correlación y con esto ya es posible diseñar un módulo que seleccione la fase central de forma sencilla.

Figura 2.8 Curva correlación con un retardo de 10 muestras.

#### 2.1.2 Etapa de cálculo del BER

En el modo de cálculo del BER se compara la señal recibida con la misma señal sin pérdidas por transmisión y se contabiliza el número de errores y el número de bits recibidos para obtener el BER

Para ello, se genera una secuencia compuesta de una cabecera para indicar el inicio de la transmisión y la señal a transmitir en sí, que se trata de una secuencia pseudoaleatoria. Se captura la señal en la fase óptima obtenida previamente en la etapa de calibración. La seña recibida pasa por un correlador configurado con la secuencia de la cabecera. Con esto se consigue detectar el inicio de la trama cuando el valor a la salida del correlador supere el umbral de correlación calculado en la fase de calibración. Así que el cálculo del BER comienza a partir de la recepción de la cabecera. A partir de este punto se realiza el cálculo del BER comparando la secuencia aleatoria recibida tras el preámbulo con la misma secuencia generada internamente por el sistema. En la Figura 2.9 se muestra el diagrama de bloques de la etapa del cálculo del BER.

Figura 2.9 Diagrama de bloques cálculo del BER.

De la misma forma que se realizó en la etapa de calibración, el bloque del cálculo del BER se implementa primero en Matlab para comprender el funcionamiento de esta etapa y para conseguir un modelo sobre el que comparar los resultados en la verificación del hardware.

El primer paso de esta etapa es generar la secuencia que se transmite para realizar el cálculo del BER. Esta secuencia se genera con un LFSR de la misma forma que en la etapa de calibración. Se utiliza como cabecera la señal utilizada como secuencia de calibración y se le concatena la generada por el LFSR. Se filtra y se añade ruido a esta señal y se captura con la fase óptima. Se compara con la secuencia generada directamente por el LFSR para realizar el cálculo del BER

Se realizan pruebas modificando la configuración de parámetros para comprobar cómo afectan al BER. En la Figura 2.10 se muestra la curva del BER en función de la SNR de dos sistemas cuyos canales están modelados uno con un filtro de frecuencia de corte wn = ½ (caso b) y otro cuatro veces menor (caso a). Se observa que con el filtro más estrecho se reduce el BER.

Figura 2.10 BER en función del ruido. (a) wn=1/8. (b) wn=1/2.

Se comprueba también la diferencia en el BER si se elige como fase óptima la fase central de entre las que superen un umbral o la fase con mayor correlación. Como se muestra en la Figura 2.11, para filtros más restrictivos la fase de mayor correlación coincide con la central. Con filtros menos restrictivos, se consigue mejor BER si se selecciona la fase de mayor correlación. El problema es que, si se selecciona la fase de mayor correlación, no se sabe exactamente dónde va a estar dentro de la curva de correlación, con lo que puede darse el caso en que esta fase esté adyacente a una fase donde la captura de señal sea mala. Es preferible capturar sabiendo que las fases que rodean a la seleccionada son también válidas.

Figura 2.11 Cálculo del BER comparando la fase central con la de máxima correlación para distintos filtros. (a) wn=1/8. (b) wn=1/2.

#### 2.2 Especificaciones técnicas

Como se ha comentado en el punto anterior, en la calibración se captura la señal con el mismo reloj de transmisión, pero desfasado en un número de fases diferentes y se selecciona la fase óptima para la captura de información. Para ello se promedia la recepción de varias secuencias de calibración. Teniendo en cuenta la funciones a realizar en esta parte, la configuración del sistema debe ser parametrizable tal y como se indica a continuación:

- Configuración de la secuencia de calibración: Se puede modificar el número de bits de esta secuencia y con el mismo número de bits, se pueden generar secuencias distintas.

- Número de fases para la captura de señal.

- Número de envíos de la señal de calibración por cada fase: Se envía la secuencia de calibración múltiples veces para realizar un promedio de todas las secuencias y minimizar la varianza introducida por el ruido.

- Cuenta de muestras por secuencia de calibración: Para compensar retardos generados por el canal de transmisión, se introduce una secuencia de ceros que se incluyen tras la secuencia de calibración, con esto se asegura que toda la secuencia de calibración es capturada.

En cuanto al cálculo del BER, como se ha comentado anteriormente, compara la secuencia recibida con una idéntica generada dentro del sistema. Por lo que los parámetros de configuración necesarios son los siguientes:

- Configuración de la secuencia transmitida: Se puede modificar el número de bits de esta secuencia y con el mismo número de bits, se pueden generar secuencias distintas.

- Número de errores a alcanzar: El cálculo del BER, se realiza hasta alcanzar el número de errores determinado en este parámetro.

- Configuración del contador: El sistema se diseña teniendo en mente que el número de muestras a contabilizar para realizar el cálculo del BER es elevado, por ello y para mejorar la frecuencia máxima del sistema, el contador se implementa con varios contadores en cascada. El número de contadores y el tamaño de los mismos es parametrizable.

Para obtener distintas frecuencias, un PLL genera distintos relojes. En Matlab se calculan los parámetros para realizar el incremento de fase en cada uno de los relojes.

El sistema se conecta al PC a través de una red TCP/IP y el usuario interactúa con el prototipo a través de comandos en Matlab.

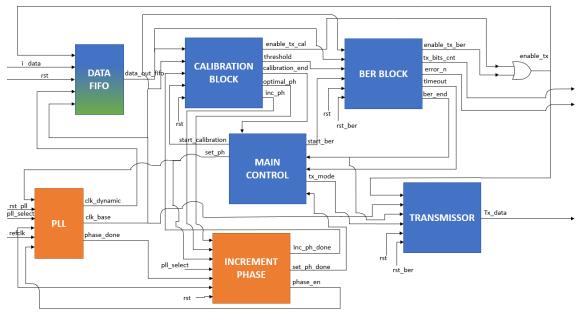

# 2.3 Implementación hardware

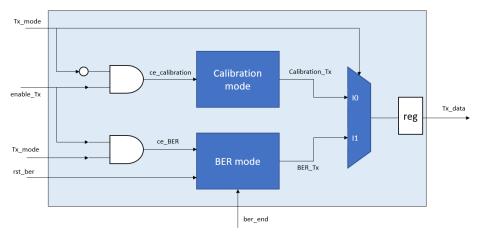

El hardware puede descomponerse en siete módulos que se encargan de realizar las acciones necesarias para conseguir la calibración de la señal recibida y el cálculo del BER:

- DATA\_FIFO: Se utiliza para capturar la señal de entrada bajo un reloj desfasado, y

enviarla al resto de bloques bajo un reloj a la misma frecuencia, pero siempre en la misma

fase. Este bloque funciona con los dos relojes generados por el PLL. Con esto se consigue

capturar la señal en distintas fases, mientras que el resto de módulos pueden funcionar

bajo un mismo reloj.

- CALIBRATION\_BLOCK: Realiza la fase de calibración, funciona bajo el reloj estático generado por el PLL.

- BER\_BLOC: Realiza la fase del cálculo del BER, funciona bajo el reloj estático generado por el PLL.

- PLL: Genera los relojes utilizados por el sistema, funciona bajo un reloj de referencia de 50MHz.

- INCREMENT\_PHASE: Gestiona las señales para realizar el incremento de fase del reloj dinámico del pll, funciona bajo el mismo reloj de referencia de 50MHz del PLL.

- TRANSMISOR: Genera la señal a transmitir a través del LED, funciona bajo el reloj estático generado por el PLL.

- MAIN\_CONTROL: Gestiona el control del sistema, funciona bajo el reloj estático generado por el PLL.

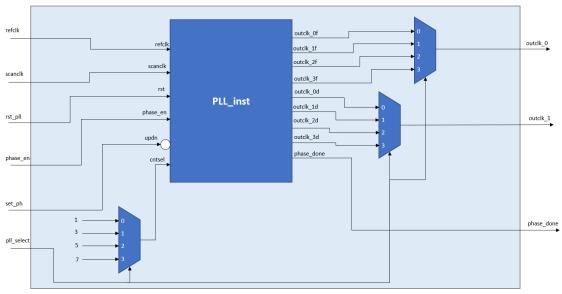

En la Figura 2.12 puede observarse el esquema de conexiones entre los distintos bloques del sistema.

Figura 2.12 Conexiones entre los bloques que componen el sistema. Naranja: reloj de referencia. Azul: Reloj estático. Verde: Reloj dinámico.

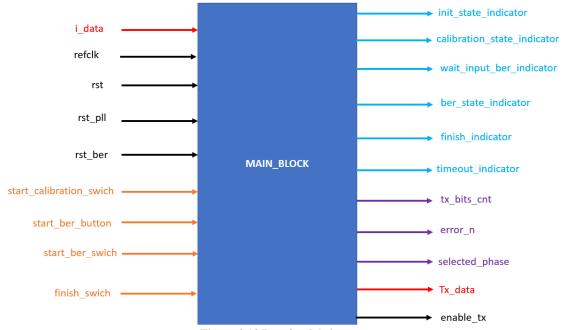

Como interfaz de usuario, se utilizan tres botones para los resets del sistema, del pll y de la fase del cálculo del BER. Un switch para comenzar con el proceso de calibración, un switch o un botón para comenzar con el cálculo del BER y un switch para finalizar el proceso completo.

El estado del sistema se indica con LEDs, uno indica que el sistema está en el estado inicial y preparado para comenzar. Otro indica que se está realizando la calibración. Otro que se está esperando al input para pasar a la etapa del cálculo del BER. Mientras está realizando el BER, se ilumina un LED indicándolo. Finalmente se enciende un LED cuando el sistema ha finalizado o cuando ha habido un timeout.

Se configuran como registros de salida los resultados obtenidos de fase óptima, número de errores y número de muestras recibidas durante el cálculo del BER. En la Figura 2.13 se muestra la interfaz del sistema.

Figura 2.13 Interfaz del sistema.

Para la configuración del sistema, se genera un paquete desde Matlab con todos los parámetros que se incluye directamente en el proyecto de Quartus Prime.

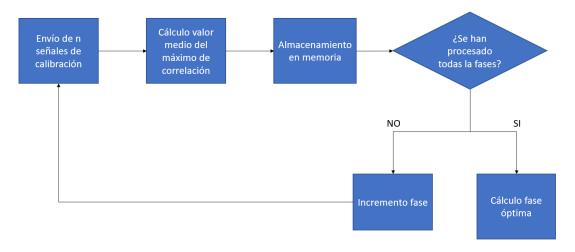

#### 2.3.1 Calibración

El bloque de calibración se encarga de seleccionar la fase óptima de entre todas las fases capturadas. Para ello se promedia la correlación de varias secuencias de calibración en una fase y se almacena el resultado obtenido en una memoria. A continuación, se activa una señal para solicitar el incremento de fase. Cuando se recibe la señal indicando que se ha completado el cambio de fase, se repite el proceso para el resto de las fases. Una vez se han procesado todas las fases, se calcula el umbral en función del promedio máximo y mínimo de correlación. Este umbral es utilizado para considerar una fase como válida. Finalmente se selecciona como fase óptima la fase intermedia de entre las que superan el umbral. Cada una de estas funcionalidades se implementa con distintos módulos.

Figura 2.14 Diagrama de flujo proceso de calibración.

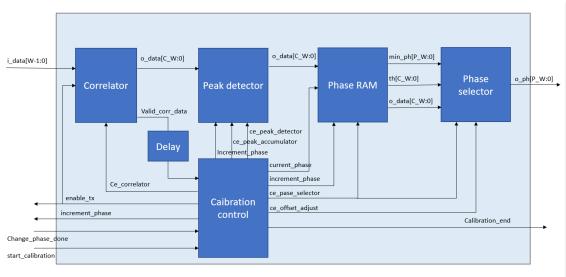

El esquema con las conexiones entre los módulos que componen el bloque CALIBRATION\_BLOCK puede observarse en la Figura 2.15.

Figura 2.15 Esquema conexiones bloque CALIBRATION\_BLOCK.

El correlador realiza la correlación de la señal recibida con la secuencia de calibración y envía el resultado a Peak\_detector donde acumula los máximos de cada secuencia. Una vez se reciben todas las secuencias de una de las fases, se dividen los máximos acumulados en Peak\_detector por el número de veces que se ha recibido la secuencia de correlación para obtener la media. Para

realizar esta operación el número de secuencias es potencia de 2 por lo que se realiza la división con un desplazamiento de bits. Este valor medio se almacena en Phase\_RAM. Una vez se ha almacenado el valor medio de todas las fases, se pasa esta información a Phase\_selector donde se decide la fase óptima. Calibration\_control gestiona el control del bloque de calibración.

El correlador se sintetiza con un número de celdas igual a los bits de calibración. Pero el control cuenta tantas muestras por secuencia como el número de bits de la secuencia de calibración y unas muestras extra para tener en cuenta el retardo. El control empieza la cuenta de muestras cuando la señal valid\_corr\_data está activa, por lo que es necesario retrasarla un número de muestras igual a las muestras extra para incluir el retardo. En caso contrario, el control comienza a trabajar antes de que el correlador haya procesado la secuencia completa.

Para ello, en el bloque Delay se utiliza un buffer de tamaño SC-N. Se podría modificar el correlador como alternativa, pero eso conllevaría un consumo de elementos lógicos ligeramente superior.

Como parámetros configurables tiene todos los utilizados por los diferentes módulos:

- N\_C: Número de secuencias de calibración por fase.

- N: Número de bits de la señal de correlación.

- C: Configuración de las celdas del correlador.

- W: Ancho de bits del dato de entrada.

- P W: Ancho de bits de la fase.

- C W: Ancho de bits de los datos del correlador.

- SC: Número de muestras contadas por secuencia.

- PH: Número de fases.

#### Como entradas:

- clk: Reloj del sistema.

- phase\_change \_done: Indica que se ha realizado el cambio de fase.

- i data: datos de entrada.

- start\_calibration: Señal de inicio de la fase de calibración.

- rst: Reset del sistema.

#### Las salidas son las siguientes:

- increment\_ph: Señal que indica que se incrementa la fase.

- enable\_tx: Habilitación del transmisor.

- calibration\_end: Final de la fase de calibración.

- o ph: Fase óptima.

#### 2.3.1.1 Correlador

La función del correlador es comparar la señal recibida con una secuencia almacenada y detectar coincidencias. Este módulo se utiliza en la fase de calibración para determinar las fases más robustas. El bloque del cálculo del BER también utiliza un correlador para detectar la secuencia de calibración en la señal recibida.

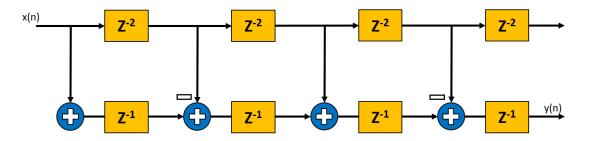

El correlador realiza una convolución de la señal recibida con una señal fijada. La convolución consiste en desplazar una de las señales n muestras, multiplicar las muestras de ambas señales y sumar los resultados.

$$y(n) = x(n) * h(n) = \sum_{r=-\infty}^{\infty} h(r) \cdot x(n-r)$$

Ecuación 2.1 Convolución.

Figura 2.16 Visualización de la operación de convolución [8].

Cuando la señal recibida coincida con la señal fijada, el valor de la operación de convolución alcanzará un máximo. La señal fijada en el bloque del correlador es la secuencia de calibración. Con lo que es posible detectar dicha secuencia durante la transmisión de datos.

Para este caso en concreto, la señal recibida es una secuencia binaria comprendida entre 1 y -1. El resultado de la multiplicación de muestras iguales es 1, por lo que el valor máximo de correlación coincide con el número de bits de la secuencia de calibración.

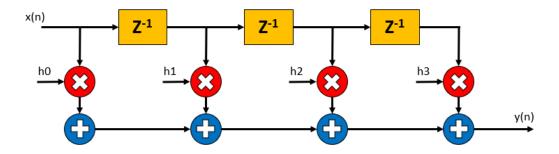

La implementación digital de este módulo es muy similar a la de un filtro FIR, en este caso se utiliza una arquitectura paralela debido a las restricciones temporales del sistema.

Figura 2.17 Arquitectura correlador.

Conociendo que la señal recibida es una secuencia de 1 y -1, es posible modificar la arquitectura para eliminar los multiplicadores del sistema. Cuando se compara una muestra recibida con un 1, se realiza la suma con el mismo valor de la muestra. Cuando se compara con un -1, se realiza la operación con complemento a dos de la muestra.

Para implementarlo en SystemVerilog, se descompone la operación en dos tipos de celdas distintas. Dependiendo de un parámetro C de entrada, se sintetiza un tipo de celda u otro tal y como se muestra en la Figura 2.18.

Figura 2.18 Izqda. celda coeficiente 1, Dcha. celda coeficiente -1.

El módulo tiene como parámetro de configuración la secuencia de calibración, que se utiliza para montar el sistema con las celdas correspondientes. En la Figura 2.19, se muestra un ejemplo de configuración del correlador.

Figura 2.19 Correlador con secuencia de calibración 1, -1, 1, -1.

Para acortar el camino de la lógica combinacional, se realiza una segmentación del sistema. Se introduce un registro después de cada sumador y después de cada registro de la señal de entrada para sincronizar los tiempos.

Figura 2.20 Correlador segmentado.

La celda cuenta con tres parámetros de configuración:

- C: Indica el valor del coeficiente de la celda. Cuando C=0 el coeficiente es -1, en caso contrario es 1.

- W: Es el número de bits del dato de entrada.

- G: Es el número de bits de guarda. El máximo de correlación corresponde con el número de bits de la señal de calibración. Así que los bits necesarios son el logaritmo en base 2 del número de bits de la señal de calibración, más un bit adicional de signo. Se realiza con la función \$clog2.

En cuanto a las entradas y salidas de la celda:

- signal\_in: Señal de entrada, con formato [W-1:0].

- sum\_in: Entrada con el resultado de la suma de la celda anterior, con formato [W+G-1:0].

- rst\_ac: Reset asíncrono del sistema, activo a nivel alto.

- val\_in: Entrada binaria que informa de una muestra válida en signal\_in.

- clk: Entrada de reloj.

- ce: Entrada de habilitación de la celda.

- signal\_out: Salida de la señal de entrada retrasada, con formato [W-1:0].

- val\_out: Salida binaria que indica que hay una muestra válida en signal\_out.

- sum\_out: Salida con el resultado de la suma de la muestra a procesar con la suma anterior, con formato [G-1:0].

La señal de entrada se registra una vez dentro de la celda, y de nuevo a la salida para sincronizar las muestras de la señal con la suma registrada.

La señal val\_out registra el estado de val\_in, así estará activa cuando comience a obtenerse el valor de correlación.

La operación suma se sintetizará dependiendo del parámetro C. Cuando es 0, sum\_out será el complemento a 2 de signal\_in más sum\_in. Si es distinto de 0, será signal\_in más sum\_in.

Para observar como el sintetizador implementa las celdas, se simplifica el código, eliminando los registros y las señales de validación. Obteniendo las celdas mostradas en la Figura 2.21.

Figura 2.21 Celdas del correlador. (a) Coeficiente -1. (b) Coeficiente 1.

Al compilar ambas celdas, los elementos lógicos utilizados coinciden.

| Top-level Entity Name       | CORRELATOR_CELL       |

|-----------------------------|-----------------------|

| Family                      | Cyclone V             |

| Device                      | 5CSXFC6D6F31C6        |

| Timing Models               | Final                 |

| Logic utilization (in ALMs) | 11 / 41,910 ( < 1 % ) |

| Total registers             | 2                     |

| Total pins                  | 49 / 499 ( 10 % )     |

Figura 2.22 Síntesis de ambos tipos de celda del correlador.

En la capa superior a la celda, se encuentra el módulo CORRELATOR. Cuenta con los siguientes Parámetros de configuración:

- N: Número de bits de la señal de calibración.

- C: Configuración de la señal de calibración. El número introducido en binario se utiliza como modelo para determinar qué tipo de celda se utiliza. Los unos representan un coeficiente 1 y los ceros un coeficiente -1. Por ejemplo, para la señal de calibración 1, -1, 1, -1; C sería 1010 en binario o 10 en decimal.

- W: Número de bits de la señal de entrada.

Las señales de entrada y salida del sistema son:

- i\_data: Señal de entrada, con formato [W-1:0].

- rst\_ac: Reset asíncrono del sistema, activo a nivel alto.

- val\_in: Entrada binaria que informa de una muestra válida en i\_data.

- clk: Entrada de reloj.

- ce: Entrada de habilitación de las celdas.

- o\_data: Salida del sistema con el resultado de la correlación, con formato [W+ceil(log2(N))-1:0].

- val\_out: Salida binaria que indica que hay una muestra válida en o\_data.

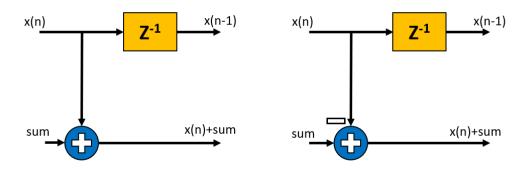

# 2.3.1.2 Detector de picos de correlación

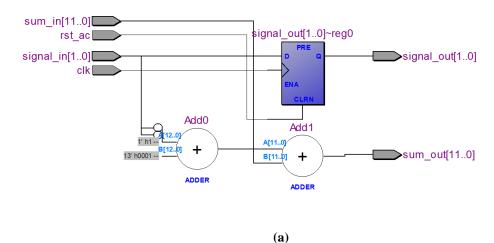

Es el módulo encargado de detectar los picos de correlación y calcular el valor medio de los máximos de correlación en cada fase. Estos máximos se acumulan con cada una de las transmisiones de la señal de calibración por fase y, finalmente, se calcula el valor medio. El número de secuencias se recibe como parámetro y el ancho de bits de los datos de entrada es parametrizable. Para poder realizar el cálculo del valor medio, el número de secuencias enviadas por fase debe ser potencia de 2. De esta forma puede realizarse la división como un desplazamiento de bits. Señales de control gestionan el flujo de funcionamiento del módulo.

El módulo utiliza 2 parámetros de configuración:

- C\_W: Tamaño de los datos de entrada y salida.

- N\_C: Número de secuencias enviadas por fase.

Además, se utilizan los parámetros n\_desp y n\_desp\_w, que dependen de los dos anteriores:

- n\_desp: Se utiliza para determinar el desplazamiento de bits del acumulador para obtener el valor medio. n=log2(N\_C).

- n\_desp\_w: Se utiliza para determinar el ancho de bits del acumulador. El máximo del acumulador será igual a N\_C multiplicado por el máximo que puede obtenerse con un ancho de bits C\_W, luego n\_desp\_w=log2(N\_C\*2^C\_W).

Respecto a las entradas y salidas del sistema:

- clk: Entrada de reloj.

- ce: Entrada de habilitación del detector de picos.

- acc\_en: Entrada de habilitación del acumulador.

- acc\_rst: Reset del acumulador.

- rst: Reset del sistema, activo a nivel alto.

- i data: Entrada de datos. Recibe los datos del módulo correlador.

- o\_data: Salida del sistema, valor medio del máximo de correlación para un número de secuencias de calibración determinado.

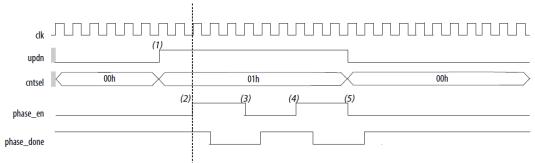

En la Figura 2.23, se muestra la parte de la máquina de estados que determina las señales de activación.

Figura 2.23 Máquina estados PEAK\_DETECTOR.

Ce habilita el registro que almacena el pico máximo, una vez se han recibido todas las muestras de una secuencia, se activa el acumulador con ce\_acc y se resetea el registro max\_peak. Una vez recibidas todas las secuencias, se resetea el acumulador.

En la Figura 2.24 se muestra el esquema del módulo.

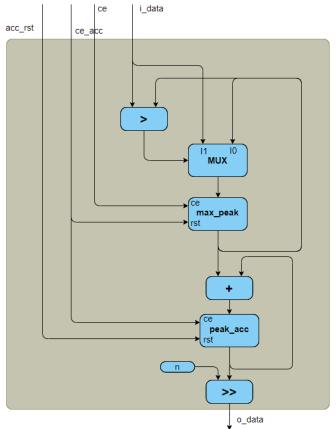

Figura 2.24 Esquema módulo PEAK\_DETECTOR.

Se crea un registro max\_peak de tamaño [C\_W:0], que almacena el máximo de correlación para cada secuencia de calibración recibida. Se crea también el registro peak\_accumulator de tamaño [n2:0] que almacena la suma del máximo de correlación de la secuencia actual con los máximos acumulados de las anteriores.

Cuando ce sea activo y el dato de entrada sea mayor que el valor registrado en max\_peak, el dato de entrada se guardará en el registro. Ce es una señal de control que se activa mientras se recibe la secuencia de calibración.

Si acc\_en es activo, significa que se ha finalizado la recepción de una secuencia de calibración. Al registro peak\_accumulator se le suma el valor de max\_peak y se resetea el registro max\_peak.

La señal acc\_rst indica que se ha finalizado el número de transmisiones para la fase actual, así que se resetea el registro peak\_accumulator para comenzar a procesar los datos de la siguiente fase.

La salida del sistema es el valor del registro peak\_accumulator desplazado n bits para calcular el valor medio.

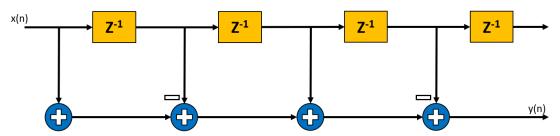

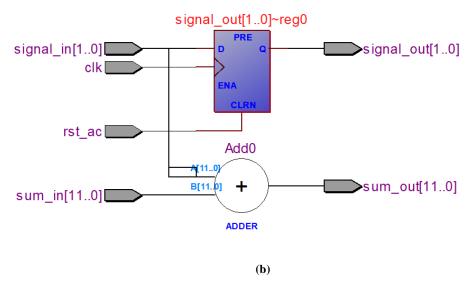

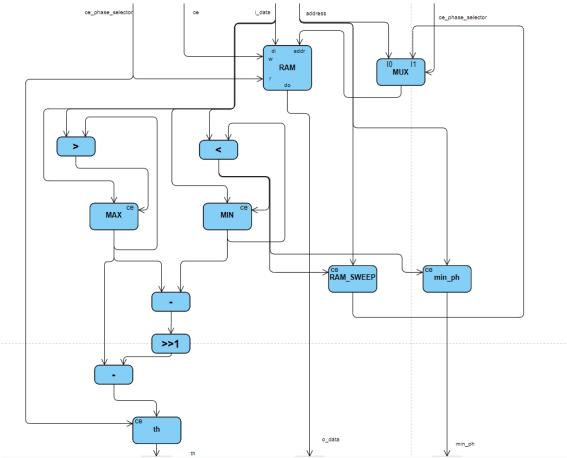

#### 2.3.1.3 Almacenamiento en RAM

Es el módulo encargado de almacenar los datos de valor medio de correlación en cada fase. Una vez finalizado el envío de señales de calibración, realiza un barrido de los datos almacenados. Debido al retraso por el medio entre el transmisor y el receptor, no se puede saber con seguridad en qué fase comienzan a procesarse los datos. Así que otra función de este módulo es la de enviar los valores ordenados al módulo encargado de determinar la fase óptima. En la Figura 2.25 se muestra el efecto de este desfase en la curva de correlación.

Figura 2.25 Curvas de correlación con 8 fases. Superior: curva de correlación, inferior: curva de correlación desfasada.

Se conoce la naturaleza de la curva de correlación de las fases gracias a las pruebas realizadas previamente en Matlab. Teniendo en cuenta esto y para simplificar el diseño del módulo que determina la fase óptima, PHASE\_RAM envía los datos comenzando por la fase con menor correlación. Con los datos en la memoria, se calcula un umbral que determina qué fases son válidas. Se envía la fase con la correlación mínima y el umbral al siguiente módulo, ya que son datos necesarios para calcular la fase óptima.

El módulo utiliza 3 parámetros de configuración:

- C W: Ancho de bits de los datos de correlación.

- P\_W: Ancho de bits de los datos de fase.

- PH: Número de fases.

Respecto a las entradas y salidas del sistema:

- clk: Entrada de reloj.

- ce: Entrada de habilitación de escritura de la memoria.

- ce\_phase\_selector: Entrada de habilitación del barrido de la memoria.

- rst: Reset del sistema, activo a nivel alto.

- i\_data: Entrada de datos. Recibe los datos con el valor medio de correlación.

- address: Entrada de datos con la fase en la que se está trabajando. Se utiliza como dirección de la memoria donde se almacenan los datos de i\_data.

- o\_data: Salida del sistema con los valores almacenados en la memoria.

- th: Salida con el umbral calculado.

- min\_ph: Salida con la fase que tiene el mínimo de correlación.

La parte de la máquina de estados que gobierna las señales del módulo es la mostrada en la Figura 2.26.

Figura 2.26 Máquina de estados PHASE\_RAM.

La señal ce habilita la escritura de datos en la RAM en la posición address. Una vez guardado el dato se incrementa la dirección y se espera al cambio de fase. Si es la última fase, se habilita la señal ce\_phase\_selector que habilita el barrido de datos de la memoria comenzando por la posición RAM\_SWEEP.

En la Figura 2.27 se muestra el esquema del módulo.

Figura 2.27 Esquema PHASE\_RAM.

Se crean los registros MAX y MIN de tamaño [C\_W:0] que almacenan el valor máximo y mínimo de correlación. RAM\_SWEEP es un registro de tamaño [P\_W:0] que almacena la fase en la que la correlación es mínima. Esta es la dirección de memoria que comienza a leerse al enviar los datos al siguiente módulo. RAM es una memoria de [PH-1:0] direcciones de tamaño [C\_W:0] donde se almacenan los datos recibidos.

La señal de control ce es activa cuando se han procesado todas las secuencias de calibración de una fase. Cuando esto ocurre se almacena el dato con la media de correlación recibida mediante i\_data en la memoria RAM en la posición determinada por address, que va por orden de fase desde la 0 hasta PH-1.

Concurrentemente se implementa la lógica para almacenar el máximo de correlación en el registro MAX, y el mínimo en MIN. Así como la fase con el mínimo de correlación en RAM\_SWEEP y min ph.

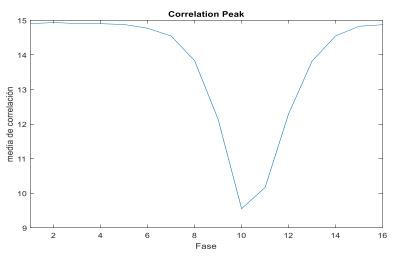

La señal de control ce\_phase\_selector es activa cuando se ha finalizado el procesado de todas las fases. Cuando esto ocurre el módulo realiza un barrido de las posiciones de memoria comenzando por RAM\_SWEEP y envía los datos almacenados a través de la salida o\_data al módulo que determina la fase óptima. Además, se realiza el cálculo del umbral utilizado para decidir si la fase es válida. El umbral se calcula como la diferencia entre el valor almacenado en el registro MAX y la resta entre el registro MAX y MIN desplazado un bit.

# 2.3.1.4 Selección de fase

Este módulo se encarga de seleccionar la fase óptima a partir de los datos facilitados por el bloque PHASE\_RAM. La fase óptima se determina como la fase intermedia entre todas las que superan el umbral. Una vez obtenida la fase óptima, se realiza el cálculo para compensar el offset entre la curva ordenada que recibe del bloque PHASE\_RAM y la curva original.

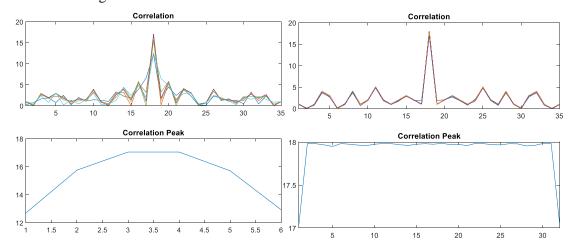

El módulo renumera las fases para hacer el cálculo según se muestra en la Figura 2.28. Por eso es necesario realizar posteriormente el cálculo para seleccionar la fase según la curva recibida. En el caso de la imagen, la fase seleccionada inicialmente por PHASE\_SELECTOR sería la 4, que corresponde originalmente con la fase 8. El cálculo final se encarga de hacer la compensación y obtener la fase 8 como fase elegida.

Figura 2.28 superior: curva de correlación ordenada. (fases recibidas: numeradas según se reciben del transmisor, fases ordenadas, según el módulo PHASE\_RAM); inferior: curva de correlación recibida.

El módulo utiliza 3 parámetros de configuración:

- C\_W: Ancho de bits de los datos de correlación.

- P W: Ancho de bits de los datos de fase.

- PH: Número de fases.

Respecto a las entradas y salidas del sistema:

- clk: Entrada de reloj.

- ce: Entrada de habilitación del proceso de selección de fase.

- ce\_offset\_adjust: Entrada del cálculo de la fase desfasada.

- rst: Reset del sistema, activo a nivel alto.

- i corr: Entrada de datos. Recibe los datos con el valor medio de correlación.

- th: Entrada de datos con el umbral a partil del cual la fase es considerada válida.

- Min\_ph: Entrada con la fase correspondiente al mínimo de correlación. Se usa para calcular el offset.

- o\_ph: Salida con la fase óptima.

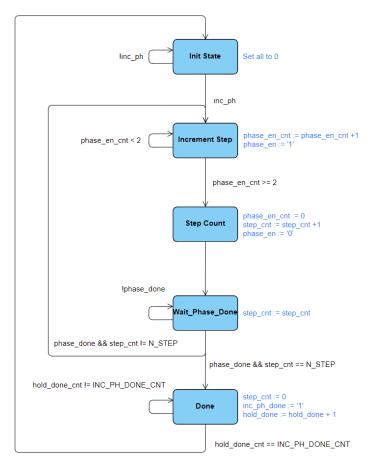

La Figura 2.29 muestra la parte de la máquina de estados con las señales de control del módulo.

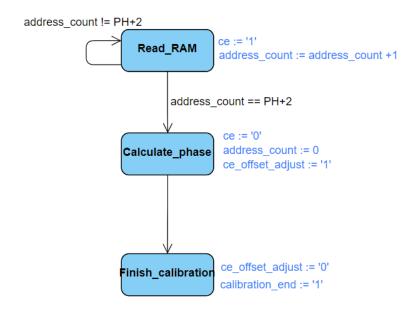

Figura 2.29 Máquina de estados PHASE\_SELECTOR.

Cuando se reciben todas las muestras de calibración, Read\_RAM activa la señal ce. Esta señal habilita los registros que forman parte del sistema encargado de decidir la fase óptima. Está activa durante 2 muestras más que el número de fases porque habilita también el módulo anterior PHASE\_RAM, y este tiene 1 retardo entre la entrada y la salida. El retardo extra es para actualizar el registro encargado de realizar el cálculo del offset que se explica más adelante.

Una vez se conoce la fase óptima, la señal ce\_offset\_adjust se activa y habilita el registro encargado de almacenar el resultado del cálculo del offset.

Tras un ciclo de reloj se deshabilita la ce\_offset\_adjust y se envía la señal de fin de calibración.

La Figura 2.30 muestra el esquema del módulo PHASE\_SELECTOR.

Figura 2.30 Esquema PHASE\_SELECTOR.

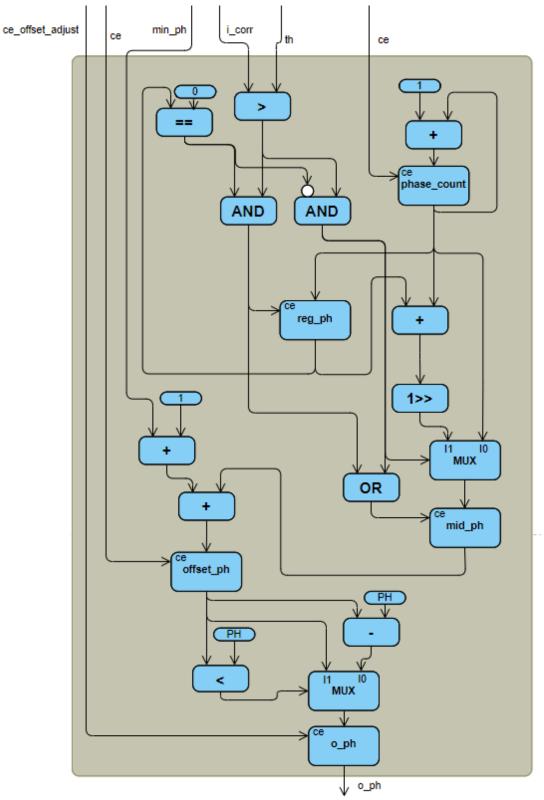

El registro phase\_count es un contador que asigna fases temporales a los valores de correlación medios recibidos desde PHASE\_RAM. Reg\_ph registra la primera fase que supera el umbral de correlación. Mid\_ph es un registro que almacena la fase central entre las que superan el umbral. Offset\_ph se utiliza para compensar el offset.

La misma señal de control activa el módulo PHASE\_RAM y PHASE\_SELECTOR. Hay un retardo entre la activación y la salida del módulo PHASE\_RAM, por lo que la primera muestra válida es la correspondiente a phase count = 1.

Cuando la señal de control ce está activa, comienza la obtención de la fase óptima. Esta es la fase central de entre todas las fases cuyo máximo de correlación supera el umbral th. Phase\_count se incrementa con cada muestra recibida y si el valor de correlación supera el umbral, se registra el valor del contador en reg\_ph. Para cada nueva muestra que llegue que supere el umbral, se asigna a mid\_ph el valor medio entre reg\_ph y la fase asignada a la nueva muestra. Esto se consigue sumando reg\_ph + phase\_count y desplazando el resultado un bit.

Concurrentemente offset\_ph es la fase central más la fase con el valor mínimo de correlación min\_ph recibido como valor de entrada del módulo. A min\_ph se le suma uno. Esto se hace porque en este módulo el rango de la fase está entre 1 y PH mientras que anteriormente estaba entre 0 y PH-1. Por lo que es necesario incrementar min\_ph para ajustarlo al nuevo rango.

Cuando se han leído todos los valores de memoria, desde el control se activa la señal ce\_offset\_adjust y comienza el ajuste de offset. Se comprueba el valor de offset\_ph, si es menor que el número de fases, offset\_ph corresponde a la fase óptima. En caso contrario, la fase óptima es offset\_ph menos el número de fases.

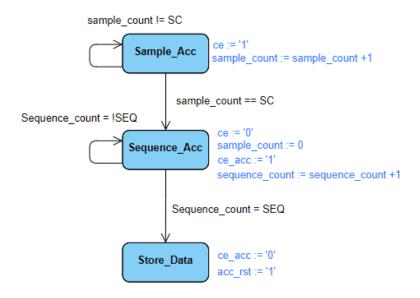

#### 2.3.1.5 Control

Módulo encargado del control de la fase de calibración. El control se implementa como una máquina de estados de Moore en el que cada estado proporciona las señales de control de los distintos módulos del bloque de calibración. Además, debe enviar señales para iniciar o parar el transmisor y tiene una señal de salida para indicar el final del proceso de calibración. La transmisión es continua para todas las secuencias de una fase.

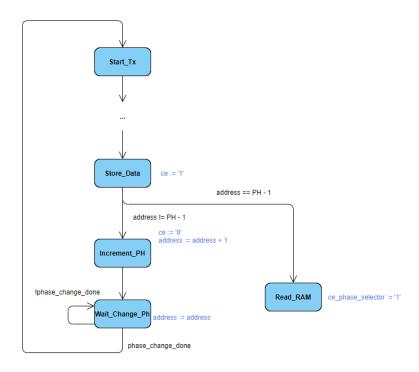

La primera etapa inicial Init\_State pondrá todos los contadores y señales a 0. En cuanto llegue la señal de inicio de calibración, pasará a la siguiente etapa Start\_Tx, donde se activará el transmisor y el correlador. El sistema se mantendrá en esta etapa hasta que empiecen a salir muestras válidas del correlador.

A continuación, en Sample\_acc, se incrementará un contador por cada muestra de entrada y se activará el detector de picos. Seguirá incrementándose hasta que cuente SC muestras, que son las de la señal de calibración más alguna muestra teniendo en cuenta el retardo de transmisión.

Cuando el contador llega a SC significa que se ha recibido la primera señal de calibración así que se pasa al estado Sequence\_Acc, donde se cuentan las secuencias recibidas. En este estado se activa el acumulador del detector de picos y se incrementa el contador de secuencias. Si el número de secuencias es inferior a SEQ-1 se vuelve al estado anterior para contar las muestras de la nueva señal. Si es SEQ-1, se pasa al estado Stop\_Tx. Y si es SEQ se pasa al estado Store\_Data.

En Stop\_Tx, se para la transmisión de datos. Se hace cuando el contador está en SEQ-1 porque el sistema empieza a contar cuando la primera muestra sale del correlador y, en este momento, la primera secuencia ya ha sido enviada. Para evitar un retraso de una muestra en la penúltima secuencia, cuando el sistema pasa por este estado, se comporta como Sample\_Acc. Se activa el detector de picos y el acumulador de muestras.

Store\_Data actúa cuando todas las secuencias de calibración de una fase han sido recibidas. Envía la señal al bloque PHASE\_RAM, para que almacene el valor medio del máximo de correlación de la fase actual. Además, se envía la señal a PEAK\_DETECTOR para borrar el acumulador. Si el contador de fase es igual a PH - 1, significa que el sistema está procesando la última fase y en lugar de pasar a Increment Phase, la siguiente etapa será Read RAM.

En Increment\_Phase, se incrementa el contador con el valor de la fase y se envía la señal de cambio de fase al bloque encargado de realizar esta función. Se necesita este estado extra porque la memoria en PHASE\_RAM utiliza como dirección este contador, y si se incrementa en el mismo

estado que se envía la señal de control al bloque, se almacena el dato en la posición de memoria siguiente. Por ejemplo, el dato de la primera fase se almacenaría en la posición de memoria 1 en lugar de la 0.

Tras un ciclo de reloj pasa a la siguiente fase Wait\_Change\_Ph, que espera a recibir la señal indicando que el bloque encargado de realizar el cambio de fase ha finalizado con su labor. Cuando llega la señal de cambio de fase, se vuelve a la etapa Start\_Tx donde se empieza a transmitir las señales de calibración para la siguiente fase.