# Escola Tècnica Superior d'Enginyeria Informàtica Universitat Politècnica de València

# HLS Kernel Execution on a Multi-FPGA Prototype

**Master Degree Final Work**

Master Degree in Computer Engineering

Author: Rosa Nuzzo

Tutor: José Flich Cardo

First External Tutor: Alessandro Cilardo

Director Experimental: Rafael Tornero Gavilá

Course 2020-2021

# **Contents**

| Co | ontent  | ts            |                              | ii   |

|----|---------|---------------|------------------------------|------|

| Li | st of I | igures        |                              | iv   |

| Li | st of T | <b>Tables</b> |                              | vi   |

| Li | stings  |               |                              | vii  |

|    | lossar  |               |                              | ix   |

|    |         | •             |                              |      |

| A  | ostrac  | τ             |                              | 1    |

| 1  | Intr    | oduction      | ı                            | 3    |

|    | 1.1     | MANG          | O prototype                  | . 5  |

|    | 1.2     | Goals a       | and Motivations of this Work | . 6  |

|    | 1.3     | Structur      | re of the Document           | . 7  |

| 2  | Bacl    | kground       | and Tools                    | 8    |

|    | 2.1     | FPGA          |                              | . 8  |

|    |         |               | FPGA Architecture            |      |

|    |         |               | Applications                 |      |

|    |         |               | FPGA-based computing engines |      |

|    | 2.2     |               | evel Synthesis               |      |

|    | 2.2     | _             | Flow                         |      |

|    |         |               | Coding                       |      |

|    |         |               | Optimization                 |      |

|    | 2 3     |               | ution                        |      |

|    | 2.5     |               |                              |      |

|    |         | 2.3.1         | Convolution 2D               | . 20 |

|    | 2.4     | Tools .       |                              | . 21 |

|    |         | 2.4.1         | Xilinx Vivado Design Suite   | . 21 |

|    |         | 2.4.2         | proFPGA                      | . 26 |

CONTENTS

|    |       | 2.4.3    | HLS application      | 31 |

|----|-------|----------|----------------------|----|

| 3  | Sing  | le-FPG   | A                    | 39 |

|    | 3.1   | Design   |                      | 39 |

|    |       | 3.1.1    | MMI64 host interface | 40 |

|    |       | 3.1.2    | Convolution IP core  | 45 |

|    |       | 3.1.3    | Memory               | 47 |

|    | 3.2   | Test .   |                      | 49 |

|    |       | 3.2.1    | System ILA           | 49 |

|    |       | 3.2.2    | Programming the FPGA | 50 |

|    |       | 3.2.3    | Testbench            | 51 |

|    |       | 3.2.4    | Run test             | 61 |

|    |       | 3.2.5    | Hardware manager     | 65 |

| 4  | Mul   | ti-FPG   | 4                    | 67 |

|    | 4.1   | Design   |                      | 67 |

|    | 4.2   | Test .   |                      | 68 |

|    |       | 4.2.1    | Inizialize FPGA      | 68 |

|    |       | 4.2.2    | Test bench           | 69 |

|    |       | 4.2.3    | Run test             | 75 |

| 5  | Con   | clusions |                      | 77 |

| D: | hling | raphy    |                      | 78 |

| וע | nnagi | арпу     |                      | 10 |

# **List of Figures**

| 1.1  | MANGO perspectives                                    | 4  |

|------|-------------------------------------------------------|----|

| 1.2  | MANGO prototype with its components                   | 5  |

| 1.3  | Photo of an HN in the MANGO prototype                 | 6  |

| 2.1  | FPGA Architecture                                     | 9  |

| 2.1  | HLS steps                                             | 14 |

|      |                                                       |    |

| 2.3  | Vivado HLS Design Flow                                | 23 |

| 2.4  | Modular hardware                                      | 26 |

| 2.5  | ProFPGA software and libraries                        | 28 |

| 2.6  | MMI64 communication channels                          | 30 |

| 2.7  | Synthesis Summary Report                              | 36 |

| 2.8  | Co-somilation report                                  | 37 |

| 2.9  | Export RTL panel                                      | 38 |

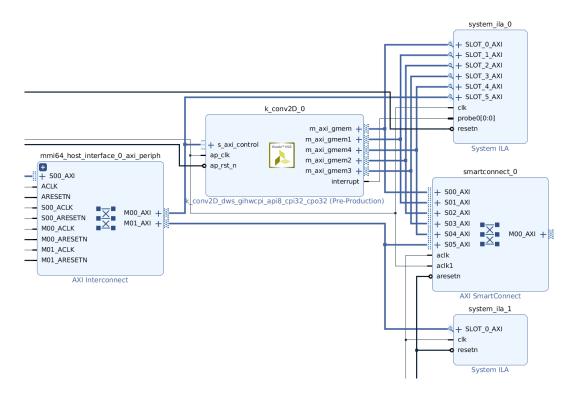

| 3.1  | Vivado design                                         | 40 |

|      |                                                       |    |

| 3.2  | Vivado mmi64 host interface module design             | 41 |

| 3.3  | Profpga_ctrl module                                   | 42 |

| 3.4  | MMI64_axi_master module                               | 43 |

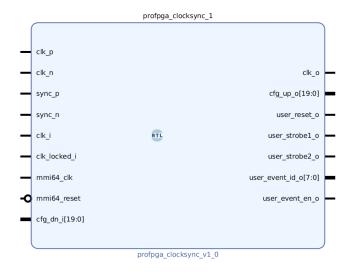

| 3.5  | Profpga_clocksync module                              | 44 |

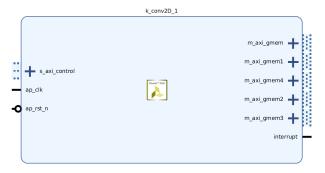

| 3.6  | Convolution IP core                                   | 45 |

| 3.7  | DDR4                                                  | 47 |

| 3.8  | Address editor                                        | 48 |

| 3.9  | Ila core                                              | 50 |

| 3.10 | Scan MMI64 connected device                           | 54 |

| 3.11 | Application execution                                 | 63 |

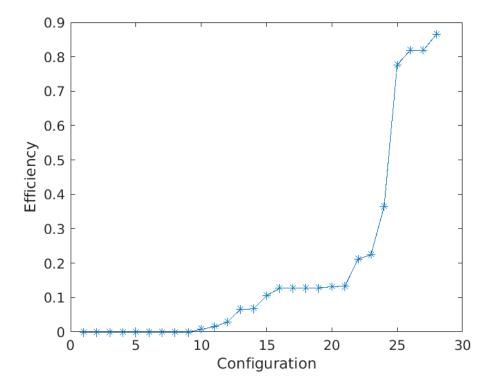

| 3 12 | Relation between the configuration and the efficiency | 64 |

LIST OF FIGURES v

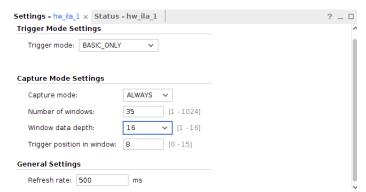

| 3.13 | Ila settings                                  | 65 |

|------|-----------------------------------------------|----|

| 3.14 | Trigget setup                                 | 65 |

| 3.15 | Waveform                                      | 66 |

|      |                                               |    |

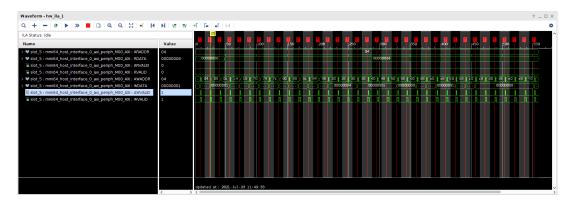

| 4.1  | design multi-FPGA                             | 67 |

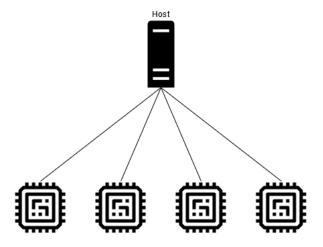

| 4.2  | Configuration mmi64_host_interface multi-FPGA | 68 |

| 4.3  | Scan MMI connected device                     | 70 |

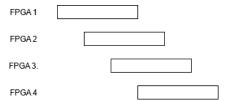

| 4.4  | Pipelined execution                           | 71 |

| 4 5  | Multi-FPGA execution                          | 76 |

# **List of Tables**

| 2.1 | XCKU115 proFPGA Characteristics | 3  |

|-----|---------------------------------|----|

| 3.1 | Input data test                 | 62 |

# Listings

| 2.1  | pragma HLS loop_merge example                                   | 18 |

|------|-----------------------------------------------------------------|----|

| 2.2  | HLS example                                                     | 32 |

| 2.3  | Test bench                                                      | 35 |

| 3.1  | Convolution pragmas to create AXI interface                     | 46 |

| 3.2  | Configuration file                                              | 53 |

| 3.3  | Loading configuration file                                      | 53 |

| 3.4  | Components scanning                                             | 54 |

| 3.5  | Modules identification                                          | 55 |

| 3.6  | Open a connection to AXI Master module domain                   | 55 |

| 3.7  | Enable interrupts                                               | 56 |

| 3.8  | Application flow                                                | 57 |

| 3.9  | Function used to copy data from CPU memory to FPGA memory       | 58 |

| 3.10 | Function to input the necessary data to the convolution IP core | 59 |

| 3.11 | Start FPGA execution                                            | 60 |

| 3.12 | Copy data from FPGA memory to CPU memory                        | 60 |

| 3.13 | Close connection to a MMI64 domain                              | 61 |

| 3.14 | Execution time                                                  | 64 |

| 4.1  | Configuration file multi_fpga                                   | 69 |

| 4.2  | Identify AXI_master module                                      | 70 |

| 4.3  | Buffer FPGA available                                           | 71 |

| 4.4  | Assign configuration to FPGA                                    | 73 |

| 4.5  | Read interrupt and CPU compiling                                | 74 |

| 4.6  | Push in the FPGA buffer                                         | 74 |

| 4.7  | Push from the FPGA buffer                                       | 75 |

| 4.8  | Checking that all executions have finished                      | 75 |

LISTINGS

# **Glossary**

ACM Advanced Clock Management.

API Application Programming Interface.

ASIC Application Specific Integrated Circuit.

AXI Advanced eXtensible Interface.

CDFG Control Data Flow Graph.

CLB Configurable Logic Block.

CPU Central Processing Unit.

DDR Double Data Rate.

DFG Data Flow Graph.

DMBI Device Message Box Interface.

DSP Digital Signal Processor.

ESL Electronic system level.

FIFO First In Frist Out.

FPGA Field Programmable Gate Array.

GAP Group of Parallel Architectures.

GN General purpose Node.

GPU Graphics Processing Units.

Glossary

HDL Hardware Description Language.

HLS High Level Synthesis.

HN Heterogeneous Node.

HPC High Performance Computing.

I/O Input/Output.

ILA Integrated Logic Analyzer.

IP Intellectual Property.

LUT Look Up Table.

MMI Module Message Interface.

MUX Multiplexer.

PCIe Peripheral Component Interconnect Express.

RTL Register Transfer Level.

SDRAM Synchronous Dynamic Random Access Memory.

SSI Small Scale Integration.

SV SystemVerilog.

TCL Tool Command Language.

UPV Universitat Politècnica de València.

VHDL VHSIC Hardware Description Language.

VHSIC Very High Speed Integrated Circuits.

Glossary

WDB Waveform Database.

XDC Xilinx Design Constraints.

# Resumen

El objetivo de este proyecto es permitir el uso de un prototipo multi-FPGA como plataforma de cálculo en la que se puedan ejecutar simultáneamente núcleos FPGA codificados en síntesis de alto nivel. El proyecto se divide en dos pasos:

En el primer paso, se desarrolla el soporte para compilar un kernel HLS desnudo para un prototipo FPGA, generando un núcleo IP. A continuación, se añade el núcleo IP generado con bloques lógicos de comunicación y memoria (DDR, AXI) en un diseño desarrollado para un dispositivo FPGA. Todos los dispositivos incluidos en la FPGA serán accesibles a través de las direcciones de memoria. En el lado del host, éste utiliza el protocolo MMI para lanzar el flujo de bits, escribir en la memoria, lanzar el kernel, leer la memoria y comprobar la corrección. El acceso a la memoria, la sincronización del kernel y el paso de argumentos se realizará a través de direcciones AXI mapeadas en memoria. Por último, se realiza la validación de los pasos anteriores mediante una ejecución satisfactoria.

En el segundo paso, el diseño a nivel de sistema se adapta a una arquitectura multi-FPGA interconectada. Cada FPGA será accesible individual y simultáneamente desde el mismo host, utilizando el protocolo MMI.

Este proyecto permitirá utilizar el prototipo como demostrador de sus capacidades computacionales.

# **Abstract**

This project aims to enable the use of a multi-FPGA prototype as a to compute platform where FPGA kernels coded in High Level Synthesis can be run concurrently. The project is divided into two steps:

In the first step, develop support to compile a bare HLS kernel for one FPGA prototype, generating an IP core. Next, the generated IP core is added with communication and memory logic blocks (DDR, AXI) in a design developed for an FPGA device. All the devices included in the FPGA will be accessible through memory addresses. On the host side, the host uses the MMI protocol to launch the bitstream, write memory, launch the kernel, read memory and check correctness. Memory access, kernel synchronization and argument passing will be performed through memory-mapped AXI addresses. Finally, the validation of the previous steps is performed by mean of a successful run.

In the second step, the system-level design is adapted for an interconnected multi-FPGA architecture. Each FPGA will be individually and simultaneously accessible from the same host, using the MMI protocol.

This project will allow the prototype to be used as a demonstrator of its computational capabilities.

# **CHAPTER 1**

# Introduction

High Performance Computing (HPC) is always pushing technology for the quest of higher performance. However, the end of the era of transistor scaling and frequency increasing makes difficult to provide sufficient performance for emerging large-scale dataset applications, within a reasonable energy budget with current HPC architectures.

To overcome this situation, and to keep increasing performance in an energy efficient manner, heterogeneity has been adopted as key factor to design and implement performance and energy efficient HPC systems. Reconfigurable devices such as Graphics Processing Units (GPUs) and Field Programmable Gate Arrays (FPGAs) have found their niche in these systems. Both GPUs and FPGAs have been proved to provide significant performance gains for HPC applications. In particular, FPGAs have been shown to provide high energy efficiency as well.

In last recent years, new European Projects have been founded by the European Commission with the focus on HPC architectures. Among them, the Group of Parallel Architectures (GAP) of the Technical University of Valencia (UPV) has been granted with the FET-HPC MANGO project [1], which end up in May 2019. The goal of this project consisted of developing and exploring new heterogeneous architectures for future HPC systems. In order to achieve such a goal, a large prototype infrastructure made of FPGAs was deployed and different HPC architectures were proposed, built into a prototype and emulated via the FPGAs of the MANGO infrastructure.

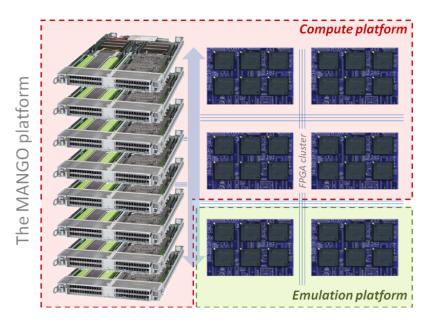

Although MANGO encompasses mainly the exploration of unconventional architectures, the MANGO prototype described in Section 1.1, has been conceived to play a twofold role. This situation is captured by Figure 1.1, highlighting that the same hardware platform can support both a physical compute platform and an emulation platform.

**Figure 1.1:** MANGO perspectives: I) computation and II) emulation. As a computation platform the focus is on bulk performance. As an emulation platform the focus lays on exploration and hardware solution prototyping.

As an emulation platform the focus is on architecture exploration, both at system and compute unit level, and validation of functional aspects. Here, performance numbers are inferred from suitable performance counters and evaluated in relative terms. Unlike, as a compute platform the focus is on bulk performance, thus the goal is to maximize the performance at system level in absolute terms, while keeping energy consumption in a manageable budget. For that reason, this latter type of platforms is being adopted and used massively in new HPC heterogeneous systems.

Enabling a reconfigurable compute platform made of multiple FPGAs involves two main challenges. The first one consists of reducing the programming complexity of these devices, which it can be done by means of programming models like OpenCL [2] or High Level Synthesis (HLS). The second one corresponds to the development of

software/hardware co-design support for managing the hardware, which includes support for efficient communication between the host and the different FPGA devices and tools to transform application kernels into hardware functions that can be uploaded to an FPGA.

# 1.1 MANGO prototype

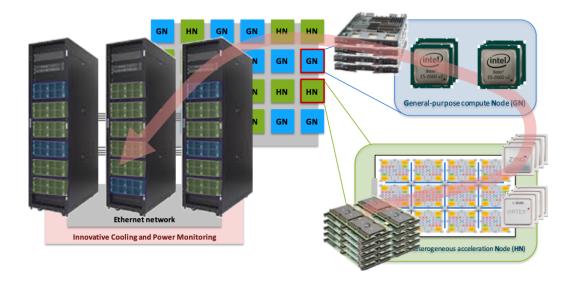

Figure 1.2 shows a complete view of the MANGO prototype with its hardware components. Among them, the most relevant ones for this project are the General purpose Node (GN) and the Heterogeneous Node (HN).

**Figure 1.2:** MANGO prototype with its components: I) General Purpose Node (GN), II) cluster of FPGAs, as known as Heterogeneous Node (HN), III) Ethernet interconnect and IV) Innovative cooling and monitoring subsystem.

The GN consists of a blade made of a high-end Intel Xeon E5 V3, 64 GB of DDR4 memory, 1 TB SSD hard disk and PCI Express (PCIe) connectivity. In this project the GN runs the low-level runtime system to support the managing of the FPGAs.

The HN, also as known as MANGO cluster, consists of 12 FPGAs and 22 GB of DDR3 and DDR4 memory. The cluster is also heterogeneous, since it is composed of different types of FPGAs: Xilinx Kintex Ultrascale (KU115) [3], Xilinx Virtex 7 Series (V2000T) [4], Xilinx Zynq 7000 SoC (Z100) [5] and Intel Stratix 10 (SG280) [6]. Every GN can access two different clusters through PCIe Gen3 x8 lanes, that is a total of 24

FPGAs and 44 GB DDR3/DDR4 memory. The Figure 1.3 shows a photo of how it looks currently. In that Figure, it can be seen the FPGAs and blue cables connecting FPGAs among them.

Figure 1.3: Photo of an HN in the MANGO prototype.

The whole MANGO prototype consisted of a total of 8 GNs and 16 HNs. However, the prototype has been split in different parts and each part has been delivered to a different partner of the MANGO consortium. UPV has received a half of the prototype, that is, 4 GNs and 8 HNs, which means a total of 96 FPGAs and 176 GB of device memory.

Initially, the MANGO prototype has been used completely as an emulation platform, however, there is an effort to adapt this huge system to a compute platform currently. Therefore, it motivates the development of this work as we show in Section 1.2.

#### 1.2 Goals and Motivations of this Work

This master thesis project aims to enable the use of a multiFPGA prototype as a to compute platform where FPGA kernels coded in High Level Synthesis can be run concurrently. This goal fits clearly with the research interests of the GAP group, since it has been granted recently with two new projects where the MANGO prototype is targeted as a computation system. This is the case of the FET-HPC RECIPE [7]

and the ICT DeepHealth project [8]. Thus, as part of the activities of both projects, the MANGO prototype is being adapted from a strictly emulation platform to an actual compute platform.

As mentioned earlier, using a multi-FPGA system as a computational platform involves two challenges. This thesis work contributes to solving one of these challenges. A hardware design has been developed, which allows an optimized kernel to be loaded via the HLS. Moreover, software design to be able to make a host communicate with a set of FPGAs.

### 1.3 Structure of the Document

This thesis is structured in a logical and chronological order with respect to how it was approached in practice.

In Chapter 2 an overview of the technologies and concepts used are given in order to make the reading of the following Chapters clearer. Specifically, it will be explained what an FPGA is and the motivation for choosing this technology. Subsequently, what is High Level Synthesis and convolution (Section 2.2 and 2.3) is explained. This is because, in the design that was modelled in the following chapters, a convolutional IP core optimised through HLS was used. The IP core specifically was developed by the Group of Parallel Architectures (GAP) of UPV. Finally, there is a description of the tools used (Section 2.4).

The actual contribution of this thesis work is described in Chapters 3 and 4. Specifically, in Chapter 3, the various components of the hardware design developed (3.1) using a single FPGA are described in detail. In Section 3.2, the described design is tested using both a hardware approach and using screen printing. Chapter 4, is structured like the previous one but with the difference of using a multi-FPGA system.

Finally, the Chapter 5 presents the final considerations.

## **CHAPTER 2**

# **Background and Tools**

This chapter briefly discusses the fundamentals of the technologies and concepts that were applied in this Project. Section 2.1 describes what an FPGA is, illustrating the architecture and the essential components of which it is constituted (Subsection 2.1.1). It will describe the areas in which FPGAs can be used and the motivation for using them. Specifically, it will be shown the specific FPGA used in this Project (Subsection 2.1.2 and 2.4.2). Section 2.2 describes what HLS is and what the positive aspects of its use might be. In addition, the subsection 2.2.1 shows the HLS execution flow as well as some tricks to pay attention to in order to make the best use of the language and the optimisations that can be done with it (Subsection 2.2.2 and 2.2.3). Finally, a small example will be explained to understand better its working (Subsection 2.4.3). Section 2.3 describes what convolution is and how it works. Specifically, 1-dimensional and 2-dimensional convolution are illustrated. Finally, Section 2.4 discusses what tools were used in this Project.

## **2.1 FPGA**

In industry, one of the key aspects is to reduce development and production time and introduce new products by reducing time-to-market. Also, there must be the lowest financial risk when a new product is introduced to propose and develop new ideas. FPGAs (Field-Programmable Gate Arrays) are a great solution to these time-to-market and risk issues because they provide instant production and prototyping at a meagre cost [9].

The use of FPGAs brings multiple advantages. The programmable nature of an FPGA allows manufacturers to correct errors and send patches or updates after the product has been purchased. Manufacturers also take advantage of this by creating their prototypes in an FPGA to be thoroughly tested and reviewed in the real world before sending the design to the IC foundry for ASIC production. This is because an ASIC can no longer be modified after it comes off the production line. They can also be used to implement causal logic and consequently as a replacement for SSI chips. Finally, a further advantage is the possibility to compile a program not via software but hardware.

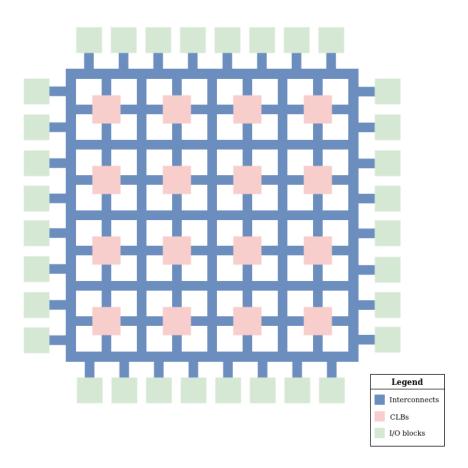

#### 2.1.1. FPGA Architecture

FPGAs are semiconductor devices based on an array of configurable logic blocks (CLBs) connected via programmable interconnects, which routes signals between the CLBs. Input/output (I/O) blocks interface between the FPGA and external devices.

Figure 2.1: FPGA Architecture

**Configurable Logic Block** CLBs are the main components of an FPGA. They are the components that are programmed so that the FPGA can execute any program.

The CLB consists of a Look UP Table (LUT), a MUX (Multiplexer) and D flip flops.

- The LUT implements the combinational logic functions;

- the MUX is used for selection logic,

- moreover, the D flip flop stores the output of the LUT.

**Interconnects** The interconnection is a routing matrix comprising programmable switches and wires. The routing elements connect Input/Output blocks, logic blocks and between one CLB and another CLB.

**Input/Output (I/O) Blocks** Input/output blocks transfer data in and out of the FPGA. The I/O blocks can be configured according to the user's needs, depending on what they want to transmit and receive. They are similar to transceivers but operate at lower speeds and can maintain greater functional flexibility.

#### 2.1.2. Applications

FPGAs can be used in many fields, including:

**Prototyping** The primary use of FPGAs is for prototyping applications. This is because FPGAs have a low cost, both in terms of implementation and time, and therefore provide significant advantages over other more traditional methods of prototyping hardware. Thus, the prototype version can be quickly implemented, and easy modifications can be made when needed.

**Random logic implementation** Random logic implementations are usually implemented with PALs, but if the speed of the circuit is not a problem with the speed of the circuit, it could be very advantageous to use FPGAs.

**Replacing SSI chips for random logic** FPGAs can also replace the SSI chips found in many commercial products, reducing the area used by these chips on circuit boards.

On-site hardware reconfiguration Advantageous use of FPGAs is when it is necessary to replace components in a machine already in operation. A system that contains a certain number of FPGAs connected via programmable interconnection provides a high degree of flexibility in increasing the functional behaviour of the circuits supplied by the board. The type of FPGA most suitable for this type of use contains re-programmable switches.

**FPGA-based computing engines** The exciting use of FPGAs is programming them so that a program is not compiled in software but hardware. This has two advantages:

The first one means that there is no need for instruction fetching as in traditional microprocessors; this is possible because the hardware incorporates the instructions.

The second advantage is due to the high levels of parallelism and consequent increase in speed.

In this Project, FPGAs are used according to the latter application type. Next, this type of application is discussed in more detail in Subsection 2.1.3.

## 2.1.3. FPGA-based computing engines

In this work, the FPGA has been used in the context of computing engines. An FPGA-based computing engine can be seen as a platform that includes a hardware element and can fully implement a software algorithm in part or whole. A programmable platform can consist of a single FPGA or several FPGAs.

On the one hand, FPGA-based computing engines act as a bridge between programmable software systems mounted on traditional microprocessors and customised hardware function-based application-specific platforms. On the other hand, progress in the design tools and technology for FPGA-based platforms permits the quick generation of hardware-accelerated algorithms.

The design for FPGAs can be seen as the design of embedded processors. Simulation tools can be used to debug and verify the functionality of an application before programming the physical device, and there are currently several tools that allow this. Although the tools may be more complex and may take longer to develop, the design can be seen as simple software development rather than hardware development with its respective advantages.

Indeed, in cases where optimisations are required to handle higher resolutions or higher bandwidth signals, these performance gains may be computational or may require entirely new approaches. Implementing a system directly into an FPGA removes or minimises the need for an instruction-based processor. This results in increased performance at a reduced cost compared to using DSP chips and ASICs.

Typically, hardware description languages such as Verilog or VHDL are used to program FPGAs. As will be shown in section 2.2, design tools have been developed that support high-level languages such as C/C++. These tools provide a process whereby an application can be transformed from its high-level description into an optimised low-level representation, which can be adapted according to the platform used. Using the C/C++ language, a software-based approach is a significant advantage because it quickly tries out different solutions. Also, making low-level changes can be very complex, and FPGAs help solves this problem because they can support such applications.

There are advantages and disadvantages to using various types of system processors. For example, although DSPs have low initial use in tools, they need a specific design and programming techniques at the assembly level. On the other hand, FPGAs need more design time and tool skills, mainly if hardware design languages are used as the primary design input method. However, compared to using ASICs, they are a lower-cost, lower-risk solution. Furthermore, if C-based design tools are used with FPGAs, the disadvantages listed above can be significantly reduced.

In conclusion, using FPGAs as a computing engine allows engineers to implement applications, or prototype applications, more quickly without the need to understand all the intricate details of the target, and to perform optimisations, while at the same time providing low-level features in order to extract the highest possible performance[10].

## 2.2 High Level Synthesis

As the complexity of applications has increased, the search has begun for new tools to work at a high level, improving performance over register transfer level (RTL). High-Level Synthesis (HLS) comes to the rescue in this regard. HLS makes it possible to synthesise high-level specifications and transform them into low-level RTL specifications; it also makes it possible to optimise the Synthesis, considering the performance, power, and cost requirements of a particular system [11].

HLS allows designers to specify design functionality in a high-level programming language and then generate a system-specific IP core. Unlike RTL IP, which has a static microarchitecture, behavioural IP can be adapted to different deployment technologies or system requirements. This reduces the time spent searching for the best compromise between area, power, and performance. Modern FPGAs incorporate many IP components, such as arithmetic function units, memories, processors, and system buses. These predefined blocks can be modelled in advance for each FPGA platform. In addition, FPGAs are often used for systems where time-to-market is critical. Thus, designers accept an increase in performance, power, or cost to reduce design time. With modern HLS tools, the designer makes this trade-off, allowing a significant reduction in design time. Finally, FPGAs are being used in reconfigurable computing platforms to accelerate High-Performance Computing (HPC) applications. However, most developers are not familiar with RTL programming in VHDL or Verilog, so providing a highly automated C/C++ to FPGA compile/synthesise flow is essential. [12].

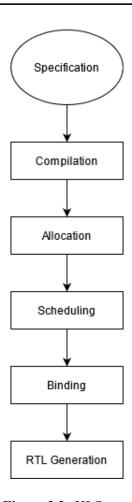

#### **2.2.1.** Flow

The figure 2.2, shows the creation flow of an RTL. The development is divided into 5 phases, starting with specifications written in a high-level language and finally generating a module written in a low-level language and ready to be imported into the desired platform. The phases are explained below.

Figure 2.2: HLS steps

**Compilation** The first step is to transform the specification into a formal representation.

In this phase, optimisations can be made, such as eliminating dead-code or eliminating false dependencies. The output of the compilation shows the dependencies of the data. This formal representation consists of creating a DFG in which nodes represent operations and arcs represent input, output, and temporary variables. The DFG model can be extended with a CDFG, in which nodes represent basic blocks. A CDFG looks at the data dependencies within the basic blocks. The positive side of using CDFGs is that they can represent cycles with unlimited iterations. The problem is that only parallelism within basic blocks is considered. In order to consider the parallelism between the basic blocks, further analysis must be performed.

**Allocation** The allocation defines the type and number of hardware resources (e.g., functional units or connectivity components) required to meet design constraints. Some

components may be added during scheduling and binding activities. The components are selected from the component library RTL.

**Scheduling** The specifications' operations may terminate within one clock cycle or multiple clock cycles, depending on the functional units to which they have been mapped. Operations can be concatenated so that the output of one operation goes into the input of the next operation. Operations can also be executed in parallel, but only if they have no data dependencies.

**Binding** All operations in the specification model must be associated with one functional unit; the binding algorithm must optimise the choice when associated with more than one functional unit. Storage and functional unit binding depend on connectivity binding, which requires that the transfer from one component to another is done with a bus or multiplexer. Ideally, high-level Synthesis considers delays due to connections so that subsequent phases can best optimise the design. An alternative way to proceed is to specify the entire architecture during the allocation phase to use initial optimisations in the binding and scheduling phase.

**Generation** The last step is to generate a model RTL by considering the design choices made in the previous allocation, scheduling, and critical steps.

## **2.2.2.** Coding

As already mentioned (section 2.2), the HLS allows the programmer to use C/C++ to generate components written in a low-level language. Various precautions need to be taken to ensure that there are no errors or malfunctions.

**System Calls** System-calls are tasks executed in the contest of the operating system that hosts the C/C++ program, as a consequence they cannot be synthetized.

**Dynamic Memory Usage** Memory allocation dedicated system-calls, such as malloc(), use resources held by the operating system's memory and are created and released at runtime. Thus, to perform Synthesis, the Project must be completely autonomous, specifying all the resources required.

**Pointer Limitations** In the High Level Synthesis workflow general pointers (i.e. function pointers) casting is not supported, however native C/C++ types can always be cast between each other. Furthermore, arrays of pointers are also supported, given that each pointer points to a scalar or array of scalars. However, arrays of pointers cannot point to other pointers.

**Recursive Functions** Synthesis of functions that form unlimited recursion is not permitted. Moreover, queued recursion is not supported, in case of countless function calls. Templates adopted in C++ programming language tail recursion is often used, these templates can be synthetized in tail recursion designs.

## 2.2.3. Optimization

With HLS, optimizations can be made and used to produce a microarchitecture that can obtain desirable results in terms of area and performance goals. Optimisation directives can be added directly into the source code as compiler pragmas using various HLS pragmas or using the TCL set\_directive commands to apply the optimisation directives in a TCL script by a solution during compilation.

Several optimisation directives can be applied to the Project:

**Throughput** Presents the main optimisations in the order in which they are typically used: pipelining tasks to improve performance, improving the flow of data between, and optimising structures to improve problems that may limit performance.

**Latency** Uses latency constraint techniques and removal of transitions to reduce the number of clock cycles required for completion. To reduce the number of clock cycles required for completion.

**Area** Focuses on how operations are implemented - controlling the number of operations and how these operations are implemented in the hardware is the primary technique for improving the area.

**Logic** Discusses optimisations concerning the implementation of RTL.

#### 2.2.3.1. Optimization pragma example

A design can be optimised by reducing the clock numbers of an operation, thus optimising the latency. The HLS provides many pragmas for this purpose. An example of this type of optimisation is loop merging. The type of pragma that is useful for this application is the **pragma HLS loop merge**.

Information about other pragmas can be found in the official Xilinx documentation [13], the pragmas are constantly evolving, so it is essential to use the proper documentation according to the tool used.

#### pragma HLS loop merge

#pragma HLS loop merge force

Merge consecutive loops into a single loop to reduce overall latency, increase sharing, and improve logic optimisation. Loop Merge:

- Reduces the number of clock cycles required in the RTL to transition between loopbody

- Allows loops to be implemented in parallel (if possible).

The LOOP\_MERGE pragma will attempt to merge all loops within the scope in which it is placed. For example, if a pragma LOOP\_MERGE is applied in the loop's body, the

2.3 Convolution 18

Xilinx HLS tool will apply the pragma to any sub-loop within the loop but not to the loop itself. All loops inside, but not themselves, are merged by using the force option. The rules for joining loops are:

- If the loop bounds are variables, they must have the same value (number of iterations).

- If the loop bounds are constant, the maximum value of the constant is used as the boundary of the merged loop.

- Loops with variable limits and constant limits cannot be merged.

- Code between loops to be merged cannot have side effects. Multiple executions of this code should generate the same results (a=b is allowed, a=a+1 is not).

- Loops cannot be merged when they contain FIFO reads. Merging changes the order of the reads. Reads from a FIFO or FIFO interface must always be in sequence.

An example of the use of this pragma is illustrated in the following listing 2.1.

```

void foo (num_samples, ...) {

#pragma HLS loop_merge

int i;

...

loop_1: for(i=0;i < num_samples;i++) {

...

loop_2: for(i=0;i < num_samples;i++) {

#pragma HLS loop_merge force

...</pre>

```

Listing 2.1: pragma HLS loop merge example

In the example, the two loops will be merged into a single loop. Moreover, all the engaged loops are merged in the second loop because the force option was used.

#### 2.3 Convolution

Convolution is a technique widely used in signal processing, image processing and other fields of engineering/science. In image processing, convolution can be used to apply a

2.3 Convolution 19

filter to an image. Convolution allows various types of filters to be used to extract different aspects and characteristics from an image. Similarly, in Convolutional Neural Network, different features are extracted using filters whose weights are learned automatically during training.

There are some advantages to doing convolution, such as sharing weights and invariant translation. Convolution also takes into account the spatial relationship of pixels. These could be very useful, especially in many computer vision tasks, as these tasks often involve identifying objects in which specific components have a specific spatial relation to other components.

The following Section shows an example to understand better how convolution works.

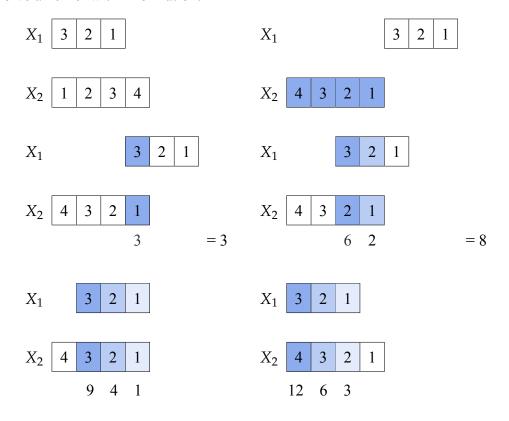

#### **2.3.0.1.** Convolution 1D

Convolution is executed by multiplying and accumulating the instantaneous values of superimposed samples corresponding to two input signals, inverted.

To better understand the convolution, below is an example. Given two signals,  $X_1[n]$  and  $X_2[n]$ , where  $X_1[n]$  is called the kernel and  $X_2[n]$  are the inputs, what you want to do is convolve a kernel with information.

2.3 Convolution 20

$$\begin{bmatrix} 3 & 2 & 1 \end{bmatrix} * \begin{bmatrix} 1 & 2 & 3 & 4 \end{bmatrix} = \begin{bmatrix} 3 & 8 & 14 & 20 \end{bmatrix}$$

- 1. The first step of the convolution is to flip and translate the vector  $X_2[n]$  to the left;

- 2. The second step is to multiply the columns and sum the products;

- 3. The third step and translate the vector  $X_2$  and repeat the second step;

- 4. Finally, the convolution will be given by the vector containing the previous sumsproducts.

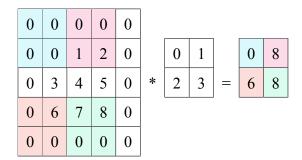

#### 2.3.1. Convolution 2D

The definition of 1D convolution is also applicable for 2D convolution save that one of the inputs is inverted twice.

This type of operation is widely used in digital image processing, where the 2D matrix representing the image will be convolved with a relatively more minor matrix called the 2D kernel.

#### **2.3.1.1.** Padding

One problem that can arise when performing convolution is losing pixels at the perimeter of the image. Considering that small kernels are used, this can lead to the loss of a few pixels, but when many convolutional layers are applied, the loss of pixels is more significant. One solution to this problem is padding, i.e. adding extra pixels around the perimeter of the image to enlarge the image. Usually, the extra pixels have a value of zero. In some cases, it wants to have the same height and width in the output as in the input, and padding makes this more accessible because it has more control over the construction of the mesh.

An example of padding is shown below:

| 0 | 0 | 0 | 0 | 0 |   |   |   |   | 0  | 3  | 8  | 4  |

|---|---|---|---|---|---|---|---|---|----|----|----|----|

| 0 | 0 | 1 | 2 | 0 |   | 0 | 1 |   | 9  | 19 | 25 | 10 |

| 0 | 3 | 4 | 5 | 0 | * | 2 | 3 | = | 21 | 37 | 43 | 16 |

| 0 | 6 | 7 | 8 | 0 |   |   |   |   | 6  | 7  | 8  | 0  |

| 0 | 0 | 0 | 0 | 0 |   |   |   |   |    |    |    |    |

#### 2.3.1.2. Stride

When calculating the convolution, the starting point is the first matrix in the top left-hand corner and is translated, to the right and down, one step at a time. For example, in some cases, to improve computational efficiency, the translation is not done one step at a time but n steps. This jump is called Stride. Stride can reduce the resolution of the output, for example, by reducing the height and width of the output to only  $\frac{1}{n}$  (with n > 1) of the height and width of the input.

Stride along with padding can be used to adjust the dimension of the data effectively.

#### 2.4 Tools

#### 2.4.1. Xilinx Vivado Design Suite

Vivado Design Suite is a software suite produced by Xilinx for HDL design synthesis and analysis, includes electronic system level (ESL) design tools for synthesising and verifying C-based algorithmic IP, standards-based packaging of both algorithmic IP and RTL for re-use, standards-based IP stitching and system integration of all types of system building blocks, and block and system verification.

Vivado IDE offer [14]:

• Register transfer level (RTL) design in VHDL, Verilog, and SystemVerilog

- Intellectual property (IP) integration for cores

- Behavioral, functional, and timing simulation with Vivado simulator

- Vivado synthesis

- Vivado implementation for place and route

- Vivado serial I/O and logic analyzer for debugging

- Vivado power analysis

- SDC-based Xilinx design constraints (XDC) for timing constraints entry

- Static timing analysis

- High-level floorplanning

- Detailed placement and routing modification

- Bitstream generation

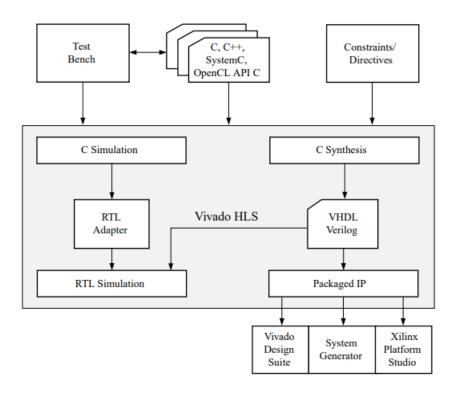

#### 2.4.1.1. Vivado High-Level Synthesis

Xilinx Vivado HLS belongs to the tools available in the Xilinx Vivado Design Suite. The tool synthesizes functions written in C/C++ into an IP core that can be integrated into a hardware system [15].

Figure 2.3: Vivado HLS Design Flow

The Vivado HLS Design flow is illustrated in the figure 2.3.

When creating a new project, the tool allows 4 types of files to be added to the project:

- C function written in C, C++, SystemC, or an OpenCL API C kernel.

These files contain the functions that are to be synthesised. These are the files that contain the code written at a high level that will later be converted.

- **Constraints**: Contain information about the clocks, such as period and uncertainty. They also have information about the target.

If not specified, the clock has an uncertainty of 12.5%.

- **Directives**: Directives are optional and direct the synthesis process to implement a specific behaviour or optimization.

- C test bench:To verify the output of RTL, Vivado uses the C/RTL Cosimulation. This step is performed before synthesis.

The C **Simulation** is made for the validation of the C algorithm that is an important part of the High-Level Synthesis (HLS) process. To ensure that the C algorithm performs the correct operation, a C test bench is used to confirm that the results are correct.

The Vivado simulator is a Hardware Description Language (HDL) event-driven simulator that supports functional and timing simulations for VHDL, Verilog, SystemVerilog (SV), and mixed VHDL/Verilog or VHDL/SV designs.

The Vivado simulator saves the simulation results of the objects (VHDL signals, or Verilog reg or wire) being traced to the Waveform Database (WDB) file.

**Synthesis** is the process of transforming an RTL-specified design into a gate-level representation. Vivado synthesis is timing-driven and optimised for memory usage and performance.

Interface synthesis is the process of adding RTL ports to the C design. In addition to adding the physical ports to the RTL design, interface synthesis includes an associated I/O protocol, allowing the data transfer through the port to be synchronised automatically and optimally with the internal logic.

When Synthesis completes, Vivado HLS generates a Synthesis Summary report for the top-level function. In this file, it is possible to find information on the resources used, times, latency.

A crucial part of creating high-quality RTL designs using High-Level Synthesis has the ability to apply optimisations to the C code. High-Level Synthesis always tries to minimise the latency of loops and functions. To achieve this, within the loops and functions, it tries to execute as many operations as possible in parallel. At the level of functions, High-Level Synthesis always tries to execute functions in parallel. However, after analysis, it is possible to change C/C++ code to optimise the performance of the function. Optimisations can be made by adding optimisation directives directly into the source code as compiler pragmas, using various HLS PRAGMAS.

This is often an iterative process, requiring multiple steps and multiple optimisations to achieve the desired results. Solutions offer a convenient way to configure the tool, add directives to the function to improve the results, and preserve those results to compare with other solutions.

The Vivado synthesis also generates a RTL implementation file in HDL (Hardware Description Language) format. The RTL is available in two industry-standard formats: VHDL and Verilog.

The High-Level Synthesis tool automates the process of **C/RTL CoSimulation**. To perform RTL verification, the tool uses both the RTL output from High-Level Synthesis (Verilog or VHDL) and the C test bench.

As described before, the test bench verifies output from the top-level function for Synthesis and returns zero to the primary () function of the test bench if the output is correct.

The RTL simulation in Vivado uses the same inputs as in the C simulation and synthesis to check the correctness of the results. If the simulation ends with a non-zero value, then the results are not correct.

The C/RTL verification process consists of three phases:

- The C simulation is executed, and the inputs to the top-level function, or the Design-Under-Test (DUT), are saved as "input vectors."

- The "input vectors" are used in an RTL simulation using the RTL created by Vivado HLS in Vivado simulator. The outputs from the RTL, or simulation results, are saved as "output vectors."

- The "output vectors" from the RTL simulation is returned to the C test bench's primary () function to verify the results are correct. The C test bench verifies the results, in some cases, by comparing them to known good results.

After the end of the co-simulation, the report showing the latency values is displayed. The final step in the Vivado HLS flow is to **export the RTL**L project in so that it can be imported on other platforms. The RTL component can be packaged in various formats:

- Vivado IP: The IP is exported as a ZIP file added to the Vivado IP catalogue.

- Vivado Kernel: The XO file output can be used for linking by the Vivado compiler in the application acceleration development flow.

- Synthesised Checkpoint: This option creates Vivado checkpoint files which can be added directly into a design in the Vivado Design Suite.

- Vivado IP for System Generator: This option creates IP for use with the Vivado edition of System Generator for DSP.

## 2.4.2. proFPGA

The proFPGA product family meets the highest requirements in the areas of FPGA boards and FPGA-based prototyping. With proFPGA products, it is possible to get maximum flexibility in building any hardware configuration, reconfigurable and adaptable to multiple applications. In this work was used the Kintex UltraScale FPGA (section 2.4.2.4).

PRO DESIGNs FPGA prototyping systems offer scalable, high-performance Single and Multi-FPGA solutions, which can be easily adapted and expanded by additional proFPGA modules with the latest FPGAs and extension boards equipped with interconnects, interfaces, or memories. The ProFPGA prototyping system is a set of modular blocks, which allows users of this system to customise the various solutions to best suit the project specifications [16].

The hardware and software layers of the proFPGA prototyping system are explained below.

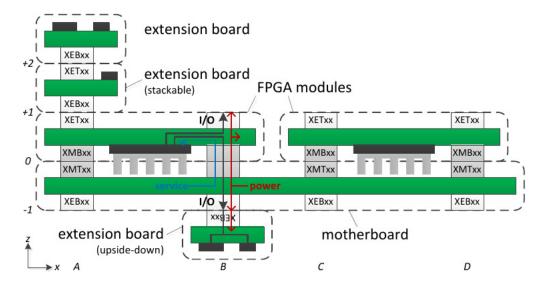

#### 2.4.2.1. Hardware Level

The hardware level of the proFPGA prototyping system is divided into several modular units, the main ones being (figure 2.4):

Figure 2.4: Modular hardware

**Motherboards** Motherboards are the heart of FPGA; they provide clock infrastructure, power supply, MMI-64 communication for multiple FPGA modules, I2C-based system management, and mechanical fixation. Motherboards have two types of connectors, one for the extension boards (carrying user I/O, power) on the bottom side and the other for the FPGA modules (carrying user I/O, power, service) on the top side. It also provides a transparent connection between the extension boards on the bottom side and the FPGA module on the top side; this is due to the direct link of the user I/O pins of the connectors on the top and bottom sides.

**FPGA Modules** The FPGA modules offer eight connectors connected to the extension sites and have 4 FPGA module connectors (user I/O, power, service) and 4 extension board connectors (user I/O, power). Each module can access the MMI-64 communication through the motherboard. Moreover, since the motherboard provides a transparent connection between the extension board and the FPGA module, each FPGA module can access up to 8 extension boards.

**Extension Boards** Extension boards provide hardware functions within FPGA modules, such as debug access, SDRAM memory, and user PCIe connection. In order to have exclusive access to the extension board, an extension board occupies one or more of the connectors of an FPGA module, and other extension boards can be added by mapping the non-used I/O pins of the FPGA module to a connector on the top side.

**Interconnects** Interconnects are used to connect the I/O pins of several FPGA modules and are unique extension boards. Interconnects are to be found in cables and boards and connect two or more extension sites. Finally, they can be point-to-point (e.g., all 2-way interconnection boards and cables) or broadcast (e.g., the 4-way interconnection board).

**System Extension Boards** System functionality can be expanded by special hardware, like the motherboard's PCIe adapter board or a motherboard-to-motherboard connector cable. This hardware uses designated connectors on the motherboard.

#### 2.4.2.2. Software Level

The Software layer of proFPGA provides various tools:

- profpga\_run: a command-line tool to turn on turn off and configure the system

- profpga\_builder: GUI to create configuration setups of the board and to execute run-time accesses the system

- profpga\_brdgen: a command-line tool to generate various VHDL/Verilog top-level files, constraint files, board description files, and a project-based self-test to test FPGA interconnects at speed

- profpga\_selftest2: a command-line tool that performs the project-based self-test on the hardware

- profpga\_freq: a command-line tool to determine proFPGA clock settings to generate a specific clock frequency or achieve the desired data rate with mux/demux proFPGA modules.

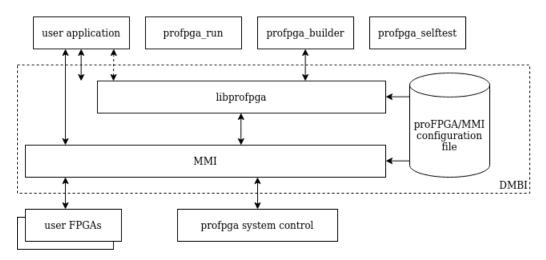

Figure 2.5: ProFPGA software and libraries

There are two parts to communicate with the system:

• MMI is a transport mechanism between the proFPGA system and a Host-PC. It is used for user project communication and system control and consists of extracting the different communication modes such as PCIe, Ethernet, and USB.

• libprofpga provides the tools to configure and control the system and to observe status information. libprofpga uses MMI to communicate with the hardware.

Both parts together form the proFPGA communication package, which is called DMBI.

#### 2.4.2.3. MMI64

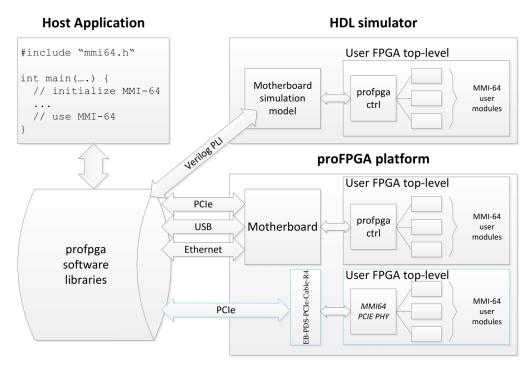

Communication between the proFPGA system and a Host-PC is achieved through a series of components [17].

**Host Application** The host application controls the communication. It will send MMI64 messages downstream and request MMI64 messages upstream.

**Software Libraries** Software libraries are pre-compiled libraries from Pro Design that implement API functions. They are used to communicate with the proFPGA system.

**proFPGA Motherboard** In order to communicate with the user application, the proFPGA motherboard provides four paths:

- PCIe

- Ethernet

- USB cable

- previous motherboard (for systems with multiple motherboards)

**proFPGA** User FPGA Control Unit Pro Design provides the proFPGA control unit, "profpga ctrl", to have MMI64 communication.

The control unit has the following functions:

• decode the communication pins into MMI64 signals

- translate the clock/sync from the LVDS pins to the internal clock and reset

- configuration access for Advanced Clock Management (ACM) on clock/sync #1 to

7

- MMI64 communication interface for the user project inside the FPGA.

The control unit also provides a routing structure for MMI64 messages:

- MMI64 communication to user project

- Service

**MMI64 PCIe PHY** Pro Design provides another module, "mmi64\_p\_pcie", which allows, through an additional extension and by instantiating MMI64 PCIe PHY, not to use the motherboard. Usually, it is chosen to use this method when more data throughput is necessary than the motherboard can provide.

Figure 2.6: MMI64 communication channels

#### 2.4.2.4. FPGA Kintex UltraScale

The XCKU115 proFPGA FPGA module is the logical heart of the scalable and modular multi FPGA proFPGA solution. This module is used by those who need a scalable

and more flexible high-performance ASIC Prototyping solution for initial software development and real-time system testing. The XCKU115 proFPGA FPGA module, which works only in combination with a proFPGA one, duo, or quad motherboard. Offers its latest Kintex UltraScale FPGA technology a maximum capacity of up to 7.9 M ASIC ports and 5520 DSP slices in a single FPGA. It is designed to achieve maximum performance in combination with its high-speed connectors. The module offers six extension sites up to 585 user I/Os for daughter cards (e.g., memory cards, interface cards), interconnect cables, or customer-specific application cards. In addition to the standard I/Os, the module also provides 52 high-speed serial transceivers (56 x GTH) operating at up to 16.375 Gbps for high-speed interfaces such as PCIe Gen4. All six extension sites offer individually adjustable and stepped voltage regions from 1.2V up to 1.8V.

| Capacity                    | Up to 7.9 M ASIC gates                                                             |

|-----------------------------|------------------------------------------------------------------------------------|

| FPGA-internal memory        | 75 Mbit                                                                            |

| DSP Slices                  | 5520                                                                               |

| Extension sites             | Up to 6 Extension sites with high speed connectors                                 |

| I/O resources               | Overall up to 585 signals for I/O and inter FPGA connection                        |

|                             | 585 free I/Os per FPGA Module (Virtex® XCVU7P FPGA)                                |

|                             | 3x153 I/Os and 1x76 I/Os to top side connectors                                    |

|                             | 2x25 I/Os to bottom side connectors                                                |

|                             | Single-ended or differential                                                       |

| High Speed I/O transceivers | 56 high speed transceivers (GTH) running up to 12.5/16.375 (speedgrade 1/2/3) Gbps |

| FPGAs interconnections      | Flexible via high-speed interconnection boards or cables                           |

| Voltage regions             | 6 individually adjustable voltage regions per FPGA Module                          |

|                             | Stepless from 1.0V up to 1.8V on 6 extension sites                                 |

|                             | Automated detection of daughter card and adjustment of right voltage               |

| Configuration               | With proFPGA uno, duo or quad Motherboard via Ethernet, USB, PCIe                  |

Table 2.1: XCKU115 proFPGA Characteristics

# 2.4.3. HLS application

This section explains and demonstrates all steps in transforming C/C++ code to an RTL implementation using High-Level Synthesis. The Section shows how to create an initial RTL implementation and then transform it using optimisation directives without changing the C code.

In the Xilinx application acceleration flow, the Vivado HLS tool automates most of the code changes required to implement and optimise C/C++ code in programmable logic and

achieve low latency and high throughput. Inference of the pragmas needed to produce the correct interface to function arguments and pipeline loops and functions within the code is the foundation of Vivado HLS in the application acceleration flow. Vivado HLS also supports code customisation to implement different interface standards or specific optimisations to achieve design goals.

The following is the vivado HLS design flow:

- 1. Compile, simulate and debug the C/C++ algorithm.

- 2. Synthesise the C algorithm and view reports to analyse and optimise the design.

- 3. Verify the RTL implementation using RTL co-simulation.

- 4. Export the RTL implementation to an RTL IP.

#### 2.4.3.1. Compile, simulate, and debug

The following listing 2.2 is represented as a simple example written in C/C++ and optimised using the HLS INTERFACE pragma.

```

void sum_value(volatile int *a){

#pragma HLS INTERFACE s_axilite port=return bundle=control

#pragma HLS INTERFACE m_axi depth=50 port=a offset=slave

#pragma HLS INTERFACE s_axilite port=a bundle=control

int i;

int buff[50];

memcpy(buff,(const int*)a,50*sizeof(int));

10

for (i=0; i < 50; i++)

11

buff[i] = buff[i] + 100;

}

14

memcpy((int *)a, buff,50*sizeof(int));

15

16

```

Listing 2.2: HLS example

This example takes a pointer (a) as input; the pointer points to a vector with a maximum size of 50 integers. The vector is copied via the memcpy function into a local vector (buff[i]). The memcpy requires a local buffer to store the results of the memory transaction

and creates burst access to memory. Sequentially is added a constant to all the values in the vector, and finally, the modified buffer is reassigned to the pointer used as input. In

this case, multiple calls of memcpy cannot be pipelined and will be scheduled.

In order to specify the I/O ports as master/slave axi buses, the HLS INTERFACE pragma

was used.

HLS INTERFACE pragma specifies how RTL ports are created from the function

definition during interface synthesis. The ports in the RTL implementation are derived

from the following:

• Block-level I/O protocols: Provide signals to control when the function starts

operation and indicate when function operation ends, is idle and ready for new

inputs.

• Function arguments: Each function argument can be specified to have its port-level

(I/O) interface protocol, such as a valid handshake, or acknowledge handshake.

Port-level interface protocols are created for each argument in the top-level function,

and the function return if the function returns a value. The default I/O protocol

created depends on the type of C argument. After the block-level protocol has been

used to initiate block operation, port-level I/O protocols will be used to route data

input and output from the block.

• Global variables accessed by the top-level function, and defined outside its scope: If

a global variable is accessed, all read and write operations are local to the function,

the resource is created in the RTL design. The RTL requires no I/O port. If the

global variable is supposed to be an external origin or destination, simply define the

interface in a way analogous to the arguments of standard functions.

**Sintax**

#pragma HLS interface <mode> port=<name> bundle=<string> depth=<int>

offset=<string>

Where:

<mode>: Specifies the interface protocol mode for function arguments, global variables used by the function, or the block-level control protocols. The mode that can be specified is:

- s\_axilite: Implements all ports as an AXI-Lite interface. the HLS facility generates a set of C driver files as part of the RTL export process.

- m\_axi: Ports are implemented as AXI interfaces. To specify 32-bit (default) or

64-bit address ports and control any address offsets, use the config\_interface command.

- port=<name>: Specifies the name of the function argument, function return, or global variable to which the INTERFACE pragma applies.

- bundle=<string>: Groups function arguments into AXI interface ports. The HLS tool groups all function arguments specified as an AXI-Lite (s\_axilite) interface into a single AXI-Lite port. Similarly, all function arguments specified as an AXI (m\_axi) interface are grouped into a single AXI port. This option explicitly groups all interface ports with the same bundle=<string> into the same AXI interface port and names the RTL port's value specified by <string>.

- depth=<int>: This setting specifies the highest number of samples that the test bench must elaborate on. This set-up specifies the maximum dimension of the FIFO required in the verification adapter the HLS tool creates for RTL co-simulation.

- offset=<string>: Controls the address offset in AXI-Lite (s\_axilite) and AXI (m\_axi) interfaces.

- For the saxilite interface, <string> provides the registration map address.

- For the m axi interface, <string> one of the following values is specified:

- \* direct: Generate a scalar input offset port.

- \* slave: Generate an offset port and automatically map it to an AXI-Lite slave interface.

- \* off: Do not generate an offset port.

C Simulation The first step in an HLS project is to confirm that the C code is correct. This process is called C Validation or C Simulation. This can be done with: **Project** > **Run C Simulation**, to compile and execute the C design.

The test bench 2.3 includes a main() top-level function. The main instantiates two vectors, one of which is used as input to the function that needs to be synthesised and another to execute the software version of the hardware function. At the end of the program, the two vectors are compared to validate the function.

```

void sum_value(volatile int *a);

int main()

int i;

int A[50];

int B[50];

printf("HLS AXI-Stream no side-channel data example\n");

10

// Put data into A

for (i=0; i < 50; i++)

A[i] = i;

13

}

14

// Call the hardware function

15

sum_value(A);

16

17

//Run a software version of the hardware function to validate results

18

for (i=0; i < 50; i++)

19

B[i] = i + 100;

20

23

//Compare results

for (i=0; i < 50; i++)

24

if(B[i] != A[i]) {

25

printf("i = %d A = %d B= %d n", i, A[i], B[i]);

26

printf("ERROR HW and SW results mismatch\n");

27

return 1;

28

}

29

}

30

printf("Success HW and SW results match\n");

return 0;

32

33 }

```

Listing 2.3: Test bench

#### **2.4.3.2.** Synthesize

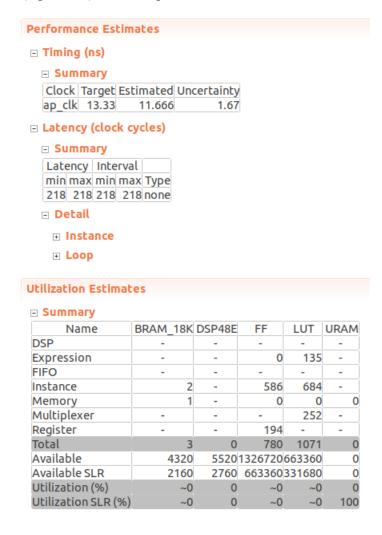

The second step consists of synthesising the C design into an RTL design and reviewing the synthesis report to see the program's performance. **Solution** > **Run C Synthesis** > **Active Solution**. When Synthesis completes, the Xilinx tool generates a Synthesis Summary report (figure 2.7) for the top-level function.

Figure 2.7: Synthesis Summary Report

In the Performance Estimates pane, shown in Figure 2.7, it is possible to see the clock period is set to 13.33 ns. Xilinx tool targets a clock period of Clock Target minus Clock Uncertainty (13.33-1.67 = 11.66 ns in this case). The clock uncertainty ensures there is some timing margin available for them (at this stage) unknown net delays due to place and routing. The estimated clock period (worst-case delay) is 11.666 ns, meeting the 11.66 ns timing requirement.

Another parameter seen in the summary is that the design has a latency of 128 cycles; it takes 128 clocks to output the results, and the next set of inputs is read after 128 clocks. The design is not pipelined. The subsequent execution of this function (or next transaction) can only start when the current transaction completes.

The Utilisation Estimates shows that the design uses 3 BRAM\_18K, 780 flip-flops and 1071 LUTs. At this stage, the device resource numbers are estimates because RTL synthesis might perform additional optimisations, and these figures might change after RTL synthesis.

#### 2.4.3.3. Verify the RTL implementation

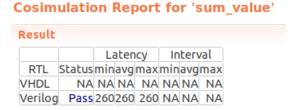

High-Level Synthesis can re-use the C test bench to verify the RTL using simulation. **Solution** > **Run** C/RTL CoSimulation.

If the C test bench returns a non-zero value, the Xilinx tool reports that the simulation failed. After simulation, the Cosimulation Report shows the pass or fail status and the measured statistics on latency (figure 2.8).

**Figure 2.8:** Co-somilation report

#### **2.4.3.4.** Export the RTL implementation

The final step in the High-Level Synthesis flow is to package the design as an IP block with other tools like the Vivado Design Suite. **Solution** > **Export RTL**.

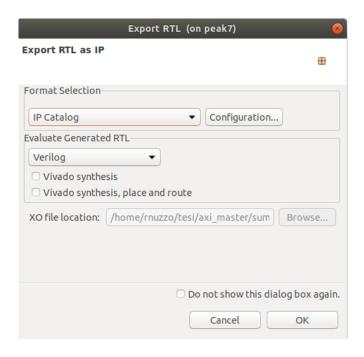

Figure 2.9: Export RTL panel

The RTL design can be packaged into different output formats. In this case, as shown in Figure 2.9, The IP is exported as a ZIP file that can be added to the Vivado IP catalogue. In addition to selecting the IP format on the Export RTL dialogue box, it is also possible to change the IP configuration. One important thing in the configuration options is to choose the IP name shown when adding the IP to the Vivado catalogue.

# **CHAPTER 3**

# Single-FPGA

The goal of this thesis work is to verify the possibility of using multiFPGA prototypes as a computing platform, discussed in the Section 2.1.3, where the FPGA kernels are coded in HLS (Section 2.2). In order to simplify the work, the project has been divided into two parts, the first part where only one FPGA is used and a second part, which will be addressed in the next chapter, where the project will be expanded to more FPGAs.

In this chapter, the design (Section 3.1) of the project using a single FPGA is explained, going into detail about the components of which it is composed. Once an overview of the design is done, Section 3.2 explains how the design was tested and what techniques were used.

# 3.1 Design

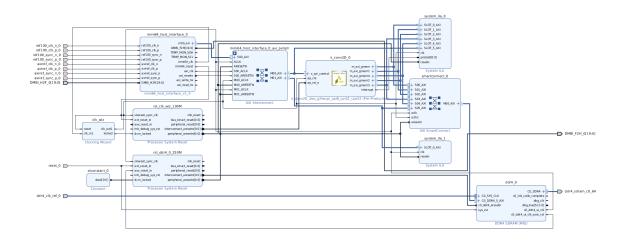

Figure 3.1 shows the design developed for the single FPGA case. The most important components of the design are as follows:

- mmi64 host interface module;

- convolution IP core;

- SDRAM;

- System ILA core.

Figure 3.1: Vivado design

Using the different interfaces illustrated in 2.6, the host can communicate with the System through DMBI (Device Message Box Interface). In this case, the interface used is the proFPGA PCIe. So the user, thanks to this interface, communicates the desired inputs to the MMI64 host interface module, designed precisely with the function of acting as a bridge between the host and the FPGA. In essence, the host, through the module MMI64 host interface, can pass input values to the IP core of the convolution to perform the convolution and can communicate directly with the memory (DDR4) to make the appropriate settings, such as enable/disable interrupts or read the data saved by the IP core. In the design, there is also another module, system ILA, used to debug the System. In the following sections, the design will be explained in more detail.

#### 3.1.1. MMI64 host interface

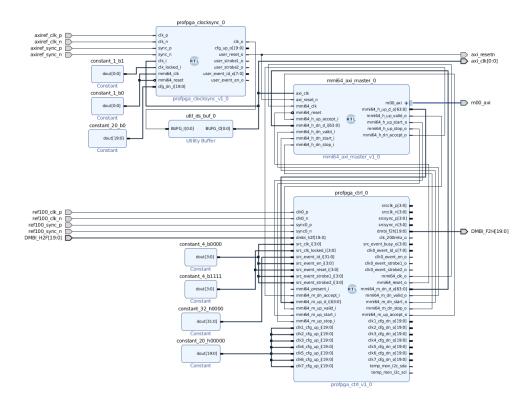

The mmi64\_host\_interface module is a module developed to implement the communication between a host and an FPGA.

The module consists of three main blocks:

- Profpga ctrl;

- MMI64 axi master;

- Profpga clocksync.

Figure 3.2: Vivado mmi64 host interface module design

The profpga\_ctrl module is instantiated, which includes the MMI64 PHY. This module is directly driven by CLK/SYNC[0] and connects to the DMBI pins. It creates the MMI64 interface with the downstream and upstream data interface and the mmi64 clock and reset. This MMI64 interface is directly connected to the mmi64\_axi\_master module. A profpga\_clocksync module creates the AXI clock and resets signals. The AXI clock is running on 125MHz, and the MMI64 clock is running on 100MHz.

#### 3.1.1.1. Profpga ctrl

The proFPGA control unit is the core interface of user FPGA designs to the infrastructure provided by the proFPGA motherboard and host software.

Figure 3.3: Profpga ctrl module

This module contains the DMBI signals that allow the host to be able to communicate with the System. The proFPGA PCIe DMBI Interface offers a high rate of data exchange. The user can benefit from remote system configuration from using this high-speed interface more efficiently for debugging purposes such as streaming data or sending and receiving test patterns, and so on.

The MMI64 interface signals implement the MMI64 protocol. This interface allows communication with another module of the System, MMI64\_axi\_master, which will be discussed in more detail in the section 3.1.1.2.

When the MMI64 is used, the signals must be connected to the host-side interface of the connected module, and mmi64\_present\_i must be driven to '1'. The MMI64 clock is a free-running 100 MHz clock. The MMI64 reset is lowered during the final system initialization stage. The user may provide clocks to the motherboard using the source clock interface. The clock configuration interface must be connected to the corresponding profpga clksync.

**setup** Various parameters of the component can be set, including:

• **Device**: in this module the type of FPGA used is chosen, in this case a Kintex UltraScale Section 2.4.2.4 - "XVUS".

- ENABLE DEBUG: set to "FALSE" when not instructed by ProDesign

- PIN\_TRAINING\_SPEED: choose real pin training for synthesis or fast pin training for simulation "auto" (synthesis tool must support "synthesis translate off")

- ENABLE DISCO: Enable MMI64 DisCo instance inside "FALSE"

- USE\_CLK\_INPUT\_BUFG: Use BUFG before PLL for UltraScale implementation "0"

#### 3.1.1.2. MMI64 axi master

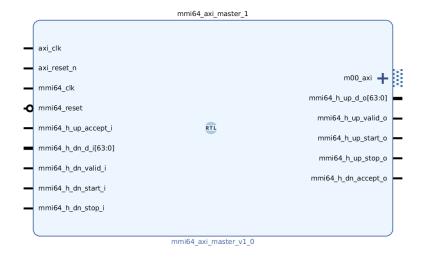

The MMI64 AXI Master module is intended to perform AXI4 bus transactions inside the user FPGA design. A host application controls it.

Figure 3.4: MMI64 axi master module

The MMI64\_axi\_master module, on the one hand, is connected to the profpga\_ctrl module via the MMI64 interface. On the other hand, the AXI master signals allow the comunication with the memory and the convolution IP core. This module has two clock types, one at 100 MHz like the profpga\_ctrl module and the other at 125 MHZ, to synchronize the AXI communication.

**setup** An important parameter of this module is "MODULE\_ID". This unique ID will be used to distinguish the various mmi64 AXI masters when multiple FPGAs are present.

• MODULE\_ID: unique id of the module instance

• AXI\_ID\_WIDTH: ID width

• AXI\_ADDR\_WIDTH: AXI address width

• AXI USER WIDTH: AXI User signal width

• AXI DATA WIDTH: AXI Data signal width

#### 3.1.1.3. Profpga clocksync

A profpga\_clocksync module creates the AXI clock and resets signals. The AXI clock is running on 125MHz, and the MMI64 clock is on 100MHz. The clock generated at 125 MHz is also output to the MMI64\_host\_interface module so that the slave is connected to the AXI master of the MMI64\_axi\_master (Section 3.1.1.2) module can run at the same speed.

**Figure 3.5:** Profpga\_clocksync module

To reduce synthesis timing issues, the clock is not used directly for the processing of the associated SYNC signal. Instead, the user design must provide clock feedback:

1. If the design uses a PLL or MMCM, it is recommended to provide a 1:1 output with no phase shift to clk\_i and the PLL "locked" signal as clk\_locked\_i.

2. If the clock is used directly, the output of the clock buffer must be provided as feedback. In this case, the clk locked i signal should be tied to '1'.

#### setup

- CLK CORE COMPENSATION

- "DELAYED": clk\_core is delayed against clock from motherboard to be used for all XILINX 7-Series and ZYNQ-7000 FPGAs,

- "ZHOLD": clk\_core is compensated to negative phase offset,

- "DELAYED\_XVUS": clk\_core is delayed against clock from motherboard to be used for all XILINX Ultrascale FPGAs.

#### 3.1.2. Convolution IP core

In this work, HLS code was used to perform the convolution, developed by the Group of Parallel Architectures (GAP) of UPV.

Figure 3.6: Convolution IP core

The IP core is connected to the MMI64\_host\_interface via AXI slave signals and to the memory via AXI master signals. The changes made to the HLS code to fit the System involve just the addition of the HLS INTERFACE pragmas s\_axilite and m\_axi, so that upon generation of the IP core, the core would create the AXI interface.

```

#pragma HLS INTERFACE s_axilite bundle=control port=ptr_data

#pragma HLS INTERFACE s_axilite bundle=control port=ptr_out

#pragma HLS INTERFACE s_axilite bundle=control port=ptr_bias

#pragma HLS INTERFACE s_axilite bundle=control port=ptr_kernel

#pragma HLS INTERFACE s_axilite bundle=control port=ptr_dw_kernel

```

```

6 #pragma HLS INTERFACE s axilite bundle=control port=ptr pw kernel

#pragma HLS INTERFACE s axilite bundle=control port=pos shift

8 #pragma HLS INTERFACE s_axilite bundle=control port=dir_shift

#pragma HLS INTERFACE s axilite bundle=control port=max clip

10 #pragma HLS INTERFACE s_axilite bundle=control port=min_clip

#pragma HLS INTERFACE s_axilite bundle=control port=enable_shift

12 #pragma HLS INTERFACE s axilite bundle=control port=enable clipping

#pragma HLS INTERFACE s_axilite bundle=control port=enable_avgpooling

4 #pragma HLS INTERFACE s_axilite bundle=control port=enable_maxpooling

#pragma HLS INTERFACE s_axilite bundle=control port=enable_lower_padding

#pragma HLS INTERFACE s_axilite bundle=control port=enable_upper_padding

17 #pragma HLS INTERFACE s_axilite bundle=control port=global_offset

#pragma HLS INTERFACE s_axilite bundle=control port=enable_relu

19 #pragma HLS INTERFACE s_axilite bundle=control port=o_iter_last

#pragma HLS INTERFACE s_axilite bundle=control port=o_iter_first

21 #pragma HLS INTERFACE s_axilite bundle=control port=I_ITER

22 #pragma HLS INTERFACE s axilite bundle=control port=I

23 #pragma HLS INTERFACE s axilite bundle=control port=O

24 #pragma HLS INTERFACE s axilite bundle=control port=I

25 #pragma HLS INTERFACE s axilite bundle=control port=W

26 #pragma HLS INTERFACE s axilite bundle=control port=H

27 #pragma HLS INTERFACE s_axilite bundle=control port=rows

28 #pragma HLS INTERFACE s_axilite bundle=control port=return

#if defined(DIRECT_CONV) || defined(WINOGRAD_CONV)

30

DO_PRAGMA(HLS INTERFACE m_axi port=ptr_kernel

depth=KERNEL_PORT_DEPTH

offset =

31

slave bundle=gmem1)

32 #endif

33 #ifdef DWS_CONV

DO PRAGMA(HLS INTERFACE m_axi port=ptr_dw_kernel depth=DW_KERNEL_PORT_DEPTH

num_read_outstanding=CPI offset=slave bundle=gmem1)

DO_PRAGMA(HLS INTERFACE m_axi port=ptr_pw_kernel depth=PW_KERNEL_PORT_DEPTH

num_read_outstanding=CPI offset=slave bundle=gmem4)

#endif

36

DO PRAGMA(HLS INTERFACE m axi port=ptr data

depth=DATA IN PORT DEPTH

37

num_read_outstanding=CPI offset=slave bundle=gmem)

DO PRAGMA(HLS INTERFACE m axi port=ptr bias

depth=BIAS PORT DEPTH

38

offset=slave bundle=gmem2)

DO_PRAGMA(HLS INTERFACE m_axi port=ptr_out

depth=DATA_OUT_PORT_DEPTH

num_write_outstanding=CPO offset=slave bundle=gmem3)

```

**Listing 3.1:** Convolution pragmas to create AXI interface

In the listing 3.1 the reader can see the same type of pragma but with two different modes. The pragma is of type INTERFACE then to create the input and output ports of the IP core. As for the mode, all data that must be input to the IP core are mapped as AXI4-Lite