# UNIVERSITAT POLITÈCNICA DE VALÈNCIA

# School of Telecommunications Engineering

Evaluation and application of new Python-based frameworks for the verification of digital integrated circuits

End of Degree Project

Bachelor's Degree in Telecommunication Technologies and Services Engineering

> AUTHOR: Amutio Duarte, Alejandro Tutor: Monzó Ferrer, José María External cotutor: GERTH, STEPHAN ACADEMIC YEAR: 2023/2024

### Resumen

El proceso de verificación de circuitos integrados evita la propagación de errores desde la etapa de diseño hasta el proceso de fabricación y el producto final, evitando así un gasto baldío de tiempo y recursos económicos. El objetivo principal es validar el comportamiento de un circuito ante cualquier entrada posible, lo que requiere la aleatorización de estímulos y, a su vez, detallados modelos de referencia. Por lo tanto, el desarrollo de bancos de pruebas se convierte en una tarea compleja. En este contexto, los ingenieros de Robert Bosch en Dresden han considerado aplicar el uso de una nueva tecnología basada en Python, con el propósito de acelerar el proceso de verificación sin afectar la calidad y la validez de las pruebas. El presente trabajo aplica un nuevo paradigma en la industria de la verificación digital basado en el lenguaje de programación Python, contrastándolo con el enfoque ampliamente adoptado de SystemVerilog. El objetivo principal del desarrollo se centra en la librería "coroutine based cosimulation testbench" (cocotb), y su implementación de la Metodología de Verificación Universal (UVM), PyUVM. La intención final es proporcionar información exhaustiva sobre su funcionamiento y uso en entornos industriales, comentando las ventajas y limitaciones respecto a metodologías alternativas. El proyecto comienza con un análisis meticuloso del panorama actual de la verificación digital, el cual abarca un examen de las metodologías existentes y una evaluación de los desafíos que cada una de ellas presenta. Posteriormente, se realiza una exploración de las librerías cocotb y PyUVM, describiendo su mecanismo operativo y desarrollando en el manejo de ambas desde una perspectiva de usuario. Para demostrar su eficacia, estas librerías se emplean en tres escenarios de verificación distintos, entre los que destaca la verificación de un diseño digital perteneciente a un circuito integrado actualmente en desarrollo. La culminación del trabajo está marcada por un resumen de los resultados obtenidos y su comparación con el enfoque convencional UVM/SystemVerilog. El segmento final evalúa críticamente la viabilidad y potencial integración generalizada de esta nueva tecnología en la industria contemporánea de la verificación digital.

## Resum

El procés de verificació de circuits integrats evita la propagació d'errors des de l'etapa de disseny fins al procés de fabricació i el producte final, evitant així una despesa erma de temps i recursos econòmics. L'objectiu principal és validar el comportament d'un circuit davant qualsevol entrada possible, la qual cosa requerix l'aleatorització d'estímuls i, al seu torn, detallats models de referència. Per tant, el desenvolupament de bancs de proves es convertix en una tasca complexa. En este context, els enginyers de Robert Bosch en Dresden han considerat aplicar l'ús d'una nova tecnologia basada en Python, amb el propòsit d'accelerar el procés de verificació sense afectar la qualitat i la validesa de les proves. El present treball aplica un nou paradigma en la indústria de la verificació digital basat en el llenguatge de programació Python, contrastant-lo amb l'enfocament àmpliament adoptat de SystemVerilog. L'objectiu principal del desenvolupament se centra en la llibreria "coroutine based cosimulation testbench" (cocotb), i la seua implementació de la Metodologia de Verificació Universal (UVM), PyUVM. La intenció final és proporcionar informació exhaustiva sobre el seu funcionament i ús en entorns industrials, comentant els avantatges i limitacions respecte a metodologies alternatives. El projecte comença amb una anàlisi meticulosa del panorama actual de la verificació digital, el qual abasta un examen de les metodologies existents i una avaluació dels desafiaments que cadascuna d'elles presenta. Posteriorment, es realitza una exploració de les llibreries cocotb i PyUVM, descrivint el seu

mecanisme operatiu i desenvolupant en el maneig de totes dues des d'una perspectiva d'usuari. Per a demostrar la seua eficàcia, estes llibreries s'empren en tres escenaris de verificació diferents, entre els quals destaca la verificació d'un disseny digital pertanyent a un circuit integrat actualment en desenvolupament. La culminació del treball està marcada per un resum dels resultats obtinguts i la seua comparació amb l'enfocament convencional UVM/SystemVerilog. El segment final avalua críticament la viabilitat i potencial integració generalitzada d'esta nova tecnologia en la indústria contemporània de la verificació digital.

### Abstract

The verification process for integrated circuits prevents the propagation of errors from the design stage to the manufacturing process and the final product, thus avoiding a futile spending of time and economic resources. Ideally, the main goal is to validate the behaviour of a circuit under any inputs, which requires elaborated stimuli randomization and intricate reference models. Hence, rendering the development of testbenches a complex task. In this context, engineers from Robert Bosch at Dresden have considered the use of a new Python-based technology, with the purpose of speeding up the verification process without affecting the quality and validity of the tests. This work applies a new Python paradigm to digital verification, contrasting it with the widely adopted SystemVerilog approach. The primary focus of this project centres on the "coroutine based cosimulation testbench" (cocotb) library and the Universal Verification Methodology (UVM) abstraction of it (PyUVM). The overarching goal is to provide comprehensive insights into their practical application in industrial settings, commenting on the advantages and limitations vis-àvis alternative methodologies. The project starts with a meticulous analysis of the current landscape of digital verification, encompassing an examination of extant methodologies and an assessment of the challenges inherent in their implementation. Subsequently, an exhaustive exploration of the cocotb and PyUVM libraries ensues, describing their underlying operational mechanism and untangling the expected usage patterns from the end-user perspective. To substantiate their efficacy, these libraries are deployed in three distinct application scenarios, notably including the verification of a digital design part of an integrated circuit currently in active development. The culmination of the present work is marked by an extensive summary, wherein the obtained results are presented and carefully benchmarked against the conventional UVM/SystemVerilog approaches. The concluding segment critically assesses the viability and potential wide integration of this Python framework within the contemporary digital verification industry.

I would like to express my deepest gratitude to Stephan Gerth and José María Monzó Ferrer, for this thesis would not have been possible without their teachings and their unwavering support. I am also thankful for the opportunity that the Mobility Electronics team at Robert Bosch has given me and for Eik Bergmann and his support in my future endeavours. Special thanks to Colin Marquardt for providing invaluable feedback and advice when I needed it.

Lastly, I would like to acknowledge my family and my closest friends, for being by my side even when I was not the person that I wanted to be. Thanks.

# Table of contents

| Chapter 1. | Introduction                         | . 7 |

|------------|--------------------------------------|-----|

| 1.1        | General overview                     | . 7 |

| 1.2        | Objectives                           | . 8 |

| 1.3        | Methodology                          | . 8 |

| 1.3.1      | Setup                                | . 8 |

| 1.3.2      | Metrics                              | .9  |

| 1.3.3      | Development timeline                 | .9  |

| Chapter 2. | State of the art                     | 11  |

| 2.1        | Design flow                          | 11  |

| 2.2        | Verification plan                    | 12  |

| 2.3        | Static verification                  | 12  |

| 2.4        | Functional verification              | 15  |

| 2.4.1      | Universal Verification Methodology   | 17  |

| Chapter 3. | Study of cocotb                      | 19  |

| 3.1        | Overview                             | 19  |

| 3.2        | Internal functioning                 | 19  |

| 3.3        | Coroutines                           | 21  |

| 3.4        | Basic concepts                       | 21  |

| 3.5        | PyUVM                                | 23  |

| Chapter 4. | Synchronous First-In First-Out       | 28  |

| 4.1        | Specifications and verification plan | 28  |

| 4.2        | Reference model                      | 29  |

| 4.3        | Testbench structure                  | 30  |

| 4.4        | Test results                         | 32  |

| 4.4.1      | Testbench comparison                 | 35  |

| 4.4.2      | Discussion                           | 36  |

| Chapter 5. | Bus arbiter                          | 37  |

| 5.1        | Specifications and verification plan | 37  |

| 5.2        | Reference model                      | 40  |

| 5.3        | Testbench structure                  | 41  |

| 5.4        | Test results                         | 14  |

| 5.4.1      | Testbench comparison                 | 51  |

| 5.4.2      | Discussion                           | 52  |

| Chapter 6.            | Chirp Start                                                                    |

|-----------------------|--------------------------------------------------------------------------------|

| 6.1                   | Specifications and verification plan                                           |

| 6.2                   | Reference model                                                                |

| 6.2.1                 | Clocking issues                                                                |

| 6.2.2                 | Model behaviour                                                                |

| 6.3                   | Testbench structure                                                            |

| 6.4                   | Test results                                                                   |

| 6.4.1                 | Discussion                                                                     |

| Chapter 7.            | Summary                                                                        |

|                       | •                                                                              |

| 7.1                   | Comparison                                                                     |

| 7.1<br>7.1.1          |                                                                                |

|                       | Comparison                                                                     |

| 7.1.1                 | Comparison                                                                     |

| 7.1.1<br>7.1.2        | Comparison63Limitations and target cases65Performance enhancing65              |

| 7.1.1<br>7.1.2<br>7.2 | Comparison63Limitations and target cases65Performance enhancing65Goal review65 |

**\_ TELECOM** ESCUELA TÉCNICA **VLC** SUPERIOR DE INGENIERÍA DE TELECOMUNICACIÓN

# List of Abbreviations

| ASIC   | Application-Specific Integrated Circuit                          |

|--------|------------------------------------------------------------------|

| BFM    | Bus functional model                                             |

| Bosch  | Robert Bosch GmbH                                                |

| CERN   | European council for nuclear research                            |

| CRV    | Constrained random verification                                  |

| DUT    | Device under test                                                |

| EDA    | Electronic design automation                                     |

| FLI    | Foreign language interface                                       |

| FOSSi  | Free and open-source silicon foundation                          |

| FPGA   | Field-programmable gate array                                    |

| FSM    | Finite state machine                                             |

| GPI    | Generic procedural interface                                     |

| HDL    | Hardware description language                                    |

| IC     | Integrated circuit                                               |

| ME     | Mobility Electronics                                             |

| ORConf | Open-source silicon conference                                   |

| RTL    | Register Transfer Level                                          |

| SDG    | Sustainable Development Goals                                    |

| SFIFO  | Synchronous first-in first-out                                   |

| SVA    | SystemVerilog assertion                                          |

| UN     | United Nations                                                   |

| UVM    | Universal Verification Methodology                               |

| VHDL   | Very high-speed integrated circuit hardware description language |

| VHPI   | VHDL procedural interface                                        |

| VPI    | Verilog procedural interface                                     |

| cocotb | "coroutine based cosimulation testbench"                         |

# **List of Figures**

| Figure 1. Simplified ASIC design flow from market survey until success of RTL verification.                         | 11       |

|---------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2. Truth table of an AND logic gate.                                                                         | .13      |

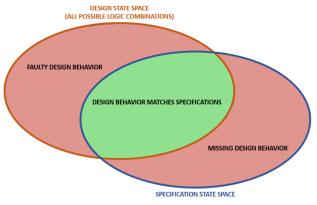

| Figure 3. Possible states of a design behaviour and those allowed by specifications                                 | . 14     |

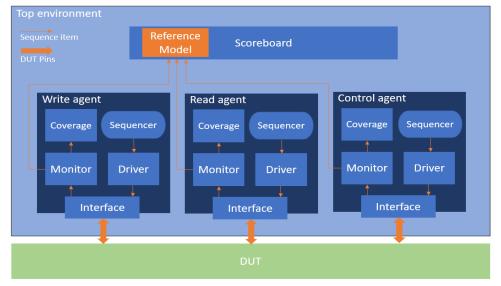

| Figure 4. Basic multi-agent UVM testbench                                                                           | . 18     |

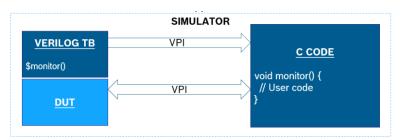

| Figure 5. Block diagram example of C code execution in a simulator using VPI.                                       | 20       |

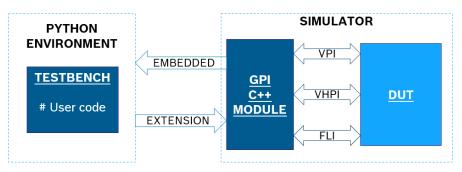

| Figure 6. Block diagram on the internal functioning of cocotb.                                                      | . 20     |

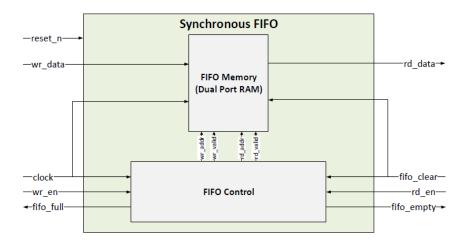

| Figure 7. Block diagram of the SFIFO design.                                                                        | . 28     |

| Figure 8. UVM structure of the SFIFO testbench.                                                                     | 31       |

| Figure 9. Simulation results of the first SFIFO version.                                                            | . 32     |

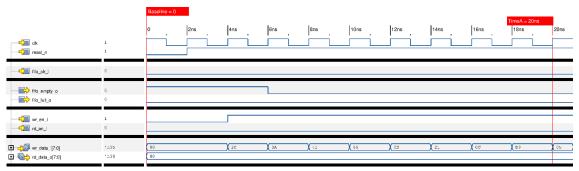

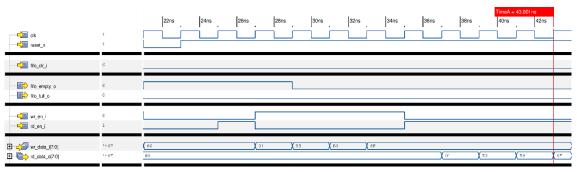

| Figure 10. Waveform of TstWriteFull simulation for the first SFIFO version                                          | . 33     |

| Figure 11. Waveform of TstReadEmpty for the first SFIFO version                                                     | . 33     |

| Figure 12. Simulation results of the second SFIFO version                                                           | . 34     |

| Figure 13. Waveform of TstRandom for the second SFIFO version.                                                      | . 34     |

| Figure 14. Simulation results of the third SFIFO version.                                                           | . 34     |

| Figure 15. Coverage of TstRandom for the third SFIFO version                                                        | . 35     |

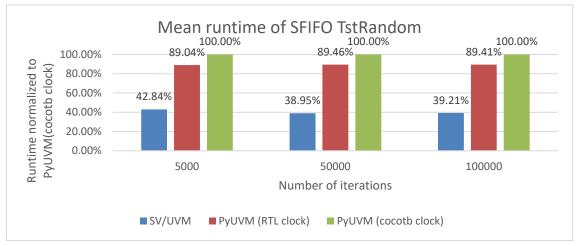

| Figure 16. Comparison of the mean runtime of different SFIFO testbench approaches for vary iterations of TstRandom. | <i>u</i> |

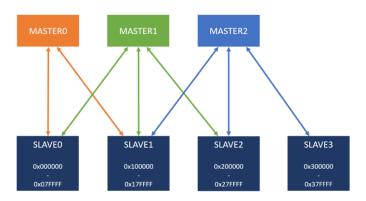

| Figure 17. Bus arbiter connection structure and address map                                                         | . 38     |

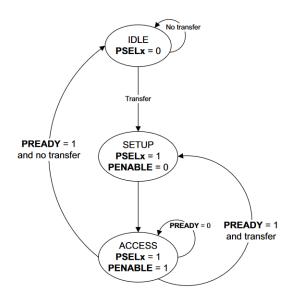

| Figure 18. State diagram of the AMBA 3 APB protocol for a master-slave access                                       | . 38     |

| Figure 19. Flowchart for master-slave connection assignment                                                         | . 40     |

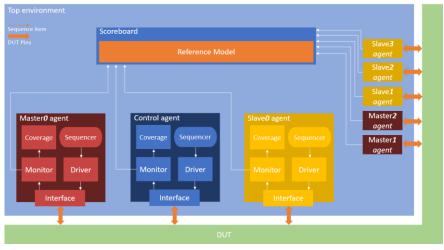

| Figure 20. UVM structure of the bus arbiter testbench                                                               | .42      |

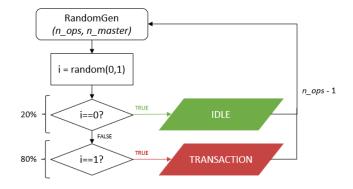

| Figure 21. RandomGen sequence flowchart model.                                                                      | .43      |

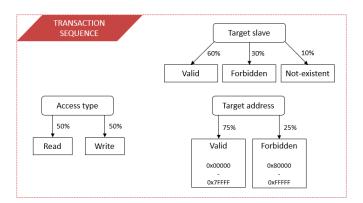

| Figure 22. Transaction sequence weighted random stimuli                                                             | . 44     |

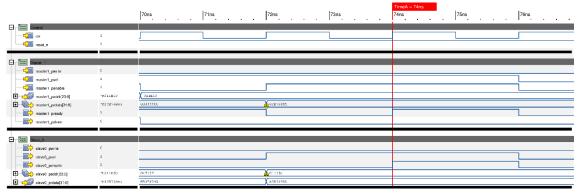

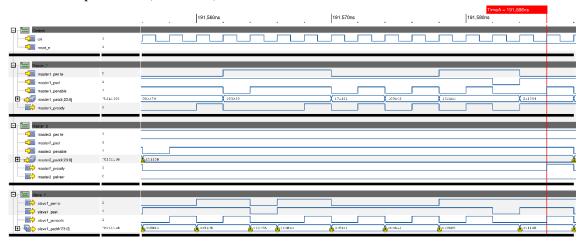

| Figure 23. Arbiter error regarding Master0 and Slave2. PSLVERR mismatch.                                            | .45      |

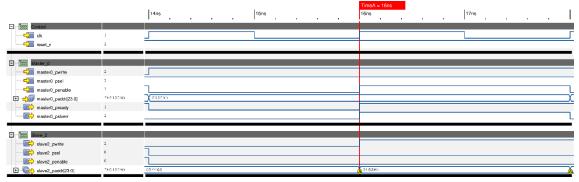

| Figure 24. Arbiter error regarding Master0 and Slave2. No PSLVERR mismatch.                                         | .45      |

| Figure 25. Arbiter error regarding Master2 and Slave3. Unmasked address value                                       | .46      |

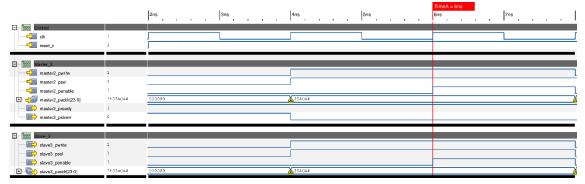

| Figure 26. Arbiter error regarding Master2 and Slave2. PSEL mismatch.                                               | .46      |

| Figure 27. Arbiter error regarding Master2 and Slave2. No PSEL mismatch                                             | . 47     |

| Figure 28. Arbiter error regarding Master1 and Slave2. PSLVERR mismatch.                                            | . 47     |

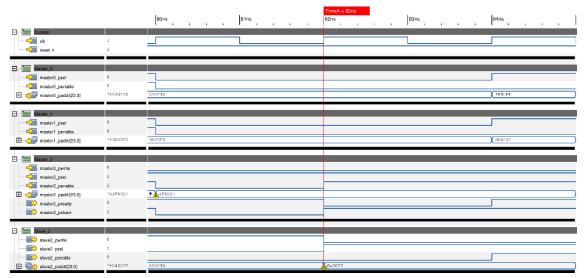

| Figure 29. Arbiter error regarding Master1 and Slave0. PRDATA mismatch (MSB = 1)                                    | . 48     |

| Figure 30. Arbiter error regarding Master1 and Slave0. PRDATA mismatch (MSB = 0)                                    | . 48     |

| Figure 31. Arbiter error regarding Master2 and Slave1. PADDR mismatch.                                              | . 49     |

| Figure 32. Arbiter error regarding Master2 and Slave1. An additional PADDR mismatch                                 | . 49     |

| Figure 33. Arbiter error regarding Master0 and Slave1. PSLVERR mismatch                                             | 50       |

| Figure 34. Coverage of TstRandom for Master1.                                                                       | . 51     |

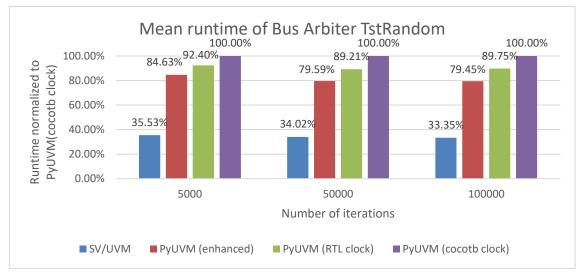

| Figure 35. Comparison of the mean runtime of different bus arbiter testbench approaches for varying iterations of TstRandom |

|-----------------------------------------------------------------------------------------------------------------------------|

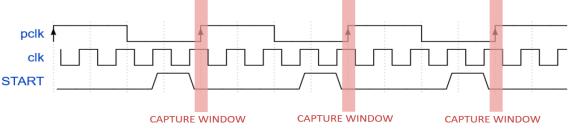

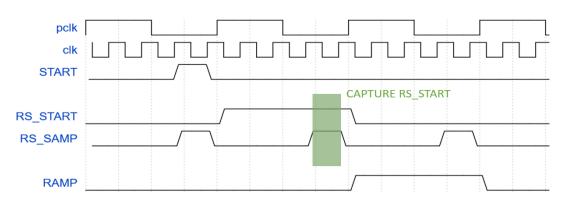

| Figure 36. Exemplary waveform of a signal not being captured in a clock domain crossing scenario                            |

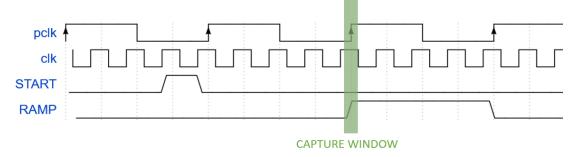

| Figure 37. Exemplary waveform of START being correctly translated from the <i>clk</i> domain to the <i>pclk</i> one         |

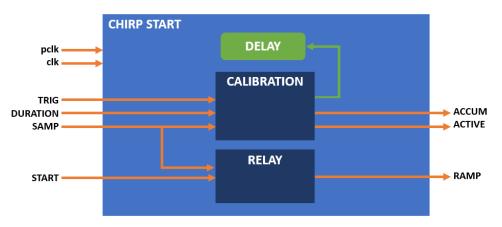

| Figure 38. Simplified block diagram of the Chirp Start system                                                               |

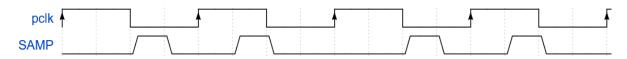

| Figure 39. Exemplary waveform on how the SAMP signal must be received                                                       |

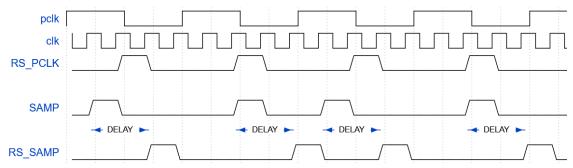

| Figure 40. Exemplary waveform on how internal signals RS_SAMP and RS_PCLK are generated                                     |

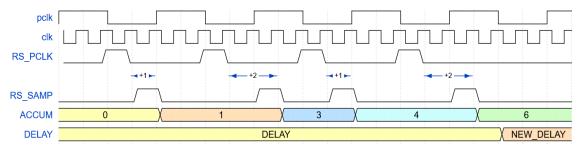

| Figure 41. Exemplary waveform on how the calibration mode operates                                                          |

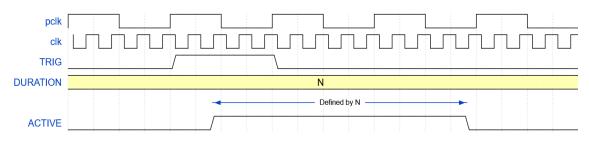

| Figure 42. Exemplary waveform on how to trigger the calibration mode                                                        |

| Figure 43. Exemplary waveform on how the relay mode operates                                                                |

| Figure 44. UVM structure of the Chirp Start testbench                                                                       |

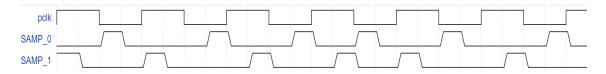

| Figure 45. Examples of implementation of the SAMP signal                                                                    |

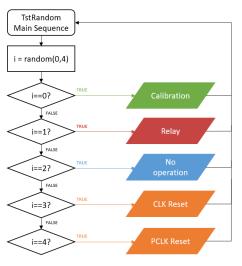

| Figure 46. State diagram for the random test of the Chirp Start testbench                                                   |

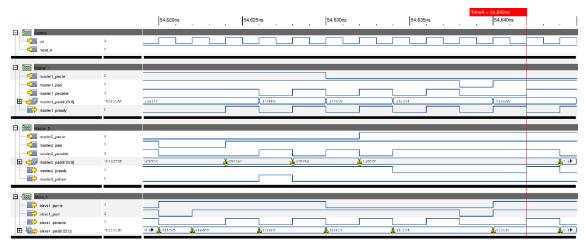

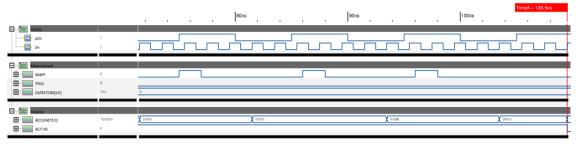

| Figure 47. Calibration measurement. Assertion error on ACTIVE                                                               |

| Figure 48. Calibration measurement. Expanded simulation                                                                     |

| Figure 49. Calibration measurement. Correct behaviour of ACTIVE                                                             |

| Figure 50. Calibration measurement. Accumulator values                                                                      |

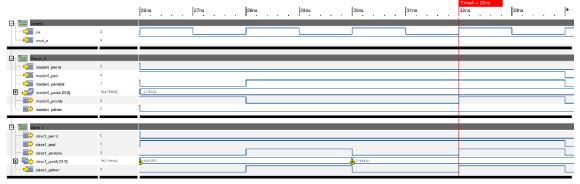

| Figure 51. Chirp Start error regarding missing RAMP signal after a reset                                                    |

| Figure 52. Chirp Start error regarding missing RAMP signal after a calibration                                              |

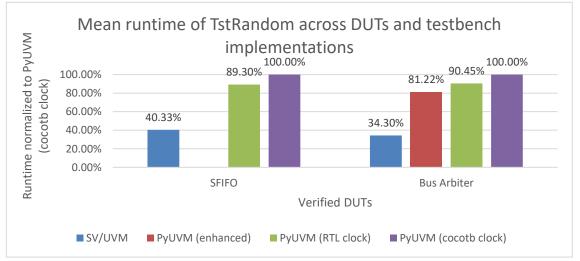

| Figure 53. Mean runtime of TstRandom across DUTs. Normalized to the respective slowest implementation                       |

# **List of Tables**

| Table 1. Line count comparison for SFIFO testbenches.       | 35 |

|-------------------------------------------------------------|----|

| Table 2. Line count comparison for bus arbiter testbenches. | 51 |

# **Chapter 1. Introduction**

#### **1.1 General overview**

Developing a new *integrated circuit* (IC) is a resource-intensive task that can expand indefinitely through time as well as through economical capabilities. These ICs present more complexities with each iteration, allowed by the advance in semiconductor technology, and a manufacturing failure of a sole product can cause havoc for any company. Errors, malfunctions, or mismatches between the expected behaviour and the one observed, should be corrected before it propagates further down the design workflow, avoiding the fabrication of a faulty design at all costs.

A study from 2020<sup>(1)</sup> notes that the growth in demand for verification engineers between 2007 and 2020 was more than double that for design engineers. Although the mean ratio between both positions seems to be one-to-one across the industry, specific markets (for instance, processor units) may experience 5-to-1 ratios. Verification is not merely a quality control measure; it is the linchpin that fortifies the foundation upon which the semiconductor industry thrives.

Digital designs are built using a *Hardware Description Language* (HDL) such as Verilog<sup>(2)</sup> and VHDL<sup>(3)</sup> to transform lines of code into synthesizable logic. However, this is not a requirement for verification, and that allows other languages to thrive. Eventually, a Verilog superset, SystemVerilog<sup>(4)</sup>, was created to unify design and verification in a single language, which in turn has synthesizable structures and others that are not.

SystemVerilog has been the most popular option for digital verification <sup>(5)</sup> in the last decade. Nonetheless, as ICs grow in complexity, the tests and the models also do. This intricacy presents a problem for a language such as SystemVerilog. Its syntax complexity does not provide the ideal environment for maintainability, and its non-usage outside the semiconductor industry introduces a significant barrier for new verification engineers.

Python <sup>(6)</sup> is one of the most used programming languages across disciplines with more than 512,937 projects available <sup>(7)</sup>, and *cocotb* (coroutine based cosimulation testbench) <sup>(8)</sup> takes advantage of it. First released in 2013 <sup>(9)</sup>, the cocotb framework allows for integration into an elevated number of the available HDL simulators, enabling the creation of testbenches using the Python language. Its popularity has awarded it to be used in the industry, presented at verification conferences <sup>(10)</sup>, and the creation of libraries that build upon it, the most notable being *PyUVM* <sup>(11)</sup>.

This project is a result of the imperative for enhancing verification methodologies, specifically for digital designs. Semiconductor companies, such as *Robert Bosch GmbH* (Bosch) being the director of this thesis, have a special interest in cocotb. This document will explore this library and related frameworks, thus providing helpful insight into the potential benefits that this emerging technology brings to the forefront of IC digital verification. Its comparison to already known and established verification methodologies, and its application to an in-development industrial design, will help to determine its significance in future projects. Additionally, this dissertation may help to understand how to apply cocotb in further verification environments.

#### 1.2 Objectives

The main objective of this project is to apply the cocotb framework as a behavioural digital verification tool and extract how this technology can be further integrated into (or replace) existing verification environments based.

Significant milestones will define the success of achieving the main goal:

- Examine the current state of the IC verification industry, the challenges of SystemVerilog-based testbenches, and how cocotb can address them.

- Provide a straightforward understanding of how cocotb works, as well as how to use it for testbench design.

- Design and run cocotb-based testbenches to verify diverse digital designs under controlled scenarios: a ramp-up project and a significantly more complex design.

- Evaluate how cocotb-based testbenches compare to SystemVerilog ones using the previously verified designs.

- Apply the acquired knowledge of cocotb to verify a digital design in active development by Bosch.

- Explore how cocotb can be used for future projects inside the company and, more generally, in the verification industry.

#### 1.3 Methodology

This project was conducted at the facilities of Robert Bosch GmbH in Dresden, Germany, under the guidance of the *Mobility Electronics* (ME) department. Certain set-up decisions have been selected according to company standards or by common usage across the department.

#### 1.3.1 Setup

The computer environment in which simulations are run has been configured according to the cocotb requirements specified in its documentation.

- **Operative system**: The selection of a UNIX-based OS (*Fedora 7.3*) is a Bosch decision. The work environment is already set up, which includes the simulator software and licenses to use it.

- **cocotb**: The latest release available while developing this thesis (v.1.8.0) has been chosen. It provides an updated insight into the current capabilities and limitations of the framework.

- **Python**: The used version must be no older than 3.6. To maximize the benefits of the language, the most recent release with ongoing security maintenance until October 2026 (v3.10) has been chosen. This ensures that written code will remain compatible with future updates.

- **Code editor**: Among the diverse options for code editors, *Visual Studio Code* was the preferred choice due to its intuitive usage and abundance of external plugins to enhance the user experience. The used version corresponds to build number 1.82.2.

- **GNU Make**: To effectively execute the Python code with system calls to the simulator, an executable is essential. The framework requires *GNU Make* as the chosen tool, and it requires a version no earlier than the third release (v3) to ensure compatible functionality. The given environment provides the 4.3 version.

- **Simulator**: Given that the framework only provides the means to code the testbench, a compatible simulator must be used to execute it. Due to the abundance of licenses available in the workspace, the ME team opted to use *Cadence Xcelium*. This decision was influenced by their previous testbenches being successfully executed using the same simulator. The proximity in experimental conditions will enable a meaningful comparison of the results obtained for both approaches.

Three designs have been chosen for this project, all of them provided by Bosch. Each one represents a *Design Under Test* (DUT) to be verified:

- *Synchronous First-In First-Out* (SFIFO): Ramp-up project for verification engineers. Since it is the first DUT for new employees, it provides helpful data regarding the learning curve of the framework.

- **Bus arbiter**: Verification challenge from 2018. It presents a more complex design that requires a more demanding testbench, therefore highlighting the benefits and limitations of cocotb against other approaches.

- *Chirp Start*: Digital design block found in the current project being developed by the ME team. It will set the stage for future real-life usage cases of the framework in the company.

#### 1.3.2 Metrics

To perform a valid comparison against already existent verification environments, the conditions of testing must be similar. Although different companies may have diverse approaches to digital verification, the one used the most across the field <sup>(5)</sup> is the *Universal Verification Methodology* <sup>(12)</sup> (UVM). Therefore, it has been chosen as the standard for this comparison.

The UVM approach to verification is discussed and explained in section 2.4.1. However, it can be described as a workflow/framework to implement reusable testbenches.

For SystemVerilog, there exists a library to implement this framework, while for cocotb there are multiple libraries available. During this project, the PyUVM library will be used as the default implementation of UVM in cocotb. This selection against other alternatives is discussed further ahead.

Henceforth, the application of UVM in SystemVerilog will be referred to as *SV/UVM*. To evaluate how it differs from PyUVM, the comparison will focus on the following categories:

- **Learning curve**: How easy it is to start a project, increase knowledge, and master its use. Availability of documentation, tutorials, and community support will be considered.

- **Performance**: The simulation speed of each of the testbenches. This metric can vary depending on the efficiency of the written testbench rather than the simulator used. Additionally, the number of code lines between testbenches will be compared, although the same statements could have been expressed differently.

- **Integration**: Ease of integrating each of the options with existent and future verification tools.

- **Maintainability**: How the code is structured and how the programming language used can influence the maintenance of the testbench.

- **Industrial adoption**: Number of users, successful deployments, and industry recognition.

#### 1.3.3 Development timeline

To accomplish the target objectives, the project has been structured into specific tasks. Each task has been assigned a time frame in which it should be completed. Note that the development of this thesis extends from September 2023 until March 2024.

- 1. **cocotb basics**: This part of the project involves setting up the work environment as well as designing and running basic testbenches using the cocotb and PyUVM frameworks. A month is dedicated to this purpose.

- 2. **SFIFO and bus arbiter verification**: This task is related to the development of PyUVM and SV/UVM testbenches for both the SFIFO and the bus arbiter designs. Being the first application of the framework and involving multiple DUTs, this development phase takes place over two months.

- 3. **Chirp Start verification**: The verification of a real design requires special dedication. The functioning of both PyUVM and cocotb is already known, but the testbench for this

scenario requires higher attention to detail. Thus, a month is the time given to complete this task.

4. **Summary and writing**: The analysis of the results, as well as narrating the development process, is a complicated task that involves constant review between the people involved in this thesis. Therefore, two months is expected to coherently assemble the recorded notes into this document.

## Chapter 2. State of the art

Electronic designs in the digital domain contemplate electronic circuits whose input and output signals are discrete values, governed by Boolean logic. As a simpler definition; circuits whose minimal building blocks are logic gates.

This chapter aims to provide the reader with background knowledge on the *Register Transfer Level* (RTL) design of digital *Application-Specific Integrated Circuit* (ASIC), with special attention to the techniques used in the process of verification.

#### 2.1 Design flow

When building a new system, each company may have its own custom approach to the design flow to follow. Nonetheless, these processes are mostly based on the same basic steps <sup>(13)</sup> (<sup>14)</sup> (<sup>15)</sup> (<sup>16)</sup>. For simplicity, the market survey phase and stages regarding physical design will be omitted.

The process starts with a design idea, and at the same time, the specification phase takes place. During this step, the design architecture is defined, and its behaviour and characteristics are described as detailed as possible. Concurrently, an attempt at balancing system requirements (based on client targets) and capabilities happens. The main goal of this phase is to establish how the overall system and its architectural blocks behave.

Although specifications are the basic description of a design, new scenarios and applications can be discovered once the design process has taken place. As a result, specifications can be improved in further stages and are constantly open to modifications.

Once the specifications have a solid foundation, the RTL design phase can commence. To describe digital logic as well as memory components, designers use a dedicated language. An HDL may look like a common programming language, but it can characterize logic components as readable text. Popular options are Verilog, SystemVerilog, and VHDL. As soon as all RTL designs are finished, they are merged into a final top design.

Concurrently to the design stage, the verification process takes place. Using different techniques, the design behaviour is compared against the specification. This process has a close connection to the RTL design step. As verification engineers discover faulty functioning in the design, the results are reported to the designer to be fixed. Once the system behaves as expected, the next stages can take place.

Further steps on the design flow include synthesizing the HDL code into logic structures, describing the connection between these structures (*netlist*), and the fabrication of the physical layout.

Figure 1. Simplified ASIC design flow from market survey until success of RTL verification.

The existence of the verification process is meant to avoid the downstream propagation of errors and faulty behaviours of the design. This avoids the manufacturing of partially defective circuits, which can result in a significant economic impact on a company. In addition, backtracking the design flow from the manufacturing phase until the RTL design has a notable time impact, thus resulting in release delays and an overall disadvantage over competitors. In an industry where 49.3% of the market revenue corresponds to just ten companies <sup>(17)</sup>, pre-silicon verification becomes an asset.

These verification engineers, although closely related to the design team, are a separate entity whose object is to compare a design against its specifications. The designers should not execute this task themselves as they inevitably introduce a level of bias to the process.

The designers have explicit knowledge on how the HDL code is going to behave, then they could inadvertently avoid testing specific cases, or only check specific scenarios where the design works correctly. An external observer provides valuable information, as it will determine if the specifications are unambiguous and if the design behaves accordingly.

The importance of the verification process is remarkably significant that in some market sectors, for instance, microprocessors, it is possible to find five verification engineers per designer<sup>(1)</sup>.

#### 2.2 Verification plan

For the verification process, there are multiple tools available. The main target, however, is to check that the design behaves accordingly, that it can work for every expected circumstance, and that it can manage unexpected scenarios correctly. Even though there are multiple approaches to evaluate the design's capabilities, a common step is defined: a verification plan.

This phase has a significant importance, as it lays out the failure and success conditions. If the verification plan is completed successfully, then the design is stated to work correctly and can continue the development flow. If not, the errors are reported to be fixed.

The plan introduces details such as to which verification approach or methodology to follow, which cases are forbidden by the specifications, which cases may present special interest, and how much the design should be stressed. This last feature establishes how many input combinations should be tested, thus indirectly designating for how long the test should run.

In the end, this is a delicate stage where every detail must be drawn, but it is also the most crucial. The verification plan is responsible for determining the conditions and scenarios that have significant importance to assess the validity of a design.

While there are multiple methodologies to approach the verification of a design, the following sections will focus on two of the most significant ones <sup>(18)</sup>; *static* and *functional* verification.

#### 2.3 Static verification

Digital designs are based upon logic elements and thus, they can be described using Boolean arithmetic. This factor allows digital designs to be characterized as mathematical models, which introduces the possibility of assessing their validity (also referred to as *correctness*) with a mathematical approach.

Take for instance the truth table of Figure 2 defining the functioning of an AND gate. It specifically defines the expected output for a given set of inputs. If a verification engineer wanted to prove that every time both inputs are 1 the output is also 1, it could use equation (1) to mathematically assert that statement.

$$\mathbf{A} \cdot \mathbf{B} = \mathbf{C} \tag{1}$$

| INPUTS |   | OUTPUT |  |

|--------|---|--------|--|

| Α      | В | С      |  |

| 0      | 0 | 0      |  |

| 0      | 1 | 0      |  |

| 1      | 0 | 0      |  |

| 1      | 1 | 1      |  |

Figure 2. Truth table of an AND logic gate.

This mathematical approach to verification is given the name of static verification, although it can also be referred to as *formal* verification. This methodology requires specific tools that may differ from what the reader may expect.

In essence, a formal verification tool analyses the provided HDL code and extracts its logical behaviour, being able to describe it as a mathematical model. In turn, this allows the tool to handle every possible state of the design.

The behaviour of a design can be checked as a set of logical properties that must be asserted. An assertion is a statement about a logical property that should hold under a set of conditions. If the statement is found to be false under those circumstances, the assertion is said to have failed.

In this context, there exist formal specification languages that let the user define assertions for a target design. These languages can be interpreted as mathematical statements that formal verification tools can use to observe if they hold against the design's mathematical model.

The *SystemVerilog Assertion*<sup>(19)</sup> (SVA) language is commonly used for this task, building upon the popularity of the SystemVerilog language itself. The language allows a variety of structures to describe the specifications of a design, although this section will only cover the basics.

An assertion is defined by the *assert* keyword and can be either immediate or concurrent. An immediate assertion is checked in reference to its location on the code; it can be considered a condensed if-else statement. A concurrent assertion, on the other hand, establishes a property to be checked constantly at any point, or state.

Both types of assertions can be used in formal and functional verification, nevertheless, both types are explained in this section. To understand concurrent assertions, it is helpful to first provide an overview of the immediate approach:

```

assert (C == 1);

CheckForC: assert (C == 1) $display("C is 1") else $display("C is not 1");

```

Note that both assertions are immediate but additional options are added to the second one. Both statements check for the value of C being 1, but the second one is assigned a name (*CheckForC*) and displays a message if the assertion succeeds or fails. In formal verification tools, the failure or success of the assertion will be reported whether there is a *\$display* message or not.

Concurrent assertions may follow a similar structure. They are described by adding the *property* keyword to the assertion statement. For example:

CheckWrRd: assert property (!(WR && RD));

The previous assertion declares that at any given moment, the signals WR and RD cannot be both 1. If at some point, or state, both signals are at their high-level value, the assertion will trigger a failure.

More types of behaviours can be described using the SVA language, but their explanation escapes the scope of this section. Nonetheless, to provide further insights into the capabilities of the language, another example is shown:

####

The previous assertion declares initially that the check should take place at the rising edge of the *clk* signal and only if the *reset\_n* signal is not 0. Afterwards, if the signal A changed from 0 to 1 (*\$rose*), at some point between the next three *clk* cycles the signal B should also change from 0 to 1.

At this point, it may be clear that the formal simulator has a mathematical model for the design (from the HDL code) and another one for the expected behaviour (SVA code), but not all scenarios may be possible to check. Specifications of a design may forbid specific input combinations, and the SVA language provides a solution, called *assumptions*.

An assumption lets the simulator know which input combination or scenarios are not allowed by the specifications, for example:

reset\_1clk: assume property @(posedge clk) !reset\_n |=> reset\_n;

The previous assumption establishes that if the *reset\_n* signal is set to 0, it must return to 1 in the next *clk* cycle. The simulator will correctly understand this assumption and constrain its input stimuli accordingly.

This approach to verification may seem ideal. The engineer can almost input the specifications as plain text and the simulator manages the rest. Nonetheless, there is a significant drawback <sup>(11)</sup>; runtime.

The design is expressed as a mathematical model, but it is still a combination of multiple equations with multiple outcomes that influence future equations. The tool evaluates every combination and every state transition; this is how the result of an equation affects the ones that depend on it.

Each design presents a specific number of logic combinations (*states*), and multiple paths to get to each of them. States can either be illegal or valid. Illegal states represent a faulty behaviour of the design based upon the specifications. On the other hand, valid states are logic combinations allowed by the specifications. Figure 3 provides further information on the possible states of a design.

Figure 3. Possible states of a design behaviour and those allowed by specifications.

A state contained in the design space but not covered by the specifications is considered a faulty behaviour, an error. On the other side, a state contained in the specification state but that does not have a design implementation represents a missing functionality.

The goal of the formal tools is to match both the specification and the design spaces using assertions. These tools have different approaches to checking all these states and transitions (bounded model check, induction, etc.), based on mathematical techniques. This process requires a noticeable runtime the more complex a design is; the more logical states are introduced.

For basic/simple designs, formal verification may be the best approach as it provides a straightforward case to completely verify its behaviour. For more complex designs, the number of available states and state transitions may make the simulation run for longer, thus making it unsuitable for an agile workflow. Nonetheless, formal verification is a valid methodology being used in the industry <sup>(18)</sup> and, like other alternatives, it has its target cases and its disadvantages.

#### 2.4 Functional verification

A functional approach to verification refers to handling the inputs and outputs of the DUT directly through a simulator. It differs from formal verification approaches as the target is not to check the overall correctness of a design but rather to observe how it behaves under certain stimuli. The elevated runtime of formal verification makes this approach an attractive option for complex sequential designs, or to speed up the verification process when checking specific scenarios.

Referring to Figure 3, functional verification has the goal of matching both the specification and the design spaces using custom stimuli.

There are specific tools that can synthesize and extract the behaviour of an HDL design to simulate it; HDL simulators. The design functionality is understood, and the simulator can imitate its behaviour using computer operations. In this case, the design is not parsed into a mathematical model but rather into a set of executable instructions.

Simulators per se do not present the autonomous capability to analyse the correctness of a design, the engineer must generate the stimuli. To manipulate the inputs and extract information from the outputs, a testbench is used. A testbench (also shortened to tb) is a structure written in an HDL that handles the stimulus generation as well as the output checking. The DUT module is instantiated and its signals are controlled directly. Engineers determine the stimuli to use based on the cases or scenarios to evaluate the test cases.

Although there exist multiple options of HDL to perform functional verification, this section will explore the SystemVerilog language, based on its popularity for this approach <sup>(18)</sup>.

The following code presents a simple testbench module. Internal signals are created to connect them to the ones in the DUT, which is instantiated afterwards. Initially the value of d is set to 1, and after the next rising edge of the *clk* signal, the value of the *q* signal is checked to be 1.

Functional verification allows engineers to customize the stimuli generation step by step. If static verification checks every possible state, functional verification could directly observe the behaviour of a design for tailored scenarios.

However, testing how a design works under a constant input sequence endlessly does not provide enough information. Ideally, the input must represent a real usage situation; different scenarios in a varying sequence.

Randomized stimuli approximate the real conditions under which the design will be held. For instance, in the previous example, the value of the d signal was explicitly set to 1. However, that may not be always the case, as the same signal could have also been 0. It is possible to add a couple more lines of code to also test this last case, although it is not a scalable method for signals with a higher number of bits.

The idea of randomized stimuli is a powerful tool that may require control over the generated values. The specifications of a design may describe not allowed input combinations, sequences, or usage conditions. In these cases, signals may have explicit rules to obey or a range of valid values. *Constrained Random Verification* (CRV) allows for a wide range of possible scenarios as the inputs of the DUT are constantly randomized, while also targeting the functionality of a design. This approach allows for input signals to take different values through the simulation, while at the same time limiting the valid values by specific conditions.

In SystemVerilog, random variables contained inside a class are defined with the *rand* keyword. Their value is randomized when calling the *randomize* function of the class. On the other hand, constraints are defined with the *constraint* keyword and can implement different types of restrictions, from simple ones to more intricate scenarios. An example follows:

```

class crv_class;

rand byte in_data;

rand bit reset_n;

constraint allowed_range {in_data inside [2:5];}

constraint reset_val {reset_n dist {0:=80, 1:=20};}

endclass

crv_class tst_example = new();

tst_example.allowed_range.constraint_mode(0);

tst_example.randomize();

```

The previous code shows a class ( $crv\_class$ ) containing two randomizable variables:  $in\_data$  and  $reset\_n$ . Then, two constraints are defined. The first one limits the  $in\_data$  variable to values between 2 and 5 (both included). The second one establishes a weighted distribution of values for  $reset\_n$ : the value will be 0 with a probability of 80/100, and it will be 1 with a probability of 20/100. Afterwards, an instance of the class is generated ( $tst\_example$ ) and before its variables are randomized, the constraint regarding  $in\_data$  is deactivated.

This randomized approach to verification allows for a colourful palette of combinations and sequences to be observed. Nevertheless, the simulation could run indefinitely if not stopped manually or by the failure of an assertion. To determine if the DUT has been stressed enough, the goals established in the verification plan come into use.

To assess the validity of a design, the general rule is that the more cases are evaluated the better. Static verification represents the extreme of this approach, as all possible scenarios are covered. In functional verification, however, because the stimuli are generated by the engineer, specific cases may be never tested. The solution to this problem is to measure which scenarios have taken place: the *coverage* of the testbench.

The SystemVerilog language natively implements structures to handle coverage. A *coverpoint* is an expression or statement that will be evaluated at a sampling point. A *covergroup* contains

multiple coverpoints and specifies a common sampling point for the evaluation of each of them. The percentage of coverage from a coverpoint is defined by the number of sampled cases and the number of possible ones. A simple example follows:

```

covergroup my_coverage @ (posedge clk);

cover_data : coverpoint in_data;

cover_rst : coverpoint reset_n;

endgroup

```

The previous code establishes that for every rising edge of the *clk* signal, the values of *in\_data* and *reset\_n* will be registered. Each coverpoint will have a complete coverage (100%) when all their possible values are sampled; when each signal has taken every possible value.

While effective, the coverage tool even presents more capabilities. For instance; if the signal  $in\_data$  is constrained to values between 2 and 5, its coverage will never be complete. Additionally, it may not make sense to sample the value of  $in\_data$  if the reset is active. For these scenarios, there is a possible implementation:

```

covergroup my_coverage @ (posedge clk);

cover_data : coverpoint in_data iff (reset_n) {

bins my_range = {[2:5]};

}

endgroup

```

In the previous code, the value of *in\_data* will only be sampled in the range between 2 and 5 and whenever the reset is not active (high-level). More coverage constructs are available to use, such as observing the combinations between two signals (*cross* coverage), but they present a more advanced topic not related to this thesis.

#### 2.4.1 Universal Verification Methodology

A common approach to testbenches does not present a real option for scalability and reusability. Changes and evaluation of the DUT signals are made through statements that are written directly on the testbench code. Each time a new test is written, the engineer must write the sequence to follow and, at the same time, handle how the variables are connected to the DUT. Ideally, the last step would be ignored; the engineer would only have to write the sequences to run and there would be a structure in place to send the sequence to the DUT.

The Universal Verification Methodology (UVM) is an approach to apply the best practices for verification, focused on the reusability of its components for changing testbenches. It was designed by Accellera based upon the Open Verification Methodology and it is now an IEEE standard <sup>(12)</sup> supported by multiple simulators from varied Electronic Design Automation (EDA) vendors. It is also the predominately used methodology for verification in industrial settings <sup>(18)</sup>. A library that implements the UVM methodology can be found in the SystemVerilog language.

In summary, this methodology is a powerful tool that can improve reusability and efficiency for testbench design. The capabilities of UVM are notably useful as they target exclusively the improvement of the verification process. In turn, mastering UVM is a time-consuming task, and learning the basics of it also presents challenges. It is a methodology with a steep learning curve that, when understood, drastically boosts testbench design and reusability.

This section will focus on a basic description of a simple UVM testbench. This technology, while widely used in the industry, presents characteristics that allow for advanced testbenches, and thus, to cover all its capabilities, entire books have been dedicated to that purpose. This section aims to provide the reader with a basic notion of how UVM testbenches operate <sup>(20)</sup>.

| Sequences<br>Sequencer<br>Driver | Agent "Y"<br>Coverage<br>Sequencer<br>Monitor<br>Driver<br>Interface |

|----------------------------------|----------------------------------------------------------------------|

|                                  | Sequencer<br>Driver                                                  |

Further explanations will be made based on the block diagram shown in Figure 4.

Figure 4. Basic multi-agent UVM testbench.

The minimal unit on a UVM testbench is a *sequence item*. This is the lowest object needed to send information from an engineer's perspective to the DUT. These items contain information which data shall be driven to the DUT.

A set of ordered sequence items is called a *sequence*. A sequence can be seen as a function; it contains multiple directives in the form of sequence items to interact with the DUT. To execute these directives, a *sequencer* manages when the next item of a sequence must be called. A sequencer can only handle one sequence at a time.

To interact with the DUT, UVM testbenches use a *driver* and a *monitor*. The first component receives the sequence items from the sequencer and decodes the data into the DUT input pins. On the other hand, the monitor encodes the DUT output pins into a sequence item. Each component has a specific event that triggers its functioning. For example, the monitor could execute its function on every falling edge of the clock signal, and the driver could send the next item to the DUT on every rising edge. A set of DUT pins is defined by the *interface* SystemVerilog structure

All these components are wrapped by a class called *agent*. Multiple agents can exist, and they can handle different signals of a DUT. For example, in a design with a read interface and a write interface, a different agent for each one can be useful, as it allows to insulate different functionalities of the DUT. Each agent may also have its own *coverage* class to apply coverage structures to its connected DUT pins.

The last steps involve checking the items from each monitor. These items are sent to a *scoreboard* where the engineer has defined a reference model. This reference model is an implementation of the expected behaviour of the design. Analysing the driven items, the model decides which outputs are expected next, and compares its expectations with the monitored items.

The agents and the scoreboard are included in a single class, an *environment*. Then, the environment can be reused in different tests, a *test* class. Each test will share the same environment but will implement its own set of sequences to execute. Thus, the engineer can reuse the structure to interact with the DUT and can focus specifically on designing the sequences.

The UVM testbenches allow for all the explained SystemVerilog structures; random constrained stimuli, assertions, and coverage. Thus, a UVM testbench can be considered a significant powerful tool when it comes to functional verification.

# Chapter 3. Study of cocotb

#### 3.1 Overview

*Cocotb* <sup>(8)</sup> (from coroutine-based cosimulation testbench) is a Python-based framework for the verification of VHDL and Verilog designs. It was first released on July 9<sup>th</sup>, 2013, as an open-source project from Potential Ventures, supported by Solarflare Communications Ltd <sup>(9)</sup>. Since mid-2018, the project has been administrated by the *Free and Open-Source Silicon* UK-based, non-for-profit, foundation (FOSSi). The source code is hosted on a GitHub repository (21) protected under the BSD-3-Clause license, which allows its usage and modification by any user without any cost, including industrial environments.

In essence, cocotb allows its users to perform the verification of HDL designs running testbenches written in the Python programming language. The framework works with many existing simulators, both proprietary and open-source ones <sup>(22)</sup>.

The project is updated regularly; four new minor versions were released in 2021, four in 2022, two in 2023, and there is already a new major version in the works. It is sponsored by *Cadence Design Systems, Siemens Digital Industries Software*, and *Aldec* <sup>(8)</sup>. These EDA tool providers supply simulator licenses to cocotb developers for integration testing.

Additionally, cocotb was also part of the Open-Source Silicon Conference (ORConf) of 2023<sup>(10)</sup>. This backed-up support by significant and popular EDA companies, as well as participation in industry-focused conferences, has made cocotb known across the verification landscape. During the ORConf conference, information from a Siemens research study showed that cocotb is an alternative being used as a functional verification tool for ASIC and Field-Programmable Gate Array (FPGA) testbenches in real design projects.

One of the most significant cases of industrial adoption of cocotb is presented by the European Council for Nuclear Research (CERN) on its ATLAS experiment, in collaboration with the University of Pennsylvania<sup>(23)</sup>. In the experiment, two ASICs were successfully verified using the cocotb framework, and the verification team is planning to use the same approach in the future. Note that in this case, the plain cocotb library was used with no UVM implementation.

#### **3.2** Internal functioning

An HDL simulator is a software program that models the behaviour of a design described in languages like SystemVerilog, VHDL, or similar. It reads the provided file, compiles the human-readable code into a connectivity description between logic components (a *netlist*), and elaborates a model of how the design works. As such, a simulator transforms HDL design code into computer operations to replicate its behaviour.

Behavioural simulators do not change the input signals of a design on their own, a stimuli generator is needed; a testbench. The testbench is also written and described in HDL code, thus it can also be interpreted directly by the simulator. Nonetheless, simulators allow for the execution of already compiled C/C++ code. Through dedicated interfaces, the C/C++ programs are granted access to the data contained in a simulation, providing the ability to actively change the state of a design. This code can either be started right away or be called from an HDL testbench; an example of the latter scenario is shown in Figure 5.

Figure 5. Block diagram example of C code execution in a simulator using VPI.

Each HDL describes its interface, thus resulting in the existence of multiple interfaces such as the *VHDL Procedural Interface* (VHPI), the *SystemVerilog Procedural Interface* (VPI), and the *Foreign Language Interface* (FLI). The latter is a non-standard proprietary interface used by the *QuestaSim* simulator.

At its highest description level, cocotb provides a wrapper for Python to interact with the simulator through the VHPI, VPI, and FLI interfaces using a background C/C++ structure. Nonetheless, its functioning presents an interesting case.

Firstly, note that each HDL uses its own interface. To get around multiple functions, cocotb implements a single Generic Procedural Interface (GPI) in C++ that can effectively communicate the same desired action to the simulator using any of the three mentioned interfaces  $^{(24)}$ .

Subsequently, a problem is met. The simulator is the one that triggers the communication with C/C++ programs, thus a Python testbench cannot directly start the simulation. The solution lies in the Python/C application programming interface (API). This API allows the Python interpreter to be embedded into C/C++ modules, and for extension modules so Python can make use of C/C++ code<sup>(25)</sup>.

When cocotb is started, the GPI C++ library is compiled by the framework into a shared library and loaded into the simulator. At the same time, the Python interpreter is embedded into the shared library as well. When the simulation begins, the simulator triggers the Python environment through the embedded interpreter, which runs the Python testbench  $^{(24)}$  (26).

At this point, the testbench is being interpreted inside the simulator. Thus, when a call to the simulator is made (e.g., changing a signal value), the previously compiled GPI module can be used. The Python directive is communicated to the simulator through the GPI C++ extension module, and the action is performed  $^{(26)}$ .

As a non-developer user, the internals of cocotb may appear complex. Nevertheless, the expected ordinary use does not require to understand these intricacies. Thus, cocotb can simply be seen as a wrapper that allows simulation control from Python. For a block diagram description of how cocotb operates, refer to Figure 6.

Figure 6. Block diagram on the internal functioning of cocotb.

#### 3.3 Coroutines

In the context of a programming language, a subroutine can be described as a set of statements stored in memory that can be executed externally. A program might call a subroutine, wait until its completion, and then return to the caller execution flow. This behaviour allows for code reusability across a main program and can be easily exemplified with a Python function calling another function.

Coroutines, however, allow for concurrency. While a coroutine is waiting for an event to take place, the execution flow is returned to the caller function, thus freeing up resources for other actions to be executed while waiting. After the event is triggered, cocotb resumes the coroutine execution where it was previously suspended. To do so, cocotb uses a "scheduler". This structure can be seen as an execution flow manager that dictates the order in which different actions may take place.

The cocotb framework is based on the use of coroutines for advancing simulation time; like the SystemVerilog task construct. When a coroutine is waiting for an event to happen (for example, a rising edge of the clock signal), other coroutines can be executed. When the scheduler detects that all the coroutines are waiting for their events, the simulation time is advanced until one of these events is triggered. Then, the coroutines are resumed and the execution continues.

#### 3.4 Basic concepts

The following section makes use of available documentation <sup>(27)</sup> (<sup>28)</sup> to explain the basic notions needed to code a testbench using cocotb.

In the cocotb framework, the main entry point of code execution is a *test*. All functions decorated with *cocotb.test()* represent structures where calls will be made to the simulator. These functions can take multiple input arguments, but the documentation encourages the user to only use one; a handle to the DUT. A simple test can be defined as follows:

```

@cocotb.test()

async def tst_base(dut:HierarchyObject) -> None:

...

```

A testbench file can contain multiple test functions, each function's name is considered the test's name. Note that the decorated function must be a coroutine, defined by the *async* keyword. Additionally, note that type-hinting the input and output of the function is an optional characteristic of Python.

The DUT object contains the handle for every modifiable object inside it. These objects can be accessed with the standard dot (".") notation. The value of a signal can be changed as follows:

```

dut.clk.value = 0

dut.clk.setimmediatevalue(0)

```

The previous approaches to changing the value of a signal are slightly different. The former schedules the value to be changed at the end of the current simulator step. The latter changes the value immediately. Meta values can also be assigned using dedicated type structures:

dut.clk.value = Logic("X")

dut.wr\_data.value = LogicArray("01XZ")

When reading a signal, the syntax follows conventional rules, with a notable difference:

rd\_val = dut.rd\_data.value

rd\_val = dut.rd\_data

The first statement reads the value of a signal while the second one retrieves the handle of a signal; a reference. The value of a signal is expressed as an integer by default. Nonetheless, an exception will raise if the signal contains a meta value. To avoid this situation, the *value* object provides the *binstr* property that returns the signal value as a binary string.

Bit slicing is also allowed either when writing or reading a signal, as shown below:

```

rd_bit = dut.rd_data[0].value

dut.wr_data[0].value = 0

```

In cocotb, time is advanced through triggers, as explained in the coroutine subsection. When calling these triggers, the Python testbench yields control to the simulator, which in turn advances the simulation time until the trigger is fired. Afterwards, the code continues its execution. The most significant ones are:

```

await FallingEdge(dut.clk)

await RisingEdge(dut.clk)

await Edge(dut.clk)

await ClockCycles(dut.clk, 1, rising=False)

await Timer(1, units='ns')

```

The first two triggers wait for a falling and rising edge of a given signal, respectively. The third one waits until a signal changes its value. The *ClockCycles* trigger waits for n number of cycles of a signal to be completed; the *rising* keyword argument establishes if it should count rising or falling edges. The last one is a timer that waits for a specific time.

Additionally, further structures allow for the combination of multiple triggers, for example:

```

await First(FallingEdge(dut.clk), RisingEdge(dut.clk))

await Combine(FallingEdge(dut.clk), RisingEdge(dut.clk))

```

The *First* trigger waits until one of the specified triggers is completed. The *Combine* structure waits until all the triggers are completed. These types of structures, found in SystemVerilog, are of significant relevance when designing testbenches.

A testbench is not only meant to drive stimuli, but it must also compare the output signals against a designated reference. The *assert* built-in Python statement can be used to trigger an exception and finish the test if a condition is not met:

assert dut.rd\_data == 20, "Error message"

The assertion approach can be useful for errors that are considered fatal; if the assertion condition is not met, the simulation will stop executing the current test and start the next one. A less aggressive alternative is to use the logging capabilities of cocotb.

The DUT object contains a logger object from the Python built-in *logging* library. It allows to print messages of different priority levels during the simulation. The priority level can be changed, hiding messages below the specified level.

```

dut._log.debug("DEBUG")

dut._log.info("INFO")

dut._log.warn("WARNING")

dut._log.error("ERROR")

dut._log.critical("CRITICAL")

dut._log.setLevel(logging.INFO)

```

Note that the *print* Python function does not work during the execution of the simulation, as the console output is managed by the simulator. These *print* statements are buffered and will be shown once the simulator flushes the output buffer.

To run the simulation, a Makefile is used. Some parameters of the testbench to run are needed, such as the simulator to use, the HDL files of the design, the top module of the RTL code as well as the name of the Python file that contains the tests. Additional arguments for the simulator's various stages can also be provided. An example of a basic Makefile is shown:

```

# Simulator options

SIM = xcelium

TOPLEVEL LANG = verilog

# Design files

VERILOG_SOURCES += $(PWD)/design_1.v

VERILOG_SOURCES += $(PWD)/design_1_a.sv

VHDL_SOURCES

+= $(PWD)/design_1_b.vhd

# Simulator arguments

COMPILE ARGS

= -v93 -sv

RUN ARGS

= -q -gui

# Testbench description

TOPLEVEL LANG = verilog

= design 1

# Design top file

TOPLEVEL

# Python testbench file name

MODULE

= python tb

```

Note that more options can be specified in the Makefile for a more customizable execution <sup>(29)</sup>.

Once the simulation starts, running the Makefile, each of the tests will run until its completion, or until an assertion error is triggered. Once every test has finished, the simulation will end, and information on the runtime and status of each test will be displayed in the console output.

#### 3.5 PyUVM

Although the cocotb framework can be useful for rapid testing, a main problem arises when it comes to industrial adoption. The *Siemens* research study from 2022<sup>(5)</sup> showed that, for ASIC verification, the most used methodology was UVM. Additionally, the study provides data from 2014 and 2018, where this methodology was also in the lead.

The majority within the verification industry uses the UVM approach to verification, thus for an opportunity for Python-based testbenches to find their way into industrial adoption, a UVM library based upon cocotb may simplify the transition.

In this context, two open-source libraries provide a UVM framework using cocotb as their background engine: PyUVM<sup>(11)</sup> and *uvm-python*<sup>(30)</sup>. The former introduces a more Python-based approach whereas the latter can be considered a 1:1 port of SV/UVM made for users who have already knowledge of the framework using SystemVerilog. An example of this can be found in the use of the UVM "phase" object, which is not required in PyUVM. Additionally, uvm-python provides a Perl script to convert SV/UVM code into Python. Both are licensed under the Apache-2.0 license, which also allows for its free usage and implementation in industrial environments.

Although uvm-python may appear the best option for this project, it is also important to note that PyUVM presents a more promising future perspective. The latter has had more updates and community activity to its repository in recent years than uvm-python. Furthermore, the author has also published a book on how to use the cocotb and PyUVM libraries <sup>(31)</sup>. It is also significant to note that PyUVM has received support from *Siemens*, featuring a series of online blogs dedicated to its usage <sup>(32)</sup>.

For these reasons, the availability of resources, community activity, and sponsorship of *Siemens*, this project will use the PyUVM library.

The PyUVM testbenches are structured as the SV/UVM ones. Its reference guide provides enough information on how to set up the verification environment, how to connect the components, and how to run the simulation, which makes use of the same type of Makefile as cocotb.

Nevertheless, the user must have some knowledge of cocotb. SV/UVM connects its agents to the DUT through an *interface* struct, which is a SystemVerilog construct, not a UVM one. Python does not provide an equivalent object, so the user must code an additional object: a *Bus Functional Model* (BFM).

By its simplest description, the BFM will connect the DUT to the driver and the monitor. It must be able to receive sequence items and translate them into DUT signals, and monitor the DUT signals and send a sequence item containing them. To perform these operations, the BFM will use cocotb triggers such as *RisingEdge* or *FallingEdge* to time when to drive and when to monitor signals. Additionally, signals will be written and read which also requires cocotb knowledge.

The following code snippets are shown to demonstrate the simplicity of PyUVM for the creation of an agent and its components, except the coverage class for directness. Note that this is a minimal implementation of a basic UVM agent. Additionally, the inherited classes are imported from the PyUVM library.

This sequence item has two transactional variables. When the item is created it can optionally receive a value for each, defaulting to 0 if not found. An additional function is written, which randomizes the value of one variable.

```

class MySeqItem(uvm_sequence_item):

def __init__(self, name:str="m_item", **kwargs) -> None:

super().__init__(name)

self.i_wr_data = kwargs.get("i_wr_data", 0)

self.o_rd_data = kwargs.get("o_rd_data", 0)

def randomize(self) -> None:

self.i_wr_data = randint(0, pow(2,32)-1)

```

The next object is the BFM. It provides a queue of a single space for the driving items and an infinite queue for the monitored items. It also has direct access to the DUT pins. Two functions are dedicated to handle the interaction with the queues, and an additional function resets the input signal. Finally, two background functions are initiated when *start* is called. The *\_driver* structure waits for the next rising edge of the clock signal and waits until there is an item in the driver queue; once the item is found the input signal is relayed to the DUT. The *\_monitor* function on the other hand waits for the falling edge of the clock signal and then creates a sequence item in which it stores the signal values from the DUT; it then stores the item in the monitor queue.

```

class MyBfm():

def __init__(self) -> None:

self.dut

= cocotb.top

self._driver_q = Queue(maxsize=1)

self. monitor q = Queue(maxsize=0)

async def get_item(self) -> MySeqItem:

seq item = await self. monitor q.get()

return seq item

async def send_item(self, m_item:MySeqItem) -> None:

await self. driver q.put(m item)

async def reset(self) -> None:

self.dut.i_wr_data.setimmediatevalue(0)

await RisingEdge(self.dut.clk)

async def _driver(self) -> None:

while True:

await RisingEdge(self.dut.clk)

seq item : MySeqItem = await self. driver q.get()

self.dut.i_wr_data.value = seq_item.i_wr_data

async def _monitor(self) -> None:

while True:

await FallingEdge(self.dut.clk)

seq_item = MySeqItem("seq_item")

seq_item.i_wr_data = self.dut.i_wr_data.value

seq item.i rd data = self.dut.i rd data.value

self._monitor_q.put_nowait(seq_item)

def start(self) -> None:

start soon(self. driver())

start_soon(self._monitor())

```

The following snippets refer to the monitor and the driver components. Each of them retrieves the BFM object from a shared database. The monitor additionally creates a port to communicate with other components.

The driver object applies the reset of the BFM and starts its background functions. Afterwards, it waits until the sequencer sends a new sequence item and then forwards it to the BFM driver queue. The monitor waits until there is a new monitored item from the BFM and then sends it through its port.

```

class MyDriver(uvm driver):

def build phase(self):

self.bfm = ConfigDB().get(None, "", "my_bfm")

async def run_phase(self):

await self.bfm.reset()

self.bfm.start()

while True:

seq_item = await self.seq_item_port.get_next_item()

await self.bfm.send item(seq item)

self.seq_item_port.item_done()

class MyMonitor(uvm monitor):

def build phase(self):

self.bfm = ConfigDB().get(None, "", "my bfm")

self.analysis_port = uvm_analysis_port("analysis_port", self)

async def run_phase(self):

while True:

seq item = await self.bfm.get item()

self.analysis_port.write(seq_item)

```

Finally, the agent class creates the driver, the monitor, a sequencer, and a port. Subsequently, the driver is connected to sequencer and the monitor port is connected to the agent port.

```

class MyAgent(uvm_agent):

def build_phase(self):

super().build_phase()

self.m_seqr = uvm_sequencer("m_seqr", self)

self.m_driver = MyDriver("m_driver", self)

self.m_monitor = MyMonitor("m_monitor", self)