# Hybrid caches: design and data management

ALEJANDRO VALERO BRESÓ

EDITORIAL UNIVERSITAT POLITÈCNICA DE VALÈNCIA

## Universitat Politècnica de València Departamento de Informática de Sistemas y Computadores

## Hybrid Caches: Design and Data Management

A thesis submitted in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy (Computer Engineering)

> > Author

Alejandro Valero Bresó

Advisors

Prof. Julio Sahuquillo Borrás Prof. Salvador V. Petit Martí

September 2013

First Edition, 2013

© Alejandro Valero Bresó

© of the present edition: Editorial Universitat Politècnica de València /

www.lalibreria.upv.es

ISBN: 978-84-9048-137-0 (printed version) Publishing reference: 5662

Any unauthorized copying, distribution, marketing, editing, and in general any other exploitation, for whatever reason, of this piece of work or any part thereof, is strictly prohibited without the authors' expressed and written permission.

## Doctoral Committee

• Prof. Ramon Canal Corretger

Universitat Politècnica de Catalunya, Barcelona, Spain.

- Prof. José F. Duato Marín

Universitat Politècnica de València, Valencia, Spain.

- Prof. María Engracia Gómez Requena

Universitat Politècnica de València, Valencia, Spain.

- Prof. Antonio González Colás

Intel Labs and Universitat Politècnica de Catalunya, Barcelona, Spain.

- Prof. David R. Kaeli Northeastern University, Boston, MA, USA.

## Agraïments

Aquest treball ha requerit de l'esforç de moltes persones perquè es pogués dur a terme. M'agradaria començar pels meus directors de tesi Julio i Salva. Gràcies per haver confiat en mi i per transmetre'm els vostres coneixements i il·lusió per la reçerca en arquitectura de computadors. Als meus pares Carmen i Antonio, les meues àvies Carmen i Vicenta, la meua nóvia Amelia, i en definitiva a tota la meua família i amics, gràcies pel vostre suport, companyia i afecte al llarg de tots aquests anys.

Vull agrair l'esforç de la resta d'autors de les nostres publicacions científiques, José, Pedro, Vicent i Ramon, que amb els seus coneixements i experiència m'han ajudat a millorar la qualitat del treball que es presenta en aquesta tesi.

També m'agradaria destacar l'ajuda prestada i el magnífic ambient de treball creat per tots els becaris, professors i altres membres que han format part del Departament d'Informàtica de Sistemes i Computadors durant aquest temps.

Moltes gràcies per tot!

## Contents

| $\mathbf{A}$  | bstra | $\mathbf{ct}$ |             |                                          |   | xi                     |

|---------------|-------|---------------|-------------|------------------------------------------|---|------------------------|

| R             | esum  | en            |             |                                          | 3 | xiii                   |

| R             | esum  |               |             |                                          |   | $\mathbf{x}\mathbf{v}$ |

| $\mathbf{Li}$ | st of | Figure        | es          |                                          | x | vii                    |

| $\mathbf{Li}$ | st of | Tables        | 8           |                                          | 3 | xix                    |

| $\mathbf{A}$  | bbrev | viation       | s and Ac    | cronyms                                  | 3 | xxi                    |

| 1             | Intr  | oducti        | on          |                                          |   | 1                      |

|               | 1.1   | Backg         | round       |                                          |   | 2                      |

|               |       | 1.1.1         | Memory      | Technologies                             |   | 2                      |

|               |       |               | 1.1.1.1     | Static Random-Access Memory (SRAM)       |   | 2                      |

|               |       |               | 1.1.1.2     | Leakage Reduction Techniques for SRAM    |   | 3                      |

|               |       |               | 1.1.1.3     | Dynamic Random-Access Memory (DRAM)      |   | 3                      |

|               |       |               | 1.1.1.4     | Other Memory Technologies and Cells      |   | 5                      |

|               |       | 1.1.2         | Last-Lev    | el Caches                                |   | 6                      |

|               |       |               | 1.1.2.1     | Replacement Algorithms                   |   | 6                      |

|               |       |               | 1.1.2.2     | Refresh Mechanisms                       |   | 8                      |

|               | 1.2   | Object        | tives of th | e Thesis                                 |   | 10                     |

|               | 1.3   | Contri        | butions of  | f the Thesis                             |   | 11                     |

|               | 1.4   | Thesis        | Outline     |                                          |   | 12                     |

| <b>2</b>      | Hyb   |               |             | RAM L1 Data Cache Architecture           |   | 13                     |

|               | 2.1   |               | 0           | oposal                                   |   | 14                     |

|               | 2.2   |               |             | esign Issues                             |   | 16                     |

|               |       | 2.2.1         |             | g the eDRAM Ways                         |   |                        |

|               |       | 2.2.2         |             | g the Percentage of Hits in the SRAM Way |   |                        |

|               |       | 2.2.3         |             | Writeback Policies                       |   |                        |

|               | 2.3   |               |             | valuation                                |   |                        |

|               |       | 2.3.1         |             | on Framework                             |   | 23                     |

|               |       | 2.3.2         | Performa    |                                          |   | 25                     |

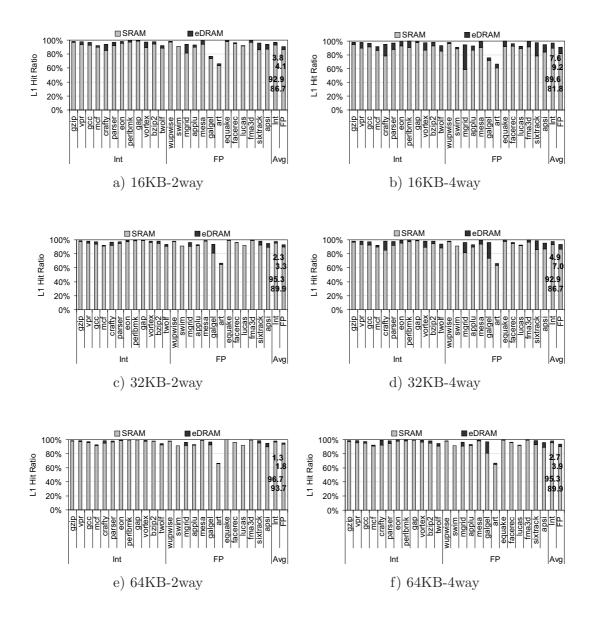

|               |       |               | 2.3.2.1     | SRAM and eDRAM Hit Ratio                 |   | 25                     |

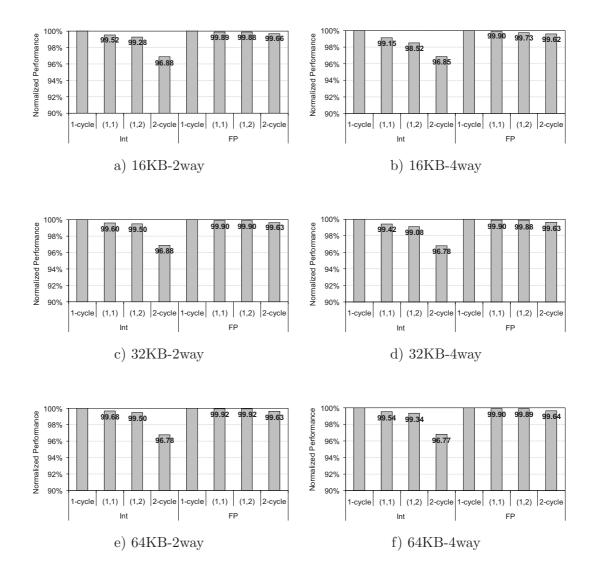

|               |       |               | 2.3.2.2     | Impact of eDRAM Access Time              |   | 26                     |

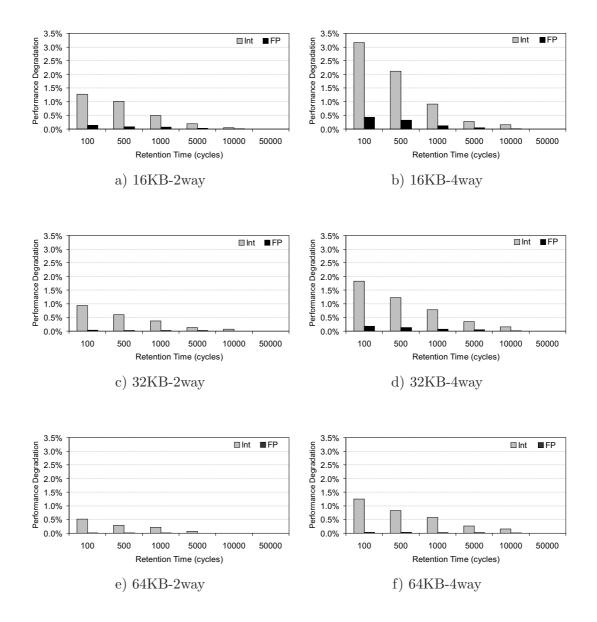

|               |       |               | 2.3.2.3     | Impact of Retention Time                 |   | 28                     |

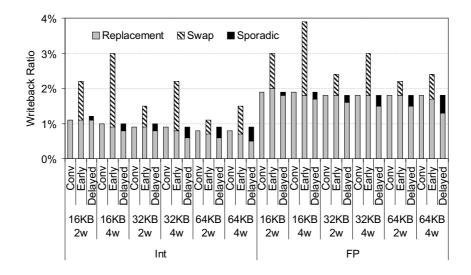

|          |      | 2.3.2.4 Writeback Policies                                                                                        | . 29 |

|----------|------|-------------------------------------------------------------------------------------------------------------------|------|

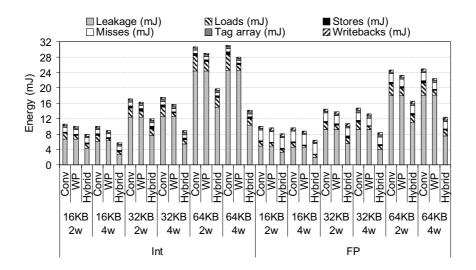

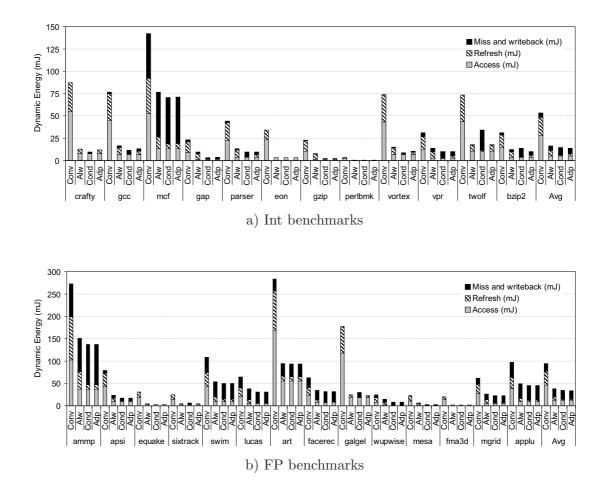

|          |      | 2.3.3 Energy Consumption                                                                                          | . 31 |

|          |      | $2.3.3.1  Methodology \ldots \ldots$ | . 31 |

|          |      | 2.3.3.2 Energy Results                                                                                            | . 32 |

|          |      | 2.3.4 Area Savings                                                                                                | . 34 |

|          | 2.4  | Summary                                                                                                           | . 35 |

| 3        | Hył  | rid eDRAM/SRAM L2 Cache Architecture                                                                              | 37   |

|          | 3.1  | Motivation                                                                                                        | . 38 |

|          | 3.2  | Hybrid Last-Level Cache Design                                                                                    | . 40 |

|          |      | 3.2.1 Accessing the Hybrid Cache: Bank-Prediction                                                                 | . 41 |

|          |      | 3.2.2 Keeping the Last Accessed Blocks in SRAM Banks                                                              | . 41 |

|          |      | 3.2.3 Distributed Refresh                                                                                         | . 43 |

|          | 3.3  | Experimental Evaluation                                                                                           | . 44 |

|          |      | 3.3.1 Area                                                                                                        | . 45 |

|          |      | 3.3.2 Performance                                                                                                 | . 46 |

|          |      | 3.3.3 Energy Consumption                                                                                          | . 50 |

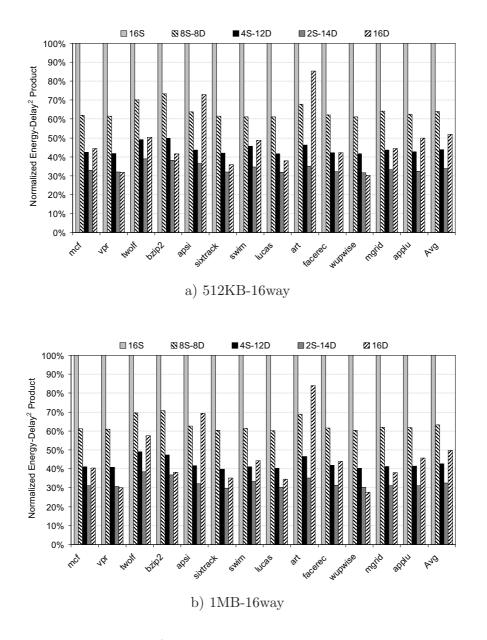

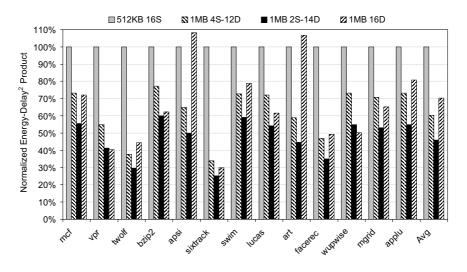

|          |      | 3.3.4 Energy-Delay Squared Product                                                                                | . 53 |

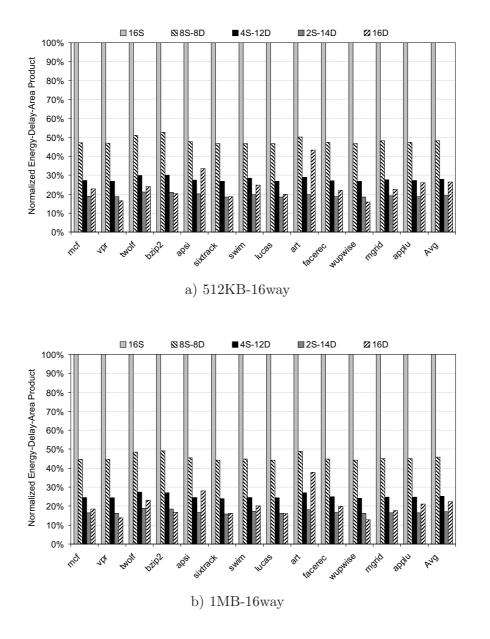

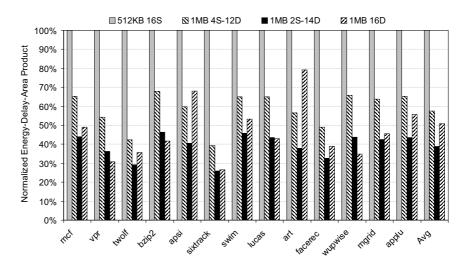

|          |      | 3.3.5 Energy-Delay-Area Product                                                                                   | . 55 |

|          | 3.4  | Contemporary Hybrid Architectures                                                                                 | . 57 |

|          | 3.5  | Summary                                                                                                           | . 58 |

| 4        | MR   | J-Tour Replacement Algorithms                                                                                     | 61   |

|          | 4.1  | Weaknesses of LRU                                                                                                 | . 62 |

|          | 4.2  | MRUT Concept and MRUT-based Algorithms                                                                            | . 63 |

|          |      | 4.2.1 Overview                                                                                                    | . 63 |

|          |      | 4.2.2 MRUT-based Algorithms                                                                                       | . 64 |

|          | 4.3  | MRUT Patterns                                                                                                     | . 65 |

|          | 4.4  | Experimental Evaluation                                                                                           | . 67 |

|          |      | 4.4.1 Performance of the Baseline MRUT                                                                            | . 67 |

|          |      | 4.4.2 Enhancing MRUT Performance                                                                                  | . 68 |

|          |      | 4.4.3 Introducing the Victim Cache                                                                                | . 73 |

|          |      | 4.4.4 Comparison Against Other Recent Approaches                                                                  |      |

|          | 4.5  | Hardware Complexity                                                                                               |      |

|          | 4.6  | Reuse Information and Other Replacement Algorithms                                                                |      |

|          | 4.7  | Summary                                                                                                           | . 82 |

| <b>5</b> | Sele | tive Refresh                                                                                                      | 85   |

|          | 5.1  | Energy-Aware eDRAM and Hybrid Cache Architectures                                                                 |      |

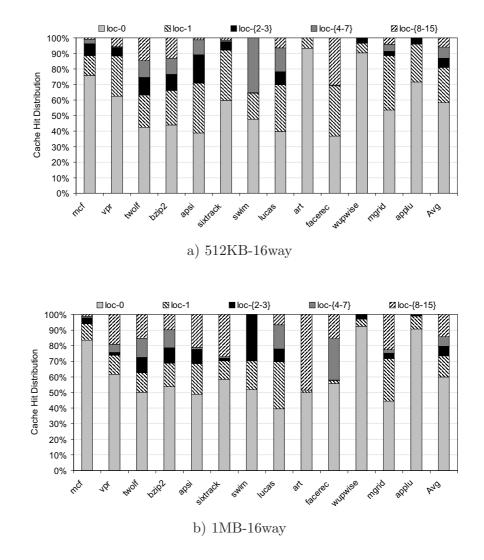

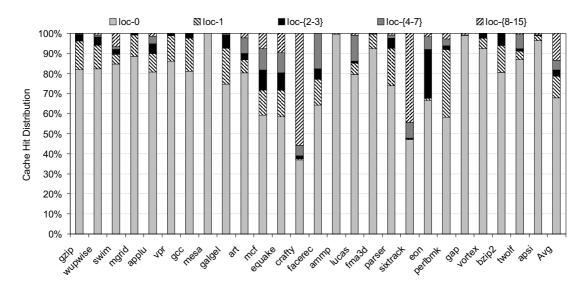

|          |      | 5.1.1 Cache Hit Distribution and Bank-Prediction                                                                  | . 86 |

|          |      | 5.1.2 Coupling the MRUT Algorithm with the Proposed Caches                                                        |      |

|          |      | 5.1.3 Selective Refresh Policies                                                                                  |      |

|          | 5.2  | Experimental Evaluation                                                                                           |      |

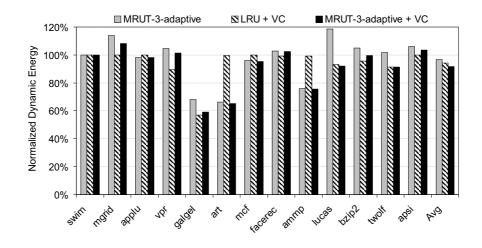

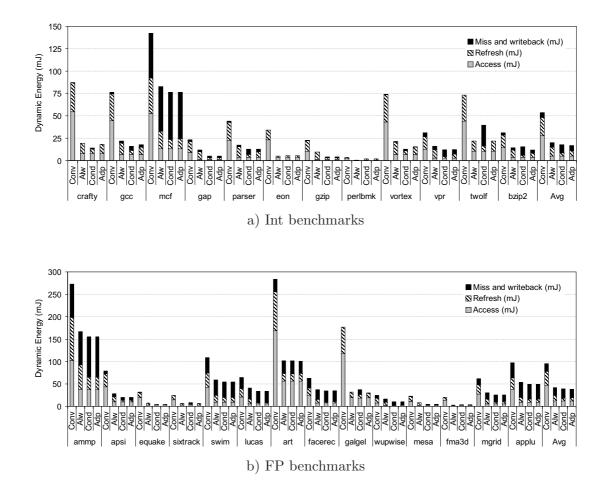

|          |      | 5.2.1 Energy Consumption                                                                                          |      |

|          |      | 5.2.2 Performance                                                                                                 |      |

|          | 5.3  | Refresh Mechanisms in Off-Chip Memories                                                                           |      |

|          | 5.4  | Summary                                                                                                           | . 98 |

| 6  | Conclusions |                   |    |  |  |  |  |

|----|-------------|-------------------|----|--|--|--|--|

|    | 6.1         | Contributions     | 02 |  |  |  |  |

|    | 6.2         | Future Directions | 03 |  |  |  |  |

|    | 6.3         | Publications      | 04 |  |  |  |  |

| Re | efere       | nces 10           | 09 |  |  |  |  |

### Abstract

Cache memories have been usually implemented with Static Random-Access Memory (SRAM) technology since it is the fastest electronic memory technology. However, this technology consumes a high amount of leakage currents, which is a major design concern because leakage energy consumption increases as the transistor size shrinks. Alternative technologies are being considered to reduce this consumption. Among them, embedded Dynamic RAM (eDRAM) technology provides minimal area and leakage by design but reads are destructive and it is not as fast as SRAM.

In this thesis, both SRAM and eDRAM technologies are mingled to take the advantatges that each of them offers. First, they are combined at cell level to implement an *n*-bit *macrocell* consisting of one SRAM cell and *n-1* eDRAM cells. The macrocell is used to build *n*-way set-associative hybrid first-level (L1) data caches having one SRAM way and *n-1* eDRAM ways. A single SRAM way is enough to achieve good performance given the high data locality of L1 caches. Architectural mechanisms such as way-prediction, swaps, and scrub operations are considered to avoid unnecessary eDRAM reads, to maintain the Most Recently Used (MRU) data in the *fast* SRAM way, and to completely avoid refresh logic. Experimental results show that, compared to a conventional SRAM cache, leakage and area are largely reduced with a scarce impact on performance.

The study of the benefits of hybrid caches has been also carried out in second-level (L2) caches acting as Last-Level Caches (LLCs). In this case, the technologies are combined at bank level and the optimal ratio of SRAM and eDRAM banks that achieves the best trade-off among performance, energy, and area is identified. Like in L1 caches, the MRU blocks are kept in the SRAM banks and they are accessed first to avoid many eDRAM reads. Nevertheless, refresh logic is not removed since data locality widely differs in this cache level. Experimental results show that a hybrid LLC with an eighth of its banks built with SRAM technology is enough to achieve the best target trade-off.

This dissertation also deals with performance of replacement policies in heterogeneous LLCs mainly focusing on the energy overhead incurred by refresh operations. In this thesis it is defined a new concept, namely MRU-Tour (MRUT), that helps estimate reuse information of cache blocks. Based on this concept, it is proposed a family of MRUTbased replacement algorithms that randomly select the victim block among those having a single MRUT. These policies are enhanced to leverage recency of information for a few blocks and to adapt to changes in the working set of the benchmarks. Results show that the proposed MRUT policies, with simpler hardware complexity, outperform the Least Recently Used (LRU) policy and a set of the most representative state-of-the-art replacement policies for LLCs.

Refresh operations represent an important fraction of the overall dynamic energy consumption of eDRAM LLCs. This fraction increases with the cache capacity, since more blocks have to be refreshed for a given period of time. Prior works have attacked the refresh energy taking into account inter-cell feature variations. Unlike these works, this thesis proposes a selective refresh policy based on the MRUT concept. The devised policy takes into account the number of MRUTs of a block to select whether the block is refreshed. In this way, many refreshes done in a typical distributed refresh policy are skipped (i.e., in those blocks having a single MRUT). This refresh mechanism is applied in the hybrid LLC memory. Results show that refresh energy consumption is largely reduced with respect to a conventional eDRAM cache, while the performance degradation is minimal with respect to a conventional SRAM cache.

### Resumen

Las memorias caché o *cache* han sido implementadas normalmente con tecnología *Static Random-Access Memory* (SRAM) ya que es la tecnología de memoria electrónica más rápida. Sin embargo, esta tecnología consume una gran cantidad de corrientes de fuga, lo cual es un problema de diseño importante porque el consumo de corrientes de fuga incrementa a medida que el tamaño del transistor encoge. Se están considerando tecnologías alternativas para reducir este consumo. Entre ellas, la tecnología embedded *Dynamic* RAM (eDRAM) ofrece por diseño un área y corrientes de fuga mínimas pero las lecturas son destructivas y no es tan rápida como SRAM.

En esta tesis, ambas tecnologías SRAM y eDRAM se mezclan para conseguir las ventajas que cada una de ellas ofrece. En primer lugar, se combinan a nivel de celda para implementar una macrocelda de n-bits consistente en una celda SRAM y n-1 celdas eDRAM. La macrocelda se utiliza para construir caches híbridas de datos de primer nivel (L1) asociativas por conjuntos de n-vías que tienen una vía SRAM y n-1 vías eDRAM. Una sola vía SRAM es suficiente para conseguir buenas prestaciones dado que la localidad de los datos en caches L1 es elevada. Mecanismos arquitectónicos como predicción de vía, intercambio de datos (swaps) y operaciones de scrub se consideran para evitar lecturas eDRAM innecesarias, mantener los datos más recientemente utilizados (MRU) en la vía SRAM rápida y eliminar completamente la lógica de refresco. Los resultados experimentales muestran que, comparado con una cache convencional SRAM, las corrientes de fuga y área se reducen considerablemente con un impacto escaso en las prestaciones.

El estudio de los beneficios de las caches híbridas también se ha llevado a cabo en caches de segundo nivel (L2) actuando como caches de último nivel (LLCs). En este caso, las tecnologías se combinan a nivel de banco y se identifica el ratio óptimo de bancos SRAM y eDRAM que consigue el mejor compromiso entre prestaciones, energía y área. Como en las caches L1, los bloques MRU se mantienen en los bancos SRAM y se acceden primero para evitar muchas lecturas eDRAM. Sin embargo, la lógica de refresco no se elimina ya que la localidad de los datos difiere ampliamente en este nivel de cache. Los resultados experimentales muestran que una LLC híbrida con un octavo de sus bancos implementados con tecnología SRAM es suficiente para conseguir el mejor compromiso.

Esta disertación también se ocupa de las prestaciones de las políticas de reemplazo en LLCs heterogéneas centrándose principalmente en la sobrecarga de energía incurrida por las operaciones de refresco. En esta tesis se define un concepto nuevo, llamado MRU-Tour (MRUT), que ayuda a la estimación de información de reuso de los bloques de cache. Basándose en este concepto, se propone una familia de algoritmos de reemplazo basados en MRUT que seleccionan aleatoriamente los bloques víctima entre aquellos que tienen un solo MRUT. Estas políticas se mejoran para hacer uso de la recencia de información de unos pocos bloques y adaptarse a los cambios en el comportamiento de las aplicaciones. Los resultados muestran que las políticas MRUT propuestas, con menor complejidad *hardware*, mejoran las prestaciones de *Least Recently Used* (LRU) y de un conjunto representativo del estado del arte de algoritmos de reemplazo para las LLC.

Las operaciones de refresco representan una fracción importante del consumo total de energía dinámica de las LLC eDRAM. Esta fracción incrementa con la capacidad de cache, ya que una cantidad mayor de bloques tienen que ser refrescados en un periodo de tiempo dado. Algunos trabajos anteriores han atacado la energía de refresco teniendo en cuenta las variaciones de los componentes entre celdas. A diferencia de estos trabajos, esta tesis propone una política de refresco selectiva basada en el concepto de MRUT. La política ideada tiene en cuenta el número de MRUTs de un bloque para seleccionar si el bloque se refresca. De esta manera, muchos refrescos realizados en una política de refresco típica y distribuida se omiten, es decir, en aquellos bloques que tienen un solo MRUT. Este mecanismo de refresco se aplica en la memoria LLC híbrida. Los resultados muestran que el consumo de energía de refresco se reduce ampliamente respecto a una cache convencional eDRAM, mientras que la degradación de prestaciones es mínima respecto a una cache convencional SRAM.

### Resum

Les memòries cau o *cache* han estat normalment implementades amb tecnologia *Static Random-Access Memory* (SRAM) ja que és la tecnologia de memòria electrònica més ràpida. No obstant això, aquesta tecnologia consumeix una gran quantitat de corrents de fugida, la qual cosa és un problema de disseny important perquè el consum de corrents de fugida incrementa a mesura que la grandària del transistor encongeix. S'estan considerant tecnologies alternatives per reduir aquest consum. Entre elles, la tecnologia *embedded Dynamic* RAM (eDRAM) ofereix per disseny un àrea i corrents de fugida mínimes però les lectures són destructives i no és tan ràpida com SRAM.

En aquesta tesi, ambdues tecnologies SRAM i eDRAM es barregen per aconseguir els avantatges que cadascuna d'elles ofereix. En primer lloc, es combinen a nivell de cel·la per implementar una macrocel·la de n-bits consistent en una cel·la SRAM i n-1 cel·les eDRAM. La macrocel·la s'utilitza per construir caches híbrides de dades de primer nivell (L1) associatives per conjunts de n-vies que tenen una via SRAM i n-1 vies eDRAM. Una sola via SRAM és suficient per aconseguir bones prestacions atès que la localitat de les dades en caches L1 és elevada. Mecanismes arquitectònics com predicció de via, intercanvi de dades (swaps) i operacions de scrub es consideren per evitar lectures eDRAM innecessàries, mantenir les dades més recentment utilitzades (MRU) en la via SRAM ràpida i eliminar completament la lògica de refresc. Els resultats experimentals mostren que, comparat amb una cache convencional SRAM, els corrents de fugida i àrea es redueixen considerablement amb un impacte escàs en les prestacions.

L'estudi dels beneficis de les caches híbrides també s'ha dut a terme en caches de segon nivell (L2) actuant com caches d'últim nivell (LLCs). En aquest cas, les tecnologies es combinen a nivell de banc i s'identifica el ràtio òptim de bancs SRAM i eDRAM que aconsegueix el millor compromís entre prestacions, energia i àrea. Com en les caches L1, els blocs MRU es mantenen als bancs SRAM i s'accedeixen primer per a evitar moltes lectures eDRAM. No obstant això, la lògica de refresc no s'elimina ja que la localitat de les dades difereix àmpliament en aquest nivell de cache. Els resultats experimentals mostren que una LLC híbrida amb un vuitè dels seus bancs implementats amb tecnologia SRAM és suficient per aconseguir el millor compromís.

Aquesta dissertació també s'ocupa de les prestacions de les polítiques de reemplaçament en LLCs heterogènies centrant-se principalment en la sobrecàrrega d'energia incorreguda per les operacions de refresc. En aquesta tesi es defineix un concepte nou, anomenat MRU-Tour (MRUT), que ajuda a l'estimació d'informació de reús dels blocs de cache. Basant-se en aquest concepte, es proposa una família d'algorismes de reemplaçament basats en MRUT que seleccionen aleatòriament els blocs víctima entre aquells que tenen un sol MRUT. Aquestes polítiques es milloren per fer ús de la recència d'informació d'uns pocs blocs i adaptar-se als canvis en el comportament de les aplicacions. Els resultats mostren que les polítiques MRUT propostes, amb menor complexitat *hardware*, milloren les prestacions de *Least Recently Used* (LRU) i d'un conjunt representatiu de l'estat de l'art d'algorismes de reemplaçament per les LLC.

Les operacions de refresc representen una fracció important del consum total d'energia dinàmica de les LLC eDRAM. Aquesta fracció incrementa amb la capacitat de cache, ja que una quantitat major de blocs han de ser refrescats en un període de temps donat. Alguns treballs anteriors han atacat l'energia de refresc tenint en compte les variacions dels components entre cel·les. A diferència d'aquests treballs, aquesta tesi proposa una política de refresc selectiva basada en el concepte de MRUT. La política ideada té en compte el nombre de MRUTs d'un bloc per seleccionar si el bloc es refresca. D'aquesta manera, molts refrescs realitzats en una política de refresc típica i distribuïda s'ometen, és a dir, en aquells blocs que tenen un sol MRUT. Aquest mecanisme de refresc s'aplica en la memòria LLC híbrida. Els resultats mostren que el consum d'energia de refresc es redueix àmpliament respecte a una cache convencional eDRAM, mentre que la degradació de prestacions és mínima respecte a una cache convencional SRAM.

# List of Figures

| 1.1  | 6T SRAM cell. Labels $WL$ and $Vdd$ refer to the wordline and supply voltage, respectively, whereas labels $BL$ and $/BL$ refer to the bitline and |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | its complementary, respectively                                                                                                                    | 3  |

| 1.2  | 1T-1C DRAM cell. Label $C$ refers to the capacitor of the cell                                                                                     | 4  |

| 1.3  | Dynamic energy split into expenses due to refresh and non-refresh oper-                                                                            |    |

|      | ations in conventional eDRAM LLCs.                                                                                                                 | 9  |

| 2.1  | Block diagram of an $n$ -bit macrocell                                                                                                             | 14 |

| 2.2  | Static to dynamic write operation details                                                                                                          | 17 |

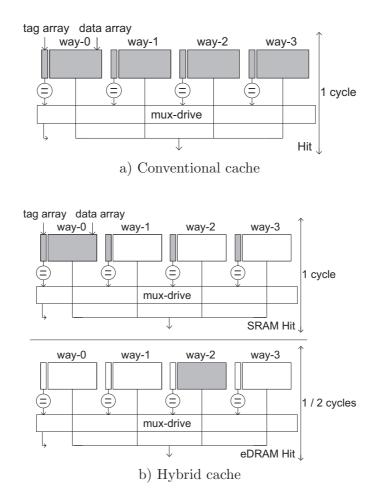

| 2.3  | Access and timing of conventional and hybrid caches                                                                                                | 19 |

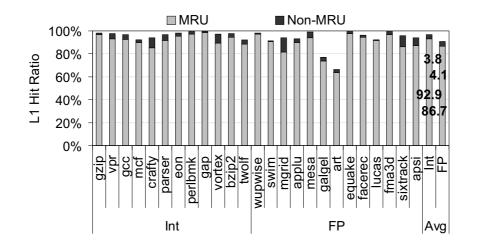

| 2.4  | L1 hit ratio (%) in a conventional 64B-line 16KB-2way cache                                                                                        | 20 |

| 2.5  | Swap operation details.                                                                                                                            | 20 |

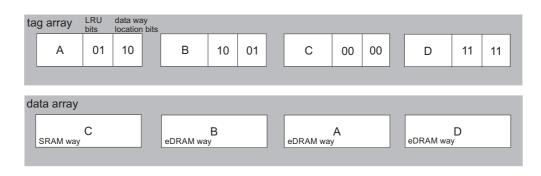

| 2.6  | Diagram of a 4-way cache with the control information to maintain the                                                                              |    |

|      | mapping between tags and data blocks.                                                                                                              | 21 |

| 2.7  | L1 hit ratio (%) for different hybrid cache organizations. $\ldots$                                                                                | 26 |

| 2.8  | Normalized performance (%) with respect to the conventional cache for different access times (in processor cycles)                                 | 27 |

| 2.9  | IPC losses (%) with respect to the perfect hybrid cache for different re-                                                                          |    |

|      | tention times (in processor cycles)                                                                                                                | 29 |

| 2.10 | Writeback ratio (%) for the devised policies and the conventional cache. $% \mathcal{C}(\mathcal{A})$ .                                            | 30 |

| 2.11 | Energy consumption (in mJ) for the analyzed schemes                                                                                                | 32 |

| 3.1  | Percentage of cache hits across the locations of the LRU stack. $\ldots$ .                                                                         | 39 |

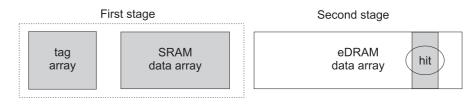

| 3.2  | Diagram of the hybrid cache access. Dark boxes represent the accessed<br>parts of the cache. The second stage is performed only on a hit in an     |    |

|      | eDRAM way detected in the first stage.                                                                                                             | 41 |

| 3.3  | Diagrams of the involved actions in an eDRAM hit and a cache miss to                                                                               |    |

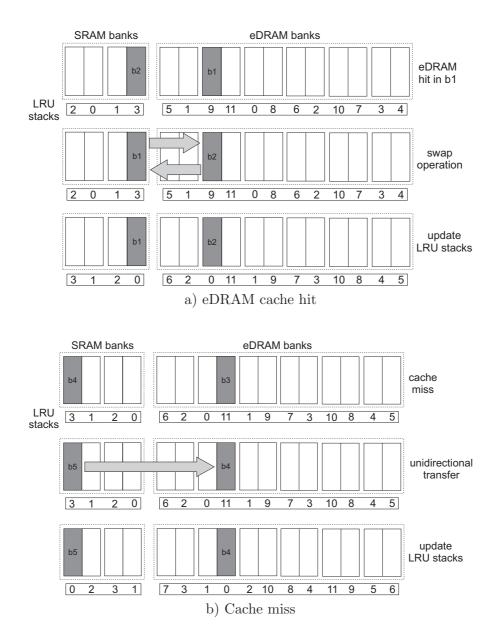

|      | keep the MRU data in SRAM banks                                                                                                                    | 42 |

| 3.4  | Area (in $mm^2$ ) of the analyzed caches. The circle groups those 1MB                                                                              |    |

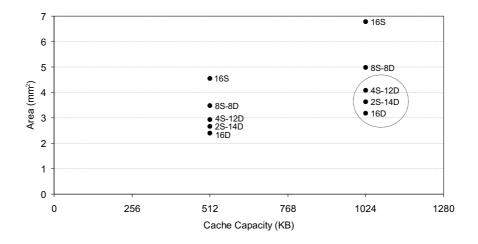

|      | eDRAM-based configurations with less area than the 512KB SRAM cache.                                                                               | 45 |

| 3.5  | Hit ratio (%) split into hits in SRAM and eDRAM banks. XS-YD con-                                                                                  |    |

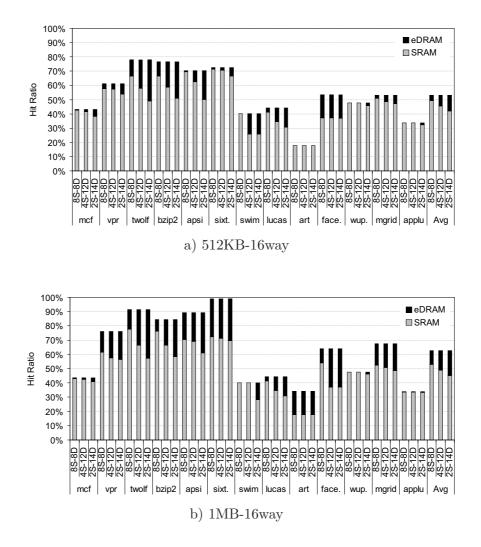

|      | figuration refers to a hybrid cache having X ways in SRAM banks and Y                                                                              |    |

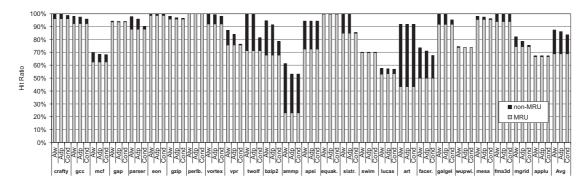

|      | 0                                                                                                                                                  | 47 |

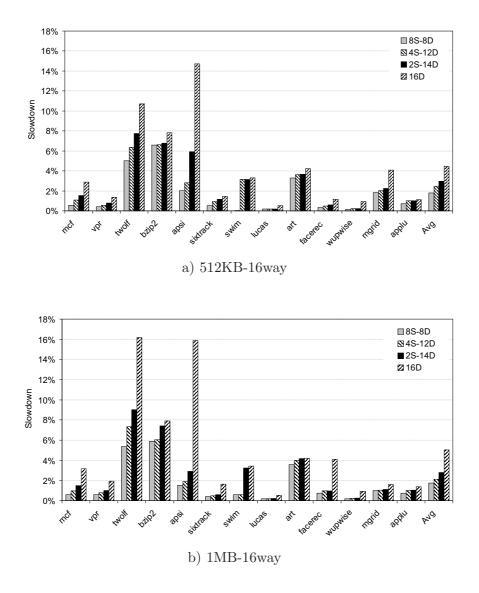

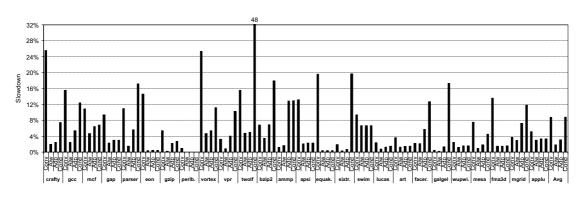

| 3.6  | Slowdown (%) of the analyzed cache configurations with respect to the                                                                              | 40 |

| 0.7  | pure SRAM cache on the basis of capacity.                                                                                                          | 48 |

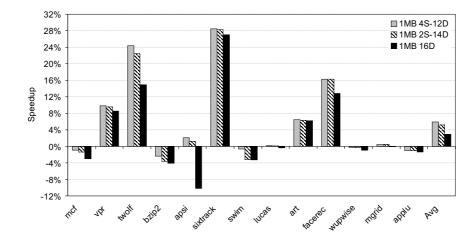

| 3.7  | Speedup (%) of the selected 1MB eDRAM-based caches with respect to the SRAM scheme on the basis of area.                                           | 40 |

| 90   | Normalized $ED^2P$ (%) with respect to the pure SRAM approach on the                                                                               | 49 |

| 3.8  | Normalized $ED^2P$ (%) with respect to the pure SRAM approach on the basis of capacity.                                                            | 54 |

|      | Dasis of Capacity                                                                                                                                  | 04 |

| 3.9   | Normalized $ED^2P$ (%) with respect to the pure SRAM scheme on the basis of area.                                                           | 55    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.10  | Normalized EDAP (%) with respect to the pure SRAM approach on the basis of capacity.                                                        | 56    |

| 3.11  | Normalized EDAP (%) with respect to the pure SRAM cache on the basis of area.                                                               | 57    |

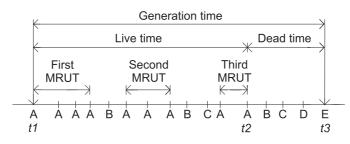

| 4.1   | Generation time of the cache block A                                                                                                        | 63    |

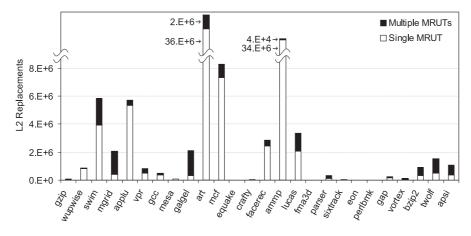

| 4.2   | Number of replacements split into single and multiple MRUTs                                                                                 | 64    |

| 4.3   | Baseline MRUT algorithm.                                                                                                                    | 65    |

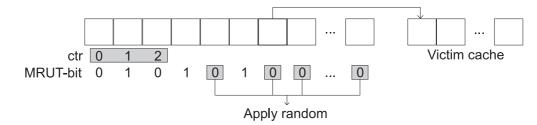

| 4.4   | Block diagram of the MRUT-3 policy working with a victim cache                                                                              | 67    |

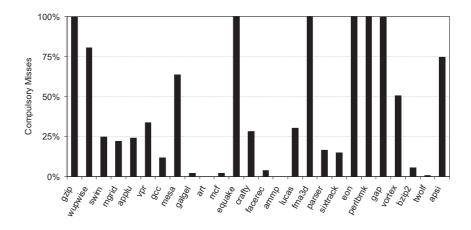

| 4.5   | Percentage of compulsory misses                                                                                                             | 68    |

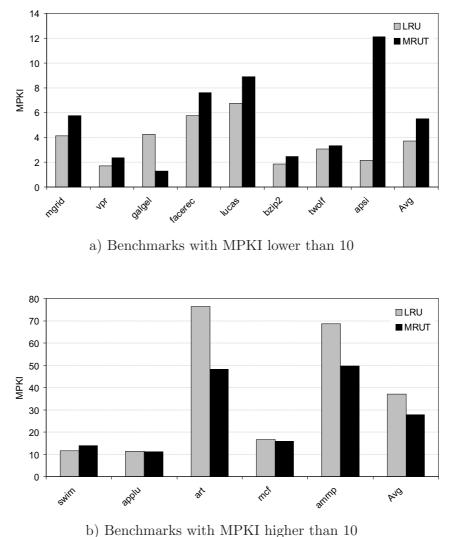

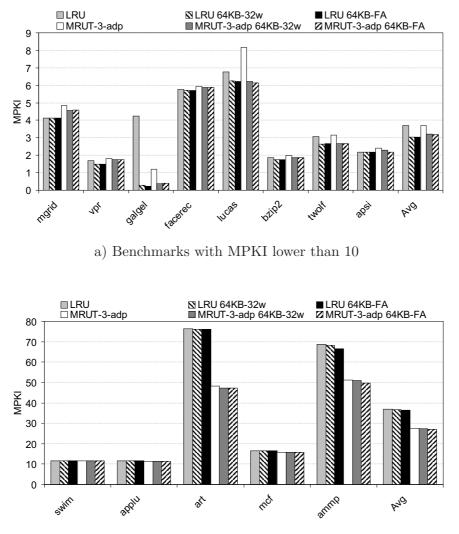

| 4.6   | MPKI of the baseline MRUT and LRU algorithms                                                                                                | 69    |

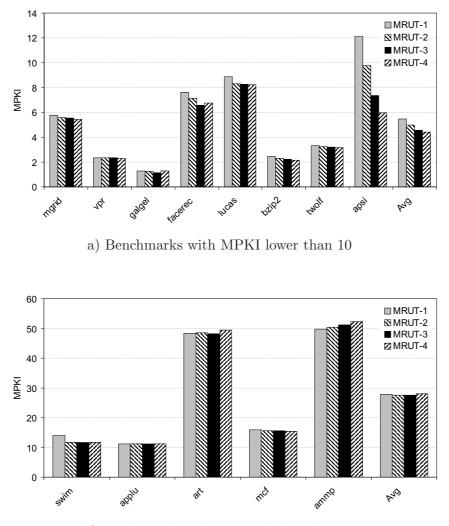

| 4.7   | MPKI of MRUT- $x$ algorithms varying $x$ from 1 to 4                                                                                        | 70    |

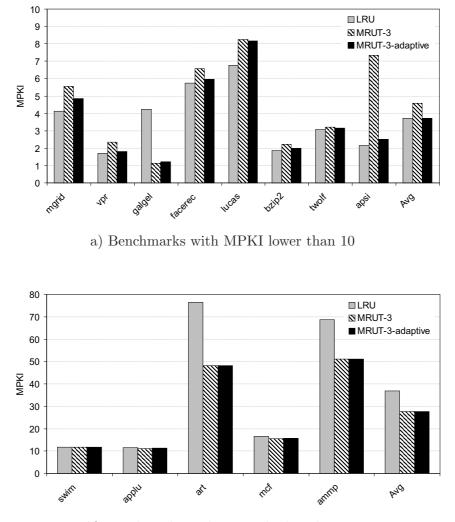

| 4.8   | MPKI achieved by MRUT-3-adaptive, MRUT-3, and LRU algorithms                                                                                | 72    |

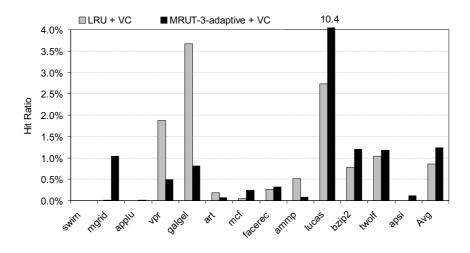

| 4.9   | MPKI of MRUT-3-adaptive working with victim cache.                                                                                          | 74    |

| 4.10  | Hit ratio $(\%)$ in the victim cache                                                                                                        | 75    |

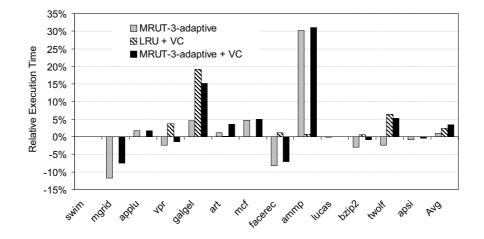

| 4.11  | Impact $(\%)$ of adding a victim cache in the relative execution time with                                                                  | 75    |

| 4 1 9 | respect to strict LRU                                                                                                                       | 75 76 |

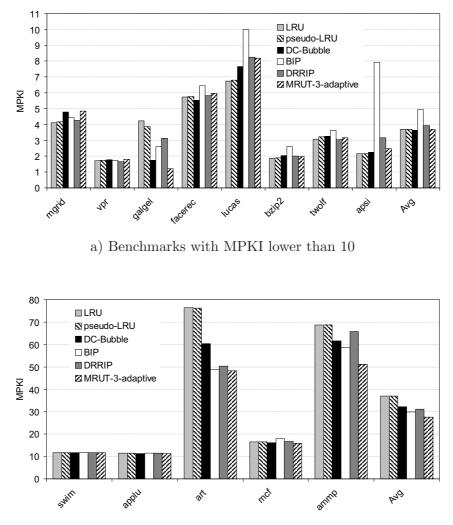

|       | MPKI achieved by MRUT-3-adaptive, pseudo-LRU, LRU, and other re-<br>cent policies (DRRIP, BIP, and DC-Bubble).                              | 70    |

|       |                                                                                                                                             |       |

| 5.1   | Percentage of cache hits across the ways of a 2MB-16way L2 cache using the MRUT policy.                                                     | 86    |

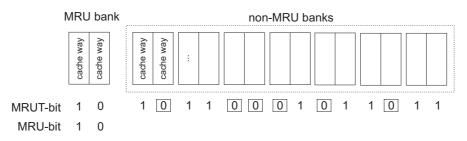

| 5.2   | Diagram of the data array of the energy-aware eDRAM cache with the control bits of the MRUT algorithm.                                      | 88    |

| 5.3   | Dynamic energy (in mJ) of the conventional eDRAM cache and the energy-<br>aware eDRAM cache for the studied refresh policies.               | 91    |

| 5.4   | Dynamic energy (in mJ) of the conventional eDRAM cache and the hybrid                                                                       | 01    |

| 0.1   | cache for the proposed refresh policies                                                                                                     | 93    |

| 5.5   | Hit ratio (%) split into hits in the MRU and non-MRU banks of the                                                                           |       |

|       | energy-aware eDRAM cache for the studied refresh policies                                                                                   | 94    |

| 5.6   | Slowdown (%) of the conventional eDRAM cache and the energy-aware<br>eDRAM cache for the proposed refresh policies with respect to the con- |       |

|       | ventional SRAM cache.                                                                                                                       | 95    |

| 5.7   | Slowdown (%) of the conventional eDRAM cache and the hybrid cache                                                                           |       |

|       | for the proposed refresh policies with respect to the conventional SRAM                                                                     |       |

|       | cache                                                                                                                                       | 96    |

## List of Tables

| 1.1 | Memory technology characteristics                                                                      | 5  |

|-----|--------------------------------------------------------------------------------------------------------|----|

| 2.1 | Architectural machine parameters                                                                       | 24 |

| 2.2 | Tag array and data array area (in $mm^2$ ) for both conventional and hybrid schemes                    | 35 |

| 3.1 | Pure and hybrid caches with the corresponding number of ways, banks, and ratio (%) of SRAM banks       | 40 |

| 3.2 | Leakage and dynamic energy consumption (in mJ) and the reduction (%) compared to the pure SRAM scheme. | 50 |

| 4.1 | Probability of a block to be referenced again using the LRU algorithm                                  | 62 |

| 4.2 | MRUT patterns. Numbers in the cells indicate the number of MRUTs                                       |    |

|     | exhibited during the generation times                                                                  | 66 |

| 4.3 | MPKI of MRUT-3 varying the reset interval                                                              | 71 |

| 4.4 | Area overhead (in number of control bits) in an <i>n</i> -way cache (per set)                          |    |

|     | and a 1MB-16way cache for the studied algorithms.                                                      | 80 |

|     |                                                                                                        |    |

# Abbreviations and Acronyms

| Adp                  | Adaptive                                                                                                                                                                                                                                                                                                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AIP                  | Access Interval Predictor                                                                                                                                                                                                                                                                                 |

| Alw                  | Always                                                                                                                                                                                                                                                                                                    |

| BIP                  | Bimodal Insertion Policy                                                                                                                                                                                                                                                                                  |

| BRRIP                | $\mathbf{B}\mathrm{imodal}\ \mathbf{R}\mathrm{e}\text{-}\mathbf{R}\mathrm{e}\mathrm{f}\mathrm{e}\mathrm{r}\mathrm{e}\mathrm{r}\mathrm{e}\mathrm{I}\mathrm{t}\mathrm{e}\mathrm{r}\mathrm{v}\mathrm{a}\mathrm{I}\mathbf{P}\mathrm{r}\mathrm{e}\mathrm{d}\mathrm{i}\mathrm{t}\mathrm{i}\mathrm{o}\mathrm{i}$ |

| Cond                 | Conditional                                                                                                                                                                                                                                                                                               |

| Conv                 | Conventional                                                                                                                                                                                                                                                                                              |

| DC                   | Divide-and-Conquer                                                                                                                                                                                                                                                                                        |

| DIP                  | Dynamic Insertion Policy                                                                                                                                                                                                                                                                                  |

| DRAM                 | $\mathbf{D} \mathrm{ynamic} \ \mathbf{R} \mathrm{andom}\text{-}\mathbf{A} \mathrm{ccess} \ \mathbf{M} \mathrm{emory}$                                                                                                                                                                                     |

| DRRIP                | <b>D</b> ynamic <b>Re-R</b> eference Interval <b>P</b> rediction                                                                                                                                                                                                                                          |

| ECC                  | Error Correcting Codes                                                                                                                                                                                                                                                                                    |

| EDAP                 | $\mathbf{E}$ nergy- $\mathbf{D}$ elay- $\mathbf{A}$ rea $\mathbf{P}$ roduct                                                                                                                                                                                                                               |

| eDRAM                | embedded Dynamic Random-Access Memory                                                                                                                                                                                                                                                                     |

| $ED^2P$              | Energy-Delay squared Product                                                                                                                                                                                                                                                                              |

| $\mathbf{FP}$        | $\mathbf{F}$ loating- $\mathbf{P}$ oint                                                                                                                                                                                                                                                                   |

| IPC                  | Instructions Per Cycle                                                                                                                                                                                                                                                                                    |

| $\mathbf{Int}$       | Integer                                                                                                                                                                                                                                                                                                   |

| LIP                  | ${\bf L} east \ Recently \ Used \ {\bf I} nsertion \ {\bf P} olicy$                                                                                                                                                                                                                                       |

| LLC                  | Last-Level Cache                                                                                                                                                                                                                                                                                          |

| $\mathbf{LRU}$       | Least Recently Used                                                                                                                                                                                                                                                                                       |

| $\operatorname{LvP}$ | $\mathbf{Live-time} \ \mathbf{P}$ redictor                                                                                                                                                                                                                                                                |

| L1                   | First-level                                                                                                                                                                                                                                                                                               |

| L2                   | Second-level                                                                                                                                                                                                                                                                                              |

| MPKI                 | Misses Per Kilo-Instruction                                                                                                                                                                                                                                                                               |

| MRAM  | $\mathbf{M} \mathbf{agnetic} \ \mathbf{R} \mathbf{andom} \textbf{-} \mathbf{A} \mathbf{ccess} \ \mathbf{M} \mathbf{emory}$ |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MRU   | Most Recently Used                                                                                                         |  |  |  |

| MRUT  | Most Recently Used-Tour                                                                                                    |  |  |  |

| PRAM  | $\mathbf{P} \text{hase-change } \mathbf{R} \text{andom-} \mathbf{A} \text{ccess } \mathbf{M} \text{emory}$                 |  |  |  |

| RRIP  | $\operatorname{\mathbf{Re-Reference}}$ Interval $\operatorname{\mathbf{Prediction}}$                                       |  |  |  |

| SRAM  | ${\bf S} {\bf tatic} \ {\bf R} {\bf andom} {\bf -} {\bf A} {\bf ccess} \ {\bf M} {\bf emory}$                              |  |  |  |

| SRRIP | Static Re-Reference Interval Prediction                                                                                    |  |  |  |

| VC    | Victim Cache                                                                                                               |  |  |  |

| WP    | Way-Prediction                                                                                                             |  |  |  |

## Chapter 1

## Introduction

This chapter introduces some concepts and presents the motivation for the work developed in this thesis. First, different semiconductor memory technologies are discussed, showing their advantages and shortcomings. Then, the concept of Last-Level Cache (LLC) is presented, and several issues related to these memories are discussed. Finally, a summary about how the rest of this dissertation deals with hybrid cache designs and their data management is given.

#### 1.1 Background

Computer architects have implemented cache memories [1] since late 1960s to mitigate the huge gap between processor and main memory speed. Caches have been normally built with Static Random-Access Memory (SRAM) technology since it is the fastest electronic memory technology. However, SRAM incurs in high *leakage* or static energy consumption, which is a major design concern given that this consumption aggravates as the transistor size shrinks [2]. Thus, many leakage reduction techniques have been proposed to mitigate this problem. Alternative technologies are also being considered. For instance, Dynamic RAM (DRAM) technology provides minimal leakage currents by design, but it has not been used to build caches because DRAM is difficult and expensive to implement in logic-circuit technology.

Current microprocessors implement two or three cache levels to reduce the difference in speed between processor and main memory. To reduce this penalty, LLCs are designed as large memory structures, which significantly increases leakage consumption. Due to this reason, LLCs are suitable for logic-compatible embedded DRAM or simply eDRAM technology. However, the main drawbacks of eDRAM are that its reads are destructive, it requires refresh operations, and it is not as fast as SRAM. Finally, researchers also have noted that the LRU replacement algorithm does not reach good performance in LLCs. One of the main reasons is that data locality in these memories is filtered by the inner cache levels.

#### 1.1.1 Memory Technologies

#### 1.1.1.1 Static Random-Access Memory (SRAM)

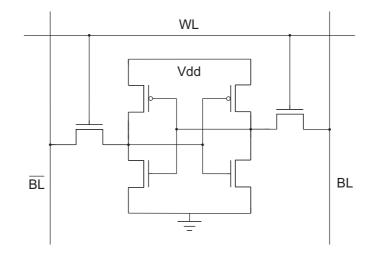

Until now, SRAM has been the predominant technology used to build memory cells in computer systems. SRAM cells are typically implemented with six transistors (6T cells). Figure 1.1 illustrates the structure of a 6T SRAM cell. These cells are usually designed for speed, which is the main reason because of they are used in cache memories, especially in the first levels of the memory hierarchy. However, the major drawbacks of SRAM-based caches are that they occupy a significant percentage of the overall die area in current multicore processors and consume an important amount of energy, especially

FIGURE 1.1: 6T SRAM cell. Labels WL and Vdd refer to the *wordline* and supply voltage, respectively, whereas labels BL and /BL refer to the *bitline* and its complementary, respectively.

leakage energy which is proportional to the number of transistors. Furthermore, this design concern aggravates as the transistor size continues shrinking. Therefore, using SRAM cells impacts both in area and leakage currents.

#### 1.1.1.2 Leakage Reduction Techniques for SRAM

Leakage energy reduction in SRAM cells has been widely investigated in the last decade. The proposed techniques can be classified into two main categories depending on whether the cache block state is preserved or not. In the first category, the supply voltage to selected cache lines is reduced and these lines remain in state-preserving low-power mode, so increasing the access time to such lines [3] [4]. In the second group, the supply voltage to the cache blocks with poorer locality is removed; thus, losing the block information [5] [6]. Subsequent accesses to such blocks will result on a cache miss; thus, the next level of the memory hierarchy must be accessed.

#### 1.1.1.3 Dynamic Random-Access Memory (DRAM)

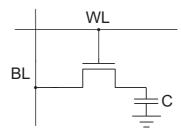

Leakage currents can also be reduced taking into account alternative technologies like DRAM, which is typically used for main memory. Figure 1.2 depicts the structure of a 1T-1C DRAM cell. Unlike SRAM cells, DRAM cells only require an active power supply during the memory access so their leakage currents are reduced by design. For

FIGURE 1.2: 1T-1C DRAM cell. Label C refers to the capacitor of the cell.

a given technology node, these cells require less area than SRAM cells since they are implemented with only one capacitor and the corresponding pass transistor. However, these cells present two major drawbacks that make them inappropriate for processor caches: low speed and information loss.

Regarding the first issue, technology advances have permitted to embed DRAM cells using CMOS technology [7]. An eDRAM cell integrates a trench DRAM storage cell into a logic-circuit technology and provides similar access delays as those presented by SRAM cells. As a consequence, some recent commercial processors such as some IBM POWER processors use eDRAM technology to build huge second-level (L2) caches or LLCs [8] [9] [10] [11].

The latter drawback is caused because capacitors in both DRAM and eDRAM cells store data as charge, which is lost either when contents are read (destructive read) or progressively with time. The elapsed time since the capacitor is charged until the contents are lost is referred to as retention time. To avoid capacitor discharges, contents are periodically read out and written back in a process known as refreshing. Refresh operations consume additional energy and affect performance since they compete for memory with regular processor requests. This is a major design concern in first-level (L1) caches, where data availability is critical. On the other hand, the refresh energy problem is expected to aggravate in future technologies with much higher memory storage capacities. For instance, as reported in [12], refresh consumption is expected to rise up to 50% in future 64Gb DRAM chips.

An important advantage of eDRAM technology is that it can be manufactured by logic technologies with minimal changes in the manufacturing process. This means that SRAM and eDRAM technologies can be mingled in the same die to obtain the best

| Technology | Speed | Density | Leakage | Refresh<br>logic | Destructive<br>reads | logic-circuit<br>compatible |

|------------|-------|---------|---------|------------------|----------------------|-----------------------------|

| SRAM       | fast  | low     | high    | no               | no                   | yes                         |

| DRAM       | slow  | high    | low     | yes              | yes                  | no                          |

| eDRAM      | slow  | high    | low     | yes              | yes                  | yes                         |

TABLE 1.1: Memory technology characteristics.

of each technology as already performed by some companies [13]. Table 1.1 summarizes the main design characteristics of the discussed memory technologies.

#### 1.1.1.4 Other Memory Technologies and Cells

Apart from the technologies discussed in this chapter, several technologies are being developed, especially non-volatile technologies, such as Magnetic RAM (MRAM) and Phase-change RAM (PRAM or PCM) [14] [15] [16].

The non-volatile property of these technologies allow them to consume less leakage than eDRAM. MRAM and PRAM also provide high density, their reads are not destructive, and they do not require refresh operations. However, manufacturing constraints prevent from mixing them with logic-circuit technology using conventional two-dimensional (2D) chips. In addition, the low speed and dynamic energy consumed by these technologies, in particular for write operations, suggest that they are more appropriate for main memory storage instead of caches.

Other research works have focused on the design of new *DRAM-like* cells for caches. Liang *et al.* [17] proposed the 3T1D (three transistors and a diode) DRAM cell. The speed of this cell is comparable to the speed of 6T SRAM cells. Thus, 3T1D cells can be used for critical latency structures such as L1 data caches. However, although reads are non-destructive, the diode charge get lost over time, requiring from refresh schemes that might have a severe impact on performance. The 3T1D cell can be smaller than the 6T SRAM cell but, the smaller the cell size the lower the retention time of the diode capacitance.

Juang *et al.* [18] proposed a dynamic cell from a 6T SRAM cell which does not include the two transistors connected to Vdd that restore the charge loss due to leakage currents. Thus, the circuit results in a non-static cell with only 4 transistors (the quasi-static 4T cell). This cell offers an easy method for DRAM implementation in a logic process production, especially in embedded systems. Compared to 6T SRAM cells, the 4T cells require less area. In contrast, the data access is a bit slower and destructive. Like in the 1T-1C cell, this problem can be solved by re-writing the read data immediately after the read operation or before the retention time expires.

#### 1.1.2 Last-Level Caches

LLCs are designed as very large memory structures in order to keep as much information as possible so reducing capacity misses. Therefore, their sizes range from several hundreds of KB up to several tens of MB [11] [19]. In addition, in order to keep low the number of conflict misses, current LLCs implement a high number of ways (e.g., 16 or more ways).

#### 1.1.2.1 Replacement Algorithms

Typically, cache memories exploit temporal locality by implementing the Least Recently Used (LRU) replacement algorithm. This algorithm acts as a stack that places the Most Recently Used (MRU) block on the top of the stack (MRU position) and the LRU block, which is the evicted block when space is required, on the bottom (LRU position). Although this algorithm works well in L1 caches with a low number of ways; with high associativities, like 8 and 16 ways that are currently found in LLCs, strict LRU is too expensive to implement. Therefore, approximations to LRU are the norm in commercial processors but their performance start to deviate from the strict LRU [20].

On the other hand, the performance of the LRU algorithm in LLCs is quite far from the optimal replacement strategy referred to as Belady's algorithm [21]. There are several reasons that explain why the LRU algorithm does not work well in LLCs with high associativity. First, most accesses that hit in the inner caches are hidden to LLC so information about temporal locality is lost. Second, LRU suffers from thrashing effects in those workloads whose working set is greater than the available cache size, resulting in cyclic accesses to blocks that *walk* through the stack without being reused. Third, LRU forces a block to descend down to the bottom of the stack before eviction, which may severely impact on performance since most blocks that are brought into the LLC are not referenced again once they leave the MRU position (see Section 4.2). For example, in a

16-way cache, a given block that leaves the MRU position and is not referenced again will not be evicted until fifteen distinct blocks mapping to the same set are accessed. This means that, instead, some useful blocks might be removed from the cache set so hurting the performance. Recent research works have focused on how to improve this shortcoming by predicting when a block can be evicted while it is still walking the LRU stack to the bottom [22] [23] [24].

The following replacement policies are some of the most representative state-of-the-art alternatives to the LRU policy in LLCs to date, and they will be compared against the policy proposed in this thesis. Other replacement strategies can be found in Section 4.6.

The Bubble algorithm [25], proposed by Zhang and Xue, unlike the LRU scheme, uses a queue instead of a stack that works as follows. An incoming block is allocated at the bottom of the queue, which is the location with the lowest access frequency. Anytime a block hits again, it is promoted one-position upwards the queue. In this way, the blocks closer to the top of the queue evince a higher access frequency than those closer to the bottom. When there is a lack of space, the block to be evicted is selected either from the bottom or the top of the queue, depending on whether the previous access to that set resulted in a cache miss or a cache hit, respectively. This work also presents a Divideand-Conquer technique referred to as DC-Bubble, which divides the blocks in each cache set into independent groups, so that each group has its own replacement logic. In this scheme, when a block is fetched, the target group within the set is randomly selected. These schemes exploit both recency of information and frequency information and adapt to changes in the working set.

In [26], three adaptive insertion policies based on LRU are proposed. The first one, referred to as LRU Insertion Policy (LIP), inserts all incoming blocks in the LRU position, and then they are promoted to the MRU position if they are referenced again. This behavior prevents LIP from the effect of cache thrashing. The second one, namely Bimodal Insertion Policy (BIP), differs from LIP in that every x cache misses, the incoming block is inserted in the MRU position. This policy adapts to changes in the working set and, like LIP, provides thrashing protection. Finally, the third policy, referred to as Dynamic Insertion Policy (DIP), dynamically combines LRU and BIP using the Set Dueling strategy. DIP uses a small fraction of the cache sets to measure the

performance of each policy, and applies to the remaining sets the policy that achieves the best performance.

Jaleel *et al.* [27] propose a family of algorithms based on Re-Reference Interval Prediction (RRIP) of cache blocks to deal with cache thrashing and bursts of accesses to non-temporal data. The simplest version, called Static RRIP (SRRIP) policy, uses a saturating counter per cache block to predict whether the block will be re-referenced sooner or later in the future. On a cache insertion, the distance prediction of the incoming block is set to be in the *distant future* (i.e., the counter is set to its maximum value), while subsequent accesses to this block reduce its distance prediction to be in the *near future* (i.e., decrease the counter by one each time the block is accessed). The victim block is selected among those blocks predicted to be accessed in the distant future. If there are not candidates, all the counters are increased by one until one of them saturates. An enhancement of SRRIP is the Bimodal RRIP (BRRIP) policy. It differs from SRRIP in that every x cache misses the counter of the incoming block is set to its maximum value minus one. Finally, both SRRIP and BRRIP policies were used together using Set Dueling as done in [26], resulting in the Dynamic RRIP (DRRIP) policy.

#### 1.1.2.2 Refresh Mechanisms

Prior research works have concentrated on reducing the refresh energy by avoiding unnecessary refresh operations in off-chip DRAM memories. Regular read accesses to memory implicitly trigger a refresh operation since DRAM contents are written back after they are read. Based on this fact, some works have focused on delaying periodic refreshes of frequently requested data [28]. Other works take into account the inter-cell variation in retention time to enhance the refresh logic in order to adapt the refresh period for each memory row [12] [29] [30]. Error-Correcting Codes (ECC) have been also used to recover lost data due to extended refresh periods [31]. Finally, refresh can be skipped for data identified as *useless* [29]. Please refer to Section 5.3 for further information.

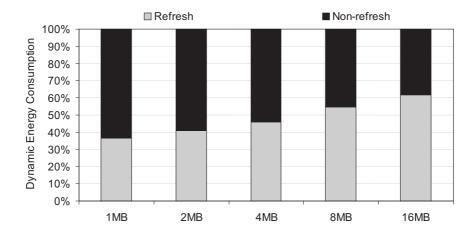

Like in their counterparts off-chip DRAM memories, refresh operations in eDRAM LLCs represent an important fraction of the total dynamic energy consumption of these devices as shown in Figure  $1.3^1$ . As observed, refresh energy increases with the cache capacity

<sup>&</sup>lt;sup>1</sup>These results have been obtained with the machine parameters and methodology presented in Section 5.2.

FIGURE 1.3: Dynamic energy split into expenses due to refresh and non-refresh operations in conventional eDRAM LLCs.

and grows up to 62% for a 16MB cache. This is because more cache lines have to be refreshed for a given retention time, which in eDRAM caches is by thousand times shorter than in off-chip DRAM memories [32].

Due to their different characteristics, the refresh techniques proposed for off-chip DRAM devices are not suitable for on-chip eDRAM caches. First, the access time among external DRAM Dual In-line Memory Modules (DIMMs) and the next level of the hierarchy (e.g., disks) is at least six orders of magnitude higher (from ns to ms), thus less aggressive techniques should be used since the misspeculation penalty (i.e., a useful memory row is not refreshed and then requested) is much higher. In contrast, techniques especially designed for on-chip caches can be much more aggressive. Second, main memory is not organized as a cache, so techniques such as way-prediction cannot be applied. Third, external memory works at coarse (row or page) granularity, typically a couple of KB. Instead, on-chip caches work with relatively smaller data blocks (e.g., 64 bytes).

The refresh problem in eDRAM caches has been previously attacked taking into account inter-cell feature variations [32] [33]. These works are orthogonal to the selective refresh proposed in this thesis. In [33], Emma *et al.* proposed to learn the appropriate refresh period from each cache set via a regressive process. Initially, this process assumes the worst-case refresh period for the entire cache. Then, refresh periods are increased step by step until ECC detect data losses. In this way, the best refresh period for each cache set is detected. Wilkerson *et al.* [32] proposed an ECC optimization to identify expired data due to enlarged refresh periods. This approach provides both single-bit and multi-bit failure detection. The single-bit error can be corrected, while those sections of the cache with multi-bit errors are disabled to avoid the high latency and complexity of multi-bit error correction.

Another recent work [34] delays periodic refreshes taking into account the implicit refresh of regular accesses. In addition, authors propose a refresh policy that makes use of a 5-bit counter per cache line. The counter is set to its maximum value when the line is accessed or written back, and it is decremented on each periodic refresh to the line. When the counter reaches zero, the line is written back and set to valid if dirty, or invalidated if non-dirty. This mechanism requires more hardware complexity and area than the single-bit per line refresh policy proposed in this dissertation.

#### 1.2 Objectives of the Thesis

The main objective of this dissertation is leveraging SRAM and eDRAM technologies in order to build a hybrid cache hierarchy that optimizes performance and reduces energy consumption. In addition, architectural design issues like refresh mechanisms and replacement algorithms are tackled in both L1 data caches and L2 caches acting as LLCs. Compared to a conventional SRAM cache, the performance degradation of hybrid caches is minimal because the most likely data blocks to be referenced are stored in *fast* SRAM technology, while eDRAM technology is used to store the remaining blocks so providing significant leakage and area savings.

For LLCs, based on the observation that most cache blocks are not referenced again once they leave the MRU position of the LRU stack, a set of replacement algorithms aware of this property are proposed to reduce hardware complexity and to obtain better performance than the traditional LRU policy. Finally, regarding the refresh problem, a selective refresh mechanism is devised. Compared to a conventional refresh method, the proposed selective refresh reduces the number of periodic refreshes by skipping refresh operations in those blocks that are candidates for eviction.

#### 1.3 Contributions of the Thesis

The four major contributions of this thesis are described below:

- A hybrid eDRAM/SRAM cache architecture for L1 data caches is developed. Both semiconductor technologies are mingled at cell level to form an *n*-bit macrocell, which consists of one SRAM cell, *n-1* eDRAM cells, and *n-1 bridge* transistors that communicate the SRAM cell with the corresponding eDRAM cells. The macrocell is used to build the data array of *n*-way set-associative hybrid caches. These memories implement one SRAM way and *n-1* eDRAM ways. Architectural mechanisms are devised to maintain the MRU data in the fast SRAM way and to completely avoid refresh logic.

- Since the macrocell design could be expensive to implement in high-associative caches, this thesis combines both SRAM and eDRAM technologies at bank level to build hybrid L2 caches. Like in the hybrid L1 cache, the MRU contents are stored in SRAM technology. Since temporal locality is much less predictable in L2 caches, the optimal ratio of SRAM and eDRAM ways is explored to achieve the best trade-off among performance, energy, and area.

- A family of low-cost replacement algorithms for LLCs is introduced, which exploits reuse information by leveraging the concept of MRU-Tour (MRUT). The number of MRUTs of a block is defined as the number of times that the block is placed in the MRU position while it resides in cache. In this dissertation it is shown that most blocks are not accessed again once they leave the MRU location. Thus, these policies select as candidates for eviction those blocks having a single MRUT.

- A selective refresh policy to minimize the number of periodic refresh operations is proposed. The devised mechanism aims to avoid energy wasting due to refreshing useless blocks, which are identified by exploiting the MRUT concept. The selective refresh policy does not refresh those blocks that have experienced one MRUT, and it is applied in both pure eDRAM and hybrid eDRAM/SRAM L2 caches.

### 1.4 Thesis Outline

This dissertation is composed of six chapters. Chapter 2 and Chapter 3 introduce the hybrid eDRAM/SRAM architecture for L1 and L2 caches, respectively. Chapter 4 presents the MRUT replacement algorithm. Chapter 5 describes the selective refresh mechanism, and finally, Chapter 6 summarizes this thesis, discusses future work, and enumerates the related publications.

## Chapter 2

# Hybrid eDRAM/SRAM L1 Data Cache Architecture

This chapter introduces the hybrid eDRAM/SRAM architecture for L1 data caches. First, the implementation of the macrocell and the architecture design issues are presented. Then, experimental results including performance, energy consumption, and area are discussed.

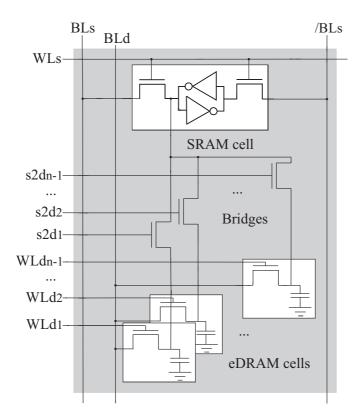

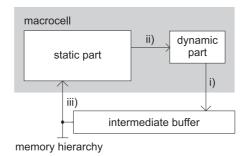

FIGURE 2.1: Block diagram of an *n*-bit macrocell.

## 2.1 Memory Cell Proposal

The main components of an *n*-bit macrocell are a typical SRAM cell, *n-1* eDRAM cells, and *n-1* bridge transistors communicating the SRAM cell and the corresponding eDRAM cell. Figure 2.1 depicts the implementation of an *n*-bit macrocell. The *static* part is limited to only one SRAM cell mainly due to leakage and area reasons. It has the same structure as a typical 6T SRAM cell. Thus, read and write operations in this part are managed like in a typical static cell through the bitline (*BLs*) and its complementary (*/BLs*).

The dynamic part is composed of n-1 eDRAM cells, each one working like a typical 1T-1C DRAM cell. Each capacitor has an NMOS pass transistor (controlled by  $WLd_i$ ) that keeps the capacitor charge insulated from the bitline (*BLd*). Like in the static part, read and write operations are performed as in a conventional eDRAM cell through the corresponding pass transistor.

Information movements among SRAM to eDRAM cells imply two main steps in a conventional design: i) read the SRAM cell content and write it to an intermediate buffer and ii) read the buffer and write its content to the eDRAM cell. The main novelty of the proposed design is that bridge transistors enable unidirectional transfers of data from the SRAM cell to the eDRAM cells. Each bridge transistor is controlled by a distinct  $s2d_i$  signal. In this way, the information state in the SRAM cell can be copied directly to one of the capacitors, that is, no intermediate buffer is required. These transfers will be referred to as internal since no bitline is involved.

Notice that implementing a cache using macrocells instead of splitting the L1 cache in two different organizations (a standard SRAM cache and an independent eDRAM cache) has important advantages. First, some resources (e.g., decoder and wordline) can be shared. Second, when using two independent caches, the internal transfers (i.e., moving a block from static to dynamic part) involve more circuitry and wire delays, which might prohibitively increase latency and energy dissipation.

In order to check the correctness of the electronic behavior, the proposed cell has been modeled in NGSPICE, a Berkeley's Spice3f5-based circuit simulator. NGSPICE allows MOSFET behavior to be accurately simulated since it uses BSIM4 MOSFET model. All simulations used the Predictive Technology Models (PTM) [35]. Transistor features have been taken from the 2007 ITRS [2] for a 45nm technology node.

Two main design issues were addressed to ensure the correct functionality of the proposed cell: i) to check that the capacitor is properly charged and ii) the absence of flips when moving data from the SRAM cell to an eDRAM cell. Regarding the former issue, the main problem in a typical 1T-1C cell is the voltage degradation when writing a logic '1' to the capacitor. This is due to NMOS pass transistors incur a voltage drop equal to Vth when they transfer a logic '1'. Thus, in order to charge the capacitor to the maximum Vdd voltage, wordlines are usually boosted to a voltage Vpp = Vdd + Vth. In eDRAM cells, Vth and Vdd are normally set to 0.4 and 1.1V, respectively, for a 45nm technology node. Regarding the macrocell, the wordlines controlled by  $WLd_i$  and  $s2d_i$ must be also boosted.

Concerning the second design issue, read operations in conventional SRAM cells must be preceded by precharging high both bitlines. Precharge operations are necessary to optimize the cell speed, area, and stability relationship [36]. This is mainly due to the different features of NMOS and PMOS transistors. In this way, flips are avoided inside the cell since NMOS transistors are stronger (i.e., they can drive more current) than PMOS transistors. Analogously, to prevent flips in the proposed design, the capacitor of the eDRAM cell must be precharged to Vdd.

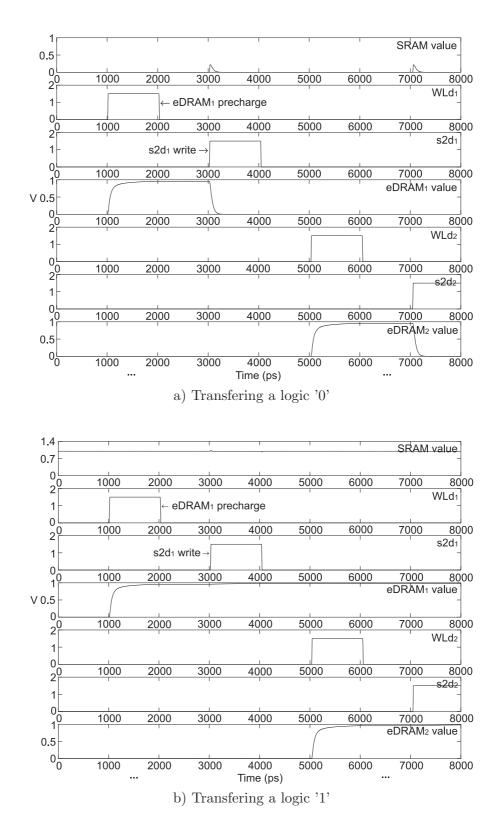

Figure 2.2 illustrates how the internal transfer operation between the SRAM cell and three eDRAM cells works in a 4-bit macrocell, highlighting both the precharge process and how flips are avoided<sup>1</sup>. Two internal transfers labeled as eDRAM1 and eDRAM2 are shown for illustrative purposes, both writing a '0' and a '1'.

The number of bits in the macrocell device defines the number of ways of macrocellbased caches. In other words, n-bit macrocells are required to implement an n-way set-associative hybrid cache. Hence, these memories will have one way built with SRAM cells (SRAM way) and n-1 ways implemented with eDRAM cells (eDRAM ways).

The proposed macrocell reduces both leakage and area. Since leakage is mainly produced by SRAM cells, the macrocell reduces leakage proportionally to the number of implemented eDRAM cells. For instance, let's assume a 4-bit macrocell that has one SRAM cell and three eDRAM cells; ideally, as only the SRAM cell has leakage, the 4-way hybrid cache would achieve 75% (i.e., 3/4) less leakage than a conventional cache with the same capacity implemented with SRAM cells (see Section 2.3.3 for a deeper and accurate analysis). On the other hand, area is also reduced since eDRAM cells are implemented with less transistors than SRAM cells (see Section 2.3.4). Finally, notice that the higher the cache associativity degree, the higher the leakage savings and area reduction achieved with macrocells.

As read operations in an eDRAM cell are destructive and capacitors progressively lose their charge with time, refresh actions are normally required. In this context, new architectural innovations are presented to avoid extra logic and energy dissipation due to refresh operations.

## 2.2 Architectural Design Issues

As mentioned above, the proposed n-bit macrocell is designed in order to implement the data array of an n-way set-associative cache, with one SRAM way and n-1 eDRAM

<sup>&</sup>lt;sup>1</sup>Bridge transistor features have been assumed the same as the pass transistors of the eDRAM cells, whose channel length and width are 45nm and 90nm, respectively.

FIGURE 2.2: Static to dynamic write operation details.

ways. From now on, it is assumed that the SRAM cells implement the way-0 of the cache.

The tag array of hybrid caches is assumed to be built with SRAM cells, since it is much smaller than the data array. Thus, much lower energy and area benefits can be obtained in this structure, and implementing it with eDRAM technology would significantly affect the access time.

The architectural proposal devised to manage this cell consists of three main strategies, detailed below: i) accessing the eDRAM cells only in the case of a hit in the corresponding tag, ii) increasing the percentage of hits in the SRAM blocks in order to minimize the number of data movements between SRAM and eDRAM cells, and iii) minimizing the number of writebacks to L2.

#### 2.2.1 Accessing the eDRAM Ways