### Universitat Politècnica de València Departamento de Informática de Sistemas y Computadores

# Smart Memory and Network Design for High-Performance Shared-Memory Chip Multiprocessors

A thesis submitted in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy (Computer Engineering)

> > Author

Mario Lodde

Advisor

Prof. José Flich

January 2014

A Stefania

### Ringraziamenti / Agradecimientos

Vorrei prima di tutto ringraziare le persone che mi sono state vicine in questi quattro anni nonostante le centinaia di km che ci separavano: la mia famiglia in Sardegna, Stefania e tutti i miei amici sparsi tra la Sardegna e la Toscana (e qualcuno ultimamente anche un po' più lontano ;) ). Questa tesi è il risultato anche del vostro continuo supporto e affetto.

Volviendo a este lado del Mediterráneo, quisiera agradecer en primer lugar a Pepe por haberme dado la oportunidad de hacer el doctorado en el GAP, por su constante seguimiento y soporte a mi trabajo y por su total disponibilidad para ayudarme con cualquier problema.

También quiero agradecer a todos los compañeros que han trabajado en los dos laboratorios del GAP en estos años, con que he compartido muchas horas de trabajo, comidas y viajes.

Y por último, pero no menos importante, quiero agradecer al resto del personal del DISCA por el gran ambiente de trabajo en que me he encontrado desde el primer día.

#### Abstract

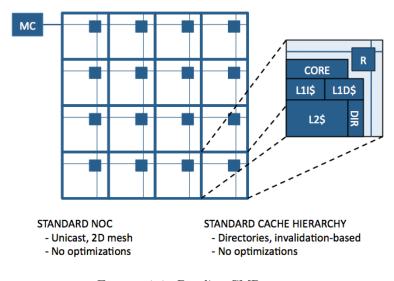

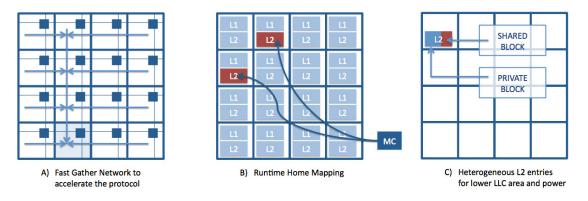

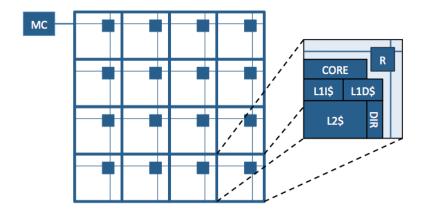

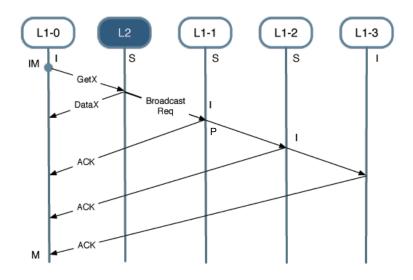

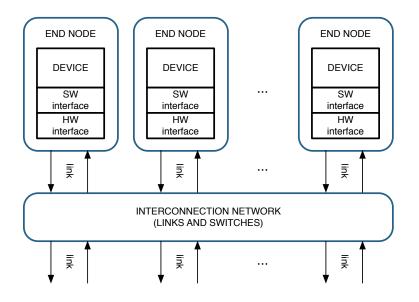

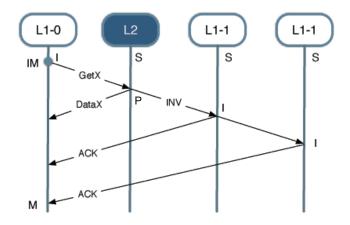

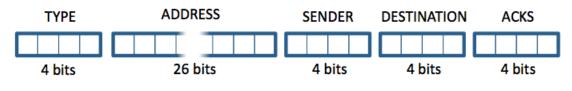

The cache hierarchy and the Network-on-Chip (NoC) are two key components of chip multiprocessors (CMPs). Most of NoC traffic is due to messages exchanged by the caches according to the coherence protocol. The amount of traffic, the percentage of short and long messages and the traffic pattern in general depend on the cache geometry and the coherence protocol. NoC architecture and the cache hierarchy are indeed tightly coupled, and these two components should be designed and evaluated together to study how varying one's design affects the other one's performance. Furthermore, each component should adjust to match the requirements and exploit the performance of the other one, and vice versa. Usually, messages belonging to different classes are sent through different virtual networks or through NoCs with different bandwidth, thus separating short and long messages. However, other classification of the messages can be done, depending on the type of information they provide: some messages, like data requests, need fields to store information (block address, type of request, etc.); other messages, like acknowledgement messages (ACKs), do not need to specify any information except for the destination node. This second class of messages do no require high NoC bandwidth: latency is far more important, since the destination node is typically blocked waiting for their reception. In this thesis we propose a dedicated network which is able to transmit this second class of messages; the dedicated network is lightweight and fast, and is able to deliver ACKs in a few clock cycles. By reducing ACKs latency and the NoC traffic, it is possible to:

- speed-up the invalidation phase during write requests in a system which employs a directory-based coherence protocol

- improve the performance of a broadcast-based coherence protocol, reaching performance which is comparable to that of a directory-based protocol but without the additional area overhead due to the directory

- implement an efficient and dynamic mapping of cache blocks to the last-level cache banks, aiming to map blocks as close as possible to the cores which use them

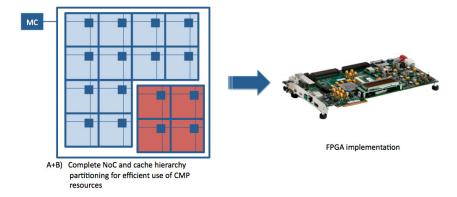

The final goal is to obtain a co-design of the NoC and the cache hierarchy which minimizes the scalability problems due to coherence protocols. In this thesis we explore the different design alternatives for fast network delivery and coherence protocol opportunities. The best mechanisms, combined on a final system, allow for a truly dynamic and customizable architecture in an environment with multiple applications demanding partitioning of resources.

### Resumen

La jerarquía de caches y la red en el chip (NoC) son dos componentes clave de los chip multiprocesadores (CMPs). La mayoría del trafico en la NoC se debe a mensajes que las caches envían según lo que establece el protocolo de coherencia. La cantidad de tráfico, el porcentaje de mensajes cortos y largos y el patrón de tráfico en general varían dependiendo de la geometría de las caches y del protocolo de coherencia. La arquitectura de la NoC y la jerarquía de caches están de hecho firmemente acopladas, y estos dos componentes deben ser diseñados y evaluados conjuntamente para estudiar cómo el variar uno afecta a las prestaciones del otro. Además, cada componente debe ajustarse a los requisitos y a las oportunidades del otro, y al revés. Normalmente diferentes clases de mensajes se envían por diferentes redes virtuales o por NoCs con diferente ancho de banda, separando mensajes largos y cortos. Sin embargo, otra clasificación de los mensajes se puede hacer dependiendo del tipo de información que proveen: algunos mensajes, como las peticiones de datos, necesitan campos para almacenar información (dirección del bloque, tipo de petición, etc.); otros, como los mensajes de reconocimiento (ACK), no proporcionan ninguna información excepto por el ID del nodo destino. Esta segunda clase de mensaje no necesita de mucho ancho de banda: la laténcia es mucho mas importante, dado que el nodo destino está bloqueado esperando su recepción. En este trabajo de tesis se desarrolla una red dedicada para trasmitir la segunda clase de mensajes; la red es muy sencilla y rápida, y permite la entrega de los ACKs con una laténcia de pocos ciclos de reloj. Reduciendo la laténcia y el tráfico en la NoC debido a los ACKs, es posible:

- acelerar la fase de invalidación en fase de escritura en un sistema que usa un protocolo de coherencia basado en directorios

- mejorar las prestaciones de un protocolo de coherencia basado en broadcast, hasta llegar a prestaciones comparables con las de un protocolo de directorios pero sin el coste de área debido a la necesidad de almacenar el directorio

- implementar un mapeado dinámico de bloques a las caches de último nivel de forma eficiente, con el objetivo de acercar al máximo los bloques a los cores que los utilizan

El objetivo final es obtener un co-diseño de NoC y jerarquía de caches que minimice los problemas de escalabilidad de los protocolos de coherencia. En esta tesis se exploran diferentes alternativas para una entrega rapida de los ACKs y las oportunidades que ofrece al protocolo de coherencia. Combinando los mecanismos presentados en un sistema final, se obtiene una arquitectura adaptable dinamicamente a los requisitos de múltiples aplicaciones en un entorno virtualizado.

### Resum

La jerarquia de cache i la xarxa en el xip (NoC) són dos components clau dels xips multiprocessador (CMPs). La majoria del trànsit en la NoC es deu a missatges que les caches envien segons el que estableix el protocol de coherència. La quantitat de trànsit, el percentatge de missatges curts i llargs i el patró de trànsit en general varien depenent de la geometria de les caches i del protocol de coherència. L'arquitectura de la NoC i la jerarquia de cache estan de fet fermament acoblades, i aquests dos components han de ser dissenyats i avaluats conjuntament per a estudiar com al variar un afecta a les prestacions de l'altre. A més, cada component s'ha d'ajustar als requisits i a les oportunitats de l'altre, i a l'inrevés. Normalment diferents classes de missatges s'envien per diferents xarxes virtuals o per NoCs amb diferent ample de banda, separant missatges llargs i curts. No obstant això, una altra classificació dels missatges es pot fer depenent del tipus d'informació que proveeixen: alguns missatges, com les peticions de dades, necessiten camps per aemmagatzemar informació (adreça del bloc, tipus de petició, etc.). Altres, com els missatges de reconeixement (ACK), no proporcionen cap informació excepte per l'ID del node destí. Aquesta segona classe de missatge no necessita molt ample de banda: la latència és molt més important, atès que el node destí està típicament bloquejat esperant la recepció d'ells. En aquest treball de tesi es desenvolupa una xarxa dedicada per a transmetre la segona classe de missatges, la xarxa és molt senzilla i ràpida, i permet el lliurament dels ACKs amb una latència de pocs cicles de rellotge. Reduint la latència i el trànsit en la NoC a causa dels ACKs, és possible:

- accelerar la fase d'invalidació en fase d'escriptura en un sistema que utilitza un protocol de coherència basat en directoris

- millorar les prestacions d'un protocol de coherència basat en broadcast , fins a aplegar a prestacions comparables amb les d'un protocol de directoris però sense el cost d'àrea a causa de la necessitat d'emmagatzemar el directori

- implementar un mapejat dinàmic de blocs a les caches d'ùltim nivell de forma eficient , amb l'objectiu d'apropar quant al màxim possible els blocs als cores que els utilitzen

L'objectiu final és obtenir un co- disseny de NoC i jerarquia de cache que minimitze els problemes d'escalabilitat dels protocols de coherència. En aquesta tesi s'exploren diferents alternatives per un lliurament ràpid dels ACKs i les oportunitats que això ofereix al protocol de coherència. Combinant els mecanismes presentats en un sistema final, s'obté una arquitectura adaptable dinàmicament als requisits de múltiples aplicacions en un entorn virtualitzat.

## Contents

| List of Figures x |                       |         |                                                      |      |  |  |

|-------------------|-----------------------|---------|------------------------------------------------------|------|--|--|

| $\mathbf{Li}$     | List of Tables xxiii  |         |                                                      |      |  |  |

| A                 | bbrev                 | viation | as and Acronyms                                      | xxv  |  |  |

| 1                 | $\operatorname{Intr}$ | oducti  | ion                                                  | 1    |  |  |

|                   | 1.1                   |         | Contributions                                        |      |  |  |

|                   | 1.2                   | Thesis  | S Outline                                            | . 6  |  |  |

| <b>2</b>          | Bac                   | kgroui  | nd and Related Work                                  | 9    |  |  |

|                   | 2.1                   | The C   | Cache Hierarchy                                      |      |  |  |

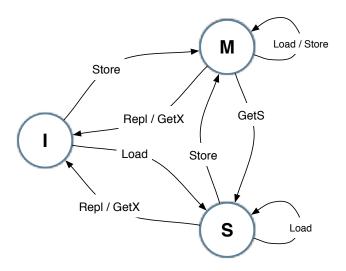

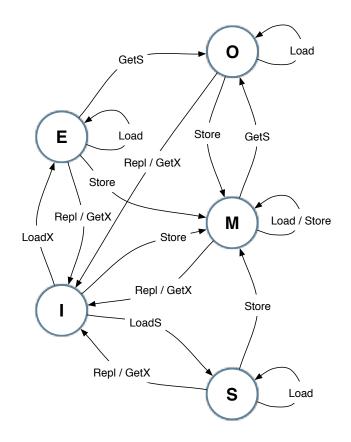

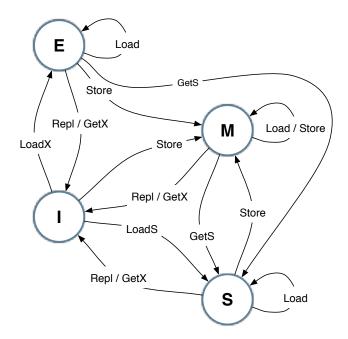

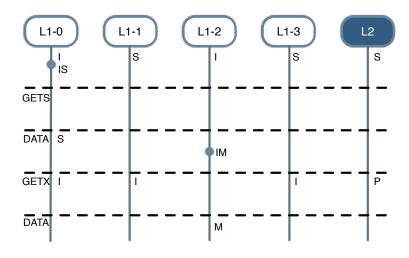

|                   |                       | 2.1.1   | Cache Coherence Protocols                            |      |  |  |

|                   |                       |         | 2.1.1.1 Invalidation-based vs Update-based Protocols | . 11 |  |  |

|                   |                       |         | 2.1.1.2 Steady States at L1 Cache Controllers        |      |  |  |

|                   |                       |         | 2.1.1.3 Snoopy and Directory Protocols               |      |  |  |

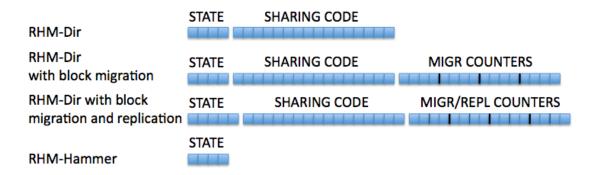

|                   |                       |         | 2.1.1.4 Directory Implementation                     |      |  |  |

|                   |                       | 2.1.2   | Block Mapping Policies in Shared Banked LLCs         |      |  |  |

|                   |                       | 2.1.3   | Power Implications                                   |      |  |  |

|                   | 2.2                   |         | letwork-on-Chip                                      |      |  |  |

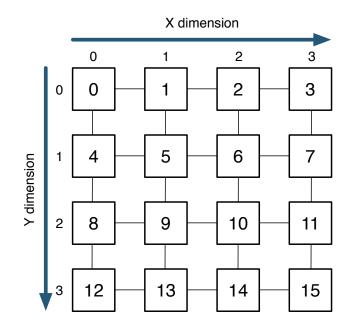

|                   |                       | 2.2.1   | NoCs Topology                                        |      |  |  |

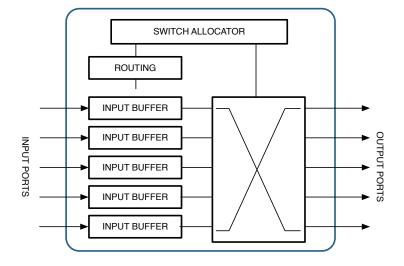

|                   |                       | 2.2.2   | The Switch                                           |      |  |  |

|                   |                       | 2.2.3   | Data Units                                           |      |  |  |

|                   |                       | 2.2.4   | Switching                                            |      |  |  |

|                   |                       | 2.2.5   | Flow Control                                         |      |  |  |

|                   |                       | 2.2.6   | Arbitration                                          |      |  |  |

|                   |                       | 2.2.7   | Routing                                              |      |  |  |

|                   |                       |         | 2.2.7.1 Implementation of a Routing Algorithm        |      |  |  |

|                   |                       |         | 2.2.7.2 Unicast, Multicast and Broadcast Messages    |      |  |  |

|                   | 0.0                   | 2.2.8   | NoC and Cache Coherence                              |      |  |  |

|                   | 2.3                   |         | ation Platform                                       |      |  |  |

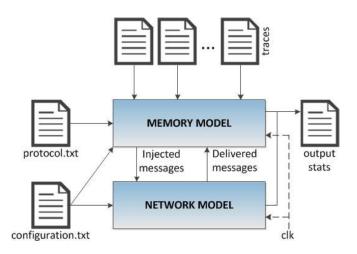

|                   |                       | 2.3.1   | gMemNoCsim                                           |      |  |  |

|                   |                       | 2.3.2   | Graphite                                             |      |  |  |

|                   |                       | 2.3.3   | Sniper                                               |      |  |  |

|                   |                       | 2.3.4   | CACTI                                                |      |  |  |

|                   |                       | 2.3.5   | Orion-2                                              |      |  |  |

|                   |                       | 2.3.6   | Xilinx ISE                                           | . 42 |  |  |

| 3        | Net | work-I  | Level Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>43</b> |

|----------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          | 3.1 | Introd  | $uction \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44        |

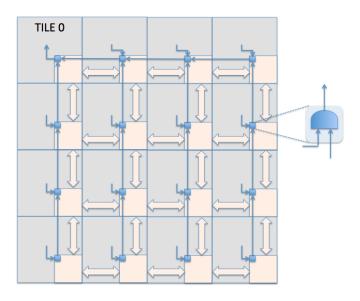

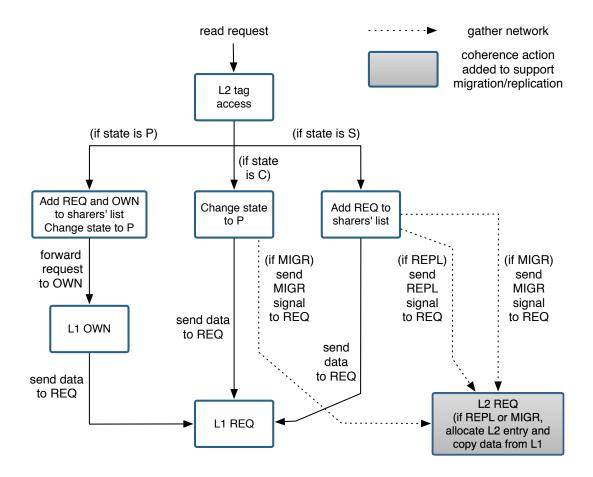

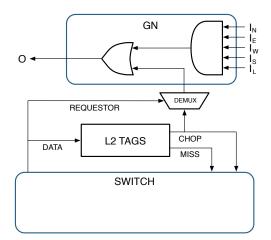

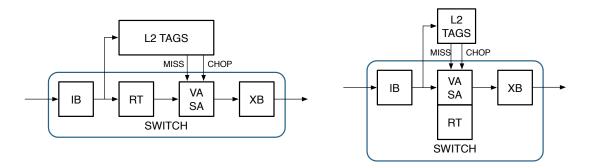

|          | 3.2 | The G   | ather Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46        |

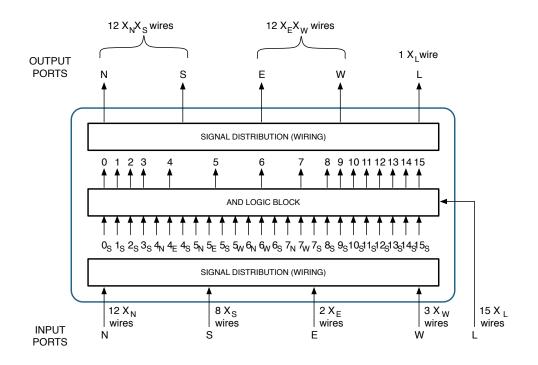

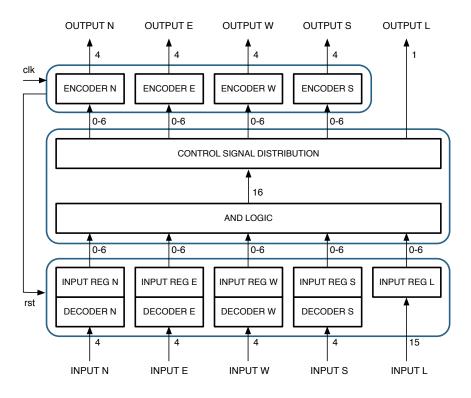

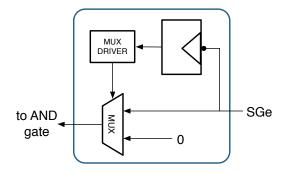

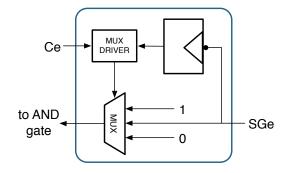

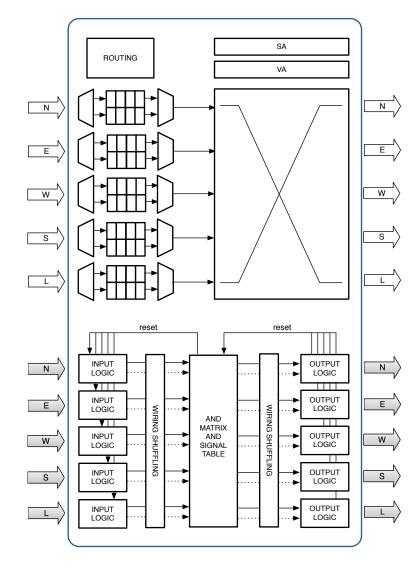

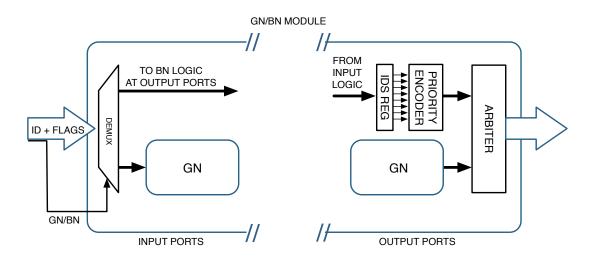

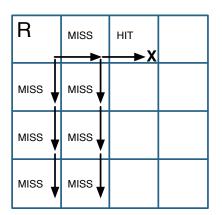

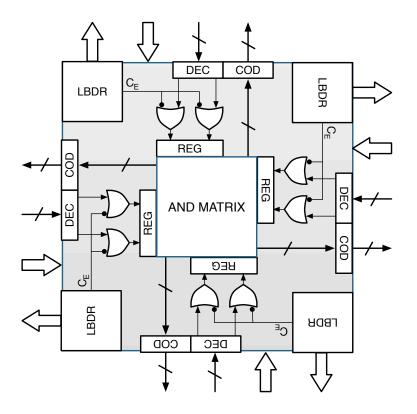

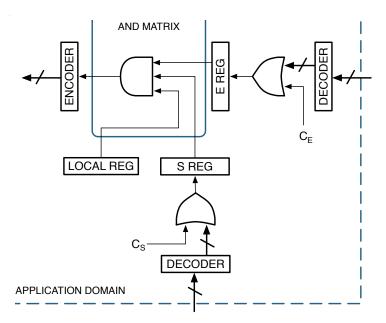

|          |     | 3.2.1   | Description of a Logic Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47        |

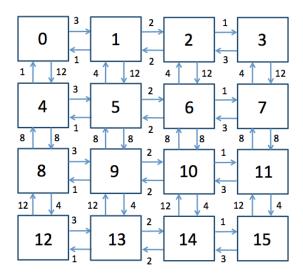

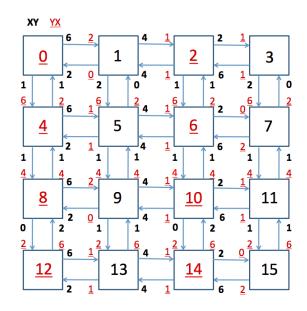

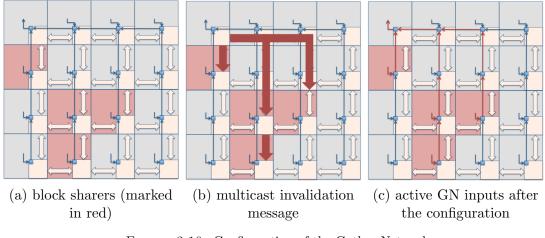

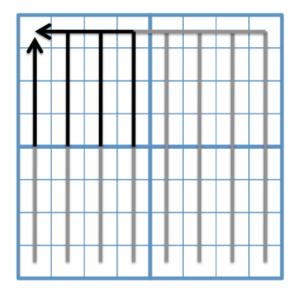

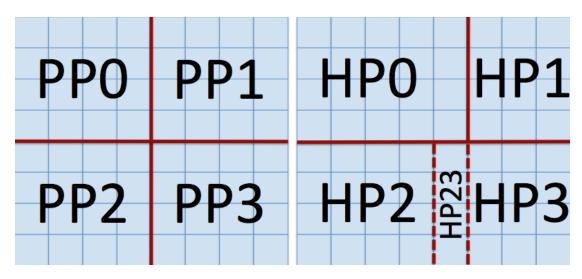

|          |     | 3.2.2   | GN Wiring Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49        |

|          |     | 3.2.3   | Implementation Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50        |

|          |     | 3.2.4   | Sequential Implementation of the Gather Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

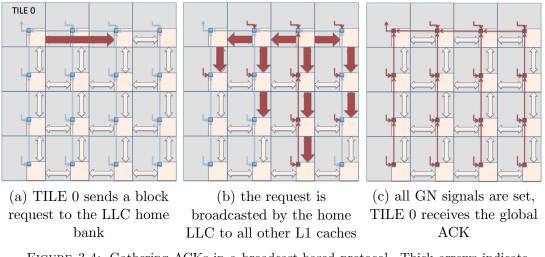

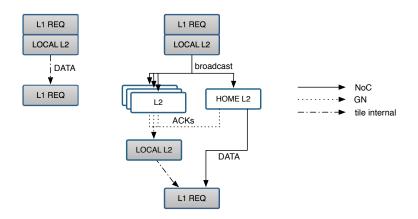

|          | 3.3 | GN A    | pplied to Hammer Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |

|          |     | 3.3.1   | Reseting The GN Wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

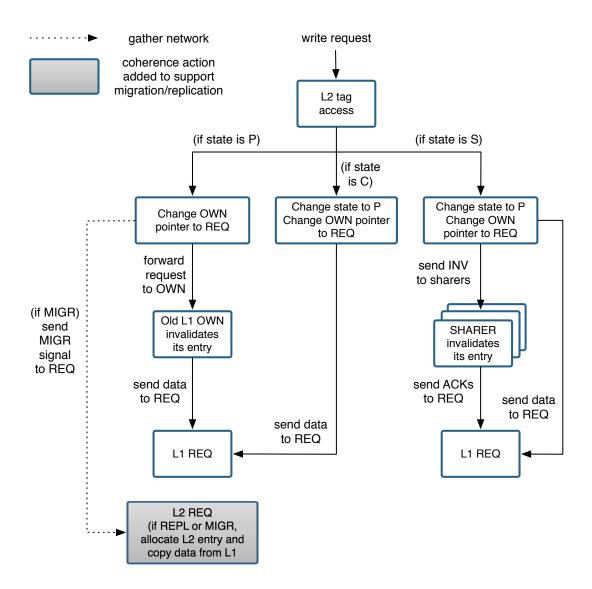

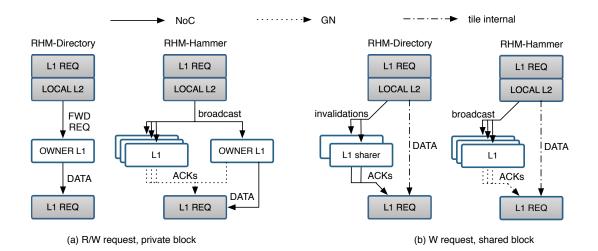

|          | 3.4 | GN A    | pplied to Directory Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56        |

|          |     | 3.4.1   | Reseting the GN Wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

|          |     | 3.4.2   | Protocol Modifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

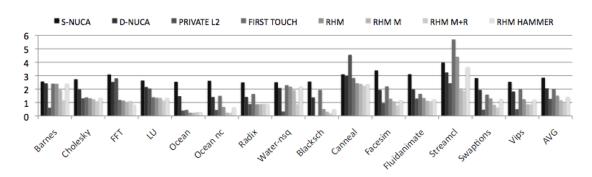

|          | 3.5 | GN Pe   | erformance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59        |

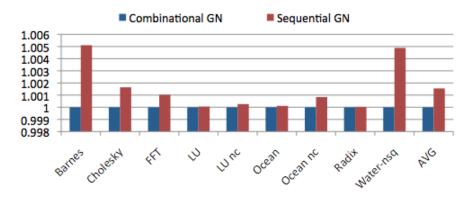

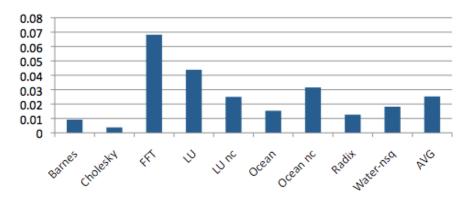

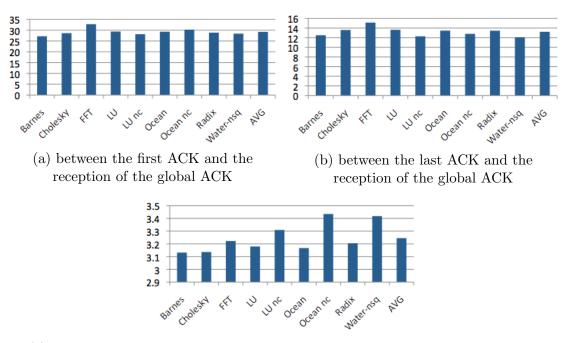

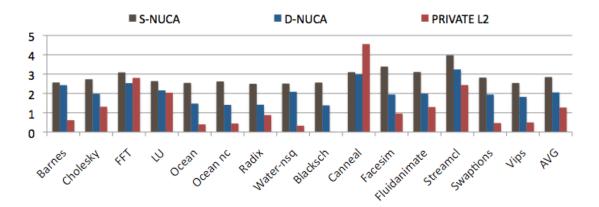

|          |     | 3.5.1   | Directory Protocol with GN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60        |

|          |     | 3.5.2   | Hammer Protocol with GN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

|          |     | 3.5.3   | Sequential Gather Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |

|          | 3.6 | Conclu  | $\mathbf{r}$ is $\mathbf{r}$ |           |

|          |     |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

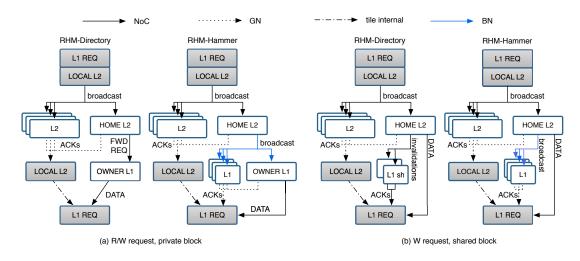

| 4        | Rur |         | Home Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73        |