Document downloaded from:

http://hdl.handle.net/10251/52882

This paper must be cited as:

Patrao Herrero, I.; Figueres Amorós, E.; González Espín, FJ.; Gabriel Garcerá (2011). Transformerless Topologies for Grid-Connected Single-Phase Photovoltaic Inverters. Renewable and Sustainable Energy Reviews. 15:3423-3431. doi:10.1016/j.rser.2011.03.034.

The final publication is available at

http://dx.doi.org/10.1016/j.rser.2011.03.034

Copyright Elsevier

# Additional Information

NOTICE: this is the author's version of a work that was accepted for publication in <Renewable and Sustainable Energy Reviews>. Changes resulting from the publishing process, such as peer review, editing, corrections, structural formatting, and other quality control mechanisms may not be reflected in this document. Changes may have been made to this work since it was submitted for publication. A definitive version was subsequently published in RENEWABLE AND SUSTAINABLE ENERGY REVIEWS, [VOL 15, ISSUE 7, (07/2011)] DOI 10.1016/j.rser.2011.03.034

# Transformerless Topologies for Grid-Connected Single-Phase Photovoltaic Inverters

Iván Patrao<sup>a,\*</sup>, Emilio Figueres<sup>a</sup>, Gabriel Garcerá<sup>a</sup>, Fran González-Espín<sup>a</sup>

<sup>a</sup>Grupo de Sistemas Electrónicos Industriales del Departamento de Ingeniería Electrónica, Universidad Politécnica de Valencia, Camino de Vera s/n, 46022 Valencia, España.

e-mail addresses: <u>ivanpatrao@gmail.com</u>, (I. Patrao), <u>efiguere@eln.upv.es</u> (E. Figueres), <u>ggarcera@eln.upv.es</u> (G. Garcerá), <u>fragone1@upvnet.upv.es</u> (F. González-Espín).

\*Corresponding author. e-mail address: ivanpatrao@gmail.com. Phone number: +34 963 87 96 06.

#### Abstract

In order to improve the efficiency of a photovoltaic system, it is possible to use a transformerless photovoltaic inverter. However, this topology needs to be studied in detail, as it presents some problems related to the galvanic connection between the grid and the photovoltaic generator (e.g. efficiency degradation and safety problems).

In this paper, a review of grid-connected single-phase photovoltaic inverters based on transformerless topologies has been carried out. On the one hand, some alternatives based on classical topologies have been presented. On the other hand, alternatives based on multi-level inverter topologies have been studied, showing up that no leakage current is generated in comparison to classical topologies.

#### Keywords

Multilevel inverters, Transformerless inverters, Photovoltaic inverters, Renewable energies.

# 1. Introduction

The renewable energy sources, in particular those of photovoltaic origin [1], have experimented a great development in recent years mainly due to the growing concern about global warming, and the grants given by the governments to these kind of technologies [2,3].

Power processing of renewable energy sources is carried out by means of power converters, with some issues like efficiency and cost as key factors. In the particular case of grid-connected photovoltaic inverters, most of the power converter topologies use a transformer operating at low or at high frequency, which provides galvanic isolation between photovoltaic panels and electrical grid. Low frequency transformers are big, heavy and expensive, and introduce additional losses in the system. The size of the isolating transformer may be significantly reduced by using a two stage topology in which the transformer operates at high frequency [4], this approach reduces the efficiency because at least two cascaded power converters are needed. Because of that, a large number of inverters based on transformerless topologies [5,6] have been proposed in the last few years, resulting in cheaper, more compact and more efficient power processing systems [7]. In addition, when using transformerless inverters some technique to measure the isolation resistance and the residual current must be used, which makes the transformerless inverters even safer than the inverters with transformer [8].

Regarding the size of grid connected power inverters, a change of paradigm has been observed in the last few years [9,10]. Large central inverters of power above 100kW are being substituted by small size inverters that processes the energy supplied by one string or a small group of strings. Following this approach, the maximum power point tracking of large photovoltaic groups of panels can be improved, as they could be exposed to very different solar radiation levels [2]. In this context, the use of single-phase inverters up to 5kW is of a great interest.

For the aforementioned reasons a significant number of small-power topologies have been proposed to implement grid connected single-phase transformerless inverters [3]. In this kind of inverters there is no galvanic isolation between photovoltaic panels and the grid, so that some problems can appear that need a special care, like common mode voltages and leakage currents across the photovoltaic panels, due to the fact that a non-negligible parasitic capacitance exists between photovoltaic cells and the installation ground, which can reach very high values under certain operating conditions (e.g. humidity, dust, or installation mode). Typical values of this capacitance vary between 50 and 150nF/kWp for crystalline-Silicon cells and values up to  $1\mu$ F/kWp for thin-film cells.

# 2. The common mode voltage problem

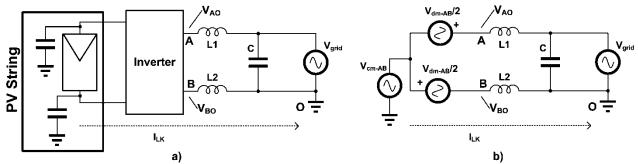

The commutation of the inverter switches can produce an alternating common mode voltage in the panel poles, which may induce a capacitive leakage current [13,14], as shown in Fig. 1a) and in Fig. 1b).

The value of the common mode voltage can be estimated following (1), where the mismatch between the values of the grid filter inductors, L1 and L2, is taken into account, and play an important role in the common mode voltage problem [4].

$$V_{CM} = (V_{AO} + V_{BO})/2 + (V_{AO} - V_{BO}) \cdot (L_2 - L_1)/(2 \cdot (L_1 + L_2))$$

(1)

Fig. 1. a) Common mode current and parasitic capacitance and b) Photovoltaic system model.

Because of the effect of both, the parasitic capacitance of the panels and the inverter common mode voltage, a leakage current to the ground appears, which may produce serious problems in photovoltaic power plants (e.g. actuation of the protections, efficiency degradation, safety problems, additional distortion of the grid current and electromagnetic compatibility problems) [7,16-20].

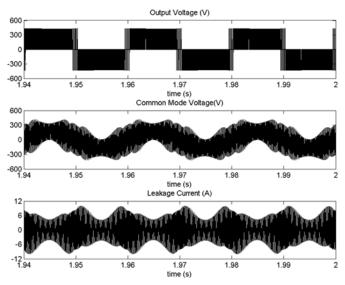

When unipolar PWM modulation is used in the transformerless full H-bridge inverter, a high frequency common mode voltage is applied to the photovoltaic panels, so that a non-negligible leakage current appears, as shown in Fig. 2, where the test conditions have been choice to be as follows; Output power: 5kW, Grid voltage: 230V/50Hz, Filter LC:  $2x850\mu H/12\mu F$ , Switching frequency: 10kHz, Ground resistance:  $1\Omega$ , Leakage capacitance: 2x140nF.

Fig. 2. Unipolar PWM modulation applied to a full H-bridge photovoltaic inverter.

Furthermore, it has been detected additional problems associated to leakage current in emerging cells technologies. When using back-contact photovoltaic cells operated at high voltage values, leakage current forms negative charges on the cells front surface, affecting recombination mechanism and reducing the cells efficiency. Fortunately, this is a reversible effect if the power photovoltaic inverter is designed to tie the negative photovoltaic string pole to ground, thus generating a negative voltage gradient which avoids this phenomenon [7]. In the case of amorphous-Silicon thin-film cells (a-Si) and cadmium telluride (CdTe), if moisture condenses inside the module and negative voltages to ground exist, an irreversible corrosive process can be started at the TCO (Transparent Conducting Oxide) [7,21]. This phenomenon leads to a reduction in the efficiency and, consequently, to a shorter photovoltaic modules life. To prevent this, it is mandatory to avoid condensation inside the photovoltaic module by hermetically sealing the modules border. However, it is difficult to guarantee the functionality of this system over the years. Another highly effective measure is to ground the negative pole of the panels, avoiding the corrosion process due to the electric field orientation.

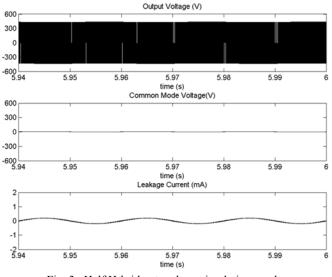

Research on transformerless inverters focuses on finding topologies which have a low leakage current, while trying to keep or to improve the performance of the classical topologies [22], e.g. the half H-bridge topology, which presents a very low leakage current since neutral is connected to the midpoint of the input voltage, as depicted in Fig. 3, where the test conditions have been choice to be the same as in Fig. 2.

This paper presents a review of topologies that have been previously proposed to implement single-phase transformerless photovoltaic inverters, by emphasizing in some aspects of interest like the common-mode voltages applied to photovoltaic panels, the quality of the generated current and the number and characteristics of the semiconductors used in each topology.

Fig. 3. Half H-bridge topology simulation results

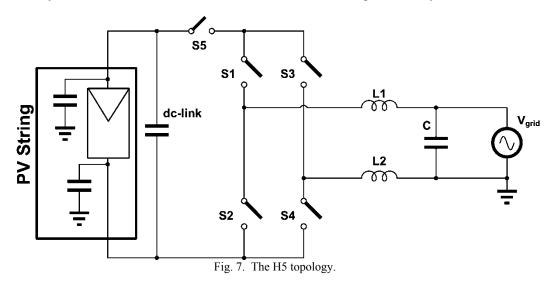

# 3. Power converters derived from bridge topologies

These inverters are based on full H-bridge and half H-bridge structures, and have been widely studied in the literature. In this section, it will be analyzed the following transformerless topologies: full H-bridge with both unipolar and bipolar modulation, half H-bridge, HERIC topology, H5 topology and half H-bridge with an additional generation control circuit.

#### 3.1. Full H-bridge

The most widely used topology in grid-connected photovoltaic inverters is the full H-bridge. It is build up by 4 transistors, which are connected as shown in Fig. 4**¡Error! No se encuentra el origen de la referencia.** Due to the fact that a large number of commercial inverters use this topology in combination with a low frequency transformer it is interesting to study its application to transformerless inverters.

Fig. 4. The full H-bridge topology.

The most common modulation used in this topology is unipolar PWM, because it presents a number of advantages in comparison to bipolar modulation (e.g. lower current ripple at high frequencies, better efficiency or lower electromagnetic interferences emission) [23]. However, when unipolar PWM modulation is used in the transformerless full H-bridge inverter, a high frequency common mode voltage of amplitude  $V_{dc}/2$  is applied to the photovoltaic panels, so that a non-negligible leakage current appears because of the photovoltaic panels parasitic capacitance. This reason advises against using this kind of modulation in transformerless inverters [5].

To solve the problem of the leakage current in the full H-bridge photovoltaic inverter, the Bipolar PWM modulation can be used. This modulation eliminates the high frequency components of the common-mode voltage applied to the panels [8], thus the common mode voltage only has the low frequency component of the first harmonic, so that a reduced leakage current results [13,14,25]. However, to limit the leakage current peak value, it is critical a good synchronization among the gate signals of the bridge transistors. Otherwise, the leakage current could significantly increase [6]. Consequently, this topology is not considered to be a good alternative to implement transformerless photovoltaic inverters, even if the bipolar PWM modulation is used [7].

#### 3.2. Half H-bridge

The half H-bridge topology is formed by 2 transistors and a capacitive divider connected to the photovoltaic module, as shown in Fig. 5. The connection of the grid neutral wire to the capacitive divider midpoint ensures an almost constant common mode voltage, thus preventing leakage current through the parasitic capacitance of the photovoltaic module [28].

Fig. 5. The Half H-bridge inverter topology.

Despite the lower cost and simplicity of this converter compared to the H-bridge topology (mainly due to fact that the half H-bridge uses half of the semiconductors than the H-bridge) [29], this topology is rarely used in practice, because of some drawbacks difficult to solve (e.g. the output waveform has only two levels, the output current is highly distorted and causes high electromagnetic interference emissions, and the switches have to support double the voltage compared to the full H-bridge topology) [15,28] thus requiring higher blocking voltage power transistors, which increases the switching losses.

In order to improve the behavior of the half H-bridge, several variants of this topology have been presented in the literature as interesting alternatives for transformerless inverters. The most important ones are shown next.

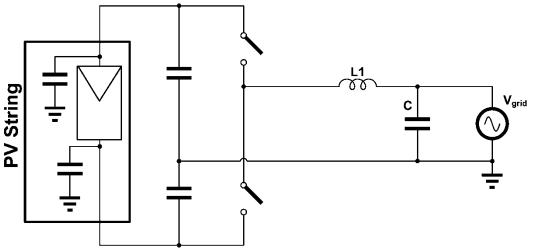

#### 3.3. High Efficient and Reliable Inverter Concept (HERIC)

This topology combines the advantages of the unipolar PWM modulation with a reduced leakage current and a high efficiency, being the topology implemented in some commercial inverters [8,24], especially those from Sunways.

As stated in previous sections, it is interesting to use a 3 level output voltage transformerless inverter to connect the photovoltaic panels to the electrical grid. However, the simulations results using a full h-bridge have shown that this arrangement introduces a high frequency ripple in the photovoltaic poles, which causes a non-negligible leakage current to flow through the parasitic capacitance of the panels into the ground. To avoid the leakage current while maintaining the 3 level output voltage, a new topology based on the full H-bridge inverter has been developed and patented [8], known by the acronym HERIC.

In the HERIC topology a couple of branches are added in parallel with the output filter, as shown in Fig. 6. These additional branches switch at the electrical grid frequency, so that T1 is in the on-state in the positive half-cycle and in the off-state in the negative half-cycle, while T2 is the on-state in the negative half-cycle and in the off-state in the positive half-cycle, This allow the diodes D1 and D2 to work as a free-wheeling diodes in the positive and the negative half-cycles, respectively, thus preventing the output current to flow through the diodes of the full H-bridge. The described feature is responsible for isolating the photovoltaic panel from the electrical grid, as well as for obtaining the third level, i.e. zero volts, in the output voltage of the inverter, since the same one remains short-circuited when D1 or D2 conduct. The HERIC topology allows the photovoltaic panel to remain at a floating voltage to ground, thus achieving a practically constant common mode voltage [8].

Moreover, it is possible to improve efficiency as compared with a conventional H-bridge, due to the fact that during free-wheeling periods current does not flow through bridge semiconductors. This characteristic is of great use when the inverter is operated at light load conditions [6,8,31].

The main drawback of HERIC topology is the high number of switches, which leads to a greater complexity of the converter compared to the conventional full H-bridge topology.

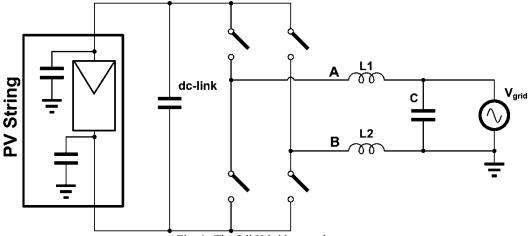

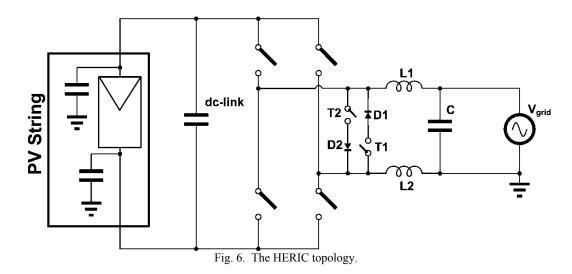

# 3.4. The H5 topology

This topology only needs an additional transistor compared to the full-bridge, and that's the reason for its name. The H5 topology is patented by SMA [9], which is considered as one of the worldwide leading manufacturers of photovoltaic inverters, and it is based on the same concept as the HERIC topology, i.e. to disconnect the photovoltaic panels from the grid during current freewheeling periods, which prevents the voltage to ground of panel poles from switching frequency ripple, thus having an almost constant common mode voltage.

In Fig. 7 it is shown the H5 topology, that uses a full-bridge consisting of the four switches S1, S2, S3 and S4, and the DC-bypass S5 switch. The switches S1 and S2 are operated at grid frequency, whereas S3, S4 and S5 are operated at high frequency. During current free-wheeling period, S5 is open, disconnecting photovoltaic panels from the inverter full H-bridge. The free-wheeling path is closed by the transistor of S1 and the inverse diode of S3 for the positive half-cycle of the electrical grid and by the transistor of S3 and the inverse diode of S1 for the negative half-cycle.

The use of the H5 transformerless inverter topology makes possible to obtain a high efficiency [10], particularly at partial load. It needs only one additional transistor in comparison with the full H-bridge topology. However, as the transistor is in series with the full H-bridge inverter [11], the conduction losses may increase if the semiconductor choice is not optimum.

Nowadays, some commercial inverters use this topology [5], especially those from the proprietary of the patent, being a valid alternative to implement transformerless photovoltaic inverters.

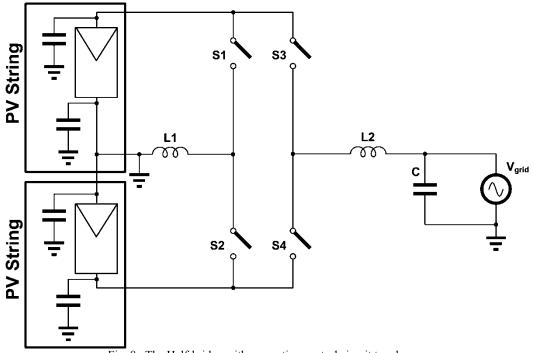

# 3.5. Half H-bridge with generation control circuit (GCC)

Half bridge with GCC [34] is based on a half-bridge inverter with two more additional transistors, which makes it possible the independent maximum power point tracking of the photovoltaic strings [35]. A schematic of this topology is depicted in Fig. 8. In this figure it is possible to identify both, the GCC circuit, composed of the switches S1 and S2 and the inductor L1, and the half H-bridge circuit, consisting of the switches S3 and S4 and the inductor L2.

Fig. 8. The Half-bridge with generation control circuit topology.

The GCC is a classical buck-boost chopper [12] that uses the middle point and the negative pole of the DC-link capacitor bank as the input and positive pole and the middle point of the DC-link capacitor bank as the output, thus allowing to share the load current between the different strings.

In spite of the fact that there exist other alternatives than the GCC to perform the independent maximum power point tracking of a several photovoltaic panels, this topology is of a great interest when a pair of strings are used, since it needs the same component count as a full H-bridge, i.e. 4 transistors and 2 inductors, while retaining the common-mode voltage performance of a half H-bridge converter, thus ensuring a low common mode current. Furthermore, the dc/dc of the GCC switches only the power difference between the photovoltaic strings, reducing the overall power losses.

It is worth pointing out that the performance of the inverter is comparable to the performance of the half H-bridge, and that the drawbacks are the same, i.e. higher current ripple, higher power losses and higher electromagnetic interferences than the full H-bridge. However, by using the GCC it is possible to improve the performance of the photovoltaic panels, due to the fact that the maximum power point of both panels can be tracked independently [13] which is important in those installations where different strings are subjected to different installation conditions (e.g. different orientation, partial shadows or even a small difference in the number of panels of each string).

## 4. Inverters based on multilevel topologies

The multilevel topologies are based on a special arrangement of the semiconductors and passive components of the inverter in such a way that a three or more discrete DC voltage levels are obtained at the power converter output. Although these topologies have been widely used in high power applications [14], it has not been considered so far as an alternative to the standard topologies used in small-power transformerless inverters, mainly due to the cost of the extra required power diodes and transistors. However, thanks to the cost reduction of semiconductors [38,39], the multilevel topologies are being recently applied to the development of small-power transformerless inverters.

It is important pointing out that these kind of converters should overcome two important limitations. On the one hand, a reduction on the number of sensed magnitudes should be accomplished. On the other hand, the building blocks of the multilevel converters should be designed to reduce the parasitic inductance [15]. To overcome these limitations, the manufacturers of semiconductors are developing power modules which integrate basic multilevel structures [16].

The following transformerless multilevel topologies are presented below: cascaded H-bridge (CHB), NPC half-bridge, flying capacitor (FC), a variant of the NPC half-bridge, the Conergy-NPC and the active-NPC (aNPC).

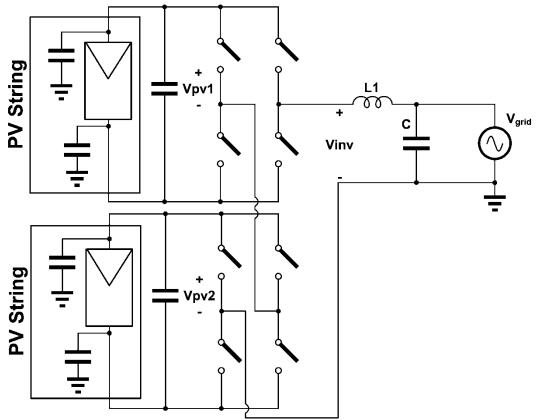

#### 4.1. Cascaded H-bridge (CHB)

The simplest multilevel structure consists in connecting H-bridge cells in series by its AC-side, while using a different photovoltaic panel for each DC-link [17]. A schematic of a two stage CHB multilevel inverter with a second order output filter is shown in Fig. 9.

Fig. 9. The cascaded H-bridge multilevel inverter.

It should be pointed out that this multilevel topology requires as many isolated power sources as H-bridge power stages, which is considered a problem when it is used in classical power electronics applications (e.g. high power motor drives). However, photovoltaic modules meet this requirement, which in turn has made the CHB topology an interesting choice for the photovoltaic power inverter design process [18].

One of the most interesting feature in this topology is the ability to boost the inverter AC side voltage enough to inject current into the grid without using neither a transformer nor an additional boost converter [5,25,44], due to the fact that as much modules as desired can be stacked in series, thus increasing the number of output voltage levels (e.g. in Fig. 9, a maximum of Vpv1+Vpv2 is obtained at the inverter output voltage, Vinv). In fact, this characteristic has motivated the study of different maximum power point tracking strategies which enables the independent control of each group of photovoltaic modules [45,46], while controlling the current injected into the electric grid. It is worth pointing out that some works have exploited this modular structure to work even with damaged power cells [47,48], thus increasing the reliability of the system.

Finally, it should be noted that the number of semiconductors needed would affect the cost and the reliability, and that the leakage current can be high, depending on the number of cells connected in series.

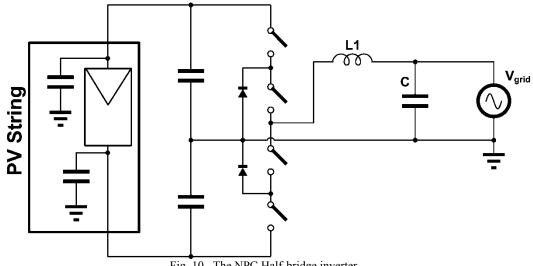

#### 4.2. NPC Half-bridge

The NPC Half-bridge is the single-phase revision of the multilevel topology used in high-power motor-drive applications [19], which has been recently proposed as an alternative topology to be used in photovoltaic inverters design. It consists of a branch with 4 transistors and 2 clamping diodes, as shown in Fig. 10. The diodes offer a free-wheeling path for the output current that causes the 0V output voltage state [8].

Fig. 10. The NPC Half-bridge inverter.

On the one hand, the NPC Half-bridge topology works in a similar way that the half-bridge, but it has better efficiency, less current ripple [4] and a constant common mode voltage, thus preventing the leakage currents. On the other hand, the NPC topology has a performance similar to the full-bridge topology with unipolar PWM modulation, i.e. 3 output inverter voltage levels, and a similar voltage derivative. Consequently, the output filter and the performance of the converter are similar to an unipolar PWM modulated full-bridge [14].

The main drawbacks of this topology are listed next. It requires a large number of power semiconductors, a high capacity bank of capacitors [5,25] and a high input voltage, which doubles the full-bridge input voltage [5]. Another important problem is the transient overvoltage that takes place at the internal transistors, due to the absence of capacitors in parallel [20]. Nevertheless, this problem can be solved by using a snubber circuit. Furthermore, power losses are not uniformly distributed over all the semiconductors [21].

Finally, it is worth pointing out that this alternative is about 15% cheaper than cascaded H-bridge (CHB) or flyingcapacitor (FC) topologies [22], as well as a robust and simple one, so that it can be found in some commercial transformerless inverters. Moreover, some manufacturers of semiconductors offer power modules with an integrated complete NPC branch.

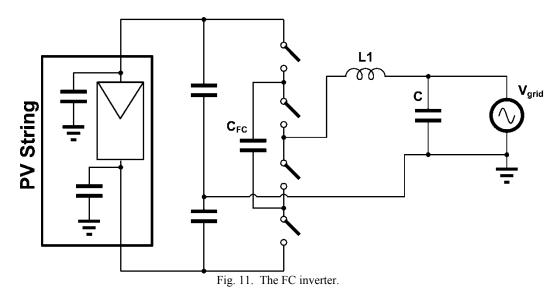

#### 4.3. Flying capacitor (FC)

The structure and performance of the flying capacitor topology is similar to the NPC topology described above [53,54], so that it presents a very low leakage current. The floating capacitor CFC depicted in Fig. 11 replaces the clamping diodes used in the NPC half-bridge topology, and provides the third level at output voltage, i.e. the 0V level.

To avoid an undesired overvoltage at the transistors during the startup, a special circuit to pre-charge the floating capacitor will be required [23]. In addition, the voltage of the floating capacitor has to be controlled in order to maintain its value at a given reference, so the FC control strategy is more complicated than the NPC control strategy [5,56]. However, a simple technique that uses the inductive output impedance of the inverter can be used when there are few output levels [57]. This technique is based on the redundant switches states of the inverter [58,59].

An interesting feature of the FC inverter is the fault-tolerant operation that can be obtained when the number of levels is high enough. This operation allows the inverter to continue working even if a transistor or a floating capacitor is damaged [60,61].

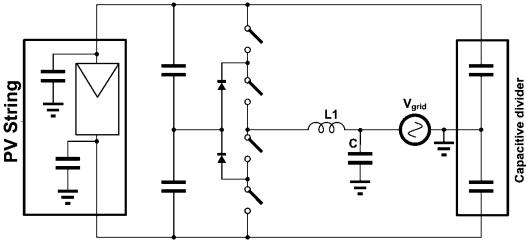

#### 4.4. NPC half-bridge with a capacitive divider

This topology, adds a capacitive divider to the aforementioned NPC half-bridge [4], thus avoiding the direct connection of the neutral wire to the midpoint of the dc-link, as shown in Fig. 12. This ensures that the voltage of the strings poles remains constant through the additional capacitive divider, hence obtaining a reduced leakage current.

Fig. 12. The NPC half-bridge with capacitive divider.

It is important pointing out that if neutral wire is connected directly to the midpoint of the dc-link the use of highaccuracy sensors is necessary to ensure that no dc-current is injected to the electrical so that the cost and complexity of the whole system is increased. In the NPC half-bridge with a capacitive divider topology, the capacitors integrates the dc component of the output current over the time, thereby facilitating its detection with less-accurate voltage sensors and, therefore, with a lower cost despite the two additional high current capacitors. It should be noted that the rest of advantages and drawbacks of the proposed topology are the same as the ones derived from the NPC half-bridge topology.

#### 4.5. Conergy NPC

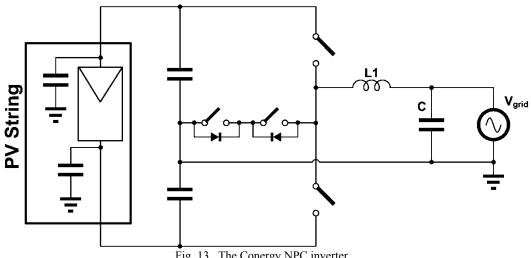

The Conergy NPC is another variant of the NPC half-bridge that has been developed and patented by Conergy [24]. In Fig. 13 is shown the basic schematic of the topology, which consists of a half-bridge inverter and a branch that can apply 0V to the output voltage.

The characteristics of this topology are similar to those of the NPC half-bridge, but it offers a higher efficiency, making it suitable for low-power applications [63].

Fig. 13. The Conergy NPC inverter.

# 4.6. Active NPC (ANPC)

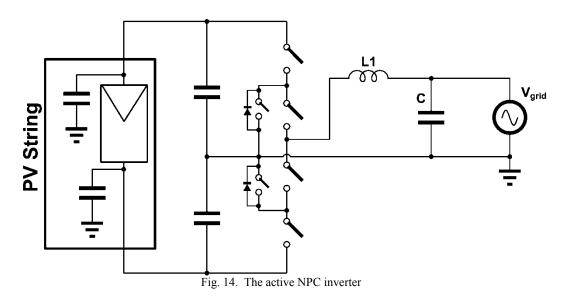

It is possible to substitute the clamping diodes of the NPC inverter by power transistors with anti-parallel diodes, which lead to the topology shown in Fig. 14. This topology is called active NPC (ANPC) and its main feature lies in the control of the current path during the free-wheeling periods [63,64], which lets the distribution of losses to be improved [65-67], thus loading uniformly the power transistors, and increasing the maximum output power of the converter [49,51]. However, sometimes it could be cheaper to select a higher maximum current NPC topology [68], especially in low-power applications.

# 5. Characteristics of transformerless PV inverters at a glance

In order to get a better performance understanding of the several topologies presented up until now, it is interesting to compare them by previously defining the next key items:

- *Number of input capacitors and capacitance:* The input capacitors are used to supply the AC component of the input current. In some topologies more than one capacitor (or more than one bank of capacitors) is necessary and, therefore, the design of the dc-link is more complicated. In some topologies the frequency of the input current is low and, therefore, the input capacitance necessary can reach high values.

- *Power semiconductors:* It is important to use the minimum number of power switches, as it affects directly to the cost of the converter. The voltage rating of a semiconductor usually affects its power losses and, therefore, it is interesting to implement topologies with a low voltage rating in the switches.

- *Output voltage:* A good output voltage quality implies a good output current quality, with a low current harmonic content which is easy to filter out. This implies that the topologies that are capable of obtaining a three level output voltage have better performance and lower electromagnetic emission than those that have only two level output voltage.

- *Number of MPPTs:* A photovoltaic inverter has to be able to control its input voltage to manage the power obtained from the photovoltaic modules. Some topologies can control more than one input voltage, so it is possible to track several maximum power points, hence improving the performance under different isolation conditions.

- Leakage current: As explained previously in the introduction, it is mandatory to reduce the leakage current in the transformerless inverters.

In Table 1 it is shown the comparative between the proposed topologies by using the items previously defined.

#### Table 1.

| Comparison | of the | ceveral | nronosed | topologies  |

|------------|--------|---------|----------|-------------|

| Comparison | or the | Several | proposed | topologics. |

|                                  | H-bridge (unipolar<br>PWM) | H-bridge (bipolar PWM) | Half-bridge | HERIC Topology | H5 Topology | Half-bridge with GCC | Cascaded H-bridge<br>(n cells) | NPC half-bridge | Flying Capacitor (FC) | NPC variant | Conergy NPC | Active NPC (ANPC) |

|----------------------------------|----------------------------|------------------------|-------------|----------------|-------------|----------------------|--------------------------------|-----------------|-----------------------|-------------|-------------|-------------------|

| Input capacitors                 | 1                          | 1                      | 2           | 1              | 1           | 2                    | n                              | 2               | 3                     | 4           | 2           | 2                 |

| Input<br>capacitance             | Low                        | Low                    | High        | Low            | Low         | Medium               | Very<br>High                   | High            | High                  | High        | High        | High              |

| Switches                         | 4                          | 4                      | 2           | 6              | 5           | 4                    | 4n                             | 4               | 4                     | 4           | 4           | 6                 |

| Diodes                           | 0                          | 0                      | 0           | 2              | 0           | 0                    | 0                              | 2               | 0                     | 2           | 0           | 0                 |

| Transistors<br>voltage           | 400V                       | 400V                   | 800V        | 400V           | 400V        | 800V                 | 400V/n                         | 400V            | 400V                  | 400V        | 400V        | 400V              |

| Output voltage<br>levels         | 3                          | 2                      | 2           | 3              | 3           | 2                    | 2n-1                           | 3               | 3                     | 3           | 3           | 3                 |

| First harmonic                   | 2fsw                       | fsw                    | fsw         | 2fsw           | 2∙fw        | fsw                  | 2n · fsw                       | 2fsw            | 2fsw                  | 2fsw        | 2fsw        | 2fsw              |

| Electromagnetic<br>Interferences | Low                        | High                   | High        | Low            | Low         | High                 | Very<br>low                    | Low             | Low                   | Low         | Low         | Low               |

| Number of<br>MPPTs | 1    | 1   | 1           | 1           | 1           | 2           | n      | 1           | 1           | 1           | 1           | 1        |

|--------------------|------|-----|-------------|-------------|-------------|-------------|--------|-------------|-------------|-------------|-------------|----------|

| Leakage current    | High | Low | Very<br>low | Very<br>low | Very<br>low | Very<br>low | Medium | Very<br>low | Very<br>low | Very<br>low | Very<br>low | Very low |

# 6. Conclusions

In this paper a review of transformerless topologies for single-phase photovoltaic inverters is presented. On one hand, alternatives based on classical topologies, derived from half-bridge and full-bridge are widely studied. On the other hand, topologies based on multi-level inverters are presented, as they are under development. Main problem of transformerless topologies is the fluctuating voltage to ground at input poles. Two methods for solving this problem are presented: disconnecting the photovoltaic panels from the grid during free-wheeling periods, or connecting the neutral wire to one pole of the photovoltaic panels.

In the half-bridge topologies the input current has a component of 50Hz, while in the full-bridge topologies the frequency of this component is 100Hz. Hence, the full-bridge topologies require less input capacitance than the half-bridge ones. Thus, a full-bridge converter might have a better reliability and a lower cost than a half-bridge one.

The CHB topology uses the lowest voltage rating switches, so it can achieve a high efficiency; however, it needs a large number of switches. On the contrary, the half-bridge topology needs only 2 switches, but they need to block the highest voltage.

In order to obtain a good ratio between performance and converter cost, it is desirable to obtain a three-level output voltage. The full-bridge topology and some multilevel half-bridge topologies allow the converter to obtain three level output voltage. Furthermore, the CHB topology can produce a higher number of output voltage levels.

The Generation Control Circuit can be used with the half-bridge topology, thus controlling two input voltages. If the CHB topology is used, then a higher number of voltages can be controlled at the input of the converter.

The HERIC and H5 topologies present a very low leakage current if the synchronization between the gate signals is correctly adjusted. In addition, it is worth pointing out that all the half-bridge topologies with the neutral connected to the midpoint of the input voltage presents pretty low leakage current.

# Acknowledgement

This work is supported by the Spanish Ministry of Science and Innovation under grant ENE2009-13998-C02-02.

# References

- [1] A. Jäger-Waldau, Photovoltaics and renewable energies in Europe, Renewable and Sustainable Energy Reviews. 11-7 (2007) 1414-1437.

- [2] I. M. de Alegría Mancisidor, P. Díaz de Basurto Uraga, I. Martínez de Alegría Mancisidor, and P. Ruiz de Arbulo López, European Union's renewable energy sources and energy efficiency policy review: The Spanish perspective, Renewable and Sustainable Energy Reviews. 13-1 (2009) 100-114.

- [3] M. A. Eltawil and Z. Zhao, Grid-connected photovoltaic power systems: Technical and potential problems--A review, Renewable and Sustainable Energy Reviews. 14-1 (2010) 112-129.

- [4] M. D. Manjrekar, R. Kieferndorf, and G. Venkataramanan, Power electronic transformers for utility applications, Conference Record of the 2000 IEEE Industry Appliactions Conferenc. 4 (2000) 2496-2502.

- [5] M. Calais, V. G. Agelidis, and M. Meinhardt, Multilevel converters for single-phase grid connected photovoltaic systems: an overview, Solar Energy. 66-5 (1999) 325-335.

- [6] T. Kerekes, R. Teodorescu, P. Rodriguez, G. Vazquez, and E. Aldabas, A new high-efficiency single-phase transformerless PV inverter topology, IEEE Transactions on Industrial Electronics. 99 (2009) 1.

- [7] S. V. Araujo, P. Zacharias, and B. Sahan, Novel grid-connected non-isolated converters for photovoltaic systems with grounded generator, PESC 2008. IEEE Power Electronics Specialists Conference. (2008) 58-65.

- [8] B. Burger and D. Kranzer, Extreme high efficiency PV-power converters, EPE '09. 13th European Conference on Power Electronics and Applications. (2009) 1-13.

- [9] D. Velasco, C. L. Trujillo, G. Garcerb, and E. Figueres, Review of anti-islanding techniques in distributed generators, Renewable and Sustainable Energy Reviews. 14-6 (2010) 1608-1614.

- [10] I. Dincer, Renewable energy and sustainable development: a crucial review, Renewable and Sustainable Energy Reviews. 4-2 (2000) 157-175.

- [11] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, A review of single-phase grid-connected inverters for photovoltaic modules, IEEE Transactions on Industry Applications. 41-5 (2005) 1292-1306.

- [12] V. Salas and E. Olías, Overview of the state of technique for PV inverters used in low voltage grid-connected PV systems: Inverters below 10kW, Renewable and Sustainable Energy Reviews. 13-6-7 (2008) 1541-1550.

- [13] M. Lin, T. Fen, Z. Fei, J. Xinmin, and T. Yibin, Leakage current analysis of a single-phase transformer-less PV inverter connected to the grid, ICSET 2008. IEEE International Conference on Sustainable Energy Technologies. (2008) 285-289.

- [14] O. Lopez, F. D. Freijedo, A. G. Yepes, P. Fernandez-Comesaa, J. Malvar, R. Teodorescu, and J. Doval-Gandoy, Eliminating Ground Current in a Transformerless Photovoltaic Application, IEEE Transactions on Energy Conversion. 25-1 (2010) 140-147.

- [15] R. Gonzalez, E. Gubia, J. Lopez, and L. Marroyo, Transformerless Single-Phase Multilevel-Based Photovoltaic Inverter, IEEE Transactions on Industrial Electronics. 55-7 (2008) 2694-2702.

- [16] F.Schimpf and L.E.Norum, Grid connected Converters for Photovoltaic, State of the Art, Ideas for Improvement of Transformerless Inverters, NORPIE. (2008)

- [17] T. Kerekes, R. Teodorescu, and U. Borup, Transformerless Photovoltaic Inverters Connected to the Grid, APEC 2007 - Twenty Second Annual IEEE Applied Power Electronics Conference. (2007) 1733-1737.

- [18] Ministerio de Economía, "Real Decreto 1663/2000, de 29 de Septiembre, sobre conexión de instalaciones fotovoltaicas a la red de baja tensión," 2000.

- [19] IEEE Standard for Interconnecting Distributed Resources With Electric Power Systems, IEEE Std 1547-2003. (2003) 0-16.

- [20] C. Liuchen and H. M. Kojabadi, "Review of interconnection standards for distributed power generation," 2002, pp. 36-40.

- [21] R. V. D'Aiello, E. N. Twesme, and D. A. Fagnan, Performance of Solarex/Philadelphia Electric Co. amorphous silicon PV test site, Conference Record of the Twentieth IEEE Photovoltaic Specialist Conference. (1988) 1092-1097.

- [22] G. Spagnuolo, G. Petrone, S. V. Araujo, C. Cecati, E. Friis-Madsen, E. Gubia, D. Hissel, M. Jasinski, W. Knapp, M. Liserre, P. Rodriguez, R. Teodorescu, and P. Zacharias, Renewable Energy Operation and Conversion Schemes: A Summary of Discussions During the Seminar on Renewable Energy Systems, IEEE Industrial Electronics Magazine. 4-1 (2010) 38-51.

- [23] D. M. Baker, V. G. Agelidis, and C. V. Nayer, A comparison of tri-level and bi-level current controlled gridconnected single-phase full-bridge inverters, ISIE '97. , Proceedings of the IEEE International Symposium on Industrial Electronics. 2 (1997) 463-468.

- [24] S. Araujo, P. Zacharias, and R. Mallwitz, Highly Efficient Single-Phase Transformerless Inverters for Grid-Connected Photovoltaic Systems, IEEE Transactions on Industrial Electronics. 99 (2000) 1.

- [25] O. Lopez, R. Teodorescu, and J. Doval-Gandoy, Multilevel transformerless topologies for single-phase gridconnected converters, IECON 2006 - 32nd Annual Conference on IEEE Industrial Electronics. (2006) 5191-5196.

- [26] Z. Kai, Z. Yunbin, Z. Yonggao, and K. Yong, Reduction of Common Mode EMI in a Full-Bridge Converter through Automatic Tuning of Gating Signals, IPEMC 2006. CES/IEEE 5th International Power Electronics and Motion Control Conference. 1 (2006) 1-5.

- [27] H. Hinz and P. Mustcher, Single phase voltage source inverters without transformer in photovoltaic applications, PEMC '96. International Power Electronics and Motion Control Conference and Exhibition. 3 (1996) 161-165.

- [28] J. Qin and J. Brown, Comparison of electromagnetic compatibility of different PV inverter, 4th IEEE International Conference on Power Electronics and Drive Systems. 1 (2001) 420-424.

- [29] C. L. Shen and S. T. Peng, A Half-Bridge PV System with Bi-direction Power Flow Controlling and Power Quality Improvement, PEDS '07. 7th International Conference on Power Electronics and Drive Systems. (2007) 725-731.

- [30] H. Schmidt, C. Siedle, and J. Ketterer, Patente: Inversor u ondulador para convertir una tensión eléctrica continua en una corriente alterna o en una tensión alterna, DE 102 21 592, 2009.

- [31] J. M. A. Myrzik and M. Calais, String and module integrated inverters for single-phase grid connected photovoltaic systems - a review, 2003 IEEE Bologna Power Tech Conference Proceedings. 2 (2003) 8.

- [32] M. Victor, F. Greizer, S. Bremicker, and U. Hübler, Patent: Method of converting a DC voltage of a DC source, in particular of a photovoltaic DC source, in an AC voltage, EP 1 626 494, 2004.

- [33] G. Vazquez, T. Kerekes, A. Rolan, D. Aguilar, A. Luna, and G. Azevedo, Losses and CMV evaluation in transformerless grid-connected PV topologies, ISIE 2009. IEEE International Symposium on Industrial Electronics. (2009) 544-548.

- [34] T. Shimizu, O. Hashimoto, and G. Kimura, A novel high-performance utility-interactive photovoltaic inverter system, IEEE Transactions on Power Electronics. 18-2 (2003) 704-711.

- [35] T. Shimizu, M. Hirakata, T. Kamezawa, and H. Watanabe, Generation control circuit for photovoltaic modules, IEEE Transactions on Power Electronics. 16-3 (2001) 293-300.

- [36] K. Hirachi, M. Yamanaka, K. Kajiyama, and S. Isokane, Circuit configuration of bidirectional DC/DC converter specific for small scale load leveling system, PCC Osaka 2002. Proceedings of the Power Conversion Conference. 2 (2002) 603-609.

- [37] B. Wu, High Power Converters and AC Drives, Wiley, IEEE Press, 2006

- [38] S. Daher, J. Schmid, and F. L. M. Antunes, Multilevel Inverter Topologies for Stand-Alone PV Systems, IEEE Transactions on Industrial Electronics. 55-7 (2008) 2703-2712.

- [39] J. Rodriguez, L. Jih-Sheng, and Z. P. Fang, Multilevel inverters: a survey of topologies, controls, and applications, IEEE Transactions on Industrial Electronics. 49-4 (2002) 724-738.

- [40] A Pandey, B Singh, B N Singh, A Chandra, K Al-Haddad, and D P Kothari, A Review of Multilevel Power Converters, The Institution of Engineers. 86 (2006)

- [41] Marco Di Lella and Riccardo Ramin, IGBTs for 3-level inverters, Sept ed. 2008

- [42] M. Malinowski, K. Gopakumar, J. Rodriquez, and M. Perez, A Survey on Cascaded Multilevel Inverters, IEEE Transactions on Industrial Electronics. 99 (2000) 1.

- [43] B. Kavidha and K. Rajambal, Transformerless cascaded inverter topology for photovoltaic applications, IICPE 2006. India International Conference on Power Electronics. (2006) 328-331.

- [44] S. A. Khajehoddin, A. Bakhshai, and P. Jain, The Application of the Cascaded Multilevel Converters in Grid Connected Photovoltaic Systems, EPC 2007. IEEE Canada Electrical Power Conference. (2007) 296-301.

- [45] O. Alonso, P. Sanchis, E. Gubia, and L. Marroyo, Cascaded H-bridge multilevel converter for grid connected photovoltaic generators with independent maximum power point tracking of each solar array, PESC '03. IEEE 34th Annual Power Electronics Specialist Conference. 2 (2003) 731-735.

- [46] S. Kouro, W. Bin, A. Moya, E. Villanueva, P. Correa, and J. Rodriguez, Control of a cascaded H-bridge multilevel converter for grid connection of photovoltaic systems, IECON '09. 35th Annual Conference of IEEE Industrial Electronics. (2009) 3976-3982.

- [47] W. Sanmin, W. Bin, L. Fahai, and S. Xudong, Control method for cascaded H-bridge multilevel inverter with faulty power cells, APEC '03. Eighteenth Annual IEEE Applied Power Electronics Conference and Exposit. 1 (2003) 261-267.

- [48] S. J. Lee, H. S. Bae, and B. H. Cho, Modeling and control of the single-phase photovoltaic grid-connected cascaded H-bridge multilevel inverter, ECCE 2009. IEEE Energy Conversion Congress and Exposition. (2009) 43-47.

- [49] J. Rodriguez, S. Bernet, P. Steimer, and I. Lizama, A Survey on Neutral Point Clamped Inverters, IEEE Transactions on Industrial Electronics. 99 (2000) 1.

- [50] Z. Zhao, C. Zhan, Y. Han, T. Xie, and L. Zhao, Analysis on voltage unbalance between the inner and outer devices in three level IGBT converters, PEDS '99. Proceedings of the IEEE 1999 International Conference on Power Electronics and Drive Systems. 1 (1999) 218-224.

- [51] T. Bruckner, S. Bernet, and H. Guldner, The active NPC converter and its loss-balancing control, IEEE Transactions on Industrial Electronics. 52-3 (2005) 855-868.

- [52] P. Panagis, F. Stergiopoulos, P. Marabeas, and S. Manias, Comparison of state of the art multilevel inverters, PESC 2008 IEEE Power Electronics Specialists Conference. (2008) 4296-4301.

- [53] L. Bor-Ren and H. Chun-Hao, Single-phase converter with flying capacitor topology, TENCON 2004. IEEE Region 10 Conferente. (2004) 73-76.

- [54] X. Lie and G. A. Vassilios, VSC Transmission System Using Flying Capacitor Multilevel Converters and Hybrid PWM Control, IEEE Transactions on Power Delivery. 22-1 (2007) 693-702.

- [55] S. Thielemans, A. Ruderman, and J. Melkebeek, Self-precharge in single-leg flying capacitor converters, IECON '09. 35th Annual Conference of IEEE Industrial Electronics. (2009) 812-817.

- [56] B. Wu, Other Multilevel Voltage Source Inverters, in High Power Converters and AC Drives. Wiley; IEEE Press, 2006, pp. 179-186.

- [57] L. Bor-Ren and H. Chun-Hao, Single-phase capacitor clamped inverter with simple structure, ISCAS '04. Proceedings of the 2004 International Symposium on Circuits and Systems. 5 (2004)

- [58] B. R. Lin, T. L. Hung, and C. H. Huang, Bi-directional single-phase half-bridge rectifier for power quality compensation, IEE Proceedings - Electric Power Applications. 150-4 (2003) 397-406.

- [59] S. Gui-Jia, Multilevel DC-link inverter, IEEE Transactions on Industry Applications. 41-3 (2005) 848-854.

- [60] C. Alian, Z. Chenghui, H. Xiangning, and C. Naxin, Fault-tolerant design for flying capacitor multilevel inverters, IPEMC '09. IEEE 6th International Power Electronics and Motion Control Conference. (2009) 1460-1464.

- [61] K. Xiaomin, K. A. Corzine, and Y. L. Familiant, A unique fault-tolerant design for flying capacitor multilevel inverter, IEEE Transactions on Power Electronics. 19-4 (2004) 979-987.

- [62] P.Knaup, International Patent: Inverter, WO 2007/048420, 2007.

- [63] M. Lin, T. Kerekes, R. Teodorescu, J. Xinmin, D. Floricau, and M. Liserre, The high efficiency transformer-less PV inverter topologies derived from NPC topology, EPE '09. 13th European Conference on Power Electronics and Applications. (2009) 1-10.

- [64] M. Lin, J. Xinmin, T. Kerekes, M. Liserre, R. Teodorescu, and P. Rodriguez, The PWM strategies of gridconnected distributed generation active NPC inverters, ECCE 2009. IEEE Energy Conversion Congress and Exposition. (2009) 920-927.

- [65] D. Floricau, E. Floricau, and M. Dumitrescu, Natural doubling of the apparent switching frequency using threelevel ANPC converter, ISNCC 2008. International School on Nonsinusoidal Currents and Compensation. (2008) 1-6.

- [66] D. Floricau, E. Floricau, and G. Gateau, Three-level active NPC converter: PWM strategies and loss distribution, IECON 2008. 34th Annual Conference of IEEE Industrial Electronics. (2008) 3333-3338.

- [67] D. Floricau, C. L. Popescu, M. O. Popescu, E. Floricau, and L. Spataru, A comparison of efficiency for three-level NPC and Active NPC voltage source converters, CPE '09. Compatibility and Power Electronics. (2009) 331-336.

- [68] J. A. Sayago, S. Bernet, and T. Bruckner, Comparison of Medium Voltage IGBT-based 3L-ANPC-VSCs, PESC 2008. IEEE Power Electronics Specialists Conference. (2008) 851-858.