### Escola Tècnica Superior d'Enginyeria Informàtica Universitat Politècnica de València

## Development of a Highly Capable Processor for a Multicore Architecture on FPGAs #4

Trabajo Fin de Grado

Grado en Ingeniería Informática

Autor: Mark Antony Holland

*Tutores:* José Flich Cardo Xavier Molero Prieto Pedro López Rodríguez

CURSO 2014-2015

#### Resumen

En este trabajo se diseña e implementa un procesador con ejecución fuera de orden siguiendo como modelo el algoritmo de Tomasulo. El procesador es reconfigurable y permite tanto la instanciación de un número variable de unidades funcionales y recursos como la obtención de diferentes configuraciones, cada una con una relación prestaciones/recursos distinta. El procesador se está integrando en la arquitectura PEAK desarrollada en el Grupo de Arquitecturas Paralelas (GAP) del Departamento de Informática de Sistemas y Computadores (DISCA) de la Universitat Politècnica de València (UPV).

El procesador incluye todos los componentes esenciales para su completa operatividad así como soporte para un conjunto amplio del juego de instrucciones de la arquitectura MIPS32. Cabe añadir que todos los componentes se han diseñado e implementado por completo en el marco del presente trabajo.

El trabajo incluye el diseño de tests de prueba y diferentes programas para verificar y validar cada componente y las diferentes configuraciones finales del procesador. Por otro lado, se ha sintetizado cada uno de los componentes con el fin de obtener los recursos que necesita para su implementación en un sistema FPGA. A lo largo del desarrollo del trabajo se han utilizado herramientas comerciales como Vivado de Xilinx, simuladores (QtSpim) y software de control de versiones (Git).

Palabras clave: procesador, PEAK, FPGA, multinúcleo, parametrizable.

#### Resum

En aquest treball es dissenya i implementa un processador amb execució fora d'ordre seguint com a model l'algorisme de Tomasulo. El processador és reconfigurable i permet tant la instanciació d'un nombre variable d'unitats funcionals i recursos com l'obtenció de diferents configuracions, cadascuna amb una relació prestacions/recursos diferent. El processador s'està integrant en l'arquitectura PEAK desenvolupada en el Grup d'Arquitectures Paral·leles (GAP) del Departament d'Informàtica de Sistemes i Computadors (DISCA) de la Universitat Politècnica de València (UPV).

El processador inclou tots els components essencials per a la seua completa operativitat així com suport per a un conjunt ampli del joc d'instruccions de l'arquitectura MIPS32. Cal afegir que tots els components s'han dissenyat i implementat per complet en el marc del present treball.

El treball inclou el diseny de tests de prova i diferents programes per a verificar i validar cada component i les diferents configuracions finals del processador. D'altra banda s'ha sintetitzat cadascun dels components amb la finalitat d'obtenir els recursos que necessita per a la seua implementació en un sistema FPGA. Al llarg del desenvolupament del treball s'han fet servir diverses ferramentes comercials com ara Vivado de Xilinx, simuladors (QtSpim) i programari de control de versions (Git).

Paraules clau: processador, PEAK, FPGA, multinucli, parametritzable.

#### Abstract

This project involves the design and implementation of a processor with outof-order execution using the Tomasulo algorithm. The processor is configurable, allowing a variable number of resources and functional units. Different configurations can be created, each with a different performance/resource ratio. The processor is being integrated into the PEAK architecture developed by the Grupo de Arquitecturas Paralelas (GAP) del Departamento de Informática de Sistemas y Computadores (DISCA) de la Universitat Politècnica de València (UPV). PEAK is a multi-core arquitecture for multi-FPGA development environments and prototyping.

The processor includes all the essential components and is fully operational along with support for a wide array of the MIPS32 architecture instruction set. All components have been designed and implemented as part of this project.

A multitude of tests and programs have been designed to verify and validate each component along with the different configurations of the processor. The synthesis of each of the components and the processor (in its different configurations) has also been performed with the goal of obtaining the resource usage on a FPGA system. During the development of this project different commercial tools have been used such as Xilinx Vivado, simulators (QtSpim) and version control software (Git).

Keywords: processor, PEAK, FPGA, multicore, configurable.

#### Abbreviations

ALU (Arithmetic Logic Unit) BRANCH (Branch) BTB (Branch Target Buffer) BUS (Common Data Bus) CAS (Controlled Adder Subtractor) CLA (Carry-Lookahead Adder) COMMIT (Commit stage) CPA (Carry Propagation Adder) **CPI** (Cycles Per Instruction) CSA (Carry Save Adder) DEC (Decoder) DISCA (Department of Computer Engineering) EX (*Execute stage*) FPGA (Field Programmable Gate Array) FPU (Floating Point Unit) GPR (General Purpose Register) HDL (*Hardware Description Lenguage*) HI (*High register*) ID (Instruction Decode) IDE (Integrated Development Environment) IF (*Instruction Fetch*) IPC (Instructions per cycle) L1 (First Level Cache) LO (Low register) MEM (*Memory*) RAM (Random Access Memory) PC (Program Counter) **RB INT** (*Integer Register Bank*) **RB FP** (*Floating Point Register Bank*) RISC (Reduced Instruction Set Computer) ROB (*Re-Order Buffer*) RR (Round Robin arbiter) **RS** (*Reservation Station*) WB (Writeback)

# Contents

| 1. | Intr | oduction                                    | 1 |

|----|------|---------------------------------------------|---|

|    | 1.1. | Context                                     | 1 |

|    | 1.2. | Objectives                                  | 3 |

|    | 1.3. | Structure of the Document                   | 3 |

|    | 1.4. | Use of References                           | 4 |

| 2. | Prio | r Knowledge                                 | 7 |

|    | 2.1. | IEEE Standard for Floating-Point Arithmetic | 7 |

|    | 2.2. | The MIPS Architecture                       | 8 |

|    |      | 2.2.1. Instruction Format                   | 0 |

|    | 2.3. | Instruction Scheduling                      | 1 |

|    |      | 2.3.1. Tomasulo Algorithm                   | 3 |

|    |      | 2.3.2. Dynamic Branch Prediction            | 4 |

|    |      | 2.3.3. Memory Disambiguation                | 4 |

| 3. | Too  | s 1                                         | 7 |

|    | 3.1. | Xilinx Vivado                               | 7 |

|    | 3.2. | QtSpim                                      | 9 |

|    | 3.3. | Git                                         | 0 |

|    | 3.4. | log2timetable                               | 1 |

| 4. | Ove  | rview of the Processor 2                    | 3 |

|    | 4.1. | Datapath                                    | 3 |

|    | 4.2. | Dataflow                                    | 7 |

|    | 4.3. | Processor Configurations                    | 8 |

| 5. | Spe   | cific Components 3           | 31         |

|----|-------|------------------------------|------------|

|    | 5.1.  | 32-bit Register Bank         | 31         |

|    | 5.2.  | Branch Target Buffer         | 34         |

|    | 5.3.  | Memory Access Unit           | 36         |

| 6. | Res   | ults 4                       | 11         |

|    | 6.1.  | Design Verification          | 11         |

|    |       | 6.1.1. Superscalar           | 12         |

|    |       | 6.1.2. Memory Disambiguation | 14         |

|    |       | 6.1.3. Conditional Branches  | <b>1</b> 6 |

|    |       | 6.1.4. Benchmarks            | 18         |

|    | 6.2.  | Design Synthesis 5           | 50         |

| 7. | Con   | clusion 5                    | 55         |

|    | 7.1.  | Outcome                      | 55         |

|    | 7.2.  | Extensions and future work   | 56         |

| Aŗ | openo | dix 5                        | 57         |

| A. | Data  | apath buses 5                | 59         |

|    | A.1.  | Register Banks               | 59         |

|    | A.2.  | Branch Target Buffer         | 50         |

|    | A.3.  | Memory Access Unit           | 50         |

| B. | Ben   | chmark source code 6         | 51         |

|    | B.1.  | axpy                         | 51         |

|    | B.2.  | pi 6                         | 62         |

| Bi | bliog | graphy 6                     | 54         |

# List of Figures

| 2.1. | Simple precision floating point | 8  |

|------|---------------------------------|----|

| 2.2. | MIPS                            | 10 |

| 2.3. | I-type                          | 10 |

| 2.4. | J-type                          | 11 |

| 2.5. | R-type                          | 11 |

| 2.6. | MIPS program 1                  | 12 |

| 2.7. | MIPS program 2                  | 13 |

| 2.8. | MIPS program 3                  | 15 |

| 3.1. | Vivado                          | 18 |

| 3.2. | QtSpim                          | 19 |

| 3.3. | Git                             | 20 |

| 3.4. | log2timetable                   | 21 |

| 4.1. | Datapath structure              | 24 |

| 4.2. | Dataflow overview               | 28 |

| 5.1. | Diagram of RB register fields   | 32 |

| 5.2. | Diagram of the RB               | 32 |

| 5.3. | Diagram of the BTB              | 34 |

| 5.4. | Diagram of BTB register fields  | 35 |

| 5.5. | Automaton used by the BTB       | 36 |

| 5.6. | Diagram of the MEM              | 37 |

| 5.7. | Diagram of byte enable bits     | 38 |

| 6.1. | Arithmetic program 1            | 42 |

| 6.2. | Timetable 1                     | 43 |

| 6.3.  | Timetable 2                                 | 43 |

|-------|---------------------------------------------|----|

| 6.4.  | Arithmetic program 2                        | 44 |

| 6.5.  | Timetable 3                                 | 44 |

| 6.6.  | Memory access program 1                     | 45 |

| 6.7.  | Timetable 4                                 | 45 |

| 6.8.  | Branch program 1                            | 46 |

| 6.9.  | Timetable 5                                 | 47 |

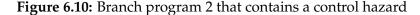

| 6.10. | Branch program 2                            | 47 |

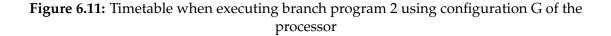

| 6.11. | Timetable 6                                 | 47 |

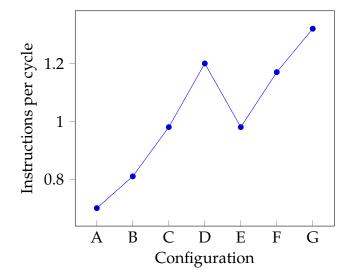

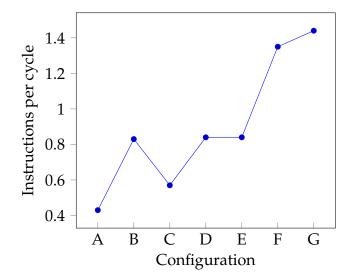

| 6.12. | <i>axpy</i> benchmark                       | 49 |

| 6.13. | <i>pi</i> benchmark                         | 50 |

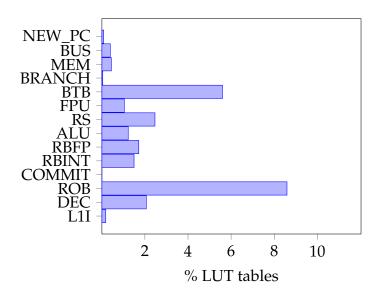

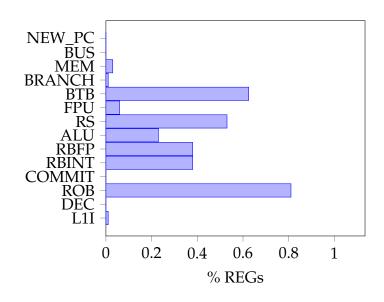

| 6.14. | Configuration G synthesis (LUTs)            | 51 |

| 6.15. | Configuration G synthesis (REGs)            | 52 |

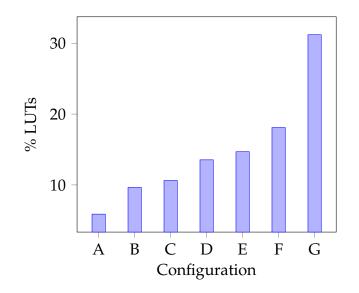

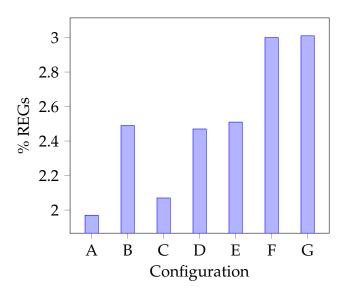

| 6.16. | Resource usage of all configurations (LUTs) | 53 |

| 6.17. | Resource usage of all configurations (REGs) | 53 |

| A.1.  | fromDEC bus encoding                        | 59 |

| A.2.  | fromBUSX bus encoding                       | 59 |

| A.3.  | fromCOMMITX bus encoding                    | 59 |

| A.4.  | fromCOMMITX bus encoding                    | 60 |

| A.5.  | RSX bus encoding                            | 60 |

# List of Tables

| 6.1. | Processor configurations |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 4 | 2 |

|------|--------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|---|

|------|--------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|---|

# Listings

| 4.1. | Macro usage example                  | 28 |

|------|--------------------------------------|----|

| 4.2. | Processor configuration using macros | 29 |

### CHAPTER 1

## Introduction

The work detailed in this document involves the design and implementation of a processor with *out-of-order* execution based on a MIPS architecture.

An important aspect about the implemented processor is that it is quickly and widely configurable providing the possibility to add and remove resources in order to create distinct configurations which can later be studied. The processor has the possibility of being in any one of seven different configurations.

The most complex configuration supported by the processor contains four instruction decoders with a configurable size re-order buffer, four buses, four commit units, two arithmetic-logic units, two floating point arithmetic units and multiple reservation stations for each operator.

Some other notable aspects are that the floating point unit is contained entirely inside the core of the processor. Jumps and conditional branches with prediction are also supported so that more complex algorithms may be executed on the processor. Finally, memory disambiguation is supported which enables safe *out-of-order* execution of read & write operations.

One last thing to consider is that this project was developed by a group of four students. We have all been involved since the first day and the work has been distributed such that each member could specialize in certain parts of the designed processor. Once it was time to validate and evaluate the resulting processor as a whole, all members worked together to solve bugs and draw conclusions to the capabilities of the different configurations of the processor.

#### 1.1 Context

The project came about as a continuation of the work being done on the PEAK architecture created by the *Grupo de Arquitecturas Paralelas* (GAP) of the *Departamento de Informática de Sistemas y Computadores* (DISCA) located at the *Universitat*

*Politècnica de València* (UPV). PEAK is a shared memory multicore processor architecture. The objective of PEAK is the use of emulation techniques on FPGA systems for use in investigation and teaching about the design of new multicore processor architectures. PEAK allows multiple variations of an architecture design starting with the definition of the cores and then moving on to changes in the memory hierarchy and the management of resources then finishing by allowing the use of different memory coherence protocols and defining communication protocols for accessing the processor from an external system.

The main purpose of defining and using PEAK is to facilitate the investigation of advanced methods of core & cache memory management in multicore systems. This is under the concept of *capacity computing* which defines the use of partitioned resources (in this case cores and cache memories) of a multicore processor where each partition is assigned to a different application. This partitioning allows the processor to concurrently execute applications using disjoint sets of resources while providing security and privacy between applications through isolation. This means that applications never interact with each other but results in a more efficient use of the resources provided by the chip. In order to provide these characteristics PEAK has defined a set of coherence protocols and routing mechanisms along with the possibility of reconfiguration at the network level inside of the chip, all of which can be modified from the software control layer.

The latest work being done on the PEAK architecture has the objective of creating a processor with 256 cores that exhibits the previously mentioned improvements provided by resource partitioning. This work is part of an agreement between UPV and a Chinese multinational corporation. The project intends to show off the concept of capacity computing with a large number of cores. Additionally the PEAK architecture is being used as the starting point in a European project centered on High Performance Computing (HPC) which will begin in October 2015. In this project the concept of *tile* that is defined by the PEAK architecture will be used such that each *tile* will have specialized cores for different types of tasks while also having different levels of performance and consumption. As an example, the processors defined in the work presented in this document can be used in different tiles and in each of them be configured with a different number of resources (FPU units, ROB size, etc). The goal of the project is to ensure the use of the optimum number of resources in each moment so as to achieve the best performance/resource ratio.

Another important part of the work contained in this document is its relationship with Field Programmable Gate Arrays (FPGAs). By using a programmable board with its accompanying software we were able to use rapid prototyping and behavioural analysis of the digital designs we have implemented so as to quickly and cheaply verify our designs without the need of having to turn to a chip fabrication plant and then physically debug the resulting silicon. This also required us to learn how to use a hardware description language we had not worked with before, which is Verilog. This involved adjusting to thinking in a paradigm where nothing is sequential, everything is a cable and electricity travels at the speed of light so great care must be taken when writing code because essentially it all happens instantly and at the same time.

Finally, the chance to work in a group was a big reason to go ahead with the project because we knew that by combining each of our skills we could finish a more expansive and complete body of work while supporting each other and allowing greater efficiency during it's development.

#### 1.2 Objectives

- The main objective of the work presented in this document is to design and implement the necessary modules that will form an architecture based on that of the MIPS32. The development of the architecture will be with the use of Verilog code and the Xilinx Vivado IDE.

- The processor supports different types of instructions: read/write to memory and registers, arithmetic-logic operations and conditional branches along with jumps.

- Provide rapid reconfiguration of the processor allowing more or less resources to be present in the architecture which could imply for example, providing multiple arithmetic-logic units or by changing the number of Reservation Stations (RS) available to each operational unit.

- Use pipelined designs for the arithmetic-logic and memory units in order to support concurrent execution of instructions and memory disambiguation.

- Develop a range of test programs written in assembly in order to verify the correctness of the final implementation with all the modules interconnected that form the architecture.

- Synthesize the project using Vivado and then perform an analysis of the space that each component of the architecture would occupy on an FPGA. This part will be performed using several different configurations of the processor providing more or less resources and observing the variations in resource usage on the FPGA by the processor.

- Make the adjustments necessary to incorporate the project into the PEAK architecture with the goal to then program the processor onto an FPGA.

#### 1.3 Structure of the Document

This document is made up of seven chapters each of which is briefly introduced below.

- Chapter 1, Introduction: To begin with we explain the motivation and context behind the work produced along with the objectives to complete.

- **Chapter 2, Prior knowledge:** Here we provide the necessary concepts to better understand the implications and mechanics of the work produced.

- Chapter 3, Development tools: In this section we detail the tools used during the project along with the advantages they bring and how they are used.

- Chapter 4, Overview of the processor: Next we describe the set of components required to create a functioning processor along with the tasks they perform and how they are all interconnected.

- Chapter 5, In-depth view of components: Each member of the group was in charge of the development of certain units. Here these specific modules of each member are introduced in greater detail.

- Chapter 6, Verification and results: A series of tests in order to verify the developed project are explained while also analysing the resulting efficiency and resource usage of the final product.

- **Chapter 7, Conclusion:** In this final chapter we detail how each initial objective was completed and also possible work that could be added in the future.

Because the work detailed in this document was performed as a team composed of Francisco Guaita, Mark Holland, Raúl Lozano and Tomás Picornell, each member dedicates sections in this document to a more in-depth look at the implications the units they spent most time working with had on the rest of the architecture.

At the end of the document there is an appendix with the interfaces of the components seen in chapter 5 along with the testbench source code used in chapter 6

#### 1.4 Use of References

During the development of the project we have made use of multiple bibliographic materials which are detailed here along with their relation to the different parts of the project.

To situate ourselves in the historical context of the type of architecture our design is based on, which is that of the MIPS32 microprocessors, we make use of a Wikipedia article [9] where MIPS processors in general are explained.

- Because one of the objectives of this project is to construct a processor with *out-of-order* execution we base ourselves off of the structures defined in the books by Hennessy and Patterson about computer architecture [6, 7]. We also use the official MIPS manual [10] that introduces the MIPS32 architecture.

- In order to correctly decode instructions and execute them on our architecture we follow the encoding defined in the official MIPS manuals that cover the set of instructions supported by the MIPS32 architecture [11, 12].

- Another important factor is correctly following the official standard for floating point numbers set by the IEEE organization [8].

- For some of the more detailed parts of the arithmetic-logic unit implementation the reference [16] is used.

- Finally, to solve questions related to the use of the chosen development tools during the creation of this work we consult the official book on Git [5] where they provide examples of common use cases, the official documentation for the program PCSPIM that contains all the needed information for its usage and to end with the user guide for Vivado [18] made available by Xilinx.

### CHAPTER 2

## Prior Knowledge

This chapter provides an overview of different technical aspects in order to better situate the reader in the context that this project is placed. This includes explanations of the mechanics of some of the components implemented during the development of this project.

#### 2.1 IEEE Standard for Floating-Point Arithmetic

This standard came about because of the usage of different ways of representing floating-point numbers on large computers near the end of the 1970s. From the years 1977 to 1985 a series of meetings were held by the IEEE (Institute of Electrical and Electronics Engineers) resulting in the publishing of the IEEE 754 standard.

The format defined in IEEE 754 is used to perform operations involving real numbers in the float and double representations. The support of these representations depends on the implementation of the floating point unit (FPU). The standard also shows how simple precision (32 bits) and double precision (64 bits) floating point numbers should be represented along with how arithmetic operations should be performed when using these types of numbers.

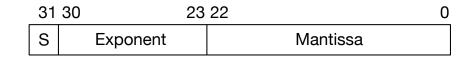

The IEEE 754 format allows the representation of a wide range of very large numbers while using a limited number of bits. For example, a simple precision floating point number occupies a single word of 32 bits and is made up by the fields shown in **Figure 2.1**.

The first bit represents the sign of the number (S), the following 8 bits form the exponent (E) while the remaining 23 bits are the mantissa (M). A number X represented in exponential notation can be written in the form:

$$X = (-1)^S \times 1.M \times 2^{E-127}$$

Figure 2.1: Fields of bits that make up a floating point number with simple precision

#### 2.2 The MIPS Architecture

The MIPS (Microprocessor without Interlocked Pipeline Stages) family of microprocessors developed by MIPS Technologies use a RISC (Reduced Instruction Set Computing) architecture where instructions are expected to only make use of an operator once during the execution of an instruction unlike a CISC (Complex Instruction Set Computing) architecture where the instructions may use the same operating unit multiple times over the course of the execution of a single instruction.

MIPS processors were initially designed at Stanford University in 1981 by a research group lead by Dr. John Henessy with the goal of adopting the principles advocated by the RISC philosphy, pioneered by Henessy, to a working microprocessor. This group later founded the company MIPS Technologies Inc. in 1984 with Henessy as a co-founder. The company's first product was the R2000 model which was the first commercial RISC processor and the first to use the MIPS architecture, it was released in January 1986. The R2000 provided 32 general purpose registers but certain things taken for granted today, such as floating point operations, had to be performed by a separate chip, the R2010 floating-point accelerator. A similar thing ocurred with memory operations where four R2020 write buffer chips were also included on the R2000 chipset to allow the queuing of up to four pending memory operations and thus freeing up the microprocessor to continue executing other instructions.

The follow up to the R2000 was released in 1988 and was called the R3000. The main improvement was the addition of an on-chip cache controller along with support for cache coherence to ensure data consistency. So although this microprocessor didn't yet have any level 1 cache it did support external instruction and data cache with sizes up to 256 KB and allowed access to both caches in the same cycle. The R3000 chipset included 32 KB of cache which was later doubled to 64 KB with the introduction of the R3000A in 1989 that also supported higher clock frequencies.

The first 64-bit instruction set supporting RISC microprocessor came in 1991 with the MIPS R4000 which used a scalar superpipelined architecture and now integrated an on-die floating-point operator. Increases in clock frequency and

attempts for it to replace the CISC microprocessors of the day such as the Intel i486 weren't enough and in 1992 SGI acquired MIPS Technologies Inc.

Under SGI, MIPS Technologies Inc. began to license their designs and by the end of 1999 had consolidated in the MIPS licensing system with the architectures MIPS32 and MIPS64 (referring to 32 and 64 bit architectures). Licensing use was quickly adopted and today these architectures can still be found in all types of embedded systems ranging from portable computers to TV decoders.

The change of ownership allowed heavy investment in new designs and in 1994 the first MIPS superscalar microprocessor was released as the model R8000 which allowed the concurrent execution of two arithmetic-logic operations and two memory operations in a single clock cycle. This was achieved by introducing the concept of pipelined operators with the use of an external floating-point operator called the R8010 which also provided the possibility of *out-of-order* execution of instructions by decoupling the integer and floating-point pipeline of the processor. Unfortunately, the elevated costs limited its use outside of scientific fields and it only managed to stay on the market for little over a year.

The successor to the R8000, the R10000, was released in January 1996 and continued with the idea of *out-of-order* instruction execution by introducing register renaming and a four-way superscalar design that permitted the launching of up to four new instructions from the cache every cycle. Along with a higher clock frequency the R10000 incorporated all the necessary components on a single chip including the floating-point unit (FPU) that consisted of four functional units made up by an adder, a multiplier, divide unit and square root unit.

All of the designs that followed would be derivatives of the R10000 that included small changes to improve clock speeds and instruction throughput, until the R18000 that was cancelled during development and thus ending the R series of MIPS microprocessors.

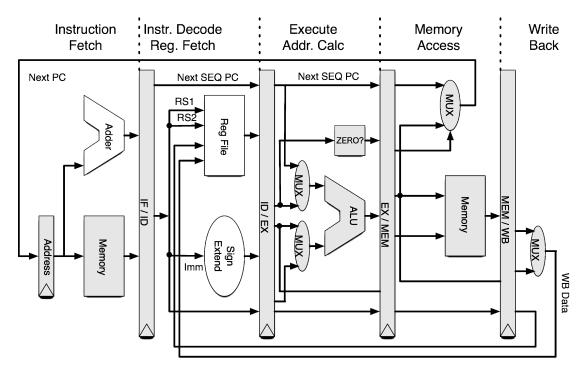

In **Figure 2.2**, we can see the complete data path of a pipelined MIPS microprocessor along with the main operational units and how they are interconnected. **Figure 2.2** also shows the different stages that instructions pass through:

- Instruction Fetch (IF): Fetch the instruction from memory.

- Instruction Decode (ID): Decoding of the instruction and request for the operands from the register bank.

- Execute (EX): In this step the instruction is executed. The actions performed depend on the instruction type. If it is arithmetic then the necessary operation is performed. If it is a memory access then the address is calculated from the base and shift values. If it is a branch instruction then the destination address is calculated relative to the program counter (PC) and if necessary the branch condition is calculated.

- Memory Access (MEM): In this stage the load instructions read from memory while store instructions write their value. Branch instructions update the value in the PC. Arithmetic instructions continue their course towards the next stage.

- Write Back (WB): In the case that the instruction produces a result then it is written to the register indicated by the instruction.

Figure 2.2: Datapath of the MIPS architecture

#### 2.2.1. Instruction Format

The MIPS architecture has three different types of instruction formats:

1. **I-type**: These are immediate operand instructions, it always has a 16-bit integer immediate value encoded in the instruction. Two other operands may be used (rs & rt) stored in registers with index rs and rt. There is also an operation code field that has the binary encoding of the instruction to perform.

| 31        |        |        |                      | 0 |  |

|-----------|--------|--------|----------------------|---|--|

| OpCod (6) | rs (5) | rt (5) | immediate/shift (16) |   |  |

Figure 2.3: I-type instruction format

2. J-type: Used for encoding jump instructions, in order to change the program flow, the amount added (or subtracted in the case of a negative number) to the Program Counter (PC) is provided in the *address* field and uses 26 bits.

| 31        | 0            |

|-----------|--------------|

| OpCod (6) | Address (26) |

Figure 2.4: J-type instruction format

3. **R-type**: This format is similar to the I-type except that all operands come from registers. The three registers to use are encoded in rs,rt & rd. There is also a *function code* field that contains the encoded instruction that indicates the operation to perform.

| 31        |        |        |        |           | 0           |  |

|-----------|--------|--------|--------|-----------|-------------|--|

| OpCod (6) | rs (5) | rt (5) | rd (5) | shamt (5) | FuncCod (6) |  |

Figure 2.5: R-type instruction format

#### 2.3 Instruction Scheduling

Historically, program instructions would be executed sequentially one after the other. If the resources for a following instruction were available the instruction would still have to wait until the previous one had finished. This way of designing a data path meant that while one instruction was being executed, the entire data path would be blocked until the instruction had completely finished. The downside to this is that in each cycle of the processor, an instruction is using only one stage of the data path when the next instruction could be using the stages the previous instruction had already passed through. Dynamic instruction scheduling solves this inefficiency.

With dynamic instruction scheduling the reordering of instructions is permitted along with multiple instructions being in the datapath at the same time. This means that subsequent instructions that don't suffer data dependencies with previous instructions can begin execution before the previous one has even began its operations. This allows a much greater throughput of instructions and vastly improves the performance of microprocessors that incorporate this type of scheduling. The introduction of non-blocking execution is of special interest when cache misses occur that can take many tens of cycles to resolve. With register renaming some data dependencies can be avoided completely allowing initially poorly written data-dependent code to be solved at execution time and be run without any delays.

Now we will explain how the previously mentioned additions provided by dynamic instruction scheduling can be used to avoid blocking the processor datapath with the use of programs using real MIPS assembly instructions.

| div.d | \$f1, \$ | \$f2, \$ | \$f4  | # | \$f0 = \$f2 / \$f4  |

|-------|----------|----------|-------|---|---------------------|

| add.d | \$f10,   | \$f1,    | \$f8  | # | \$f10 = \$f0 + \$f8 |

| sub.d | \$f12,   | \$f8,    | \$f14 | # | \$f12 = \$f8 - \$f4 |

Figure 2.6: Example of a program using MIPS32 insturctions

In the example of **Figure 2.6** we can observe how if we were using static instruction scheduling the sub.d instruction will be delayed because there exists a data dependency between the two previous instructions even though the sub.d instruction doesn't use any of the data involved in the two previous instructions which results in lost cycles while the add.d is waiting to begin. With *out-of-order* execution the sub.d could be placed before the add.d and begin executing. Then, when the div.d finishes, the pushed back add.d can now begin as the dependency is no longer a risk.

To support *out-of-order* instruction execution the instruction decoding stage must be split into two new stages which are:

- 1. **Issue** Performs instruction decoding and detection of hazards that would create a dangerous program structure with unknown consequences.

- 2. **Read operands** Waits for all the operands to be ready with their latest values in order to avoid conflicts leading to incorrect results.

Along with this division, for *out-of-order* execution to make sense, the processor must have available multiple operational units of each type so as to allow the concurrent execution of instructions of the same type that do not have dependencies between them.

With register renaming we can also solve an additional type of dependency called an anti-dependency. An anti-dependency, also known as write-after-read (WAR), happens when an instruction saves its result to a location that is used in a previous instruction so if the later instruction is re-ordered and finishes before the previous instruction then the programs structure has been changed and will provide an incorrect result.

| div.d \$f0, | \$f2, \$f4   | # | \$f0 = \$f2 / \$f4   |

|-------------|--------------|---|----------------------|

| add.d \$f6, | \$f0, \$f8   | # | \$f6 = \$f0 + \$f8   |

| s.d \$f6,   | 0(\$t1)      | # | MEM[0+\$t1] = \$f6   |

| sub.d \$f8, | \$f10, \$f14 | # | \$f8 = \$f10 - \$f14 |

| mul.d \$f6, | \$f10, \$f8  | # | \$f6 = \$f10 * \$f8  |

**Figure 2.7:** Example of a program using MIPS32 instructions that has an anti-dependency data hazard

In the program of **Figure 2.7** there is an anti-dependency between the sub.d and add.d instructions, the later instruction stores its result in \$f8 while the earlier add.d instruction uses that same register as an operand. So if the sub.d were to finish before the add.d through *out-of-order* execution then the add.d would be using incorrect data as an operand. By using register renaming we can remove this anti-dependency by renaming the \$f8 register used in the sub.d instruction to, for example, \$f9 then if the sub.d were to occur before the add.d they no longer share the same register and the dependency has been eliminated.

#### 2.3.1. Tomasulo Algorithm

The most well known and widely used method of dynamic scheduling is the Tomasulo algorithm developed by Robert Tomasulo while working at IBM in 1967. This algorithm introduced the concepts of register renaming and reservation stations along with a common data bus (BUS) to allow all the operational units to register their results in the corresponding reservation station if necessary. To allow *out-of-order* instruction execution, the Tomasulo algorithm makes use of a re-order buffer (ROB) to ensure that even though the calculations of instructions may occur in a dynamic order, instructions must finish and write their result in a new final stage – the commit stage – where the instructions enter this stage in the original order of the source code. Reservation stations are used as an intermediate store for the resulting value of an instruction that is used in a following instruction as an input operand, thus eliminating the delay caused by waiting for the instruction producing the result to have committed its result to a register.

With these new structures, the Tomasulo algorithm completely eliminates writeafter-read (WAR) and write-after-write (WAW) dependencies through register renaming and allows optimum use of the processors resources with the re-order buffer while also reducing delays for the latest operands with reservation stations. The Tomasulo algorithm saw greater use from the 1990s when cache memory was more feasible because of the cost penalty reduction of cache misses that the algorithm provides along with branch speculation that will now be introduced to the reader.

#### 2.3.2. Dynamic Branch Prediction

With the Tomasulo Alogrithm we have seen how different types of data dependencies can be eliminated and thus avoid the hazard of incorrect results in programs run on a processor. But there is a different type of hazard, the so called *control hazard*. Control hazards occur when a program makes use of conditional branch instructions, these instructions allow the control of the program flow. There are two methods that can increase the IPC (instructions per cycle) of branch instructions: static branch prediction which occurs at program compile time and dynamic branch prediction which occurs in the processor while the program is executing. This project uses speculative execution of branches with dynamic branch prediction.

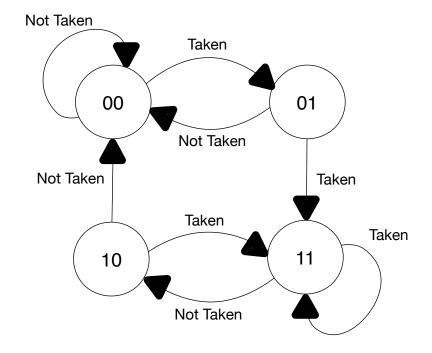

Dynamic branch prediction involves keeping a record of all the conditional branches executed in a program along with a prediction of whether the branch will be *taken* or *not taken* and whether this prediction was correct the last time the branch instruction was executed. The prediction is usually calculated by the use of a deterministic automaton that allows multiple incorrect predictions before it changes its prediction for the following branch instructions.

As soon as a conditional branch instruction is decoded the prediction is made and in the next cycle the instructions that are decoded will be the ones following this prediction. Once the branch instruction has the result of its condition calculated and is then later confirmed, if the prediction was correct then execution can continue as normal and multiple cycles have been saved. But if it turns out that the branch prediction was incorrect then all the instructions after the branch must be cancelled. Thanks to the commit stage of the Tomasulo algorithm, even though incorrect instructions were being executed, data will not be corrupted as no instruction after the branch can enter the commit stage, where results are written, until the branch has entered this stage. At which point the commit stage has discovered the incorrect prediction and launched a *flush* of the incorrect instructions already in execution including their operands and any temporary calculation.

#### 2.3.3. Memory Disambiguation

We have contemplated how to enable *out-of-order* execution of instructions but in the case of memory operations such as reads and stores there is an extra level of complexity involved which is known as memory disambiguation. This more advanced technique is used to detect dependencies between memory operations, the most important of which is what's known as true dependencies. Resolving this type of dependency involves correctly detecting when a load operation has a conflict with a previous store operation.

| addi | \$t0, | \$0, 0    | # | t0 = t0 + 0        |

|------|-------|-----------|---|--------------------|

| add  | \$t0, | \$t0, \$0 | # | t0 = t0 + t0       |

| SW   | \$t1, | 0(\$t0)   | # | MEM[0+\$t0] = \$t1 |

| lw   | \$t2, | 0(\$0)    | # | t2 = MEM[0+\$0]    |

**Figure 2.8:** Example of a program using MIPS32 memory access instructions that has a data hazard

In the example of **Figure 2.8** we can quickly observe that the 1w operation has a conflict with the previous sw operation and must wait until the value in \$t1 has finished being stored in the first memory entry before loading the fresh data into register \$t2. Another important part of memory disambiguation is storing write operations in a buffer so that they may be executed speculatively, this is needed should a conditional branch fail in its prediction and forces all following instructions to be cancelled. By using speculative stores, if a store is cancelled it only will have written to the store buffer and not to the external memory and consequently data correctness is assured and write-after-read and write-after-write dependencies are eliminated.

## CHAPTER 3

## Tools

In this chapter we describe the main tools (external to the project) that were used to help complete the body of work presented in this document, along with what function each of them serves.

#### 3.1 Xilinx Vivado

The most important tool used during the project is a development environment called Vivado provided by the company Xilinx. We choose this particular product provided by Xilinx because the FPGA boards that the architecture will later run on are provided and supported by Xilinx. Vivado is an IDE that provides all the tooling needed to design, implement and integrate a design onto an FPGA.

This provides us with a single program where we can:

- 1. Design the modules that form the architecture by writing Verilog code in the integrated editor.

- 2. Use static analysis for finding syntax errors in the Verilog code and incoherencies in the design.

- 3. Write *testbench* code for each module that creates an instance of the module and then sends valid binary signals to the various inputs of each module in different instances of time. This is later used with the integrated simulator.

- 4. Run the simulation of the design using the previously created testbench modules and then observe the resulting timetable of output and register signals over a period of time in order to verify that each module's implementation is correct and eventually the architecture as a whole.

- 5. Synthesize the design observing statistics related to the cost of different configurations of the architecture as if it were to be implemented on an FPGA.

- 6. Implement the final design on the FPGA.

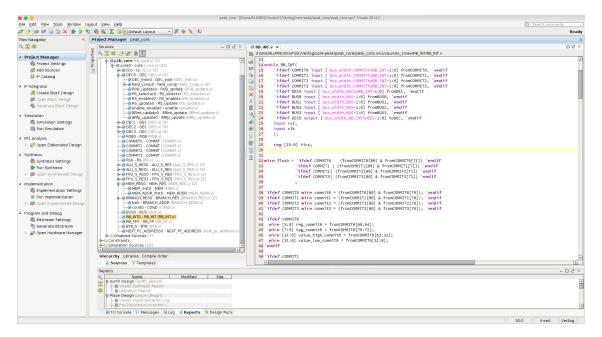

Figure 3.1: Screen capture of the Vivado IDE while editing a module

In **Figure 3.1** we can see how the Vivado IDE is split up into different sections providing an overview of all the modules in the project in a hierarchy that includes the submodules that some modules are made up of and also a text editor for the writing of Verilog code. On the far left we can see all the different steps from design to programming an FPGA, all of which can be carried out using Vivado.

#### 3.2 QtSpim

Spim is a simulator for running MIPS32 programs. Because our architecture is implemented following this instruction set we can use the Spim simulator to test our programs written in assembly and view the correct result. Then when running the same assembly programs on our simulated architecture in Vivado we can compare the results and ensure the architecture is correct. QtSpim is the most recent version of Spim and utilizes the Qt UI framework allowing QtSpim to be cross-platform which means that everyone can use the same program for checking their assembly code.

QtSpim also provides a useful feature as can be seen in **Figure 3.2** in that it displays the encoding of the assembly instructions in hexadecimal. We take advantage of this by having the instruction cache of our architecture directly accept this encoding, which allows us to quickly pass from MIP32 assembly code to hexadecimal values that our architecture can decode and run. These encoded programs are used in *testbench* code in order to verify that the processor works correctly.

| FP Regs            | Int Regs [16] | Data       | Text     |                        |                                                       |   |

|--------------------|---------------|------------|----------|------------------------|-------------------------------------------------------|---|

| FP Regs            | ₽×            | Text       |          |                        |                                                       | 8 |

| FIR = 98           | 00 🔺          | [00400000] | 34020002 | ori \$2, \$0, 2        | ; 3: 1i \$2, 2 # \$2 = 2                              |   |

| FCSR = 0           | 1             | [00400004] | 44821000 | mtc1 \$2, \$f2         | ; 4: mtc1 \$2, \$f2 # \$f2 = 2                        |   |

| FCCR = $0$         |               | [00400008] | 468010a0 | cvt.s.w \$f2, \$f2     | ; 5: cvt.s.v \$f2, \$f2 # \$f2 = 2.0                  |   |

| FEXR = 0           |               | [0040000c] | 34030003 | ori \$3, \$0, 3        | ; 7: li \$3, 3 # \$3 = 3                              |   |

|                    |               | [00400010] | 44831800 | mtc1 \$3, \$f3         | ; 8: mtc1 \$3, \$f3 # \$f3 = 3                        |   |

| Single Preci       | sion          | [00400014] | 468018e0 | cvt.s.w \$f3, \$f3     | ; 9: cvt.s.v \$f3, \$f3 # \$f3 = 3.0                  |   |

| FGO = 0            | sion          | [00400018] | 34040004 | ori \$4, \$0, 4        | ; 11: li \$4, 4 # \$4 = 4                             |   |

| FG1 = 0            |               | [0040001c] | 44842000 | mtc1 \$4, \$f4         | ; 12: mtc1 \$4, \$f4 # \$f4 = 4                       |   |

| FG2 = 40000        | 000           | [00400020] | 46802120 | cvt.s.w \$f4, \$f4     | ; 13: cvt.s.v \$f4, \$f4 # \$f4 = 4.0                 |   |

| FG3 = 40400        |               | [00400024] | 34050002 | ori \$5, \$0, 2        | ; 15: li \$5, 2 # \$5 = 2                             |   |

| FG4 = 40800        | 000 =         | [00400028] | 44852800 | mtc1 \$5, \$f5         | ; 16: mtc1 \$5, \$f5 # \$f5 = 2                       |   |

| FG5 = 4a68b        | f40           | [0040002c] | 46802960 | cvt.s.w \$f5, \$f5     | ; 17: cvt.s.w \$f5, \$f5 # \$f5 = 2.0                 |   |

| G6 = 4a68b         | £44           | [00400030] | 34060003 | ori \$6, \$0, 3        | ; 19: li \$6, 3 # \$6 = 3                             |   |

| G7 = 4a68b         | f48           | [00400034] | 44863000 | mtc1 \$6, \$f6         | ; 20: mtc1 \$6, \$f6 # \$f6 = 3                       |   |

| G8 = 40490         | fdc           | [00400038] | 468031a0 | cvt.s.w \$f6, \$f6     | ; 21: cvt.s.w \$f6, \$f6 # \$f6 = 3.0                 |   |

| G9 = 1faa5         | 30b           | [0040003c] | 34070004 | ori \$7, \$0, 4        | ; 23: li \$7, 4 # \$7 = 4                             |   |

| FG10 = 0           |               | [00400040] | 44873800 | mtc1 \$7, \$f7         | ; 24: mtc1 \$7, \$f7 # \$f7 = 4                       |   |

| FG11 = 0           |               | [00400044] | 468039e0 | cvt.s.w \$f7, \$f7     | ; 25: cvt.s.w \$f7, \$f7 # \$f7 = 4.0                 |   |

| FG12 = 0           |               | [00400048] | 34080000 | ori \$8, \$0, 0        | ; 27: li \$8, 0 # \$8 = 0                             |   |

| G13 = 0            |               | [0040004c] | 44884000 | mtc1 \$8, \$f8         | ; 28: mtc1 \$8, \$f8 # \$f8 = 0                       |   |

| G14 = 0            |               | [00400050] | 46804220 | cvt.s.w \$f8, \$f8     | : 29: cvt.s.v \$f8, \$f8 # \$f8 = 0.0                 |   |

| FG15 = 0           |               | [00400054] | 34090000 | ori \$9, \$0, 0        | ; 31: li \$9, 0 # \$9 = 0                             |   |

| G16 = 0<br>G17 = 0 |               | 1004000581 | 44894800 | mtc1 \$9. \$f9         | : 32: mtc1 \$9, \$f9 # \$f9 = 0                       |   |

| G17 = 0<br>G18 = 0 |               | [0040005c] | 46804a60 | cvt.s.w \$f9, \$f9     | ; 33: cvt.s.v \$f9, \$f9 # \$f9 = 0.0                 |   |

| G10 = 0            |               |            |          | add.s \$f8, \$f8, \$f3 | ; 35: add.s \$f8, \$f8, \$f3 # \$f8 = 3.0             |   |

| $G_{20} = 0$       |               |            |          | mul.s \$f9, \$f5, \$f6 | ; 37: mul.s \$f9, \$f5, \$f6 # \$f9 = 2 * 3           |   |

| $G_{21} = 0$       |               | 1890004000 | 46074a42 | mul.s \$f9, \$f9, \$f7 | ; 38: mul.s \$f9, \$f9, \$f7 # \$f9 = 2 * 3 * 4       |   |

| G22 = 0            |               | [0040006c] | 46092243 | div.s \$f9, \$f4, \$f9 | ; 39: div.s \$f9, \$f4, \$f9 # \$f9 = 4/(2*3*4)       |   |

| $G_{23} = 0$       |               | -          |          | add.s \$f8, \$f8, \$f9 | ; 40: add.s \$f8, \$f8, \$f9 # \$f8 = 3.0 + 4/(2*3*4) | 8 |

| G24 = 0            |               |            |          | add.s \$f5, \$f5, \$f2 | ; 42: add.s \$f5, \$f5, \$f2 # \$f5 +2                |   |

| G25 = 0            |               |            |          | add.s \$f6, \$f6, \$f2 | ; 43: add.s \$f6, \$f6, \$f2 # \$f6 +2                |   |

| G26 = 0            |               | [0040007c] | 460239c0 | add.s \$f7, \$f7, \$f2 | ; 44: add.s \$f7, \$f7, \$f2 # \$f7 +2                |   |

| G27 = 0            |               |            |          | mul.s \$f9, \$f5, \$f6 | ; 46: mul.s \$f9, \$f5, \$f6 # \$f9 = 4 * 5           |   |

| G28 = 0            |               |            |          | mul.s Sf9, Sf9, Sf7    | ; 47: mul.s \$f9, \$f9, \$f7 # \$f9 = 4 * 5 * 6       |   |

| FG29 = 0           | -             |            |          | div.s \$f9, \$f4, \$f9 | ; 48: div.s \$f9, \$f4, \$f9 # \$f9 = 4/(4*5*6)       |   |

|                    |               |            |          |                        |                                                       |   |

Figure 3.2: Example of execution of a program using QtSpim

#### 3.3 Git

The work presented in this document, as has already been mentioned, has been developed in parallel as a team of four people and as such requires a great deal of synchronisation and care when designing and implementing the architecture. For this to be feasible it is necessary to use some kind of version control for the actual files with the code of the project. We choose Git because the team members were already familiar with it and it suits our needs. The University has provided us with a server so that we can have a remote repository accessible from wherever each team member may be working at any particular time.

The workflow used with git can be observed by a snippet of the project in **Figure 3.3** and involved creating new git branches for each new feature or bug fix, thus allowing time for proper code review and verification before incorporating new code into the main development trunk.

```

| | * | | | f8d1991 Finished adding ROB to TOP

| | * | | | e524649 Merge branch 'feature/Add_DEC_to_TOP' into feature/Add_ROB_to_TOP

| | | * | | | 98eb6b2 Add DEC wires to TOP

| | | * | | | d67874d Several wires added

| | * | | | | d67874d Several wires added

| | * | | | | b59c1bb Started adding ROB module to TOP

| * | | | | | 9b4e865 Removed .cache from staging

| * | | | | | d1521db Updated .gitignore

| |/////

* | | | | | 16de20f Verified modules RB, RS, BUS and ROB

| |_1////

```

**Figure 3.3:** A small list of commits in descending order showing how they diverge into a new branch and are later merged

### 3.4 log2timetable

To facilitate faster conclusions from the test programs run on the processor we implement a set of *python* and *bash* scripts that when combined allow a quick overview of the program execution in the form of a timetable. A bash script is used that takes as input the vivado.log file generated by Xilinx Vivado during a simulation run on the architecture. In this input we have specially crafted logged text from the Verilog code that contains the stage each instruction from the reorder buffer is in for each program cycle. The script cleans up this log file and then passes it to a python program that parses our special timetable logs and then prints out a timetable of the execution of each instruction.

This final output allows us to quickly check if the programs were functioning as expected and to detect improvements between configurations. An example of a resulting timetable is in **Figure 3.4** and these outputs will be used extensively in chapter 6. The x-axis shows the time measured in clock cycles. Each row of the table is a instruction and by following the x-axis it can be seen how each instruction passes through the different execution stages and in which cycles.

| instr/cyc]   | 2       | 3   | 4   | 5   | 6   | 7   | 8   | 9   |     |

|--------------|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| addi \$8, §  | \$0, 10 | DEC | ADD | ADD | WBK | COM |     |     |     |

| addi \$9, \$ | \$0, 20 |     | DEC | ADD | ADD | WBK | COM |     |     |

| addi \$10, § | \$0, 30 |     |     | DEC | ADD | ADD | WBK | COM |     |

| addi \$11, § | \$0, 40 |     |     |     | DEC | ADD | ADD | WBK | COM |

Figure 3.4: An example timetable output from log2timetable

## CHAPTER 4

## Overview of the Processor

In this chapter we provide a general overview of the processor created so that the reader may better understand how certain parts of the architecture work.

### 4.1 Datapath

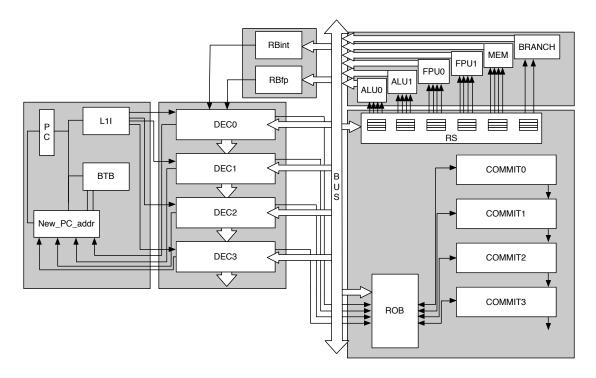

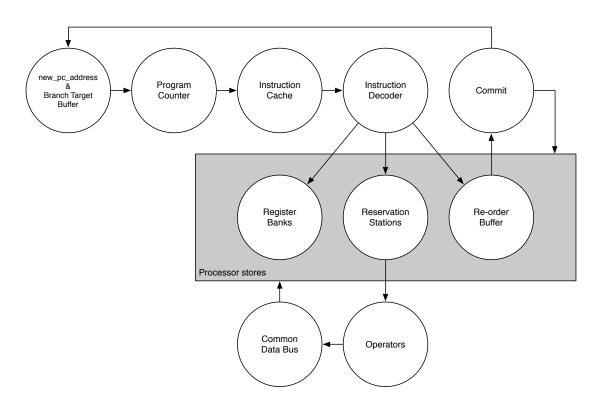

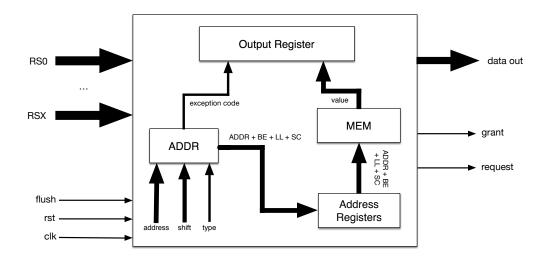

In **Figure 4.1** there is a diagram with a general overview of the processor that has been developed. It is important to note that this diagram does not contain the entirety of the design due to its complexity, as such it only shows the most important modules in order to provide a brief overview while detailing how the units are interconnected. Even so, some less crucial connections are missing in order to provide a cleaner diagram.

In the previously detailed **Figure 4.1**, it can be seen how the datapath is made up of several different groups of modules (remarked in grey boxes). Each group will be detailed in-depth before passing on to the next one.

Starting from the left we will begin by looking at the group made up by:

- Program Counter (PC): This is nothing more than a 32-bit register that holds a pointer to the current program line being executed.

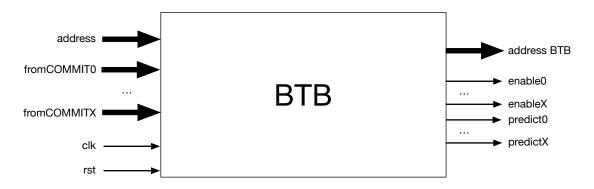

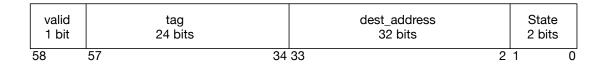

- Branch Target Buffer (BTB): The BTB provides the possibility of predicting the result of conditional branch instructions, that is, whether the branch is taken or not. Internally it contains a register table of configurable size where each entry represents a branch instruction of the program being executed, adding the entry as each branch instruction is first executed. Each branch instruction has an entry in the table that saves the destination address if the branch is taken, the PC of the branch instruction and a set of bits that represent the latest prediction and if it was correct. The prediction is updated by the use of an automaton with four states. If the BTB predicts a branch will

**Figure 4.1:** The general structure of the datapath that forms the processor along with the different operational units

be taken, it also provides the new destination address for the branch along with updating the corresponding entry in the internal table of the BTB.

- **New\_PC\_addr:** This unit takes the address calculated by the BTB and correctly updates the pointer in the PC so that the program flow will continue correctly after the execution of a branch.

- Instruction cache (l1I): This contains the set of MIPS32 instructions represented in hexadecimal that make up the program to be executed by the processor.

Next up in the pipeline we have the set of **instruction decoders (DEC)** the number of which can be configured allowing more or less instructions to enter the pipeline in a single cycle. The decoders are in charge of interpreting the binary code that represents operations on the processor and consequently gives orders to the rest of the modules in the architecture so that the expected operation is performed as indicated by the current instruction being decoded. In order to achieve this, the decoders must be made aware of the data flow in nearly all of the modules that make up the processor so that they can act as *control* units making decisions and giving orders to each module with how they should procede. All control in the processor is centralized in the decoders and as such any performance bottleneck in the processor is usually blamed on the decoders.

The **register banks (RB INT & RB FP)** take on the task of holding data during the execution time of programs on the processor. The register banks provide the input data to operations and a location to store the result of said operations. The architecture has two register banks: one for integer and one for floating point numbers. The integer register bank contains 34 registers (\$0,...,\$33) each of which holds a 32-bit length piece of data. The \$0 register contains a hardwired value of 0 while registers \$32 and \$33 provide LO and HI registers to facilitate operations that have a 64 bit result, such as integer divisions and multiplications. The floating point register bank has 32 registers (\$f0,...,\$f31) and no hardwired 0. It also doesn't include the LO and HI registers that the integer register bank has. A choice was made to provide a simpler architecture design by having all of the registers wired to the decoder. This allows instructions to quickly move from the decoding stage to the execution stage without having to make requests to the register banks.

The next module enables the implementation of Tomasulo's algorithm, this means the pipeline requires a **re-order buffer (ROB)** so that we can make use of the *out-of-order* execution of instructions. The ROB is in charge of storing all the instructions as they are decoded and later executed as a *first in first out* (FIFO) queue so that instructions can't change the state of any data before any instruction that come before have done so first. With this we ensure the correct execution of programs. When an instruction is decoded it is added to the first available entry in the ROB. Once the instruction has finished its execution by receiving the result of the operation from the bus and setting its corresponding *write back* bit in the ROB, it then waits in the ROB until it is the oldest entry at which point it moves on to the commit stage where it saves its result to a register bank or memory. The ROB can support a configurable number of commit stages that allows multiple completed instructions to be committed and removed from the ROB in the same cycle.

Another important module to allow the correct *out-of-order* execution of instructions is the set of **Reservation Stations (RS)**. Each operator has a configurable number of reservation stations assigned to them. A reservation station contains the operands of instructions that are waiting to be executed. If an operand isn't available then the reservation station will store a mark indicating where the operand will come from in order to capture it from the bus when it is made available.

To end with the group of modules that bring support of the Tomasulo algorithm to the processor we have the **commit** module, which, as previously mentioned can be replicated to allow multiple concurrent instructions to pass to the commit stage. This unit has strong ties to the ROB and provides order with what to do with each instruction contained in the ROB and even gives the order to *flush* the ROB which involves removing all of the entries in its table of instructions. A flush occurs when a branch prediction failed (or an exception occurred) and instructions that shouldn't have been executed have started their way through the pipeline and must be cancelled, freeing up the processor for the correct instructions that will come next.

Now that we've got all the modules needed to supply the instructions, decoded them and prepared their operands in the correct reservation stations, provided the mechanisms so that instructions can be executed and committed out-oforder, we next have the operators which provide the results from executing each instruction. To start with we have arguably the most important operators: the Arithmetic-Logic Unit (ALU) that operates with integers and the Floating Point Unit (FPU) for operations using real numbers represented using the IEEE 754 standard. These units follow a combinational logic design but are contained inside a wrapper with a gated output register so as to correctly regulate data flow inside the processor. Following with the high configurability of previously presented modules, the processor can be configured to have multiple instances (up to two of each) of both the ALU and the FPU as can be seen in Figure 4.1. This increases the capacity to have concurrent execution of instructions in the datapath that involve the use of an ALU or FPU. Both the ALU and the FPU are themselves made up of smaller sub modules contained inside the wrapper, some of which are pipelined providing an optimum use of resources. Continuing with configuration capabilities the ALU provides three different types of adder modules that can be easily chosen when configuring the processor. Multiplications and divisions are also contained in their own submodules along with logic and type conversion operators. When it comes to the FPU, great care had to be taken with this more complex unit as there are multiple extra operations to perform before and after the actual calculation takes place. Working with numbers represented in IEEE 754 requires checks on the operands before their usage to ensure compatibility for the operation, and if not, perform the corresponding conversions to make compatible operands available. After the calculation has been performed if any of the operands have been converted then the result may need a final conversion before sending the result to the common data bus (BUS).

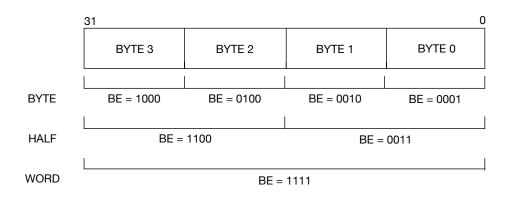

Moving on to a different type of operator, we have the **memory unit (MEM)** which allows for the execution of more complicated programs that process large amounts of data, some of which we will see in chapter 6. The memory unit in the processor of this project has 1024 entries each of which stores a 32 bit wide datum. The MEM is pipelined in two separate stages: first the address calculation stage and second the memory operation. By pipelining the MEM we can bring forward the address calculation of an instruction whose data to store won't be available until an unknown number of cycles later. This delay could be caused by data dependencies between the instructions of the program. Seperating the address calculation and memory operation will reduce the memory operation. The memory operator supports three types of read/write operations which are *byte, half* and *word*. The type is used when calculating the address so as to ensure that the result is valid for the memory operation type. In the case of an invalid address being calculated, an exception is raised, sent to the common data bus

(BUS) and the memory operation is cancelled. The MEM (like the ALU and FPU) is contained in a wrapper with a gated output register. Inside this wrapper there is extensive logic that provides support for memory disambiguation that allows safe *out-of-order* execution of stores and reads.

The last operator to introduce is the **branch** operator that enables the processor to execute programs with complicated data flow sequences. The processor in this document supports speculative execution which allows instructions after a branch to be issued before the branch has been confirmed. The operation performed by this module is nothing more than a small calculation that provides a logical result indicating whether the branch should be taken or not.

The last piece to the pipeline has been mentioned multiple times when introducing the rest of the modules and that is the common data bus (BUS). The BUS is in charge of managing all the results of the different operators and sending them to the next stage with the use of a round-robin algorithm. The number of instances of the BUS can be configured providing a greater throughput of data leaving the operators.

### 4.2 Dataflow

Now that we've seen an overview of the different modules that make the processor, we will move on to an example of the dataflow that occurs while the processor is in execution.

Everything begins at the instruction cache (l1I) because this is where the program that we want to run is stored as MIPS32 instructions in hexadecimal representation. The next stage is to decode an instruction which will be the one situated in the cache at the address given by the PC register, which has the data calculated by the New\_PC\_address module. This module calculates the address of the instruction in the cache to be executed in the following cycle.

The instruction is sent to the instruction decoder (DEC) which checks the different fields of the instruction and decides what resources will be required and also what operands need to be transmitted to the different operators that might be involved in this particular instruction. The decoder also adds a new entry to the re-order buffer (ROB) and sends the available operands to a reservation station so that *out-of-order* execution will be correctly supported.

Once all the operands are ready in the reservation station, the dataflow moves onto the operator for the instruction being executed. When it finishes calculating, the result this is sent to the common data bus (BUS) so that the rest of the modules can check to see if they were waiting for this result to be available.

Finally, now that the instruction has completed all of its operations and provided a result, it moves on to the commit stage; releasing its entry in the ROB and writing the operation result in one of the register banks or the memory unit.

In **Figure 4.2** we can see a brief overview of how data flows from left-to-right and top-to-bottom between the modules as an instruction is executed. Missing from the diagram are the connections from the common data bus to the modules so that they may retrieve the data they are waiting for.

### 4.3 Processor Configurations

Previously, we have seen that multiple parts of the processor datapath can be configured to add modules and increase the complexity of these modules. The technique we use to achieve this is by using preprocessor macros so that different sections of our code are conditionally compiled. All the possible configurations are available in our code, we just hide parts of it by using the macros: 'ifdef x and 'endif where x will have to be added to a global header file for the project if we want that section of the code to be compiled. This is accomplished with the 'define macro. An example of macro usage in the source code can be found in the listing 4.1 along with the corresponding entry in the global header file so that the display sentence will be compiled.

```

// Ths is in the source code

'ifdef codeBlockA

$display("code block A is executed");

'endif

```

```

// This is in the header file

'define codeBlockA

```

Listing 4.1: Macro usage example

Finally, in listing 4.2 there is an example of how the processor is configured by using macros. The example represents the simplest of the configurations that will be seen in chapter 6.

|   | <pre>'ifdef CORE_1way_1op_1rs</pre> |    |                           |        |

|---|-------------------------------------|----|---------------------------|--------|

| ĺ | 'define DEC0                        |    |                           |        |

|   | 'define num_ROB_entries             | 16 | // Number of ROB entries  |        |

|   | 'define log_num_ROB_entries         | 4  | // log of number of ROB e | ntries |

|   | 'define BUS0                        |    |                           |        |

|   | 'define COMMIT0                     |    |                           |        |

|   | 'define RB_INT                      |    |                           |        |

|   | 'define RB_FP                       |    |                           |        |

|   | 'define ALU0                        |    |                           |        |

|   | 'define ALU0_RS0                    |    |                           |        |

|   | 'define FPU0                        |    |                           |        |

|   | 'define FPU0_RS0                    |    |                           |        |

|   | 'define FPU                         |    |                           |        |

|   | 'define ALU                         |    |                           |        |

|   | 'define FPU_RS0                     |    |                           |        |

|   | 'define ALU_RS0                     |    |                           |        |

|   | 'define CLA_level2_2stages          |    |                           |        |

|   | 'define MEM0                        |    |                           |        |

|   | 'define MEM0_RS0                    |    |                           |        |

|   | 'define BRANCH0                     |    |                           |        |

| ĺ | 'define BRANCH0_RS0                 |    |                           |        |

| ĺ | 'endif                              |    |                           |        |

| l |                                     |    |                           |        |

Listing 4.2: Processor configuration using macros

### CHAPTER 5

## Specific Components

This chapter contains a detailed look at the modules that the author spent most time working with and consequently is the most capable to provide an indepth look at the inner workings of each of these units of the processor. A diagram showing all the inputs and outputs for each module will be shown along with a description of why the module is included in the architecture and how it delivers on its requirements.

### 5.1 32-bit Register Bank

Microprocessors were created to fulfill the wish of automating lengthy calculations. All calculations work with data, the type of data may vary but all operations will use some data as an input to a calculation which will then produce a new piece of data, the result. Now you could design a computer where every piece of data has to be provided by human interaction as it is needed by the processor but a much more powerful solution is to allow the processor to store and retrieve enough data so as not to require any interaction while it performs its operations. This capability to store and retrieve data can be achieved by using components that are implemented using different types of storage technology. Each of these technologies will have different speeds at which they can manipulate data but they will also have a trade-off in that faster storage will generally have a higher monetary cost. The balancing act between speed and cost leads to the so called *memory hierarchy* where different components using different storage technologies are connected in a top-down fashion with the fastest at the top. It only makes sense to use the fastest available storage mechanism when directly providing data to the internal units of the processor. This function is performed by a register bank. The register bank will be tightly coupled and contained in the datapath of the processor and will retrieve and store data in a single cycle. The architecture designed in this project has two register banks so as to support

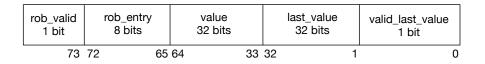

| rob_valid | rob_entry | value   | last_value | valid_last_value |

|-----------|-----------|---------|------------|------------------|

| 1 bit     | 8 bits    | 32 bits | 32 bits    | 1 bit            |

| 73        | 72 65     | 64 33   | 32 1       |                  |

Figure 5.1: The fields that a register contains

two types of data, integer numbers and real numbers in IEEE 754 floating point representation.

Internally, each register is made up of 74 bits and contains multiple fields that can be seen in **Figure 5.1**. The rob\_entry and rob\_valid fields represent whether this register is currently associated with an instruction in the re-order buffer (ROB). This will be used in order to know whether data on the common data bus (BUS) corresponds to this register and should be retrieved. The value field will contain the 32-bit value of the register while the *last\_value field* is used to store the result that will be written to the register by the latest instruction that reserved it. That instruction has reached the *writeback* (WB) stage but it has not committed yet. The usage of the *last\_value* field provides support for *register renaming* and *speculation* without requiring to access the ROB to retrieve the last confirmed but not consolidated value of a register.

Figure 5.2: The connections to the RB unit

In **Figure 5.2** we can see the different inputs and outputs that both register banks utilize. The register banks are two separate modules and as such it is possible to configure the processor to have both register banks or one or the other. The register banks are synchronous modules so will require the global clock signal of the processor along with a reset signal which will trigger the erasing of all the stored data. The current design of the architecture has a trade off which is that because the instruction decoder is not pipelined it is necessary to provide the data in the register bank in an asynchronous way solely to the decoder so that the rest of the pipeline will remain in sync when decoding instructions. This is achieved by having two very large buses on each bank that lead to and from the instruction decoder and carries the entire contents of the register banks so that instructions can be decoded in a single cycle. This connection also allows the decoder to update the associated entries of the re-order buffer (ROB) to the registers that will be used by each instruction. Updates to the values in the register banks are all carried out in a synchronous manner. The banks retrieve values from the common data bus (BUS) when the re-order buffer (ROB) entry of the data on the BUS coincides with that of the rob\_entry field of a register in either bank. This value is assigned to the last\_value field of the register rather than the value field. It isn't until a signal comes from a commit module indicating that an instruction has been confirmed that the respective register will have the definitive value in its value field copied.

We have seen an example of how the register banks function; data is retrieved from the bus, the final value of the data will come from the commit module once the instruction has been cofirmed. But it is important to note that following with the general idea of the project which is to provide a configurable processor, the register banks can be configured to support a variable number of buses and also commit modules. This means that in a single cycle either register bank can store the temporary or final value for multiple registers.

The increased complexity of allowing multiple buses and commit modules in the architecture also introduces some new edge cases that must be correctly treated. The first of which occurs when there are multiple instructions in the confirm phase and they are sending their final values to one of the register banks. But what if it turns out the destination register of more than one of those instructions coincides. The decision of which commit module to listen to is actually quite simple. Each commit module has an instance ID associated and this is tied to the instruction decoders that also have instance IDs, this means that the instructions will be confirmed by different commits but in order of decodification. So if we ensure that we always take the value from the highest instance ID commit module when multiple commits want to store to the same value we will have the most recently decoded instruction and in consequence the most recently updated value.

Another case is when an update to the latest value field of a register comes from the bus but at the same time the instruction decoder is changing the associated re-order buffer entry for this same register. In this case the DEC has priority and will write the new ROB entry but the register bank must also invalidate its latest value field.

The last case is when a *flush* is being performed on the register bank in order to erase all of its unconfirmed values but a new value is ready to be retrieved from the BUS. In this case the value coming from the BUS is ignored and the flush is performed as normal.