### Universitat Politècnica de València

Ph.D. Thesis

# Cache Architectures Based on Heterogeneous Technologies to deal with Manufacturing Errors

Author: Vicente Jesús Lorente Garcés Advisors: Prof. Salvador V. Petit Martí Prof. Julio Sahuquillo Borrás

A thesis submitted in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy (Computer Engineering)

> > $in \ the$

Parallel Architectures Group Department of Computer Engineering

November 2015

## Doctoral Committee

- Prof. María Engracia Gómez Requena

Universitat Politècnica de València, Valencia, Spain.

- Prof. Manuel Eugenio Acacio Sánchez Universidad de Murcia, Murcia, Spain.

- Prof. Manuel Pérez Malumbres

Universidad Miguel Hernández, Elche, Spain.

## Agraiments

Durant la realització d'aquesta tesi he passat per períodes difícils en els quals he trobat el recolzament incondicional dels meus directors, Julio i Salva. A ells els vull agrair la seua paciència i comprensió durant aquests anys, però sobretot els ànims que m'han donat per a que continuara endavant amb aquest projecte.

També estic molt agraït a Alex, amb el que he col·laborat en diferents articles. A més a més m'ha oferit sempre la seua ajuda donant-me una resposta ràpida a qualsevol dubte que li he plantejat.

Moltes gràcies als tres!

# Contents

| 1.1       Current cache design and motivation       2         1.2       RAM technologies       2         1.3       Manufacturing imperfections       4         1.4       Working under the threshold voltage       5         1.5       Objectives of the thesis       6         1.6       Contributions of the thesis       6         1.7       Thesis outline       7         2       Related work       9         2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16                                                                                                                                                                                                                                                                                          | Li | st of        | Figures                             | xi   |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------|-------------------------------------|------|--|--|

| Resumen       xvii         Resum       xix         1 Introduction       1         1.1 Current cache design and motivation       2         1.2 RAM technologies       2         1.3 Manufacturing imperfections       4         1.4 Working under the threshold voltage       5         1.5 Objectives of the thesis       6         1.6 Contributions of the thesis       6         1.7 Thesis outline       7         2 Related work       9         2.1 Leakage reduction in SRAM caches       10         2.2 Fault-tolerant caches       10         2.2 Fault-tolerant caches       13         3.1 General view of the simulation environment       14         3.2 HSPICE       15         3.3 CACTI       15         3.4 SimpleScalar       16         3.5 Workload       16         4 Heterogeneous Caches       19         4.1 Macrocell-based caches (M-Caches)       20         4.1.1 Macrocell-internals       20         4.1.2 Accessing the M-Cache       23         4.2 Timing and area details       25         4.2.1 Retention time       25         4.2.2 Access time       26                                           | Li | st of        | Tables                              | ciii |  |  |

| Resum       xix         1 Introduction       1         1.1 Current cache design and motivation       2         1.2 RAM technologies       2         1.3 Manufacturing imperfections       2         1.4 Working under the threshold voltage       5         1.5 Objectives of the thesis       6         1.6 Contributions of the thesis       6         1.7 Thesis outline       7         2 Related work       9         2.1 Leakage reduction in SRAM caches       10         2.2 Fault-tolerant caches       11         3 Experimental Framework       13         3.1 General view of the simulation environment       14         3.2 HSPICE       15         3.3 CACTI       15         3.4 SimpleScalar       16         3.5 Workload       16         4 Heterogeneous Caches       19         4.1 Macrocell-based caches (M-Caches)       20         4.1.1 Macrocell internals       20         4.1.2 Accessing the M-Cache       23         4.2 Timing and area details       25         4.2.1 Retention time       25         4.2.2 Access time       26                                                                       | A  | bstra        | .ct                                 | xv   |  |  |

| 1       Introduction       1         1.1       Current cache design and motivation       2         1.2       RAM technologies       2         1.3       Manufacturing imperfections       4         1.4       Working under the threshold voltage       5         1.5       Objectives of the thesis       6         1.6       Contributions of the thesis       6         1.7       Thesis outline       7         2       Related work       9         2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         <                                             | R  | esum         | .en x                               | vii  |  |  |

| 1.1       Current cache design and motivation       2         1.2       RAM technologies       2         1.3       Manufacturing imperfections       4         1.4       Working under the threshold voltage       5         1.5       Objectives of the thesis       6         1.6       Contributions of the thesis       6         1.7       Thesis outline       7         2       Related work       9         2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25                             | R  | e <b>sum</b> | ,                                   | cix  |  |  |

| 1.2       RAM technologies       2         1.3       Manufacturing imperfections       4         1.4       Working under the threshold voltage       5         1.5       Objectives of the thesis       6         1.6       Contributions of the thesis       6         1.7       Thesis outline       7         2       Related work       9         2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                  | 1  | Intr         | oduction                            | 1    |  |  |

| 1.2       RAM technologies       2         1.3       Manufacturing imperfections       4         1.4       Working under the threshold voltage       5         1.5       Objectives of the thesis       6         1.6       Contributions of the thesis       6         1.7       Thesis outline       7         2       Related work       9         2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                  |    | 1.1          | Current cache design and motivation | 2    |  |  |

| 1.3       Manufacturing imperfections       4         1.4       Working under the threshold voltage       5         1.5       Objectives of the thesis       6         1.6       Contributions of the thesis       6         1.7       Thesis outline       7         2       Related work       9         2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26 <td></td> <td>1.2</td> <td></td> <td></td> |    | 1.2          |                                     |      |  |  |

| 1.4       Working under the threshold voltage       5         1.5       Objectives of the thesis       6         1.6       Contributions of the thesis       6         1.7       Thesis outline       7         2       Related work       9         2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell internals       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                |    |              | 0                                   |      |  |  |

| 1.5       Objectives of the thesis       6         1.6       Contributions of the thesis       6         1.7       Thesis outline       7         2       Related work       9         2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell internals       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                              |    |              |                                     |      |  |  |

| 1.6       Contributions of the thesis       6         1.7       Thesis outline       7         2       Related work       9         2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       10         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                    |    |              |                                     |      |  |  |

| 1.7 Thesis outline       7         2 Related work       9         2.1 Leakage reduction in SRAM caches       10         2.2 Fault-tolerant caches       10         3 Experimental Framework       13         3.1 General view of the simulation environment       14         3.2 HSPICE       15         3.3 CACTI       15         3.4 SimpleScalar       16         3.5 Workload       16         4 Heterogeneous Caches       19         4.1 Macrocell-based caches (M-Caches)       20         4.1.1 Macrocell internals       20         4.1.2 Accessing the M-Cache       23         4.2 Timing and area details       25         4.2.1 Retention time       25         4.2.2 Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                |    |              |                                     |      |  |  |

| 2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                        |    | 1.7          |                                     |      |  |  |

| 2.1       Leakage reduction in SRAM caches       10         2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                        | 2  | Belated work |                                     |      |  |  |

| 2.2       Fault-tolerant caches       11         3       Experimental Framework       13         3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -  |              |                                     | -    |  |  |

| 3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |              |                                     |      |  |  |

| 3.1       General view of the simulation environment       14         3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3  | Evr          | perimental Framework                | 13   |  |  |

| 3.2       HSPICE       15         3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Č  |              |                                     |      |  |  |

| 3.3       CACTI       15         3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |              |                                     |      |  |  |

| 3.4       SimpleScalar       16         3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |              |                                     |      |  |  |

| 3.5       Workload       16         4       Heterogeneous Caches       19         4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |              |                                     |      |  |  |

| 4.1Macrocell-based caches (M-Caches)204.1.1Macrocell internals204.1.2Accessing the M-Cache234.2Timing and area details254.2.1Retention time254.2.2Access time26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | -            | *                                   |      |  |  |

| 4.1       Macrocell-based caches (M-Caches)       20         4.1.1       Macrocell internals       20         4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4  | Het          | erogeneous Caches                   | 19   |  |  |

| 4.1.1Macrocell internals204.1.2Accessing the M-Cache234.2Timing and area details254.2.1Retention time254.2.2Access time26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |              | 0                                   | 20   |  |  |

| 4.1.2       Accessing the M-Cache       23         4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |              |                                     |      |  |  |

| 4.2       Timing and area details       25         4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |              |                                     |      |  |  |

| 4.2.1       Retention time       25         4.2.2       Access time       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 42           |                                     |      |  |  |

| 4.2.2 Access time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |              |                                     |      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |              |                                     |      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |              |                                     |      |  |  |

| 4.3 Experimental evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 4.3          |                                     |      |  |  |

|   |                   | 4.3.1   | Performance analysis varying capacitance & processor frequency . | 28       |

|---|-------------------|---------|------------------------------------------------------------------|----------|

|   |                   | 4.3.2   | Energy distribution analysis                                     | 31       |

|   |                   | 4.3.3   | Impact of capacitance & processor frequency on energy            | . 34     |

|   |                   | 4.3.4   | Trade-off between energy consumption and performance             | 35       |

|   | 4.4               | Imple   | mentation constraints and alternative implementation             | . 37     |

|   | 4.5               |         | 1ary                                                             |          |

| 5 | Fou               | lt Tole | erant Heterogeneous Caches                                       | 39       |

| 9 | <b>rau</b><br>5.1 |         | ation                                                            |          |

|   | 5.1               |         | based HER cache                                                  |          |

|   | 0.2               |         |                                                                  |          |

|   |                   | 5.2.1   | High-performance mode                                            |          |

|   |                   | 5.2.2   | Design issues: manufacturability and low voltages                |          |

|   |                   | 5.2.3   | Low-power working behavior                                       |          |

|   |                   |         | 5.2.3.1 Read hit in the SRAM way                                 |          |

|   |                   |         | 5.2.3.2 Write hit in the SRAM way $\dots$                        |          |

|   |                   |         | 5.2.3.3 Read/Write hit in an eDRAM way                           |          |

|   |                   |         | 5.2.3.4 Cache miss                                               |          |

|   |                   | 5.2.4   | Mode changes                                                     |          |

|   | 5.3               |         | g details                                                        |          |

|   | 5.4               | · ·     | imental results                                                  |          |

|   |                   | 5.4.1   |                                                                  |          |

|   |                   |         | 5.4.1.1 Performance and retention time analysis                  |          |

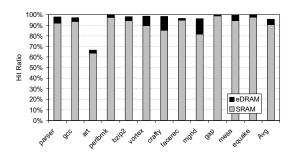

|   |                   |         | 5.4.1.2 Hit rate evaluation                                      |          |

|   |                   | 5.4.2   | Power and energy consumption                                     |          |

|   |                   | 5.4.3   | Area                                                             | 55       |

|   | 5.5               | Summ    | nary                                                             | 57       |

| 6 | Tra               | de-offs | between SRAM Failures and Operation Modes                        | 59       |

|   | 6.1               | Backg   | round on SRAM cell failures                                      | 60       |

|   |                   | 6.1.1   | Hold failure                                                     | 61       |

|   |                   | 6.1.2   | Read failure                                                     | 61       |

|   |                   | 6.1.3   | Write failure                                                    | 61       |

|   |                   | 6.1.4   | Access failure                                                   | 62       |

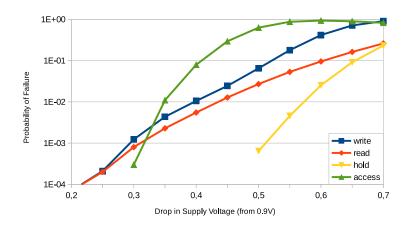

|   | 6.2               | SRAM    | I cell failure characterization                                  | 62       |

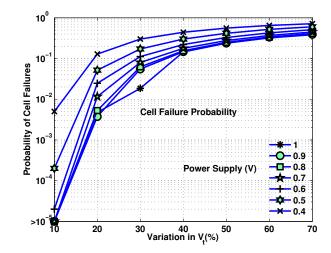

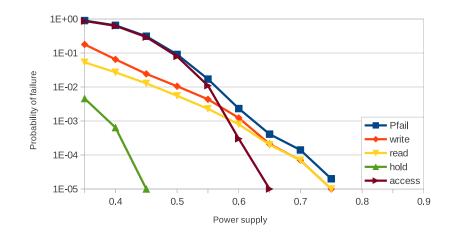

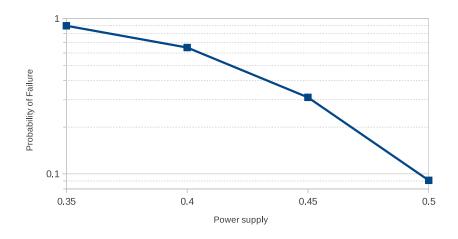

|   |                   | 6.2.1   | Impact of the power supply on the failure probabilities          | 63       |

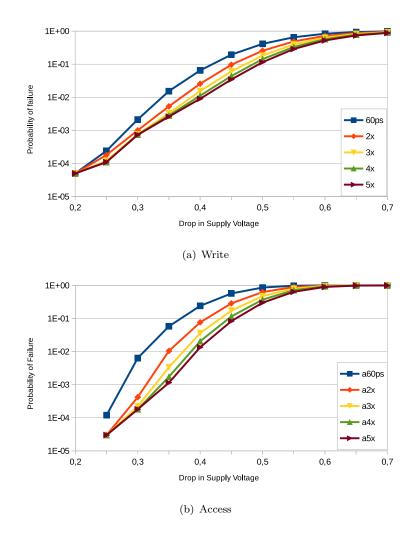

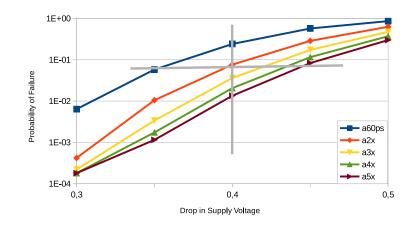

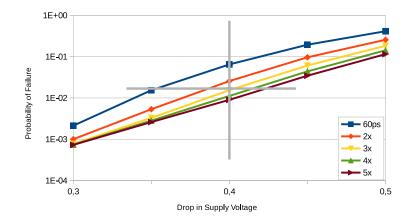

|   |                   | 6.2.2   | Impact of the WL pulse length on write and access failures       | 63       |

|   | 6.3               | Optim   | nal voltage/frequency pairs in fault-tolerant                    |          |

|   |                   | •       | 5                                                                | 66       |

|   |                   | 6.3.1   | Operation modes                                                  | 67       |

|   |                   | 6.3.2   | Experimental evaluation                                          | 68       |

|   |                   |         | 6.3.2.1 Performance                                              |          |

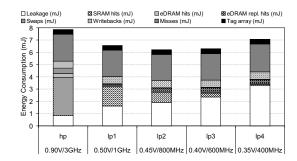

|   |                   |         | 6.3.2.2 Energy Consumption                                       |          |

|   | 6.4               | Summ    | nary                                                             |          |

|   | C                 | 1*      |                                                                  |          |

| 7 |                   | iclusio |                                                                  | 75<br>76 |

|   | 7.1               |         | ibutions                                                         |          |

|   | 7.2               | Future  | e Directions                                                     | . 77     |

| 7.3    | Publications | 77 |

|--------|--------------|----|

| Refere | nces         | 79 |

# List of Figures

| 1.1  | 6T SRAM cell                                                                                                                    | 3  |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | 1T-1C DRAM cell                                                                                                                 | 3  |

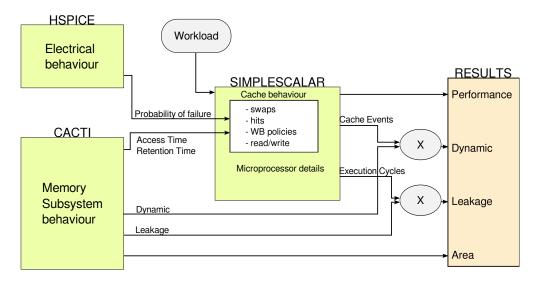

| 3.1  | Block diagram of the simulation environment                                                                                     | 14 |

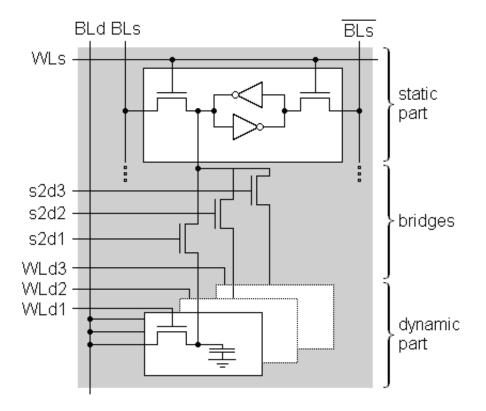

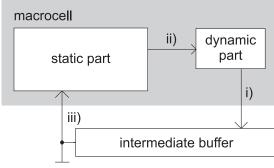

| 4.1  | 4-bit macrocell block diagram                                                                                                   | 20 |

| 4.2  | Swap operation block diagram                                                                                                    | 21 |

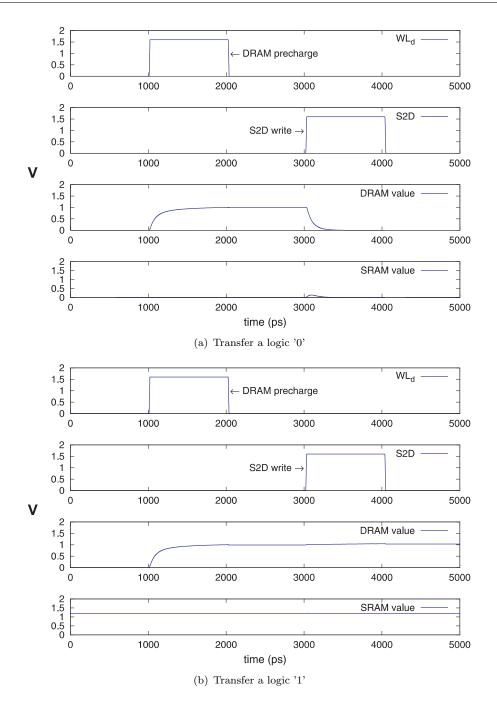

| 4.3  | Operation detail of the internal transfer                                                                                       | 22 |

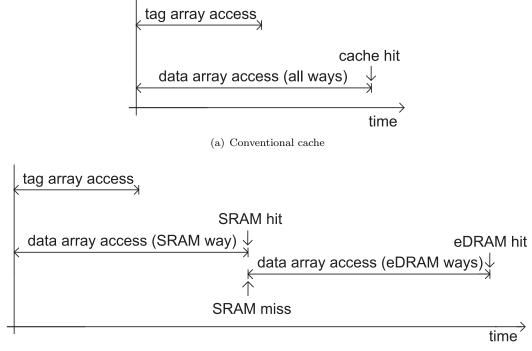

| 4.4  | Tag and data arrays access timing diagram                                                                                       | 23 |

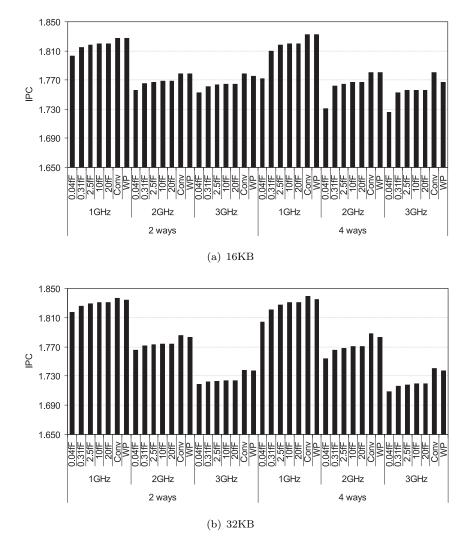

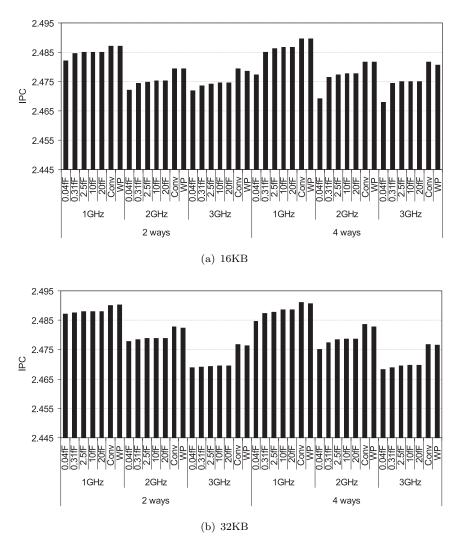

| 4.5  | Performance varying the eDRAM capacitance and processor frequency<br>for the analyzed cache schemes (Integer benchmarks)        | 29 |

| 4.6  | Performance varying the eDRAM capacitance and processor frequency                                                               |    |

|      | for the analyzed cache schemes (Floating Point benchmarks)                                                                      | 30 |

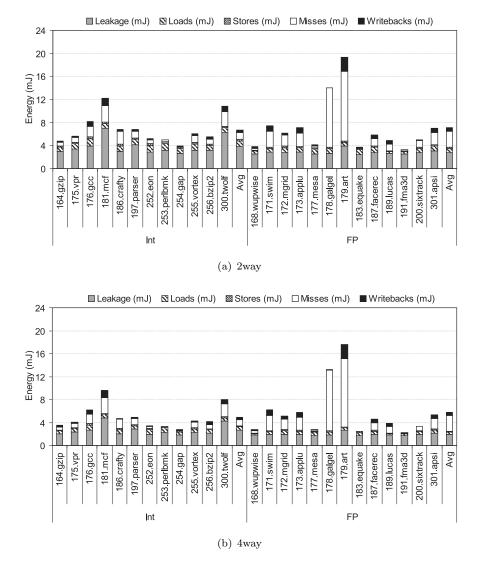

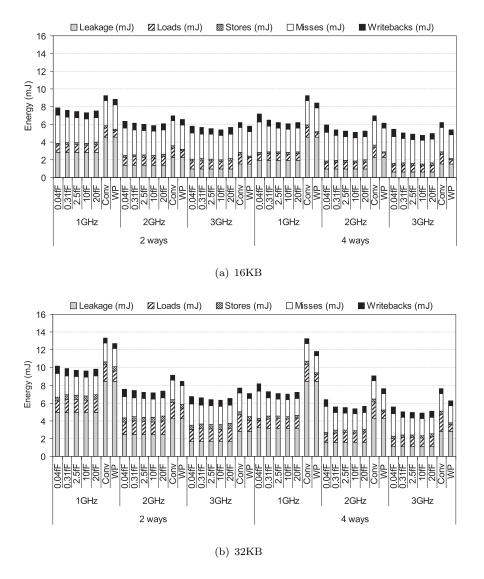

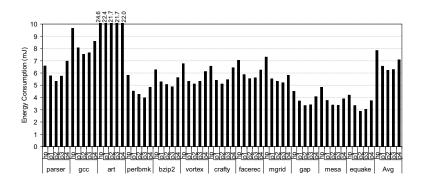

| 4.7  | M-Cache energy consumption (mJ) per benchmark. 16KB                                                                             | 31 |

| 4.8  | M-Cache energy consumption (mJ) per benchmark. 32KB                                                                             | 32 |

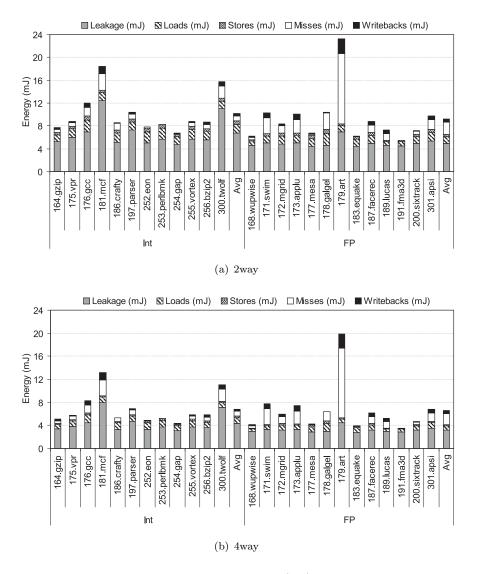

| 4.9  | Energy consumption (mJ) varying the capacitance and the frequency for the analyzed cache schemes. Integer benchmarks.           | 33 |

| 4.10 | Energy consumption (mJ) varying the capacitance and the frequency for<br>the analyzed cache schemes. Floating Point benchmarks. | 34 |

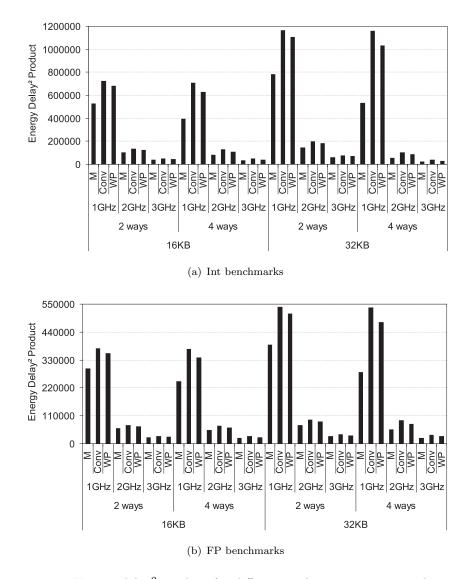

| 4.11 | Energy delay <sup>2</sup> product for different cache organizations and processor frequencies                                   | 36 |

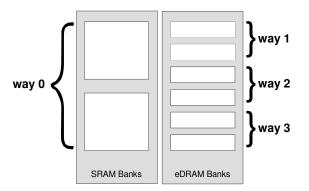

| 4.12 | Alternative heterogeneous cache implementation using independent banks instead of macrocells                                    | 37 |

| 5.1  | Probability of cell failures varying the power supply and the variation in Vt                                                   | 41 |

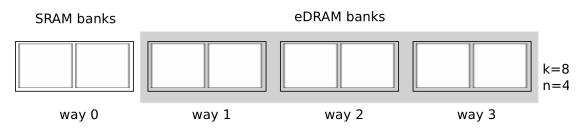

| 5.2  | Block diagram of a 4-way HER cache architecture implemented with 8 banks                                                        | 42 |

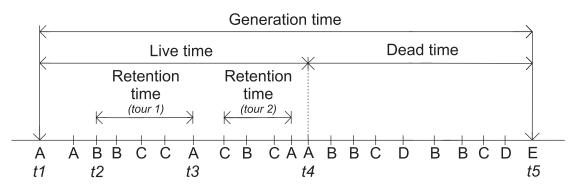

| 5.3  | Generation time of block A (blocks A, B, C, D, and E map to the same set of 4 ways)                                             | 43 |

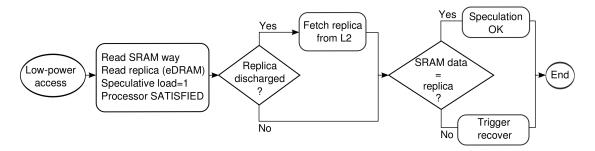

| 5.4  | State diagram and actions carried out by the cache controller on a read                                                         | 10 |

|      | hit in the SRAM way                                                                                                             | 46 |

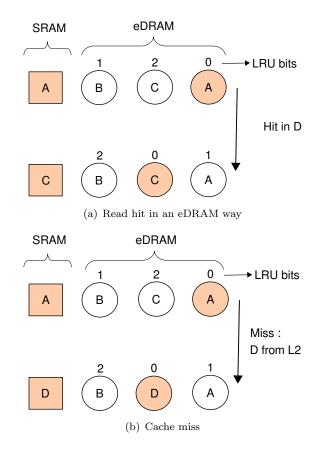

| 5.5  | Example of accesses in low-power mode                                                                                           | 47 |

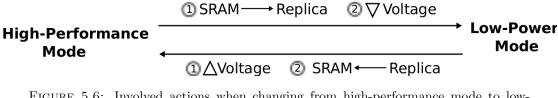

| 5.6  | Involved actions when changing from high-performance mode to low-                                                               |    |

|      | power and vice versa (the number in the action establish the order in which they will be performed)                             | 48 |

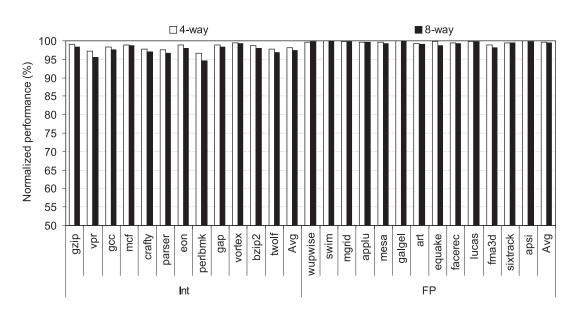

| 5.7  | Normalized performance (%) of the HER cache with respect to the Conv                                                            |    |

|      | cache in $hp$ mode                                                                                                              | 50 |

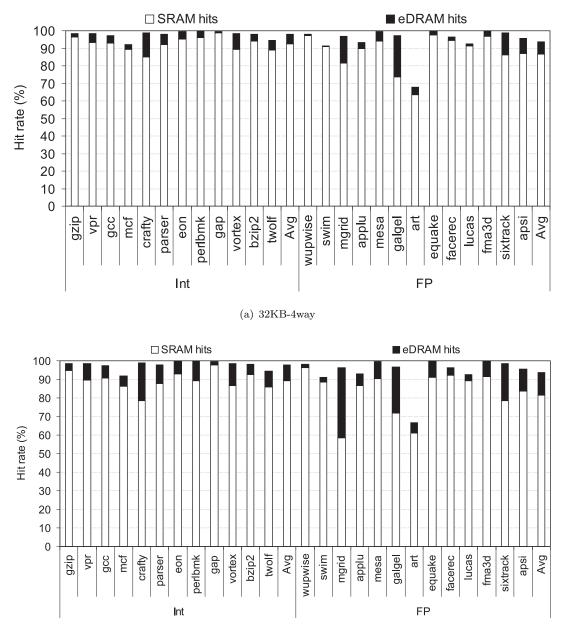

| 5.8  | Hit rate (%) split into SRAM and eDRAM hits per benchmark for the HER cache in $hp$ mode                                        | 52 |

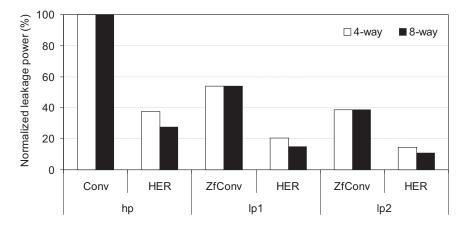

| 5.9  | Normalized leakage power (%) of the HER cache scheme with respect to    |    |

|------|-------------------------------------------------------------------------|----|

|      | the Conv cache                                                          | 54 |

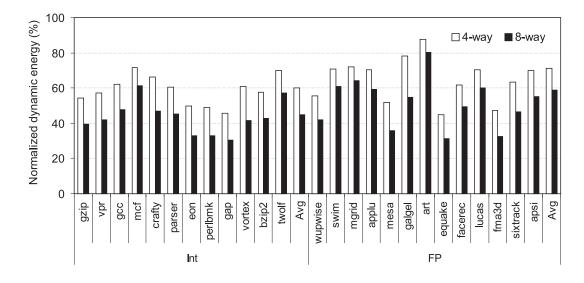

| 5.10 | Normalized dynamic energy (%) of the HER cache with respect to the      |    |

|      | Conv cache in $hp$ mode $\ldots$                                        | 55 |

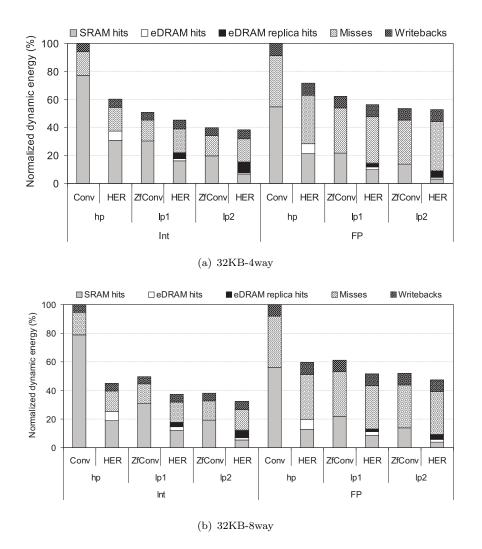

| 5.11 | Normalized dynamic energy categorized with respect to the Conv cache .  | 56 |

| C 1  | CT CD AMII J-t-I-                                                       | 60 |

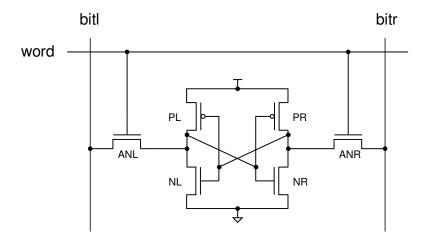

| 6.1  | 6T SRAM cell details                                                    | 00 |

| 6.2  | Breakdown of SRAM cell failure probabilities for a 32nm technology node |    |

|      | reducing the power supply from 0.9V                                     | 63 |

| 6.3  | Probability of write and access failures varying the WL pulse           | 64 |

| 6.4  | Probability of access failure                                           | 65 |

| 6.5  | Probability of write failure                                            | 65 |

| 6.6  | Overall SRAM cell failure probabilities for a 32nm technology node      | 67 |

| 6.7  | Low-power range                                                         | 67 |

| 6.8  | SRAM and eDRAM hit ratio per benchmark for the HER cache in $hp$ mode   | 69 |

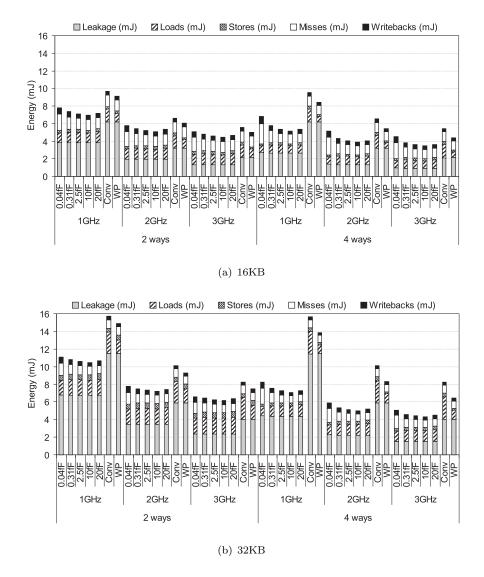

| 6.9  | Energy consumption (in mJ) of the HER cache for each benchmark          | 71 |

| 6.10 | Categorized average energy consumption (in mJ)                          | 71 |

# List of Tables

| 3.1 | CINT2000 applications                                                                                                                             | 16              |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 3.2 | CFP2000 applications                                                                                                                              | 17              |

| 4.1 | Retention time (retention times exceeding 50K cycles are shown in boldface)                                                                       | 25              |

| 4.2 | Performance degradation (32KB-4way M-Cache with 1GHz for integer benchmarks)                                                                      | 25              |

| 4.3 | Access time (in processor cycles) for the studied cache schemes                                                                                   | 20<br>26        |

| 4.4 | Cell areas $(\mu m^2)$ and reduction for different macrocell sizes                                                                                | $\frac{20}{27}$ |

| 4.5 | Machine parameters                                                                                                                                | 28              |

| 5.1 | Error-failure schemes comparison                                                                                                                  | 40              |

| 5.2 | Summary of the actions performed by the cache controller                                                                                          | 46              |

| 5.3 | Access time in cycles for the cache schemes studied (cycle time varies                                                                            |                 |

|     | across the operation modes)                                                                                                                       | 49              |

| 5.4 | Architectural machine parameters                                                                                                                  | 50              |

| 5.5 | Retention time (cycles), capacitance (fF), and performance degradation (%) of the HER cache compared to the Conv cache for the different op-      |                 |

|     | eration modes                                                                                                                                     | 51              |

| 5.6 | Hit rate (%) split into SRAM, eDRAM, and eDRAM replica hits for the cache schemes across the studied operation modes.                             | 53              |

| 5.7 | Tag array and data array areas (in $mm^2$ ) of both Conv cache and HER                                                                            |                 |

|     | cache schemes                                                                                                                                     | 57              |

| 6.1 | Operation modes with their voltage, frequency, and SRAM probability of                                                                            | 00              |

| 0.0 | failure                                                                                                                                           | 68              |

| 6.2 | Architectural machine parameters                                                                                                                  | 68              |

| 6.3 | Retention time (in processor cycles), IPC losses (%) in absolute processor cycles, and normalized execution time of the HER cache with respect to |                 |

|     | the conventional SRAM cache in $hp$ mode $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                       | 69              |

| 6.4 | Hit ratio (%) of the HER cache in the analyzed operation modes $\ldots$                                                                           | 70              |

### Abstract

Static Random-Access Memory (SRAM) technology has traditionally been used to implement processor caches since it is the fastest existing RAM technology. However, one of the major drawbacks of this technology is its high energy consumption. To reduce this energy consumption modern processors mainly use two complementary techniques: i) low-power operating modes and ii) low-power memory technologies. The first technique allows the processor working at low clock frequencies and supply voltages. The main limitation of this technique is that manufacturing defects can significantly affect the reliability of SRAM cells when working these modes. The second technique brings alternative technologies such as embedded Dynamic RAM (eDRAM), which provides minimum area and power consumption. The main drawback of this memory technology is that reads are destructive and eDRAM cells work slower than SRAM ones. To address these design concerns, heterogeneous (SRAM/eDRAM) cache organizations have recently been proposed with the aim of reducing consumption without sacrificing the performance.

This thesis presents three main contributions regarding low-power caches and heterogeneous technologies: i) an study that identifies the optimal capacitance of eDRAM cells, ii) a novel cache design that tolerates the faults produced by SRAM cells in low-power modes, iii) a methodology that allows obtain the optimal operating frequency/voltage level when working with low-power modes.

Regarding the first contribution, in this work SRAM and eDRAM technologies are combined to achieve a low-power fast cache that requires smaller area than conventional designs and that tolerates SRAM failures. First, this dissertation focuses on one of the main critical aspects of the design of heterogeneous caches: eDRAM cell capacitance. This capacitance affects both the performance and the energy consumption because when the capacitors' retention time of the eDRAM cells expires, they lose the stored logic value. In this dissertation the optimal capacitance for an heterogeneous L1 data cache is identified by analyzing the compromise between performance and energy consumption. Experimental results show that an heterogeneous cache implemented with 10fF capacitors offers similar performance as a conventional SRAM cache while providing 55% energy savings and reducing by 29% the cache area.

Regarding the second contribution, this thesis proposes a novel organization for a faulttolerant heterogeneous cache. Currently, reducing the supply voltage is a mechanism widely used to reduce consumption and applies when the system workload activity decreases. However, SRAM cells cause different types of failures when the supply voltage is reduced and thus they limit the minimum operating voltage of the microprocessor. This limitation makes difficult further energy savings, since other parts of the system could correctly work with lower supply voltages. The proposal allows higher reductions on supply voltage than other existing solutions addressing SRAM error detection and correction. In the proposal, memory cells implemented with eDRAM technology serve as backup in case of failure of SRAM cells, because the correct operation of eDRAM cells is not affected by reduced voltages. The proposed architecture has two working modes: high-performance mode for supply voltages that do not induce SRAM cell failures, and low-power mode for those voltages that cause SRAM cell failures. In high-performance mode, the cache provides full capacity, which enables the processor to achieve its maximum performance. In low-power mode, the effective capacity of the cache is reduced because some of the eDRAM cells are dedicated to recover from SRAM failures. Experimental results show that the performance is scarcely reduced (e.g. less than 2.7% across all the studied benchmarks) with respect to an ideal SRAM cache without failures.

Finally, this thesis proposes a methodology to find the optimal frequency/voltage level regarding energy consumption for the designed heterogeneous cache. For this purpose, first SRAM failure types and their probabilities are characterized. Then, the energy consumption of different frequency/voltage levels is evaluated when the system works in low-power mode. The study shows that, mainly due to the impact of SRAM failures on performance, the optimal combination of voltage and frequency from the energy point of view does not always correspond to the minimum voltage.

### Resumen

La tecnología Static Random-Access Memory (SRAM) se ha utilizado tradicionalmente para implementar las memorias cache debido a que es la tecnología de memoria RAM más rápida existente. Por contra, uno de los principales inconvenientes de esta tecnología es su elevado consumo energético. Para reducirlo los procesadores modernos suelen emplear dos técnicas complementarias: i) modos de funcionamiento de bajo consumo y ii) tecnologías de bajo consumo. La primeras técnica consiste en utilizar bajas frecuencias y voltajes de funcionamiento. La principal limitación de esta técnica es que los defectos de fabricación pueden afectar notablemente a la fiabilidad de las celdas SRAM en estos modos. La segunda técnica agrupa tecnologías alternativas como la *embedded Dynamic* RAM (eDRAM), que ofrece área y consumo mínimos. El inconveniente de esta tecnología es que las lecturas son destructivas y es más lenta que la SRAM. Para atacar este problema de diseño, recientemente se han propuesto organizaciones de cache implementadas con tecnologías heterogéneas con el objetivo de reducir el consumo sin sacrificar las prestaciones.

Esta tesis presenta tres contribuciones principales centradas en caches de bajo consumo y tecnologías heterogéneas: i) estudio de la capacitancia óptima de las celdas eDRAM, ii) diseño de una cache tolerante a fallos producidos en las celdas SRAM en modos de bajo consumo, iii) metodología para obtener la relación óptima entre voltaje y frecuencia en procesadores con modos de bajo consumo.

Respecto a la primera contribución, en este trabajo se combinan las tecnologías SRAM y eDRAM para conseguir una memoria cache rápida, de bajo consumo, área reducida, y tolerante a los fallos inherentes a la tecnología SRAM. En primer lugar, esta disertación se centra en uno de los aspectos críticos de diseño de caches heterogéneas: la capacitancia de los condensadores implementados con tecnología eDRAM. Esta capacitancia afecta tanto a las prestaciones como al consumo del procesador debido a que cuando expira el tiempo de retención de los condensadores, estos pierden el valor lógico almacenado. En esta disertación se identifica la capacitancia óptima de una cache de datos L1 heterogénea mediante el estudio del compromiso entre prestaciones y consumo energético. Los resultados experimentales muestran que condensadores de 10fF ofrecen prestaciones similares a las de una cache SRAM convencional ahorrando un 55% de consumo y reduciendo un 29% el área ocupada por la cache.

Respecto a la segunda contribución, esta tesis propone una organización de cache heterogénea tolerante a fallos. Actualmente, reducir el voltaje de alimentación es un mecanismo muy utilizado para reducir el consumo en condiciones de baja carga. Sin embargo, las celdas SRAM producen distintos tipos de fallos cuando se reduce el voltaje de alimentación y por tanto limitan el voltaje mínimo de funcionamiento del microprocesador. Esta limitación impide que se pueda reducir aún más el consumo, ya que otras partes del sistema podrían bajar más el voltaje sin verse afectado su funcionamiento. La cache heterogénea propuesta permite mayores reducciones del voltaje de alimentación que otras soluciones existentes de detección y corrección de errores basadas en tecnología SRAM. En la cache heterogénea propuesta, las celdas de memoria implementadas con tecnología eDRAM sirven de copia de seguridad en caso de fallo de las celdas SRAM, ya que el correcto funcionamiento de las celdas eDRAM no se ve afectado por tensiones reducidas. La arquitectura propuesta consta de dos modos de funcionamiento: high-performance mode para voltajes de alimentación que no inducen fallos en celdas implementadas en tecnología SRAM, y low-power mode para aquellos que sí lo hacen. En el modo highperformance mode, el procesador dispone de toda la capacidad de la cache lo que le permite alcanzar las máximas prestaciones. En el modo low-power mode se reduce la capacidad efectiva de la cache puesto que algunas de las celdas eDRAM se dedican a la recuperación de fallos de celdas SRAM. El estudio de prestaciones realizado muestra que éstas bajan hasta un máximo de 2.7% con respecto a una cache perfecta sin fallos.

Finalmente, en esta tesis se propone una metodología para encontrar la relación óptima de voltaje/frecuencia con respecto al consumo energético sobre la cache heterogénea previamente diseñada. Para ello, primero se caracterizan los tipos de fallos SRAM y las probabilidades de fallo de los mismos. Después, se evalúa el consumo energético de diferentes combinaciones de voltaje/frecuencia cuando el sistema se encuentra en un modo de bajo consumo. El estudio muestra que la combinación óptima de voltaje y frecuencia desde el punto de vista energético no siempre corresponde al mínimo voltaje debido al impacto de los fallos de SRAM en las prestaciones.

### Resum

La tecnologia *Static Random-Access Memory* (SRAM) s'ha utilitzat tradicionalment per a implementar les memòries cau degut a que és la tecnologia de memòria RAM més ràpida existent. Per contra, un dels principals inconvenients d'aquesta tecnologia és el seu elevat consum energètic. Per a reduir el consum els processadors moderns solen emprar dues tècniques complementàries: i) modes de funcionament de baix consum i ii) tecnologies de baix consum. La primera tècnica consisteix en utilitzar baixes freqüències i voltatges de funcionament. La principal limitació d'aquesta tècnica és que els defectes de fabricació poden afectar notablement a la fiabilitat de les cel·les SRAM en aquests modes. La segona tècnica agrupa tecnologies alternatives com la *embedded Dynamic* RAM (eDRAM), que ofereix àrea i consum mínims. L'inconvenient d'aquesta tecnologia és que les lectures són destructives i és més lenta que la SRAM. Per a atacar aquest problema de disseny, recentment s'han proposat organitzacions de cau implementades amb tecnologies heterogènies amb l'objectiu de reduir el consum sense sacrificar les prestacions.

Aquesta tesi presenta tres contribucions principals centrades en caus de baix consum i tecnologies heterogènies: i) estudi de la capacitancia òptima de les cel·les eDRAM, ii) disseny d'una cau tolerant a fallades produïdes en les cel·les SRAM en modes de baix consum, iii) metodologia per a obtenir la relació òptima entre voltatge i freqüència en processadors amb modes de baix consum.

Respecte a la primera contribució, en aquest treball es combinen les tecnologies SRAM i eDRAM per a aconseguir una memòria cau ràpida, de baix consum, àrea reduïda, i tolerant a les fallades inherents a la tecnologia SRAM. En primer lloc, aquesta dissertació se centra en un dels aspectes crítics de disseny de caus heterogènies: la capacitancia dels condensadors implementats amb tecnologia eDRAM. Aquesta capacitancia afecta tant a les prestacions com al consum del processador a causa que quan expira el temps de retenció dels condensadors, aquests perden el valor lògic emmagatzemat. En aquesta dissertació s'identifica la capacitancia òptima d'una cache de dades L1 heterogènia mitjançant l'estudi del compromís entre prestacions i consum energètic. Els resultats experimentals mostren que condensadors de 10fF ofereixen prestacions similars a les d'una cau SRAM convencional estalviant un 55% de consum i reduint un 29% l'àrea ocupada per la cau. Respecte a la segona contribució, aquesta tesi proposa una organització de cau heterogènia tolerant a fallades. Actualment, reduir el voltatge d'alimentació és un mecanisme molt utilitzat per a reduir el consum en condicions de baixa càrrega. Per contra, les cel·les SRAM produeixen diferents tipus de fallades quan es redueix el voltatge d'alimentació i per tant limiten el voltatge mínim de funcionament del microprocessador. Aquesta limitació impedeix que es puga reduir encara més el consum, ja que altres parts del sistema podrien baixar més el voltatge sense veure's afectat el seu funcionament. La cau heterogènia proposta permet majors reduccions del voltatge d'alimentació que altres solucions existents de detecció i correcció d'errors basades en tecnologia SRAM. En la cau heterogènia proposta, les cel·les de memòria implementades amb tecnologia eDRAM serveixen de còpia de seguretat en cas de fallada de les cel·les SRAM, ja que el correcte funcionament de les cel·les eDRAM no es veu afectat per tensions reduïdes. L'arquitectura proposada consta de dues maneres de funcionament: high-performance mode per a voltatges d'alimentació que no indueixen fallades en cel·les implementades en tecnologia SRAM, i low-power mode per a aquells que sí ho fan. En el mode highperformance, el processador disposa de tota la capacitat de la cau el que li permet aconseguir les màximes prestacions. En el mode low-power es redueix la capacitat efectiva de la cau posat que algunes de les cel·les eDRAM es dediquen a la recuperació de fallades de cel·les SRAM. L'estudi de prestacions realitzat mostra que aquestes baixen fins a un màxim de 2.7% pel que fa a una cache perfecta sense fallades.

Finalment, en aquesta tesi es proposa una metodologia per a trobar la relació òptima de voltatge/freqüència pel que fa al consum energètic sobre la cau heterogènia prèviament dissenyada. Per a açò, primer es caracteritzen els tipus de fallades SRAM i les probabilitats de fallada de les mateixes. Després, s'avalua el consum energètic de diferents combinacions de voltatge/freqüència quan el sistema es troba en un mode de baix consum. L'estudi mostra que la combinació òptima de voltatge i freqüència des del punt de vista energètic no sempre correspon al mínim voltatge degut a l'impacte de les fallades de SRAM en les prestacions.

### Chapter 1

## Introduction

This chapter introduces the basic concepts needed to understand and frame this PhD. Dissertation. First, the main reasons that motivated us to do this work are introduced. Then, several technology issues about the use of the different RAM technologies in cache memories are discussed. After that, the problems arising in low-power modes are detailed. Next, the main objectives and contributions of the thesis are described. Finally, the organization of the rest of this dissertation is presented.

#### 1.1 Current cache design and motivation

Cache memories are a critical component in current microprocessors and have been used by computer architects for many decades to reduce the average memory access time. Their design and implementation have evolved and continue still evolving with advances in both processor architecture and technology.

To reduce memory access time, caches are organized in current processors in a multilevel hierarchy, where the first level cache (the closest to the processor core) is designed to be fast and the low-level cache to be large in order to capture memory requests and avoid, as many as possible, the access to the very slow off-chip main memory.

Manufacturing costs and technology issues dictate the design space and rules to be followed for a successful design. To reduce manufacturing costs, the maximum amount of cache storage capacity must be placed within the minimum die size. This is an important design concern, since current caches occupy more than half of overall microprocessor die in current processors. Some of them are deployed with a huge cache capacity; for instance, the IBM Power 8 implements a 96MB on-chip L3 cache. On the other hand, technology constraints need to be analyzed to select the best technology to keep energy cache consumption within a given power envelope. Technology issues, however, introduce novel design concerns that rise as a consequence of shrinking the transistor node and that need to be addressed in order to enable caches to efficiently work in current microprocessors. Examples of major issues are providing support for manufacturing errors due to process variation, and allowing operation with under-threshold voltages to reduce energy consumption.

In summary, we are living nowadays in a exciting scenario regarding cache design that presents many research challenges and a wide design space that offers a high number of possibilities. This thesis is aimed at providing an efficient cache design by combining diverse RAM technologies to address performance, area and energy. Technological issues like manufacturing errors and support for low-voltage thresholds will be also investigated. Next, we discuss the basics of current cache technologies.

#### **1.2 RAM technologies**

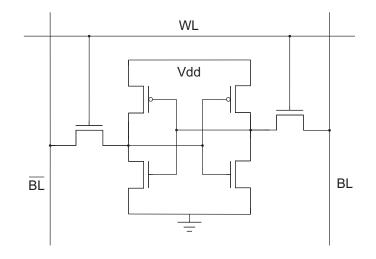

Cache memory cells have been typically implemented in microprocessor systems using Static Random Access Memory (SRAM) technology because it provides fast access time and does not require refresh operations. SRAM cells are usually implemented with six transistors (6T cells, see Figure 1.1). The major drawbacks of SRAM caches are that they

FIGURE 1.1: 6T SRAM cell

occupy a significant percentage of the overall die area and consume an important amount of energy, specially leakage energy which is proportional to the number of transistors. Furthermore, this problem is expected to aggravate with future technology generations that will continue shrinking the transistor size.

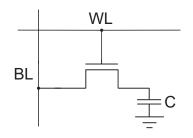

Leakage energy can be reduced by using alternative technologies like Dynamic RAM (DRAM), which is typically used for main memory. Unlike SRAM cells, DRAM cells only require an active power supply during the memory access so their leakage currents are reduced by design. These cells require less area than SRAM cells since they are implemented by using only one capacitor and the corresponding pass transistor (1T-1C cells, see Figure 1.2).

DRAM cells have been considered too slow for processor caches. Nevertheless, technology advances have recently allowed to embed DRAM cells using CMOS technology [30]. An embedded DRAM cell (eDRAM) integrates a trench DRAM storage cell into a logic-circuit technology, and provides similar access delays as those presented by SRAM cells. As a consequence, some recent commercial processors use eDRAM technology to implement large or huge and low-power last-level caches [41, 42, 44, 45].

FIGURE 1.2: 1T-1C DRAM cell

In an eDRAM cache design, the capacitance of the cells (i.e., the amount of electrical energy that can be stored in the eDRAM capacitor) impacts on performance and dynamic energy consumption. The reason is that capacitors lose their charge with time. That is, after a given period of time, which depends on the capacitance, the data information stored in the eDRAM cell cannot be retrieved any longer. This time is referred to as the cell retention time. If the capacitance is fixed too low (i.e., too short retention time), each time the retention time expires, an access from the processor to the data will result in a miss, that is, the processor will fetch the data block from a lower level of the memory hierarchy (e.g., L2 cache), which might negatively impact on performance and energy consumption. As opposite, if the capacitor charge is fixed too high, energy is wasted without bringing performance benefits.

#### **1.3** Manufacturing imperfections

As technology node continues to shrink, dealing with manufacturing imperfections is a major design concern since they affect the manufacturing yield, the energy consumption, and the performance of current and incoming processors.

Because of process variations, the manufacturing process provides transistors with different features (e.g. threshold voltage, channel length, or channel width) so that not all the transistors in a chip are able to properly work with the same voltage and frequency conditions. Due to this fact, manufacturers opt for relaxing the conditions and increase yield by introducing in the market chips that present a noticeable amount of transistors that are not able to properly work under the initial target design goal. For instance, some processors are sold cheaper when their speed is lowered below the originally targeted one to avoid process variation errors.

As a consequence, dealing with process variation in cache memories is a critical design issue. Failures due to the manufacturing process in caches mainly rise in destructive reads, unsuccessful writes, increase of the access times, and content destruction in standby mode; known as read, write, access time and hold failures, respectively.

The number of failures due to process variation is determined by the processor working conditions (power supply and frequency). In other words, most errors usually appear in a subset of the working conditions range. For instance, it may happen that an error reading a memory cell appears when the processor works at a given frequency, but that error might not appear when working at a slower frequency (i.e., access time failure). Other failures, such as destructive reads, can be avoided by increasing the voltage supply. Understanding why errors appear and which conditions allow avoiding them (or most of them) is important for microprocessor architects in order to take the proper architectural design choices to achieve the best tradeoff between performance and power.

#### 1.4 Working under the threshold voltage

Among the different transistor features, the most significant source of random manufacturing variations is the threshold voltage.

Current microprocessors support multiple power modes to exploit the trade-off between performance and power. In order to speedup the execution time, in *high-performance* modes the processor enables a high frequency which makes use of a high voltage levels. In *low-power* modes, low voltage/frequency levels are used for energy savings.

SRAM memory cells are more unreliable at low voltages because process variation induces Static Noise Margin (SNM) variability in such cells, which causes failures [32] (known as hard errors) in some of them when working below a certain reliable voltage level, namely  $Vcc_{min}$ .

Providing support to work with under-threshold voltages requires different solutions depending on the target RAM technology. On the one hand, regarding SRAM cache arrays, several techniques have been used by the industry [40] as row/column redundancy or Error Detection/Correction Codes (EDC/ECC). However multi-bit error correction codes have high overhead [51] because they need additional storage for correction codes as well as complex and slow decoders to identify errors. Other SRAM fault-tolerant solutions basically allow the system to work below  $Vcc_{min}$  by disabling those segments of the cache where one or more bits fail, thus reducing the effective storage capacity [1, 2, 13, 36, 51, 52]. Moreover, the highest fault coverage achieved by these techniques is below 10%, which makes them unsuitable for fault-dominated future technology nodes. On the other hand, regarding eDRAM cells, an interesting feature of these cells is that hard errors basically lump into the cell retention time instead of altering the stored value, thus variation problems can be addressed in eDRAM by increasing the refresh rate.

In summary, existing SRAM fault-tolerant proposals incur on a significant performance penalty since they increase access latency and reduce the effective cache capacity when working at low-power modes. At very-low voltages, the execution time can dramatically grow due to these effects, so extra energy is required to complete the program execution. Moreover, low voltages are necessarily paired with low processor frequencies, extending the cycle time in such a way that the execution time can be critically enlarged. Unfortunately, this can imply not only performance loss but also higher energy consumption with respect to higher voltage/frequency pairs. Therefore, despite the processor is working in a low-power mode and voltage is reduced for energy savings, the total energy consumption can exceed that consumed with a higher voltage level. We found that this effect appears regardless of the effectiveness of the fault-tolerant technique, even if it is able to recover 100% SRAM errors in low-power modes.

#### 1.5 Objectives of the thesis