Departament d'Informàtica de Sistemes i Computadors Universitat Politècnica de València

## Adaptive prefetch for multicores

## MASTER'S THESIS

Máster en Ingeniería de Computadores

Author

Vicent Selfa Oliver

Advisors

Prof. Julio Sahuquillo Borrás Prof. María Engracia Gómez Requena Prof. Crispín Gómez Requena

September 5, 2014

#### Abstract

Current multicore systems implement various hardware prefetchers since prefetching can significantly hide the huge main memory latencies. However, memory bandwidth is a scarce resource which becomes critical with the increasing core count. Therefore, prefetchers must smartly regulate their aggressiveness to make an efficient use of this shared resource.

Recent research has proposed to throttle up/down the prefetcher aggressiveness level, considering local and global system information gathered at the memory controller. However, in memory-hungry mixes, keeping active the prefetchers even with the lowest aggressiveness can, in some cases, damage the system performance and increase the energy consumption.

This Master's Thesis proposes the ADP prefetcher, which, unlike previous proposals, turns off the prefetcher in specific cores when no local benefits are expected or it is adversely interfering with other cores. The key component of ADP is the activation policy which must foresee when prefetching will be beneficial without the prefetcher being active. The proposed policies are orthogonal to the prefetcher mechanism implemented in the microprocessor.

The proposed prefetcher improves both performance and energy with respect to a state-of-the-art adaptive prefetcher in both memory-bandwidth hungry workloads and in workloads combining memory hungry with CPU intensive applications. Compared to a state-of-the-art prefetcher, the proposal almost halves the increase in main memory requests caused by prefetching while improving the performance by 4.46% on average, and with significantly less DRAM energy consumption.

*Keywords*: Cache, Prefetch, Adaptive, Memory Hierarchy, Performance Indexes, Multicore, Deactivation Policies, Global Feedback

# Contents

| 1 | Intr | oduction                                      | 8  |

|---|------|-----------------------------------------------|----|

|   | 1.1  | Prefetching                                   | 8  |

|   | 1.2  | Evaluation Methodologies for Multicores       | 9  |

|   | 1.3  | Contributions of this Master's Thesis         | 9  |

|   | 1.4  | Master's Thesis Outline                       | 10 |

| 2 | Bac  | kground                                       | 12 |

|   | 2.1  | Multi2Sim                                     | 12 |

|   | 2.2  | DRAMSim2                                      | 13 |

|   | 2.3  | Main Memory Organization                      | 13 |

|   | 2.4  | Prefetch Techniques                           | 14 |

|   |      | 2.4.1 One Block Lookahead                     | 14 |

|   |      | 2.4.2 Tagged Prefetch                         | 15 |

|   |      | 2.4.3 Global History Buffer Based Prefetchers | 15 |

|   |      | 2.4.4 Stream Buffers                          | 17 |

|   | 2.5  | Coherence Protocols                           | 17 |

|   |      | 2.5.1 MOESI Protocol                          | 17 |

|   | 2.6  | Benchmarks                                    | 18 |

|   |      | 2.6.1 Integer Point Arithmetics               | 19 |

|   |      | •                                             | 20 |

| 3 | Base | eline System                                  | 22 |

|   | 3.1  | L2 Prefetching System                         | 22 |

|   | 3.2  | Network-on-Chip                               | 23 |

|   | 3.3  | Memory controller and memory organization     | 25 |

| 4 | Rela | ated Work                                     | 26 |

| 5 | Eva  | luation Methodologies                         | 28 |

|   | 5.1  | Single-Threaded Processor Evaluation          | 29 |

|   | 5.2  | Methodologies for Multicores                  | 30 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.1 Typical Simulation Methodologies                                                                                                                  | 30                                                  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.2 Discussion                                                                                                                                        | 31                                                  |

|   | 5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Evaluation Indexes for Multiprogram Workloads                                                                                                           | 32                                                  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.3.1 Performance Indexes                                                                                                                               | 32                                                  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.3.2 Understanding Performance Metrics: A Practical Approach                                                                                           | 35                                                  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.3.3 Discussion                                                                                                                                        | 38                                                  |

|   | 5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Performance and Power Simulators                                                                                                                        | 39                                                  |

|   | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Experimental Evaluation                                                                                                                                 | 41                                                  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.5.1 Effect of the Simulation Methodology on Performance                                                                                               |                                                     |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | and Energy                                                                                                                                              | 41                                                  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.5.2 Effect of Modeling Details on Performance                                                                                                         | 43                                                  |

|   | 5.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Summary                                                                                                                                                 | 45                                                  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         |                                                     |

| 6 | Cha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | racterization Study And Prefetcher Proposal                                                                                                             | 46                                                  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         |                                                     |

|   | 6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Characterization Study                                                                                                                                  | -                                                   |

|   | 6.1<br>6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Characterization Study                                                                                                                                  | -                                                   |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         | 49                                                  |

|   | 6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Proposed Prefetching Scheme                                                                                                                             | 49<br>52                                            |

|   | 6.2<br>6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Proposed Prefetching Scheme                                                                                                                             | 49<br>52<br>53                                      |

|   | 6.2<br>6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Proposed Prefetching Scheme                                                                                                                             | 46<br>49<br>52<br>53<br>54<br>56                    |

|   | 6.2<br>6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Proposed Prefetching Scheme                                                                                                                             | 49<br>52<br>53<br>54<br>56                          |

|   | 6.2<br>6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Proposed Prefetching Scheme                                                                                                                             | 49<br>52<br>53<br>54                                |

| 7 | <ul><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Proposed Prefetching SchemeEvaluation MethodologyExperimental Evaluation6.4.1Performance Analysis6.4.2Prefetches Reduction Analysis6.4.3Energy Analysis | 49<br>52<br>53<br>54<br>56<br>58                    |

| 7 | <ul><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Proposed Prefetching Scheme                                                                                                                             | 49<br>52<br>53<br>54<br>56<br>58<br>60              |

| 7 | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Contact of the second sec</li></ul> | Proposed Prefetching Scheme                                                                                                                             | 49<br>52<br>53<br>54<br>56<br>58<br>60<br><b>62</b> |

# **List of Figures**

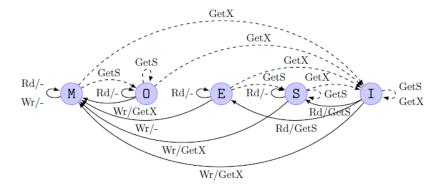

| 2.1        | MOESI state transitions                                                                                      | 19       |

|------------|--------------------------------------------------------------------------------------------------------------|----------|

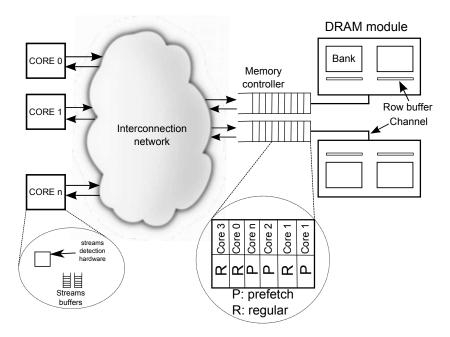

| 3.1        | Baseline multicore with prefetching components and memory con-<br>troller                                    | 23       |

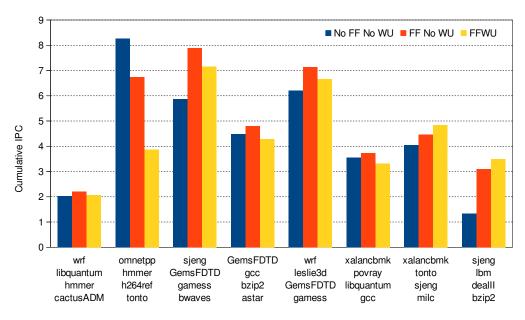

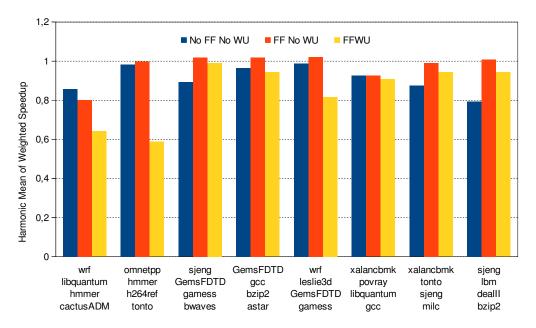

| 5.1<br>5.2 | Cumulative IPC for three of the studied methods                                                              | 42<br>43 |

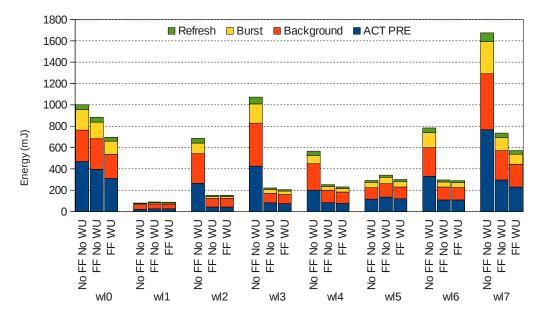

| 5.3        | Effect of applied methodology on main memory energy consumption.                                             | 44       |

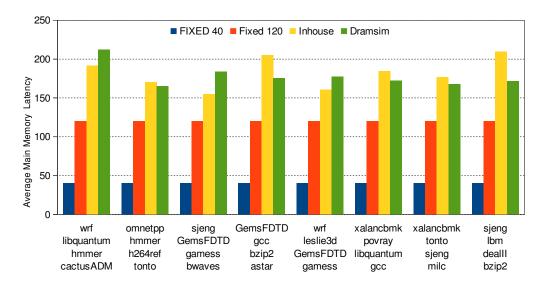

| 5.4        | Memory latencies for the studied memory controllers                                                          | 44       |

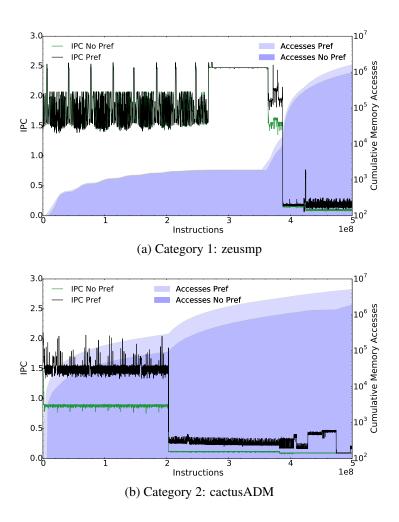

| 6.1        | Characterization study. Categories 1 and 2                                                                   | 47       |

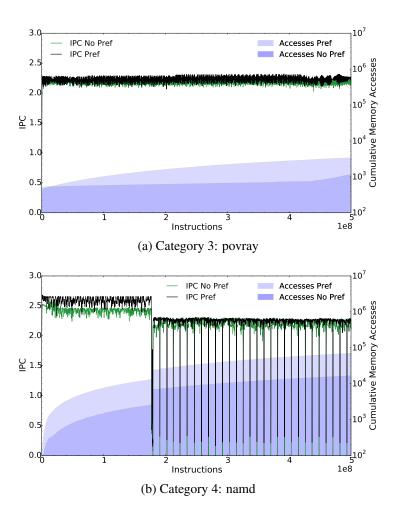

| 6.2        | Characterization study. Categories 3 and 4.                                                                  | 48       |

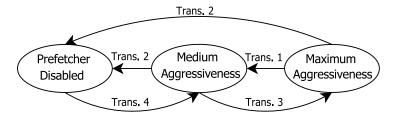

| 6.3        | ADP state transitions. Transitions on the edges correspond to the transitions in Algorithm 1 and Algorithm 2 | 51       |

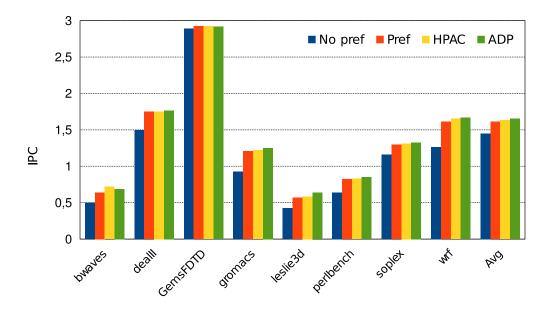

| 6.4        | Performance of prefetchers running benchmarks in isolation                                                   | 54       |

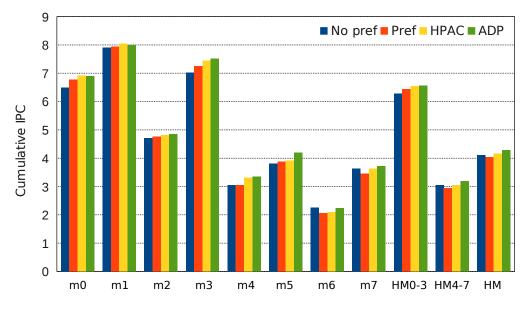

| 6.5        | Cumulative IPC per Workload.                                                                                 | 55       |

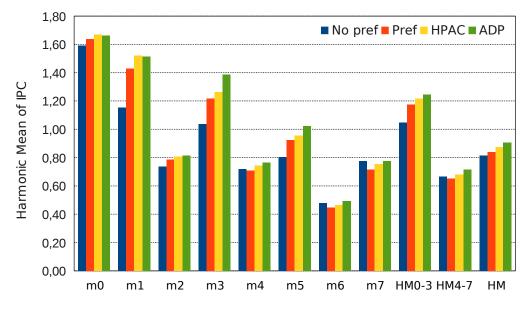

| 6.6        | Harmonic Mean of IPC per Workload.                                                                           | 56       |

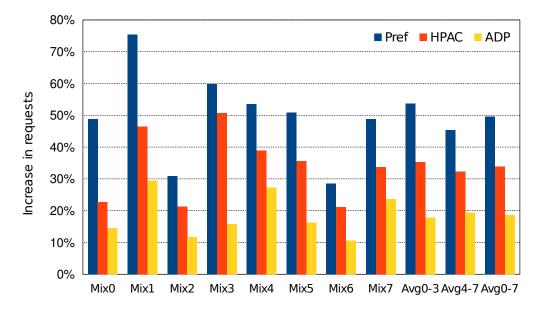

| 6.7        | Requests increase of the studied prefetchers over no prefetching                                             | 57       |

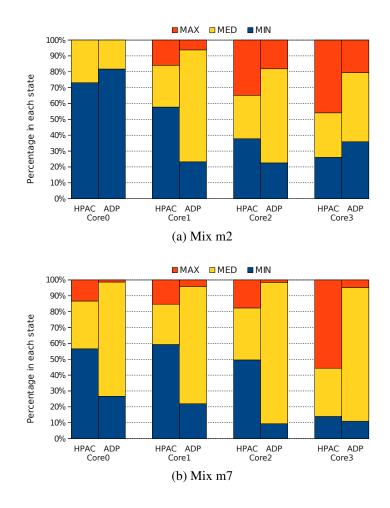

| 6.8        | Fraction of time spent in each state for HPAC and ADP                                                        | 58       |

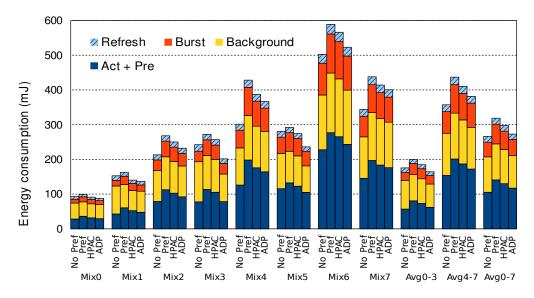

| 6.9        | Energy consumption of the prefetching mechanisms                                                             | 59       |

## **List of Tables**

| 2.1        | Stream of deltas                                                       | 16 |

|------------|------------------------------------------------------------------------|----|

| 3.1<br>3.2 | System configuration                                                   |    |

| 5.1        | IPCs and Speedups of the benchmarks in the 4-core compared machines.   | 36 |

| 5.2        | Summarizing performance and fairness metrics in the compared machines. |    |

| 5.3        | Four-core mixes composition.                                           |    |

| 6.1        | Mix composition.                                                       | 53 |

| 6.2        | Thresholds used in ADP                                                 | 53 |

## Chapter 1

## Introduction

This chapter presents the motivation for the work developed in this Master's Thesis. First, prefetching is introduced, discussing its pros and cons and showing the potential of adaptive approaches to overcome some of the shortcomings of prefetching. After that, the need of adequate metrics for multicore evaluation is introduced. Finally, an overview about the contents of this Master's Thesis is given.

### **1.1 Prefetching**

Addressing memory latencies is a major design concern in modern chip multiprocessors (CMPs). Prefetching is a well-known technique that hides memory latencies by fetching data blocks before the core demands them. Because of prefetching benefits, modern microprocessors [1–4] typically implement several prefetchers along their cache hierarchy. In current CMPs, memory requests from different cores compete among them for off-chip DRAM bandwidth. As the core count increases, the memory becomes a major contention point, and the system performance highly depends on how the limited memory bandwidth is managed.

In these environments the prefetching schemes must be revisited. A direct solution to increase bandwidth availability would be to turn off the core prefetchers, so avoiding speculative prefetches. However, this way could result in important performance losses for those applications where prefetchers achieve a noticeable coverage so hiding memory latency. Therefore, solutions should be focused on reducing the number of useless prefetches, saving bandwidth and energy.

Recent approaches [5] propose the use of throttling up/down mechanisms to control the prefetcher aggressiveness. The aggressiveness level is throttled down when scarce or no performance benefits are expected from prefetching. As opposite, aggressiveness is throttled up when performance improvements are foreseen. These approaches try to keep the benefits of prefetching while reducing the memory bandwidth consumption with respect to aggressive prefetching. Nevertheless, since memory bandwidth requirements from different applications widely differ among them, this situation may lead the performance of some cores to improve but at the cost of hurting the performance of some others. To deal with fairness, the *Hierarchical Prefetcher Aggressiveness Control (HPAC)* scheme [6] takes into account *global* system performance information (e.g. memory-bandwidth interferences among the different applications at the memory controller).

In this Master's Thesis we claim that bandwidth-aware prefetchers are required in current multicores to make an efficient use of the limited memory bandwidth. This kind of prefetcher is needed to keep or enhance the performance gains of adaptive prefetchers, especially when running memory-hungry workloads.

### **1.2** Evaluation Methodologies for Multicores

Researchers modeling and evaluating performance and energy in multicores face three main issues, which are still evolving. First, there are multiple methodologies being used to evaluate these systems, mainly inherited from single-threaded processor research. Second, due to the nature of multiprogram workloads, new performance metrics different from those used in single-thread processors are required. Many metrics have been defined and distinct metrics are used across the published work. Finally, multicore processors are really complex systems which require from sophisticated and complementary (e.g. energy and performance) simulators.

## **1.3** Contributions of this Master's Thesis

The main focus of this Master's Thesis is on the design of new prefetchers to efficiently work in multicore processors both from the performance and energy points of view. These systems suffer from interferences of memory requests of the multiple cores, which can strangle the scarce main memory bandwidth. In such a case, a twofold effect rises in the system: i) the overall system performance suffers, and ii) the memory energy consumption rises. These problems exacerbate with aggressive prefetching. However, prefetching cannot be deactivated for all the cores, since it is well known that many applications benefit from prefetching.

This work presents an adaptive bandwidth-aware prefetcher designed to make an efficient use of the limited memory bandwidth, which the main contribution of this work. The devised approach tries to keep or enhance the performance gains of aggressive prefetchers while consuming a fraction of the energy and main memory traffic. Our Activation/Deactivation Prefetcher (ADP) incorporates two main mechanisms: On the one hand, as an adaptive prefetcher, it implements throttling up and down policies to regulate the aggressiveness. On the other hand, activation and deactivation policies are also implemented taking into account global system information, which is the main novelty of the proposed prefetcher. This improves the performance while reducing main memory energy consumption.

To design an efficient prefetcher we firstly characterized the dynamic behavior of each SPEC-CPU2006 benchmark across its execution time, analyzing how prefetching and main memory activity impact on performance, which is the second major contribution of this work. We found that although prefetching brings important performance improvements in some phases of the program execution, in other phases it scarcely or negatively affects the performance. Current adaptive prefetchers do not match this finding, since most of them dynamically regulate the aggressiveness but never turn off the prefetchers completely or do not consider the system main memory requirements.

Nowadays the microprocessor market is dominated by multicores, and most research work has sharply moved to this kind of processors. This quick shift of the research has left researchers with outdated research methods taken from the evaluation of their single-threaded counterparts. This new situation has lead researchers to face three important research issues targeting multicores: simulation methodologies, performance and energy metrics, and simulation frameworks. The first contribution of this Master's Thesis is a survey of the mentioned methodological issues across a sample of 28 papers published in 2013 in the top-computer architecture conferences (ISCA, HPCA, PACT, and MICRO), focusing on multicores with multiprogram workloads. For the sake of completeness, this work presents an overview of the simulation methods, discusses the performance indexes used to evaluate the proposals, and analyzes how the simulation details (used in the different system components) can affect both performance and energy results.

### **1.4 Master's Thesis Outline**

Chapter 2 introduces a broad set of concepts tightly connected with this work. Chapter 3 presents the simulated system in which the experimental results have been obtained. Chapter 4 discusses prior work related to this Master's Thesis. Chapter 5 presents an in-depth analysis of performance metrics used in multicore research in order to determine the most suited for this work. Chapter 6 presents the characterization analysis and our proposed prefetching mechanism, and finally, Chapter 7 summarizes this thesis, discusses future work, and enumerates the related publications.

## Chapter 2

## Background

### 2.1 Multi2Sim

Multi2Sim [7] is a cycle accurate event driven simulation framework for CPU-GPU heterogeneous computing written in C. It includes models for superscalar, multithreaded, and multicore CPUs, as well as GPU architectures.

The CPU simulation framework consists of two major interacting software components: the functional simulator and the architectural simulator. The functional simulator (i.e. emulator) mimics the execution of a guest program on a native x86 processor, by interpreting the program binary and dynamically reproducing its behavior at the ISA level. The architectural simulator (i.e. detailed or timing simulator) obtains a trace of x86 instructions from the functional simulator, and tracks execution of the processor hardware structures on a cycle-by-cycle basis.

The experimental results of this Master's Thesis have been obtained using version 4.2 of Multi2Sim, which supports the execution of a number of different benchmark suites without requiring any porting, including SPEC2006, as well as custom self-compiled user code. The architectural simulator models many-core superscalar pipelines with out-of-order execution, a complete memory hierarchy with cache coherence, interconnection networks, and can be easily extended to model additional components.

A drawback of Multi2Sim is that it does not accurately model the main memory nor a memory controller. Consequently, main memory requests have no contention at all and latencies are fixed. This is not realistic and a serious limitation if evaluating a prefetcher and measuring main memory energy consumption.

To overcome this, we have integrated DRAMSim2 [8], a dedicated main memory simulator.

## 2.2 DRAMSim2

DRAMSim2 is a cycle accurate simulator that provides a DDR2/3 memory system model that includes ranks, banks, command queue, the memory controller, etc. and the buses by which they communicate. It provides a C++ API that can be used to integrate it in a full system simulator easily. As Multi2Sim is written in pure C, the project has been forked and extended with a C API and other requirements of this Master's Thesis.

## 2.3 Main Memory Organization

DRAM memories usually are presented as DIMMs, a circuit board with a handful of chips or DRAM devices and associated circuitry attached to it. Each DIMM module has several DRAM devices, which are grouped in ranks. A rank is a collection of DRAM devices that operate in lockstep (all chips in a rank respond to a single command) and read or write 64 bits to the bus, which is 64 bits wide, as defined in the JEDEC [9] standard. The number of devices that compose a rank depend of the specific device width, thats is, the number of data pins of the device. For example, a DIMM module using  $\times 4$  DRAM devices, which can output four bits per transaction, will have 64/4 devices per rank.

Internally, each of these DRAM devices implements multiple independent banks, which are the smallest memory structures that can be accessed in parallel with respect to each other (bank-level parallelism). Each bank operates independently, but banks in the same rank must comply with some timing restrictions to reduce resource utilization and thus peak power consumption. As devices in a rank operate in lockstep, when a bank is accessed it is accessed in all the devices that compose the rank, transmitting a total of 64 bits from or to the bus.

In addition, each bank is composed of multiple memory arrays, where the number of arrays is equal to the data width of the DRAM part. DRAM banks are therefore composed of two-dimensional arrays of capacitor-based DRAM cells. Each bank has a row-buffer which stores the values of the last accessed row and consists of an array of sense-amplifiers that act as latches. Therefore, subsequent accesses to the same row are faster if the row is in the row buffer. Actually, at the end of an access, the memory controller can either keep the row open in the row buffer (open-row policy) or close it if no more accesses to this row are expected (closed-row policy).

The DRAM memory controller manages the flow of data into and out of DRAM devices connected to that DRAM controller in the memory system. Specifically, it defines the Row-Buffer-Management Policy, the Address Mapping Scheme, and the Memory Transaction and DRAM Command Ordering Scheme. A memory system can have a single channel, or multiple channels. A channel is the physical link between the processor and a set of DIMM modules that communicate through it. Multiple ranks are connected to the same channel so all receive the same commands, but only one replies. If there are multiple channels, they can be independent, with a dedicated memory controller, or configured in lockstep mode to have a wider interface (e.g. dual-channel).

Three different commands are needed to access a DRAM bank: i) a precharge command to precharge the row bitlines, ii) an activate command to open the row corresponding to the row address into the row buffer, and finally iii) a read/write command to access the row buffer at the position indicated by the column address. Depending on the row policy used by the controller and the address of the requests, very different latencies to memory can be perceived by the processor. If the row accessed is in the row buffer, the latency is low, as only a read/write command has to be issued. If the row is not in the row buffer, then the memory controller needs to issue the three commands: precharge, activate and read/write. If the controller uses a close-row policy, this means that there is no valid data in the row buffer and therefore every access has to issue an activation command and a read/write command. In all cases perceived latency is the sum of the latencies of the issued commands, as they must be executed sequentially and in order.