TECHNICAL UNIVERSISTY OF VALENCIA DEPARTMENT OF SYSTEMS DATA PROCESSING AND COMPUTERS

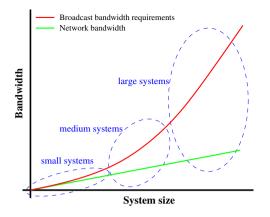

# Efficient Techniques to Provide Scalability for Token-based Cache Coherence Protocols

A dissertation submitted in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy (Computer Sciences)

Author Blas Antonio Cuesta Sáez

Advisors

Antonio Robles Martínez José Francisco Duato Marín

VALENCIA, 2009

# Acknowledgments

"Perfection (in design) is achieved not when there is nothing more to add, but rather when there is nothing more to take away"

Eric S. Raymond, The Cathedral and the Bazaar

I have received a lot of support, encouragement, and help throughout all these years in university. Many of the people I have met during these years have greatly influenced my research and changed me as a person.

First and foremost I thank my parents and my brother for their support, encouragement, constant interest in my life, and patience throughout all this time; they have always been there for me.

My advisers, Antonio Robles and José Duato, have had a great influence on me. The depth of knowledge that I have gained due to my numerous meetings with them is incredible. I have learned a lot about computer architecture and interconnection networks, but they have not been the only things, as they taught me about many aspects of performing research, communicating with others, delivering speeches, and many other related aspects. Most importantly, I have learned a great deal by simply observing their excellent example and behavior. I do not have any doubt that my research and non-research life has forever been changed by their advice. I specially thank Antonio Robles for his dedication and, above all, his patience, because like all true "manchegos", sometimes I may be too stubborn.

Many of the other faculty members in the Parallel Architecture Group have helped me too. I have benefited from interacting with them. Julio Sahuquillo, José Flich, Pedro López, and Federico Silla all provided useful insight into my dissertation research and provided valuable feedback during the process. Likewise, I would like to thank María Engracia Gómez, Vicente Santonja, and Elvira Baydal because they all contributed in making me feel comfortable and integrated in the group.

I have met many interesting students while in university. Although I can not possibly mention everyone who has enriched my experience or provided moral support, I wish to specifically thank a few individuals. Gaspar Mora, Crispín Gómez, Francisco Gilabert, Andres Mejía, José Miguel Montañana, Rafa Ubal, Carles Hernández, Héctor Montaner, and David Yuste have unselfishly helped me in different aspects of my research and I would like to highlight their support. Furthermore, I would like to thank Ricardo Marín for his constant availability to help me to resolve each one of the numerous problems that I have faced

Gaspar and I created a fantastic hobby called "football Xtreme". I want to thank Gaspar for his help in creating and maintaining this hobby alive and for introducing me to such a great group of people. "Football Xtreme" has been very useful for me to relieve stress, keep fit, and have fun.

I could not finish without thanking all my English teachers at the American Institute, specially Meredith and Dana, who had to deal with strange questions.

Finally, I thank Virtutech AB for their support of Simics and for providing us with a license server. I also want to thank those individuals who paid taxes and, therefore, helped me during my time in university. This work was supported by the Spanish program CONSOLIDER-INGENIO 2010 under Grant CSD2006-00046, by the Spanish CICYT under Grant TIN2006-15516-C04-01, the JCC de Castilla-La Mancha under Grant PBC-05-007-2, and by the European Commission in the context of the SARC integrated project #27648 (FP6).

# Contents

| A        | ckno  | wledgr  | nents                             | iii  |

|----------|-------|---------|-----------------------------------|------|

| A        | bstra | ict     | 2                                 | xvii |

| R        | esum  | en      |                                   | xix  |

| R        | esum  | L       |                                   | xxi  |

| 1        | Intr  | roducti | ion                               | 1    |

|          | 1.1   | Conte   | xt and Motivation                 | 1    |

|          | 1.2   | Objec   | tives                             | 5    |

|          | 1.3   | Thesis  | s Contributions                   | 6    |

|          |       | 1.3.1   | Priority Requests                 | 6    |

|          |       | 1.3.2   | Limiting the Storage Requirements | 8    |

|          |       | 1.3.3   | Switch-based Packing Technique    | 9    |

|          |       | 1.3.4   | Multicast Data Responses          | 10   |

|          |       | 1.3.5   | Summary                           | 11   |

|          | 1.4   | Thesis  | s Outline                         | 11   |

| <b>2</b> | Cor   | ncepts  | and Background                    | 13   |

|          | 2.1   | Basis   | of Cache Memories                 | 13   |

|          |       | 2.1.1   | Block Placement Policy            | 14   |

|          |       | 2.1.2   | Replacement Policy                | 15   |

|          |       | 2.1.3   | Write Policy                      | 16   |

|          |       | 2.1.4   | Structure                         | 17   |

|          | 2.2   | Cache   | e Coherence                       | 18   |

|   | 2.3 | Coherence Models                           | 2 |

|---|-----|--------------------------------------------|---|

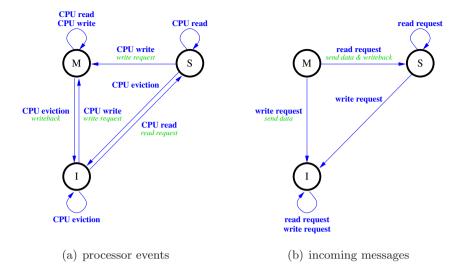

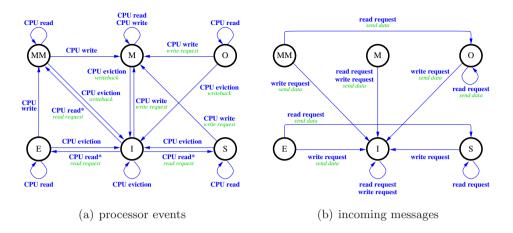

|   |     | 2.3.1 MSI                                  | 2 |

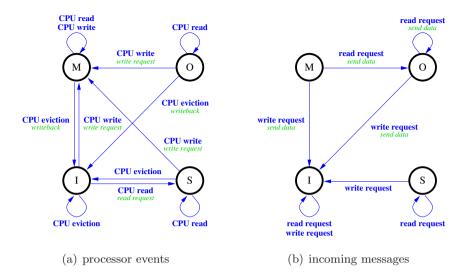

|   |     | 2.3.2 MOSI                                 | 4 |

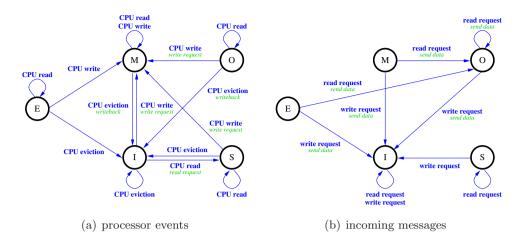

|   |     | 2.3.3 MESI                                 | 5 |

|   |     | 2.3.4 MOESI                                | 6 |

|   |     | 2.3.5 Optimization for Migratory Sharing 2 | 7 |

|   | 2.4 | Consistency Models                         | 9 |

|   | 2.5 | Interconnection Networks                   | 0 |

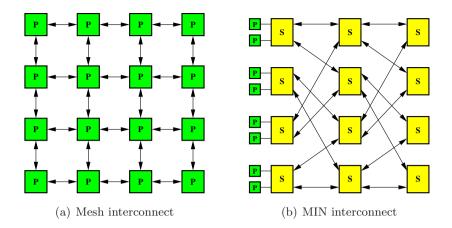

|   |     | 2.5.1 Network Topology                     | 0 |

|   |     | 2.5.2 Switching Techniques                 | 2 |

|   |     | 2.5.3 Routing Techniques                   | 3 |

| 3 | Cac | he Coherence Mechanisms 3                  | 5 |

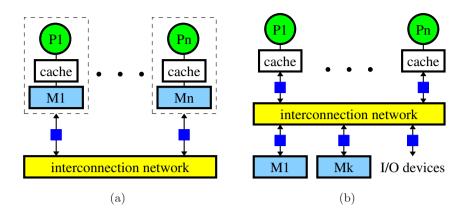

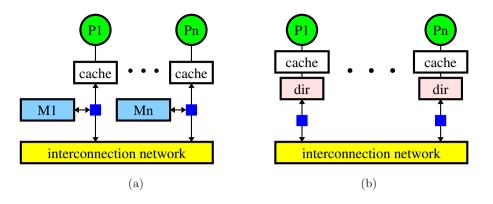

|   | 3.1 | Snooping-based Protocols                   |   |

|   | 3.2 | Directory-based Protocols                  | 7 |

|   | 3.3 | Non-traditional Protocols                  | 0 |

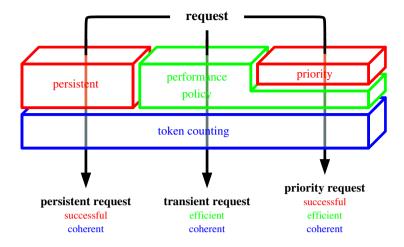

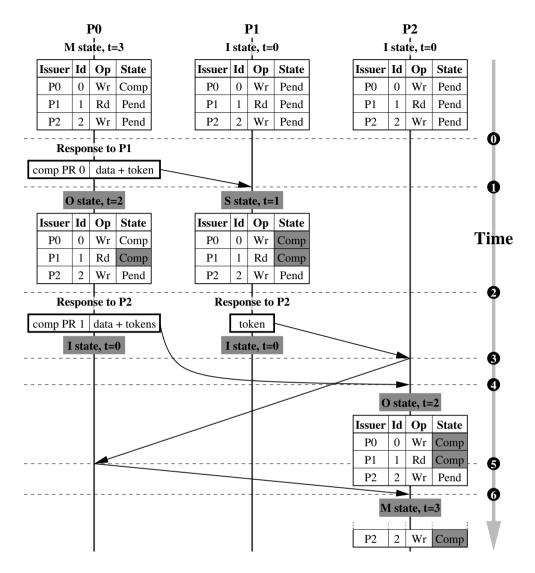

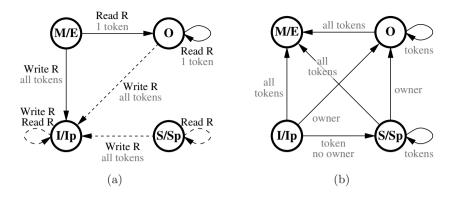

|   | 3.4 | Token-based Protocols                      | 0 |

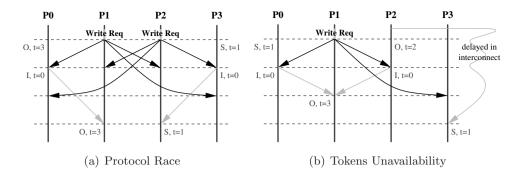

|   |     | 3.4.1 Token Counting                       | 1 |

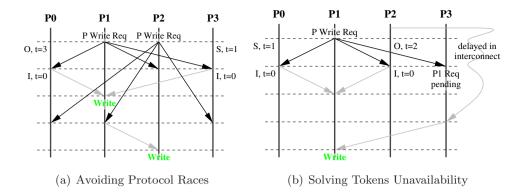

|   |     | 3.4.2 Persistent Requests                  | 2 |

|   |     | 3.4.3 Performance Policy                   | 5 |

|   | 3.5 | Summary                                    | 7 |

| 4 | Eva | luation Methodology 4                      | 9 |

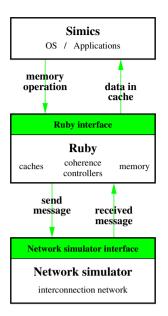

|   | 4.1 | Simulation Tools                           | 9 |

|   |     | 4.1.1 Simics Simulator                     |   |

|   |     | 4.1.2 Ruby Module                          | 1 |

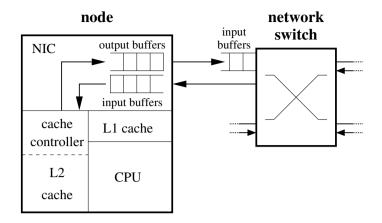

|   |     | 4.1.3 Network Simulator                    | 1 |

|   |     | 4.1.4 Interconnection between Simulators   | 2 |

|   | 4.2 |                                            | 3 |

|   | 4.3 | -                                          | 6 |

|   | 4.4 | Workload Descriptions                      | 8 |

| 5 | The | Priority Request Mechanism 6               | 3 |

| - | 5.1 | Introduction                               |   |

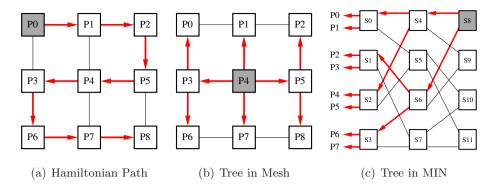

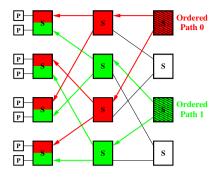

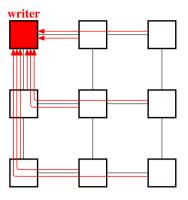

|   | 5.2 | Ordered Paths                              |   |

|   |     |                                            |   |

|   | 5.3  | Priority Request Table                                               | 9 |

|---|------|----------------------------------------------------------------------|---|

|   | 5.4  | $Priority Request Identifier \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 1 |

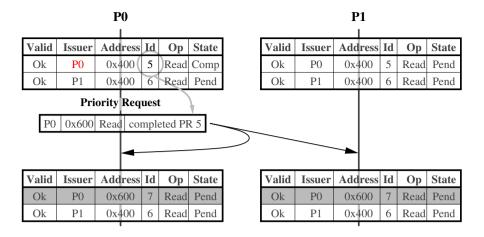

|   | 5.5  | Removing Completed Priority Requests                                 | 2 |

|   | 5.6  | Avoiding Serving Completed Priority Requests                         | 5 |

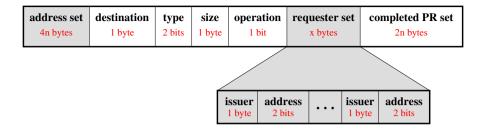

|   | 5.7  | Coding Identifiers in Messages                                       | 9 |

|   | 5.8  | The Performance Policy                                               | 2 |

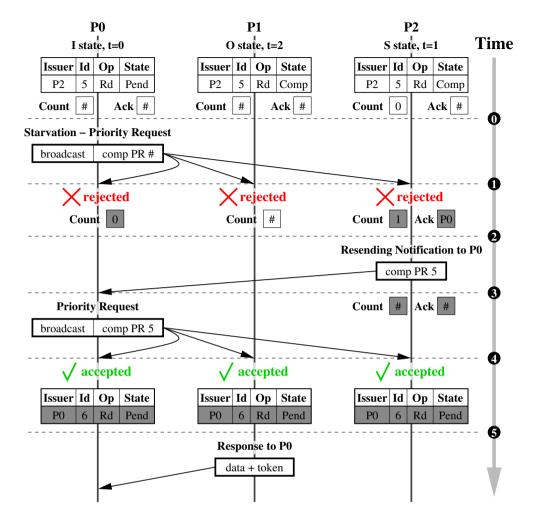

|   | 5.9  | Guaranteeing Starvation-Freedom                                      | 3 |

|   |      | 5.9.1 Deadlock-Free Message Delivery 8                               | 3 |

|   |      | 5.9.2 Ordering Delivery Guarantee                                    | 4 |

|   |      | 5.9.3 Priority Request Storage Guarantee                             | 4 |

|   |      | 5.9.4 Requested Token Reception Guarantee                            | 5 |

|   | 5.10 | Using Several Ordered Paths 8                                        | 6 |

|   |      | 5.10.1 Selecting the Ordered Path                                    | 7 |

|   |      | 5.10.2 Priority Request Identifier                                   | 8 |

|   |      | 5.10.3 Storing Priority Requests                                     | 9 |

|   | 5.11 | Discussion: Persistent Vs Priority                                   | 9 |

|   | 5.12 | Priority Request Summary 9                                           | 3 |

|   | 5.13 | Evaluation                                                           | 4 |

|   |      | 5.13.1 Target System and Parameters                                  | 4 |

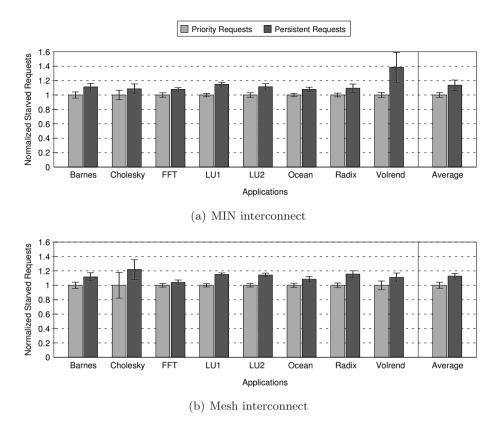

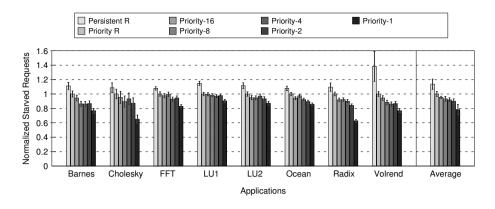

|   |      | 5.13.2 Starved Requests                                              | 4 |

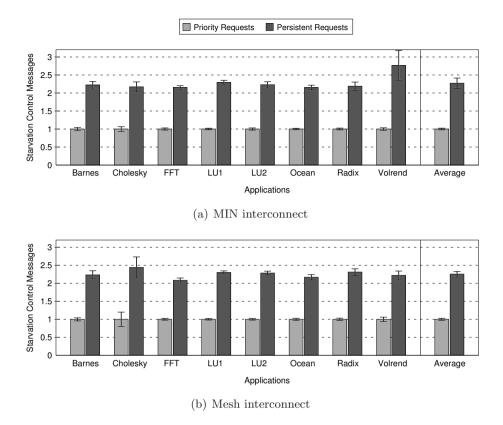

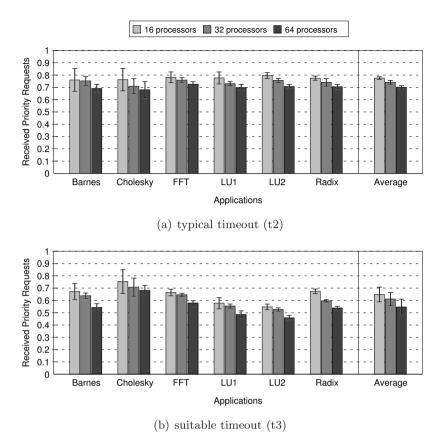

|   |      | 5.13.3 Starvation Control                                            | 6 |

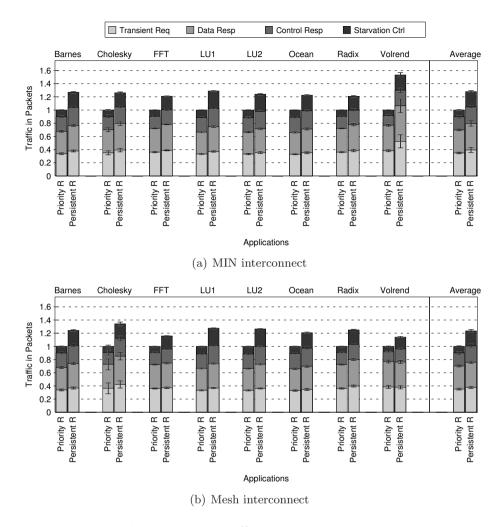

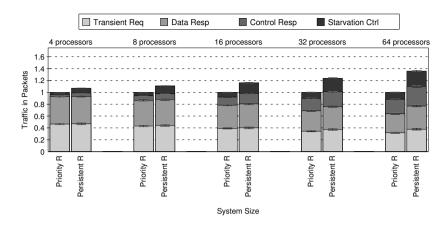

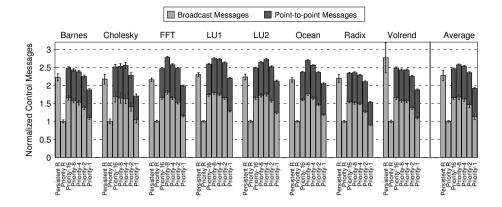

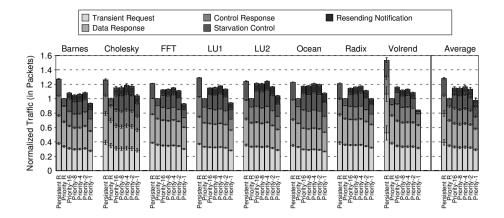

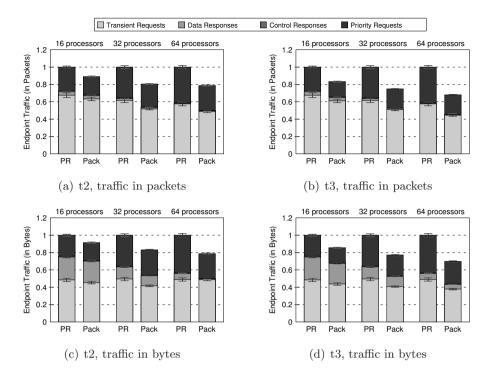

|   |      | 5.13.4 Network Traffic                                               | 7 |

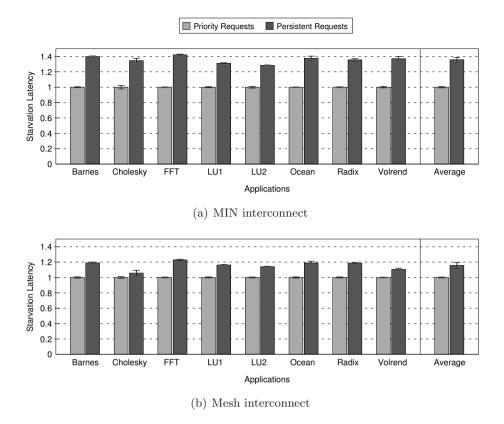

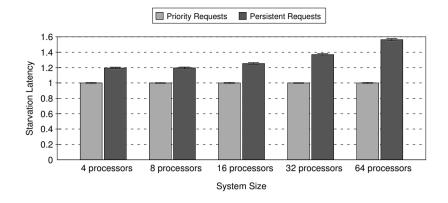

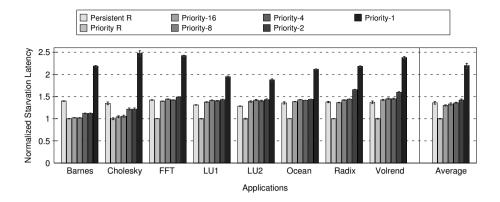

|   |      | 5.13.5 Starvation Latency                                            | 8 |

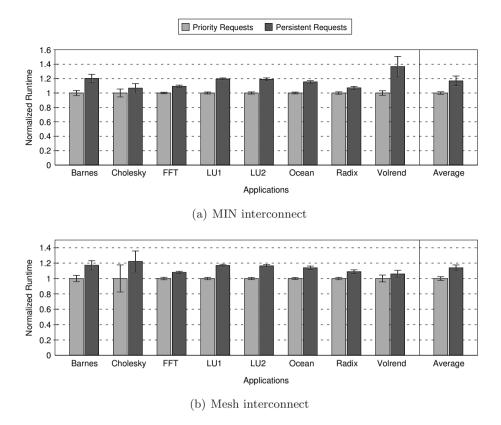

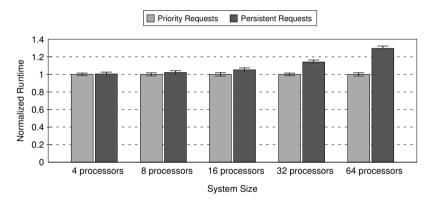

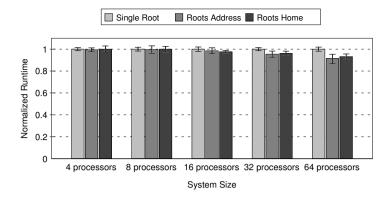

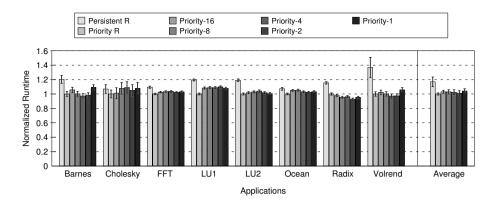

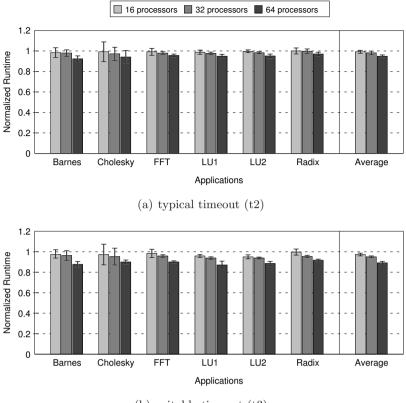

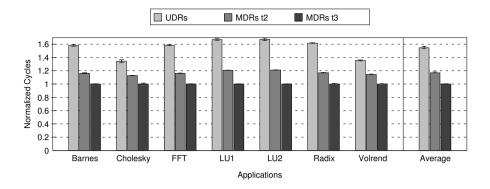

|   |      | 5.13.6 Runtime                                                       | 0 |

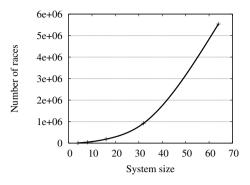

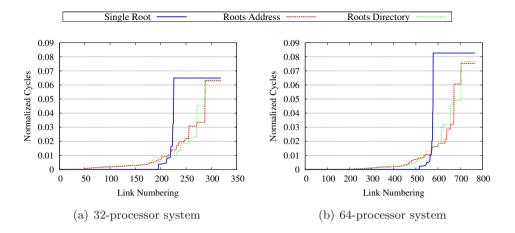

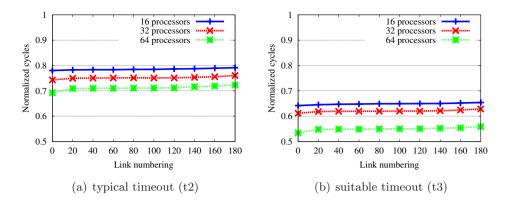

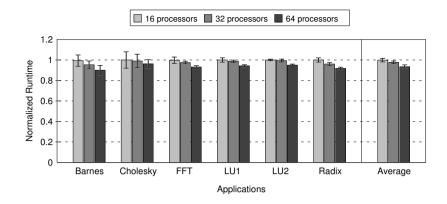

|   |      | 5.13.7 Scalability                                                   | 1 |

|   |      | 5.13.8 Several Ordered Paths                                         | 3 |

|   | 5.14 | Conclusions                                                          | 5 |

| 6 | Bou  | nding Storage Requirements 10'                                       | 7 |

|   | 6.1  | Introduction                                                         | 7 |

|   | 6.2  | Data Structures                                                      | 9 |

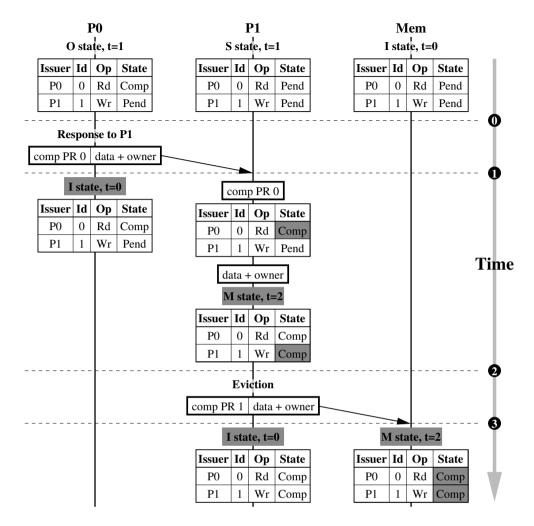

|   | 6.3  | General Working Scheme                                               |   |

|   | 6.4  | Ensuring the Priority Request Storage                                |   |

|   | 6.5  | Notifying the Priority Request Completion                            |   |

|   |      |                                                                      |   |

|   | 6.6  | Reduci | ng the Control Traffic $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 |

|---|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   |      | 6.6.1  | Size of Rejected Priority Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7 |

|   |      | 6.6.2  | Removing Acknowledgments 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3 |

|   |      | 6.6.3  | Handling Rejected Priority Requests as Transient Re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|   |      |        | quests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ) |

|   | 6.7  | Evalua | $tion \ldots 120$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ) |

|   |      | 6.7.1  | Target System and Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ) |

|   |      | 6.7.2  | Starved Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L |

|   |      | 6.7.3  | Starvation Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2 |

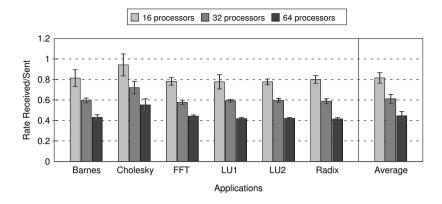

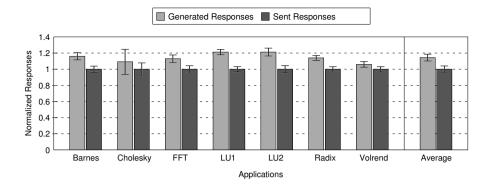

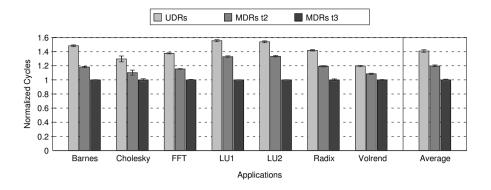

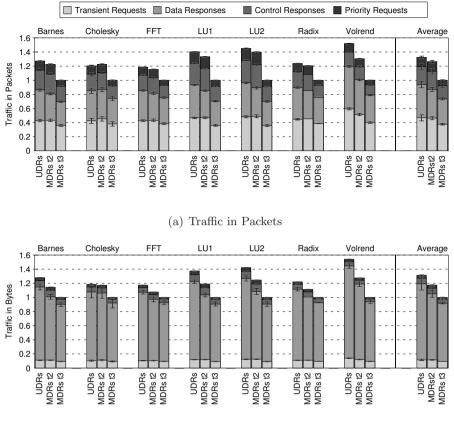

|   |      | 6.7.4  | Network Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2 |

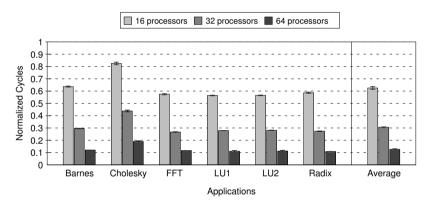

|   |      | 6.7.5  | Starvation Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3 |

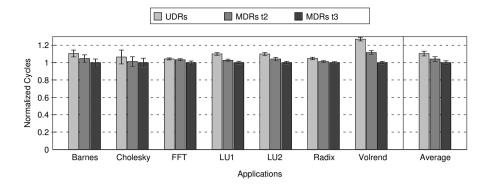

|   |      | 6.7.6  | Runtime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 |

|   | 6.8  | Conclu | sions $\ldots \ldots 125$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 |

| 7 | Swit | ch-bas | ed Packing Technique 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7 |

| • | 7.1  |        | $\begin{array}{c} 127 \\ 127 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\ 107 \\$ |   |

|   | 7.2  |        | t of Priority Request Packs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

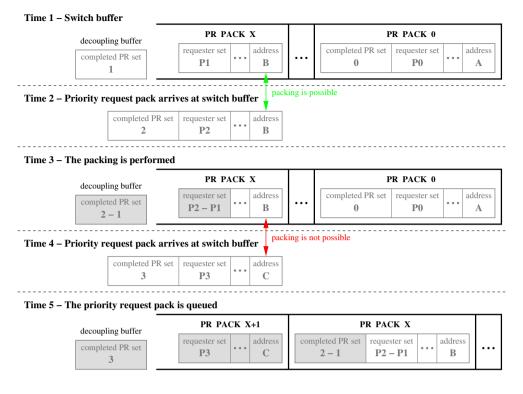

|   | 7.3  |        | l Packing Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

|   | 7.4  |        | ng Message Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|   | 7.5  |        | g Priority Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|   | 7.6  |        | sing Packing Opportunities $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

|   | 1.0  | 7.6.1  | Increasing the Number of Ordered Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

|   |      | 7.6.2  | Allowing Different Request Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

|   |      | 7.6.3  | Allowing Different Memory Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|   | 7.7  |        | ing the Starvation Detection Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|   | 7.8  | 0      | g Non-Silent Invalidations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|   | 7.9  |        | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|   |      | 7.9.1  | Target System and Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |