UNIVERSIDAD POLITÉCNICA DE VALENCIA Departamento de Informática de Sistemas y Computadores

# Metodología para hipervisores seguros utilizando técnicas de validación formal

TESIS DOCTORAL PRESENTADA POR: Salvador Peiró Frasquet

> DIRIGIDA POR: Dr. Alfons Crespo i Lorente Dr. Miguel Masmano Tello Dr. José Simó Ten

Valencia, December 22, 2015

Acknowledgements

This words are dedicated to those that have provided his support to perform this work, specially, to my supervisors, colleagues, friends and family.

## Abstract

The availability of new processors with more processing power for embedded systems has raised the development of applications that tackle problems of greater complexity. Currently, the embedded applications have more features, and as a consequence, more complexity. For this reason, there exists a growing interest in allowing the secure execution of multiple applications that share a single processor and memory. In this context, partitioned system architectures based on hypervisors have evolved as an adequate solution to build secure systems.

One of the main challenges in the construction of secure partitioned systems is the verification of the correct operation of the hypervisor, since, the hypervisor is the critical component on which rests the security of the partitioned system. Traditional approaches for Validation and Verification (V&V), such as testing, inspection and analysis, present limitations for the exhaustive validation and verification of the system operation, due to the fact that the input space to validate grows exponentially with respect to the number of inputs to validate. Given this limitations, verification techniques based in formal methods arise as an alternative to complement the traditional validation techniques.

This dissertation focuses on the application of formal methods to validate the correctness of the partitioned system, with a special focus on the XtratuM hypervisor. The proposed methodology is evaluated through its application to the hypervisor validation. To this end, we propose a formal model of the hypervisor based in Finite State Machines (FSM), this model enables the definition of the correctness properties that the hypervisor design must fulfill. In addition, this dissertation studies how to ensure the functional correctness of the hypervisor implementation by means of deductive code verification techniques.

Last, we study the vulnerabilities that result of the loss of confidentiality (CWE-200 [CWE08b]) of the information managed by the partitioned system. In this context, the vulnerabilities (infoleaks) are modeled, static code analysis techniques are applied to the detection of the vulnerabilities, and last the proposed techniques are validated by means of a practical case study on the Linux kernel that is a component of the partitioned system.

## Resumen

La disponibilidad de nuevos procesadores más potentes para aplicaciones empotradas ha permitido el desarrollo de aplicaciones que abordan problemas de mayor complejidad. Debido a esto, las aplicaciones empotradas actualmente tienen más funciones y prestaciones, y como consecuencia de esto, una mayor complejidad. Por este motivo, existe un interés creciente en permitir la ejecución de múltiples aplicaciones de forma segura y sin interferencias en un mismo procesador y memoria. En este marco surgen las arquitecturas de sistemas particionados basados en hipervisores como una solución apropiada para construir sistemas seguros.

Uno de los principales retos en la construcción de sistemas particionados, es la verificación del correcto funcionamiento del hipervisor, dado que es el componente crítico sobre el que descansa la seguridad de todo el sistema particionado. Las técnicas tradicionales de V&V, como testing, inspección y análisis, presentan limitaciones para la verificación exhaustiva del comportamiento del sistema, debido a que el espacio de entradas a verificar crece de forma exponencial con respecto al número de entradas a verificar. Ante estas limitaciones las técnicas de verificación basadas en métodos formales surgen como una alternativa para completar las técnicas de validación tradicional.

Esta disertación se centra en la aplicación de métodos formales para validar la corrección del sistema particionado, en especial del hipervisor XtratuM. La validación de la metodología se realiza aplicando las técnicas propuestas a la validación del hipervisor. Para ello, se propone un modelo formal del hipervisor basado en máquinas de autómatas finitos, este modelo formal permite la definición de las propiedades que el diseño hipervisor debe cumplir para asegurar su corrección. Adicionalmente, esta disertación analiza cómo asegurar la corrección funcional de la implementación del hipervisor por medio de técnicas de verificación deductiva de código.

Por último, se estudian las vulnerabilidades de tipo *information leak* (CWE-200 [CWE08b]) debidas a la perdida de la confidencialidad de la información manejada en el sistema particionado. En este ámbito se modelan las vulnerabilidades, se aplican técnicas de análisis de código para la detección de vulnerabilidades en base al modelo definido y por último se valida la técnica propuesta por medio de un caso práctico sobre el núcleo del sistema operativo Linux que forma parte del sistema particionado.

## Resum

La disponibilitat de nous processadors amb major potencia de còmput per a aplicacions empotrades ha permès el desenvolupament de aplicacions que aborden problemes de major complexitat. Degut a açò, les aplicacions empotrades actualment tenen més funcions i prestacions, i com a conseqüència, una major complexitat. Per aquest motiu, existeix un interès creixent en per permetre la execució de múltiples aplicacions de forma segura i sense interferències en un mateix processador i memòria. En aquest marc sorgeixen les arquitectures de sistemes particionats basats en hipervisors com una solució apropiada per a la construcció de sistemes segurs

Un dels principals reptes en la construcció de sistemes particionats, es la verificació del correcte funcionament del hipervisor, donat que aquest es el component crític sobre el que descansa la seguretat del sistema particionat complet. Les tècniques tradicionals de V&V, com són el testing, inspecció i anàlisi, presenten limitacions que fan impracticable la seva aplicació per a la verificació exhaustiva del comportament del sistema, degut a que el espai de entrades a verificar creix de forma exponencial amb el nombre de entrades a verificar. Front a aquestes limitacions les tècniques de verificació basades en mètodes formals sorgeixen com una alternativa per a completar les tècniques de validació tradicional.

Aquesta dissertació es centra en la aplicació de mètodes formals per a validar la correcció del sistema particionat, en especial d del hipervisor XtratuM. La validació de la metodología es realitza aplicant les tècniques proposades a la validació del hipervisor. Per a aquest fi, es proposa un model formal del hipervisor basat en màquines de estats finits (FSM), aquest model formal permet la definició de les propietats que el disseny del hipervisor deu de complir per assegurar la seva correcció. Addicionalment, aquesta dissertació analitza com assegurar la correcció funcional de la implementació del hipervisor mitjançant tècniques de verificació deductiva de codi.

Per últim, s'estudien les vulnerabilitats de tipus *information leak* (CWE-200 [CWE08b]) degudes a la pèrdua de la confidencialitat de la informació gestionada per el sistema particionat. En aquest àmbit, es modelen les vulnerabilitats, s'apliquen tècniques de anàlisis de codi per a la detecció de les vulnerabilitats en base al model definit, per últim es valida la tècnica proposada mitjançant un cas pràctic sobre el nucli del sistema operatiu Linux que forma part de l'arquitectura particionada.

| Co  | ver   |                                                                                                                 | 1         |

|-----|-------|-----------------------------------------------------------------------------------------------------------------|-----------|

| Ac  | knov  | wledgements                                                                                                     | 3         |

| Ab  | ostra | ct                                                                                                              | 5         |

| Re  | sum   | en                                                                                                              | 7         |

| Re  | sum   | L Contraction of the second | 9         |

| Co  | nten  | nts                                                                                                             | 14        |

| Lis | st of | Figures                                                                                                         | 15        |

| Lis | st of | Tables                                                                                                          | 17        |

| Lis | st of | Listings                                                                                                        | 19        |

| 1   | Intr  | roduction                                                                                                       | <b>21</b> |

|     | 1.1   | Secure partitioned systems                                                                                      | 21        |

|     |       | 1.1.1 Secure hypervisors                                                                                        | 21        |

|     |       | 1.1.2 Validation and verification of secure hypervisors                                                         | 22        |

|     |       | 1.1.3 Challenges on the validation of secure hypervisors                                                        | 24        |

|     |       | 1.1.4 Terminology                                                                                               | 26        |

|     | 1.2   | Motivation and main goals                                                                                       | 26        |

|     | 1.3   | Contributions of this thesis                                                                                    | 26        |

|     | 1.4   | Outline of this thesis                                                                                          | 27        |

|     | 1.5   | Research Context                                                                                                | 28        |

| 2 | Sec | ure Hypervisor Verification                 | 29 |

|---|-----|---------------------------------------------|----|

|   | 2.1 | Formal methods in secure hypervisors        | 29 |

|   |     | 2.1.1 Deductive verification                | 29 |

|   |     | 2.1.2 Theorem provers                       | 30 |

|   |     | 2.1.3 Static code analysis                  | 31 |

|   | 2.2 | Formal methods in safety standards          | 32 |

|   |     | 2.2.1 RTCA Standards                        | 32 |

|   |     | 2.2.2 IEC-61508 Standards                   | 33 |

|   |     | 2.2.3 ECSS Standards                        | 33 |

|   |     | 2.2.4 Common Criteria Framework             | 34 |

|   | 2.3 | Summary                                     | 35 |

| 3 | Xtr | atuM foundations: A formalisation approach. | 37 |

|   | 3.1 | Introduction                                | 37 |

|   | 3.2 | XtratuM Overview                            | 38 |

|   |     | 3.2.1 XtratuM Architecture                  | 38 |

|   | 3.3 | Trustability enforcement                    | 39 |

|   |     | 3.3.1 Interrupt Model                       | 41 |

|   |     | 3.3.2 Fault Management Model                | 42 |

|   |     | 3.3.3 System specification                  | 43 |

|   | 3.4 | Hypervisor model                            | 45 |

|   |     | 3.4.1 Hypervisor state variables            | 47 |

|   |     | 3.4.2 General properties                    | 48 |

|   |     | 3.4.3 Spatial isolation properties          | 48 |

|   |     | 3.4.4 Temporal isolation properties         | 49 |

|   |     | 3.4.5 Hypervisor state management           | 50 |

|   |     | 3.4.6 Hypervisor pre- and post-conditions   | 50 |

|   | 3.5 | Conclusion                                  | 51 |

| 4 | For | mal Validation of XtratuM Components        | 53 |

|   | 4.1 | Introduction                                | 53 |

|   |     | 4.1.1 XtratuM Hypervisor core               | 54 |

|   | 4.2 | Deductive Formal Methods                    | 54 |

|   | 4.3 | Proposed Approach                           | 55 |

|   |     | 4.3.1  | Method                                             | 55 |

|---|-----|--------|----------------------------------------------------|----|

|   |     | 4.3.2  | Contract Specification                             | 56 |

|   |     | 4.3.3  | The Frama-C Framework                              | 56 |

|   | 4.4 | Appro  | ach Evaluation                                     | 57 |

|   |     | 4.4.1  | Code Refactor                                      | 57 |

|   |     | 4.4.2  | Contract Annotation                                | 57 |

|   |     | 4.4.3  | Proof Verification                                 | 58 |

|   |     | 4.4.4  | Proof Results                                      | 58 |

|   |     | 4.4.5  | Results                                            | 58 |

|   | 4.5 | Conclu | isions                                             | 59 |

| 5 | And | lucing | the Impact and Detection of Kernel Stack Infoleaks | 61 |

| J | 5.1 |        | uction                                             | 61 |

|   | 5.2 |        | d Work                                             | 62 |

|   | 0.2 | 5.2.1  | Protection Mechanisms                              | 62 |

|   |     | 5.2.2  | Protection Techniques                              | 63 |

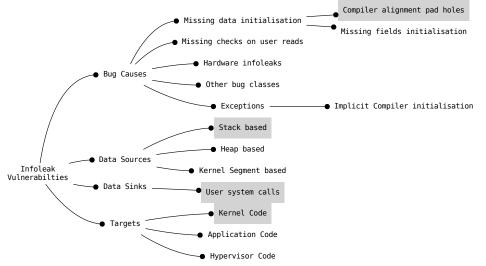

|   | 5.3 | -      | fication of Information Disclosure Vulnerabilities | 64 |

|   |     | 5.3.1  | The Anatomy Of An Infoleak                         | 64 |

|   |     | 5.3.2  | Targets of Infoleaks                               | 65 |

|   |     | 5.3.3  | Infoleaks Bug Causes                               | 65 |

|   |     | 5.3.4  | Infoleaks Data Sources                             | 66 |

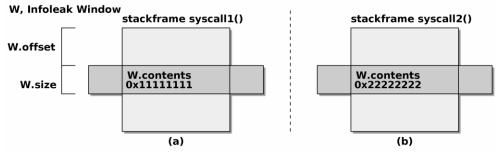

|   | 5.4 | Analys | sis on the Impact of Stack Infoleaks               | 67 |

|   |     | 5.4.1  | The Anatomy of An Attack                           | 67 |

|   |     | 5.4.2  | The Contents of the Kernel Stack                   | 68 |

|   |     | 5.4.3  | Infoleak Based Attacks                             | 69 |

|   | 5.5 | The D  | etection of Information Leak vulnerabilities       | 70 |

|   |     | 5.5.1  | Infoleak Vulnerability Model                       | 70 |

|   |     | 5.5.2  | Semantic Patch Preparation                         | 71 |

|   |     | 5.5.3  | Filter and Rank of matches                         | 71 |

|   |     | 5.5.4  | Infoleak Code Review and Correction                | 71 |

|   | 5.6 | Experi | imental Evaluation of the Detection Technique      | 72 |

|   |     | 5.6.1  | Existing Infoleak Detection                        | 72 |

|   |     | 5.6.2  | Discovery of Vulnerabilities                       | 72 |

|   |     | 5.6.3  | Applications and Limitations of our Approach       | 73 |

|   | 5.7 | Conclu | sions and Further Work                             | 73 |

| 6  | Con   | clusions and open research lines    | 75 |

|----|-------|-------------------------------------|----|

|    | 6.1   | Conclusions                         | 75 |

|    | 6.2   | Research Lines                      | 76 |

|    | 6.3   | Publications related to this thesis | 76 |

| Bi | bliog | raphy                               | 79 |

| A  | erony | <b>7ms</b>                          | 87 |

| G  | ossa  | ry                                  | 89 |

# List of Figures

| 1.1 | V&V phases on V Model Software Development Cycle                                   | 23 |

|-----|------------------------------------------------------------------------------------|----|

| 1.2 | Commercial-Off-The-Shelf (COTS) product components                                 | 25 |

| 1.3 | Contributions along the Hypervisor Software Development Life Cycle                 | 27 |

| 2.1 | Formal methods applied to hypervisor verification.                                 | 30 |

| 3.1 | XtratuM architecture.                                                              | 39 |

| 3.2 | Interrupt model.                                                                   | 41 |

| 3.3 | XtratuM deployment.                                                                | 44 |

| 3.4 | Finite set of states.                                                              | 47 |

| 3.5 | State variables.                                                                   | 48 |

| 4.1 | XtratuM architecture.                                                              | 54 |

| 5.1 | Identification and Classification of the Infoleak vulnerabilities.                 | 65 |

| 5.2 | Directions of data flow in kernel information leaks and writes.                    | 67 |

| 5.3 | Stack Layout on function call relative to ebp (x86-32). $\ldots$ $\ldots$ $\ldots$ | 69 |

| 5.4 | Kernel stackframe infoleak window                                                  | 70 |

# List of Tables

| 2.1 | DO-178B/ED-12B Criticality Levels Overview                                       | 33 |

|-----|----------------------------------------------------------------------------------|----|

| 2.2 | IEC 61508 Safety Integrity Level (SIL).                                          | 33 |

| 2.3 | Common Criteria Evaluation Assurance Level                                       | 34 |

| 2.4 | Common Criteria Assurance levels.                                                | 34 |

| 2.5 | Safety-critical standards summary.                                               | 35 |

|     |                                                                                  |    |

| 4.1 | Coverage of contracts.                                                           | 58 |

| 4.2 | Proof verification results.                                                      | 59 |

|     |                                                                                  |    |

| 5.1 | Stack Layout on function call() relative to %ebp (x86-32) $\ldots \ldots \ldots$ | 68 |

| 5.2 | Statistical performance of stack infoleak detection per kernel version           | 72 |

|     |                                                                                  |    |

| 6.1 | Listing of main publications of this dissertation                                | 77 |

# List of Listings

| 4.1 | memset function annotated for verification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | XtratuM code properties verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58 |

| 5.1 | Example of infoleak code from CVE-2013-2147 (edited to fit) $\hdots \ldots \hdots \hdd$ | 64 |

| 5.2 | Semantic patch (SmPL) for stack based infoleak detection (edited to fit) $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71 |

# CHAPTER 1 Introduction

This chapter introduces the main topics addressed in this dissertation. First, the section 1.1 presents the topics of secure hypervisors construction and validation. Next, the section 1.2 details the main motivation and objectives of the work followed by our contributions section 1.3. Last, the section 1.4 defines the outline, and section 1.5 sets the research context where this work has been performed.

## **1.1** Secure partitioned systems

The increasing complexity of current software systems complicates its exhaustive V&V by means of traditional validation techniques, such as testing, analysis and inspection  $[D^+09]$ . This is caused by the fact that the size of the input space to validate grows exponentially with the number of inputs, making impracticable the exhaustive validation of the input space as the number of inputs to test increases. In this context, the V&V techniques based on formal methods arise as an alternative that complements traditional V&V techniques, and, enable to reduce the input space, by means of abstract execution and state-space reduction techniques.

The study of the security vulnerability history of current operating systems  $[CMW^{+}11]$  provides insight about the defects that affect the security and quality of current operating systems. These defects can lead to: (1) Failures in critical systems, that affect the safety of humans. (2) Security breaches in systems used by companies and government institutions. (3) Security issues in the widespread consumer services and devices, such as: mobile phones, laptops, servers, routers, ...

In the above scenario, this thesis focuses on the analysis of the secure hypervisors (subsection 1.1.1), and, the application of formal validation methods (subsection 1.1.2) to improve the hypervisors security.

### 1.1.1 Secure hypervisors

The availability of new processors for embedded applications has raised new possibilities for these applications. Now, the embedded applications have more functionalities and, as consequence, more complexity. There exist a growing interest in enabling multiple applications to share a single processor and memory. To facilitate such a model the execution time and memory space of each application must be protected from other applications in the system.

Partitioned software architectures represent the future of secure systems. They have evolved to fulfill security and avionics requirements where predictability is extremely important [fAR12].

The separation kernel proposed by Rushby et al. [Rus81a] established a combination of hardware and software to allow multiple functions to be performed on a common set of physical resources without interference. The MILS initiative is a joint research effort between academia, industry, and government to develop and implement a high-assurance, real-time architecture for embedded systems. The technical foundation adopted for the so-called MILS architecture is a separation kernel. Also, the ARINC-653 standard [Ai96] uses these principles to define a baseline operating environment for application software used within IMA, based on a partitioned architecture.

The idea behind a partitioned system is the virtualization. This idea is present in current operating systems: processor and memory are multiplexed to processes. A physical computer is partitioned into several logical partitions, each of which looks like a real computer. Each of these partitions can have an operating system installed on it, and function as if it were a completely separate machine. Virtual machine technology can be considered a secure and efficient way to build partitioned systems. A virtual machine (VM) is a software implementation of a machine (computer) that executes programs like a real machine. **Hypervisor** (also known as VMM [Gol74]) is a small layer of software (or a combination of software/hardware) that enables to run several independent execution environments or partitions in a single computer. The key difference between hypervisor technology and other kinds of virtualisation (such as Java virtual machine or software emulation) is the performance.

The low overhead and the reduced size of the hypervisor can be considered as an appropriated solution to achieve secure systems if it is designed following strict design criteria to meet security requirements. Its correctness can be sufficient to ensure the security of the system as a whole or, at least, the security of a set of trusted partitions. In a partitioned system, the partitions can accommodate different kinds of applications: real-time, trusted, non trusted, etc.

The concept of partitioned software architectures [Rus01] was developed to address security and safety issues. The central design criteria behind this concept consists in isolating modules of the system in *partitions*. The temporal and spatial isolation properties of the partitioned software architectures are the key aspects in partitioned systems. Therefore, the validation and verification of the hypervisor properties are fundamental, and, are introduced in the next subsection 1.1.2.

### 1.1.2 Validation and verification of secure hypervisors

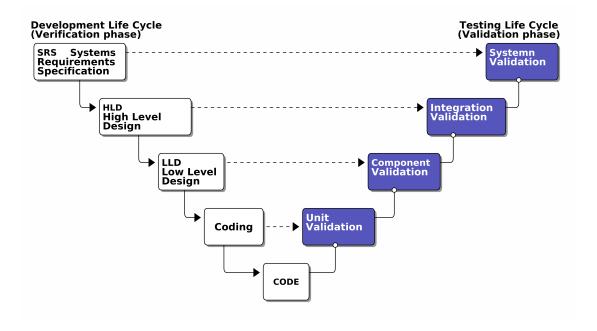

The V-Model software development cycle schedules phases  $[BF^{+}14, \$7]$  for the construction and verification of the software product. The verification phases are counterparts of the construction phases that verify that the outputs of each phase are correctly built using an incremental approach, these are depicted in blue in Figure 1.1. In the V-Model, the traditional V&V phases are performed by means of testing, inspection and analysis activities  $[BF^{+}14, \$10]$  to achieve the defined testing objectives:

• Traditional System verification activities.

System testing activities consists in the specification and development of a testsuite that checks the system specification (system requirements).

• Traditional Integration verification activities.

Integration testing activities consist in the specification and development of a testsuite that checks the components specification (component contracts).

Figure 1.1: V&V phases on V Model Software Development Cycle

• Traditional Unit verification activities.

Unit testing activities consist in the specification and development of a testsuite that check the units specification (function contracts).

For each testing activities, the testing objectives are defined based on risk, criticality and prioritization analysis. Each of the testing objectives are defined in terms of: (1) Testing the whole functionality offered by the component/unit, and, (2) Ensuring that the execution of testsuite reaches a high structural code coverage value (typically above 90%). However, these objectives alone are not considered sufficient to ensure high confidence on the robustness of the software product being built [IH14].

In addition to the traditional V&V activities presented above, formal methods  $[BF^{+}14, §4]$  arise as an alternative to complement traditional V&V activities to address the limitations and challenges of V&V (subsection 1.1.3). Formal methods can be applied along the V&V phases of the V-Model, depicted in Figure 1.1:

• Formal System verification activities.

System verification activities consists in the use of formal methods to check the system specification (system requirements) against a formal model.

• Formal Integration verification activities.

Integration verification activities consist in the use of formal methods to check the implementation of software components against a specification of the component contracts [Mey92]. • Formal Unit verification activities.

Unit verification activities consist in the use of formal methods to check the implementation of software units against a specification of the unit (functions) contracts [Mey92].

This work addresses the use of formal methods for the Validation and Verification.

#### 1.1.3 Challenges on the validation of secure hypervisors

This section analyses the main challenges and causes that difficult the validation of secure hypervisors. Next, we discuss each of the identified challenges in a separate paragraph.

#### The Complexity of Secure Hypervisors

The Complexity of current software systems is a key challenge to overcome in the construction of secure hypervisor systems  $[D^+09]$ , since complexity of software systems directly relates to the validation complexity. The analysis of software complexity identifies two types of complexity that contribute to the increase of the complexity  $[D^+09, \S A, p. 32]$ :

- (1) Essential complexity: Complexity essential to the problem to solve.

- (2) *Incidental complexity*: Complexity non-essential introduced by the approach selected to solve the problem.

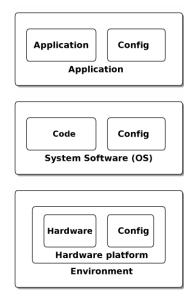

The analysis of incidental complexity  $[D^+09$ , on COTS] notes that the use of COTS can contribute to the complexity of software products. COTS components are used as a way to reduce costs and risks by utilizing well-tested components. This is the trend of current hypervisors [Xen, Vxworks, pikeos, ...] which are designed as COTS components. However, for COTS components to remain widely applicable need to remain highly adaptable and configurable to different application contexts, to achieve this goal COTS feature multiple components. We can identify three main state spaces that contribute to complexity depicted in Figure 1.2:

- *Input state space*, that comprises all the combinations of calls of the offered services, e.g.: call service(parameters).

- *Configuration space*, that comprises all the combinations of build time configuration parameters.

- *Environment space*, that comprises all the combinations of environments where the system runs.

Each of the above state spaces contribute to the Equation 1.1 of the complexity (C) of the system depicted in Figure 1.2:

$C(product) = C(application) \times C(code \times code\_cfg) \times C(hardware \times hardware\_cfg) \quad (1.1)$

#### The difficulties of exhaustive testing for validation purposes

Based on the above complexity analysis and performing some back-of-the-envelope calculations of the size of the state space under test:

Figure 1.2: COTS product components

- Input API state space: Is the state space that consists of all the possible API call input parameters combinations. For a typical 32-bit based CPU with an small API of 30-50 services each one receiving between 1 an 5 input parameters (Linux sports 300 system calls). The total number of combinations to test exhaustively would yield a total of  $50 * (2^{32})^5$  tests to be performed. Then assuming a rate of 1000 tests/second requires  $8 * 10^{46}$  seconds, or  $2 * 10^{39}$  years, that is not feasible.

- System Configuration state space: Is the state space that consists of all the possible configuration parameters that determine the behaviour of software, this configuration parameters, refer mainly configuration parameters that are fixed at build time.

- Environment state space: Is the state space that consists of combinations of environments where the system runs, that is, hardware platforms, etc.

Notice that we are not considering each of the state spaces separately, but the complete state space is the Cartesian product of the state spaces:  $input \times config \times environment$  that results in a greater state space.

The main conclusion drawn is that due to the great size of the state space <sup>1</sup> traditional validation techniques alone can only test a subset of the state space, therefore, leaving untested areas of the state space, that contribute to untested and potentially faulty behaviour in the program space [And86]. Additionally, when considering traditional V&V testing is important to consider that: "testing alone can only be used to show the presence of defects, however, it can never be used to show the complete absence of defects" [DDH72].

<sup>&</sup>lt;sup>1</sup>There exist testing techniques that enable to reduce the size of the input space, such as equivalence partitioning  $[BF^{+}14, §3.2.1]$ , by considering only a subset of the input space to test. But this reduction comes at the cost of assuming equivalence of behaviour for similar inputs as a justification to not test those inputs.

### 1.1.4 Terminology

The main topic of this work is the validation of secure hypervisors by means of formal methods. Therefore, a common ground for terms used in this work is required. Where possible we have employed definitions coming from standard bodies and institutions as the Institute of Electrical and Electronics Engineers (IEEE), otherwise, we provide references to the research works that define the terms we used. Through the rest of this work we use: (1) The dependability and security definitions from by Avizienis taxonomy et al. [ALRL04]. (2) The software engineering, specially validation and verification terminology refers to the IEEE Software Engineering Book (SWEBOOK) [BF<sup>+</sup>14, oEE90]. Last, a glossary of the terms and acronyms used through this work is available at section 6.3.

# **1.2** Motivation and main goals

The main challenges in the validation of secure hypervisors are identified in subsection 1.1.3, and are the main motivation for our work, these are summarised below:

- 1. The increasing complexity of secure software systems subsection 1.1.3.

- 2. The difficulties of traditional validation techniques for the exhaustive validation of complex software systems subsection 1.1.3.

- 3. The inevitability of failures in complex operating systems [LSM<sup>+</sup>98].

#### Main goals

The above challenges define the main objectives of the thesis, and, have encouraged us to propose solutions that address them: (1) The use of formal models to define the correctness properties of the hypervisor design. (2) The use of source code analysis techniques to verify the functional correctness of the hypervisor implementation. (3) The definition of formal models to detect information disclosure vulnerabilities (infoleaks) that compromise the confidentiality of the information managed on a secure system.

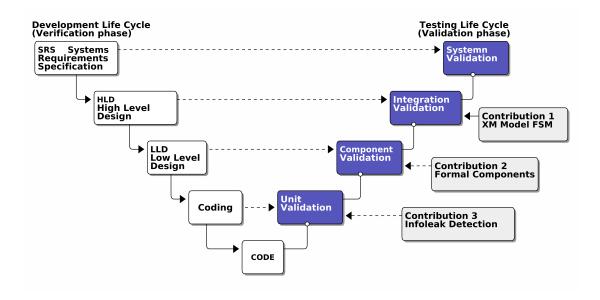

# **1.3** Contributions of this thesis

This thesis proposes formal methods for hypervisors verification that complement traditional V&V approaches. The contributions are presented in the order in which these apply through the software development cycle (subsection 1.1.2) as depicted in Figure 1.3. The main contributions of this thesis are:

1. At the integration validation (HLD).

The first contribution is the proposal of a formal model of the secure hypervisor, and the definition of the properties that ensure its correctness in chapter 3.

2. At the component validation (LLD).

The second contribution is the proposal of an approach for the verification of the functional correctness of the hypervisor components implementation, by applying deductive analysis techniques to the components source-code in chapter 4.

3. At the unit validation (Coding)

The third contribution is the security analysis, characterization and detection of the vulnerabilities that affect the confidentiality of the information managed by secure hypervisors in chapter 5.

Figure 1.3: Contributions along the Hypervisor Software Development Life Cycle

# 1.4 Outline of this thesis

The contributions are presented in the order in which these apply through the V&V phases of the software development cycle as depicted in Figure 1.3. With the above structure in mind, the remainder of the thesis is organised as follows:

First, the chapter 2 surveys the current state of art in the V&V of secure hypervisors using formal methods. Then, the chapter 3 proposes an approach to ensure the correctness of the hypervisor based in the formal modelling of the hypervisor using FSM and the definition of the properties that the secure hypervisor must meet.

Next, the chapter 4 applies deductive verification techniques to the hypervisor components source code to ensure the functional correctness.

The chapter 5 analyses the security impact of the confidentiality vulnerabilities in the security of the partitioned system, then proposes and evaluates source code static analysis techniques to the detection of vulnerabilities that affect the confidentiality (*information leaks*) of the information managed by the components of the partitioned system.

Last, the chapter 6 summarises the main contributions of this thesis, presents the final conclusions and the open research lines that derive from this dissertation.

# 1.5 Research Context

This thesis has been developed in the context of the following research projects focused on the industrialization of secure hypervisor technologies.

• DREAMS: Distributed REal-time Architecture for Mixed Criticality Systems.

The main goal is to develop a cross domain architecture and design tools for networked complex systems where application subsystems of different criticality, executing on networked multi core chips.

• MultiPARTES: Multi-cores Partitioning for Trusted Embedded Systems.

The main goal is the development tools and solutions for building trusted embedded systems with mixed criticality components on multi core platforms.

• OVERSEE: Open Vehicular Secure Platform

The overall goal of OVERSEE is to contribute to the efficiency and safety of road transport by developing the OVERSEE platform, which will provide a secure, standardized and generic communication and application platform for vehicles.

• HI-PartES: High Integrity Partitioned Embedded Systems

The main goal of HI-PartES is the development of a execution platform providing virtualisation, and the development of tools oriented to model the development of high integrity partitioned systems.

In the above research context, the techniques presented in this dissertation have contributed to improve the quality of the developed software products. In addition, the results of this thesis have been presented in national and international publications, that are listed in chapter 6.

# Chapter 2 Secure Hypervisor Verification

This chapter present the current state of the art in the construction of secure hypervisors using formal verification techniques. First, the section 2.1 presents the approaches that are applied currently to the formal verification of hypervisors. Next, the section 2.2 presents the application of formal methods in safety critical standards. Last, the section 2.3 summarises the conclusions of the chapter, that motivate the main contributions of this dissertation.

# 2.1 Formal methods in secure hypervisors

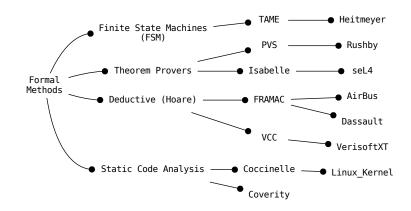

Formal validation of operating systems has been an on going research topic on operating systems [Rus81b] to achieve the security and safety critical objectives mandated by the safety standards [fAR92, Cri12, IEC10] to reach the assurance levels required for the industrial qualification of the system. The exhaustive verification of software systems by means of formal methods, presents various advantages over traditional validation techniques: (1) The formal verification enables the exhaustive verification of software in an automated way. (2) The formal verification reduces the number of defects found during after deployment. (3) The above two advantages lead to reduce the development costs of validation and testing phases in software projects.

The wide adoption of the virtualisation technologies, and its implantation in critical systems as solutions to provide fault isolation, has led to the application of formal methods for the validation of hypervisors. Next, we review the use of formal methods for the validation of secure hypervisors on the open literature. These are grouped in three main groups according to the formal verification theories applied (Figure 2.1):

- subsection 2.1.1 Deductive verification

- subsection 2.1.2 Theorem provers

- subsection 2.1.3 Static code analysis

### 2.1.1 Deductive verification

Baumann et al. [BBBB10] perform the formal verification of the PikeOS microkernel to reach Common Criteria (CC) qualification [Cri12]. The objective is the application of the source code deductive techniques to verify the functional correctness of the PikeOS microkernel. The authors achieve their objective by using the *Verifying C compiler (VCC)* [CDH<sup>+</sup>09] that enables the

Figure 2.1: Formal methods applied to hypervisor verification.

deductive verification of the microkernel code annotated with function contracts to ensure the functional correctness.

Souyris et al. [SWDD09] present a methodology for the integration of formal verification techniques in the development cycle of the avionics software products developed at AirBus. The objective of the work is qualifying the software products for DO-178B [fAR92]. To achieve the objective the authors apply source code deductive verification techniques [CKK<sup>+</sup>12] during the software V&V phases of the Software Development Life Cycle (SDLC).

D. Pariente et al. [PL10] present the results and lessons learn on the application of source code verification techniques  $[CKK^{+}12]$  for the verification of Industrial C code developed at Dassault Aviation.

Frama-C [CKK<sup>+</sup>12] is an open-source static analysis tool that targets ANSI C programs, constructed with a plugin architecture. That allows one to connect different kinds of analysis tools together such that they can cooperate and provide precise results. Frama-C is based on the work of Hoare [Hoa69].

#### 2.1.2 Theorem provers

Klein et al. [KEH<sup>+</sup>09] perform the formal verification of the seL4 microkernel. The objective of the work is to prove functional correctness of the hypervisor implementation with respect to an abstract hypervisor specification. The target of the verification is a simplified version of the seL4 hypervisor for the ARM architecture, that is comprised of 8700 C Source Lines of Code (SLOC) and 600 assembly SLOC. The verification is performed using the Isabelle [Pau94] theorem prover, to prove the functional correctness required to reach the Evaluation Assurance Level 7 (EAL7) of the CC standard [Cri12]. The presented approach makes the following assumptions: (1) correctness of compiler, assembly code and hardware.

Heitmeyer et al. [HALM08] present the formal verification of security properties on the ED (Embedded Device). The objective is to prove the security properties of the ED to reach CC certification [Cri12]. To achieve the objective the authors present an innovative approach that reduces the verification costs by means of code partitioning techniques based of the criticality of the code to verify. This has the main benefit of reducing the amount of critical code to verify to

the 10% of the total. Additionally, the approach presented enables the use of the theorem prover PVS [ORS92] based on annotations of the security properties to verify on the source code.

### 2.1.3 Static code analysis

J. L. Lawall et al. developed Coccinelle  $[LBP^+09]$  a tool that performs control-flow based program searches and transformations in C code. Coccinelle is actively used to perform API evolutions and identify defects on the Linux kernel  $[LBP^+09]$ .

Coverity Prevent [Cov02] is a source code static analysis tool developed by Coverity. The tool was originated at Stanford META/xgcc project to find defects in source-code, the authors evaluate the tool effectiveness on finding defects on open-source projects ranging from OpenSSL to the Linux Kernel [CEH02].

## 2.2 Formal methods in safety standards

This section surveys and analyzes the application of formal methods on safety-critical standards. The survey targets the field of software development of safety-critical systems [ALRL04] and is based on the work of J. Bowen [Bow93]. Due to the nature of safety-critical systems, the majority of standards are safety related, however, security related standards as CC [Cri12] have also been considered. The selection, which is summarized in Table 2.5, although incomplete (as there are more than 170 safety standards [Bow93]), considers the current developments in the areas of certification of secure hypervisors:

- (1) Avionics: Requirements and Technical Concepts for Aviation (DO-178B).

- (2) Space industry: European Cooperation for Space Standardization (ECSS).

- (3) Industrial: International Electro-technical Commission (IEC).

- (4) Information Technologies (IT) security: CC.

### 2.2.1 RTCA Standards

The US Radio Technical Commission for Aeronautics (RTCA) produced a guideline on Software Considerations in Airborne Systems and Equipment Certification (DO-178A) [fAR85] and defines five Safety Levels ranging from Level E (lowest) to Level A (highest) (see Table 2.1). Initially DO-178A did not explicitly recognise formal methods as part of accepted practice. However, the DO-178B [fAR92] guideline was updated in 1992 and completely rewritten to include a very brief reference to formal methods in [fAR92, subsection 12.3.1] This gives a general introduction to formal methods and mentions three levels of rigour: (1) formal specification with no proofs, (2) manual proofs and (3) automatically checked or generated proofs. It is now possible for a manufacturer following the DO-178B guideline to make use of formal methods in the context of aircraft certification, although it is incumbent on the manufacturer to justify its use.

In the latest update to the DO-178C guideline the RTCA has also issued separate guideline that specifically cover the use of formal methods DO-333 [fAR11]. Additionally, this update considers other techniques for achieving certification, as the robust partitioning techniques Integrated Modular Avionics (IMA) Development Guidance and Certification Considerations (DO-297) in [fAR05].

|   | Failure<br>Condition | Description                                                                                                         |

|---|----------------------|---------------------------------------------------------------------------------------------------------------------|

| Ā | Catastrophic         | Failure may cause multiple fatalities, usually with loss of the airplane (Extremely improbable).                    |

| В | Hazardous            | Failure has a large negative impact on safety or performance, causing serious or fatal injuries (Extremely remote). |

| С | Major                | Failure significantly reduces the safety margin or significantly increases crew workload (Remote).                  |

| D | Minor                | Failure slightly reduces the safety margin or slightly increases crew workload (Probable).                          |

| Е | No effect            | Failure has no impact on safety, aircraft operation, or crew workload (Not applicable).                             |

| Failure<br>Condition | Description |  |  |

|----------------------|-------------|--|--|

|                      |             |  |  |

Table 2.1: DO-178B/ED-12B Criticality Levels Overview

### 2.2.2 IEC-61508 Standards

The IEC has issued a standard Functional Safety of Electrical/Electronic/Programmable Electronic Safety-related Systems (IEC-61508) [IEC10]. This is an international standard focusing on the functional security of electrical/electronic/programmable devices. This is a generic international standard (umbrella standard) which is designed to be applied to several industrial sectors, some instantiations of the IEC-61508 are: (1) Automotive (ISO 26262), (2) Railway (EN/CELENEC 50128) and (3) Process Industry (IEC 61511). These standard was originally issued in 1989, but have subsequently been updated and reissued. Is concerned with the functional safety of programmable electronic systems in general.

The [IEC10] standard is organized in several parts covering the Functional Safety of Safety-Related Systems, amongst them: (1) Generic requirements; (2) Requirements for electronic/electronic/programmable systems; and (3) Software requirements. The formal methods CCS, CSP, HOL, LOTOS, OBJ, Temporal Logic, VDM and Z are specifically mentioned in [IEC10] as possible techniques to be applied in the development of safety-critical systems in an extensive section [IEC10, B.30, pp. B-14 B-18].

| SIL  | Failure prob. per hour (systems active>once per year) | Failure prob. per demand (systems active <once per="" th="" year)<=""></once> |

|------|-------------------------------------------------------|-------------------------------------------------------------------------------|

| SIL1 | $10^{-6} - 10^{-5}$                                   | $10^{-1} - 10^{-2}$                                                           |

| SIL2 | $10^{-7} - 10^{-6}$                                   | $10^{-2} - 10^{-3}$                                                           |

| SIL3 | $10^{-8} - 10^{-7}$                                   | $10^{-3} - 10^{-4}$                                                           |

| SIL4 | $10^{-9} - 10^{-8}$                                   | $10^{-4} - 10^{-5}$                                                           |

Table 2.2: IEC 61508 SIL.

#### 2.2.3 ECSS Standards

The European Space Agency (ESA) has issued guidelines for software engineering standards: ECSS-E-40 [ECS09a] is the ECSS standard for software engineering. ECSS-Q-80 [ECS09b] is the ECSS standard for software Product Assurance. They are both based on ISO/IEC 12207.

These suggests that formal methods such as Z or VDM should be considered for the specification of safety-critical systems in the Software Requirement Document . A short section on formal proof suggests that proof of the correctness of the software should be attempted if practicable. Because of the possibility of human error, proofs should be checked independently. Methods such as formal proof should always be tried before testing is undertaken. This the use of formal

methods is strongly recommended, but not mandated by the document.

#### 2.2.4 Common Criteria Framework

The CC [Cri12] is a framework that allows the rigorous specification of security and assurance requirements, that are implemented by vendors in their products, and evaluated by testing laboratories to determine if the products meet their requirement claims. The CC defines seven Evaluation Assurance Level (EAL), which range from EAL1 (lowest) to EAL7 (highest) assurance level (see Table 2.4). The Table 2.4 presents the formal methods requirements at each assurance level, where formal methods are mandated to achieve the certification of the highest levels: EAL6 and EAL7.

| EAL  | Description                                                                                            |

|------|--------------------------------------------------------------------------------------------------------|

| EAL1 | Functionally tested, security threats not serious                                                      |

| EAL2 | Structurally tested, low to moderate assurance                                                         |

| EAL3 | Methodically tested and checked, maximum assurance without infringing sound                            |

| EAL4 | Methodically designed, tested and reviewed, maximum assurance compatible with good commercial practise |

| EAL5 | Semi-formally designed and tested, maximum assurance with moderate security engineering                |

| EAL6 | Semi-formally verified design and tested, protect high value assets against significant risk           |

| EAL7 | Formally verified design and tested, extremely high risk situations and/or high assets values          |

| CC   | Requirement | Specification | Design      | Implementation |  |

|------|-------------|---------------|-------------|----------------|--|

| EAL1 | Informal    | Informal      | Informal    | Informal       |  |

| EAL2 | Informal    | Informal      | Informal    | Informal       |  |

| EAL3 | Informal    | Informal      | Informal    | Informal       |  |

| EAL4 | Informal    | Informal      | Informal    | Informal       |  |

| EAL5 | Formal      | Semi-formal   | Semi-formal | Informal       |  |

| EAL6 | Formal      | Semi-formal   | Semi-formal | Informal       |  |

| EAL7 | Formal      | Formal        | Formal      | Informal       |  |

Table 2.3: Common Criteria Evaluation Assurance Level

Table 2.4: Common Criteria Assurance levels.

# 2.3 Summary

This section analyses the information of the survey to conclude the position of the standards regarding formal methods, which is summarized in table 2.5.

| Standard  | Formal<br>Methods | Organization | Sector     | Country       | Year |

|-----------|-------------------|--------------|------------|---------------|------|

| DO-178C   | Recommended       | RTCA         | Avionics   | USA           | 2012 |

| IEC-61508 | Recommended       | IEC          | Industrial | Europe        | 2010 |

| ECSS-E-40 | Recommended       | ESA          | Space      | Europe        | 2009 |

| CCV3.1R4  | Recommended       | ISO/IEC      | IT         | International | 2012 |

Table 2.5: Safety-critical standards summary.

- **DO-178C**: Formal methods are explicitly considered as a complement to dynamic testing, that can be presented as evidences for certification. Additionally, formal methods (DO-333) and robust partitioning techniques (DO-297) are specifically addressed on separate guidelines.

- IEC 61508: Formal methods are "highly recommended" to achieve SIL4, while are "recommended" to achieve the lower SIL2 and SIL3 safety levels [IEC10, part 3]

- EN 50128 (railway): Formal methods are "highly recommended" to achieve SIL3 and SIL4, while they're "recommended" to achieve SIL1 and SIL2.

- ISO 26262 (automotive): Formal methods are "recommended" to achieve ASILB, ASILC and ASILD.

- ECSS-E-40: Formal methods are "recommended" as supplementary or replacement of the existing practices defined in [ECS09a].

- CCV3.1R4: Formal methods are "mandated" for EAL7 and semi-formal methods are "mandated" for Evaluation Assurance Level 6 (EAL).

The main conclusion to be drawn is that the surveyed standards recommend the use of formal methods to achieve the highest safety levels, and for highly critical applications formal methods are mandatory.

## CHAPTER 3

## XtratuM foundations: A formalisation approach.

Partitioned software architectures represent the future of secure systems. They have evolved to fulfill security and avionics requirements where predictability is extremely important.

The idea behind a partitioned system is the virtualization. A virtual machine (VM) is a software implementation of a machine (computer) that executes programs like a real machine. A Hypervisor (also known as virtual machine monitor) is a layer of software (or a combination of software/hardware) that enables to run several independent execution environments or partitions in a single computer. Hypervisor is a new and promising technology which can be designed to meet safety and security properties. In order to achieve these properties, the hypervisor has to follow strict design criteria and be modeled using a formal approach.

In this chapter first, the XtratuM hypervisor is presented, next, we present our contribution: an attempt to extend the trusted environment from the hardware level to the hypervisor level on the basis of preserving the temporal and spatial isolation properties.

## 3.1 Introduction

The availability of new processors for embedded applications has raised new possibilities for these applications. Now, the embedded applications have more functionalities and, as consequence, more complexity. There exist a growing interest in enabling multiple applications to share a single processor and memory. To facilitate such a model the execution time and memory space of each application must be protected from other applications in the system.

Partitioned software architectures represent the future of secure systems. They have evolved to fulfill security and avionics requirements where predictability is extremely important. The separation kernel proposed in [Rus81a] established a combination of hardware and software to allow multiple functions to be performed on a common set of physical resources without interference. The MILS (Multiple Independent Levels of Security and Safety) initiative is a joint research effort between academia, industry, and government to develop and implement a high-assurance, real-time architecture for embedded systems. The technical foundation adopted for the so-called MILS architecture is a separation kernel. Also, the ARINC-653 [ Ai96] standard uses these principles to define a baseline operating environment for application software used within Integrated Modular Avionics (IMA), based on a partitioned architecture.

Virtual machine technology can be considered the most secure and efficient way to build partitioned systems. A virtual machine (VM) is a software implementation of a machine (computer) that executes programs like a real machine. **Hypervisor** (also known as virtual machine monitor

VMM [Gol74]) is a small layer of software (or a combination of software/hardware) that enables to run several independent execution environments or partitions in a single computer. The key difference between hypervisor technology and other kind of virtualisation (such as java virtual machine or software emulation) is the performance. In bare-machine hypervisors the overhead can be very low maintaining the throughput of the virtual machines very close to the native hardware. Hypervisor is a new and promising technology, but has to be adapted and customized to the requirements of the target application.

The low overhead and the reduced size of the hypervisor can be considered as an appropriated solution to achieve secure systems if it is designed following strict design criteria to meet security requirements. Its correctness can be sufficient to ensure the security of the system as a whole or, at least, the security of a set of trusted partitions. In a partitioned system, the partitions can accommodate different kinds of applications: real-time, trusted, non trusted, etc. As consequence, the partition's operating system can be customised to provide the specific services to its applications.

In this chapter we present a solution for partitioned based on a bare-metal hypervisor called XtratuM. The XtratuM hypervisor has been designed specifically for critical real-time systems following a set of requirements for secure space applications and a set of services to build applications based on the ARINC-653 standard

In the next section, we present a review of the virtualisation techniques with special emphasis in the real time characteristics. Section 3.2 presents the main design criteria. Also, we analyse the processor dependencies and the virtualised services to the partitions. Section 3.2.1 describes the hypervisor architecture and the services provided to the partitions. It also provides a model for interrupt and fault management to the partitions. Finally some conclusions are enumerated.

# 3.2 XtratuM Overview

XtratuM [MRC05] has been designed to achieve temporal and spatial requirements of safety critical systems. It is being used as TSP-based solution for payload on-board software, highly generic and reusable, in space applications [AMGC09] by CNES using the LEON2 [Res05] processor. TSP (Time and Space Partitioning) based architecture has been identified as the best solution to ease and secure reuse, enabling a strong decoupling of the generic features to be developed, validated and maintained in mission specific data processing [AM08].

LEON2 processor is a 32-bit processor core based on the SPARC V8 architecture suitable for system-on-a-chip (SOC) designs, which can be synthesized in an FPGA. It is used by the European Space Agency and has successfully been used in various commercial and research endeavors.

## 3.2.1 XtratuM Architecture

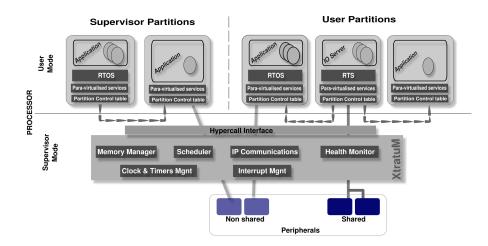

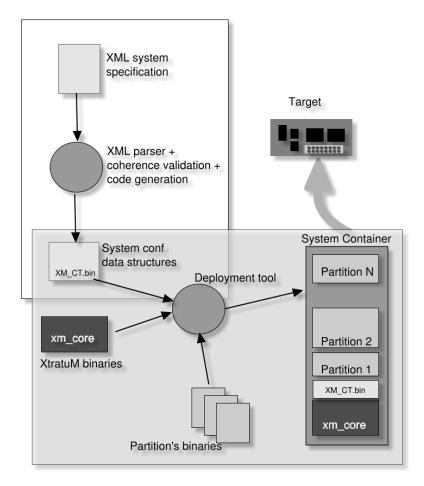

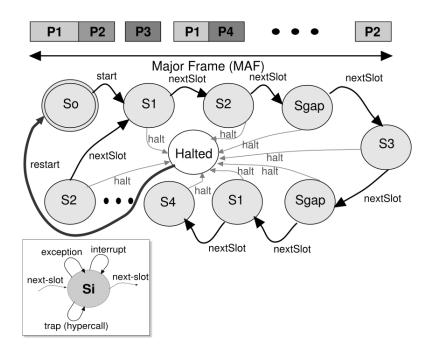

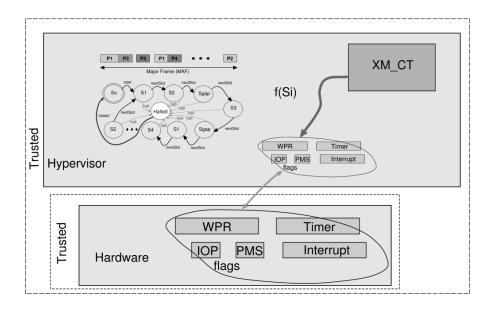

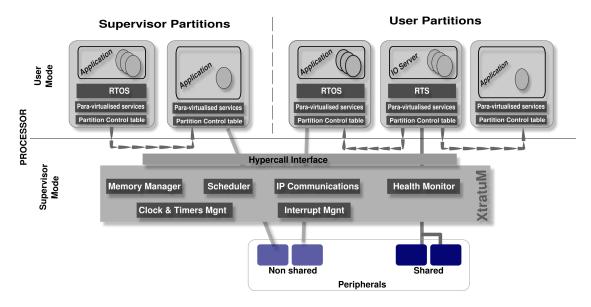

Figure 3.1 depicts the complete system architecture. The main components of this architecture are:

XtratuM is in charge of virtualisation services to partitions. It is executed in supervisor processor mode and virtualises the cpu, memory, interrupts and some specific peripherals. The internal XtratuM architecture includes: memory management, scheduling (fixed cyclic scheduling), interrupt management, clock and timers management, partition communication management

Figure 3.1: XtratuM architecture.

(ARINC-653 communication model), health monitoring and tracing facilities. Three layers can be identified:

- Hardware-dependent layer: It implements the set of drivers required to manage the strictly necessary hardware: processor, interrupts, hardware clocks, hardware timers, paging, etc. This layer is isolated from the rest through the Hardware Abstraction Layer (HAL). Thus, the HAL hides the complexity of the underlying hardware by offering a high-level abstraction of it (for instance, a ktimer is the common abstraction to all the hardware timers).

- Internal-service layer: Those services are not available to the partitions. This layer includes a minimal C library which provides the strictly required set of standard C functions (e.g. strcpy, memcpy, sprintf) and a bundle of data structures. The system boot is also part of the internal services.

- Virtualization-service layer: It provides the services required to support the paravirtualisation services, which are provided via the hypercall mechanism to partitions. Some of these services are also used from other XtratuM modules.

## 3.3 Trustability enforcement

In this section we provide a set of principles that permit to achieve a high secure hypervisor.

- Strong spatial isolation: Hypervisor has to be executed in privilege processor mode whereas partitions are executed in user processor mode. Partitions are allocated in independent physical memory addresses. Partitions can not access to other partition memory addresses.

- Strong temporal isolation: Hypervisor enforces the temporal isolation by using the appropriated scheduling policies to execute partitions. The policies can be cyclic scheduling or fixed priority scheduling based on the server concept.

- Partition management: Partitions are executed in user mode, thus guaranteeing that they have not access to processor control registers. Any partition access to a processor device is detected and handled by the hypervisor.

- Supervisor partitions: Some partitions can use *special* services provided by the hypervisor. These services include: partition management, access to system logs, etc.

- Robust communication mechanisms: Partitions can communicate with other partitions using the specific services provided by the hypervisor. The basic mechanism provided to the partitions is the port based communication. The hypervisor implements the link (channel) between partitions. Two types of ports are provided: sampling a queuing as defined in [Ai96].

- Interrupt Model: The hypervisor provides an interrupt model to the partitions. Partitions can not interact with native traps. All the interrupts are detected handled by the hypervisor and propagated to the partitions according to the interrupt model.

- Fault management model: Faults are detected and handled by the hypervisor. The detection of a fault can be the occurrence of a system trap or the occurrence of an event generated by the hypervisor code. The hypervisor code includes a set of assertions to verify the properties of the system. All hypervisor services have a set of pre- and post- conditions that assert the system properties. A Health Monitor module in the hypervisor implements the fault management model. Actions associated to the Health Monitor depend on the partition or hypervisor fault generator.

- Non-preemptible: In order to reduce the design complexity and increase the reliability of the implementation, the hypervisor is designed as a monolithic kernel to be non-preemptible.

- Resource allocation: Fine grain hardware resource allocation is specified in the system configuration file. This configuration permits to assign system resources (memory, I/O registers, devices, memory, etc.) to the partitions.

- Minimal entry points: the hypervisor has to clearly identify the execution paths and the entry points.

- Small: The level of difficulty and complexity of validation and formal verification increases in an exponential manner with the number of analyzed lines of code. The hypervisor code shall provide the minimum services in order to be as minimal as possible. XtratuM has around 5 MLOCs.

- Deterministic hypercalls: All services (hypercalls) shall be deterministic and fast.

The hardware protection mechanisms imposes strong limitations in the hypervisor design:

- Partition allocation restrictions (1) Each partition is allocated in one non overlapping memory region. (2) A partition has to be multiple of 64 Kbytes.

- On-chip peripherals are handled exclusively by the hypervisor and virtualised to the partitions.

- IO ports are handled exclusively by the hypervisor due to the protection mechanisms (1 bit). Partitions have to use specific services (hypercalls) to access to IO ports.

- Window registers are handled by the hypervisor providing a flat stack model to the partitions.

## 3.3.1 Interrupt Model

Different manufacturers use terms like exceptions, faults, aborts, traps, and interrupts to describe the processor mechanism to receive a signal indicating the need for attention. Also, different authors adopt different terms to their own use. In order to define the interrupt model, we provide the definition of the terms used in this work.

A *trap* is the mechanism provided by the processor to implement the asynchronous transfer of control. When a trap occurs, the processor switches to supervisor mode and unconditionally jumps into a predefined handler.

A *software trap* is raised by a processor instruction and it is commonly used to implement the system call mechanism in the operating systems.

An *exception* is an automatically generated interrupt that occurs in response to some exceptional condition violation. It is raised by the processor to inform about a condition that prevents the continuation of the normal execution sequence. There are basically two kind of exceptions: those caused by the normal operation of the processor (like register window under/overflow in Sparc architecture), and those caused by an abnormal situation (like an memory error).

A hardware interrupt is trap raised due to an external hardware event (external to the CPU). These interrupts generally have nothing at all to do with the instructions currently executing and informs the CPU that a device needs some attention.

In a partitioned system, the hypervisor handles these interrupts (*native interrupts*) and generates the appropriated *virtual interrupts* to the partitions.

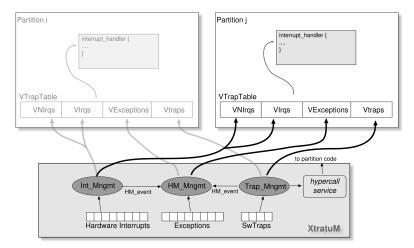

Figure 3.2: Interrupt model.

Figure 3.2 depicts the interrupt model. A partition have to deal with the following *virtual traps*:

- *virtual traps* are generated by the hypervisor to the partitions as consequence of a *native trap* occurrence.

- *virtual exceptions* are the exceptions propagated by the hypervisor to the partitions as consequence of a *native exception* occurrence. Not all the *native exceptions* are propagated

to the partition. For instance, a memory access error that is generated as consequence of a space isolation violation is handled by the hypervisor which can perform a halt partition action or can generate another different virtual exception (like memory isolation fault). On the other hand, a numeric error is propagated directly to the partition. *Virtual exceptions* are a superset of the *native exceptions* which include additional exceptions generated by the hypervisor (virtual processor). Some of them are: memory isolation error, IO isolation error and temporal isolation error.

- *virtual hardware interrupts* are directly generated by the real or the virtual hardware. The real hardware corresponds to external devices (dedicated devices technique) or peripherals and the virtual hardware includes the different virtual devices associated to the virtualisation. Some of these virtual devices are:

- Virtual hardware and global and local clocks and timers

- New message arrival. The communication mechanism (channel) implemented by XtratuM is seen as a hardware device.

- Partition slot execution. In a partitioned system the partition is aware of the partition scheduling, this interrupt informs to the partition that a new slot has been scheduled.

Only virtual hardware interrupts can be enabled or disabled by partitions.

We will use in the next paragraphs the terms *trap* and *vtrap* as the main mechanism to deal with any kind of interrupt at native or virtual level. Four strategies have been used to prevent partitions to jeopardise temporal isolation:

- Partitions have no access to the trap table. Thus, partitions are unable to install their own trap handlers. All traps are directly handled by XtratuM and, when required, propagated to partitions which define its own *virtual trap table*.

- Partitions cannot interact with native traps. Partitions are executed in user mode, thus guaranteeing that they have not access to control registers.

- A partition can not enable/unmask those *virtual hardware interrupts* not allocated to the partition.

- When a partition is scheduled, the *hardware interrupts* associated to other partitions are disabled. When a partition context switch occurs, the hypervisor detects the hardware interrupts pending for the next partition to be executed and raise them depending on the partition interrupt mask.

#### 3.3.2 Fault Management Model

The Health Monitor (HM) is the part of XtratuM that detects and reacts to anomalous events or states. The purpose of the HM is to discover the errors at an early stage and try to solve or confine the faulting subsystem in order to avoid or reduce the possible consequences.

HM is executed as result of a HM\_event occurrence. Next scenarios can raise a HM\_event:

• An exception has been raised by the CPU. The exception handler generates the associated HM\_event.

- A native interrupt has been received and the temporal or spatial properties are not validated.

- A trap has been received and the temporal or spatial properties are not validated.