## VLSI algorithms and architectures for non-binary-LDPC decoding

September, 2016

Author: Jesús Omar Lacruz Jucht

Thesis supervisor: Javier Valls Coquillat Thesis supervisor: Francisco García Herrero

## Abstract

This thesis studies the design of low-complexity soft-decision Non-Binary Low-Density Parity-Check (NB-LDPC) decoding algorithms and their corresponding hardware architectures suitable for decoding high-rate codes at high throughput (hundreds of Mbps and Gbps).

In the first part of the thesis the main aspects concerning to the NB-LDPC codes are analyzed, including a study of the main bottlenecks of conventional softdecision decoding algorithms (Q-ary Sum of Products (QSPA), Extended Min-Sum (EMS), Min-Max and Trellis-Extended Min-Sum (T-EMS)) and their corresponding hardware architectures. Despite the limitations of T-EMS algorithm (high complexity in the Check Node (CN) processor, wiring congestion due to the high number of exchanged messages between processors and the inability to implement decoders over high-order Galois fields due to the high decoder complexity), it was selected as starting point for this thesis due to its capability to reach high-throughput.

Taking into account the identified limitations of the T-EMS algorithm, the second part of the thesis includes six papers with the results of the research made in order to mitigate the T-EMS disadvantages, offering solutions that reduce the area, the latency and increase the throughput compared to previous proposals from literature without sacrificing coding gain. Specifically, five low-complexity decoding algorithms are proposed, which introduce simplifications in different parts of the decoding process. Besides, five complete decoder architectures are designed and implemented on a 90nm Complementary Metal-Oxide-Semiconductor (CMOS) technology. The results show an achievement in throughput higher than 1Gbps and an area less than 10  $\text{mm}^2$ . The increase in throughput is 120% and the reduction in area is 53% compared to previous implementations of T-EMS, for the (837,726) NB-LDPC code over GF(32). The proposed decoders reduce the CN area, latency, wiring between CN and Variable Node (VN) processor and the number of storage elements required in the decoder. Considering that these proposals improve both area and speed, the efficiency parameter (Mbps / Million

iii

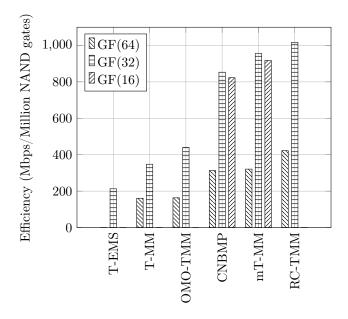

NAND gates) is increased in almost five times compared to other proposals from literature.

The improvements in terms of area allow us to implement NB-LDPC decoders over high-order fields which had not been possible until now due to the highcomplexity of decoders previously proposed in literature. Therefore, we present the first post-place and route report for high-rate codes over high-order fields higher than Galois Field (GF)(32). For example, for the (1536,1344) NB-LDPC code over GF(64) the throughput is 1259Mbps occupying an area of 28.90 mm<sup>2</sup>. On the other hand, a decoder architecture is implemented on a Field Programmable Gate Array (FPGA) device achieving 630 Mbps for the high-rate (2304,2048) NB-LDPC code over GF(16). To the best knowledge of the author, these results constitute the highest ones presented in literature for similar codes and implemented on the same technologies.

September, 2016

Jesús Omar Lacruz jlacruz@ula.ve

### Resumen

En esta tesis se aborda el estudio del diseño de algoritmos de baja complejidad para la decodificación de códigos de comprobación de paridad de baja densidad no binarios (NB-LDPC) y sus correspondientes arquitecturas apropiadas para decodificar códigos de alta tasa a altas velocidades (cientos de Mbps y Gbps).

En la primera parte de la tesis los principales aspectos concernientes a los códigos NB-LDPC son analizados, incluyendo un estudio de los principales cuellos de botella presentes en los algoritmos de decodificación convencionales basados en decisión blanda (QSPA, EMS, Min-Max y T-EMS) y sus correspondientes arquitecturas hardware. A pesar de las limitaciones del algoritmo T-EMS (alta complejidad en el procesador del nodo de chequeo de paridad (CN), congestión en el rutado debido al intercambio de mensajes entre procesadores y la incapacidad de implementar decodificadores para campos de Galois de orden elevado debido a la elevada complejidad), éste fue seleccionado como punto de partida para esta tesis debido a su capacidad para alcanzar altas velocidades.

Tomando en cuenta las limitaciones identificadas en el algoritmo T-EMS, la segunda parte de la tesis incluye seis artículos con los resultados de la investigación realizada con la finalidad de mitigar las desventajas del algoritmo T-EMS, ofreciendo soluciones que reducen el área, la latencia e incrementando la velocidad comparado con propuestas previas de la literatura sin sacrificar la ganancia de codificación. Especificamente, cinco algoritmos de decodificación de baja complejidad han sido propuestos, introduciendo simplificaciones en diferentes partes del proceso de decodificación. Además, arquitecturas completas de decodificadores han sido diseñadas e implementadas en una tecnologia CMOS de 90nm consiguiéndose una velocidad mayor a 1Gbps con un área menor a 10  $\mathbf{mm}^2$ , aumentando la velocidad en 120% y reduciendo el área en 53% comparado con previas implementaciones del algoritmo T-EMS para el código (837,726) implementado sobre campo de Galois GF(32). Las arquitecturas propuestas reducen el área del CN, latencia, número de mensajes intercambiados entre el nodo de comprobación de paridad (CN) y el nodo variable (VN) y el número de elementos de almacenamiento en el decodificador. Considerando que estas propuestas mejoran tanto el área como

v

la velocidad, el parámetro de eficiencia (Mbps / Millones de puertas NAND) se ha incrementado en casi cinco veces comparado con otras propuestas de la literatura.

Las mejoras en términos de área nos ha permitido implementar decodificadores NB-LDPC sobre campos de Galois de orden elevado, lo cual no habia sido posible hasta ahora debido a la alta complejidad de los decodificadores anteriormente propuestos en la literatura. Por lo tanto, en esta tesis se presentan los primeros resultados incluyendo el emplazamiento y rutado para códigos de alta tasa sobre campos finitos de orden mayor a GF(32). Por ejemplo, para el código (1536,1344) sobre GF(64) la velocidad es 1259 Mbps ocupando un área de 28.90 mm<sup>2</sup>. Por otro lado, una arquitectura de decodificador ha sido implementada en un dispositivo FPGA consiguiendo 660 Mbps de velocidad para el código de alta tasa (2304,2048) sobre GF(16). Estos resultados constituyen, según el mejor conocimiento del autor, los mayores presentados en la literatura para códigos similares implementados para las mismas tecnologías.

September, 2016

Jesús Omar Lacruz jlacruz@ula.ve

### Resum

En esta tesi s'aborda l'estudi del disseny d'algoritmes de baixa complexitat per a la descodificació de codis de comprovació de paritat de baixa densitat no binaris (NB-LDPC), i les seues corresponents arquitectures per a descodificar codis d'alta taxa a altes velocitats (centenars de Mbps i Gbps).

En la primera part de la tesi els principals aspectes concernent als codis NB-LDPC són analitzats, incloent un estudi dels principals colls de botella presents en els algoritmes de descodificació convencionals basats en decisió blana (QSPA, EMS, Min-Max i T-EMS) i les seues corresponents arquitectures. A pesar de les limitacions de l'algoritme T-EMS (alta complexitat en el processador del node de revisió de paritat (CN), congestió en el rutat a causa de l'intercanvi de missatges entre processadors i la incapacitat d'implementar descodificadors per a camps de Galois d'orde elevat a causa de l'elevada complexitat), este va ser seleccionat com a punt de partida per a esta tesi degut a la seua capacitat per a aconseguir altes velocitats.

Tenint en compte les limitacions identificades en l'algoritme T-EMS, la segona part de la tesi inclou sis articles amb els resultats de la investigació realitzada amb la finalitat de mitigar els desavantatges de l'algoritme T-EMS, oferint solucions que redueixen l'àrea, la latència i incrementant la velocitat comparat amb propostes prèvies de la literatura sense sacrificar el guany de codificació. Específicament, s'han proposat cinc algoritmes de descodificació de baixa complexitat, introduint simplificacions en diferents parts del procés de descodificació. A més, s'han dissenyat arquitectures completes de descodificadors i s'han implementat en una tecnologia CMOS de 90nm aconseguint-se una velocitat major a 1Gbps amb una àrea menor a  $10 \text{ mm}^2$ , augmentant la velocitat en 120% i reduint l'àrea en 53% comparat amb prèvies implementacions de l'algoritme T-EMS per al codi (837,726) implementat sobre camp de Galois GF(32). Les arquitectures proposades redueixen l'àrea del CN, la latència, el nombre de missatges intercanviats entre el node de comprovació de paritat (CN) i el node variable (VN) i el nombre d'elements d'emmagatzemament en el descodificador. Considerant que estes propostes milloren tant l'àrea com la velocitat, el paràmetre d'eficiència (Mbps / Milions de portes NAND) s'ha incrementat en quasi cinc vegades comparat amb altres propostes de la literatura.

Les millores en termes d'àrea ens ha permès implementar descodificadors NB-LDPC sobre camps de Galois d'orde elevat, la qual cosa no havia sigut possible fins ara a causa de l'alta complexitat dels descodificadors anteriorment proposats en la literatura. Per tant, nosaltres presentem els primers reports després de l'emplaçament i rutat per a codis d'alta taxa sobre camps finits d'orde major a GF(32). Per exemple, per al codi (1536,1344) sobre GF(64) la velocitat és 1259 Mbps ocupant una àrea de 28.90 mm<sup>2</sup>. D'altra banda, una arquitectura de descodificador ha sigut implementada en un dispositiu FPGA aconseguint 660 Mbps de velocitat per al codi d'alta taxa (2304,2048) sobre GF(16). Estos resultats constitueixen, per al millor coneixement de l'autor, els millors presentats en la literatura per a codis semblants implementats per a les mateixes tecnologies.

September, 2016

Jesús Omar Lacruz jlacruz@ula.ve

## Acknowledgments

Firstly, i want to thank my advisor Dr. Javier Valls for let me embark in this PhD project, give me the confidence and support during these years, even when it seems really hard to finish it.

Besides, my deeply gratitude to Dr. Francisco Garcia for his brilliant ideas that help me to develop the works presented in this thesis. More than an advisor he and Javier are good friends.

Secondly, I have to thank all the staff of GISED, specially to Dr. Maria Jose Canet for her invaluable help improving the quality of the papers and this manuscript. Moreover, to my lab partners Julian, Ferran and Joan Marc for the good moments we share all these years.

Thanks to Universidad de Los Andes in Venezuela, to give me the chance to improve my quality as university professor, giving me the financial support during the major part of the PhD program.

Finally i would like to thank my parents for their encouragement words in the distance. To you, Ori, you came into my life at the right time to give me your love and support to finish this project.

ix

## Contents

| Abstract                                                        | iii   |

|-----------------------------------------------------------------|-------|

| Resumen                                                         | V     |

| Resum                                                           | vii   |

| Acknowledgments                                                 | ix    |

| Contents                                                        | xi    |

| List of Figures                                                 | XV    |

| List of Tables                                                  | xxi   |

| Acronyms                                                        | xxiii |

| Preface                                                         | 1     |

| 1 State of the art of non-binary low-density parity-check codes | 9     |

| 1.1 LDPC codes and decoding process                             | 9     |

| 1.2 Nomenclature                                                | 11    |

| 1.3 Decoding schedules                                          | 12    |

| 1.4 Decoding architectures                                      | 15    |

xi

| 1.5 NB-LDPC decoding algorithms and architectures             | 18 |

|---------------------------------------------------------------|----|

| 1.5.1 Trellis Extended Min-Sum Algorithm                      | 23 |

| 1.6 Frame Error Rate (FER) Performance                        | 26 |

| 1.7 Conclusions of the state of the art                       | 30 |

|                                                               |    |

| 2 Simplified Trellis Min-Max Decoder Architecture for NB-LDPC |    |

| Codes                                                         | 31 |

| 2.1 Introduction                                              | 32 |

| 2.2 Trellis Extended Min-Sum Algorithm                        | 34 |

| 2.3 Simplified Trellis Min-Max Algorithm                      | 36 |

| 2.3.1 Algorithm Description                                   | 36 |

| 2.3.2 Frame Error Rate Performance                            | 39 |

| 2.4 Check Node Architecture                                   | 39 |

| 2.5 Architecture for the Complete Decoder                     | 44 |

| 2.5.1 Decoder Schedule                                        | 44 |

| 2.5.2 Decoder Architecture                                    | 45 |

| 2.5.3 Decoder Timing                                          | 47 |

| 2.5.4 Decoder Complexity and Implementation Results           | 48 |

| 2.6 Comparisons With Other NB-LDPC Decoders                   | 49 |

| 2.7 Conclusions                                               | 51 |

| 3 One Minimum Only Trellis Decoder for NB-LDPC Codes          | 53 |

| v                                                             |    |

| 3.1 Introduction                                              | 54 |

| 3.2 Trellis - Extended Min-Sum algorithm                      | 56 |

| 3.3 One Minimum Only Trellis Decoder                          | 58 |

| 3.3.1 Estimators for the second minimum value                 | 58 |

| 3.3.2 Statistical analysis of the different estimators        | 60 |

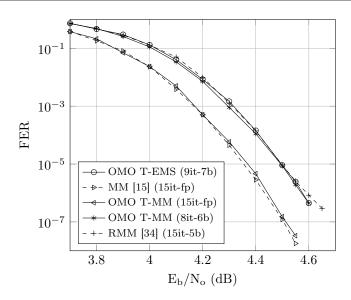

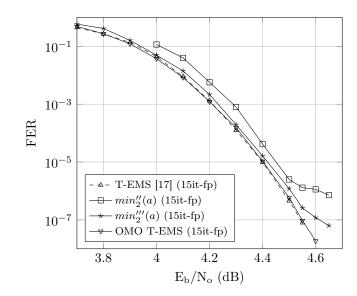

| 3.3.3 Frame Error Rate Performance                            | 62 |

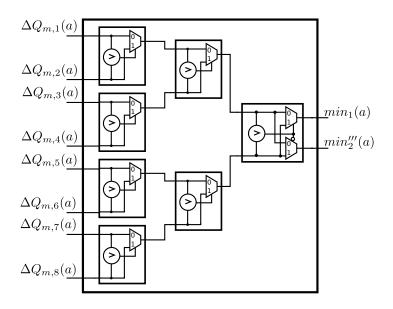

| 3.4 OMO T-EMS and OMO T-MM Hardware Architectures             | 63 |

| 3.4.1 Check Node Architecture                                 | 64 |

| 3.4.2 Complete decoder architecture                           | 68 |

| 3.5 Conclusions                                               | 70 |

| 4 Reduction of complexity for NB-LDPC decoders with com-                               |     |

|----------------------------------------------------------------------------------------|-----|

| pressed messages                                                                       | 71  |

| 4.1 Introduction                                                                       | 72  |

| 4.2 Non-binary LDPC message passing                                                    | 73  |

| 4.3 Compressed Non-Binary Message-Passing (CNBMP)                                      | 76  |

| 4.4 Hardware impact of CNBMP                                                           | 77  |

| 4.5 Conclusions                                                                        | 80  |

| 5 A 630 Mbps Non-Binary LDPC Decoder for FPGA                                          | 81  |

| 5.1 Introduction                                                                       | 82  |

| 5.2 Basis on NB-LDPC codes and T-MM decoding algorithm                                 | 83  |

| 5.3 Proposed Decoder Architecture                                                      | 85  |

| 5.3.1 Check-node architecture                                                          | 85  |

| 5.3.2 Top-level decoder architecture                                                   | 87  |

| 5.4 Conclusions                                                                        | 91  |

| 6 High-performance NB-LDPC decoder with reduction of mes-<br>sage exchange             | 93  |

| 6.1 Introduction                                                                       | 94  |

| 6.2 Trellis Min-Max decoding algorithm                                                 | 96  |

| 6.3 Modified Trellis Min-Max Algorithm                                                 | 98  |

| 6.3.1 Reformulation of Trellis Min-Max Algorithm                                       | 99  |

| 6.3.2 Reduction of replicated information in check-to-variable exchanged mes-<br>sages | 99  |

| 6.3.3 Modified Trellis Min-Max algorithm                                               | 102 |

| 6.4 NB-LDPC Decoder Implementation                                                     | 107 |

| 6.4.1 CN architecture for mT-MM algorithm                                              | 109 |

| 6.4.2 Top-level decoder architecture                                                   | 110 |

| 6.4.3 Decoder implementation results and comparisons                                   | 115 |

| 6.5 Conclusions                                                                        | 117 |

| 7 Reduced-complexity NB-LDPC decoder for high-order GF based on T-MM algorithm         | 119 |

| 7.1 Introduction                                                                       | 120 |

xiii

|     | 7.2 T-MM decoding algorithm with compressed messages                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 123                                    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|     | 7.3 T-MM algorithm with reduced set of messages                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 125                                    |

|     | 7.3.1 Reduction of the CN-to-VN messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 126                                    |

|     | 7.3.2 Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 127                                    |

|     | 7.3.3 Generation of the set $I^*(a')$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 129                                    |

|     | 7.4 Check Node architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 132                                    |

|     | 7.5 Top-level decoder architecture and complexity comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 138                                    |

|     | 7.5.1 Decoder implementation results and comparisons                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 139                                    |

|     | 7.6 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 141                                    |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

| 8 I | Discussion and conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 143                                    |

|     | Discussion and conclusions         8.1 Summary of the main contributions                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                      |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 143                                    |

|     | 8.1 Summary of the main contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 143<br>146                             |

|     | 8.1 Summary of the main contributions         8.2 Analysis of results                                                                                                                                                                                                                                                                                                                                                                                                                                         | 143<br>146<br>153                      |

|     | <ul> <li>8.1 Summary of the main contributions.</li> <li>8.2 Analysis of results.</li> <li>8.3 Comparison with other works from literature</li> <li>8.4 Conclusions.</li> </ul>                                                                                                                                                                                                                                                                                                                               | 143<br>146<br>153                      |

|     | <ul> <li>8.1 Summary of the main contributions.</li> <li>8.2 Analysis of results.</li> <li>8.3 Comparison with other works from literature</li> <li>8.4 Conclusions.</li> <li>8.4.1 Objective 1: reduction of area and latency of Check Node (CN) processors</li> <li>8.4.2 Objective 2: reduction of the number of messages exchanged between pro-</li> </ul>                                                                                                                                                | 143<br>146<br>153<br>156               |

|     | <ul> <li>8.1 Summary of the main contributions.</li> <li>8.2 Analysis of results.</li> <li>8.3 Comparison with other works from literature</li> <li>8.4 Conclusions.</li> <li>8.4 Conclusions.</li> <li>8.4.1 Objective 1: reduction of area and latency of Check Node (CN) processors</li> <li>8.4.2 Objective 2: reduction of the number of messages exchanged between processors in NB-LDPC decoders.</li> <li>8.4.3 Objective 3: implementation of high-performance decoders for Galois fields</li> </ul> | 143<br>146<br>153<br>156<br>156        |

|     | <ul> <li>8.1 Summary of the main contributions.</li> <li>8.2 Analysis of results.</li> <li>8.3 Comparison with other works from literature</li> <li>8.4 Conclusions.</li> <li>8.4.1 Objective 1: reduction of area and latency of Check Node (CN) processors</li> <li>8.4.2 Objective 2: reduction of the number of messages exchanged between processors in NB-LDPC decoders.</li> <li>8.4.3 Objective 3: implementation of high-performance decoders for Galois fields larger than 32.</li> </ul>           | 143<br>146<br>153<br>156<br>156<br>157 |

xiv

# List of Figures

| 1    | Software simulation model                                                                                                                         | 3  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2    | Key points of the improvements presented in each chapter of the manuscript                                                                        | 7  |

| 1.1  | (a) Example of a LDPC code parity-check matrix. (b) Tanner graph representation for the matrix in (a) $\ldots \ldots \ldots \ldots \ldots \ldots$ | 10 |

| 1.2  | (a) Example of a NB-LDPC code parity-check matrix. (b) Tanner graph corresponding to the matrix in (a)                                            | 11 |

| 1.3  | Simplified block diagram for the system model $\ \ldots \ \ldots \ \ldots \ \ldots$                                                               | 11 |

| 1.4  | Detail of a Tanner graph used to show the nomenclature of the exchanged messages between nodes in NB-LDPC decoding algorithms.                    | 12 |

| 1.5  | Example of horizontal layered schedule message exchange $\ldots$ .                                                                                | 14 |

| 1.6  | Example of a fully-parallel decoder for the code of Fig. 1.2 $\ldots$                                                                             | 15 |

| 1.7  | Example of a serial decoder for the code of Fig. 1.2. It requires $d_v = 2$ VN processors.                                                        | 17 |

| 1.8  | Example of a partial parallel decoder                                                                                                             | 17 |

| 1.9  | Forward Backward example                                                                                                                          | 22 |

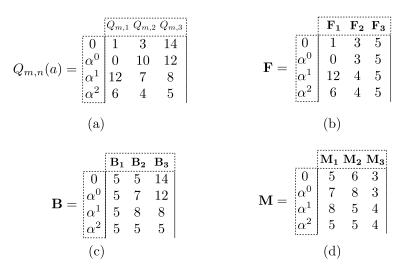

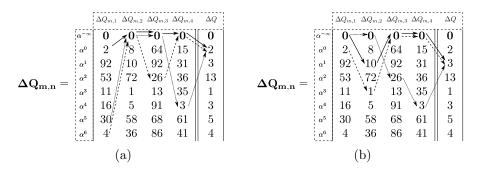

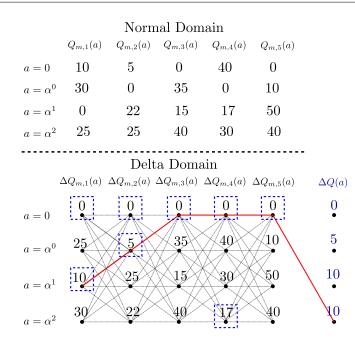

| 1.10 | Example of the set $Q_{m,n}(a)$ and $\Delta Q_{m,n}(a)$ including the extra column $\Delta Q(a)$ . $q = 8$ and $d_c = 4$ in this example.         | 24 |

| 1.11 | (a) Example of paths taken into account to compute the $\Delta Q(\alpha^0)$ reliability. (b) Example for the $\Delta Q(\alpha^1)$ reliability     | 25 |

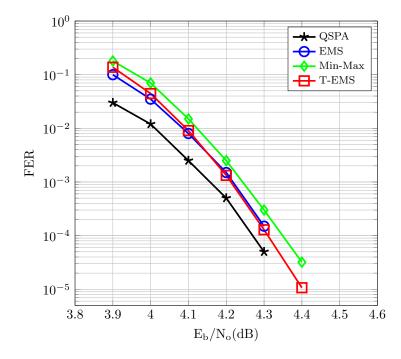

| 1.12 | FER performance for QSPA, EMS, Min-Max and T-EMS decoding algorithms for the $(837,726)$ NB-LDPC code over GF $(32)$                              | 27 |

xv

| 1.13 | FER performance for T-EMS algorithm quantifying the LLR values. The test code is the $(837,726)$ NB-LDPC code over GF $(32)$                                                                                                                                  | 28 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.14 | Fixed point analysis for the T-EMS algorithm. The test code is the (837,726) NB-LDPC code over GF(32). Layered schedule and 15 decoding iterations are used for all cases.                                                                                    | 29 |

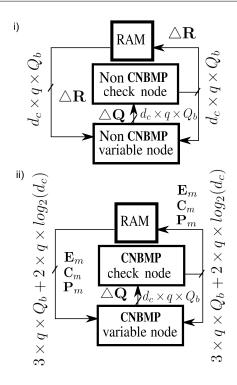

| 2.1  | Key points of the improvements presented in this chapter                                                                                                                                                                                                      | 31 |

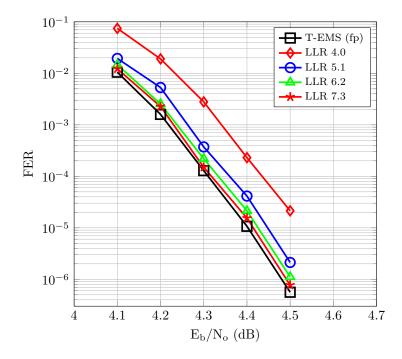

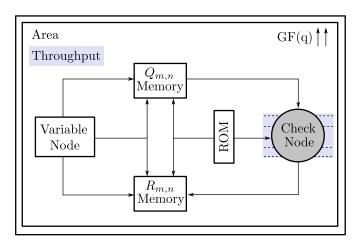

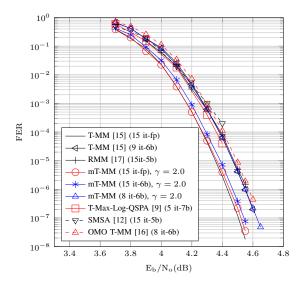

| 2.2  | FER of (837,726) NB-LDPC over $GF(32)$ under AWGN channel.<br>Layered schedule is used for all algorithms. $\lambda = 0.375$ for T-EMS algorithm and $\lambda = 0.5$ for TMM algorithm.                                                                       | 40 |

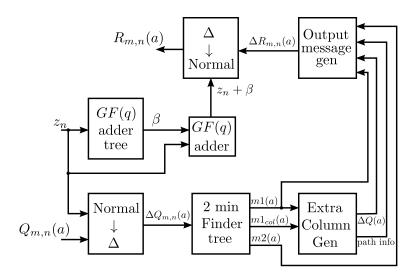

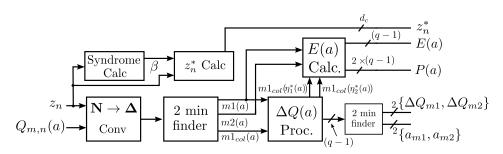

| 2.3  | Proposed top level check node structure                                                                                                                                                                                                                       | 41 |

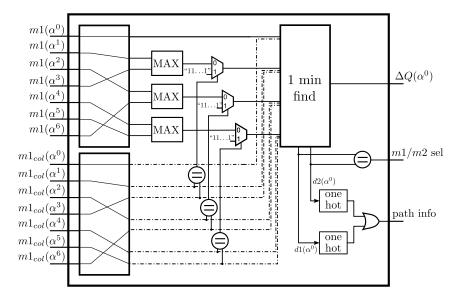

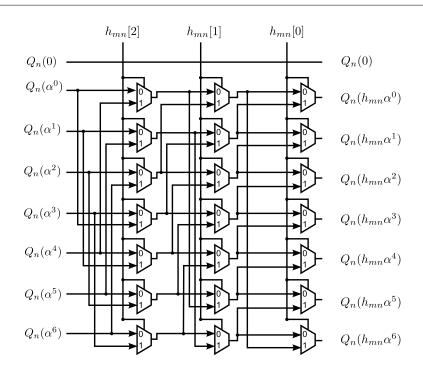

| 2.4  | Architecture for extra column extraction. Example for generation<br>of message $\Delta Q(\alpha^0)$ over $GF(8)$                                                                                                                                              | 42 |

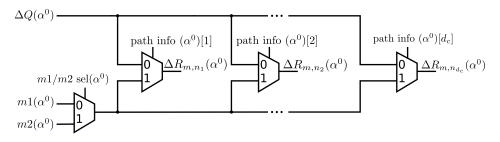

| 2.5  | Output message generation in delta domain. Example for symbol $\alpha^0$                                                                                                                                                                                      | 43 |

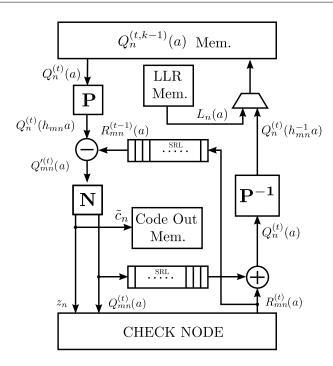

| 2.6  | Top level decoder architecture based on the horizontal layered schedule                                                                                                                                                                                       | 46 |

| 2.7  | Permutation network implemented for $GF(8)$                                                                                                                                                                                                                   | 47 |

| 3.1  | Key points of the improvements presented in this chapter                                                                                                                                                                                                      | 53 |

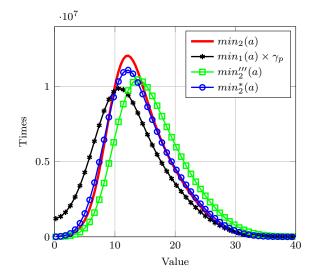

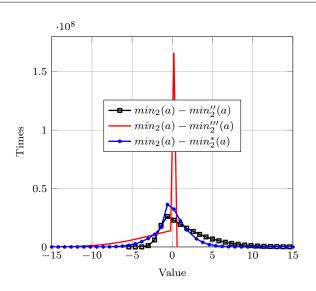

| 3.2  | Histograms for the different estimators of $min_2(a)$ . The $\gamma_p$ value was set to 1.125                                                                                                                                                                 | 59 |

| 3.3  | Histograms showing the error distribution of different estimators of $min_2(a)$ . The $\gamma_p$ value was set to 1.125                                                                                                                                       | 60 |

| 3.4  | Second minimum estimation based on a radix-2 one-minimum finder.<br>Example for an eight inputs tree                                                                                                                                                          | 61 |

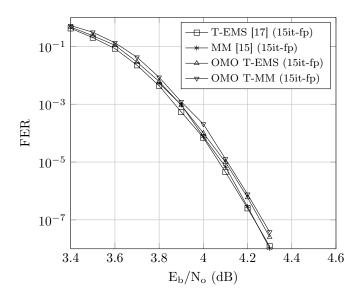

| 3.5  | FER performance for the (837,726) NB-LDPC code over GF(32) with AWGN channel. Layered schedule is applied to all algorithms. $\lambda=0.5$ for TEMS and OMO T-EMS algorithms. $\gamma_p=1.125$ for OMO T-EMS algorithm. $\gamma_p=1.5$ for OMO T-MM algorithm | 64 |

| 3.6  | FER performance for the (837,726) NB-LDPC code over GF(32) with AWGN channel for the estimators of the second minimum value. $\gamma_p = 1.125$ for OMO T-EMS algorithm                                                                                       | 65 |

| 3.7 | FER performance for the (2212,1896) NB-LDPC code over $GF(4)$ with AWGN channel. Layered schedule is applied to all algorithms.<br>$\lambda = 0.5$ for T-EMS and OMO T-EMS algorithms. $\gamma_p = 2.5$ for<br>OMO T-EMS algorithm. $\lambda = 0.75$ for MM and OMO T-MM algo-<br>rithms. $\gamma_p = 1.125$ for OMO T-MM algorithm   | 66  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

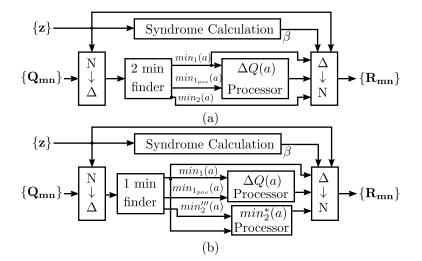

| 3.8 | Check node top architecture for T-EMS algorithm (a). Proposed OMO T-EMS/ OMO T-MM check node architecture (b)                                                                                                                                                                                                                         | 66  |

| 4.1 | Key points of the improvements presented in this chapter                                                                                                                                                                                                                                                                              | 71  |

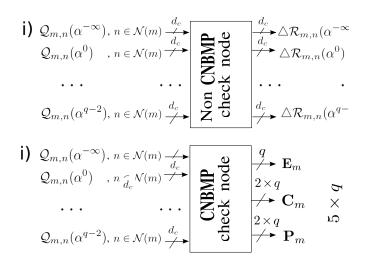

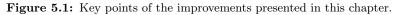

| 4.2 | i) Check node without CNBMP ii) Check node with CNBMP $\ . \ . \ .$                                                                                                                                                                                                                                                                   | 78  |

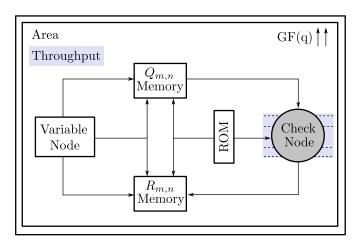

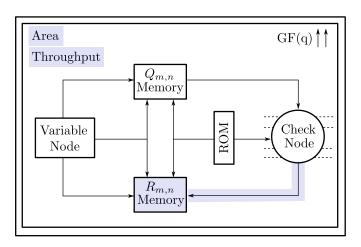

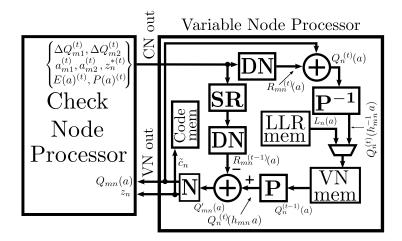

| 4.3 | i) Layered architecture of a NB-LDPC decoder without CNBMP.<br>RAM memory from this architecture has $M$ addresses of size $d_c \times q \times Q_b$ ii) Layered architecture of a NB-LDPC decoder with CNBMP.<br>RAM memory from this architecture has $M$ addresses of size $3 \times q \times Q_b + 2 \times q \times \log_2(d_c)$ | 79  |

| 5.1 | Key points of the improvements presented in this chapter                                                                                                                                                                                                                                                                              | 81  |

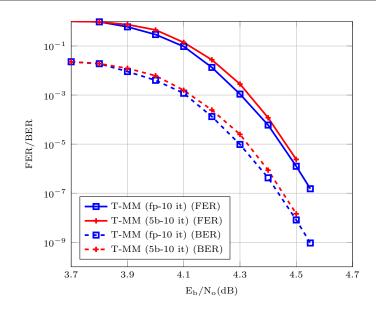

| 5.2 | FER-BER performance of T-MM algorithm for the $(2304,2048)$ NB-LDPC code over GF(16), with AWGN channel and BPSK modulation.                                                                                                                                                                                                          | 85  |

| 5.3 | Check-node top-level architecture                                                                                                                                                                                                                                                                                                     | 87  |

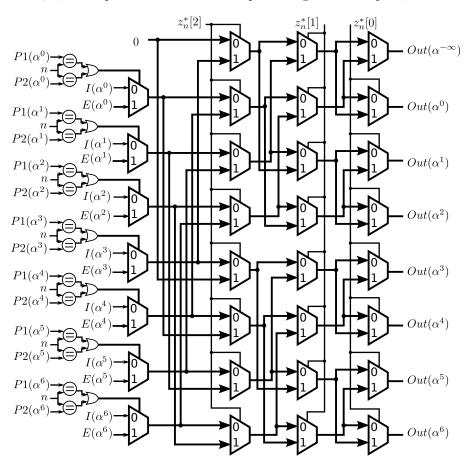

| 5.4 | Decompression Network for CN output messages. Example for $\mathrm{GF}(8)$ .                                                                                                                                                                                                                                                          | 88  |

| 5.5 | Top-level proposed decoder architecture                                                                                                                                                                                                                                                                                               | 89  |

| 6.1 | Key points of the improvements presented in this chapter                                                                                                                                                                                                                                                                              | 93  |

| 6.2 | Example of CN input messages in normal domain (upper size). Mes-<br>sages in delta domain and organized in trellis way including the<br>extra column $\Delta Q(a)$ (bottom size). Example for GF(4) and $d_c = 5$ .                                                                                                                   | 101 |

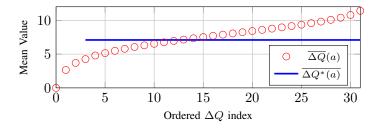

| 6.3 | Mean values for each reliability in the ordered set $\Delta Q(a)$ . The code used is the (837,726) NB-LDPC code over GF(32)                                                                                                                                                                                                           | 103 |

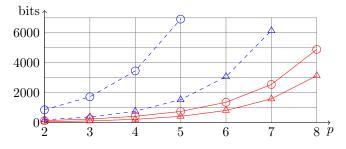

| 6.4 | Number of bits exchanged from CN to VN varying the GF order.<br>Dashed lines corresponds to T-MM and solid lines to mT-MM. Circle mark corresponds to $d_c = 36$ and Triangle mark to $d_c = 8$ .<br>w = 6.                                                                                                                           | 105 |

xvii

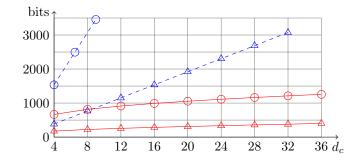

| 6.5  | Number of bits exchanged from CN to VN varying the CN degree. Dashed lines corresponds to T-MM and solid lines to mT-MM. Circle mark corresponds to $q = 64$ and Triangle mark to $q = 16$ . $w = 6$ .                                                                                                           | 106 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

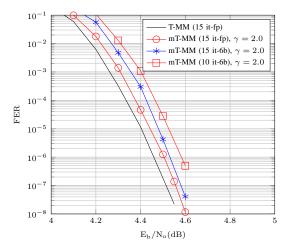

| 6.6  | Frame-error-rate simulation for the (837,726) NB-LDPC code over                                                                                                                                                                                                                                                  | 100 |

|      | GF(32), BPSK modulated and assuming AWGN channel                                                                                                                                                                                                                                                                 | 107 |

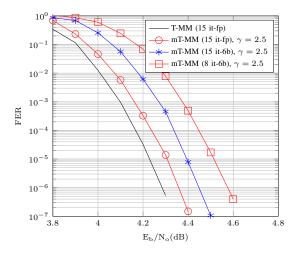

| 6.7  | Frame-error-rate simulation for the (2304,2048) NB-LDPC code over GF(16), BPSK modulated and assuming AWGN channel                                                                                                                                                                                               | 107 |

| 6.8  | Frame-error-rate simulation for the (1536,1344) NB-LDPC code over GF(64), BPSK modulated and assuming AWGN channel                                                                                                                                                                                               | 108 |

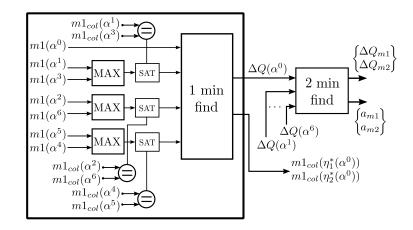

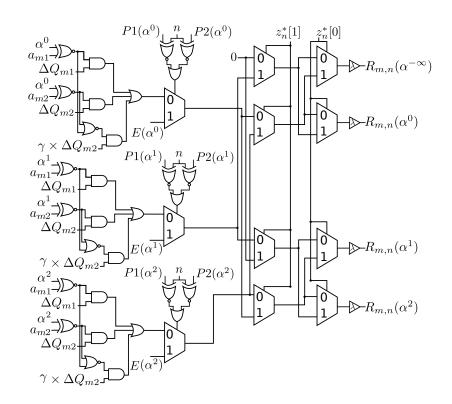

| 6.9  | Extra-Column processor. Example for GF(8) and symbol $\alpha^0$ $~$                                                                                                                                                                                                                                              | 110 |

| 6.10 | Proposed check-node block diagram                                                                                                                                                                                                                                                                                | 111 |

| 6.11 | Top-level proposed decoder architecture $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                     | 113 |

| 6.12 | Proposed Decompression Network. Example for $\mathrm{GF}(4)$                                                                                                                                                                                                                                                     | 114 |

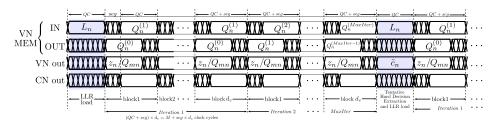

| 6.13 | Decoder timing                                                                                                                                                                                                                                                                                                   | 115 |

| 7.1  | Key points of the improvements presented in this chapter                                                                                                                                                                                                                                                         | 119 |

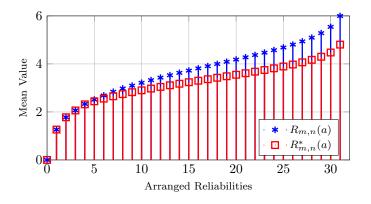

| 7.2  | Mean values for each reliability in the set $\Delta Q(a)$ . The values were arranged in the x axis. The code under test is the (837,726) NB-LDPC code over GF(32).                                                                                                                                               | 128 |

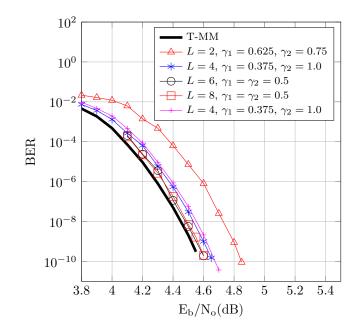

| 7.3  | Bit Error Rate performance for our proposal varying the $L$ parameter compared to T-MM algorithm. The code under test is the (837,726) NB-LDPC code over GF(32). 15 decoding iterations and floating point model are considered in all cases except for the last curve where 8 iteration and 6 bits are employed | 129 |

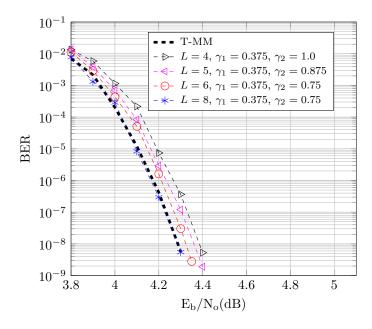

| 7.4  | Bit Error Rate performance for our proposal with different values of $L$ compared to T-MM algorithm. The test code is the (1536,1344) NB-LDPC code over GF(64). 15 decoding iterations and floating point model are considered for both algorithms                                                               | 130 |

| 7.5  | Example of the sets $\Delta Q_{m,n}(a)$ and $I(a)$ for GF(8) and $d_c = 4$                                                                                                                                                                                                                                       | 131 |

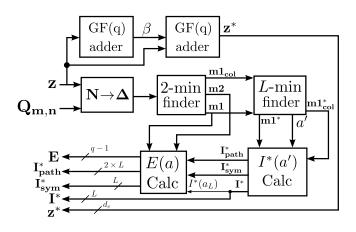

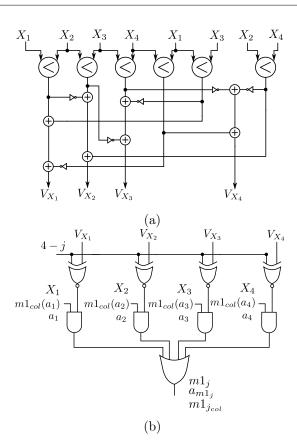

| 7.6  | Proposed check-node block diagram                                                                                                                                                                                                                                                                                | 134 |

| 7.7  | (a) First stage of the proposed $L$ -min finder. (b) Circuit to extract the $j$ -th minimum value. Example for four inputs                                                                                                                                                                                       | 135 |

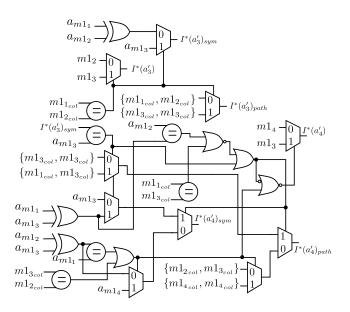

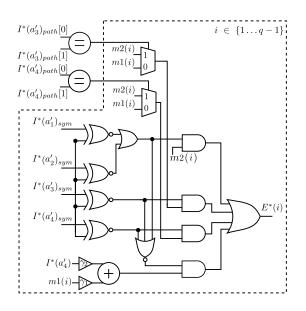

| 7.8  | Circuit to generate the set $I^*(a')$                                                                                                                        | 136 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.9  | Circuit to generate the set $E^*(a')$                                                                                                                        | 137 |

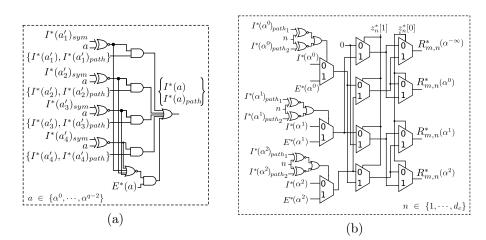

| 7.10 | Proposed decompression network circuits. (a) Circuit to generate the set $I^*(a)$ . (b) Circuit to generate the set $R^*_{m,n}(a)$ , an example with $GF(4)$ | 138 |

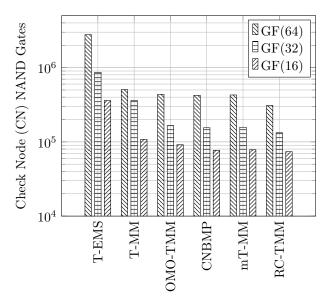

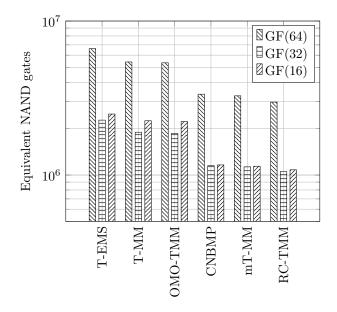

| 8.1  | Graphical comparison of the CN area for all the proposals included<br>in this thesis                                                                         | 148 |

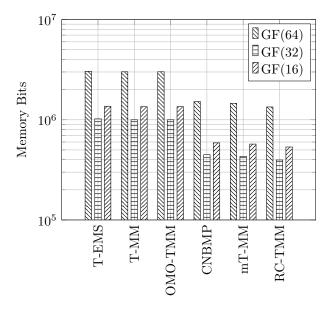

| 8.2  | Graphical comparison of the memory bits required for all the pro-<br>posals included in this thesis                                                          | 149 |

| 8.3  | Graphical comparison of the decoder area for all the proposals in-<br>cluded in this thesis                                                                  | 150 |

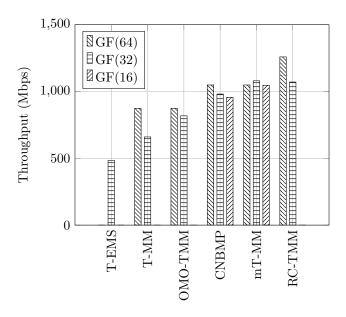

| 8.4  | Graphical comparison of the achieved throughput for all the pro-<br>posals included in this thesis                                                           | 151 |

| 8.5  | Graphical comparison of the efficiency parameter for all the propos-<br>als included in this thesis                                                          | 153 |

$_{\rm xix}$

## List of Tables

| 2.1 | Complexity analysis for the proposed decoder. For the (N=837,K=726) NB-LDPC code over $GF(32)$                                    | 49  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison of the proposed NB-LDPC layered decoder with other works from literature. For the NB-LDPC code (837,726) over $GF(32)$ | 50  |

| 3.1 | Statistical properties of the different $\widehat{min}_2(a)$ estimators after $I = 1$<br>and $I = 15$ decoding iterations         | 62  |

| 3.2 | CN complexity comparisons. For the $(837,726)$ NB-LDPC code over $GF(32)$                                                         | 67  |

| 3.3 | Comparison of the proposed NB-LDPC layered decoders to other works from literature. For the $(837,726)$ NB-LDPC code over GF(32)  | 70  |

| 4.1 | Comparison of the proposed NB-LDPC layered decoder with other works from literature                                               | 78  |

| 5.1 | Minimum number of bits required to be exchanged from CN to VN processor                                                           | 86  |

| 5.2 | Comparison of the proposed NB-LDPC decoder with other works implemented in FPGA devices from literature                           | 90  |

| 5.3 | ASIC implementation of the proposed NB-LDPC decoder for the (2304,2048) NB-LDPC code over GF(16)                                  | 91  |

| 6.1 | Number of bits exchanged from CN to VN processor after reduction<br>of the replicated information                                 | 102 |

xxi

| 6.2 | Comparison between multiple proposals from literature to reduce<br>the number of messages exchanged from CN to VN                    | 105 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3 | Experimental results to select the appropriate scaling value $\gamma$ , optimized for $E_b/N_0 = 4.3dB$                              | 108 |

| 6.4 | Implementation results for the proposed mT-MM algorithm. 90nm         CMOS process                                                   | 116 |

| 6.5 | Comparison of the proposed NB-LDPC layered decoder with other works from literature, for the NB-LDPC code $(837,726)$ over GF $(32)$ | 117 |

| 7.1 | Number of bits required to be exchanged from CN to VN processor                                                                      | 126 |

| 7.2 | Possible candidates for the $I^*(a'_4)$ reliability                                                                                  | 132 |

| 7.3 | Adders required to implement the circuit from Fig 7.7.a $\ . \ . \ .$ .                                                              | 136 |

| 7.4 | Synthesis results for the proposed CN architecture                                                                                   | 137 |

| 7.5 | Implementation results for the (1536,1344) NB-LDPC code over (GF(64) in a 90nm CMOS process                                          | 139 |

| 7.6 | Comparison of the proposed NB-LDPC layered decoder with other works from literature, for the $(837,726)$ NB-LDPC code with GF $(32)$ | 142 |

| 8.1 | Main benefits of each proposal presented in this thesis                                                                              | 147 |

| 8.2 | NB-LDPC codes used to perform comparisons between the propos-<br>als included in the manuscript                                      | 148 |

| 8.3 | Latency of all the proposals for the $(837,726)$ NB-LDPC code over $GF(32)$                                                          | 152 |

| 8.4 | Comparison of the works from this manuscript with other proposals from literature, for the (837,726) NB-LDPC code with $GF(32)$ .    | 154 |

## Acronyms

**ASIC** Application Specific Integrated Circuit.

${\bf AWGN}\,$  Additive White Gaussian Noise.

**BER** Bit Error Rate.

BPSK Binary Phase Shift Keying.

**CMOS** Complementary Metal-Oxide-Semiconductor.

${\bf CN}\,$  Check Node.

**CNBMP** Compressed Non-Binary Message Passing.

**EMS** Extended Min-Sum.

FER Frame Error Rate.

${\bf fp}\,$  floating point.

FPGA Field Programmable Gate Array.

${\bf GF}\,$  Galois Field.

${\bf GSL}\,$  GNU Scientific Library.

HD hard-decision.

${\bf LDPC}\,$  Low-Density Parity-Check.

${\bf LLR}\,$  Log-Likelihood Ratio.

xxiii

$\mathbf{m-TMM}\xspace$  modified Trellis Min-Max.

**NB-LDPC** Non-Binary Low-Density Parity-Check.

$\mathbf{NCG}~\mathrm{Net}$  Coding Gain.

**OMO** One - Minimum - Only.

${\bf PRNG}\,$  Pseudo-Random Number Generator.

QC Quasi-cyclic.

$\ensuremath{\mathbf{QSPA}}$  Q-ary Sum of Products.

**RC-TMM** Reduced Complexity Trellis Min-Max.

${\bf SD}\,$  Soft-Decision.

${\bf SNR}\,$  Signal-to-Noise Ratio.

**T-EMS** Trellis-Extended Min-Sum.

$\mathbf{T}\text{-}\mathbf{M}\mathbf{M}$  Trellis Min-Max.

**UUT** Unit Under Test.

VHDL Very High Speed Integrated Circuit Hardware Description Language.

**VLSI** Very Low Scale Integration.

**VN** Variable Node.

## Preface

Communication and storage systems demand for high-speed information exchange between transmitter and receiver nodes. At these high-speed information rates, channel impairments become more harmful as well as the inherent non-linearities of the electronic components, which reduce the reliability of the received information. To overcome this situation and provide more reliable communications, efficient channel coding techniques are required [1]. In the last two decades, Low-Density Parity-Check (LDPC) codes [2] have been successfully included in numerous standards such as DVB-S2 [3], IEEE 802.16e [4] and IEEE 802.11n [5], among others. The main reasons for their success are that their performance are close to the channel capability for long codewords and that they can be decoded with lowcomplexity algorithms based on belief propagation, which make them suitable for practical applications where high-speed and low area are important constraints.

LDPC codes defined over a GF GF( $q = 2^p$ ), with p > 1, were analyzed in [6] as an extension of binary LDPC codes. These codes perform better than their binary counterparts for codes with low and medium codeword length. Additionally, they improve the burst error-correction capability and work in conjunction with high-order modulation schemes (16QAM, 64QAM, 256QAM) [7, 8]. Nowa-days, NB-LDPC codes have been considered strong candidates to be used in the 100Gbps optical transport system [9, 10]. These systems require Soft-Decision (SD) decoding strategies that provide 10dB of Net Coding Gain (NCG) at a BER =  $10^{-15}$ , with a maximum overhead of 20% and code rate higher than 0.8.

NB-LDPC codes are strong candidates to be used in other important applications such as flash memory devices [11]. The NB-LDPC coding scheme is suitable for this application due to the constant increase in capacity, the use of multi-level NAND cells and the requirement of high-rate codes.

Besides the previous applications, NB-LDPC codes have been studied to be used in space communications [12, 13], where burst error correction capability and high coding gain are important issues.

1

Despite the multiple advantages of NB-LDPC codes over another coding schemes, they can not still be practically implemented because the state-of-the-art hardware implementations are far from offering high-throughput and high-rate decoders with reasonably low area.

This work is focused on reducing the complexity of SD decoding algorithms suitable for high-rate NB-LDPC codes, without sacrificing the coding gain of conventional algorithms such as EMS [14] and Min-Max [15]. The high-speed architectures derived from this low-complexity algorithms are also part of this job.

#### Objectives

The starting point of this thesis is the results obtained during the realization of my Master Degree thesis, where a complete decoder architecture based on the T-EMS algorithm was implemented. In that work, the main bottlenecks for the implementation of T-EMS were identified. The first one is the high complexity of the CN processor, which increases the latency and limits the throughput, especially for high-order Galois fields. The second bottleneck is the high density of wires that exchange information between CN and VN processors, due to the transportation of the full set of q messages. This congestion increases the decoder area and also reduces the achieved throughput.

The main objective of this thesis is to develop low-complexity algorithms and architectures for Very Low Scale Integration (VLSI) implementation of high-speed SD NB-LDPC decoders suitable for high-rate codes over high-order Galois fields. The emphasis is placed on the reduction of both bottlenecks, previously mentioned, that limit the performance of current NB-LDPC decoder architectures. Therefore, the specific objectives of this thesis are:

- Objective 1: To propose low-complexity decoding algorithms and their corresponding decoder architectures to simplify and reduce the complexity of the CN processor, with the goal of reducing the area and increase the throughput compared to the existing approaches from literature without compromising the coding gain.

- Objective 2: To develop solutions to reduce the number of messages exchanged between processors in NB-LDPC decoders with the aim of reducing the wiring congestion that usually appear on decoder implementations.

- Objective 3: To formulate a EMS- based algorithm that allows the implementation of high-performance decoders for Galois fields larger than 32.

#### Methodology

The methodology followed to meet the objectives of this thesis includes the next steps:

- Bibliography review of the state-of-the-art decoding algorithms. Analysis of the most efficient decoder architectures in terms of area and throughput, and detection improvements.

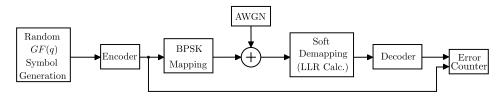

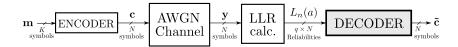

- Development of a software communication system model using C/C++ language that includes the components in Fig. 1. The method used to test the algorithms is through Montecarlo simulation, where the non-binary message is constructed using uniform random number generation. Next, this message is encoded (using the generator matrix) and modulated in Binary Phase Shift Keying (BPSK). For each modulated message the noise pattern is changed using Additive White Gaussian Noise (AWGN) generators<sup>1</sup>. The received signal is demodulated and the soft information is used to obtain the Log-Likelihood Ratio (LLR) which is the input of the decoding algorithm under test. The decoder receives the LLR values and then, applies the iterative message exchange to estimate the codeword. Finally, the estimated codeword is compared to the transmitted one to check if the decoding is successful or there is a decoding failure.

Figure 1: Software simulation model

- Analysis of the Frame Error Rate (FER)/BER performance of the proposed algorithms, and comparison to the state-of-the-art proposals from literature. Measurement of the possible performance loss introduced by our proposal and adjustment in the parameters of the algorithm in order to minimize these losses.

- Analysis of the iterative decoding algorithm with finite precision, after the validation of its floating-point model. To this end, a finite precision model is included in the software simulator and then Montecarlo simulations are performed (Fig. 1). The objective is to find the best fixed-point parameters

<sup>&</sup>lt;sup>1</sup>The AWGN model included in GNU Scientific Library (GSL) is used to make all the simulations required to validate each algorithm at low Bit Error Rate (BER) values. The standadard C/C++ Pseudo-Random Number Generator (PRNG) can not be employed because its short period length would affect the validation process

to establish a balance between performance loss, compared to the floatingpoint model, and required area.

- Design of the decoder architecture applying the results of the finite precision analysis and taking into account the next hardware constraints: area, latency and decoding throughput.

- Early estimation of the gate count of the design and comparison to other proposals from literature. Modifications in the architecture, in the quantization scheme or in the algorithm are made when the area of the design or the estimated latency do not accomplish requirements.

- Description of the hardware architecture using Very High Speed Integrated Circuit Hardware Description Language (VHDL) and functional verification before implementing the design. The verification is performed following the steps listed below:

- 1. Generation of the input and output vectors using the software finite precision model.

- 2. Description of a testbench in VHDL to validate the proposed design at functional level using Modelsim simulator. The Unit Under Test (UUT) will receive the input test vectors, process them and then it will generate the output values which are compared to the output test vectors (obtained using the software finite precision model).

- Implementation of the design for FPGA and Application Specific Integrated Circuit (ASIC) technologies considering the particular characteristics of each one of them. For FPGA implementation Xilinx tools are used and Cadence tools are employed for ASIC implementation. Once implementation is completed, the area results are compared to the estimations made during the design process and to other proposals from literature. After implementation, new simulations are made to ensure that the design fits with the software simulation model. If any constraint is not meet or there is some malfunction, the previous steps are applied again to redesign the decoder. Therefore, the design process is iterative.

#### Contributions

The contributions made during the realization of this research are summarized in the following list:

1. Five NB-LDPC decoding algorithms were proposed, two of them (Trellis Min-Max (T-MM) and Compressed Non-Binary Message Passing (CNBMP)) do not introduce any performance loss compared to previous proposals from

literature. The remaining three algorithms introduce a negligible performance loss less than 0.1dB for the high-rate codes under test.

- 2. Five decoding architectures were coded in VHDL and implemented in a 90nm CMOS technology and, moreover, post place and route results were presented. Besides, the architectures designed were implemented for three different high-rate codes with GF(16), GF(32) and GF(64). For the three codes the achieved throughput was higher than 1Gbps, being the highest compared to other proposals from literature for codes with similar characteristics to the best knowledge of the author.

- 3. One decoding architecture based on the CNBMP approach was implemented in a FGPA device for the (2304,2048) NB-LDPC code with GF(16) achieving 630 Mbps, the highest throughput for FPGA based decoder architectures compared to other proposals from literature.

- 4. The first post-place and route report for a high-rate decoding architecture with GF(64) was presented. The decoding algorithm was the Reduced Complexity Trellis Min-Max (RC-TMM) which introduces simplifications over the T-MM algorithm that saves a considerably amount of area for codes over high-order fields.

- 5. All the proposed decoding architectures applied parallel processing of messages, thus low latency is achieved in all of them (less than  $4 \ \mu s$ ).

- 6. Since the proposals presented in this manuscript improve both area and throughput, the efficiency parameter (Mbps / Million NAND gates) was greatly increased in almost six times compared to the T-EMS approach previous to this thesis.

The results got during the realization of this thesis have been published in five international journals. Furthermore, an international conference paper have been presented. Chapter 2 to 7 include the publications derived from this thesis.

- International journals:

- Chapter 2: Jesús O. Lacruz, Francisco Garcia-Herrero, David Declercq, Javier Valls, "Simplified Trellis Min-Max Decoder Architecture for Non-Binary Low-Density Parity-Check Codes". IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 23, No. 9, pp. 1783-1792, Sept. 2015.

- Chapter 3: Jesús O. Lacruz, Francisco García-Herrero, David Declercq, Javier Valls, "One Minimum Only Trellis Decoder for Non-Binary Low-Density Parity-Check Codes". IEEE Transaction on Cir-

5

cuits and Systems-I: Regular Papers, Vol. 62, No. 1, pp. 177-184, Jan. 2015.

- Chapter 4: Jesús O. Lacruz, Francisco Garcia-Herrero, Javier Valls, "Reduction of Complexity for Nonbinary LDPC Decoders With Compressed Messages". IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 23, No. 11, pp. 2676-2679, Nov. 2015.

- Chapter 6: Jesús O. Lacruz, Francisco Garcia-Herrero, María José Canet, Javier Valls, "High-performance NB-LDPC decoder with reduction of message exchange". IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 24, No. 5, pp. 1950-1961, May 2016.

- Chapter 7: Jesús O. Lacruz, Francisco Garcia-Herrero, María José Canet, Javier Valls, "Reduced-complexity Non-Binary LDPC decoder for high-order Galois fields based on Trellis Min-Max algorithm". IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 24, No. 8, pp. 2643-2653, Aug. 2016.

- International Conferences:

- Chapter 5: Jesús O. Lacruz, Francisco Garcia-Herrero, María José Canet, Javier Valls, Asunción Perez-Pascual, "A 630 Mbps Non-Binary LDPC Decoder for FPGA". IEEE International Symposium on Circuits & Systems (ISCAS) 2015, pp. 1989-1992. Lisbon-Portugal. May, 2015

#### Thesis Structure

This thesis is presented as a compilation of publications. Chapter 1 includes the basis of NB-LDPC codes, schedules, hardware architectures and soft-decision decoding algorithms. Chapters from 2 to 7 include the compilation of publications product of this thesis. The articles have been organized in chronological order just as the research was made. The structure of these chapters is the one commonly used for papers, ie, state-of-the-art and related works, presentation of the proposed approach, BER/FER performance of the algorithm, proposed hardware implementation, results and comparison to related works and, finally, the conclusions.

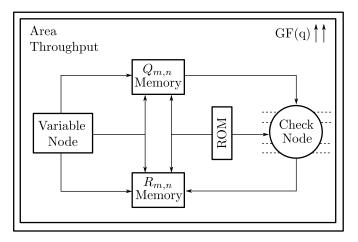

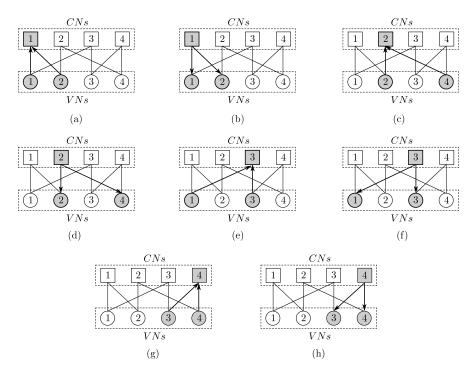

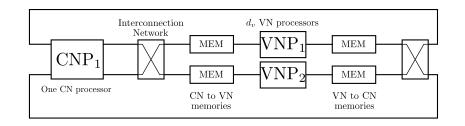

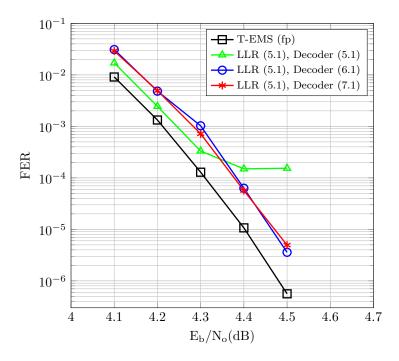

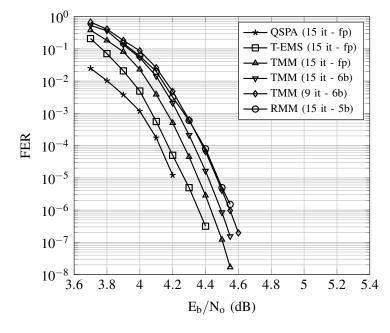

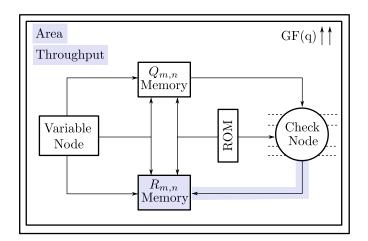

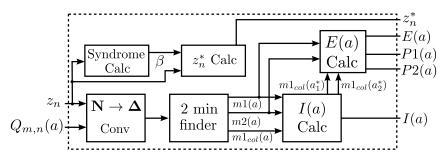

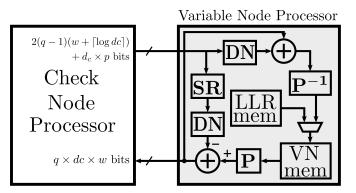

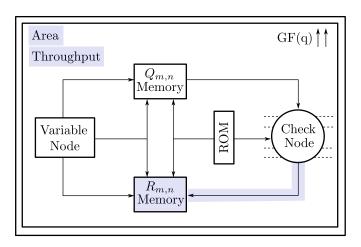

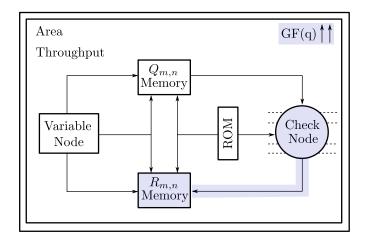

To ease the identification of the improvements made in each paper, we include in the corresponding chapter a figure as the one in Fig. 2, where the decoder characteristics that were improved in each paper are highlighted. Therefore, if the algorithm complexity was reduced, the "Check Node" is highlighted. If the latency was decreased, the discontinuous lines crossing the "Check Node", that represent the pipeline of the architecture are highlighted. In case of the reduction of the messages exchanged, the wires connecting the corresponding blocks are emphasized. Similar treatment was done for the memory, area and throughput improvements. In cases where the proposal is suitable for high-order Galois fields, "GF(q)  $\uparrow\uparrow$ " is highlighted.

Figure 2: Key points of the improvements presented in each chapter of the manuscript.

The starting point of the research made in this thesis is the T-EMS algorithm from [16]. T-EMS offers the possibility of the parallel processing of messages in the decoder, which allows the design of high-speed decoders with higher throughput compared to previous proposals from literature. The first implementation of this algorithm, also made by this author [17], achieved a throughput of 484Mbps in a 90nm CMOS process after synthesis results for the (837,726) NB-LDPC code over GF(32). This previous work allowed the identification of bottlenecks in both algorithm and hardware architecture of T-EMS, and set the bases of this thesis.

Chapter 2 introduces simplifications over the T-EMS algorithm and decoder architecture. Specifically, the way to derive the check-node output messages in T-EMS was simplified. On the other hand, the reliability of the output messages was computed with min-max operators, and this reduces the width of the decoder data-path. This simplification of T-EMS was named Trellis Min-Max algorithm (T-MM). Additionally, a complete decoder architecture for the (837,726) NB-LDPC code over GF(32) was proposed. It achieves a throughput 660Mbps and an area of 14.75 mm<sup>2</sup>.

Chapter 3 includes further simplifications over the CN processor compared to the proposal presented in Chapter two. Estimators for the second-most reliable value for the check-node input messages were presented. This estimators avoids the use of two-minimum finders in the check-node processors of NB-LDPC decoders. A complete hardware architecture was also presented, which achieves 818 Mbps of

7

throughput with an area of  $16.10 \text{ mm}^2$ . The increase in throughput is about 24% compared to the results achieved in Chapter 2.

Chapter 4 presents a method to reduce the quantity of messages exchanged between CN and VN processors. The number of storage elements in the decoder was also reduced. The performance of T-MM or T-EMS algorithms was kept since there is no information loss. The achieved throughput was 981 Mbps requiring an area of 10.6 mm<sup>2</sup>. The increase in throughput is 20% and the reduction in area is about 34% compared to the results from Chapter 3.

The work from Chapter 5 includes implementation details for the proposal from Chapter 4, describing the CN and VN architectures thoroughly. Furthermore, the design was particularized and optimized for FPGA using the (2304,2048) NB-LDPC code over GF(16). It achieved 630 Mbps of throughput, the highest for FPGA implementation compared to previous proposals.

An algorithm which reduces the number of messages exchanged between processors in NB-LDPC decoders was proposed in Chapter 6. The results from Chapter 4 and 5 were used to derive this new algorithm. The reduction of messages causes a performance loss that is negligible compared to T-MM algorithm (Chapter 2). The achieved throughput was 1.08 Gbps and the area 8.97 mm<sup>2</sup>, outperforming the results of the paper from Chapter 4 in 10% and 19% for throughput and area, respectively.

Finally, a new method to reduce the number of messages exchanged between processors in NB-LDPC decoders is included in Chapter 7. This reduction of messages allows a great decrease in the complexity of the CN processor compared to the architecture from Chapter 2, whose application was limited for codes with field orders higher than GF(32) due to its complexity. The implementation of the design for the (837,726) NB-LDPC code over GF(32) achieved a throughput (1.07 Gbps) and area (9.8mm<sup>2</sup>) are very similar to the results from Chapter 6. Additionally, we included the first post place & route results for a high-rate code over GF(64). The achieved throughput was 1.26 Gbps with an area of 28.9mm<sup>2</sup> for the high-rate (1536,1344) NB-LDPC code over GF(64).

To analyze the contributions of this thesis, Chapter 8 includes a discussion of the main results achieved during this research. First, each proposal is analyzed individually; secondly, the impact of each proposal in the objectives of the thesis is studied. Next, a comparison between the starting-point [17] and the final results achieved during this thesis is made. The improvement in throughput is about 120%, whereas the reduction in area (measured in terms of NAND gates) is about 53%. Furthermore, this chapter includes the conclusions derived from the thesis and the future research lines.

### Chapter 1

## State of the art of non-binary low-density parity-check codes

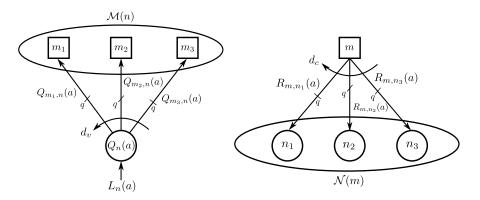

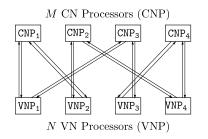

This chapter summarizes the background necessary to understand the following chapters and the state of art of the Non-Binary Low-Density Parity-Check (NB-LDPC) decoding algorithms and architectures. It includes  $1^{st}$ ) the basis of the NB-LDPC codes and their iterative decoding mechanism;  $2^{nd}$ ) the nomenclature to formulate the decoding algorithms;  $3^{rd}$ ) the schedules used in the decoding process;  $4^{th}$ ) the different architectural options suitable to implement the decoders; and finally,  $5^{th}$ ) the algorithms and architectures to compute the check node, with the emphasis placed in the Trellis Extended Min-Sum algorithm, which is the starting point of this thesis.

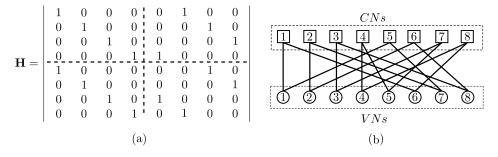

#### 1.1 LDPC codes and decoding process

LDPC codes are linear block codes characterized by a parity-check matrix  $\mathbf{H}$ . The term low-density means that  $\mathbf{H}$  is sparse, with just a few non-zero elements. If the elements in  $\mathbf{H}$  belong to the set  $\{0, 1\}$ , the code is said to be binary. LDPC codes were first investigated by Gallager [18] during his doctoral studies. His work was ignored due to the complexity of the decoding process and due to technology limitations in those years, until MacKay and Neal rediscovered them in 1995 [19]. LDPC codes can also been characterized by a bipartite graph called Tanner graph [20], where two kind of nodes are distinguished: the ones called VN, related to each column of  $\mathbf{H}$ , and the others called CN, which correspond to each row of  $\mathbf{H}$ . LDPC codes are decoded iteratively by means of message-passing algorithms between VN and CN and vice versa. Fig. 1.1 shows an example of a parity-check matrix (a), and its corresponding Tanner graph (b). The decoding process is the

following: i) bit reliability values are passed from VN to CN, where parity-check equations are solved; ii) messages based on the incoming reliability values are sent back to the VNs, where each node is updated. The process is repeated iteratively until all parity-check equations are satisfied or a maximum number of iterations *(iter)* is reached.

LDPC decoding algorithms usually include an early stopping criterion that consists on verifying if all parity-check equations are fulfilled with the tentative codeword  $\tilde{\mathbf{c}}$ . If that condition is reached,  $\tilde{\mathbf{c}}$  is a valid codeword and the decoder stops, otherwise a new iteration starts.

**Figure 1.1:** (a) Example of a LDPC code parity-check matrix. (b) Tanner graph representation for the matrix in (a)

LDPC codes can be regular or irregular. The first ones contain the same number of non-zero elements in all the columns of  $\mathbf{H}(d_c)$  and the same number of non-zero elements in all the rows  $(d_v)$ . In the second ones the columns and/or rows do not necessarily have the same number of non-zero elements. In this thesis, without loss of generality and for the sake of simplicity, we only consider regular LDPC codes. The CN degree  $(d_c)$  refers to the number of non-zero elements per row in  $\mathbf{H}$ . In the same way, the VN degree  $(d_v)$  corresponds to the number of non-zero elements per column in  $\mathbf{H}$ . In the example of Fig. 1.1  $d_c = d_v = 2$ .

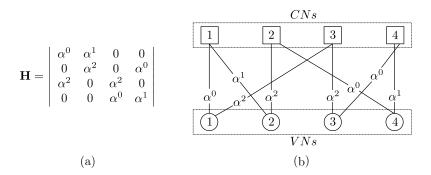

NB-LDPC codes were first studied by Davey and MacKay [6], emerging as a natural extension of the binary ones. Similar to the binary case, NB-LDPC codes are characterized by a parity-check matrix whose non-zero elements,  $h_{m,n}$ , belong to a Galois field  $GF(q = 2^p)$ , with p > 1, being p = 1 the binary case, as in the example of Fig. 1.1.

Fig. 1.2.a includes an example of a non-binary parity-check matrix with the nonzero elements from  $GF(2^2)$ . In the non-binary case, the Tanner graph is modified to include the non-zero **H** elements in the edge that connects the nodes. In the literature, some authors [14, 16, 21] include intermediate nodes between CN and VN in the Tanner graph, denominated permutation nodes, which include the corresponding non-zero **H** values. These nodes perform the multiplication of the

symbols coming from the VN and the corresponding non-zero  $\mathbf{H}$  value. The symbols from CN to VN are multiplied by the corresponding non-zero  $\mathbf{H}$  element.

**Figure 1.2:** (a) Example of a NB-LDPC code parity-check matrix. (b) Tanner graph corresponding to the matrix in (a)

#### 1.2 Nomenclature

Let us define  $\mathbf{m} = [m_1, m_2, \ldots, m_K]$  as the message to be coded, where each element  $m_i \in GF(q)$  and  $K = N - GFrank(\mathbf{H})^1$ . The codeword  $\mathbf{c} = [c_1, c_2, \ldots, c_N]$ is obtained by means of  $\mathbf{c} = \mathbf{m} \cdot \mathbf{G}$ , where  $\mathbf{G}$ , with dimensions  $K \times N$ , is the code generator matrix which must accomplish  $\mathbf{G} \cdot \mathbf{H}^T = 0$ .  $\mathbf{y} = [y_1, y_2, \ldots, y_N]$  is the sequence at the receiver side, being  $\mathbf{y} = \mathbf{c} + \mathbf{e}$ , where  $\mathbf{e}$  is the GF representation of the noise introduced by the communication channel, assumed as AWGN. The received sequence is used to calculate the LLR values, which serve as input for most of the NB-LDPC decoding algorithms. LLRs are obtained by means of  $L_n(a) =$  $\log[P(c_n = z_n | y_n) / P(c_n = a | y_n)]$ , where usually a normalization is made to ensure that all the values are non-negative,  $L'_n(a) = |L_n(a) - L_n(z_n)|$ , being  $z_n$  the harddecision symbol associated to the highest reliability. So, for each symbol n in the received sequence  $\mathbf{y}$ , the LLR forms the set  $\mathbf{L_n} = [L_n(0), L_n(1), \ldots, L_n(q-1)]$ . Fig. 1.3 includes a simplified block diagram for the system model including the nomenclature used and the cardinality of each set.

Figure 1.3: Simplified block diagram for the system model

$<sup>^1</sup>GFrank(\cdot)$  denotes the number of linearly independent equations of a matrix, using GF arithmetic