# Study and design of the front-end and readout electronics for the tracking plane in the NEXT experiment

PhD dissertation by Javier Rodríguez Samaniego

under the supervision of **José Francisco Toledo Alarcón**

July 2017

– Temet Nosce –

本來面目現前

### Abstract

The NEXT experiment is one of the most innovative ones looking for the neutrinoless double beta decay, which finding will answer one of the most important questions in the last years physics: is the neutrino its own antiparticle? Or in other words, is it a Majorana particle?

With that purpose NEXT uses a TPC (Time Projection Chamber) filled with enriched xenon gas at high pressure, and two photosensors planes, one on each end. The first plane contains PMTs (PhotoMultiplier Tube), that collect the light emitted by the xenon when an event happens and precisely measures its energy. The second plane is a SiPM (Silicon PhotoMultiplier) matrix that allows to 3D-reconstruct the event track. Both planes together allows NEXT to have a great background rejection, which makes a difference with the other experiments aiming for the neutrinoless double beta decay. In addition, SiPMs are a new technology which nowadays is evolving to, in the future, displace the classical PMTs. For that reason the study of these sensors starts from zero, as there were not previous uses as pixel-tracking, and lead a new path in the physics detectors, for both high and low energy.

This thesis is focused on the study and design of the electronics involving the tracking plane, which includes some technical solutions related also with mechanical issues. From the sensors placed inside the detector, the SiPMs, to the front-end electronic boards, there are few elements on the chain; as the support boards for the SiPMs which must satisfy severe outgassing and radiopurity levels. Also the inner and outer cabling has been designed, focusing on obtaining the best signal-noise ratio; and also the feedthrough for the tracking plane, which solved at low cost the huge problem of taking out about 4000 lines from the pressurized xenon to the outside.

Finally, one of the most important elements on this chain and the one that this thesis is focused on, is the front-end board. Starting with the experience acquired with the first prototype, NEXT-DEMO, the electronics have been improved, able to condition, integrate and digitize the signals from all the tracking plane SiPMs; allowing the further acquisition and processing through an ATCA-based system (Advanced Telecommunications Computing Architecture).

All the elements designed have been produced and assembled on the NEW detector, a large-scale prototype of the final detector, placed at the *Laboratorio Subterráneo de Canfranc*, an underground laboratory at the aragonese Pyrenee.

### Resumen

El experimento NEXT es uno de los más innovadores en la búsqueda de la desintegración doble beta sin neutrinos, cuyo hallazgo daría con la respuesta a una de las cuestiones más importantes de la física en los últimos años: ¿es el neutrino su propia antipartícula? O dicho de otro modo, ¿es una partícula de Majorana?

Para ello NEXT hace uso de una TPC (Time Projection Chamber) llena de gas xenón enriquecido a alta presión, y con dos planos de fotosensores, uno en cada extremo. El primero de ellos está formado por PMTs (Photo Multiplier Tube), que recogen la luz generada por el xenón cuando ocurre un evento, y miden la energía de éste. El segundo consiste en una matriz de SiPMs (Silicon PhotoMultipliers) que permiten reconstruir tridimensionalmente la traza de dicho evento. El conjunto de ambos planos de fotosensores otorga al experimento NEXT un gran rechazo a eventos de fondo, lo que marca la diferencia con otros experimentos en busca de la desintegración doble beta sin neutrinos. Además, los SiPMs son una tecnología de reciente aparición que en la actualidad está evolucionando a grandes pasos para, en un futuro, desplazar a los fotomultiplicadores clásicos. Por ello el estudio de estos fotosensores parte prácticamente desde cero, ya que no existen aplicaciones previas de su uso como pixel-tracking, y ha permitido abrir un nuevo camino en los detectores de física, tanto de alta como baja energía.

Esta tesis doctoral tiene como objetivo el estudio y diseño de la electrónica involucrada en el plano de reconstrucción de trazas, y que involucran en menor medida dar solución a problemas técnicos de aspecto mecánico. Partiendo de los sensores ubicados dentro del detector, los SiPMs, hasta las tarjetas de front-end, se incluyen varios elementos de la cadena; como son las tarjetas empleadas como soporte para los SiPM en el interior de la cámara, las cuáles deben cumplir rigurosas medidas de radiopureza y degasificación. También se ha diseñado el cableado tanto interno como externo, haciendo énfasis en conseguir la mayor relación posible señal-ruido; y el pasamuros específico para el plano de reconstrucción de trazas, el cual ha resuelto a bajo coste el problema de extraer casi 4000 líneas desde la zona de xenón a alta presión hasta el exterior.

Por último, uno de los elementos más importantes de esta cadena y en el cuál se centra principalmente esta tesis, es la tarjeta de front-end. Partiendo de la experiencia adquirida del primer prototipo del experimento, NEXT-DEMO, se ha perfeccionado una electrónica capaz de tratar, integrar y adquirir las señales de todos los SiPM del plano de reconstrucción de trazas, permitiendo su posterior adquisición y procesado mediante un sistema basado en la estructura ATCA (Advanced Telecommunications Computing Architecture).

Todos los elementos diseñados han sido ensamblados y puestos en marcha en el detector NEW, un prototipo a gran escala del detector final, que está ubicado en el Laboratorio Subterráneo de Canfranc, en el Pirineo Aragonés.

### Resum

L'experiment NEXT és un dels més innovadors en la recerca de la desintegració doble beta sense neutrins, i aquesta troballa donaria amb la resposta a una de les qüestions més importants de la física en els últims anys: és el neutrí la seua pròpia antipartícula? O dit d'una altra manera, és una partícula de Majorana?

Per açò NEXT fa ús d'una TPC (Time Projection Chamber) plena de gas xenó enriquit a alta presió, i amb dos plànols de fotosensors, un a cada extrem. El primer d'ells està format per PMTs (Photo Multiplier Tube), que arrepleguen la llum generada pel xenó quan ocorre un esdeveniment, i mesuren l'energía d'aquest. El segon consisteix en una matriu de SiPMs (Silicon PhotoMultipliers) que permeten reconstruir tridimensionalment la traça d'aquest esdeveniment. El conjunt de tots dos plànols de fotosensors atorga a l'experiment NEXT un gran rebuig a esdeveniments de fons, la qual cosa marca la diferència amb altres experiments a la recerca de la desintegració doble beta sense neutrins. A més, els SiPMs són una tecnología de recent aparició que en l'actualitat està evolucionant a grans passos per a, en un futur, desplaçar als fotomultiplicadors clàssics. Per això l'estudi d'aquests fotosensors part pràcticament des de zero, ja que no hi ha aplicacions prèvies del seu ús com a pixel-tracking, i ha permés obrir un nou camí en els detectors de física, tant d'alta com de baixa energia.

Aquesta tesi doctoral té com a objectiu l'estudi i diseny de l'electrònica involucrada en el plànol de reconstrucció de traces, i que involucra en menor mesura donar solució a problemes tècnics d'aspecte mecànic. Partint dels sensors situats dins del detector, els SiPMs, fins a les targetes de front-end, s'inclouen diversos elements de la cadena; com són les targetes emprades com a suport per als SiPMs a l'interior de la càmera, les quals han de complir rigoroses mesures de radioactivitat i degasificació. També s'ha disenyat el cablejat tant intern com extern, fent èmfasi en aconseguir la major relació possible senyalsoroll; i el passamurs específic per al plànol de reconstrucció de traces, el qual ha resolt a baix cost el problema d'extraure quasi 4000 línies des de la zona de xenó a alta presió fins a l'exterior.

Finalment, un dels elements més importants d'aquesta cadena i en el qual es centra principalment aquesta tesi, és la targeta de front-end. Partint de l'experiència adquirida del primer prototip de l'experiment, NEXT-DEMO, s'ha perfeccionat una electrònica capaç de tractar, integrar i adquirir les senyals de tots els SiPM del plànol de reconstrucció de traces, permetent la seua posterior adquisició i processament mitjançant un sistema basat en l'estructura ATCA (Advanced Telecommunications Computing Architecture).

Tots els elements disenyats han sigut muntats i engegats en el detector NEW, un prototip a gran escala del detector final, que està situat en el *Laboratorio Subterráneo de Canfranc*, al Pirineu Aragonès.

# Agradecimientos

Es difícil dar las gracias adecuadamente, y puede que ese sea precísamente el motivo por el cual no lo hacemos tan a menudo como deberíamos. Dar las gracias con motivo de esta tesis no es únicamente cuestión de agradecer a esas personas que han estado ahí durante la redacción de la misma, sino a todas aquellas personas que, de un modo u otro, han influido en mi vida encaminándola hacia donde estoy ahora. A todas esas personas con las que me he cruzado a lo largo de mi vida y han hecho de mí la persona que soy. No voy a dar nombres, pues la lista sería interminable. Dejo a decisión de cada uno darse o no por aludido:

A aquellos que han creído en mí, por darme la confianza necesaria para seguir adelante; y también a aquellos que no lo hicieron, por darme motivos para superarme. A quienes me han educado, y también a quienes me han enseñado. A los que me han dado la oportunidad de demostrar de qué soy capaz; pero también a los que no, pues me enseñaron que las oportunidades hay que ganárselas. A las personas que me han hecho pasar buenos momentos y han dado sentido a mi vida; y a las que me enseñaron que los malos momentos te hacen valorar más lo que tienes. A quienes me han dado lo que tengo; y no menos a quienes me han hecho ganármelo y aprender el valor de las cosas. A aquellos que me han ayudado a estar dónde estoy, y a aquellos que todavía me ayudan. A los que me han acompañado durante gran parte del camino y siguen ahí; y a los que me acompañaron en su día, y jamás olvidaré.

A todos vosotros, gracias.

# Acknowledgments

The author would like to acknowledge support from the following agencies and institutions: the European Research Council (ERC) under the Advanced Grant 339787-NEXT; the Ministerio de Economía y Competitividad of Spain under grant FIS2014-53371-C04.

# Contents

| Abstract                                                    | v   |

|-------------------------------------------------------------|-----|

| Resumen                                                     | vii |

| Resum                                                       | ix  |

| Agradecimientos                                             | xi  |

| Contents                                                    | xv  |

| Introduction                                                | 1   |

| 1 The NEXT Experiment                                       | 5   |

| 1.1 Neutrinoless Double Beta Decay ( $\beta\beta$ 0 $\nu$ ) | 6   |

| 1.2 NEXT Concept                                            | 11  |

| 1.3 NEXT-DEMO                                               | 12  |

| 1.4 NEW                                                     | 21  |

| 1.5 NEXT-100 and Beyond                                     | 40  |

| 1.6 Seeing the invisible: Silicon PhotoMultipliers (SiPM)   | 42  |

| 1.6.1 Semiconductor devices                                 | 42  |

|   | 1.6.2 Silicon PhotoMultipliers                            | 48  |

|---|-----------------------------------------------------------|-----|

|   | 1.6.3 SiPMs and MPPCs in Physics Experiments.             | 55  |

| 2 | The NEXT-DEMO Tracking Plane                              | 57  |

|   | 2.1 Design Requirements.                                  | 58  |

|   | 2.2 From Mother and Daughter Boards to CuFlon DICE-Boards | 60  |

|   | 2.3 Front-end and Readout Electronics.                    | 64  |

|   | 2.4 Results                                               | 66  |

|   | 2.5 State of the art in SiPM Front-end Electronics        | 72  |

| 3 | From the Beginning: Front-end Prototype                   | 75  |

|   | 3.1 First Scheme                                          | 76  |

|   | 3.2 Single ended Scheme                                   | 77  |

|   | 3.2.1 Circuit                                             | 77  |

|   | 3.2.2 Results                                             | 85  |

|   | 3.2.3 Conclusions                                         | 87  |

|   | 3.3 Moving to a Differential input Scheme                 | 88  |

|   | 3.4 Noise Analysis                                        | 91  |

| 4 | Front-end Electronics: The FEB64                          | 97  |

|   | 4.1 Power Supply Requirements                             | 98  |

|   | 4.2 From Prototyping to Full Design                       | 99  |

|   | 4.3 Board Layout Distribution: a Matter of Size           | 101 |

|   | 4.4 A Functional Design: FEB64v2                          | 103 |

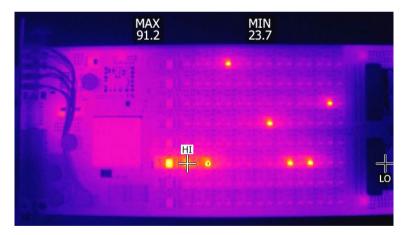

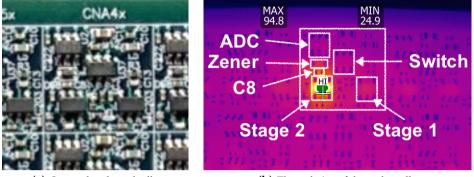

|   | 4.5 The zener issue                                       | 105 |

|   | 4.5.1 Malfunction detection                               | 105 |

|   | 4.5.2 Solution                                            | 107 |

|   | 4.6 Planned design modifications: Future FEB64v3          | 108 |

|   | 4.7 SRS-ATCA & Java Interface                     | 110 |

|---|---------------------------------------------------|-----|

|   | 4.7.1 ATCA                                        | 110 |

|   | 4.7.2 DAQ Architecture                            | 111 |

|   | 4.7.3 DAQ Features                                | 113 |

|   |                                                   |     |

| 5 | New SiPM array: The Kapton DICE-Board             | 115 |

|   | 5.1 Embedded microstrip                           | 117 |

|   | 5.1.1 Crosstalk                                   | 118 |

|   | 5.1.2 Stackup                                     | 120 |

|   | 5.1.3 Transmission Line Parameters                | 121 |

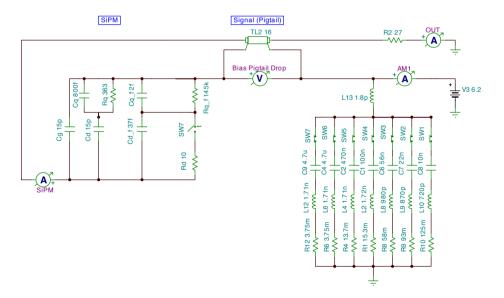

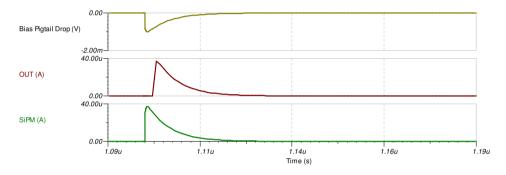

|   | 5.1.4 Bypass Capacitors                           | 124 |

|   | 5.1.5 Simulation                                  | 125 |

|   | 5.2 Broadside Coupled Traces                      | 130 |

|   | 5.2.1 Stackup                                     | 131 |

|   | 5.2.2 Line Parameters                             | 131 |

|   | 5.2.3 Simulation                                  | 134 |

|   | 5.3 Finishing the DICE-Board                      | 136 |

|   | 5.3.1 Mechanical Design                           | 136 |

|   | 5.3.2 Radiopurity issues                          | 140 |

| ( | Enore the CiDM to Enorth and The Cabling Duckland | 145 |

| 0 | From the SiPM to Front-end: The Cabling Problem   | 145 |

|   | 6.1 Inner Cables                                  | 146 |

|   | 6.2 Outer Cables                                  | 149 |

|   | 6.2.1 Cable specifications                        | 150 |

|   | 6.2.2 Noise                                       | 154 |

|   | 6.2.3 Crosstalk                                   | 159 |

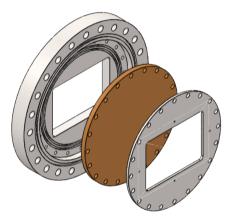

|   | 6.3 Custom Feedthrough                            | 160 |

|   | 6.3.1 FR4 PCB feedthrough prototype               | 161 |

|   | 6.3.2 NEW FR4 PCB Feedthrough                     | 163 |

|   | 6.3.3 Adapter Boards                              | 164 |

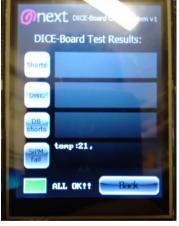

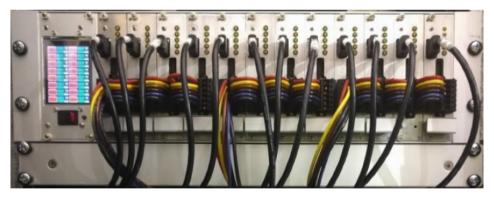

| 6.4 SiPM & Cabling connection test ("Check System")                                                  | 166                      |

|------------------------------------------------------------------------------------------------------|--------------------------|

| 6.5 Protection against ESD                                                                           | 168                      |

|                                                                                                      |                          |

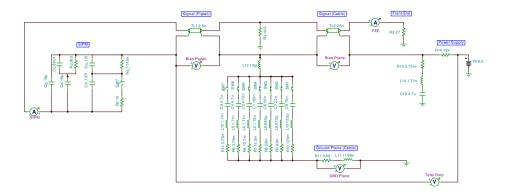

| 7 Programmable Power Supply with SiPM gain stabilization                                             | 171                      |

| 7.1 Requirements for NEW and NEXT-100                                                                | 172                      |

| 7.2 Design                                                                                           | 173                      |

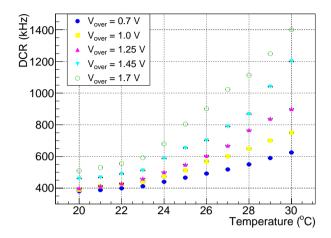

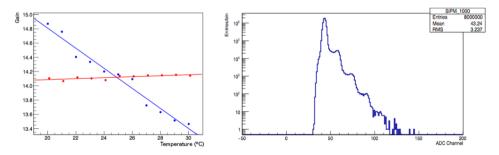

| 7.2.1 Temperature Compensation                                                                       | 173                      |

| 7.2.2 Output channel                                                                                 |                          |

| 7.2.3 I/O Interfaces.                                                                                |                          |

| 7.2.4 Mechanical Design                                                                              |                          |

| 7.3 Results and Outlook                                                                              | 178                      |

|                                                                                                      |                          |

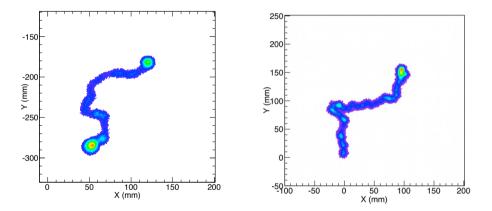

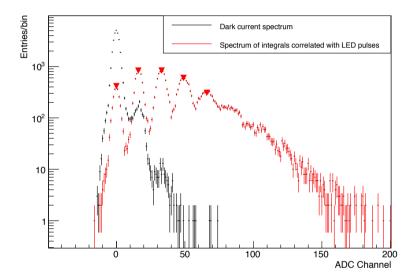

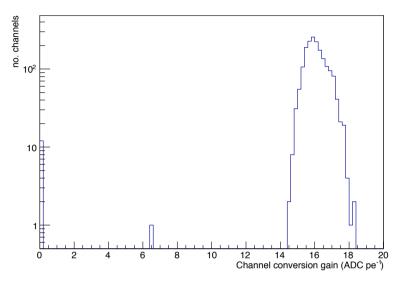

| 8 First Results of NEW Tracking Plane                                                                | 181                      |

| <ul> <li>8 First Results of NEW Tracking Plane</li> <li>8.1 NEW Tracking Plane Calibration</li></ul> |                          |

| Ŭ                                                                                                    | 182                      |

| 8.1 NEW Tracking Plane Calibration                                                                   | 182                      |

| 8.1 NEW Tracking Plane Calibration                                                                   | 182                      |

| 8.1 NEW Tracking Plane Calibration                                                                   | 182<br>184               |

| 8.1 NEW Tracking Plane Calibration                                                                   | 182<br>184               |

| <ul> <li>8.1 NEW Tracking Plane Calibration</li></ul>                                                | 182<br>184<br>189<br>195 |

| <ul> <li>8.1 NEW Tracking Plane Calibration</li></ul>                                                | 182<br>184<br>189        |

| <ul> <li>8.1 NEW Tracking Plane Calibration</li></ul>                                                | 182<br>184<br>189<br>195 |

### Introduction

The Neutrino Experiment with a Xenon TPC (NEXT) started in 2008, as the first experiment with tracking reconstruction in the neutrinoless doublebeta decay search race. Some time and prototyping later, the SiPM (Silicon PhotoMultipliers) were chosen as the photosensors for the pixel tracking. This decision implied a lot of hard work and studies which the NEXT collaboration carried out, as the SiPM were still (and are) a novel technology.

The student stepped in the collaboration in summer 2010, and since then has been working on the experiment's electronics group. This implies knowledge in all the areas developed almost since the beginning, and a lot of experience acquired during the first prototype assembly, NEXT-DEMO. Then, as responsible of the electronics group, started to work on the next step of the tracking plane: the NEW detector, a mid-scale prototype. All the experience gained in NEXT-DEMO helped to evolve and improve all the elements of the detector, but also the size of this new tracking plane implied new challenges that must be solved for further scaling in the future and final detector: NEXT-100.

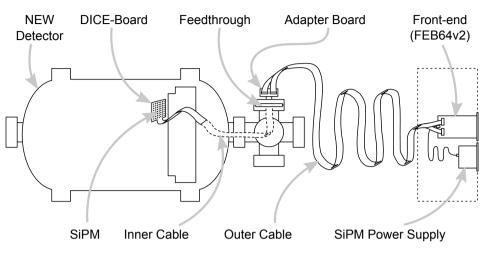

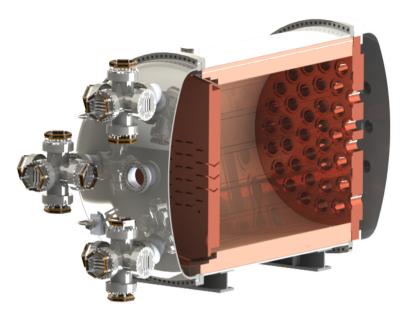

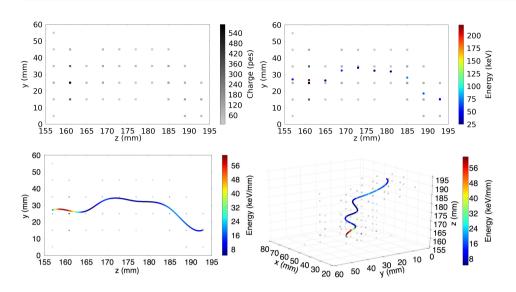

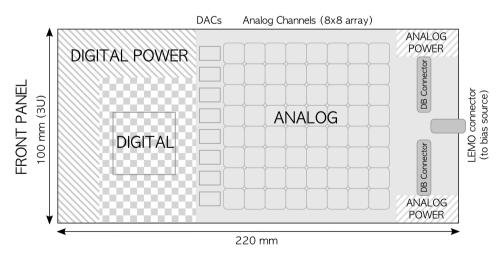

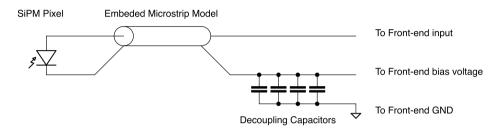

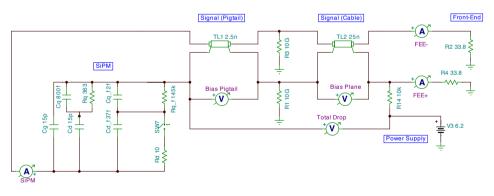

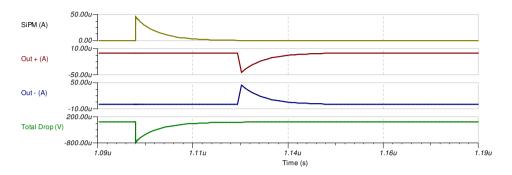

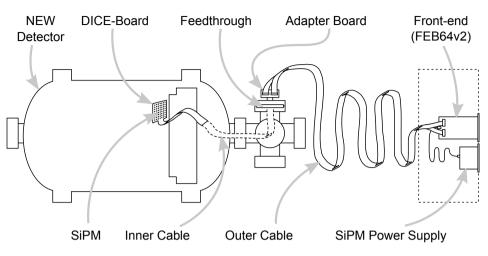

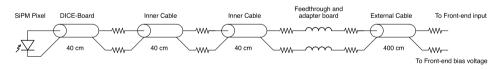

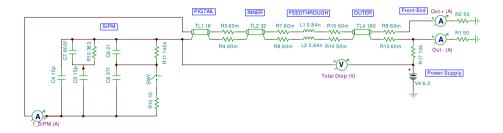

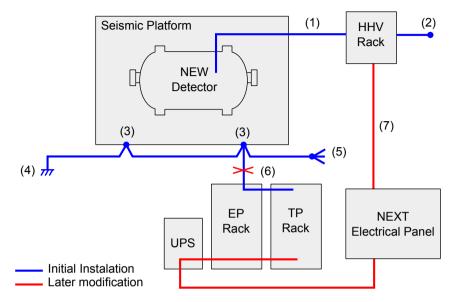

This thesis describes the studies and work done in the tracking plane, focused in the NEW detector, which rough scheme can be seen on figure 1. From the beginning the whole system needed to be redesigned, as the detector must be radiopure to have enough background rejection, and its size implies almost 1800 photosensors in the tracking plane, compared to the  $\sim 250$  working on NEXT-DEMO.

**Figure 1:** NEW Detector tracking plane scheme. The full signal chain from the silicon photomultipliers to the front-end electronics is shown.

The proposed objectives for this thesis were:

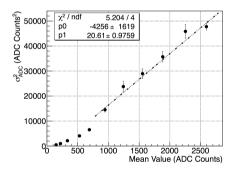

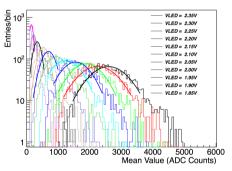

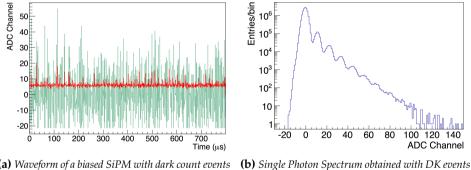

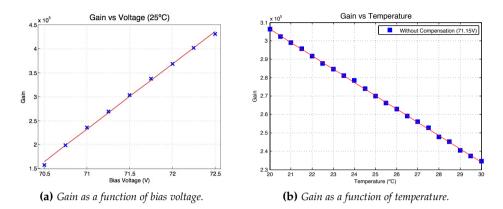

- Study of the silicon photomultipliers properties for different models and manufacturers, like gain dependence with bias voltage and temperature, dark count and noise.

- Design and production of a SiPM bias supply scalable for NEXT-100.

- Design and production of a front-end for the NEXT experiment silicon photomultipliers, fitting all the performance required.

- Design, production and installation of the SiPM carrier boards.

- Study of the NEXT experiment ground system.

Chapter 1 summarizes the NEXT experiment target, evolution, status and future. An introduction to neutrinoless double beta decay physics helps to understand the concept of the experiment and the implication on the physic research areas. Also the silicon photomultipliers are described in detail; its structure, working principle and performance. Chapter 2 focuses on the NEXT-DEMO tracking plane, the first SiPM pixel tracking system. It describes the whole chain of electronics, the different stages of the prototype and the first front-end electronics boards. The design requirements are also described, together with the status of the art in SiPM electronics. This acts as a base for further designs, like NEW.

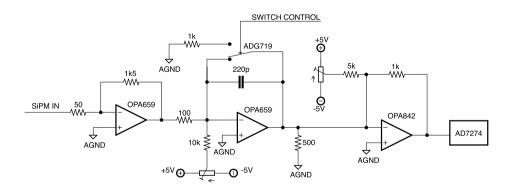

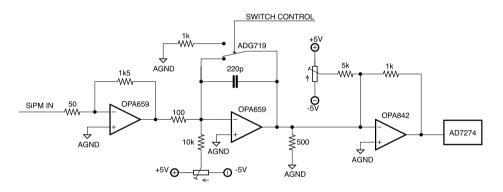

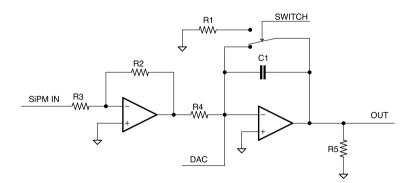

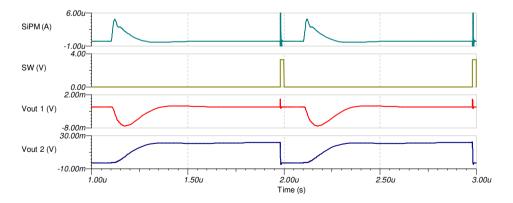

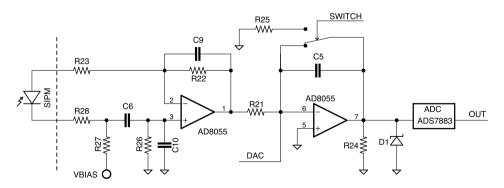

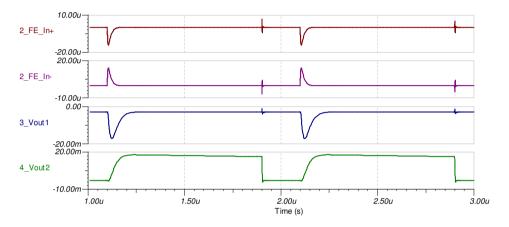

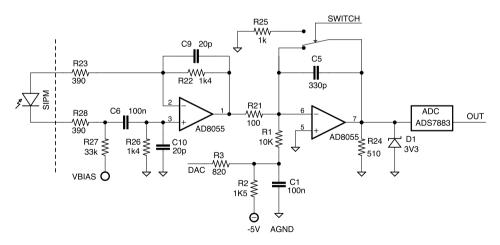

Then, on Chapter 3, firsts front-end prototypes are shown and explained. This involved several studies and simulations, trying to understand the optimal performance for the new requirements on the tracking plane. This development lead into a differential scheme for the SiPM readout, which entail a full redesign of the cabling and support boards for the photodetectors.

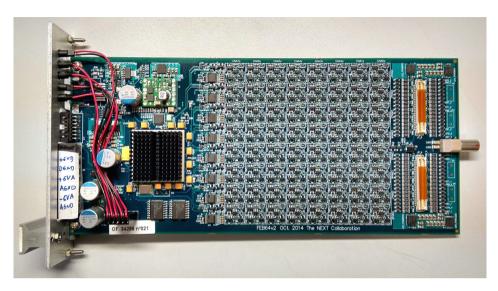

After the conclusions on Chapter 3, Chapter 4 describes the final design for the front-end electronic boards. These ones are able to provide the bias voltage, read, integrate and digitize 64 SiPMs. Compared to the previous front-ends in NEXT-DEMO, this one allows the readout of 4 times more SiPMs in half the board area. Also, as described in the chapter, some performance improvements were achieved; like noise reduction, less power consumption per channel and less cost per channel.

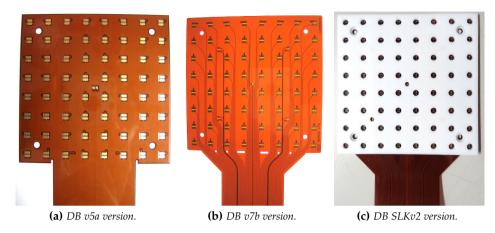

Chapter 5 shows the design of the support board for the SiPMs: the DICE-Boards. Two designs were made during the tracking plane development, for single-ended signals and for differential ones, as both schemes were considered for the front-end electronics.

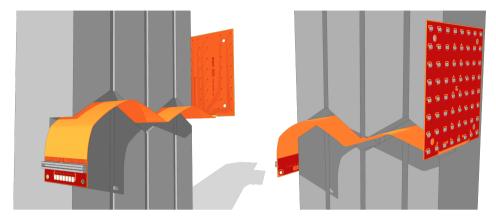

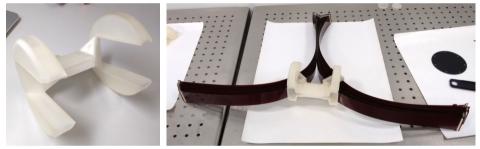

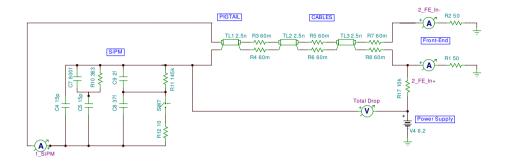

On Chapter 6 is described all the cabling done specifically for the SiPM tracking plane, both internal and external. This includes simulations and numerical studies, due to the difficulty of carrying the small current signals produced by the SiPMs along five meters of cable, in a noisy environment. A custom feedthrough was also designed, to solve the problem of supply the bias voltage and take out the signal of almost 1800 SiPMs. The solution came on a combination of electronics and mechanics, using a thick printed circuit board (PCB) as barrier between the pressurized xenon and the atmospheric air.

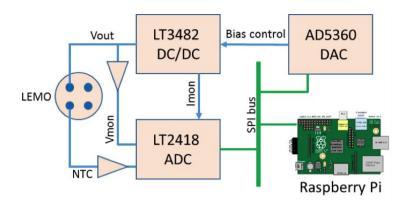

Chapter 7 describes the custom power supply unit designed by the collaboration, which allows to provide the bias voltage to the SiPMs and also stabilize the gain

of the whole tracking plane in a constant value, by compensating actively the bias as a function of temperature in the DICE-Boards.

Finally, Chapters 8 and 9 show the results and conclusions of the work described in this thesis. As said before, all the electronics and elements described here have been produced and installed in the NEW detector at the LSC (Laboratorio Subterráneo de Canfranc). By now, NEW has been successfully running for several weeks, and a huge amount of calibration data has been acquired.

Proudly, the tracking plane is fully functional; and hopefully it will be running for a long time.

"The scientific man does not aim at an immediate result. He does not expect that his advanced ideas will be readily taken up. His work is like that of the planter - for the future. His duty is to lay the foundation for those who are to come, and point the way."

– Nikola Tesla

## The NEXT Experiment

The Neutrino Experiment with a Xenon TPC (NEXT), will search for the neutrinoless double beta decay of  $^{136}$ Xe using a radiopure high-pressure xenon gas Time Projection Chamber (TPC) filled with 100 kg of Xe enriched in its  $^{136}$ Xe isotope. The experiment will be located at *Laboratorio Subterráneo de Canfranc*, which is carved into the rock at 850 meters deep below the Tobazo Mountain, on the Spanish side of the Pyrenees. NEXT will be the first large high-pressure gas TPC to use electroluminescence readout with SOFT (Separated, Optimized Functions TPC) technology. The following sections outline the most relevant aspects of the experiment, summarizing the neutrinoless double beta decay.

### **1.1** Neutrinoless Double Beta Decay ( $\beta\beta0\nu$ )

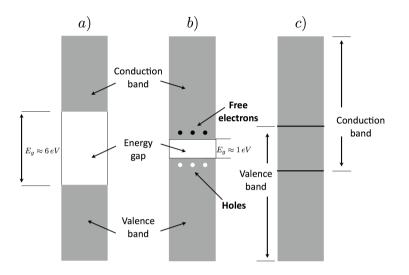

The Standard Model (SM) of Particle Physics is a theory concerning the electromagnetic, weak, and strong nuclear interactions, which describes fundamental properties of subatomic particles. This model works well in general, but there are still some missing pieces, many of them related to neutrinos. These particles are unique in many ways; in particular, their lack of color or electromagnetic charge means that, of the three fundamental forces described by the SM, they only feel the weak force. The Standard Model requires massless neutrinos in its basic formulation, but recent experiments on neutrino oscillations have demonstrated that they are massive particles, opening a new field of physics beyond the Standard Model.

Neutrinos might be the only particles having a Majorana mass term, forbidden to the other fermions, explaining the different mass scale of neutrinos compared with other fundamental particles. Experimental evidence of this phenomenon would have deep implications in physics and cosmology, since Majorana particles would be their own antiparticles as described by Majorana [Majorana 1937].

If neutrinos are Majorana particles, neutrinoless double beta decay ( $\beta\beta0\nu$ ) could be observable and a mean to prove this hypothesis. The simple existence of  $\beta\beta0\nu$ decay would prove that neutrinos are Majorana particles and that lepton number is not always conserved, while the decay rate would measure the Majorana neutrino mass.

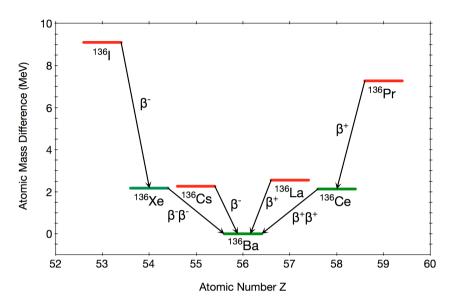

Double beta decay ( $\beta\beta$ ) is a very rare nuclear transition in which a nucleus with *Z* protons decays into a nucleus with *Z* + 2 protons and same mass number A. It can only be observed in those isotopes where the  $\beta$  decay mode is forbidden due to the energy of the daughter nuclei being higher than the energy of the parent nuclei, or highly suppressed. If this condition is fulfilled, two simultaneous  $\beta$  decays are possible.

Two  $\beta\beta$  decay modes are normally considered. The standard two neutrino double beta decay mode ( $\beta\beta2\nu$ ) was proposed by Goeppert-Mayer in 1935

**Figure 1.1:** Atomic masses of isotopes with A = 136 given as differences with respect to the most bound isotope, <sup>136</sup>Ba. The red levels indicate odd-odd nuclides, whereas the green indicate even-even ones. The arrows show the type of nuclear transition connecting the levels. Double beta (either plus or minus) transitions are possible because the intermediate state ( $\Delta Z = \pm 1$ ) is less bound, forbidding the beta decay [Justo Martín-Albo 2015].

[Goeppert-Mayer 1935] and has been observed in several nuclei, where an antineutrino associated to each electron is emitted. This process has typical lifetimes on the order of  $10^{18} - 10^{21}$  years.

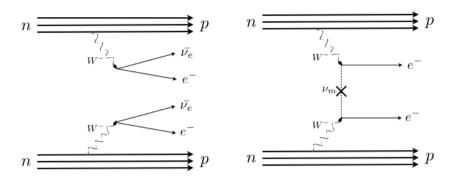

In the neutrinoless double beta decay mode ( $\beta\beta0\nu$ ) the electrons carry essentially all the energy released in the decay. This process, which was postulated by Furry in 1939 [Furry 1939] and has not been observed yet, is forbidden in the Standard Model of Particle Physics. The Feynman diagrams for both possible decays are represented on figure 1.2.

Only if neutrinos are massive Majorana particles, and therefore their own antiparticles,  $\beta\beta0\nu$  can take place. The anti-neutrino created in a vertex from one  $\beta$  decay virtually propagates to the other vertex, where it acts as a neutrino producing an electron via inverse beta decay. As the neutrino acts in a vertex as a neutrino and in the other as an anti-neutrino, this process is only possible

**Figure 1.2:** Feynman diagram for the  $\beta\beta 2\nu$  (left) and the  $\beta\beta 0\nu$  (right).

if both particles are the same. Additionally, the observation would demonstrate that total lepton number is violated in physical phenomena, an observation that could be linked to the cosmic asymmetry between matter and antimatter through the process known as leptogenesis.

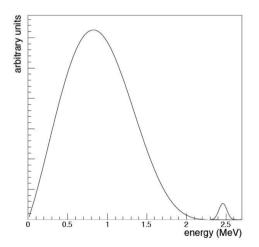

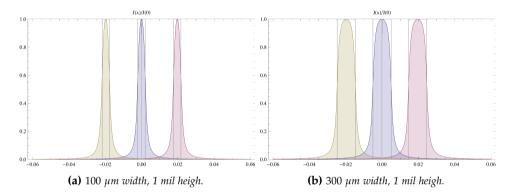

**Figure 1.3:** Energy spectrum of the electrons emitted in the  $\beta\beta$  decay of <sup>136</sup>Xe, as seen with a 1% FWHM energy resolution at  $Q_{\beta\beta}$ . The left peak corresponds to the  $\beta\beta2\nu$  decay, while the right peak, centered at  $Q_{\beta\beta} = 2458$  keV, corresponds to the  $\beta\beta0\nu$ . The normalization scale between the two peaks is arbitrary.

In the case of  $\beta\beta0\nu$ , the sum of the kinetic energies of the two released electrons is always the same, and corresponds to the mass difference between the parent and the daughter nuclei:  $Q_{\beta\beta} \equiv M(Z, A) - M(Z + 2, A)$ . However, due to the finite energy resolution of any detector,  $\beta\beta0\nu$  events are reconstructed within a non-zero energy range centered around  $Q_{\beta\beta}$ , typically following a gaussian distribution, as shown in figure 1.3. Other processes occurring in the detector can fall in that region of energies, thus becoming a background and compromising drastically the experiment's expected sensitivity to the effective Majorana neutrino mass ( $m_{\beta\beta}$ ).

#### $\beta\beta$ Experiments

The main goal of basically all double beta decay experiments is to measure the total energy of the radiation emitted by a  $\beta\beta$  source. In a neutrinoless double beta decay, the sum of the energies of the two emitted electrons is constant and equal to the mass difference between the parent and the daughter atoms ( $Q_{\beta\beta}$ ). Any experiment hoping to measure the  $\beta\beta0\nu$  half-life must be able to count the number of events at this energy due to  $\beta\beta0\nu$ . However, the measurement is limited by the experimental sensitivity of the detector employed.

Natural fluctuations and detector effects combine to smear the energy response and backgrounds from naturally occurring radioisotopes can pollute the energy region. For that reason, the materials with which the detector is built must be selected carefully to reduce the natural radioactivity present in all materials. In addition, double beta decay experiments must be placed at underground facilities, in order to reduce the background levels from atmospheric radiation. Finally, the intrinsic background from the standard two neutrino double beta decay mode, which has a continuous energy spectrum, can be problematic if the energy resolution is not very good.

Three experiments of the present generation are taking data already. On the one hand, the GERDA experiment [Lehnert 2014] looks for the neutrinoless double beta decay of <sup>76</sup>Ge at *Laboratori Nazionale del Gran Sasso*. In GERDA, high purity germanium detectors (HPGe) are arranged in strings and mounted in special low-mass holders made of ultra-pure copper and PTFE. The strings are

suspended inside a vacuum-insulated stainless steel cryostat of 4.2 *m* diameter and 8.9 *m* height filled with 64  $m^3$  of liquid argon. A copper lining 6 *cm* thick covers the inner cylindrical shell of the cryostat. The cryostat is placed in a 590  $m^3$  water tank instrumented with PMTs which serves as a Cherenkov muon veto as well as a gamma and neutron shield. The GERDA Collaboration has published a measurement of the  $\beta\beta 2\nu$  half-life of  $T_{1/2}^{2\nu}(^{76}Ge) = (1.926 \pm$  $0.095) \times 10^{21}$  years [Agostini et al. 2015] and a limit on the  $\beta\beta 0\nu$  half-life,  $T_{1/2}^{0\nu}(^{76}Ge) > 5.3 \times 10^{25}$  years (90% C.L.) [The GERDA Collaboration 2017].

On the other hand, there are xenon-based detectors like KamLAND-Zen [Gando et al. 2013], a transparent nylon-based balloon with 3.08 *m* diameter, containing 13 tons of liquid scintillator loaded with 320 kg of xenon (enriched to 91% in <sup>136</sup>Xe). The balloon is suspended by film straps at the center of a stainless steel spherical vessel with 1879 photomultiplier tubes mounted on the inner surface, which record the scintillation light generated by  $\beta\beta$  events occurring in the detector. With this configuration it has achieved an extrapolated energy resolution of 9.9% FWHM at the  $Q_{\beta\beta}$  value of <sup>136</sup>Xe, publishing recently a limit on the half-life of  $\beta\beta0\nu$  of  $T_{1/2}^{0\nu}(^{136}Xe) > 1.07 \times 10^{26}$  years.

In parallel, the EXO Collaboration has published a limit on the half- life of  $\beta\beta0\nu$  of  $T_{1/2}^{0\nu}(^{136}Xe) > 1.1 \times 10^{25}$  years [The EXO-200 Collaboration 2014] using the EXO-200 detector, a symmetric TPC filled with 110 kg of liquid xenon (enriched to 80.6% in <sup>136</sup>Xe). In EXO-200, ionization charges in the xenon created by charged particles drift towards the two anodes of the TPC due to the presence of an electric field. Events in the chamber are reconstructed by a pair of crossed wire planes which measure their amplitude and transverse coordinates, and an array of avalanche photodiodes (APDs), which detect the 178 *nm* xenon scintillation light. The sides of the chamber are covered with teflon sheets that act as VUV reflectors, improving the light collection. The EXO-200 detector has achieved an energy resolution of 4% FWHM at the  $Q_{\beta\beta}$  value of <sup>136</sup>Xe.

In the following section, a new neutrinoless double beta decay experiment is introduced: the NEXT experiment, which will search for neutrinoless double beta decay of  $^{136}$ Xe at *Laboratorio Subterráneo de Canfranc* with the NEXT-100 detector. Such a detector, containing 100 kg of  $^{136}$ Xe, thanks to its excellent

and demonstrated energy resolution, together with a high efficiency background rejection, will be one of the leading experiment in the field, exploring the region of neutrino mass lower than 100 *meV*.

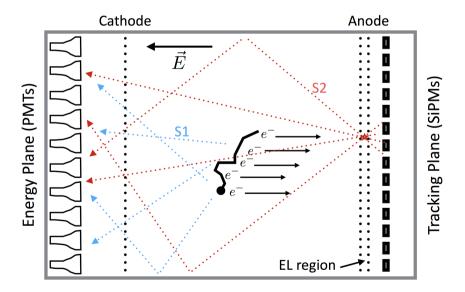

### 1.2 NEXT Concept

The NEXT detector uses the Separated, Optimized Functions TPC (SOFT) concept (figure 1.4), which consists in the idea that tracking and energy measurements are performed separately [Nygren 2009]. Using this concept, both energy resolution and tracking described in the previous sections can be achieved. When a charged particle interacts with the high pressure xenon, ionizes and excites its atoms. The excitation energy results is the prompt emission of VUV ( $\sim 172 \text{ } nm$ ) scintillation light (S1) which is detected by a plane of PMTs located behind a transparent cathode in one side of the TPC and giving the start-of-event ( $t_0$ ).

**Figure 1.4:** The Separated, Optimized Functions TPC (SOFT) concept. EL (Electroluminescence) light generated at the anode is recorded in the photosensor plane right behind it and used for tracking. It is also recorded in the photosensor plane behind the transparent cathode and used for a precise energy measurement.

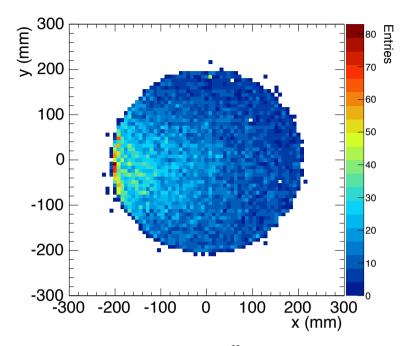

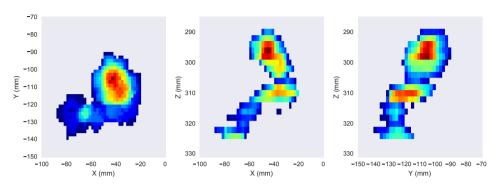

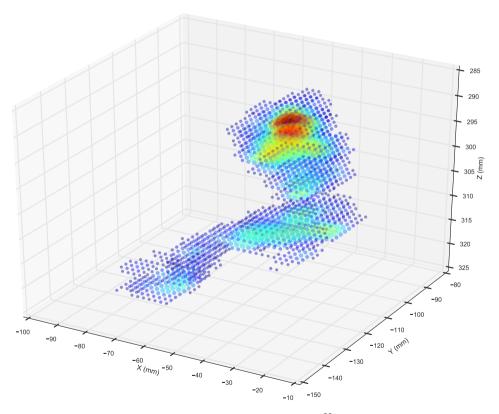

The ionization electrons left by the passage of the charged particle are prevented from recombining by an electric field which causes them to drift towards the TPC anode where they enter a region of more intense electric field between two meshes. In this region they are accelerated and induce the production of secondary excitation of xenon atoms without secondary ionization, by electroluminescence (EL) amplification. The EL light (S2) is generated a few millimeters away from an array of Silicon Photomultipliers (SiPMs), which form the tracking plane, providing the track of the event. As EL light is emitted isotropically, roughly half will reach the PMT plane, since now energy plane, giving a precise energy measurement. The advantage of the separate functions for the two measurements is the decoupling of the operational configuration between the two planes of sensors, which gives more freedom to modify the operational parameters of each set, optimizing the performance of the whole detector.

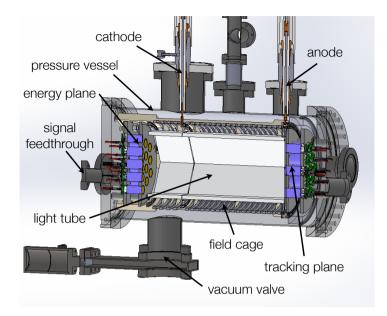

### 1.3 NEXT-DEMO

NEXT-DEMO [Álvarez et al. 2013a], shown in figure 1.5, is a high-pressure xenon electroluminescent TPC implementing the NEXT detector concept described above. Its active volume is 30 *cm* long and 30 *cm* diameter. A tube of hexagonal cross section made of PTFE is inserted into the active volume to improve the light collection. The TPC is housed in a stainless-steel pressure vessel that can withstand up to 15 *bar*. Natural xenon circulates in a closed loop through the vessel and a system of purifying filters. The detector is not radiopure and is not shielded against natural radioactivity. It is installed in a semi-clean room (see figure 1.6) at the *Instituto de Física Corpuscular* (IFIC), in Valencia, Spain.

The main objective of NEXT-DEMO was the validation of the NEXT-100 design. More specifically, the goals of the prototype were the following: (a) to demonstrate good energy resolution in a large active volume; (b) to reconstruct the topological signature of electrons in high-pressure xenon gas (HPXe); (c) to test long drift lengths and high voltages; (d) to understand gas recirculation and purification in a large volume, including operation stability and robustness

Figure 1.5: Cross-section drawing of the NEXT-DEMO detector with all major parts labelled.

against leaks; and (e) to understand the collection of light and the use of wavelength shifters (WLS).

The initial operation of NEXT-DEMO had a tracking plane implemented using 19 pressure-resistant photomultipliers, identical to those used in the energy plane but operated at a lower gain. Instrumenting the tracking plane with PMTs — unlike NEW and NEXT-100, which will use SiPMs — during the first period simplified the initial commissioning, debugging and operation of the detector due to the smaller number of readout channels (19 PMTs in contrast to the 248 SiPMs projected for the second phase of NEXT-DEMO) and their intrinsic sensitivity to the UV light emitted by xenon. Later the tracking plane was updated, and the PMTs were replaced by SiPMs as will be detailed on Chapter 2.

The detector response was studied under two different conditions: an ultraviolet configuration (UVC) in which the PTFE light tube had no coating; and a blue configuration (BC) in which the panels were coated with tetraphenyl butadiene

**Figure 1.6:** The NEXT-DEMO detector and ancillary systems (gas system, front-end electronics and DAQ) in their location at a semi-clean room at IFIC.

(TPB), a wavelength shifter, in order to study the possible improvement in light collection.

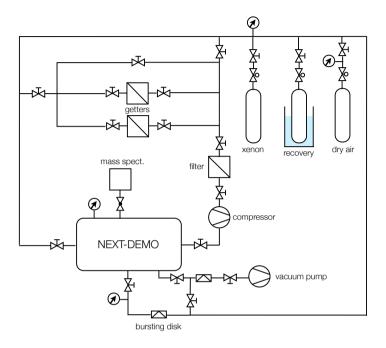

#### Gas system

The functions of the gas system of NEXT-DEMO are the evacuation of the detector, its pressurization and depressurization with xenon (and argon), and the recirculation of the gas through purification filters. A schematic of the system is shown on figure 1.7.

The standard procedure during normal operation of the detector starts with the evacuation of the vessel to vacuum levels around  $10^{-5}$  *mbar*, followed by an argon purge. A second vacuum step exhausts the argon from the system. The detector is then filled with xenon gas to pressures up to 15 *bar*. The xenon can be cryogenically recovered to a stainless-steel bottle connected to the gas system

Figure 1.7: Simplified schematic of the gas system of NEXT-DEMO.

by simply immersing this in a dewar filled with liquid nitrogen. The pressure regulator of the bottle is fully opened to allow the xenon gas to flow inside it (due to the temperature difference) and freeze.

The vacuum pumping system consists of a roughing pump (*Edwards XDS5* scroll vacuum pump) and a turbo molecular pump (*Pfeiffer HiPace 300*). Vacuum pressures better than  $10^{-7}$  *mbar* have been obtained after pumping out the detector for several days. The recirculation loop is powered by an oil-less, single-diaphragm compressor (*KNF PJ24999-2400*) with a nominal flow of 100 standard liters per minute. This translates to an approximate flow of 10 liters per minute at 10 *bar*, thus recirculating the full volume of NEXT-DEMO (~ 45 *L*) in about 5 minutes. The gas system is equipped with both room-temperature (*SAES MC50*) and heated *getters* (*SAES PS4-MT15*) that remove electronegative impurities (O<sub>2</sub>, H<sub>2</sub>O, etc.) from the xenon. All the gas piping, save for the inlet gas hoses

and getter fittings, are 1/2 inch diameter with VCR<sup>1</sup> fittings. A set of pressure relief valves (with different settings for the various parts of the system) and a bursting disk in the vacuum system protect the equipment and personnel from overpressure hazards.

The operation of the gas system has been, in general, very stable. The detector has run without interruption for long periods of up to 6 weeks with no leaks and continuous purification of the gas.

#### Pressure vessel

NEXT-DEMO pressure vessel is a stainless-steel (grade 304L) cylindrical shell, 3 *mm* thick, 30 *cm* diameter and 60 *cm* length, welded to CF<sup>2</sup> flanges on both ends. The two end-caps are 3 *cm* thick plates with standard CF knife-edge flanges. Flat copper gaskets are used as sealing. The vessel was certified to 15 *bar* operational pressure. It was designed at IFIC and built by *Trinos Vacuum Systems*, a local manufacturer. Additional improvements — including the support structure and a rail system to open and move the end-caps — have been made using the mechanical workshop at IFIC.

The side of the chamber includes 8 CF40 half-nipples. One set of 4 is located in the horizontal plane while the other is displaced towards the underside with respect to the first set by  $60^{\circ}$ . These contain radioactive source ports used for calibration of the TPC. The ports are made by welding a 0.5 *mm* blank at the end of a 12 *mm* liquid feedthrough. On top of the vessel and along the vertical plane there are three additional half-nipples (CF130, CF67 and CF80) used for high-voltage feeding and connection to a mass spectrometer (through a leak valve). On the opposite side, at the bottom, a CF100 port connects the pressure vessel to the vacuum pumping system. A guillotine valve closes this connection when the vessel is under pressure. The end-caps include several CF ports for the connections to the gas recirculation loop and for the feedthroughs (power and signal) of the PMT planes.

<sup>&</sup>lt;sup>1</sup>VCR are metal gasket face seal fittings commonly used in pressurized gas systems which require good tightness levels.

<sup>&</sup>lt;sup>2</sup>CF flanges use a copper gasket and knife-edge flange to achieve an ultrahigh vacuum seal. A number following this designation indicates the tube inner diameter in millimeters.

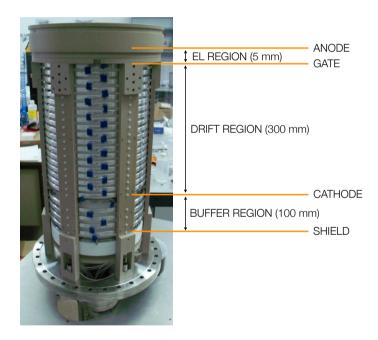

#### Time projection chamber

Three metallic wire grids — referred to as *cathode*, *gate* and *anode* — define the two active regions of the chamber (see figure 1.8): the 30 *cm* long *drift region*, between cathode and gate; and the 0.5 *cm* long *EL region*, between gate and anode. Gate and anode were built using stainless-steel meshes with 88% open area (30  $\mu$ m diameter wires, 50 wires/inch) clamped in a tongue-and-groove circular frame with a tensioning ring that is torqued with set screws to achieve the optimum tension. The cathode was built in a similar fashion by clamping parallel wires 1 *cm* apart into another circular frame.

**Figure 1.8:** *External view of the time projection chamber mounted on one end-cap. The approximate positions of the different regions of the TPC are indicated.*

The electric field in the TPC is created by supplying a large negative voltage to the cathode and then degrading it across the drift region using a series of metallic rings of 30 *cm* diameter spaced 5 *mm* apart and connected via 0.5  $G\Omega$  resistors. The rings were manufactured by cutting and machining aluminum pipe. The gate is at negative voltage so that a moderate electric field — up to

$1 \ kV/cm$  — is created towards the cathode; and a high electric field — typically of 2.5 to 3 kV cm<sup>-1</sup> bar<sup>-1</sup> — is created between the gate and the anode, which is at ground. A *buffer region* of 10 *cm* between the cathode and the energy plane protects this from the high-voltage by degrading it safely to ground potential.

The high voltage is supplied to the cathode and the gate through custom-made high-voltage feed-throughs (HVFT) built pressing a stainless-steel rod into a Tefzel (a plastic with high dielectric strength) tube, which is then clamped using plastic ferrules to a CF flange. They have been tested to high vacuum and 100 kV without leaking or sparking.

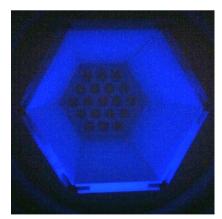

A set of six panels made of PTFE (Teflon) are mounted inside the electricfield cage forming a *light tube* of hexagonal cross section (see figure 1.9) with and apothem length of 8 *cm*. PTFE is known to be an excellent reflector in a wide range of wavelengths [Silva et al. 2009], thus improving the light collection efficiency of the detector. In a second stage, the panels were vacuum-evaporated with TPB — which shifts the UV light emitted by xenon to blue ( $\sim 430 \text{ } nm$ ) — in order to study the improvement in reflectivity and light detection. Figure 1.9b shows the light tube illuminated with a UV lamp after the coating.

(a) The meshes of the EL region can be seen in the foreground, and in the background, at the end of the light tube, the PMTs of the energy plane are visible.

**(b)** *The light tube of NEXT-DEMO illuminated with a UV lamp after being coated with TPB.*

Figure 1.9: View of the light tube from the position of the tracking plane.

Six bars manufactured from PEEK, a low outgassing plastic, hold the electricfield cage and the energy plane together. The whole structure is attached to one of the end-caps using screws, and introduced inside the vessel with the help of a rail system. All the TPC structures and the HVFT were designed and built by *Texas A&M*.

### **Detection planes**

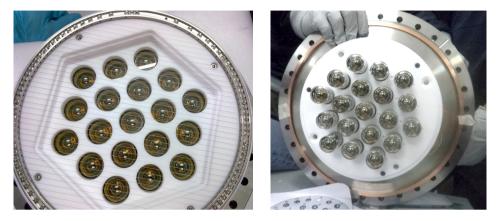

In NEXT-DEMO, the energy plane (see figure 1.10, left panel) is equipped with 19 *Hamamatsu R7378A* photomultiplier tubes. These are 1 *inch*, pressure-resistant (up to 20 *bar*) PMTs with acceptable quantum efficiency ( $\sim$  15%) in the VUV region. The resulting photocathode coverage of the energy plane is about 39%. The PMTs are inserted into a PTFE holder following an hexagonal pattern. A grid, known as *shield* and similar to the cathode but with the wires spaced 0.5 *cm* apart, is screwed on top of the holder and set to electrical ground. As explained above, this protects the PMTs from the high-voltage set in the cathode, and ensures that the electric field in the 10 *cm* buffer region is below the EL threshold.

As mentioned already, the first tracking plane of NEXT-DEMO detector also uses 19 *Hamamatsu R7378A* PMTs, as shown on figure 1.10 (right), but operated at lower gain. They are also held by a PTFE honeycomb, mirroring the energy plane. The PMT windows are located 2 *mm* away from the anode mesh. Position reconstruction is based on energy sharing between the PMTs, being therefore much better than the distance between PMTs (35 *mm* from center to center).

The PMTs are connected to custom-made electronic bases that are used as voltage dividers, and also allow the extraction of the signal induced in the PMTs. This requires a total of 38 cables (on each side, as both planes have PMTs) inside the pressure vessel connected via feedthroughs.

**Figure 1.10:** The energy (left) and tracking (right) planes of NEXT-DEMO, each one equipped with 19 Hamamatsu R7378A PMTs.

### **Electronics and DAQ**

The two optical primary signals in the NEXT-DEMO detector are in very different scales, and the photomultipliers and their front-end electronics must be ready to handle both. Primary scintillation results in weak (a few photoelectrons per photomultiplier) and fast (the bulk of the signal comes in about 20 *ns*) signals, whereas the secondary scintillation — that is, the EL-amplified ionization — is intense (hundreds to thousands of photoelectrons per PMT) and slow (several microseconds long).

The gain of the PMTs in NEXT-DEMO was adjusted to around  $5 \times 10^6$  for the energy plane to place the mean amplitude of a single photoelectron pulse well above electronic system noise, and approximately half that for the tracking plane since they record the direct secondary-scintillation light produced in the EL region and, as such, would have a higher probability of saturation at the same gain as those of the cathode.

The PMTs produce fast signals (less than 5 *ns* wide) making necessary the shaping and filtering of the detector output so that they match the sampling rate of the digitizer. This process also performs the important function of eliminating high frequency noise. A first low pass filter is implemented by

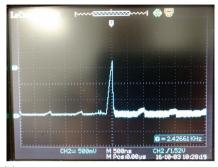

adding a capacitor and a resistor to the PMT base output. The charge integration capacitor shunting the anode stretches the pulse and reduces the primary signal peak voltage accordingly. The design uses a single amplification stage based on a fully differential amplifier THS4511, which features low noise  $(2 \text{ nV}/\sqrt{\text{Hz}})$ and provides enough gain to compensate for the attenuation in the following stage. Amplification is followed by a passive CRC filter with a cut-off frequency This filtering produces enough signal stretching to allow the of 800 kHz. acquisition of many samples per single photo-electron at 40 MHz. The front-end circuit for NEXT-DEMO was implemented in 7 channel boards and connected via HDMI cables to 12-bit 40 MHz digitizer cards. These digitizers are read out by the FPGA-based DAQ modules (FEC cards) that buffer, format and send event fragments to the DAQ PCs. As for the FEC card, the 16-channel digitizer add-in card was designed in a joint effort between CERN and the NEXT Collaboration within the RD-51 program [Martoiu et al. 2011]. These two cards are edge mounted to form a standard 6U 220 mm Eurocard. An additional FEC module with a different plug-in card is used as trigger module. Besides forwarding a common clock and commands to all the DAQ modules, it receives trigger candidates from the DAQ modules, runs a trigger algorithm in the FPGA and distributes a trigger signal. The trigger electronics also accepts external triggers for detector calibration purposes.

As said before, the first tracking plane was implemented using the same PMTs than the energy plane, but the real tracking plane (TP) was intended to be with silicon photomultipliers (SiPMs) as NEXT-100 will be. As this thesis focuses on the SiPM TP, the NEXT-DEMO tracking plane with SiPMs is detailed on Chapter 2, and the electronics developed for it are explained on sections 2.3 and 3.1.

# 1.4 NEW

NEXT-DEMO was the prove of concept for the NEXT experiment, and still is a bench for tests that may extend our knowledge and understanding. And the so called NEXT-100 detector will be a radiopure detector that will start operation in *Laboratorio Subterráneo de Canfranc* (LSC) in the following years.

Between them we find the NEW (NExt-White) detector, which really is the first stage of the NEXT experiment (figure 1.11). The primary goal of NEW is to provide an intermediate step in the construction of the NEXT-100 detector that would allow the validation of the technological solutions proposed in the TDR [Álvarez et al. 2012c]. In addition, NEW would permit a measurement of the energy resolution at high energy, and the characterization of the 2-electron topological signature, by measuring the  $\beta\beta 2\nu$  mode. Finally, NEW will permit a realistic assessment of the NEXT background model before the construction of the NEXT-100 detector.

Figure 1.11: NEW detector pressure vessel.

#### Gas system

The gas system used for the NEW detector is almost the same than the one for NEXT-100, because both detectors have the same gas requirements except, of course, for the volume. Thereby, once the NEXT-100 detector is ready, the only parts that we will need to change are the vessel and the recovery tanks.

The functions of the gas system are the same described for NEXT-DEMO: pressurize and depressurize the system, recirculate and clean the gas, and evacuate the detector. However, the reliability that we have to acquire for NEW

and NEXT-100 is enormous due to the xenon cost, so the gas system has become a huge subsystem. So only some parts will be described.

This reliability level can not be achieved just with passive components, because there are some decisions that require a minimum of "intelligence". For this reason the gas system has been fully automated, using a *Compact RIO*; a FPGA-based PLC (Programmable Logic Controller) from *National Instruments*. The *Compact RIO* runs a real time *LabVIEW* variant, and has connections for monitoring the whole system (pressure gauges, vacuum gauges, valves, compressor, chiller...) and acts properly opening and closing the valves that control the gas flow. The *Compact RIO* is also connected to the Slow Control net, so all the parameters can be used to generate the proper reports, alarms and interact with the other elements connected to this net, explained later.

For the gas evacuation, the standard procedure allows to liquefy the gas stored in the whole system using a custom cryo-recovery bottle. This bottle is cooled carefully with liquid nitrogen, so the gas is recovered slowly by the depressurization created. Then, a vacuum pump is used to recover the residual gas in the vessel and the rest of the pipes.

(a) Cryo-recovery bottle.

**(b)** *Carten valve connected to the* **(c)** *NEXT-100 vessel used as tracking plane side for evacuation. emergency recovery tank.*

Figure 1.12: Different parts of the NEW gas system involved in gas recovery.

But this method is too slow in case of emergency due to, for instance, a leak in the system. For that reason we needed the emergency recovery tank. This tank is kept at a moderate vacuum and its volume is calculated to hold the whole gas in the experiment at  $\sim 1 \text{ bar}$ . Then, during normal operation, if an anomaly is detected and the gas on the experiment is compromised, a big *Carten* valve (figure 1.12b) is automatically opened and the gas flows quickly from the vessel to the tank through a 4" pipe. Once there, the gas can be redirected to the cryorecovery bottle to safely store the gas. As shown on figure 1.12c, during the NEW phase the NEXT-100 vessel is used as recovery tank, as it has the desired volume for this function and allows the collaboration to save money.

The compressor for the gas recirculation (figure 1.13b) was built by the *SERA* company, according our specific requirements for pressure, reliability and leak rate. As the compressor has to be running continuously during the data taking periods, it needs to be cooled to guarantee the performance. For this reason it is connected to a chiller device, which is automatically controlled by the *Compact RIO* each time the compressor is running.

(a) Gas system frame with the main components.

(b) Compressor.

(c) Compact RIO cabinet.

Figure 1.13: Different parts of the NEW gas system involved in gas recirculation.

On figure 1.13a the gas system frame is shown. Here are placed most of the manual valves, which are the ones that are too critical to rely on an automated system, lot of pipes to redirect the gas flow and the getters. This getters are

used, same as in NEXT-DEMO, to clean the gas from impurities that deteriorate the energy measurement in the detector. Two types of getters are used: the cold getters, which clean the gas from  $O_2$ ,  $H_2O$ , CO,  $H_2$ , volatile acids, organics, refractory compounds and volatile bases; and the hot getter, which outlet impurity levels for  $O_2$ ,  $H_2O$ , CO,  $CO_2$ ,  $H_2$ ,  $N_2$  and  $CH_4$  are reduced to low parts per billion (ppb) levels or below.

Also for gas cleanliness purpose, several vacuum pumps are distributed and connected at some points of the gas system. This allows to have the whole gas system at vacuum, which is desirable to clean all the pipes, valves and volumes before the clean gas is introduced; and also allows to find leaks on the system. An additional vacuum pump is connected also to the energy plane volume because, as will be explained, this entire cavity needs a good vacuum for the PMTs to operate safely and for easier leak detection.

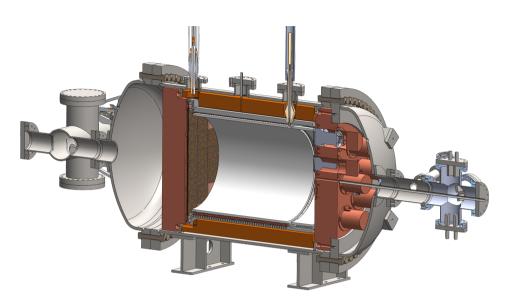

### Pressure vessel

The NEW pressure vessel has been manufactured with the same 316Ti steel alloy selected for the NEXT-100 detector, from *Nironit* [Maneschg et al. 2008] [Aprile et al. 2011]. The fabrication of the vessel was made possible thanks to a *CEDETI* grant. Figure 1.11 shows the pressure vessel before placing it in the operation platform, where will be surrounded by the lead castle; and figure 1.14 shows the cross-section of the vessel, with its inner parts.

With an internal diameter of 64 cm and a length of 950 cm, the dimensions of NEW are intermediate between NEXT-DEMO and NEXT-100. By design the pressure vessel can hold up to 50 *bar*, and it is **CC** certified to 20 *bar*.

For shielding purposes inside the vessel there are 6 *cm* thick copper bars, covering all the cylinder. The bars are designed with a stepped profile, so each one matches the adjacent bars. This way there are no straight paths for outer particles to getting into the active volume. Also, as can be seen on figure 1.14, both detection planes have big copper plates with 12 *cm* thickness. This ensures that all the active volume is properly shielded form any direction. However,

**Figure 1.14:** Cross-section view of the NEW detector. The tracking plane (on the left) holds 28 DICE-Boards for the tracking reconstruction, and the energy plane (right) has 12 PMTs for the precise energy measurement.

there are some openings in the copper, placed to allow the detector calibration using radioactive sources outside the vessel.

### **Time Projection Chamber (TPC)**

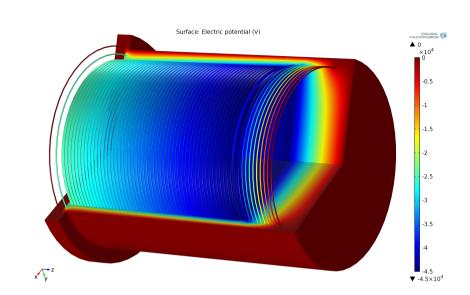

#### Simulation

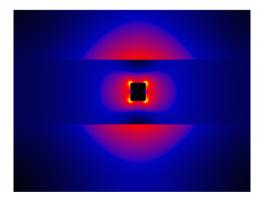

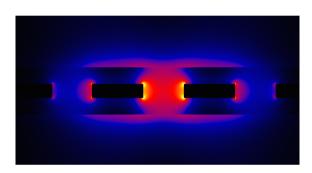

The electric field of the field cage has been simulated with finite elements algorithms using *COMSOL Multiphysics*. All the geometry was imported and the electric field was computed for the whole field cage (figure 1.15). In order to see the variations of the electric field across the field cage a detailed study of the critical regions of the field cage has been performed.

**Figure 1.15:** The NEW field cage electric field was simulated using finite elements software (COMSOL Multiphysics).

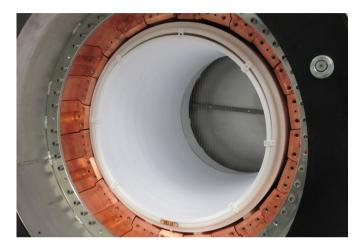

### Field Cage

The NEW field cage design is based on a high density polyethylene (HDPE) cylindrical shell, 25 *mm* thick, which isolates the copper shield from the voltage in the copper rings and the cathode. The rings are placed inside grooves and connected by copper clamps to a resistor chain. The field cage has an outer diameter of 500 *mm* and a length of 500 *mm*. Thus, both the longitudinal and radial dimensions are roughly half of those of NEXT-100.

The drift region in high pressure xenon needs of a moderate electric field (300 - 600 V/cm), thus a maximum voltage of 30 kV (for a drift of 500 mm) is foreseen in the cathode. This electric field is enough to avoid electron recombination in gas and drift the charges towards the anode. On the other hand, the field in the drift region should be highly uniform and homogeneous trying to avoid any radial component of the field. Those field characteristics are mandatory to ensure no charge losses in the walls during the drifting process.

The rings in the drift region are made out of electrolytic copper which section is a rounded rectangle of  $10 \times 3mm$  and 0.5mm radius on the edges. The rings are

(a) Field cage before being installed. (b) HDPE supports to keep the (c) Detail of the copper rings field cage in place. attached to the resistor chain.

Figure 1.16: NEW field cage details during assembly.

inserted in grooves inside the high density polyethylene body of the field cage. These grooves are 4 *mm* in depth, allowing some space between the surface of the ring and the wall of the field cage that is necessary to support the light tube inside the field cage.

#### Cathode

In the energy plane side (where the PMTs are) the field cage is terminated by a transparent cathode grid (figure 1.17a), placed at 100 *mm* from the PMTs. The cathode is the section with the highest voltage, which produces the electric field towards the gate, but also towards the PMTs along what we have called "the buffer".

The buffer zone is necessary to degrade the electric potential from the cathode to near zero volts at the PMT window surface. In that region of the TPC we do not demand the electric field to be highly uniform and then different degrading options are possible. The current design degrades the voltage without using rings, trying to avoid electric fields regions near the breakdown. In order to protect the PMTs against the electric field, their windows are coated with ITO (Indium-Tin Oxide), a transparent conductive molecule. The polyethylene in the buffer region is slightly thinner (15 *mm*) than in the drift region to give enough space to introduce the cathode inside the field cage.

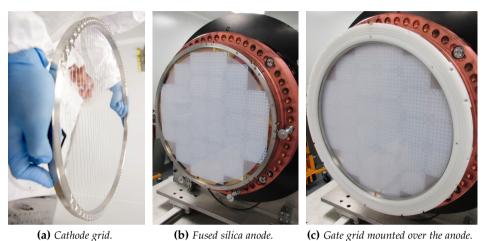

**Figure 1.17:** NEW field cage cathode, anode and gate, during the installation on June 2016.

### Gate & EL region

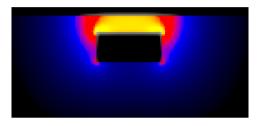

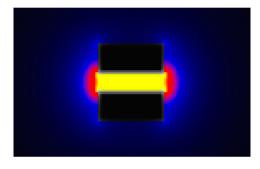

The solution for the EL region is to use a mixture between a mesh for the gate (figure 1.17c) and a solid quartz (fused silica) plate coated with Indium-Tin Oxide (ITO) as anode (figure 1.17b). This coating results in a  $\sim$  90% transparency conductive layer that allows to fix a voltage in the surface of the quartz plate and then creates an homogeneous field in the EL region. The quartz plate has to be coated with TPB to shift the VUV light of the Xenon electroluminescence to blue, to be detected by the tracking plane SiPMs.

The quartz plate solution has multiple advantages. First, it protects the SiPMs from sparking and then there is no need to coat the SIPMs. Second, it removes the necessity for tension and strength at one side of the mesh, only a small ring surrounding the edge of the ITO coating is needed to prevent sharp edges of the conductive layer. Last, the production of the quartz plate is simpler and cheaper than the mesh.

Both anode and gate are assembled in the tracking plane copper plate, so the distance between the anode and the SiPMs can be precisely adjusted. Then a spring contact in the gate connects it electrically to the field cage.

#### **Resistor** Chain

The resistor chain has two purposes: to hold together the two sides of the different rings, and to connect the rings by resistors. Thereby a voltage divider is created and the potential is uniformly degraded.

**Figure 1.18:** NEW resistor chain in two pieces before the assembly on the field cage. The chain shown is the first FR4 prototype, made to test the field cage performance before the final one is produced.

The NEW resistor chain (figure 1.18) will be mounted on a *CuFlon* board connecting every ring to the next one and also the cathode and the gate to their closest rings. The resistors need to hold high voltage and their tolerance needs to be minimum to guarantee homogeneity in the electric field. Instead of using just one resistor between rings we have mounted two parallel 10  $G\Omega$  resistors, to safeguard a possible resistor failure. These values may be soon decreased by one order of magnitude, as the high voltage modules can provide enough current and the power dissipation will be performed by the copper rings according to the calculations. This change will have the benefits of making it easier to

find radiopure resistors and reducing the effect of parasitic conductance and capacitance.

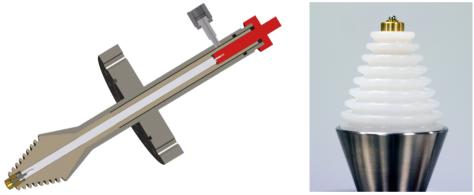

### High Voltage Feedthroughs

The voltages needed for NEW operation are similar to the NEXT-DEMO requirements. The design has been slightly modified for a better connection with the cathode and gate in the NEW detector.

(a) *HV* feedthrough design cross section.

**(b)** *HV feedthrough tip detail.*

Figure 1.19: High voltage feedthroughs designed for NEW.

The feedthroughs have been completely redesigned to ensure that they hold easily the 50 *kV* considered as the maximum requirement for normal operation. The design is based on an original idea by H. Wang presented in the "*High Voltage in Noble Liquids for High Energy Physics*" workshop held at *Fermilab* [Rebel et al. 2014].

### Light Tube

The light tube (figure 1.20) consists of a hollow PTFE cylinder, placed inside the field cage. It is the most internal part of the detector, where the events of interest are produced. For the same reasons explained before for the NEXT-DEMO detector, the inner side of the light tube has been coated with TPB. Due to the big size of the pieces, the coating was made at the facilities of the *Laboratori Nazionali del Gran Sasso* (LNGS) by the members of the NEXT collaboration.

Figure 1.20: NEW light tube, made of PTFE.

The light tube has a inner diameter of 416 *mm*, and a wall of just 10 *mm*. Due to the tricky design parameters, the one showed in the picture is made by several rings attached together; but a new one will be produced in just one piece and will be installed in the next detector upgrade.

Near the cathode there is a small support that prevents it from touching the cathode wires. The light tube does not need any fixing to the field cage, it is supported by friction to it.

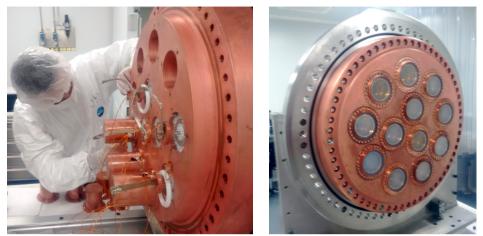

### **Energy Plane**

The design of the energy plane (shown on figure 1.21) consists of a 12 *cm* thick copper support plate with 12 copper window surrounds with brazed sapphire windows fixed to the front of the plate and covering the 12 apertures through which the PMTs will be fed. The set-up as a whole seals the pressure vessel from the torispherical head which will be held at vacuum levels of  $\sim 10^{-4}$  *mbar*.

Additional copper shielding (see figure 1.21a) will be fixed to the vacuum side of the apertures to guard against gammas traversing the PMTs and entering in

(a) Back side of the energy plane being installed. The PMTs are placed inside the holes, and covered with a 12 cm copper "hat".

(b) Front side of the energy plane. The sapphire windows isolate the vacuum from the pressure.

Figure 1.21: NEW energy plane during installation on July 2015.

the detector volume. The 12 *Hamamatsu R11410-10* PMTs are optically coupled to the sapphire window using *NyoGel OCK-451* and held in place by a HDPE brace and spring.

In order to improve the light recollection, the sapphire windows were coated with TPB. And to protect the PMTs from TPC the electric field, the windows were also coated with a conductive layer of ITO, the same used for the fused silica plate on the field cage.

The PMTs are supplied with high voltage and have their signal extracted via a shielded twisted pair cable connected to a custom feedthrough in the torispherical head. The distribution of signal and supply at each individual PMT is controlled via *Kapton* circuit board (base) which has the resistor divider to properly fed the PMT dynodes. Then the base is covered with a copper cap filled with epoxy which is connected by a braid to the support plate, to allow generated heat to be dissipated in the vacuum conditions.

Figure 1.22: PMT and its polarization base used in NEW.

### **Tracking Plane**

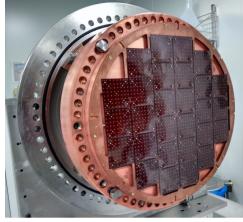

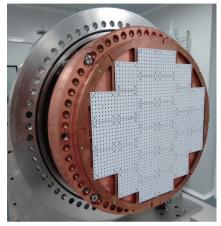

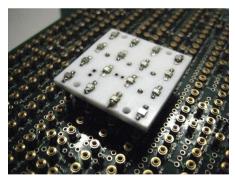

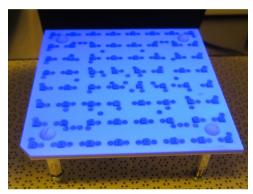

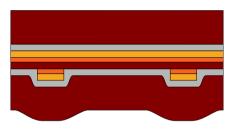

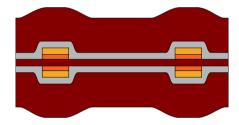

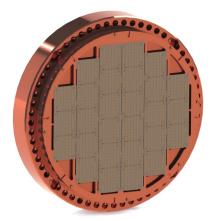

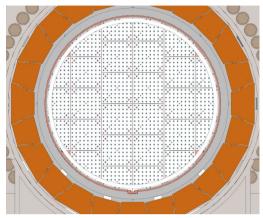

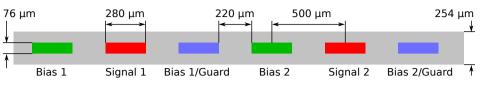

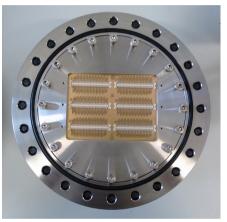

The NEW tracking plane is made of 28 *Kapton* DICE-Boards (KDB). Each KDB has an  $8 \times 8$  SiPM array placed with 1 *cm* pitch, a NTC temperature sensor and four LEDs for calibration. The KDBs over-cover the fiducial region with ~ 1800 SiPMs, ensuring that there are no dead regions. The connector is located at the end of a long tail, and is screened from the gas, in the fiducial volume, by a 120 *mm* thick copper plate shield.

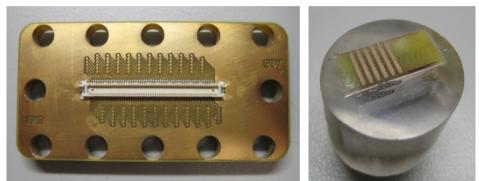

The DICE-Boards (DBs) for NEXT-DEMO were made of multi-layer *CuFlon*, and their radioactivity budget was moderately high, due to the adhesive needed to glue the layers. Two additional problems with the DBs were the need to solder SiPMs by hand (since *CuFlon* does not tolerate the temperatures of an oven) and the need to use connectors (all of which are known to be non radiopure).

The new KDBs for NEW solve all the above issues. The material is *Kapton*, and the measured radioactivity budget (only upper limits) is one order of magnitude less than in the old DBs. In addition, TPB was coated directly on top of the DEMO DBs. Instead, the design of the electroluminescent region with a quartz plate allows for a direct coating of the plate instead of the individual DICE-Boards.

(a) Tracking plane installation on November 2015.

**(b)** *Tracking plane upgrade with PTFE masks on April 2016.*

Figure 1.23: NEW tracking plane.

To improve the reflectivity of the tracking plane and be able to collect more light on the energy plane the DICE-Boards were covered by PTFE masks, as shown on figure 1.23b, some months after the initial installation.

As this thesis is focused on the NEW tracking plane, more technical details can be found on further chapters.

### **Electronics and DAQ**

From the beginning of the NEXT Experiment, the electronics were thought to be easily scalable and compatible with all the detector stages. So almost all the electronics are evolved versions from the early stages of NEXT-DEMO.

In case of the energy plane front-end, the main specifications and components remain the same (see section 1.3), but upgraded to the new differential cable scheme intended to reduce the coupled noise due to the long cables. Also, as the new PMTs are biased with positive voltage, a coupling capacitor is needed in order to isolate the high voltage from the input analog stage, but allowing the smalls signals to pass through. This produce a known effect that distort the

signal, so a further offline signal reconstruction is needed to keep the energy resolution. Once the analog signal has been amplified and shaped it is sent also in differential mode to the ADC cards via HDMI cable. There the signals are digitized, and then processed as explained later.

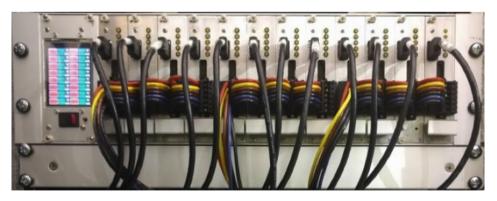

**Figure 1.24:** The NEW electronics cabinets. From the left, the computers and servers, the energy plane, and the tracking plane cabinet. At each side of the cabinets there is a big UPS, capable of supply the whole system up to 40 minutes in case of power failure.

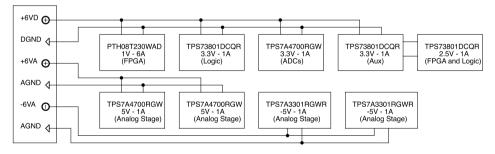

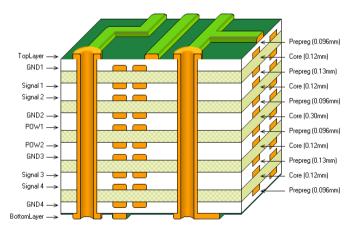

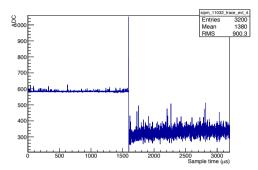

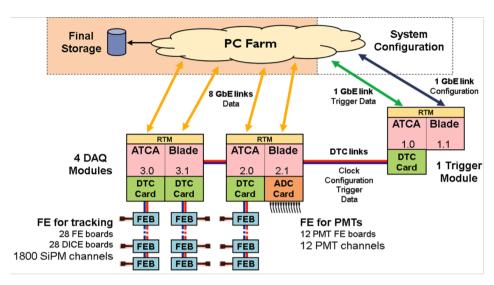

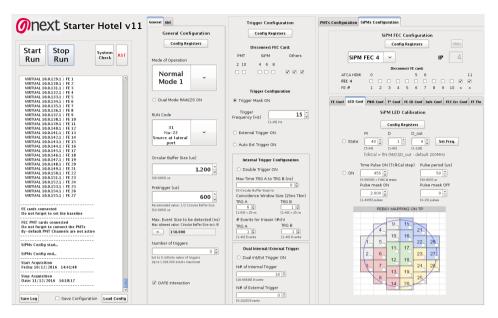

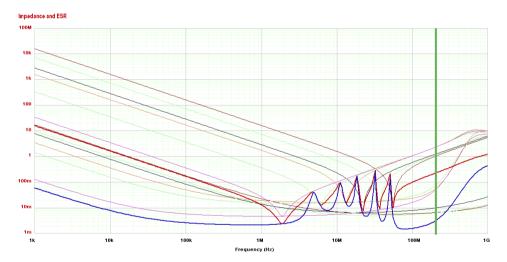

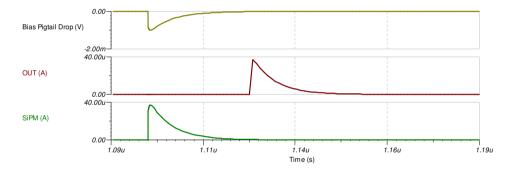

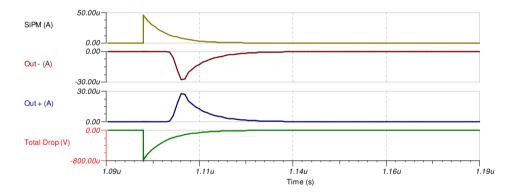

The tracking plane front-end electronics will be widely explained on chapters 3 and 4. Concerning the digital stage, each front-end board has a *Virtex-6 XC6VLX130T* FPGA which reads out data from up to sixty-four 1 *MHz* ADCs, formats data, time-stamps and stores them in a reconfigurable-length dual-event circular buffer to avoid dead time. When a trigger is received, zero-suppressed data is read out and sent to the upper stage. The circular buffer is implemented with the internal resources of the FPGA and is able to store two complete events in raw mode, whose maximum size corresponds to approximately twice the maximum detector drift time (up to 3.2 *ms*).

Baseline adjustment and zero-suppression parameters (baseline reference, value over the baseline, pre- and post-samples, minimum number of samples to consider a pulse) are configurable through a set of commands. In zerosuppression mode, the system triggers when the signal exceeds the value over the baseline fixed during at least the minimum number of samples to consider a pulse. Then, this signal is sent with its pre- and post-samples. Raw data mode of operation, where no zero suppression occurs, is also supported for testing purposes.

Both tracking plane and energy plane front-end cards interface the Scalable Readout System's (SRS) DAQ interface modules [Toledo et al. 2011] (tested on both FECv3 and the new FECv6) through the SRS' DTCC (Data, Trigger, Clock and Control) link specification over copper [Tarazona et al. 2014]. In this link, data, trigger, clock and slow controls flow on the same RJ-45 or HDMI connector over 4 LVDS pairs. *ALICE's DATE* is used as DAQ software environment. As a result, the front-end electronics are fully compatible with CERN RD-51 SRS electronics. The DTCC configuration used is the basic one. The link has been fully tested up to 250 *Mbps* over the two data pairs using 1 *meter* SFTP 6A copper cables.

## **Slow Control**

Obviously, an experiment with such complexity as the NEW detector will need an advanced control system. That is what we have called the Slow Control (SC).

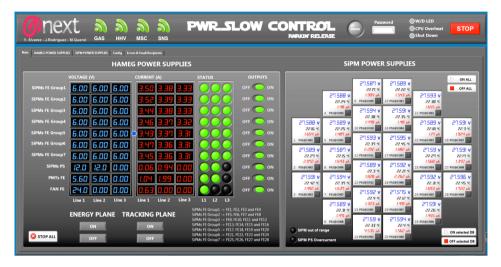

With the slow control we have created an internal network which connects all the subsystems and devices involved in the experiment, and adds an intelligence that keeps the system safe and acts to prevent and solve problems immediately. On figure 1.25 the control displays are shown.

Without going into greater detail, there are 6 different programs connected to the experiment and between them:

- **High Voltage:** Monitors and controls the voltage on the field cage cathode and gate. Detects the sparks and recovers or shuts down the system according to the parameters set.

- Gas System: Monitors all the parameters involving the gas system: valves, pressure, vacuum, compressor, chiller, vacuum pumps, RGA... As the gas

Figure 1.25: The NEXT Slow Control.

system was defined as critical, almost all intervention is forbidden because the system is autonomous. Nevertheless, an emergency stop can be done through the SC.

- **Power Supplies:** Monitors and controls all the power supplies that power the electronics in the experiment, including the SiPM custom bias sources.

- **PMT High Voltage:** Monitors and controls the PMTs power supply, detects overcurrents and controls also the vacuum pump connected to the energy plane volume.

- Sensors: Monitors the temperatures and other important parameters of the electronics and DAQ computers. Controls also the contactors that power almost all the equipment and electronics.

- Main: This slow control receives the main parameters and warnings from the other ones, so the shifter knows if everything is working properly just looking at this one. It also has an emergency button, that stops everything to prevent damage, and can remotely switch on the other slow control computers.

Each one of the slow controls also generates reports, including all the events registered for each subsystem and the main parameters measured. Also emails

are sent to the shifter, with warnings or alarms produced, so he can act as soon as possible.

## Lead Castle

To shield NEW (and NEXT-100 in the future) from the external flux of highenergy gamma rays, a relatively simple lead castle (figure 1.26) has been chosen, mostly due to its simplicity and cost-effectiveness. The lead wall has a thickness of 20 *cm* and is made of layers of staggered lead bricks held with a steel structure.

**Figure 1.26:** The NEXT Experiment lead castle. The NEW detector stands previously to the piping and cabling installation.

The lead bricks have standard dimensions  $(200 \times 100 \times 50 \text{ mm}^3)$ , and, by requirement, an activity in uranium and thorium lower than 0.4 mBq/kg. The lead castle is made of two halves mounted on a system of wheels that move on rails with the help of electric engines. The movable castle has an open and a closed position. The former is used for the installation and service of the pressure vessel; the latter position is used in normal operation. A lock system

fixes the castle to the floor in any of the two configurations to avoid accidental displacements.

In both castle sides, where the two halves seal, there are moving "doors". This "doors" are also made of lead bricks, and can be moved to allow working space (on the open position) and to shield the joint between the two castle halves (on the closed position).

Due to the mild seismic activity of the part of the Pyrenees where the LSC is located, the lead castle is mounted on a seismic structure in order to isolate it from possible ground vibrations. Thereby the lead castle is not mechanically attached to the working platform, and all the electrical and gas connections are flexible between these separate structures.

# 1.5 NEXT-100 and Beyond

The NEXT experiment was formally proposed to the Laboratorio Subterráneo de Canfranc (LSC) in 2009 in a Letter of Intent [Granena et al. 2009]. The detector design was narrowed down in a Conceptual Design Report [Álvarez et al. 2011] published in 2011, and fixed a year later in a Technical Design Report (TDR) [Álvarez et al. 2012c]. Consequently, the Collaboration favored the configuration that had been tested with the NEXT-DEMO and NEXT-DBDM prototypes.

As explained before, NEW is a reduced version of NEXT-100 with the same technologies. So there is no need of a detailed explanation of every NEXT-100 component. However, the main differences are the following:

- **Pressure vessel:** The pressure vessel of NEXT-100, shown on figure 1.27, consists of a cylindrical central section of 160 cm length, 136 *cm* inner diameter and 1 *cm* wall thickness, and two identical torispherical heads of 35 *cm* height, 136 *cm* inner diameter and 1 *cm* wall thickness. It has been fabricated with stainless steel type 316Ti due to its low levels of natural radioactive contaminants.

- Field cage: The main body of the field cage is an open-ended high-density polyethylene (HDPE) cylinder of 148 *cm* length, 107.5 *cm* inner diameter

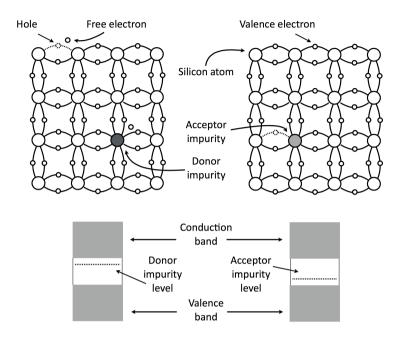

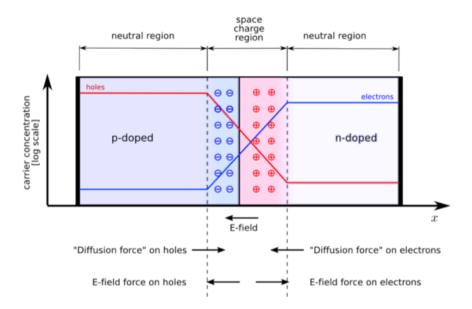

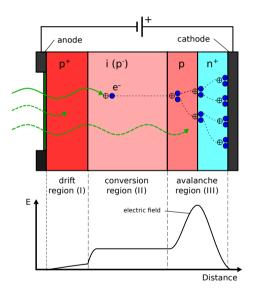

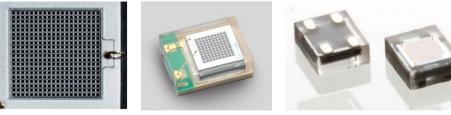

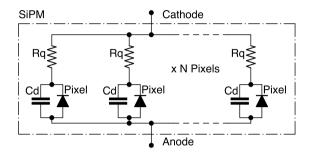

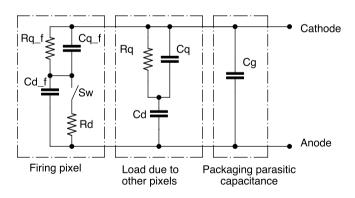

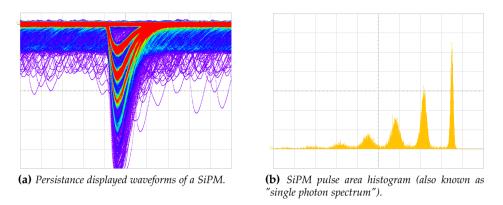

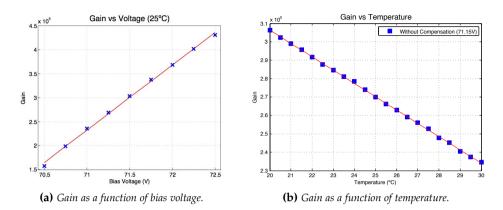

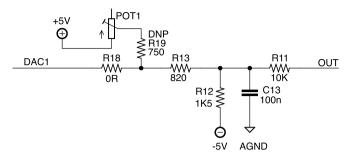

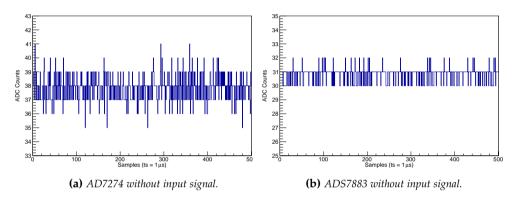

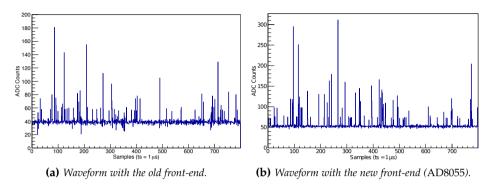

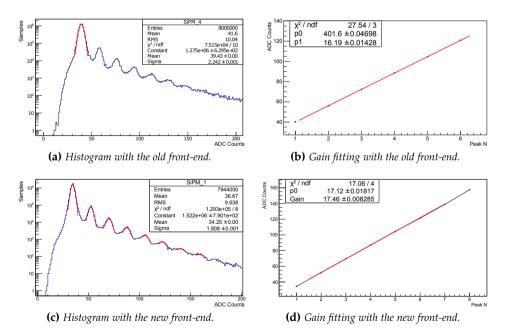

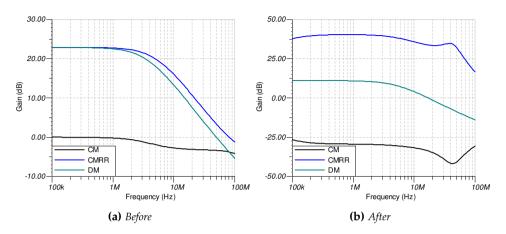

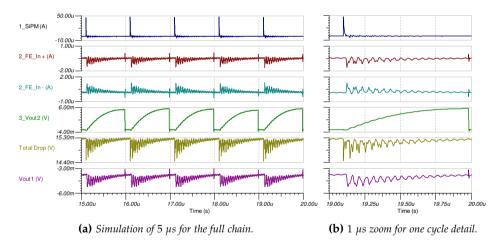

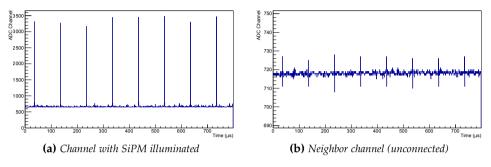

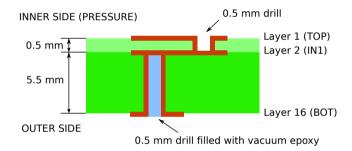

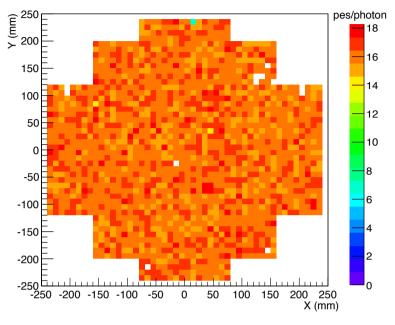

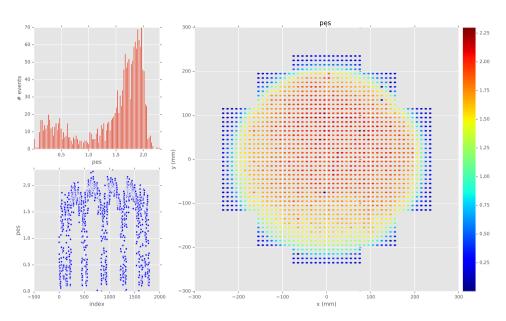

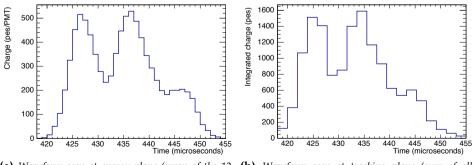

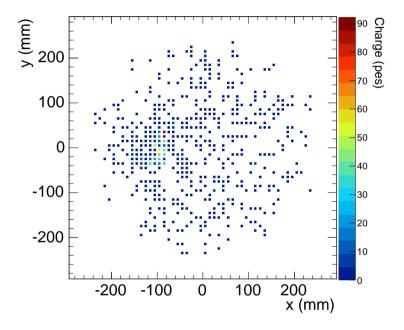

**Figure 1.27:** Cross-section view of the NEXT-100 detector. The active volume is shielded from external radiation by at least 12 cm of copper in all directions.