# UNIVERSITAT POLITÈCNICA DE VALÈNCIA

#### ESCOLA POLITÈCNICA SUPERIOR DE GANDIA

#### Trabajo final de grado

Grado en ingeniería de sistemas de telecomunicación, sonido e imagen

Departamento de ingeniería electrónica

Josep Rioja Ibañez

Generador de formas de onda arbitrario con una FPGA

Tutor:

Javier Valls Coquillat

# Agraïments Agraïsc tant a la meua família com el Professor Javier Valls la paciència que han tingut en el transcurs de l'aprenentatge i confecció d'aquest treball.

## Índice

| 1. | Intr  | roducción                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6               |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

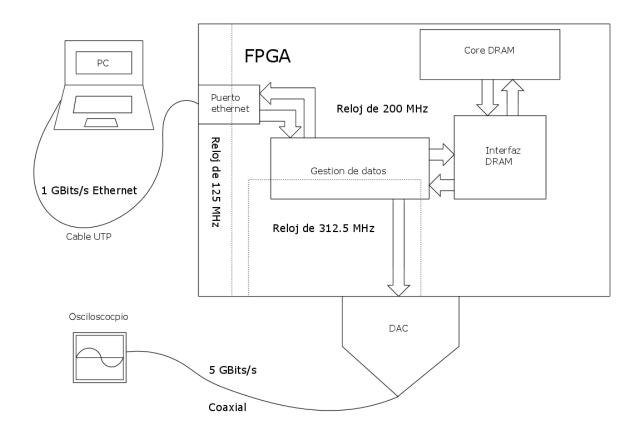

|    | 1.1.  | Estructura general del generador de formas de onda                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7               |

|    |       | 1.1.1. Principales características de la transmisión ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8               |

|    |       | 1.1.2. Principales características del procesado y gestión de datos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8               |

|    |       | 1.1.3. Principales características del conversor DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8               |

|    |       | 1.1.4. Principales características de la memoria DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8               |

|    | 1.2.  | Objetivos del TFG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S               |

|    | 1.4.  | Objetivos del 11 d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ü               |

| 2. | Dise  | eño Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10              |

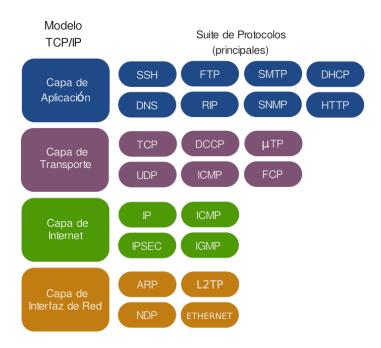

|    | 2.1.  | Protocolos utilizados para la comunicación punto a punto entre dispositivos .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11              |

|    | 2.2.  | Funciones del sistema programadas en Matlab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12              |

|    |       | 2.2.1. Funciones relacionadas con la configuración del protocolo TCP/IPv4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |

|    |       | y ARP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12              |

|    |       | 2.2.2. Función de escritura de datos en la DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14              |

|    |       | 2.2.3. Función de lectura vía ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14              |

|    |       | 2.2.4. Función lectura vía DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14              |

|    |       | 2.2.11 I different feet data for the first f |                 |

| 3. | Dise  | eño Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16              |

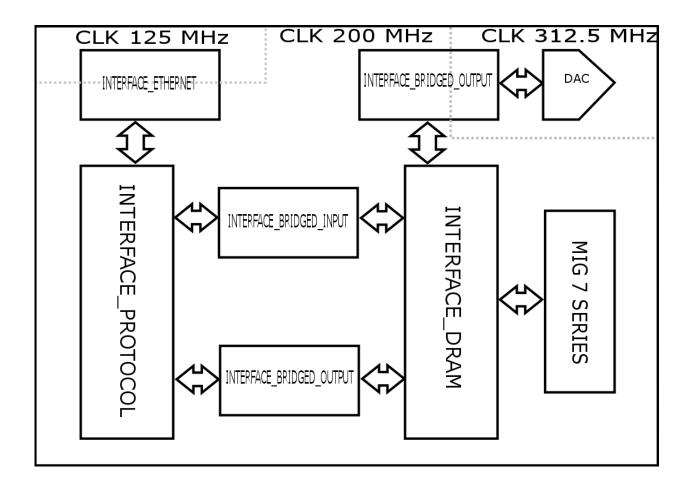

|    | 3.1.  | Esquema hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17              |

|    | 3.2.  | Dominios de reloj                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17              |

|    | 3.3.  | Interfaz hardware ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18              |

|    |       | 3.3.1. Configuración hardware ethernet del                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |

|    |       | protocolo TCP/IPv4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18              |

|    |       | 3.3.2. Transmisión y recepción de datos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18              |

|    | 3.4.  | Función del módulo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

|    |       | INTERFACE PROTOCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19              |

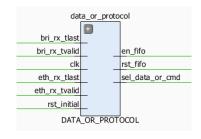

|    |       | 3.4.1. Datos o comandos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19              |

|    |       | 3.4.2. Comandos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20              |

|    | 3.5.  | Función del módulo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

|    |       | INTERFACE_BRIDGE_INPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21              |

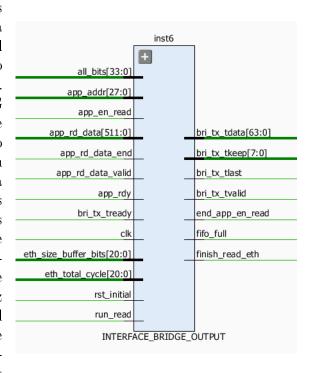

|    | 3.6.  | Función del módulo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

|    |       | INTERFACE_BRIDGE_OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22              |

|    | 3.7.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

|    | - • • | INTERFACE DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23              |

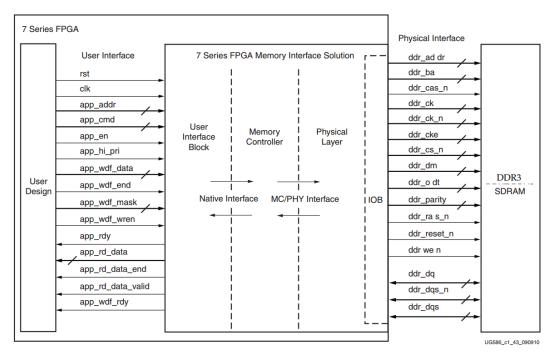

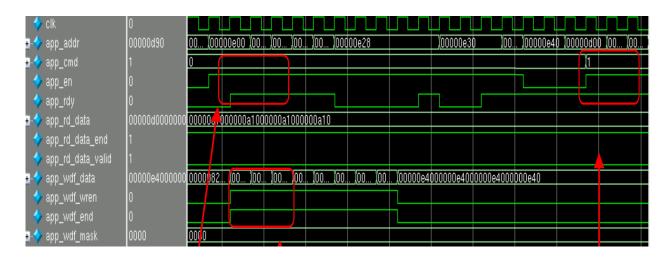

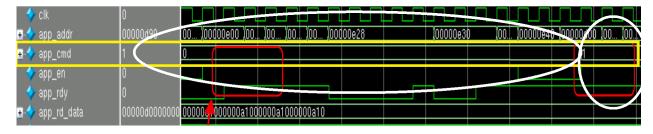

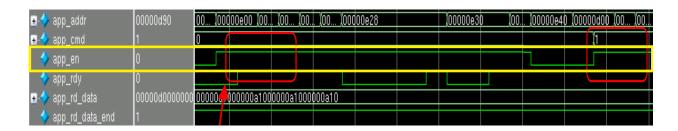

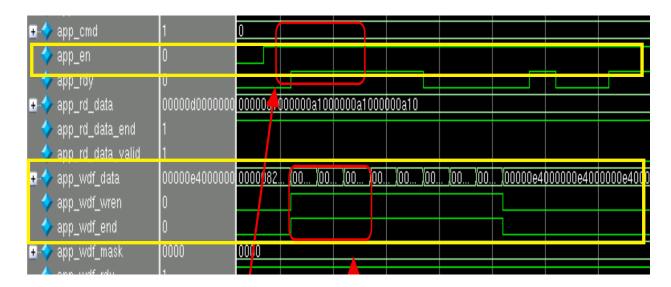

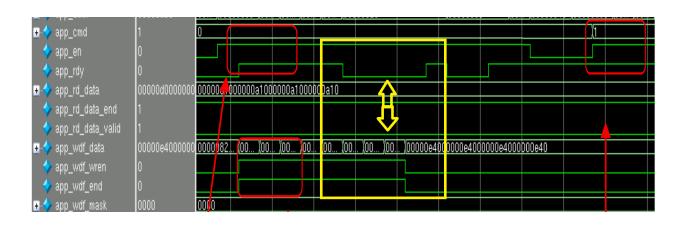

|    |       | 3.7.1. Comportamiento de la interfaz MIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\frac{-}{23}$  |

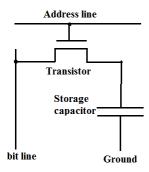

|    |       | 3.7.2. Interfaz de memoria 7 Series FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\frac{-3}{24}$ |

#### TFG: Generador de formas de onda arbitrario con una FPGA

|    | 3.8. | 3.7.3. Módulo INTERFACE_DRAM                         |    |

|----|------|------------------------------------------------------|----|

| 4. | Ren  | ndimiento del sistema Hardware                       | 30 |

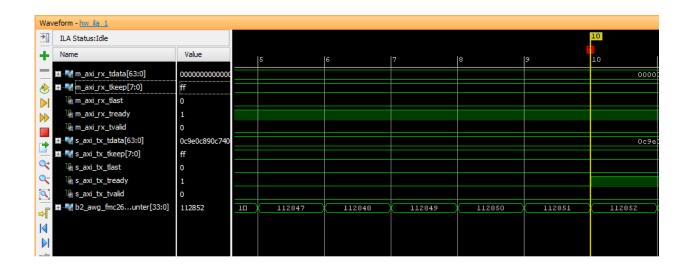

|    | 4.1. | Prestaciones del Core ethernet                       | 31 |

|    | 4.2. | Prestaciones del Core DRAM                           | 31 |

| 5. | Pru  | eba del generador de formas de onda arbitrario       | 33 |

|    | 5.1. | Características del montaje                          | 34 |

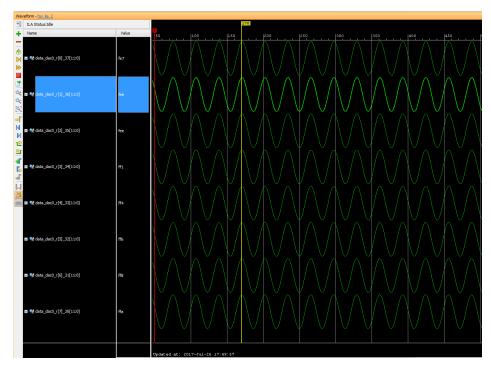

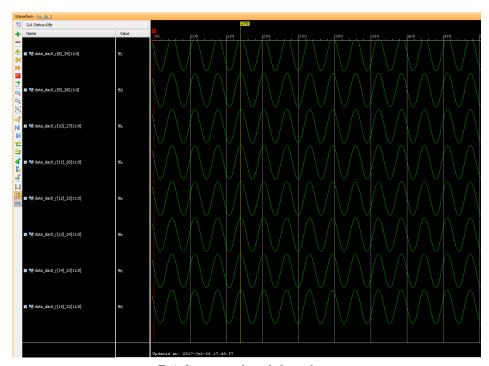

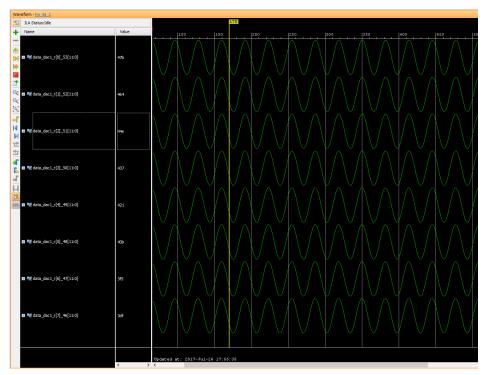

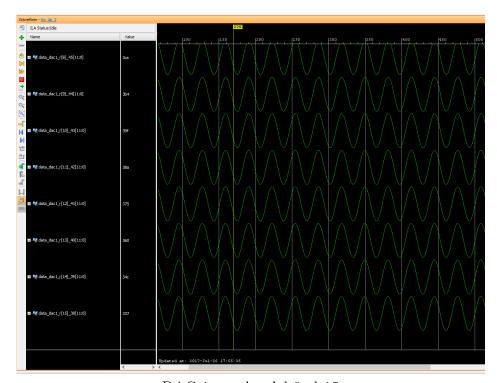

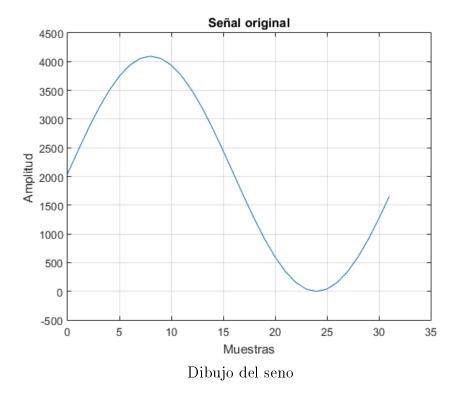

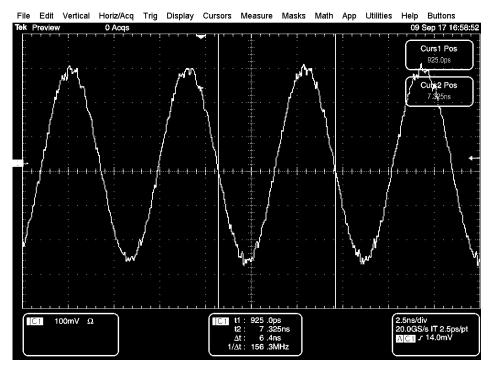

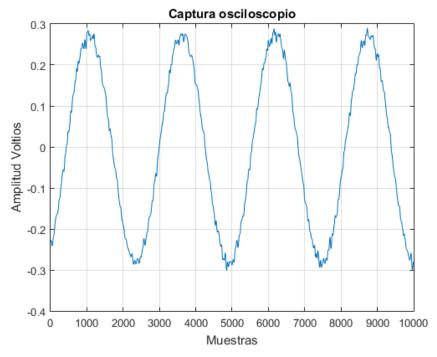

|    |      | Capturas con instrumental de laboratorio             | 38 |

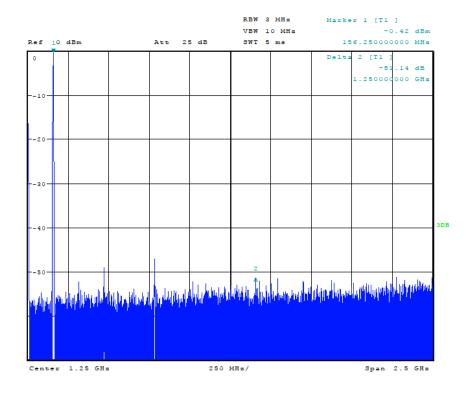

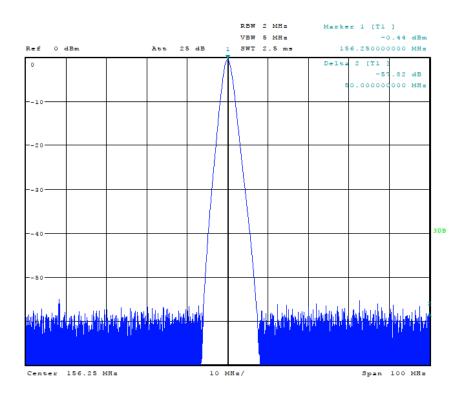

|    |      | 5.2.1. Señal original                                | 38 |

|    |      | 5.2.2. Captura con un osciloscopio                   | 38 |

|    |      | 5.2.3. Captura con un analizador de espectros        | 40 |

| 6. | Con  | nclusiones                                           | 42 |

|    | 6.1. | Análisis de objetivos                                | 43 |

|    | 6.2. | Planificación y metodología del TFG                  | 44 |

|    |      | 6.2.1. Proceso de aprendizaje                        | 44 |

|    |      | 6.2.2. Diseño y ejecución del trabajo final de grado | 44 |

|    | 6.3. | Futuras ampliaciones                                 | 44 |

|    |      | Conclusiones personales                              | 45 |

| 7. | Doc  | cumentación técnica                                  | 46 |

|    |      | Documentación FPGA Virtex y Kintex Serie 7           | 47 |

|    |      | Documentación Conversor EURVIS 5 Gsps                |    |

|    |      | Dogumento sión Motlab                                | 45 |

#### Resumen

En este trabajo se va a explicar cómo se ha diseñado e implementado utilizando un PC con el programa Matlab y una FPGA, un generador de formas de onda arbitrario de alta velocidad (el conversor muestrea a 5 Gsps). Un generador de formas de ondas arbitrario es un sistema que repite cíclicamente un tipo de señal seleccionada por el usuario (una señal seno, una rampa, etc.). El sistema propuesto en este trabajo de fin de grado cumple con este principio de funcionamiento ya que, desde el Matlab el usuario va a programar una función o cargar desde un archivo los datos de la señal a utilizar. Esta señal seleccionada por el usuario será enviada vía ethernet desde el PC por medio del programa Matlab hasta la FPGA. Una vez llegada la señal a la FPGA será procesada y almacenada dentro de una memoria DRAM para su después reproducción. Por último, el sistema está preparado para seleccionar el canal de transmisión de los datos. Existen dos opciones de uso del sistema para el usuario, hacer una comprobación de vuelta de los datos almacenados en la DRAM o seleccionar su transmisión cíclica por el canal auxiliar implementado.

Palabras clave: FPGA, Matlab, DRAM, Ethernet y Generador.

#### Abstract

In this final paper we will explain how an arbitrary hihg-speed waveform generator was designed and implented, by using a PC with the Matlab program and a FPGA, an arbitrary high-speed waveform generator (the converter working at 5 Giga samples per second). An arbitrary waveform generator is a system that cyclically repeats a type of signal selected by the user (a sine signal, a ramp, etc.). The system proposed in this end-of-degree project meets this principle of functionality since, the user will be able to program a function from Matlab, or load the data of the signal from a file to be used. This signal selected by the user will be sent via ethernet from the PC via the Matlab program to the FPGA. Once the signal arrives to the FPGA it will be processed and stored inside a DRAM memory for its later reproduction. Finally, the system is ready to select the transmission channel of the data. There are two options for using the system for the user, checking the data stored in the DRAM or selecting its cyclic transmission via the implemented auxiliary channel.

**Keywords:** FPGA, Matlab, DRAM, Ethernet y Generator.

#### Resum