# Addressing Fiber-to-Chip Coupling Issues in Silicon Photonics

Jose Vicente Galán

Supervisor: Dr. Pablo Sanchis

Departamento de Comunicaciones Universidad Politécnica de Valencia

Thesis submitted for the degree of Doctor of Philosophy

Valencia, December 2010

## Prefacio

Este trabajo trata sobre fotónica de silicio. Trata, pues, de la manipulación de la luz, o fotones. La luz que transporta la información por todo el planeta. La luz de los sistemas de comunicaciones basados en fibra óptica. La fotónica de silicio es la aplicación a estos sistemas fotónicos que usan silicio como medio óptico. La fotónica de silicio estudia la manipulación de la luz en dispositivos a una escala sub-micrométrica (hasta nanométrica) para muchas aplicaciones y, por tanto, también para comunicaciones en particular.

Cuando empecé mi trabajo en el NTC como estudiante de ingeniería en 2005, este Centro estaba casi empezando a investigar en el campo, especialmente en el tema del acoplo fibra-chip. Tuve así pues el placer de continuar investigando en el tema como estudiante de doctorado, bajo la supervisión de Pablo, a quien estoy muy agradecido por ello. En los pasados cinco años, la fotónica de silicio se ha convertido en un campo muy activo en el grupo, con al menos diez personas investigando en diferentes aplicaciones. Con los años, hemos intentado desarrollar una exhaustiva comprensión de la complejidad de la fotónica de silicio. Este es uno de los propósitos de este libro: compartir nuestra visión.

Muchas de las ideas aquí expuestas son resultado de fructíferas discusiones entre compañeros tanto del interior del grupo como de otros grupos de investigación. Con el riesgo de olvidar a alguien, me gustaría mencionar algunas personas por su nombre.

Gracias, Javier, por darme la oportunidad de formar parte del NTC, donde durante estos casi cinco años he conocido gente maravillosa y que nunca olvidaré. Gracias, Alex, por tus ltimas correcciones de la Tesis.

Gracias especiales a Pablo, por supervisar excelentemente mi trabajo durante este tiempo, y por su siempre humilde apoyo y ayuda.

Gracias, Mariam. Guiarte en tu tesis de master y en tu proyecto final de carrera ha sido un placer. Parte de tu trabajo y muchas de tus valiosas aportaciones están, de algún modo, también incluidas en este libro. Gracias, Antoine, por haber sido mi compañero durante este tiempo. Soy consciente de la increíble persona con la que he estado trabajando. Te deseo todo lo mejor con tu tesis, y mucha suerte tanto en lo personal como en lo profesional.

Gracias a todos los estudiantes de doctorado del NTC: Carlos, Rubén, Guillermo, Pak, Jesús, Sara, Ana, Javi, Jose, entre otros.

Enhorabuena a los recintes Doctores Ruth y Rakesh, a quienes también deseo lo mejor profesionalmente.

Gracias al prometedor equipo de encapsulado que está surgiendo en el NTC: Giani y, recientemente, Mercè. Espero sigamos colaborando juntos por muchos años, especialmente en lo que respecta al laboratorio del banco de alineamiento, donde continuaremos pasando buenos ratos.

Este trabajo no habría sido posible sin las manos del equipo de fabricación del NTC, quienes, con el objetivo de poder hacer nuestros experimentos, han procesado tantas obleas como ha sido necesario, y empleado siempre el tiempo que se les ha requierido. Gracias Amadeu, Jose, Juan, Laurent, Paco por vuestro siempre buen trabajo de fabricación, y por vuestras siempre útiles discusiones sobre procesos y métodos de fabricación. Gracias también al equipo de instalaciones Alfredo, Luis, Antonio y Glenn, por hacer posible "construir" nuestra casi nueva sala limpia (recordar, el lugar más limpio de España).

Nuestros compañeros de los proyectos ePIXnet y HELIOS también se merecen las gracias. Mucho de mi trabajo se ha llevado a cabo en el marco de estos proyectos, y sin las colaboraciones, las cosas habrían sido diferentes. Gracias especiales a nuestros amigos Lars y Tolga, a quienes conocí gracias a nuestra colaboración dentro de estos proyectos. Gracias de nuevo, Tolga, por tu generoso alojamiento en Berlin el verano de 2009. Nunca lo olvidaré.

Fuera de mi trabajo, hay algunas personas que siempre me han mantenido con los pies en la tierra en estos años. De algún modo, ellos también han contribuído en mi trabajo. Papá, Mamá, gracias por todo vuestro apoyo (incluído financiero) que me ha ayudado desde el principio hasta el fin en la universidad. Hermana, gracias por ser parte de mi sangre.

Y sobre todo, gracias, Ariana. Siempre has estado ahí para mí, lo estás, y espero que lo estés siempre.

Perdón si no nombro a todo el mundo, pero un gracias general a toda la gente con la que he estado en contacto de cualquier modo durante estos años.

Jose Vicente Galán. Valencia, 28 de Noviembre de 2010

#### Resumen

Interés de la investigación: Esta tesis trata de resolver el problema de la interconexión (acoplo) entre un circuito integrado fotónico de silicio (chip) y el mundo exterior, es decir una fibra óptica. Se trata de uno de los temas más importantes a los que hoy en día se enfrenta la comunidad científica en óptica integrada de silicio. A pesar de que pueden realizarse circuitos integrados fotónicos de silicio de muy alta calidad utilizando herramientas estándar de fabricación CMOS, la interfaz con la fibra óptica sigue siendo la fuente más importante de pérdidas, debido a la gran diferencia en el tamaño entre los modos de propagación de la fibra y de las guías de los circuitos integrados fotónicos. Abordar el problema es, por lo tanto, muy importante para poder utilizar los circuitos integrados fotónicos de silicio en una aplicación práctica.

**Objetivos**: El propósito de este trabajo es hacer frente a este problema en la interfaz del acoplamiento fibra-chip, con énfasis en el ensamblado o empaquetado final. Por lo tanto, los objetivos principales son: 1) estudio, modelado y optimización de diseños de diferentes técnicas eficientes de acoplamiento entre fibras ópticas y circuitos integrados fotónicos de silicio, 2) fabricación y demostración experimental de los diseños obtenidos, 3) ensamblado y empaquetado de algunos de los prototipos de acoplamiento fabricados.

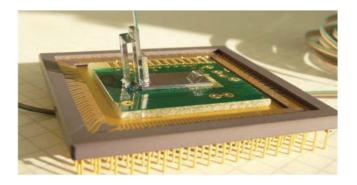

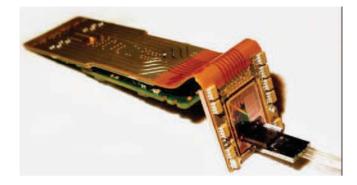

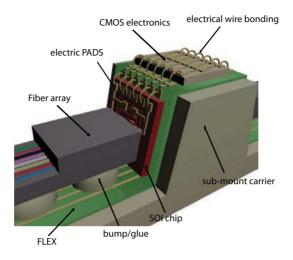

Metodología: Este trabajo se desarrolla a lo largo de dos líneas de investigación, en conformidad con las dos principales estrategias de acoplamiento que pueden encontrarse en la literatura, concretamente, estructuras de acoplamiento tipo "grating" (la fibra acopla verticalmente sobre la superficie de circuito), y estructuras del tipo "inverted taper" (la fibra acopla horizontalmente por el extremo de circuito). El texto comienza con una introducción (capítulo uno), incluyendo la motivación y el contexto de la investigación, la definición del problema de acoplamiento fibra-circuito en fotónica de silicio, así como los objetivos y la organización del trabajo. El estado del arte de las dos estrategias de acoplamiento a investigar se incluye en el capítulo dos. Cada una de las estrategias (acopladores "grating" e "inverted taper"), se trata ampliamente en capítulos separados (capítulos tres y cuatro, respectivamente), incluyendo tanto el principio de funcionamiento del dispositivo, como el diseño y estrategia de fabricación seguidos, así como resultados de las pruebas experimentales de diseños fabricados, con el fin de comprobar su validez. En el capítulo cinco, se tratan soluciones de empaquetado para ambas técnicas de acoplamiento fibra-chip desarrolladas, donde también se examina previamente el estado del arte de empaquetado de circuitos fotónicos de silicio. A tales efectos, el objetivo principal es el empaquetado de circuitos integrados fotónicos de silicio multipuerto basado en componentes disponibles comercialmente. En el último capítulo, se incluye un resumen y conclusión de los resultados obtenidos, así como las perspectivas de trabajo futuro.

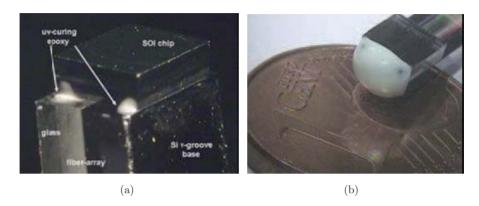

**Resultados**: tanto en el caso de estructuras tipo "grating" como en el caso de estructuras "inverted taper", son importantes los avances conseguidos sobre el estado del arte. En lo que respecta al "grating", se ha demostrado dos tipos de estructuras. Por un lado, se ha demostrado "gratings" adecuados para acoplo a guías de silicio convencionales. Por otra parte, se ha demostrado por primera vez el funcionamiento de "gratings" para guías de silicio tipo "slot" horizontal, que son un tipo de guía muy prometedora para aplicaciones de óptica no lineal. En relación con el acoplamiento a través de "inverted taper", se ha demostrado una estructura novedosa basada en este tipo de acoplamiento. Con esta estructura, importantes son los avances conseguidos en el empaquetado de fibras ópticas con el circuito de silicio. Su innovadora integración con estructuras de tipo "V-groove" se presenta como un medio para alinear pasivamente conjuntos de múltiples fibras usando acopladores tipo "grating", resultando en un prototipo de empaquetado de reducido tamaño.

### Resum

Interès de la investigació: Aquesta tesi tracta de resoldre el problema de la interconnexió (acoblament) entre un circuit integrat fotònic de silici (xip) y el món exterior, és dir, una fibra òptica monomode. Aquest és un del temes més importants als que s'enfronta hui en dia la comunitat científica en òptica integrada de silici. Tot i que es poden implementar circuits integrats fotònics de silici d'alta qualitat utilitzant ferramentes estàndard de fabricació CMOS, la interfície amb la fibra òptica continua sent la causa més important de pèrdues, degut a la gran diferència entre el tamany de la fibra òptica monomode i de les guies dels circuits integrats fotònics. El tractament del tema és, per tant, molt important per a la utilització dels circuits integrats fotònics en una aplicació pràctica.

**Objetctius**: L'objectiu d'aquest treball és fer front a aquest problema en el interfície fibra-xip, emfatitzant l'ensamblament o empaquetament final dels circuits. Per tant, els objectius principals són: 1) estudi, modelat i optimització dels dissenys de tècniques eficients d'acoblament entre fibres òptiques i circuits integrats fotònics de silici, 2) fabricació i demostració experimental dels dissenys obtinguts, 3) ensamblament i empaquetament d'alguns dels prototips d'acoblament fabricats.

Metodologia: Aquest treball es desenvolupa al voltant de dos línies, corresponents a les dos estratègies principals d'acoblament existents a la literatura: acoblament de llum verticalment sobre la superfície del circuit (estructura "grating coupler") i horitzontalment per la seua vora (estructura "inverted taper"). El manuscrit comença amb una introducció (capítol 1) que inclou la motivació i el context de la investigació, la definició del problema d'acoblament fibra-circuit en fotònica de silici i els objectius i organització del treball. L'estat de l'art de les dos estratègies d'acoblament s'inclou al capítol 2. Cadascuna de les estratègies (acoblador "grating" i "inverted taper") s'analitza àmpliament de manera separada als capítols 3 i 4 respectivament, incloent els principis de funcionament dels dispositius, fabricació, i els resultats de les proves experimentals de dissenys fabricats amb la finalitat de comprovar la seua validesa. Al capítol 5 s'estudien les solucions d'empaquetament per a les dos tècniques d'acoblament fibra-xip desenvolupades i s'examina l'estat de l'art d'empaquetament de circuits fotònics de silici. A tals efectes, l'objectiu principal és l'empaquetament de circuits integrats fotònics de silici multiport basat en components disponibles comercialmet. A l'últim capítol, s'inclou un resum del resultats obtinguts, així com les perspectives de treball futur.

**Resultats**: Tant per al cas de "grating" com per a les estructures "inverted taper", són importants els avanços produïts sobre l'estat de l'art. Respecte al "grating", s'han demostrat dos tipus d'estructures. D'una banda, s'han demostrat "gratings" adequats per a l'acoblament a guies de silici convencionals. D'altra banda, s'ha demostrat per primera vegada el funcionament dels "gratings" per a guies de silici tipus "slot" horitzontal, que son guies molt prometedores per a aplicacions d'òptica no lineal. Respecte a l'acoblament amb "inverted taper", s'ha demostrat una estructura innovadora basada en aquest tipus d'acoblament. Amb aquesta estructura són importants els avanços aconseguits en relació amb l'empaquetament de fibres òptiques amb el circuit de silici. La integració amb estructures de tipus "V-groove" es presenta com una solució per a alinear passivament conjunts de múltiples fibres a un mateix circuit integrat fotònic. També s'estudia l'empaquetament de conjunts de múltiples fibres amb acobladors "grating", resultant un prototipus d'empaquetament de reduït tamany.

## Preface

This work is on silicon photonics. It is about the manipulation of light or photons. Light that carries information all over the planet. Light for fiber-optic communication systems. Silicon photonics is the application of these photonic systems which use silicon as an optical medium. Silicon photonics is about the manipulation of light on sub-micron (even nano) scale devices for many applications, and so for communications in particular.

When I started my work at NTC as engineering student in 2005, the NTC was almost starting to research in the field, specially in the fiber-chip coupling topic. I had so the pleasure to continue researching on the field as a PhD student, under supervision of Pablo, to whom I am very grateful for that. In the past five years, silicon photonics research has become an active activity in the group, with at least ten people working on different research topics. Over the years, we have developed a thorough understanding of the intricacies of silicon photonics. This is one of the purposes of this book: to share these insights.

Many of the ideas here are a result of fruitful discussions with colleagues both from within the group and other research groups. At the risk of forgetting someone, I would like to mention a number of people by name.

Thank you Javier for giving me the opportunity to join the NTC, where I have met very nice and friendly people I will never forget during these almost five years. Thank you Alex for your last corrections of the thesis.

Special thanks to Pablo for supervising all my work always in a perfect way, and for his always kind support and help.

Thank you, Mariam. Guiding you in the master thesis, as well in your graduation project was a pleasure, and parts of your work and many valuable insights are in some way incorporated in this book.

Thanks Antoine, for being my workmate during all this time. I am aware of the amazing person (including personally) I have been working with. I wish you all the best with your thesis, and with your professional and personal life.

Thank you all PhD students (and also friends) at NTC: Carlos, Rubén, Guillermo, Pak, Jesús, Sara, Ana, Javi, Jose, among others. Congratulations to recent Drs. Ruth an Rakesh, to whom I also wish all the best professionally.

Thank you to the promising packaging team it is coming consolidated at NTC: Giani, and recently Mercè. I hope we continue collaborating together for many years, specially regarding the alignment bench lab, where we will continue having great times.

This work would not have been possible without the hands of the fabrication team people at NTC in UPV, who, in order to get our experiments made, processed as many wafers as necessary, and spent all the time required. Thank you, Amadeu, Jose, Juan, Laurent, Paco, for you always good fabrication work and for your always helpful discussions on fabrication processes and methods. Also thank you to the facilites team, Alfredo, Luis, Antonio and Glenn, for making possible to "build" our almost new cleanroom place (remember, the cleanest place in Spain).

Also, the partners of the ePIXnet and HELIOS projects deserve a big thank you. Much of my work has been carried out in the framework of these projects, and without the collaborations, things would have been very different. Special thanks to our colleagues Lars and Tolga, to whom I met thanks to our collaboration within those projects. Thank you again Tolga for you kind hosting in Berlin during the summer of 2009. I will never forget it.

Outside of my work, there are some other people who have kept me on my feet in those years. In some ways, they have contributed to my work, too. Dad and Mom, thanks for all the support (including financial) that helped me through university. Sister, thank you for being part of my blood.

And most of all, thank you, Ariana. You were always there for me, still are, and I hope you will always be.

Sorry if I do not name everybody, but general thanks to all people I have been in touch in any way during these years.

Jose Vicente Galán

Valencia, 28th November 2010

#### Abstract

**Research interest**: This thesis deals with the interconnection (coupling) problem between a silicon photonic integrated circuit (chip) and the outside world, (i. e., a single mode fiber). This is one of the most important problems that the silicon integrated optics scientific community is facing nowadays. While very high quality silicon photonic integrated circuits can be realized using standard CMOS fabrication tools, the interface with the optical fiber remains the most important source of loss, due to the large difference in mode size between the single mode fiber and the waveguides on the photonic integrated circuits. Addressing the issues is therefore very important to apply silicon photonic integrated circuits in a practical application.

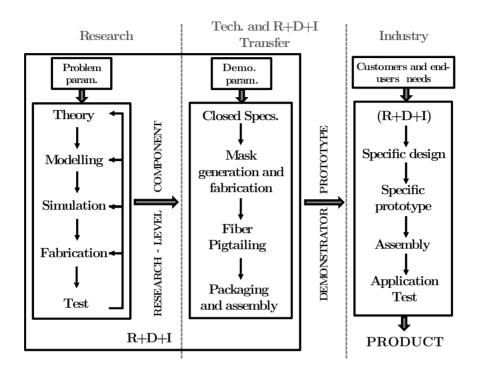

**Objectives**: The aim of this work is so to tackle this fiber-chip coupling interface problem, with an emphasis on the packaging. Thus, the main objectives are: 1) study, modelling and design optimization of efficient coupling techniques between optical fibers and silicon photonic integrated circuits, 2) fabrication and experimental demonstration of the obtained designs, 3) assembling and packaging of some of the fabricated coupling prototypes.

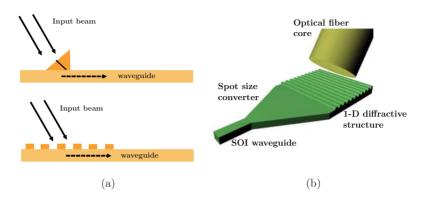

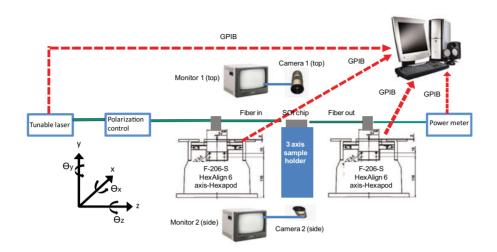

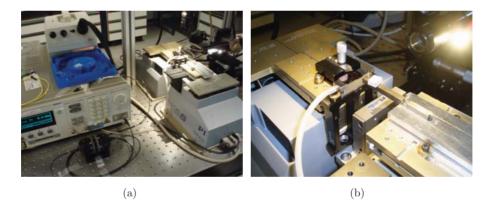

**Methodology**: This work develops along two investigation lines, in accordance with the two main strategies that can be found in literature, namely diffractive grating coupler structures (the fiber couples vertically onto the circuit surface) and inverted taper structures (horizontal fiber coupling onto the circuit end). The manuscript starts with an introduction (chapter one), including the motivation and research context, the definition of the fiber-chip coupling problem in silicon photonics, as well as the objectives and organization of the thesis. The state-of-the art of the two coupling strategies to be investigated is therefore included in chapter two. Each strategy (grating coupler and inverted taper) is then extensively discussed in a separate chapter (chapters three and four, respectively), including the device operation principle, the design and fabrication strategy followed, as well as experimental testing results of fabricated designs, in order to cross-check their validity. In chapter five, the packaging solutions based on both fiber-chip coupling techniques are discussed, where also briefly the state-of-the-art of silicon photonic packaging is reviewed. Hereto, the main focus is multichannel silicon photonic integrated circuits and their packaging based on commercial available components. In last chapter, the achieved results are summarized and future perspectives are discussed.

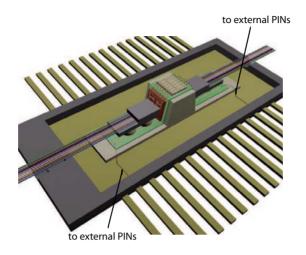

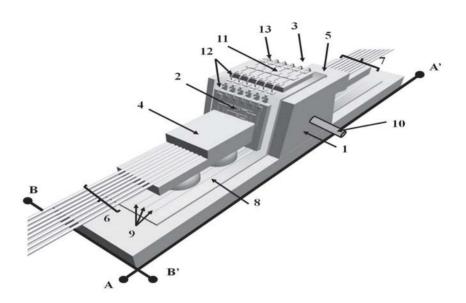

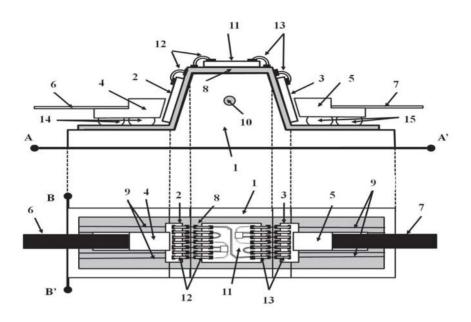

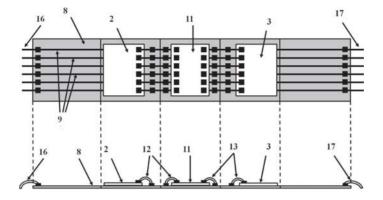

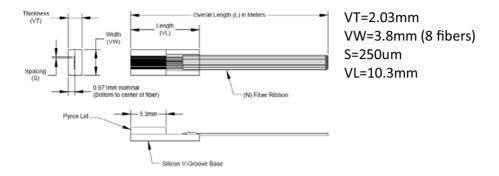

**Obtained results**: Both in the case of diffractive grating couplers and in the case of inverted taper structures, important advances are made over the stateof-the-art. Concerning diffractive gratings, two types of structures have been demonstrated. On one hand, grating couplers suitable for conventional silicon waveguides have been achieved. On the other hand, diffractive grating structures are shown to work on horizontal slot waveguide structures for the first time, which are very promising for nonlinear optics applications. With regard to the coupling via inverted taper, a novel inverted taper-based structure is experimentally demonstrated. Using this structure, important advances are made in the packaging of optical fibers with the silicon waveguide circuit. Its innovative integration with V-groove structures is presented as a means to passively align arrays of fibers to a photonic integrated circuit. Also, packaging of fiber arrays using diffractive grating couplers is studied, resulting in a prototype of small form factor package.

## List of Publications and Patents

### Publications

#### Peer-reviewed Journals

#### Main contributions

- J1. J. V. Galan, P. Sanchis, J. Martí, "Una técnica de acoplo eficiente entre fibra óptica y circuitos integrados ópticos de silicio," ITECKNE: Innovación e investigación en Ingeniería, vol. 4, pp. 51-54 (2007).

- J2. J. V. Galán, P. Sanchis, G. Sánchez, and J. Martí, "Polarization insensitive low-loss coupling technique between SOI waveguides and high mode field diameter single-mode fibers," Opt. Express, vol. 15, no. 11, pp. 7058-7065 (2007).

- J3. J.V. Galan, P. Sanchis, J. Blasco, A. Martinez, J. Marti, "High efficiency fiber coupling to silicon sandwiched slot waveguides," Optics Communications, vol. 281, no. 20, pp. 5173-5176 (2008).

- J4. J.V. Galan, P. Sanchis, J. Blasco and J. Marti, "Study of High Efficiency Grating Couplers for Silicon-Based Horizontal Slot Waveguides," IEEE Photon. Technol. Lett., vol.20, no.12, pp.985-987 (2008).

- J5. J.V. Galan, P. Sanchis, J. Blasco, A. Martinez, J. Marti, J.M. Fedeli, E. Jordana, P. Gautier, and M. Perrin, "Silicon sandwiched slot waveguide grating couplers," IEE Electron. Lett., vol. 45, p. 262 (2009).

- J6. Jose Vicente Galan, Pablo Sanchis, Jaime Garcia, Javier Blasco, Alejandro Martinez, and Javier Martí, "Study of asymmetric silicon cross-slot waveguides for polarization diversity schemes," Appl. Opt., vol. 48, no. 14, pp. 2693-2696 (2009).

- J7. Jose Vicente Galan, Tolga Tekin, Giovani B. Preve, Antoine Brimont and Pablo Sanchis, "Standard compatible packaging solution for silicon photonic integrated circuits with vertical coupling to fiber," submitted to IEEE J. Lightw. Technol. (2010).

- J8. Experimental results on V-groove coupling (in progress, Optics Letters, 2010).

#### Other contributions

- J9. P. Sanchis, J. V. Galan, A. Griol, J. Marti, M. A. Piqueras, J. M. Perdigues, "Low-Crosstalk in Silicon-On-Insulator Waveguide Crossings With Optimized-Angle," IEEE Photon. Technol. Lett., vol.19, no.20, pp.1583-1585 (2007).

- J10. Pablo Sanchis, Pablo Villalba, Francisco Cuesta, Andreas Håkansson, Amadeu Griol, José V. Galán, Antoine Brimont, and Javier Martí, "Highly efficient crossing structure for silicon-on-insulator waveguides," Opt. Lett., vol. 34, no. 14, pp. 2760-2762 (2009).

- J11. J. Palaci, G. E. Villanueva, J. V. Galan, J. Marti, B. Vidal, "Single Bandpass Photonic Microwave Filter Based on a Notch Ring Resonator," IEEE Photon. Technol. Lett., IEEE, vol.22, no.17, pp.1276-1278 (2010).

- J12. Antoine Brimont, Jose Vicente Galán, Jose Maria Escalante, Javier Martí, and Pablo Sanchis, "Group-index engineering in silicon corrugated waveguides," Opt. Lett., vol. 35, no. 16, pp. 2708-2710 (2010).

- J13. A. Martínez, J. Blasco, P. Sanchis, J. V. Galán, J. García-Rupérez, E. Jordana, P. Gautier, Y. Lebour, S. Hernndez, R. Guider, N. Daldosso, B. Garrido, J. M. Fedeli, L. Pavesi, J. Martí, "Ultrafast All-Optical Switching in a Silicon-Nanocrystal-Based Silicon Slot Waveguide at Telecom Wavelengths," Nano Letters, vol. 10, no. 4, pp. 1506-1511 (2010).

- J14. J. Blasco, J. V. Galán, P. Sanchis, J. M. Martínez, A. Martínez, E. Jordana, J. M. Fedeli, J. Martí, "FWM in silicon nanocrystal-based sandwiched slot-waveguides," Optics communications, vol. 283, no. 3, pp. 435-437 (2010).

J15. Sara Mas, José Caraquitena, José V. Galán, Pablo Sanchis, and Javier Martí, "Tailoring the dispersion behavior of silicon nanophotonic slot waveguides," Opt. Express, vol. 18, pp. 20839-20844 (2010).

#### **Conference Proceedings**

#### Main contributions

- C1. J. V. Galán, P. Sanchis and J. Martí, "Low-loss coupling technique between SOI waveguides and standard single-mode fibers," Proceedings of 13th European Conference on Integrated Optics, p. ThG11 (2007).

- C2. J. V. Galan, P. Sanchis, B. Sanchez, J. Marti, "Polarization insensitive fiber to SOI waveguide experimental coupling technique integrated with a V-Groove structure," Proceedings of 4th IEEE International Conference on Group IV Photonics, pp. 110-112 (2007).

- C3. J. V. Galan, P. Sanchis, J. Blasco and J. Marti, "Horizontal slot waveguidebased efficient fibercouplers suitable for silicon photonics," Proceedings of 14th European Conference on Integrated Optics, ThP16, pp. 248-250 (2008).

- C4. J. V. Galan, J. Blasco, P. Sanchis, A. Martinez, J. Marti, J. M. Fedeli, E. Jordana, P. Gautier, M. Perrin, "Vertical grating couplers for silicon sand-wiched slot waveguides," Proceedings of 5th IEEE International Conference on Group IV Photonics, pp. 105-107 (2008).

- C5. J. V. Galan, P. Sanchis, J. Blasco, and J. Marti, "Broadband and highly efficient grating couplers for silicon-based horizontal slot waveguides," Proceedings of SPIE, vol. 6996, p. 69960Q (2008).

- C6. P. Sanchis, J. V. Galan, A. Brimont, A. Griol, J. Hurtado and J. Marti, "High efficiency coupling in silicon photonic devices," Proceedings of Conferencia Espaola de Nanofotnica, pp. 45-46 (2008).

- C7. A. Griol, J. Hurtado, J. V. Galan, P. Sanchis, G. Sanchez, J. Marti, G. Petersson, B. Nilsson and J. Halonen, "Experimental realization of a high efficient coupling technique for SOI devicesbased on inverted taper and V-groove integration" Proceedings of NanoSpain Conference (2008).

- C8. A. Griol, J. Hurtado, J. V. Galán, P. Sanchis, J. A. Ayúcar, J. Martí;, "Physical implementation of an efficient coupling technique for SOI devices employing inverted tapers and V-groove integration," Proceedings of 34th International Conference on Micro and Nano Engineering, p. 560 (2008).

- C9. J. V. Galan, A. Griol, J. Hurtado, P. Sanchis, G. B. Preve, A. Håkansson, J. Marti, "Packaging of silicon photonic devices: grating structures for high efficiency coupling and a solution for standard integration," Proceedings of 17th European Microelectronics and Packaging Conference, pp. 1-6 (2009).

- C10. J. V. Galan, P. Sanchis, J. Marti, S. Marx, H. Schröder, B. Mukhopadhyay, T. Tekin, S. Selvaraja, W. Bogaerts, P. Dumon, L. Zimmermann, "CMOS compatible silicon etched V-grooves integrated with a SOI fiber coupling technique for enhancing fiber-to-chip alignment," Proceedings of 6th IEEE International Conference on Group IV Photonics, pp.148-150 (2009).

- C11. J. V. Galan, P. Sanchis, J. Garcia, A. Martinez, J. Blasco, J. M. Martinez, A. Brimont, J. Marti, "Silicon cross-slot waveguides insensitive to polarization," Proceedings of IEEE LEOS Winter Topicals Meeting, pp. 32-33 (2009).

- C12. J. V. Galan, M. Aamer, P. Sanchis, A. Griol, L. Bellieres, J. Ayucar, J. Marti, "A compact and broadband polarization splitter in SOI," Proceedings of 23rd Annual Meeting of the IEEE Photonics Society, pp.309-310 (2009).

- C13. T. Tekin, L. Zimmermann, H. Schröder, P. Dumon, W. Bogaerts, J. V. Galan, P. Sanchis, W. Whelan-Curtin, D. Beggs. "Generic packaging concepts in the frame of network of excellence ePIXnet," Proceedings of SPIE, vol. 7604, p. 7604-17 (2010).

#### Other contributions

- C14. P. Sanchis, J. V. Galan, A. Brimont, A. Griol, J. Marti, M. A. Piqueras, J. M. Perdigues, "Low-crosstalk in silicon-on-insulator waveguide crossings with optimized-angle," Proceedings of 4th IEEE International Conference on Group IV Photonics, pp. 159-161 (2007).

- C15. R. Spano, J. V. Galan, P. Sanchis, A. Martinez, J. Marti, L. Pavesi, "Group velocity dispersion in horizontal slot waveguides filled by Si nanocrystals," Proceedings of 5th IEEE International Conference on Group IV Photonics, pp. 314-316 (2008).

- C16. A. Brimont, P. Sanchis, J. V. Galan, J. M. Fedeli, A. M. Gutierrez, and J. Marti, "Experimental demonstration of moderately low group velocity in silicon rib photonic Wire Bragg Gratings," Proceedings of 23rd Annual Meeting of the IEEE Photonics Society, pp. 713-714 (2009).

- C17. C. Garcia-Meca, M. Tung, J. V. Galan, R. Ortuno, F. J. Rodriguez-Fortuno, J. Marti, and A. Martinez, "Light compression without reflections," Proc. SPIE, vol. 7711, p. 771121 (2010).

- C18. P. Sanchis, C. J. Oton, J. V. Galan and J. Marti, "High Q Microring Demultiplexer Filter for 60GHz Microwave Photonics Applications," Proceedings of 7th IEEE International Conference on Group IV Photonics, pp.84-86 (2010).

- C19. S. Mas, J. Caraquitena, J.V. Galán, P. Sanchis, J. Martí, "Tailored chromatic dispersion in silicon-on-insulator slot waveguides," Proceedings of 15th European Conference on Integrated Optics, p. ThP28 (2010).

- C20. Rakesh Sambaraju, Jose Vicente Galan-Conejos, Javier Herrera, Amadeu Griol, Claudio Oton, Pablo Sanchis, and Alejandro Martinez, "RF frequency transparent 90° hybrid based on silicon on insulator photonic circuit," Proceedings of SPIE, vol. 7719, p. 771914 (2010).

### Meeting Abstracts

A1. J. V. Galan, P. Sanchis, W. Bogaerts, P. Dumon and L. Zimmermann, "V-Groove approach for inverted taper coupling in silicon photonics," ePIXnet Spring School on Technology for Photonics Integration, Elba island, Italy, 11-17 May (2008).

## Patents

P1. Jose Vicente Galán Conejos, Giovanni Battista Preve, Pablo Sanchis Kilders, Javier Martí Sendra, Günter Lang, Sebastian Marx, Jan Krissler, Tolga Tekin, "CONCEPT AND APPARATUS OF PACKAGING SEV-ERAL PHOTONIC INTEGRATED CIRCUITS WITH VERTICAL FIBER COUPLING" (Spanish application P201031898, pending European extension).

# Contents

| Preface  |                                                |                                                   |                                                 |    |  |  |  |  |  |  |  |

|----------|------------------------------------------------|---------------------------------------------------|-------------------------------------------------|----|--|--|--|--|--|--|--|

| A        | Abstract i<br>List of Publications and Patents |                                                   |                                                 |    |  |  |  |  |  |  |  |

| Li       |                                                |                                                   |                                                 |    |  |  |  |  |  |  |  |

| Ta       | able (                                         | of Con                                            | tents                                           | xi |  |  |  |  |  |  |  |

| 1        | Intr                                           | oduct                                             | ion                                             | 1  |  |  |  |  |  |  |  |

|          | 1.1                                            | Motiv                                             | ation and research context                      | 1  |  |  |  |  |  |  |  |

|          | 1.2                                            | Silicor                                           | Photonics                                       | 4  |  |  |  |  |  |  |  |

|          |                                                | 1.2.1                                             | The fiber-to-chip coupling problem              | 6  |  |  |  |  |  |  |  |

|          | 1.3                                            | Objec                                             | tives and organization of this work             | 8  |  |  |  |  |  |  |  |

| <b>2</b> | Bac                                            | kgrou                                             | nd                                              | 11 |  |  |  |  |  |  |  |

|          | 2.1                                            | Photo                                             | nic Waveguides                                  | 11 |  |  |  |  |  |  |  |

|          |                                                | 2.1.1                                             | SOI nanophotonic waveguides                     | 11 |  |  |  |  |  |  |  |

|          |                                                |                                                   | 2.1.1.1 Polarization: polarization transparency | 14 |  |  |  |  |  |  |  |

|          |                                                | 2.1.2                                             | SOI slot waveguides                             | 16 |  |  |  |  |  |  |  |

|          |                                                | 2.1.3                                             | Coupling to optical fiber                       | 20 |  |  |  |  |  |  |  |

|          | 2.2                                            | 2.2 Efficient coupling to fiber in SOI waveguides |                                                 | 25 |  |  |  |  |  |  |  |

|          |                                                | 2.2.1                                             | Vertical coupling                               | 26 |  |  |  |  |  |  |  |

|          |                                                | 2.2.2                                             | Lateral coupling                                | 27 |  |  |  |  |  |  |  |

|          |                                                | 2.2.3                                             | Grating coupler vs Inverted taper               | 28 |  |  |  |  |  |  |  |

|          |                                                | 2.2.4                                             | 2D-gratings for transparency to polarization    | 32 |  |  |  |  |  |  |  |

|          | 2.3                                            | Summ                                              | nary and conclusions                            | 34 |  |  |  |  |  |  |  |

#### CONTENTS

| 3                                             | Grating-based fiber-to-chip coupling                   |                                                                                   |     |  |

|-----------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------|-----|--|

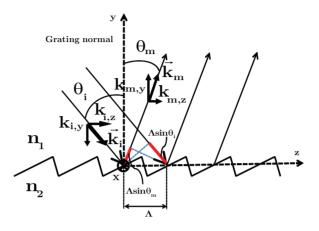

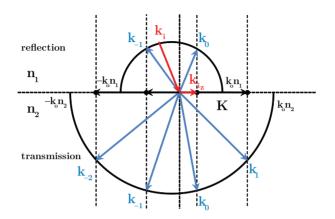

|                                               | 3.1                                                    | Diffraction gratings                                                              | 37  |  |

|                                               | 3.2                                                    | Grating couplers theory                                                           | 39  |  |

|                                               | 3.3                                                    | SOI grating coupler engineering                                                   | 44  |  |

|                                               |                                                        | 3.3.1 Modelling                                                                   | 44  |  |

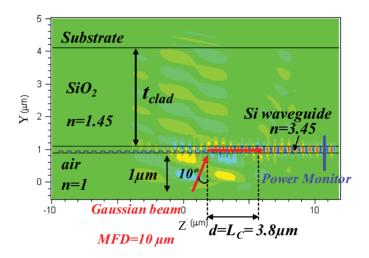

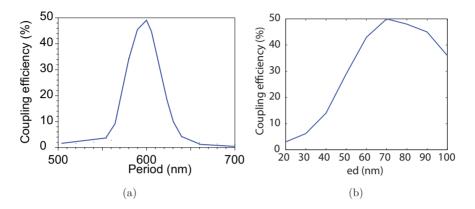

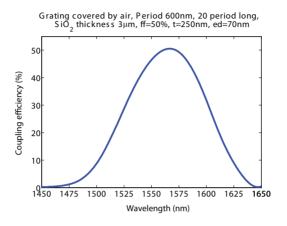

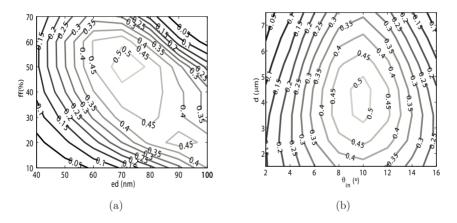

|                                               |                                                        | 3.3.2 Design and simulations                                                      | 48  |  |

|                                               |                                                        | 3.3.3 Fabrication and experimental results                                        | 52  |  |

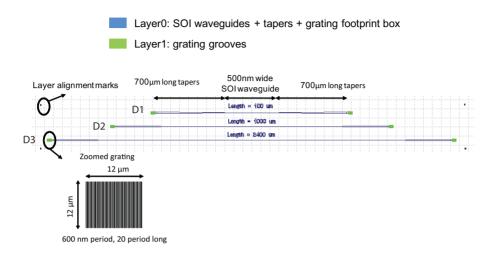

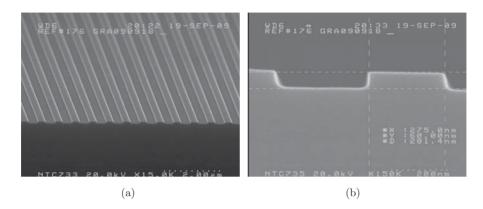

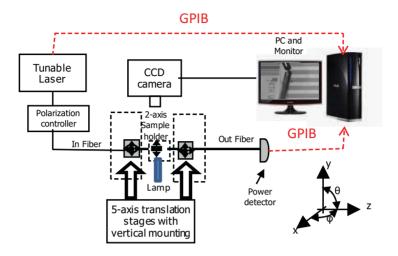

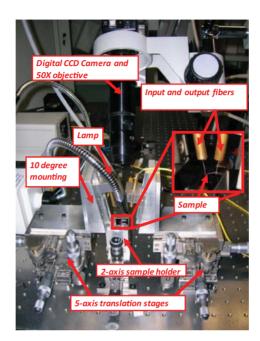

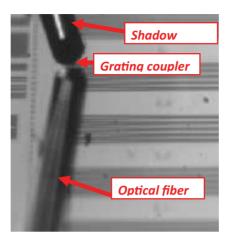

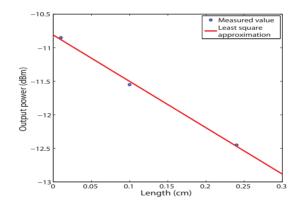

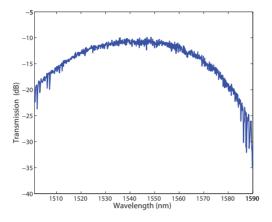

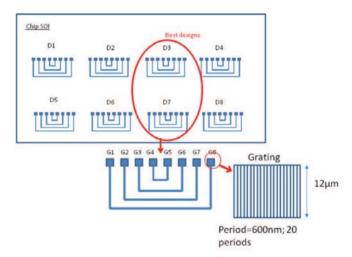

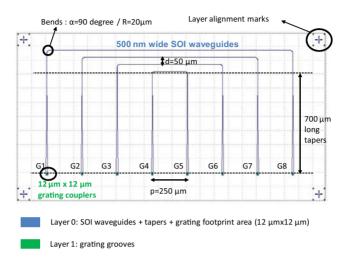

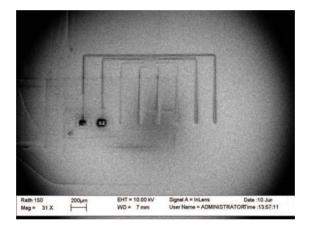

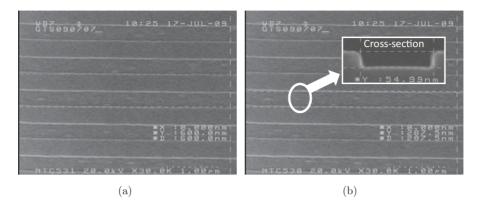

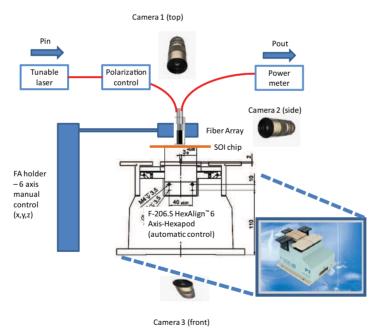

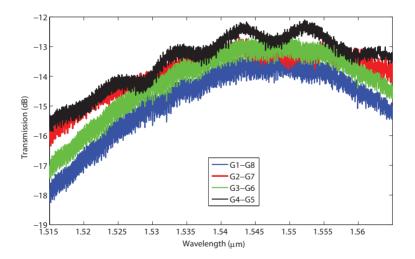

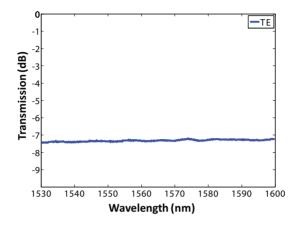

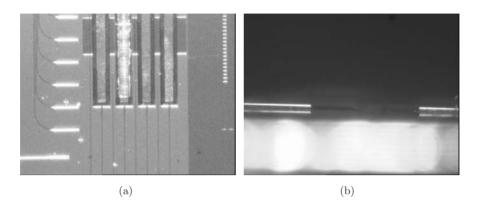

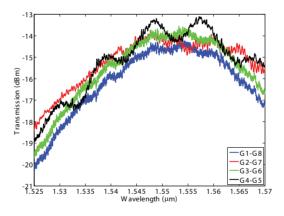

|                                               |                                                        | 3.3.3.1 Multiport grating coupler SOI chips experiments                           | 58  |  |

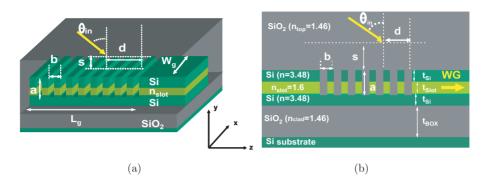

|                                               | 3.4                                                    | Horizontal slot waveguide grating couplers                                        | 68  |  |

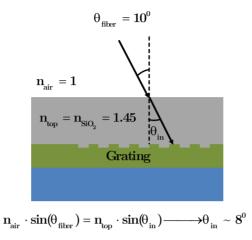

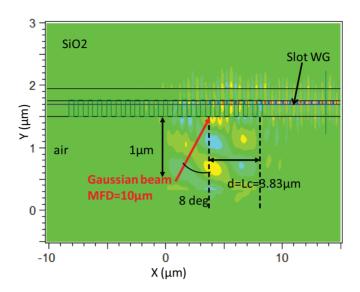

|                                               |                                                        | 3.4.1 Design                                                                      | 69  |  |

|                                               |                                                        | 3.4.2 Fabrication and experimental results                                        | 75  |  |

|                                               | 3.5                                                    | Summary and conclusions                                                           | 77  |  |

| 4 Inverted taper-based fiber-to-chip coupling |                                                        |                                                                                   |     |  |

|                                               | 4.1                                                    | Introduction                                                                      | 83  |  |

|                                               | 4.2                                                    | Inverted taper approach for V-groove integration                                  | 86  |  |

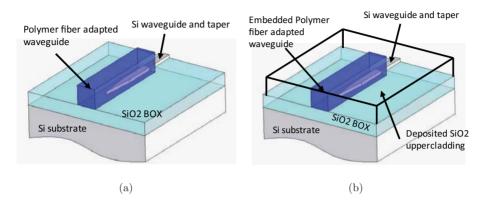

|                                               |                                                        | 4.2.1 Design                                                                      | 88  |  |

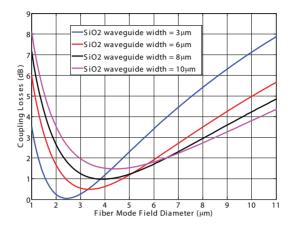

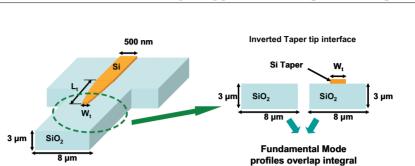

|                                               |                                                        | 4.2.1.1 $SiO_2$ waveguide design and optical fiber choice .                       | 89  |  |

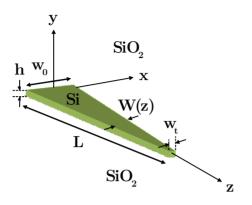

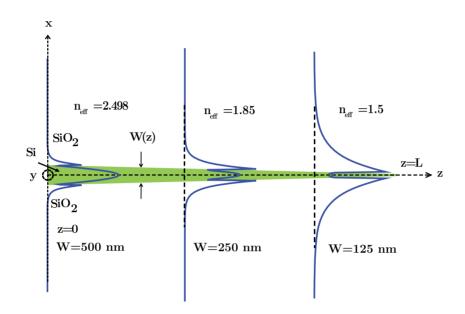

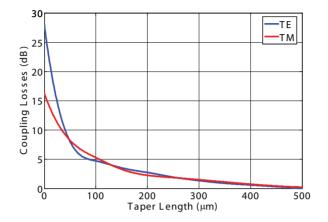

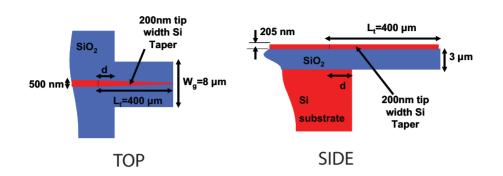

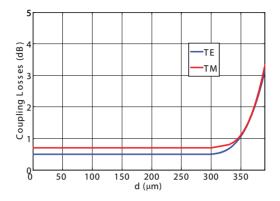

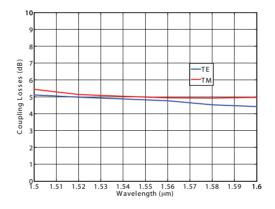

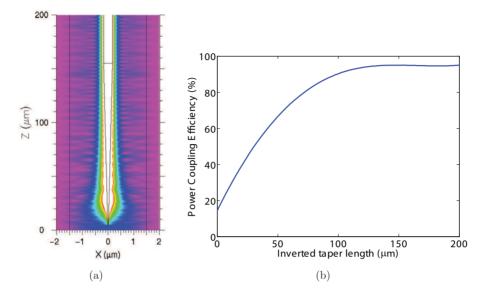

|                                               |                                                        | $4.2.1.2  \text{Inverted taper design} \dots \dots \dots \dots \dots \dots \dots$ | 91  |  |

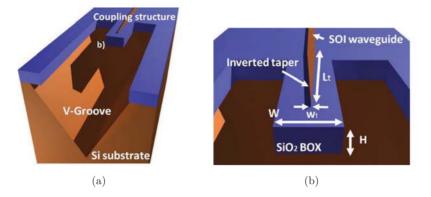

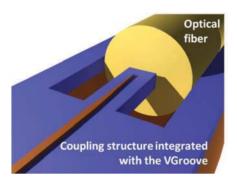

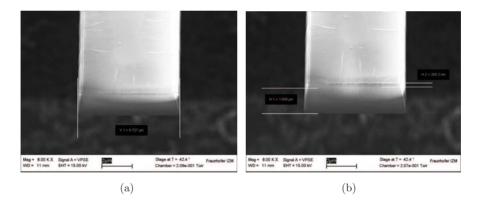

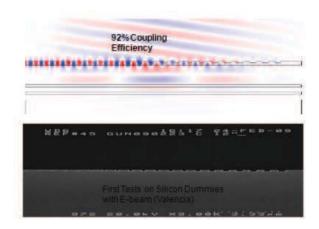

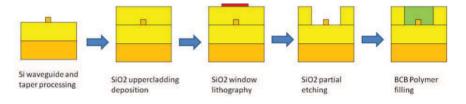

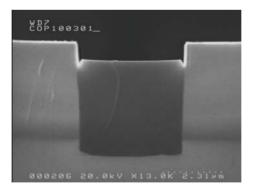

|                                               |                                                        | 4.2.2 Realization                                                                 | 96  |  |

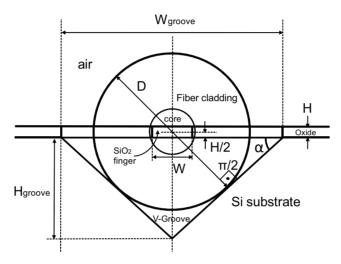

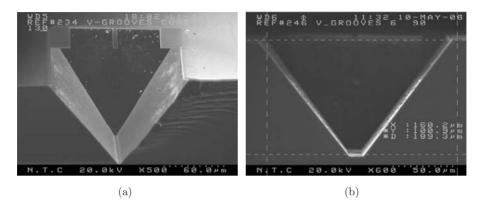

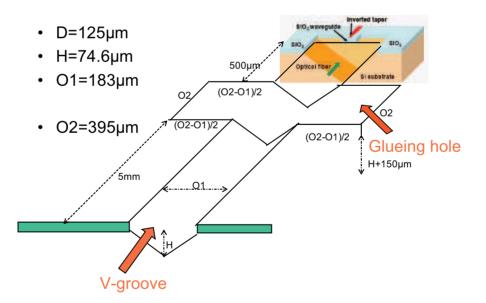

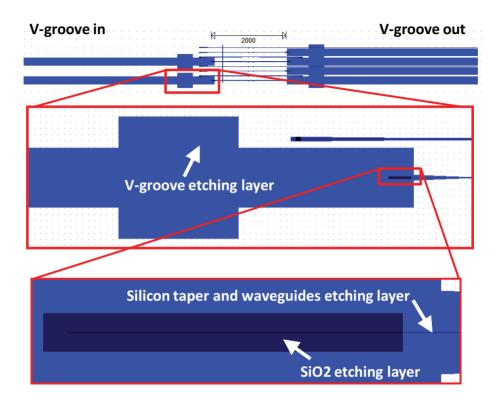

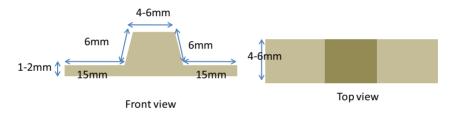

|                                               |                                                        | 4.2.2.1 V-Groove design                                                           | 97  |  |

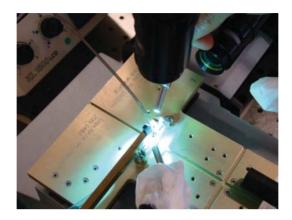

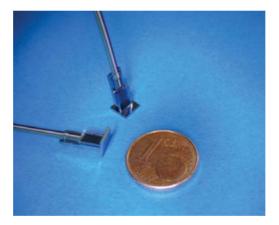

|                                               |                                                        | 4.2.2.2 Fabrication and experimental results                                      | 99  |  |

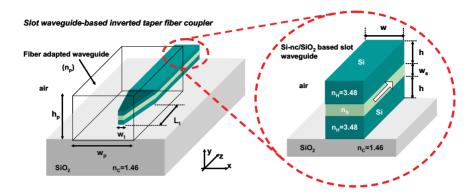

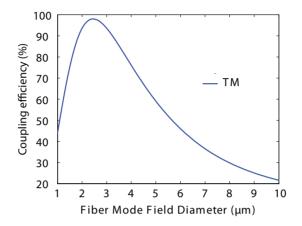

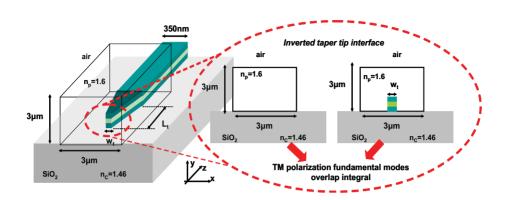

|                                               | 4.3                                                    | Inverted taper structures for horizontal slot waveguides 1                        | 106 |  |

|                                               |                                                        | 4.3.1 Design                                                                      | 108 |  |

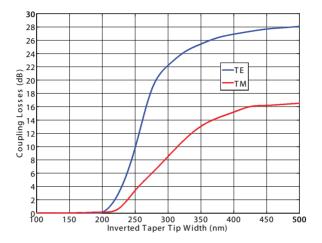

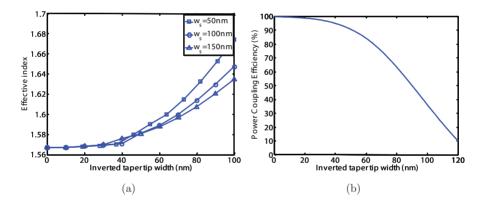

|                                               |                                                        | 4.3.1.1 Inverted taper tip width optimization 1                                   | 109 |  |

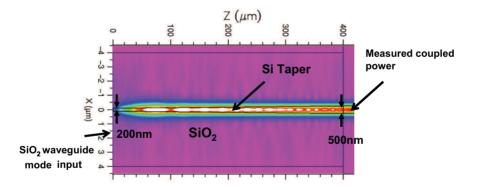

|                                               |                                                        |                                                                                   | 110 |  |

|                                               | 4.4                                                    | Summary and conclusions                                                           | 113 |  |

| <b>5</b>                                      | Ger                                                    | heric packaging solutions for SOI chips                                           | 17  |  |

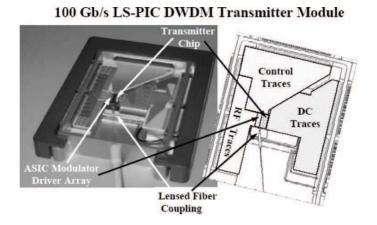

|                                               | 5.1                                                    | Silicon Photonics Packaging                                                       | 117 |  |

|                                               |                                                        | 5.1.1 Fiber Pigtailing                                                            | 118 |  |

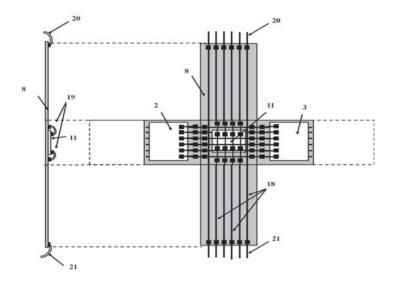

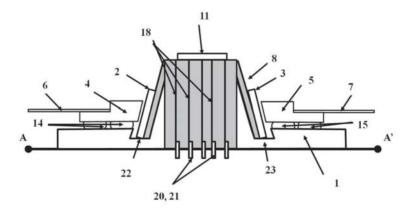

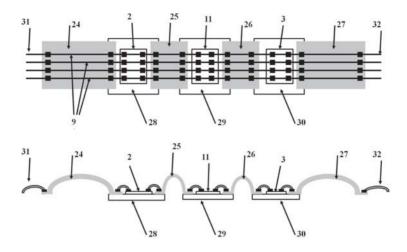

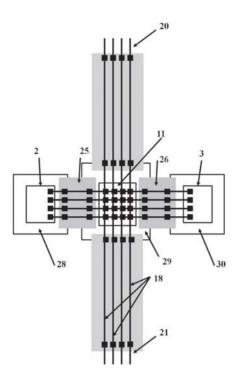

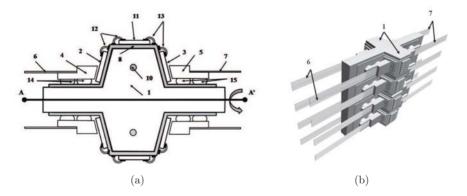

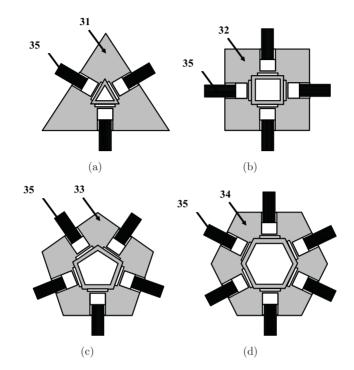

|                                               | 5.2                                                    | Packaging of multiport silicon PICs with vertical coupling to fiber               | 121 |  |

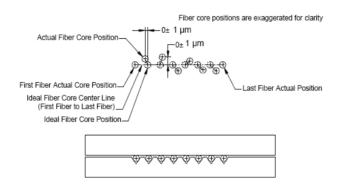

|                                               | 5.3 Packaging solution for grating coupler SOI devices |                                                                                   |     |  |

|                                               |                                                        | 5.3.1 Description of the packaging solution                                       | 125 |  |

#### CONTENTS

|                |                                | 5.3.2  | Detailed   | description $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 126 |  |  |  |  |  |  |  |

|----------------|--------------------------------|--------|------------|-------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

|                |                                |        | 5.3.2.1    | Extensions for different shape FLEX designs                                         | 129 |  |  |  |  |  |  |  |

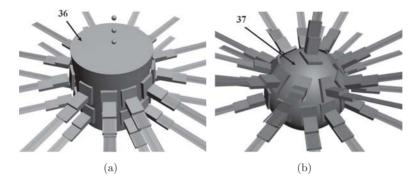

|                |                                |        | 5.3.2.2    | Mirroring and arrays                                                                | 132 |  |  |  |  |  |  |  |

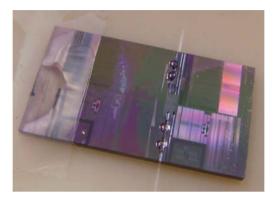

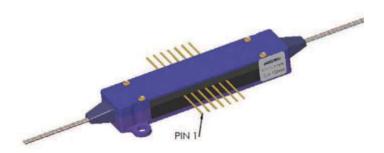

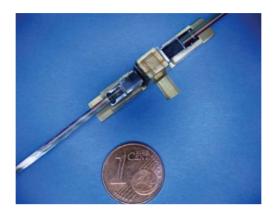

|                |                                | 5.3.3  | Demonst    | rator prototyping                                                                   | 135 |  |  |  |  |  |  |  |

|                | 5.4                            | Summa  | ary and co | onclusions                                                                          | 139 |  |  |  |  |  |  |  |

| 6              | 6 Conclusions and perspectives |        |            |                                                                                     |     |  |  |  |  |  |  |  |

|                | 6.1                            | Conclu | isions     |                                                                                     | 143 |  |  |  |  |  |  |  |

|                | 6.2                            | Perspe | rspectives |                                                                                     |     |  |  |  |  |  |  |  |

|                | 6.3                            | Summa  | ary of ach | ieved results                                                                       | 150 |  |  |  |  |  |  |  |

| Bi             | Bibliography                   |        |            |                                                                                     |     |  |  |  |  |  |  |  |

| Lis            | List of Figures                |        |            |                                                                                     |     |  |  |  |  |  |  |  |

| List of Tables |                                |        |            |                                                                                     |     |  |  |  |  |  |  |  |

## Chapter 1

## Introduction

The aim of this thesis is to tackle the fiber-chip coupling interface problem in silicon photonic technology. This chapter gives an introduction of the innate evolution from fiber optics to integrated photonics towards all-optical networks. Therefore, the main advantages of using silicon photonics are addressed. The fiber-to-chip coupling problem in silicon photonics is then introduced. Finally, we present the main objectives and the organization of this work.

### 1.1 Motivation and research context

Signal transmission and processing by means of optical beams rather than electrical currents or radio waves has been a very interesting topic since the 1960s [1]. Low loss, high data rate capabilities, noise rejection and electrical isolation are just a few of the important features that make fiber optic technology ideal for the transport of information in communication networks [2]. In current telecom and datacom network scenarios, the optical fibers are used to transport the information in the form of light from point A to point B, and is usually installed in the backbone and backhaul network<sup>1</sup>, whilst copper wire or coaxial cable is

$<sup>^{1}</sup>$ In a hierarchical telecommunications network the backhaul portion of the network comprises the intermediate links between the core network, or backbone, of the network and the small subnetworks at the edge of the entire hierarchical network.

#### 1. INTRODUCTION

commonly used in the access network<sup>1</sup> for *last mile*<sup>2</sup> links. One reason is the relatively high cost to bring the fiber closer to the end user. However, these links are several kilometers long, and the fiber significantly outperforms copper and coaxial cables in this range. So, replacing at least part of these links with fiber shortens the remaining copper segments and allows them to run much faster. Following this approach, new emerging technologies such as FTTH (Fiber-To-The-Home)<sup>3</sup> started to arouse the interest of consolidated Telecom operators all over the world. The key objective was to be able to offer to the customers a higher speed and broadband access, by bringing the fiber link directly to their homes. An overview on FTTH technology standards and deployments is reported in [3]. Even in FTTH technology, the network equipment mainly remains electronic circuitry, and the optical signals are just used to transport the data, nor for data processing. So, in the network nodes, the routing and signal processing is performed electrically, and the electrical signal is converted back into light and sent on the output fiber and transport it towards the next node. These opto-electronic conversions cause an increase of the latency of the whole transport network, and the benefits of high velocity capability of using optical fibers is unfortunately wasted. This fact represents the real bottleneck in current communication networks. Current fiber-based networks use so electronic switching and are therefore limited to electronic speeds of a few gigabits per second. The most efficient way for making the most of optical fiber advantages is to replace microelectronic circuitry with optical circuits capable for all-optical signal processing. For enabling higher speeds up to terabit per second that support optical fiber, it is important that the signal remains in the photonic domain throughout its path. Such networks, which use optical switching and routing, are called all-optical. Fortunately, besides the main function of guiding light, optical fibers can also be developed as attractive photonic components performing desired optical signal

<sup>&</sup>lt;sup>1</sup>An access network is that part of a communications network which connects subscribers to their immediate service provider.

<sup>&</sup>lt;sup>2</sup>In telecommunications, the *last mile* or *last kilometer* is the final leg of delivering connectivity from a communications provider to a customer in the access network.

$<sup>{}^{3}</sup>FTTH$  is a broadband network architecture that uses optical fiber to replace all or part of the usual metal local loop used for last mile telecommunications in which the fiber reaches the boundary of the living space, such as a box on the outside wall of a home.

processing, through corresponding modifications on the fiber core. For instance, very selective optical filters can be obtained by adding a periodic variation (or (1) grating<sup>1</sup>) to the refractive index of the fiber core [4], and very good performance erbium doped fiber amplifier (EDFA) can be achieved by doping the fiber core with erbium material [5]. Moreover, more complex devices and systems can be obtained by combining several of those discrete single elements. However, optical fiber-based devices result in high cost and large discrete elements. The key to make more advanced and cheaper components is the integration of these optical components on a single chip. This integration should enable the replacement of the large racks of equipment used in the network nodes today by a few photonic chips. When the optical components are integrated on chip, we talk about photonic integrated circuits (PICs), and the term photonics is then used, as the realization of these photonic components deals with the manipulation of light or photons. Following same approach as in microelectronic devices, the commitment towards a process of photonic device integration and miniaturization has stirred up the interest of industry, and thereby integrated photonics emerges [6]. Hybrid technologies based on alloys of III-V compounds, such as indium phosphyde (InP) or gallium arsenide (GaAs), had initially a stronger impact for the development of PICs. The main reason was that it was easier to obtain light emitting sources with these materials, due to their direct fundamental energy bandgap compared to indirect bandgap of silicon at telecom wavelengths<sup>2</sup> [9, 10]. The main objective in III-V photonics research has been to find a technology in which a variety of PICs can be easily fabricated in a generic foundry process. This concept is well known in silicon microelectronics, but in III-V photonics it was new and lead to a high cost technology development. As happend with silicon microelectronics, photonic technology to the mass market may happen only if one can bring high volume manufacturing at low cost. It was possible because microelectronic integration processes support the integration of a set of basic building blocks, which make possible more complex circuits by simple interconnection between them,

<sup>&</sup>lt;sup>1</sup>Also known as Fiber Bragg Grating (FBG).

<sup>&</sup>lt;sup>2</sup>Although first electro-optical free carrier injection laser prototypes have recently been achieved in silicon technology [7], electrically pumped pure silicon-based lasers continue being the Holy Grail in silicon photonics [8]

#### 1. INTRODUCTION

but was not initially a trivial task in III-V photonics. So, the idea of using silicon and its mature technologic platform for developing photonics started to make sense driven by the increasing demand for low-cost mass-production [11].

### **1.2** Silicon Photonics

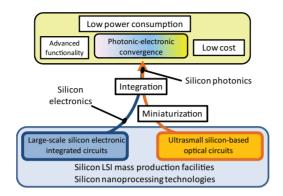

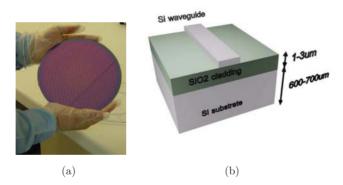

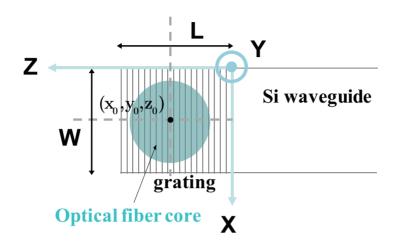

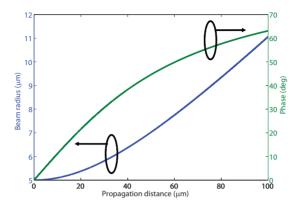

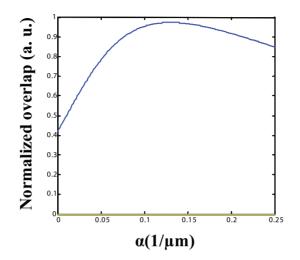

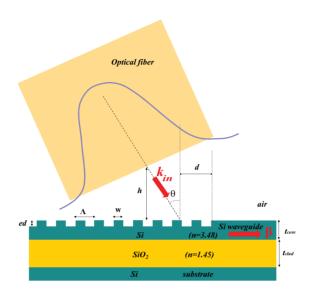

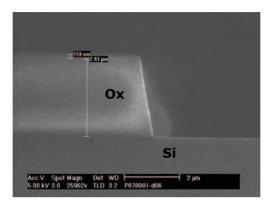

The leading motivation in favor of silicon photonic technology is that it aims to achieve a compact convergence between photonics and electronics. The directions are to use silicon, which has been the base material for electronic circuits, to replace the various non-silicon materials currently used to form optical devices and to integrate ultrasmall silicon optical circuits and silicon electronic circuits on the same chip. The use of silicon lets us utilize the advanced planar mass-production facilities that have enabled the low-cost production of electronic circuits (i. e. mature silicon complementary metal-oxide semiconductor (CMOS) microelectronic manufacturing). Therefore, it is expected to provide an economical benefit by achieving advanced functionality in optical devices that support the network at a lower cost. It is also expected to minimize the total power consumption in network systems through the development of photonic-electronic convergence equipment that consumes less power while achieving even more advanced functionality. Fig. 1.1 depicts a graph summarizing the silicon photonics industry direction towards a photonic-electronic convergence by courtesy of NTT Microsystem Integration Laboratories<sup>1</sup> [12]. Moreover, the possibility for getting high-quality and cheap Silicon-on-Insulator (SOI) wafers makes the motivation more attractive. With the availability of platforms like SOI technology, creating planar waveguide circuits becomes even more feasible. An example of a commercial 8" SOI wafer is illustrated in Fig. 1.2(a). Fig. 1.2(b) depicts a schematic of a conventional strip SOI waveguide showing the SOI wafer layerstack and its main layer thickness values. The strong light confinement in SOI, given by the high index contrast between silicon core  $(n = 3.48 \text{ at } \lambda = 1550 nm)$  and silicon dioxide  $(SiO_2)$  (n = 1.45)at  $\lambda = 1550 nm$ ), makes it feasible to scale photonic devices to the hundreds of nanometer level. Moreover, it is possible to reduce the minimum bending radius

<sup>&</sup>lt;sup>1</sup>https://www.ntt-review.jp/archive/2010/201002.html

Figure 1.1: Silicon photonics industry direction towards a photonic-electronic convergence by courtesy of *NTT Microsystem Integration Laboratories* [12].

Figure 1.2: (a) Commercial 8'' SOI wafer. (b) Schematic of a SOI strip waveguide showing section layerstack of SOI wafers. The thickness of the silicon waveguiding layer is between 200 nm and 400 nm.

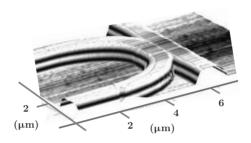

to the micrometre range, also offering the possibility of an ultra-high scale of integration of photonic circuits. This can so extremely decrease the cost of silicon devices. The most illustrative example of a compact device in SOI platform is a ring resonator. Fig. 1.3 depicts an atomic force microscope (AFM) image of a  $5\mu m$  diameter SOI ring resonator based on singlemode SOI waveguides with 500 nm × 220 nm cross-section dimension. Small waveguides with small bending

#### 1. INTRODUCTION

Figure 1.3: AFM image of a  $5\mu m$  diameter SOI ring resonator based on strip waveguides with 500 nm  $\times$  250 nm cross section dimension.

radii can improve the characteristics of basic photonic devices such as modulators and optical filters [13, 14]. Moreover, such small waveguides can realise an ultra-high optical power density, which can be as much as 1000 times that in a conventional singlemode fiber, enhancing nonlinear optical effects in chipscale devices [15]. This interesting outcome has enabled important features, such as optical amplification [16], Raman lasing [17], all optical switching [18] and wavelength conversion [19], among others; functions that until recently were perceived to be beyond the reach of silicon. Novel potential applications even beyond optical communications have so emerged, such as environmental monitoring, imaging, biomedicine, spectroscopy, lab-on-a-chip, and optical logic, among others [20].

#### 1.2.1 The fiber-to-chip coupling problem

Conventional singlemode SOI strip waveguides are about 220 nm thick and 500 nm wide. Because of their small dimensions, and also because the related fabrication tolerances are in the nanometer range, we use the term nanophotonic<sup>1</sup> waveguides. However, standard singlemode fibers (SMF) are very large size compared to nanophotonic SOI waveguides. Typical core diameter size of a standard

<sup>&</sup>lt;sup>1</sup>Nanophotonics or Nano-optics is the study of the behavior of light on the nanometer scale. It is considered as a branch of optical engineering which deals with optics, or the interaction of light with particles or substances, at deeply subwavelength length scales. The study of nanophotonics involves two broad themes: studying the novel properties of light at the nanometer scale and enabling highly power efficient devices for engineering applications.

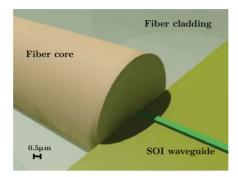

Figure 1.4: The fiber-to-chip coupling problem. Optical fiber and nanophotonic SOI waveguide drawn on same scale.

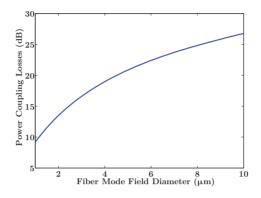

SMF is about  $8\mu m$ . Thus, injecting (coupling) light from an optical fiber to a nanophotonic waveguide becomes a difficult task. This is depicted in Fig. 1.4. where an optical fiber and a nanophotonic SOI waveguide are drawn on same scale. The high difference in the dimensions between the fiber and the waveguide causes a high mismatch between their optical modes. Due to this mismatch, a coupling structure is needed to adapt a wide fiber to a narrow silicon waveguide improving the coupling loss. Typically, a direct butt coupling between a singlemode fiber (mode field diameter MFD=10  $\mu$ m) and a nanophotonic waveguide  $(MFD < 1 \ \mu m)$  leads to more than 20dB insertion (coupling) loss. The insertion loss between an optical fiber and a nanophotonic circuit is definitively a big issue as it is directly linked with performances such as the link reach, the signalling rate, the receiver sensitivity, and so on. Moreover, in order to be compatible with functions for FTTH or wavelength division multiplexing (WDM) applications for instance, a good coupling structure is also required to be broadband and polarization insensitive. Finally, considering the packaging cost, the footprint of a coupling structure must be kept small and have sufficient alignment tolerances.

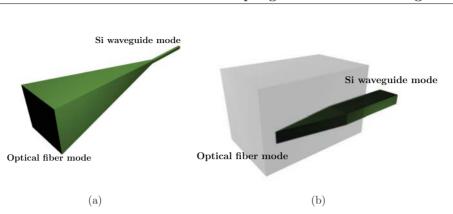

To solve the fiber-chip coupling problem, two main strategies have appeared in literature, depending on the physical direction in which the fiber is coupled to the PIC: vertical and lateral (horizontal) coupling techniques. So, this work develops along these two lines, in accordance with the literature.

### 1.3 Objectives and organization of this work

The basic objective of the work reported on this thesis is to develop efficient fiberto-chip coupling techniques in SOI technology. To achieve this objective, we will mainly focus on the study of the fiber coupling problem in SOI waveguides, by designing efficient vertical and lateral coupling structures. Hence, the final goal of this work is the experimental realization of the studied coupling techniques. To carry out this study, we first need to understand the performance of SOI waveguides, as well as their coupling issues to these vertical and horizontal coupling techniques. Second, the ability for electromagnetic modelling of the photonic structures involved is also needed. Once modelling and design optimization in finished, the designs will be fabricated using standard CMOS fabrication tools, in order to crosscheck experimental and theoretical results. We will also apply the studied coupling techniques to other kinds of waveguiding structures in silicon. such as slot waveguides. Finally, after successing in the realization of these coupling techniques prototypes, the assembly and packaging of some of the developed practical examples will be done, as an starting point for functional SOI chips for practical applications. Our main researching tasks are so described as follows:

- 1. Study, modeling and design optimization of efficient vertical coupling techniques between optical fibers and silicon photonic integrated circuits.

- 2. Study, modeling and design optimization of efficient horizontal coupling techniques between optical fibers and silicon photonic integrated circuits.

- 3. Apply the studied techniques to other kinds of silicon waveguides (i. e., slot waveguides).

- 4. Fabrication and experimental demonstration of the obtained designs.

- 5. Assemble and package of some of the developed coupling prototypes.

To reach the score objectives, this work is organized as follows: Chapter 2 gives an overview on the background of silicon nanophotonic waveguides, and the coupling to fiber problem is discussed. A summary of the state-of-the art of the already existing solutions for an efficient coupling to fiber is presented. The polarization problem is also explained. Novel kinds of silicon slot waveguides are also introduced. Chapter 3 deals with vertical coupling techniques. As we will focus on grating coupler-based structures, design, modelling as well as fabrication and characterisation results of grating-based fiber couplers are included. We also include here slot-waveguide based grating couplers for coupling to silicon slot waveguides. Chapter 4 deals with lateral (horizontal) coupling techniques. As we will focus on inverted taper-based structures, design, modelling as well as fabrication and characterisation issues of inverted taper-based fiber couplers are included. We also include here slot waveguide-based inverted taper couplers for coupling to silicon slot waveguides. Chapter 5 is focused on packaging solutions of our coupling approaches. A generic packaging solution for multiport grating coupler silicon photonic devices is studied in detail. As a result, s demonstrator prototype based on this packaging approach is achieved. Finally, in chapter 6 we present our main conclusions and perspectives for future work.

## Chapter 2

## Background

The aim of this thesis was introduced in chapter one by bringing into context the fiber-to-chip coupling problem in silicon photonics. Before starting to tackle the problem, this second chapter encloses the background and state-of-the-art. Subsequently, our work contributions will be introduced in the consecutive chapters.

### 2.1 Photonic Waveguides

The essential building block of a PIC is a waveguide. A waveguide plays a double role in a PIC. On one hand, the components on the PIC are linked to each other by means of waveguides. On the other hand, an access waveguide acts as the interface between the PIC and the outside world. Most of the optical waveguides used in communications are singlemode: they support only one guided mode for each polarization. For taking the most of the strong light confinement in silicon photonic technology, such as SOI platform, the SOI nanophotonic strip waveguide (or silicon nanowire) is the most attractive waveguiding structure, as its cross-section dimension is in the nanometer range.

#### 2.1.1 SOI nanophotonic waveguides

SOI nanophotonic waveguides will make it possible to integrate a lot of functions on one chip, thus enabling important cost reductions. Fig. 2.1(a) depicts the cross-section drawing of an asymmetric strip SOI nanophotonic waveguide

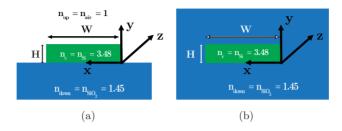

Figure 2.1: (a) Asymmetric and (b) symmetric SOI nanophotonic waveguides.

(shallow etch<sup>1</sup>), which is covered by air (air refractive index:  $n_{up} = n_{air} = 1$ ), as well as Fig. 2.1(b) depicts the cross-section drawing of a symmetric SOI strip waveguide which is covered by  $SiO_2$  ( $SiO_2$  refractive index:  $n_{down} = n_{SiO_2} = 1.45$ @  $\lambda = 1.55 \mu m$ ). The refractive index of the waveguide silicon core is also shown in Figs. 2.1(a) and 2.1(b), and is equal to  $n_c = n_{Si} = 3.48 \ @ \lambda = 1.55 \mu m$ . The waveguide width is W, and the waveguide thickness is H in both cases. Propagation direction is along the z-axis, and (x,y) axis are with the cross-section of the waveguide, according to axis definition of Fig. 2.1. For propagation by total internal reflection (TIR) in the waveguide core, we have  $n_c > n_{up}$  and  $n_c > n_{down}$ . Multimode waveguides are undesirable in SOI circuits, as their performance can be compromised by the presence of multiple modes, causing undesirable effects such as intermodal dispersion or optical signal distorsion, among others. Singlemode condition in these kinds of waveguides basically depends on both boundary conditions (polarization state of light, and waveguide material refractive indices) and waveguide dimensions. Regarding the waveguide height (H), and considering commercial SOI wafers, typical values are H = 200 nm, H = 220 nm, and H = 250 nm. To achieve SOI singlemode waveguides, typical width value is W = 500 nm and W = 450 for asymmetric and symmetric waveguides, respectively [21].

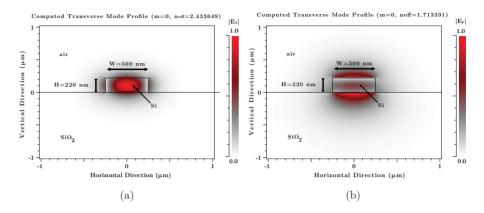

Figs. 2.2(a) and 2.2(b) respectively depict the Transverse Electric (TE) and the Transverse Magnetic (TM) electric field profiles ( $|E_x|$  and  $|E_y|$ , respectively)

<sup>&</sup>lt;sup>1</sup>When just the silicon is etched, we call the waveguide shallow etch, as well as the waveguide is called deep etch wire when also the oxide is etched. Shallow etch wires are desirable because the wire losses without oxide etch are much lower [21].

Figure 2.2: Electric field profile for (a) the TE ( $|E_x|$ ) and (b) the TM ( $|E_y|$ ) fundamental modes of asymmetric SOI waveguide @  $\lambda = 1.55 \mu m$ .

of the optical mode of a 500 nm wide singlemode asymmetric SOI waveguide for H = 220 nm and  $\lambda = 1.55 \ \mu$ m. For the calculation of the modes in Fig. 2.2 we have used a full-vectorial mode solver based on the Beam Propagation Method (BPM). As in three dimensional (3D) structures do not exist exact solutions for pure orthogonal TE and TM modes when solving the wave equation, they are respectively referred in literature as TE-like and TM-like modes. Simplifying, we will just name them here as TE and TM. In Fig. 2.2, we can see that a stronger confinement in the waveguide core is obtained for the TE mode, compared to the TM one. It can also be corroborated by obtaining a higher mode effective index  $(n_{eff})$  for the case of TE polarization (see Fig. 2.2). The effective index of an optical mode  $(n_{eff})$  is related to its propagation constant ( $\beta$ ) according to the following equation [22]:

$$\beta = k_0 n_{eff} \tag{2.1}$$

where  $k_0 = 2\pi/\lambda$  is the wave number in vacuum. Assuming that  $n_c > n_{up}$ ,  $n_c > n_{down}$  and  $n_{up} \leq n_{down}$ , we have  $k_0 n_{up} \leq k_0 n_{down} < \beta < k_0 n_c$ , and, consequently,  $n_{up} \leq n_{down} < n_{eff} < n_c$  for the guided modes in the waveguide. So, as  $n_{eff,TE} \neq n_{eff,TM}$ , we have  $\beta_{TE} \neq \beta_{TM}$ , and the SOI waveguides are strongly polarization dependent, and a strongly birefringent medium. This high birefringence can

#### 2. BACKGROUND

cause a polarization beating between TE and TM modes, thus confusing the polarization. Due to a stronger confinement of the TE mode, most existing SOI devices work with TE polarization. So, the polarization should be controlled externally in order to assure the propagation of the TE fundamental mode, also minimizing the TM mode propagation in the waveguide, and so the polarization beating effect.

#### 2.1.1.1 Polarization: polarization transparency

Regarding the polarization in the waveguides, when both TE and TM modes propagate in the waveguide, we can define the birefringence parameter (B) as [23]:

$$B = \frac{2\pi\delta n}{\lambda_0} \tag{2.2}$$

where  $\lambda_0$  is the free space wavelength, and  $\delta n = n_{eff,TE} - n_{eff,TM}$  is the difference between the effective indices of the optical modes of each polarization. The waveguide length for  $2\pi$  polarization rotation is definded as the beating length and is expressed as [23]:

$$L_p = \frac{2\pi}{B} \tag{2.3}$$

So, the waveguide length for  $\pi/2$  polarization rotation can be defined as  $L_p/4$ , and it corresponds to the waveguide length in which TE and TM polaritations (orthogonals) are 90 degrees rotated, thus confusing them. For the effective indices obtained in Fig. 2.2 for the asymmetric 500 nm wide SOI waveguide and  $\lambda = 1.55\mu m$ , we obtain  $B = 2.92rad/\mu m$ , and  $L_p/4 = 0.538\mu m$ . So, in just a 538 nm short distance, each polarization has rotated 90 degrees and may be confused with its orthogonal polarization. Hence, a control of the polarization of light has to be implemented externally in every SOI circuit.

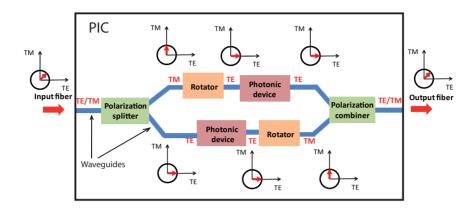

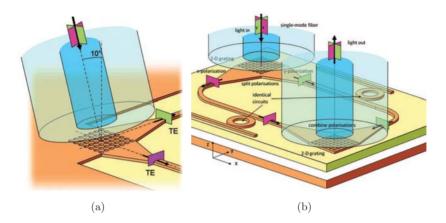

A more elegant solution for transparency to polarization in SOI devices is the implementation of polarization diversity schemes [24]. One example of a polarization diversity circuit is shown in Fig. 2.3. Light coming from the input fiber (with random polarization) is launched into the circuit and then splitted in two orthogonal polarizations (TE and TM) using a polarization splitter component. The TM arm is also TE rotated by using a polarization rotator component.

Figure 2.3: Example of polarization diversity circuit in silicon photonics [24]. The polarization state of light is shown along the circuit.

Then, by duplicating same photonic device in both arms, just TE polarization interacts with the devices, which are previously optimized for optimum TE polarization performance. At the output of the polarization diversity circuit, same configuration as at the input is implemented for rotating the other arm, combine them by using a polarization combiner, which is equal to the input splitter, and finally coupled into the output fiber. Recently, we have experimentally demonstrated very compact and broadband SOI polarization splitters less than 5  $\mu$ m long [25]. Regarding polarization rotators in SOI, slanted angle [26] and triangular waveguide [27] based devices have been proposed in literature for better rotating the optical axis of the modes. However, fabrication of such devices is not trivial, as their physical geometry is not compatible with planar fabrication processes. Novel planar-compatible devices based on the breaking symmetry of an almost square waveguide also recently appeared in literature [28]. The problem continues being the fabrication tolerances of such devices, and postcompensation methods are required by modifying the reflractive index of the upper cladding layer for achieving the rotation efficiently [28]. Polarization rotators are so the most difficult building block device in polarization diversity schemes.

For an efficient implementation of a polarization diversity scheme in SOI, efficient fiber-to-chip coupling structures insensitive to polarization are required for light coupling into the waveguides in the access ports of the polarization

Figure 2.4: Schematic of a slot-waveguide [29, 30]. Light propagates along the z-direction.

diversity circuit in Fig. 2.3. So, the fiber-to-chip coupling problem is strongly linked to the polarization problem for transparency to polarization purposes in SOI devices.

#### 2.1.2 SOI slot waveguides

A slot-waveguide [29, 30] is a waveguide that guides strongly confined light in a subwavelength-scale low refractive index region by TIR. A slot-waveguide (see Fig. 2.4) consists of two strips or slabs of high-refractive-index  $(n_H)$  materials separated by a subwavelength-scale low-refractive-index  $(n_S)$  slot region and surrounded by low-refractive-index  $(n_C)$  cladding materials. This kind of waveguide is also called vertical slot waveguide.

The principle of operation of a slot-waveguide is based on the discontinuity of the electric field (E) at high-refractive index contrast interfaces. Maxwell equations state that, to satisfy the continuity of the normal component of the electric displacement field (D) at an interface, the corresponding E-field must undergo a discontinuity with higher amplitude in the low refractive index side. That is, at an interface between two regions of dielectric constants  $\epsilon_S$  and  $\epsilon_H$ , respectively [29]:

$$D_S^N = D_H^N \tag{2.4}$$

$$\varepsilon_S E_S^N = \varepsilon_H E_H^N \tag{2.5}$$

$$n_S^2 E_S^N = n_H^2 E_H^N (2.6)$$

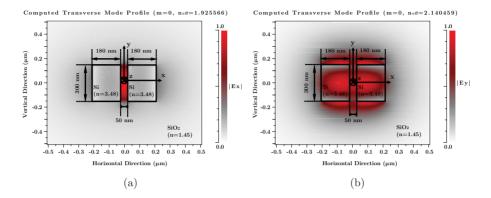

Figure 2.5: E-field distribution of the fundamental mode in a SOI slot waveguide  $@ \lambda = 1.55 \ \mu m$  and for (a) TE and (b) TM polarizations.

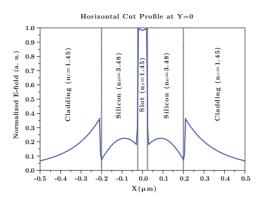

where the superscript N indicates the normal components of  $\vec{D}$  and  $\vec{E}$  vector fields. Thus, if  $n_S \ll n_H$ , then  $E_S^N \gg E_H^N$ . Given that the slot critical dimension (distance between the high-index slabs or strips) is comparable to the exponential decay length of the fundamental eigenmode of the guided-wave structure, the resulting E-field normal to the high-index-contrast interfaces is enhanced in the slot and remains high across it. The power density in the slot is much higher than that in the high-index regions. Since wave propagation is due to TIR, there is no interference effect involved and the slot-structure exhibits very low wavelength sensitivity [29]. Figs. 2.5(a) and 2.5(b) depict the E-field distribution of the fundamental mode in a SOI slot waveguide with a  $SiO_2$  filled 50 nm wide slot region for TE and TM polarizations, respectively, and an operating wavelength  $\lambda = 1.55 \ \mu m$ . For the calculation of the modes in Fig. 2.5 we have used a full-vectorial mode solver based on the BPM. Waveguide dimensions are also depicted in both figures. Strong confinement in the slot region is just with Fig. 2.5(a), in which major E-field component is parallel to the x-axis (TE polarization). Fig. 2.6 depicts a horizontal cut at y = 0 of the E-field distribution profile in the slot waveguide for TE polarization, better showing the strong E-field intensity in the slot region.

Multiple slot regions in the same guided-wave structure (multi-slot waveguide) have also been proposed in order to increase the optical field in the low-refractive-

Figure 2.6: Horizontal cut at y = 0 of the E-field distribution in Fig. 2.5(a).

Figure 2.7: Schematic of a sandwiched slot waveguide [33]. Light propagates in the z-direction.

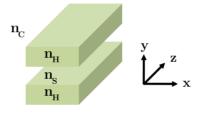

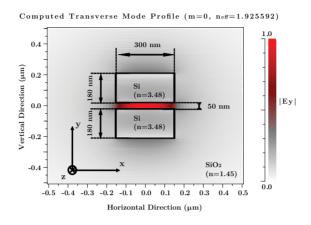

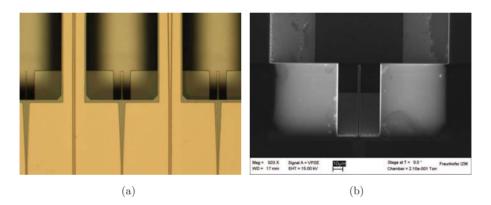

index regions [31,32]. For achieving a strong confinement in the slot region for TM polarization, sandwiched (horizontal) slot waveguides have also been implemented in literature [33]. Fig 2.7 depicts an schematic of a sandwiched slot waveguide. Due to the 90 degrees rotation compared to slot waveguide in Fig. 2.4, the strong confinement in the slot region is now with TM polarization. Fig 2.8 depicts the E-field distribution of the fundamental mode in a SOI horizontal slot waveguide @  $\lambda$ =1.55 µm and for TM polarization, calculated via 3D-BPM based full-vectorial mode solver simulations. Compared to vertical slot waveguides, fabrication of sandwiched slot waveguides is easier, as its sandwiched geometry allows to use industrial microelectronic fabrication tools, especially deep-UV lithography [34].

A slot-waveguide produces high E-field amplitude, optical power, and optical intensity in low-index materials at levels that cannot be achieved with conventional waveguides. This property allows highly efficient interaction between

Figure 2.8: E-field distribution of the fundamental mode in a SOI slot waveguide  $@ \lambda = 1.55 \ \mu m$  and for TM polarization.

fields and active materials, which may lead to all-optical switching [35], optical amplification [36] and optical detection [37] on integrated photonics. As firstly pointed out in [29], the slot waveguide can be used to greatly increase the sensitivity of compact optical sensing devices ([38]-[41]) or to enhance the efficiency of near-field optics probes. Strong E-field confinement can be localized in a nanometer-scale low-index region. This can so efficiently exploited in such nonlinear applications, where the change of the refractive index ( $\Delta n$ ) of the slot material due to the Kerr effect<sup>1</sup> can be modelled as [42]:

$$\Delta n = 2n_2 I \tag{2.7}$$

where  $n_2$  is the nonlinear refractive index and I is the optical intensity, which can also be expressed as [42]:

$$I = \frac{P}{A_{eff}} \tag{2.8}$$

where P is the optical power and  $A_{eff}$  is the effective area. So, the only way for achieving an increase in  $\Delta n$  is to increase either  $n_2$  or I, which is also equivalent

<sup>&</sup>lt;sup>1</sup>The Kerr effect, also called the quadratic electro-optic effect, is a change in the refractive index of a material in response to an applied electric field. The Kerr effect is distinct from the Pockels effect in that the induced index change is directly proportional to the square of the electric field instead of varying linearly with it.

#### 2. BACKGROUND

Figure 2.9: Schematic for loss contribution in SOI waveguides.

to reduce  $A_{eff}$  for a given optical power, according to Eq. 2.8. Thus, due to light strong confinement in a lower nanometer sized region, the slot waveguide can achieve a stronger nonlinear Kerr effect compared to conventional SOI waveguides. Moreover, if the slot is filled with a nonlinear material with higher  $n_2$ , the nonlinear effect can be even stronger. Recently, silicon nanocrystals (Si-nc) embedded in  $SiO_2$  has demonstrated very promising characteristics for nonlinear applications [43]. Its Kerr coefficient is approximately two orders of magnitude higher than in silicon [44]. Design of slot waveguides filled with Si-nc/SiO<sub>2</sub> material for optimum nonlinear performance is presented in [45]. Recently, we experimentally demonstrated all-optical switching at telecom wavelengths in a horizontal silicon slot waveguide-based ring resonator filled with highly nonlinear Si-nc/SiO<sub>2</sub> [46]. We also proposed silicon cross-slot waveguides insensitive to polarization, which are also suitable for the implementation of the access waveguides in polarization diversity schemes in slot waveguide based devices [47, 48].

#### 2.1.3 Coupling to optical fiber

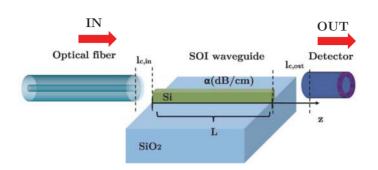

When the light coming from an optical fiber with power  $P_{in}$  is launched into a SOI waveguide, output detected power  $(P_{out})$  can be expressed as (see Fig. 2.9):

$$P_{out}(mW) = P_{in}(mW) \cdot \eta_{c,in} \cdot \eta_{c,out} \cdot e^{-\alpha(Np/cm) \cdot L(cm)}$$

(2.9)

where  $\eta_{c,in}$ ,  $\eta_{c,out}$  are the input and output insertion (coupling) factors or coupling efficiencies ( $0 \le \eta_c \le 1$ ), respectively, L is the waveguide length expressed in cm, and  $\alpha$  is waveguide propagation loss, which is expressed in Np/cm. Eq. 2.9 can also be expressed in the following logarithm form:

$$P_{out}(dBm) = P_{in}(dBm) - L_{c,in}(dB) - L_{c,out}(dB) - \alpha(dB/cm) \cdot L(cm) \quad (2.10)$$

where  $L_{c,in}$  and  $L_{c,out}$  are the input and output coupling losses, respectively, and  $\alpha(dB/cm)$  are the waveguide propagation losses, expressed in dB/cm. The relation between Np/cm and dB/cm is (for power units):

$$\alpha(dB/cm) = 10\log_{10}e \cdot \alpha(Np/cm) \approx 4.34 \cdot \alpha(Np/cm)$$

(2.11)

as well as coupling efficiencies are related to coupling loss by means of the expression:

$$L_c = -10\log_{10}(\eta_c) \tag{2.12}$$

The major cause for propagation loss in a SOI waveguide operating at  $\lambda$ =1.55  $\mu m$  is the waveguide sidewall roughness, which is introduced by imperfections in the waveguide fabrication processes [49]. For obtaining low propagation loss below 1 dB/cm, very precise fabrication processes and very accurate lithography machinery are needed [50]. Novel strategies have recently been demonstrated for achieving ultra-low loss silicon waveguides fabricated without any silicon etching, achieving propagation loss downto 0.3 dB/cm [51].

The most important source of loss in SOI waveguides is so the coupling to the optical fiber. It is basically due to the large difference in both mode size and index contrast<sup>1</sup> between the singlemode fiber and the waveguide.

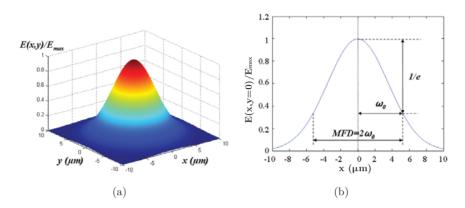

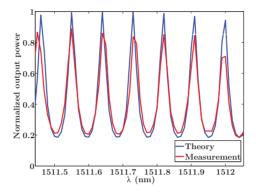

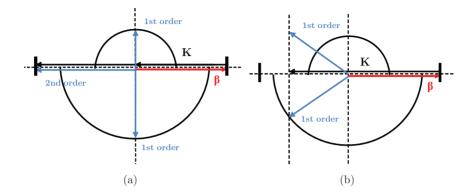

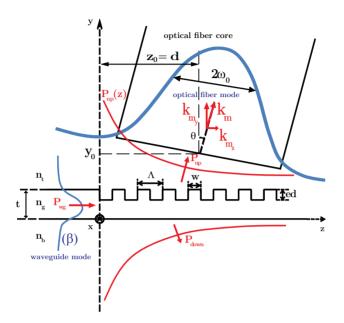

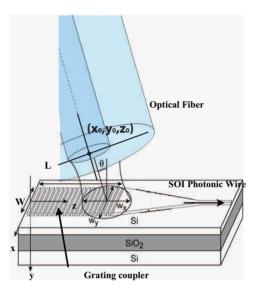

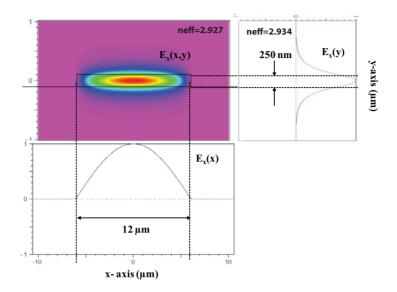

For evaluating the coupling loss factor due to difference in mode size between the fiber and the SOI waveguide, we can calculate the power overlap integral between the electric field profile of the fundamental mode in the fiber  $(E_f)$  and in the waveguide  $(E_{wg})$  at the fiber-waveguide interface (i. e. the position z = 0) [22]: