Listar por autor "Gadea Gironés, Rafael"

RiuNet: Repositorio Institucional de la Universidad Politécnica de Valencia

- RiuNet repositorio UPV

- :

- Listar por autor

JavaScript is disabled for your browser. Some features of this site may not work without it.

Buscar en RiuNet

Listar

Mi cuenta

Ayuda RiuNet

Admin. UPV

Listar por autor "Gadea Gironés, Rafael"

Mostrando ítems 1-20 de 169

-

Gadea Gironés, Rafael; Rocabado-Rocha, José Luis; Fe, Jorge; Monzó Ferrer, José María (MDPI AG, 2024-01)[EN] Artificial intelligence (AI) is one of the most promising technologies based on machine learning algorithms. In this paper, we propose a workflow for the implementation of deep neural networks. This workflow attempts ...

-

Rosa Seivane, Manuel Antonio (Universitat Politècnica de València, 2017-03-01)Se enseña la programación en OpenCL, comenzando por la instalación de un SDK y un ejemplo sencillo para posteriormente mejorar la eficiencia del algoritmo de redes neuronales “differential evolution”. Para esto se programa ...

-

Spaggiari, Michele; Herrero Bosch, Vicente; Lerche, Christoph Werner; Aliaga Varea, Ramón José; Monzó Ferrer, José María; Gadea Gironés, Rafael (IOP Publishing: Hybrid Open Access, 2011-01)In this article we introduce AMIC (Analog Moments Integrated Circuit), a novel analog Application Specific Integrated Circuit (ASIC) front-end for Positron Emission Tomography (PET) applications. Its working principle is ...

-

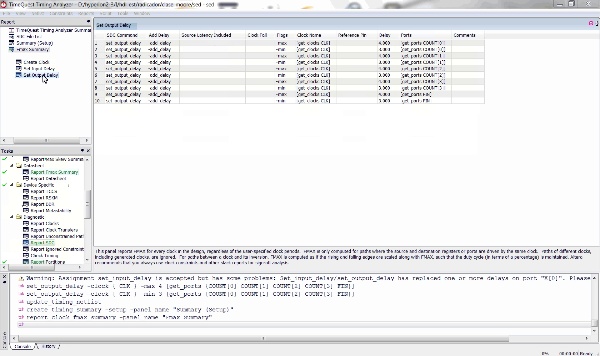

Gadea Gironés, Rafael (Universitat Politècnica de València, 2020-03-02)Analisis temporal estático de un diseño básico con un control-path y un data path

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2017-05-19)Analizar el consumo mediante fichero de actividad obtenida por simulación HDL de un diseño complejo hardware software, que nos permita evaluar la eficiencia energética de las modificaciones realizadas a un sistema digital ...

-

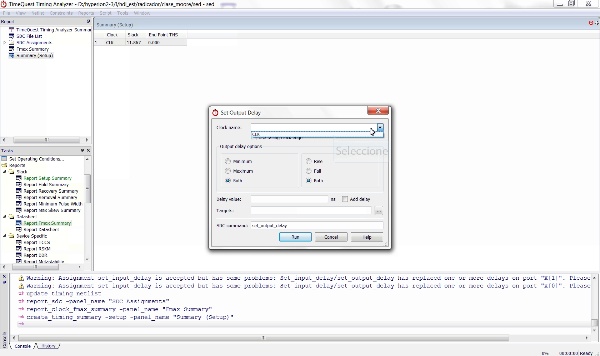

Gadea Gironés, Rafael (Universitat Politècnica de València, 2020-03-11)Obtención cambios de prestaciones al analizar paths que terminan en el exterior

-

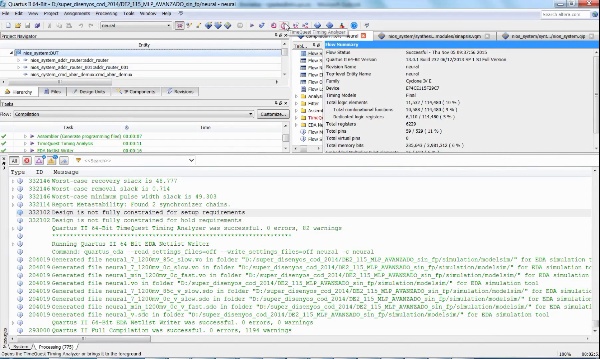

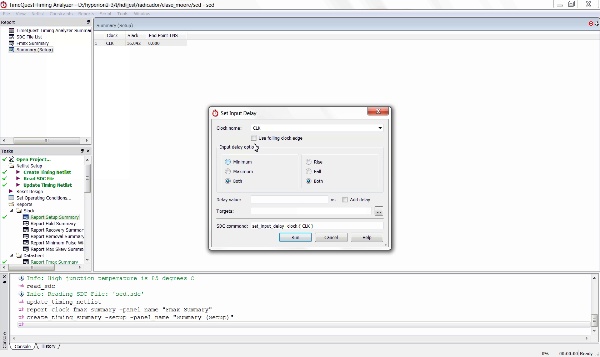

Gadea Gironés, Rafael (Universitat Politècnica de València, 2020-03-02)Obtención cambios de prestaciones al analizar paths procedentes del exterior

-

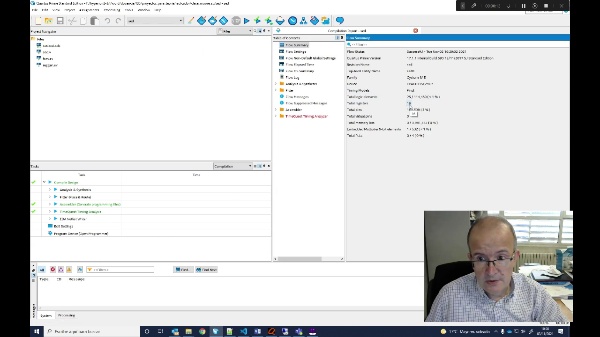

Gadea Gironés, Rafael (Universitat Politècnica de València, 2019-02-19)Caracterizar temporalmente un diseño con NIOS2 Obtención de la frecuencia máxima de reloj con la que podemos trabajar

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2013-05-31)Estudio de cómo realizar un análisis de los márgenes de activación de un diseño incluyendo los "path" que empiezan en el exterior de nuestro diseño

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2013-05-31)Estudio de cómo realizar un análisis de los márgenes de activación de un diseño incluyendo los "path" que terminan en el exterior de nuestro diseño

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2013-05-30)Estudio de como se puede acometer una análisis temporal estático que estudie los márgenes de retención

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2020-03-11)Incidencia en los diseños de problemas de márgenes de retención

-

Barriuso Medrano, Claudio (Universitat Politècnica de València, 2020-09-04)[ES] Conforme avanza la industria electrónica, los circuitos integrados aumentan en complejidad. Las nuevas capacidades de fabricación permiten integrar en un chip de reducidas dimensiones gran cantidad de transistores. El ...

-

Gadea Gironés, Rafael (2021-12-21)Realización de ASM con un solo fichero SystemVerilog

-

Gadea Gironés, Rafael (2024-06-13)Paso de ASM de tipo Mealy a una descripción Verilog fundamentalmente constituida por un proceso always que describe conjuntamente Control-Path y acciones del Data-path

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2024-06-17)Este objeto describe como plantear una solución hardware mediante el uso de máquinas algorítmicas (ASM) de tipo Mealy

-

Gadea Gironés, Rafael (2024-06-20)Paso de un ASM Moore a código Verilog, eludiendo poner jerarquía pero separando claramente los elementos de data-path y control-path

-

Gadea Gironés, Rafael (2024-06-09)Paso de especificación a solución ASM mediante un modelo Moore

-

Roig Monzón, Pablo (Universitat Politècnica de València, 2022-04-07)[ES] El presente proyecto plantea, en el ámbito del diseño digital y la verificación funcional, un sistema de automatización de regresiones. Existe un repositorio compartido donde se suben tanto los ficheros de diseño ...

-

Sánchez Alfaro, Marc (Universitat Politècnica de València, 2022-10-15)[ES] El presente TFG busca desarrollar un banco de pruebas mediante un entorno o gestor Python denominado VUNIT que permita automatizar la verificación de un microprocesador RISC-V descrito en HDL que cumpla un juego de ...

Mostrando ítems 1-20 de 169

Universitat Politècnica de València. Unidad de Documentación Científica de la Biblioteca (+34) 96 387 70 85 · RiuNet@bib.upv.es