Listar por palabra clave "HDL"

RiuNet: Repositorio Institucional de la Universidad Politécnica de Valencia

- RiuNet repositorio UPV

- :

- Listar por palabra clave

JavaScript is disabled for your browser. Some features of this site may not work without it.

Buscar en RiuNet

Listar

Mi cuenta

Ayuda RiuNet

Admin. UPV

Listar por palabra clave "HDL"

Mostrando ítems 1-10 de 10

-

Marcos Ortigosa, Pablo (Universitat Politècnica de València, 2024-11-21)[EN] This work addresses the problem of generating different types of waves. In a wave generator, it is necessary to be able to control the characteristics of the waves being used, which are basically amplitude and frequency, ...

-

Sánchez Alfaro, Marc (Universitat Politècnica de València, 2022-10-15)[ES] El presente TFG busca desarrollar un banco de pruebas mediante un entorno o gestor Python denominado VUNIT que permita automatizar la verificación de un microprocesador RISC-V descrito en HDL que cumpla un juego de ...

-

Rohde, Johanna (Universitat Politècnica de València, 2017-12-12)This master thesis describes the "SOCAO" source-to-source compiler that translates C/C++ input sources into an OpenCL accelerated program. The concept is to accelerate a time consuming software function in a two step ...

-

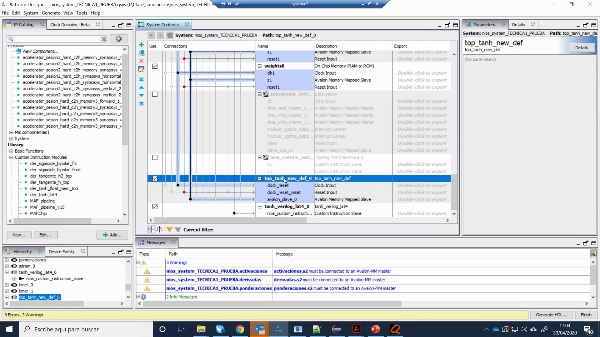

Gadea Gironés, Rafael (2023-06-06)Diseño de funciones con HDL: verificación

-

Martínez Martínez, César (Universitat Politècnica de València, 2017-05-03)El Trabajo Fin de Grado que aquí se propone consiste en la realización de un pequeño robot, tipo plataforma con dos motores de control que lleve un sistema de detección de obstáculos para poder cambiar la trayectoria y ...

-

Rodríguez Vercher, Juan Carlos (Universitat Politècnica de València, 2019-03-06)[ES] En el presente trabajo se aborda el diseño y prototipado de un sintetizador digital de audio sobre una arquitectura System on Chip (SoC). El diseño se plantea sobre la herramienta Simulink® y, mediante plug-ins para ...

-

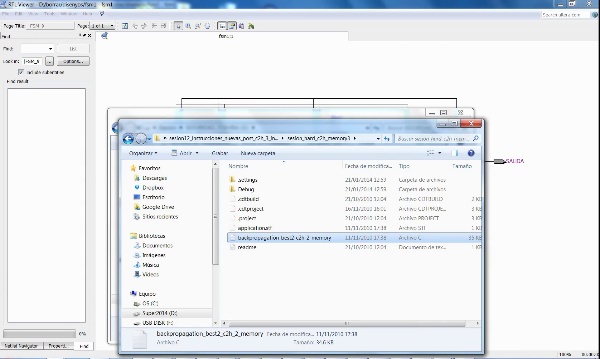

Gadea Gironés, Rafael (2024-06-09)Configuración de vscode para poder ver el hardware descrito en HDL

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2020-05-19)Realización mediante simulador HDL de una verificación de un sistema Hardware-software

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2016-06-01)El objeto presenta de modo muy básico cómo simular un fichero HDL de tipo Verilog mediante el uso de un simulador multilenguaje

-

Zomeño Tortajada, Alejandro (Universitat Politècnica de València, 2020-10-19)[ES] Proyecto de desarrollo de un sistema de verificación de implementaciones HDL del microprocesador RISC mediante una plataforma embebida PYNQ basada en FPGA de la serie ZINQ, que disponen en su interior de cores ARM. ...

Mostrando ítems 1-10 de 10

Universitat Politècnica de València. Unidad de Documentación Científica de la Biblioteca (+34) 96 387 70 85 · RiuNet@bib.upv.es