Listar por palabra clave "SystemVerilog"

RiuNet: Repositorio Institucional de la Universidad Politécnica de Valencia

- RiuNet repositorio UPV

- :

- Listar por palabra clave

JavaScript is disabled for your browser. Some features of this site may not work without it.

Buscar en RiuNet

Listar

Mi cuenta

Ayuda RiuNet

Admin. UPV

Listar por palabra clave "SystemVerilog"

Mostrando ítems 1-14 de 14

-

Ravelo Mederos, Álvaro (Universitat Politècnica de València, 2020-10-19)[ES] El objetivo de este Trabajo Fin de Máster es desarrollar una Verification IP (VIP). Una VIP es una IP desarrollada utilizando lenguajes de descripción hardware (HDL) que tiene como finalidad garantizar el correcto ...

-

Seguí Pérez, Mireia (Universitat Politècnica de València, 2023-10-05)[ES] El presente trabajo de fin de grado ha sido desarrollado en la empresa Maxlinear. El objetivo de este es desarrollar el diseño de una Verificacion IP (VIP) para comprobar el funcionamiento de interfaces que utilicen ...

-

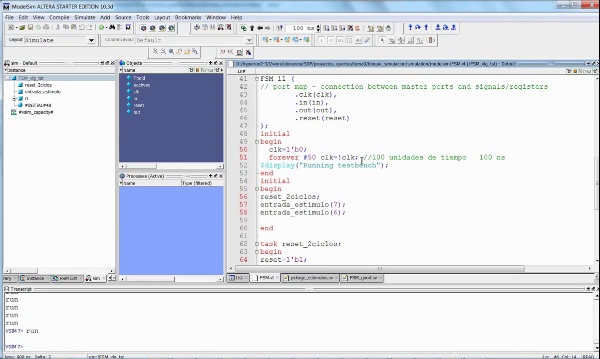

Ramón Alamán, David (Universitat Politècnica de València, 2023-07-11)[EN] The present work develops, in System Verilog, a RISC-V IP core, both single-cycle and multi-cycle, employing the RV32I (32-bit integer handling RISC-V architecture) ISA (Instruction Set Architecture). A PID controller ...

-

Herraiz Calatayud, María (Universitat Politècnica de València, 2019-10-09)[ES] La Metodología de Verificación Universal (UVM) es una metodología estandarizada para la verificación de diseños de circuitos integrados. Se basa en una extensa biblioteca de clases escritas en SystemVerilog a partir ...

-

Fernández Bravo, Álvaro (Universitat Politècnica de València, 2021-10-11)[ES] El presente Trabajo Fin de Máster ha sido desarrollado dentro de la empresa Maxlinear. Su objetivo principal es desarrollar una metodología que permita el uso del lenguaje de programación Python en un entorno de ...

-

Fernández Bravo, Álvaro (Universitat Politècnica de València, 2019-10-09)[ES] Este proyecto se ha llevado a cabo para entender y analizar el funcionamiento de una memoria caché, y cómo esta puede mejorar la velocidad de acceso del procesador a memoria. En concreto, nos hemos centrado en una ...

-

Barreras Almarcha, Héctor (Universitat Politècnica de València, 2021-10-11)[ES] Proponemos una solución de librerías software para habilitar el análisis, modificación y virtualización programáticos de lenguajes de descripción hardware con el principal objetivo de aumentar la productividad de los ...

-

Amutio Duarte, Alejandro (Universitat Politècnica de València, 2024-04-09)[ES] El proceso de verificación de circuitos integrados evita la propagación de errores desde la etapa de diseño hasta el proceso de fabricación y el producto final, evitando así un gasto baldío de tiempo y recursos ...

-

Ern Triviño, Nuria (Universitat Politècnica de València, 2024-10-10)[ES] El objetivo principal del presente proyecto es la implementación de diversos efectos de audio en un dispositivo FPGA. Para ello, se ha empleado el software Quartus Prime de Intel para el diseño, y los programas ...

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2016-06-01)Caracterizar las limitaciones de un procedimiento Verilog punto de partida Uso de paquetes, pasos por referencia y variables automáticas

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2015-03-09)En este objeto de aprendizaje se demuestra el funcionamiento de las operaciones básicas en el manejo de colas de Systemverilog, que suelen ser muy importantes en tareas de verificación de sistemas digitales

-

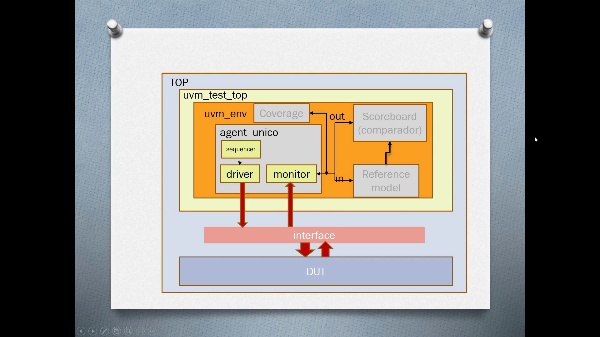

Gadea Gironés, Rafael (2021-05-21)Tecnología UVM. Generación del proyecto de banco de pruebas basado en metodología UVM e inserción de los componentes del environment.

-

Melgar Beltrán, Tomás (Universitat Politècnica de València, 2024-09-26)[ES] Este trabajo trata sobre la verificación digital de un circuito integrado encargado de proporcionar digitalmente las lecturas que le llegan de un sensor de píxeles activos. Este dispositivo está siendo desarrollado ...

-

Fabregat López, Jorge (Universitat Politècnica de València, 2019-10-09)[ES] Metodología de verificación mediante el sistema de clases UVM de un sub bloque funcional basado en una memoria OTP Synopsis DesignWare NVM. El bloque incluye el controlador para la memoria, sistemas de detección y ...

Mostrando ítems 1-14 de 14

Universitat Politècnica de València. Unidad de Documentación Científica de la Biblioteca (+34) 96 387 70 85 · RiuNet@bib.upv.es