Listar por palabra clave "UVM"

RiuNet: Repositorio Institucional de la Universidad Politécnica de Valencia

- RiuNet repositorio UPV

- :

- Listar por palabra clave

JavaScript is disabled for your browser. Some features of this site may not work without it.

Buscar en RiuNet

Listar

Mi cuenta

Ayuda RiuNet

Admin. UPV

Listar por palabra clave "UVM"

Mostrando ítems 1-18 de 18

-

Barriuso Medrano, Claudio (Universitat Politècnica de València, 2020-09-04)[ES] Conforme avanza la industria electrónica, los circuitos integrados aumentan en complejidad. Las nuevas capacidades de fabricación permiten integrar en un chip de reducidas dimensiones gran cantidad de transistores. El ...

-

Roig Monzón, Pablo (Universitat Politècnica de València, 2022-04-07)[ES] El presente proyecto plantea, en el ámbito del diseño digital y la verificación funcional, un sistema de automatización de regresiones. Existe un repositorio compartido donde se suben tanto los ficheros de diseño ...

-

Ravelo Mederos, Álvaro (Universitat Politècnica de València, 2020-10-19)[ES] El objetivo de este Trabajo Fin de Máster es desarrollar una Verification IP (VIP). Una VIP es una IP desarrollada utilizando lenguajes de descripción hardware (HDL) que tiene como finalidad garantizar el correcto ...

-

Andújar Muñoz, Sofía (Universitat Politècnica de València, 2023-10-05)[ES] El objetivo de este trabajo fin de grado es el diseño y verificación de una Verification Intelectual Property (VIP) del protocolo Open Core Protocol (OCP) utilizando la metodología Universal Verification Methodology ...

-

Seguí Pérez, Mireia (Universitat Politècnica de València, 2023-10-05)[ES] El presente trabajo de fin de grado ha sido desarrollado en la empresa Maxlinear. El objetivo de este es desarrollar el diseño de una Verificacion IP (VIP) para comprobar el funcionamiento de interfaces que utilicen ...

-

Herraiz Calatayud, María (Universitat Politècnica de València, 2019-10-09)[ES] La Metodología de Verificación Universal (UVM) es una metodología estandarizada para la verificación de diseños de circuitos integrados. Se basa en una extensa biblioteca de clases escritas en SystemVerilog a partir ...

-

Barrera Comeche, Vicente (Universitat Politècnica de València, 2022-10-14)[ES] El presente TFG busca desarrollar un banco de pruebas mediante la metodología UVM que permita automatizar la verificación de un microprocesador RISC-V descrito en HDL que cumpla un juego de instrucciones determinado. RISCV ...

-

Fernández Bravo, Álvaro (Universitat Politècnica de València, 2021-10-11)[ES] El presente Trabajo Fin de Máster ha sido desarrollado dentro de la empresa Maxlinear. Su objetivo principal es desarrollar una metodología que permita el uso del lenguaje de programación Python en un entorno de ...

-

Bayo Pérez, Pablo (Universitat Politècnica de València, 2024-10-10)[ES] Este TFG aborda el diseño e implementación de un banco de pruebas para realizar la verificación de un controlador de alimentación a nivel de bloques. Se realiza en el marco de un proyecto con la empresa Analog Devices. ...

-

Amutio Duarte, Alejandro (Universitat Politècnica de València, 2024-04-09)[ES] El proceso de verificación de circuitos integrados evita la propagación de errores desde la etapa de diseño hasta el proceso de fabricación y el producto final, evitando así un gasto baldío de tiempo y recursos ...

-

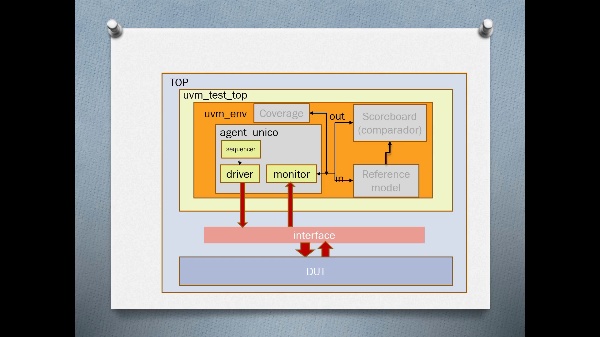

Gadea Gironés, Rafael (2021-05-21)Tecnología UVM. Generación del proyecto de banco de pruebas basado en metodología UVM y comprobación de resultados.

-

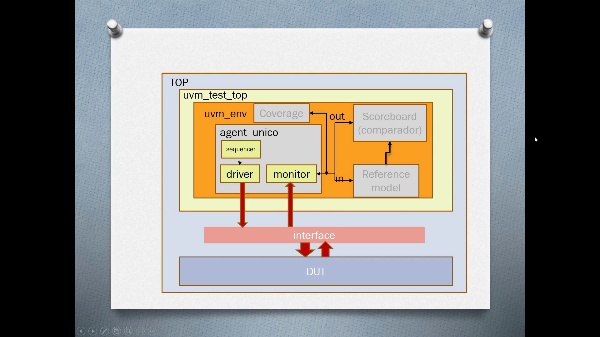

Gadea Gironés, Rafael (2021-05-21)Tecnología UVM. Generación del proyecto de banco de pruebas basado en metodología UVM e inserción de los componentes del environment.

-

Gadea Gironés, Rafael (2021-05-21)Metodología UVM. Generación del proyecto de banco de pruebas basado en metodología UVM, introducción del modelo de referencia y monitorización de estímulos y respuestas.

-

Gadea Gironés, Rafael (Universitat Politècnica de València, 2020-06-10)La creación de la estructura de tetstbench en UVM viene facilitada por herramientas de generación semiautomática que vamos a utilizar

-

Gadea Gironés, Rafael (2021-05-21)Metodología UVM. Generación del proyecto de banco de pruebas basado en metodología UVM y aleatorización con constraints.

-

Fabregat López, Jorge (Universitat Politècnica de València, 2019-10-09)[ES] Metodología de verificación mediante el sistema de clases UVM de un sub bloque funcional basado en una memoria OTP Synopsis DesignWare NVM. El bloque incluye el controlador para la memoria, sistemas de detección y ...

-

Juan Cerdá, José (Universitat Politècnica de València, 2022-04-07)[ES] El trabajo trata sobre la verificación des de cero de un conversor analógico-digital de aproximaciones sucesivas a nivel de bloque en un entorno DMS. Este bloque forma parte de un chip que va a ser desarrollado por ...

-

Martínez Sánchez, Pablo (Universitat Politècnica de València, 2023-10-05)[ES] Cada vez la sociedad demanda circuitos más complejos y de tamaño más reducido, requiriendo un rediseño de estos de forma continua, adaptándolos a cada necesidad y a cada sistema en los que van a ser finalmente ...

Mostrando ítems 1-18 de 18

Universitat Politècnica de València. Unidad de Documentación Científica de la Biblioteca (+34) 96 387 70 85 · RiuNet@bib.upv.es