- RiuNet repositorio UPV

- :

- Investigación

- :

- Tesis doctorales

- :

- Ver ítem

JavaScript is disabled for your browser. Some features of this site may not work without it.

Buscar en RiuNet

Listar

Mi cuenta

Estadísticas

Ayuda RiuNet

Admin. UPV

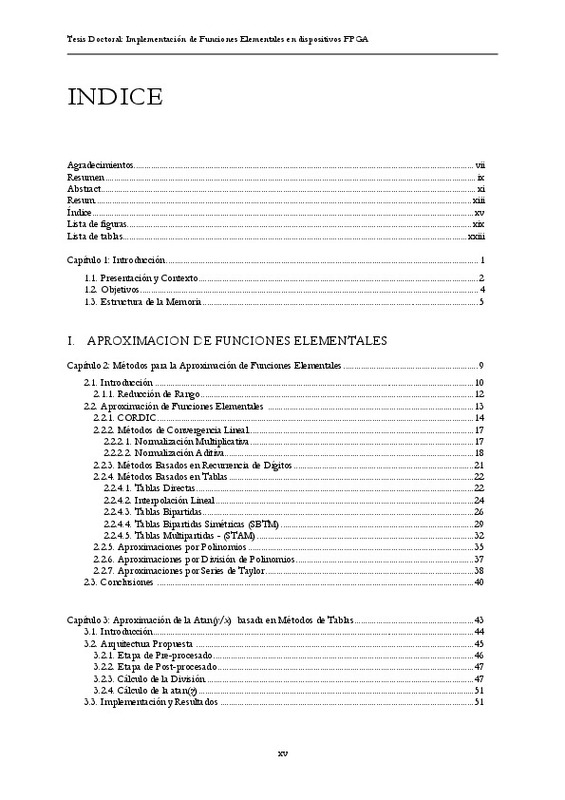

Implementaciones de Funciones Elementales en Dispositivos FPGA

Mostrar el registro sencillo del ítem

Ficheros en el ítem

| dc.contributor.advisor | Valls Coquillat, Javier

|

es_ES |

| dc.contributor.advisor | Torres Carot, Vicente

|

es_ES |

| dc.contributor.author | Gutiérrez Mazón, Roberto

|

es_ES |

| dc.date.accessioned | 2011-09-12T06:40:09Z | |

| dc.date.available | 2011-09-12T06:40:09Z | |

| dc.date.created | 2011-07-19T08:00:00Z | es_ES |

| dc.date.issued | 2011-09-12T06:40:03Z | es_ES |

| dc.identifier.uri | http://hdl.handle.net/10251/11519 | |

| dc.description.abstract | En esta tesis doctoral se han diseñado arquitecturas hardware de algunos subsistemas digitales característicos de los sistemas de comunicaciones de elevadas prestaciones, buscando implementaciones optimizadas para dichos sistemas. El trabajo realizado se ha centrado en dos áreas: la aproximación de funciones elementales, concretamente el logaritmo y la arcotangente, y el diseño de un emulador de canal de ruido Gaussiano aditivo. Las arquitecturas se han diseñado en todo momento teniendo como objetivo lograr una implementación eficiente en dispositivos Field Programmable Gate Arrays (FPGAs), debido a su uso creciente en los sistemas de comunicaciones digitales de elevadas prestaciones. Para la aproximación del logaritmo hemos propuesto dos arquitecturas, una basada en la utilización de tablas multipartidas y la otra basada en el método de Mitchell sobre el que añadimos dos etapas de corrección: una interpolación lineal por rectas con pendientes potencias de dos y mantisa truncada, y una tabla para la compensación del error cometido en la interpolación por rectas. Una primera arquitectura para la aproximación de la atan(y/x) está basada en el cómputo del recíproco de x y en el cálculo de la arcotangente, utilizando básicamente tablas Look-up (LUT) multipartidas. Esta propuesta ya permite reducir el consumo de potencia con respecto a las mejores técnicas recogidas en la bibliografía, como las basadas en CORDIC. Una segunda estrategia para la aproximación de la atan(y/x) está basada en transformaciones logarítmicas, que convierten el cálculo de la división de las dos entradas en una sencilla resta y que hacen necesario el cómputo de atan(2w). Esta segunda estrategia se ha materializado en dos arquitecturas, una primera en la que tanto el logaritmo como el cálculo de atan(2w) se han implementado con tablas multipartidas, combinado además con el uso de segmentación no-uniforme en el cálculo de atan(2w), y una segunda arquitectura que emplea interpolación lineal por tramos con pendientes potencias de dos y tablas de corrección. | es_ES |

| dc.language | Español | es_ES |

| dc.publisher | Universitat Politècnica de València | es_ES |

| dc.rights | Reserva de todos los derechos | es_ES |

| dc.source | Riunet | es_ES |

| dc.subject | Aproximación funciones elementales | es_ES |

| dc.subject | Atan(y/x) | es_ES |

| dc.subject | Logaritmo | es_ES |

| dc.subject | Fpga | es_ES |

| dc.subject | Awgn | es_ES |

| dc.subject | Comunicaciones inalámbricas | es_ES |

| dc.subject.classification | TECNOLOGIA ELECTRONICA | es_ES |

| dc.title | Implementaciones de Funciones Elementales en Dispositivos FPGA | |

| dc.type | Tesis doctoral | es_ES |

| dc.identifier.doi | 10.4995/Thesis/10251/11519 | es_ES |

| dc.rights.accessRights | Abierto | es_ES |

| dc.contributor.affiliation | Universitat Politècnica de València. Departamento de Ingeniería Electrónica - Departament d'Enginyeria Electrònica | es_ES |

| dc.description.bibliographicCitation | Gutiérrez Mazón, R. (2011). Implementaciones de Funciones Elementales en Dispositivos FPGA [Tesis doctoral]. Universitat Politècnica de València. https://doi.org/10.4995/Thesis/10251/11519 | es_ES |

| dc.description.accrualMethod | Palancia | es_ES |

| dc.type.version | info:eu-repo/semantics/publishedVersion | es_ES |

| dc.relation.tesis | 3605 | es_ES |

Este ítem aparece en la(s) siguiente(s) colección(ones)

-

Tesis doctorales [5399]

![Text file [Text]](/themes/UPV/images/text.png)