|

Resumen:

|

Los diseños multi-núcleo se están convirtiendo en la solución más popular a la mayoría de las limitaciones de los diseños mono-núcleo. Un diseño multi-núcleo sigue el paradigma de diseño conocido como Sistema dentro del ...[+]

Los diseños multi-núcleo se están convirtiendo en la solución más popular a la mayoría de las limitaciones de los diseños mono-núcleo. Un diseño multi-núcleo sigue el paradigma de diseño conocido como Sistema dentro del Chip (o SoC , del inglés System on-Chip), en el cuál varios núcleos se integran en un mismo chip. Las prestaciones de un diseño SoC dependen en gran medida de la infraestructura de interconexión que implemente.

En este contexto, el paradigma de diseño conocido como red dentro del chip (o NoC, del inglés Network on-Chip) surge como una solución a los desafíos de interconexión presentes en los nuevos diseños de tipo SoC. Para un diseño concreto, el alto número de posibles soluciones basadas en NoCs incrementa la complejidad de analizar el espacio de diseño y de elegir la NoC óptima. La solución más común a este problema pasa por la utilización de herramientas de alto nivel para la obtención de estimaciones sobre las prestaciones de cada posible solución, que posteriormente serán utilizadas por el diseñador para cribar el espacio de diseño en las primeras etapas del proceso de diseño. Pero hay una gran diferencia entre las prestaciones estimadas por herramientas de alto nivel y las prestaciones reales obtenidas una vez el sistema se implementa.

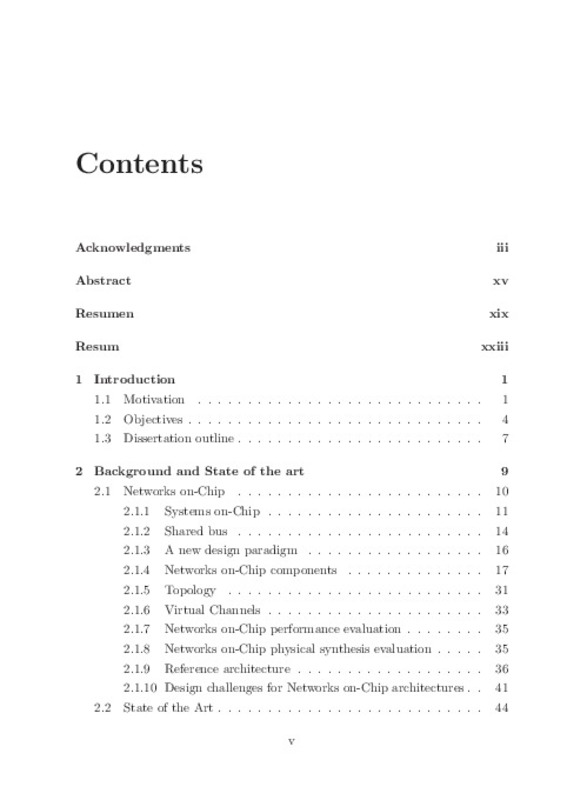

Este trabajo se centra en el desarrollo de nuevas herramientas de alto nivel de diseño, modelado y simulación de NoCs, con el fin de cribar el espacio de diseño de los candidatos menos atractivos. En un primer paso, nos centraremos en el diseño y desarrollo de una plataforma experimental para analizar arquitecturas alternativas para el diseño de NoCs de forma que permitan evaluar cualquier punto del espacio de diseño de forma rápida y precisa, mediante la anotación de algunos parámetros claves del proceso de síntesis física.

En el segundo paso, se revisaron arquitecturas y técnicas de diseño adoptadas del dominio de las redes de interconexión fuera del chip, seleccionando las más prometedoras y, en algunos casos, explotando las características propias de las

redes dentro de chip para obtener nuevas soluciones. Este paso, preliminar al

desarrollo de la herramienta para la realización de exploraciones del espacio

de diseño (o herramientas DSE, del inglés Design Space Exploration), tiene

como objetivo depurar las técnicas para la abstracción de los efectos de la

implementación física de las NoCs sobre sus prestaciones.

[-]

|

![Text file [Text]](/themes/UPV/images/text.png)