- RiuNet repositorio UPV

- :

- Investigación

- :

- Tesis doctorales

- :

- Ver ítem

JavaScript is disabled for your browser. Some features of this site may not work without it.

Buscar en RiuNet

Listar

Mi cuenta

Estadísticas

Ayuda RiuNet

Admin. UPV

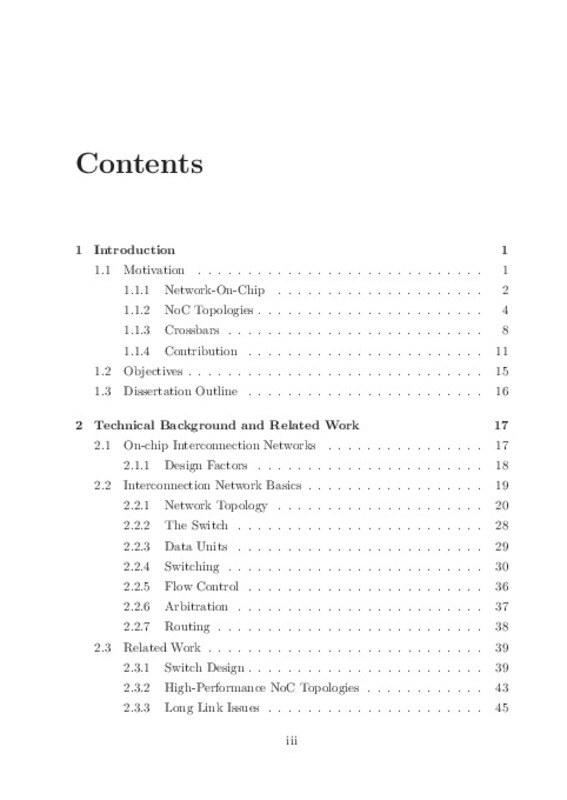

Floorplan-Aware High Performance NoC Design

Mostrar el registro sencillo del ítem

Ficheros en el ítem

| dc.contributor.advisor | Flich Cardo, José

|

es_ES |

| dc.contributor.advisor | Silla Jiménez, Federico

|

es_ES |

| dc.contributor.author | Roca Pérez, Antoni

|

es_ES |

| dc.date.accessioned | 2012-11-20T08:17:15Z | |

| dc.date.available | 2012-11-20T08:17:15Z | |

| dc.date.created | 2012-10-26T08:00:00Z | es_ES |

| dc.date.issued | 2012-11-20T08:17:09Z | es_ES |

| dc.identifier.uri | http://hdl.handle.net/10251/17844 | |

| dc.description.abstract | Las actuales arquitecturas de m�ltiples n�cleos como los chip multiprocesadores (CMP) y soluciones multiprocesador para sistemas dentro del chip (MPSoCs) han adoptado a las redes dentro del chip (NoC) como elemento -ptimo para la inter-conexi-n de los diversos elementos de dichos sistemas. En este sentido, fabricantes de CMPs y MPSoCs han adoptado NoCs sencillas, generalmente con una topolog'a en malla o anillo, ya que son suficientes para satisfacer las necesidades de los sistemas actuales. Sin embargo a medida que los requerimientos del sistema -- baja latencia y alto rendimiento -- se hacen m�s exigentes, estas redes tan simples dejan de ser una soluci-n real. As', la comunidad investigadora ha propuesto y analizado NoCs m�s complejas. No obstante, estas soluciones son m�s dif'ciles de implementar -- especialmente los enlaces largos -- haciendo que este tipo de topolog'as complejas sean demasiado costosas o incluso inviables. En esta tesis, presentamos una metodolog'a de dise-o que minimiza la p�rdida de prestaciones de la red debido a su implementaci-n real. Los principales problemas que se encuentran al implementar una NoC son los conmutadores y los enlaces largos. En esta tesis, el conmutador se ha hecho modular, es decir, formado como uni-n de m-dulos m�s peque-os. En nuestro caso, los m-dulos son id�nticos, donde cada m-dulo es capaz de arbitrar, conmutar, y almacenar los mensajes que le llegan. Posteriormente, flexibilizamos la colocaci-n de estos m-dulos en el chip, permitiendo que m-dulos de un mismo conmutador est�n distribuidos por el chip. Esta metodolog'a de dise-o la hemos aplicado a diferentes escenarios. Primeramente, hemos introducido nuestro conmutador modular en NoCs con topolog'as conocidas como la malla 2D. Los resultados muestran como la modularidad y la distribuci-n del conmutador reducen la latencia y el consumo de potencia de la red. En segundo lugar, hemos utilizado nuestra metodolog'a de dise-o para implementar un crossbar distribuid | es_ES |

| dc.language | Inglés | es_ES |

| dc.publisher | Universitat Politècnica de València | es_ES |

| dc.rights | Reserva de todos los derechos | es_ES |

| dc.source | Riunet | es_ES |

| dc.subject | Noc | es_ES |

| dc.subject | Switch design | es_ES |

| dc.subject | On-chip networks | es_ES |

| dc.subject | Vlsi | es_ES |

| dc.subject.classification | ARQUITECTURA Y TECNOLOGIA DE COMPUTADORES | es_ES |

| dc.title | Floorplan-Aware High Performance NoC Design | |

| dc.type | Tesis doctoral | es_ES |

| dc.identifier.doi | 10.4995/Thesis/10251/17844 | es_ES |

| dc.rights.accessRights | Abierto | es_ES |

| dc.contributor.affiliation | Universitat Politècnica de València. Departamento de Sistemas Informáticos y Computación - Departament de Sistemes Informàtics i Computació | es_ES |

| dc.description.bibliographicCitation | Roca Pérez, A. (2012). Floorplan-Aware High Performance NoC Design [Tesis doctoral]. Universitat Politècnica de València. https://doi.org/10.4995/Thesis/10251/17844 | es_ES |

| dc.description.accrualMethod | Palancia | es_ES |

| dc.type.version | info:eu-repo/semantics/acceptedVersion | es_ES |

| dc.relation.tesis | 3965 | es_ES |

Este ítem aparece en la(s) siguiente(s) colección(ones)

-

Tesis doctorales [5389]

![Text file [Text]](/themes/UPV/images/text.png)